# 次世代データセンターの大容量化／低電力化を実現する光電融合技術

*Opto-electronic Convergence Technology for Achieving High Capacity and Low Power Consumption in Next-generation Data Centers*

白尾瑞基\*

Mizuki Shirao

大畠伸夫\*

Nobuo Ohata

\*情報技術総合研究所(工博)

## 要旨

近年、LLM(Large Language Model)を代表とする生成AIの登場によって、マシンラーニングに必要な演算量が爆発的に増加し続けている。演算量の増加に伴って、AIデータセンターの電力も増加の一途をたどっており、大きな社会課題になっている。この課題に対する一つのソリューションとして、光電融合技術が注目を集めている。電気ICと光デバイスを小型に集積する光電コパッケージは、従来の光トランシーバーでは実現が難しい大容量通信と低消費電力化を実現でき、次世代のAIデータセンターでの導入が期待されている。

## 1. まえがき

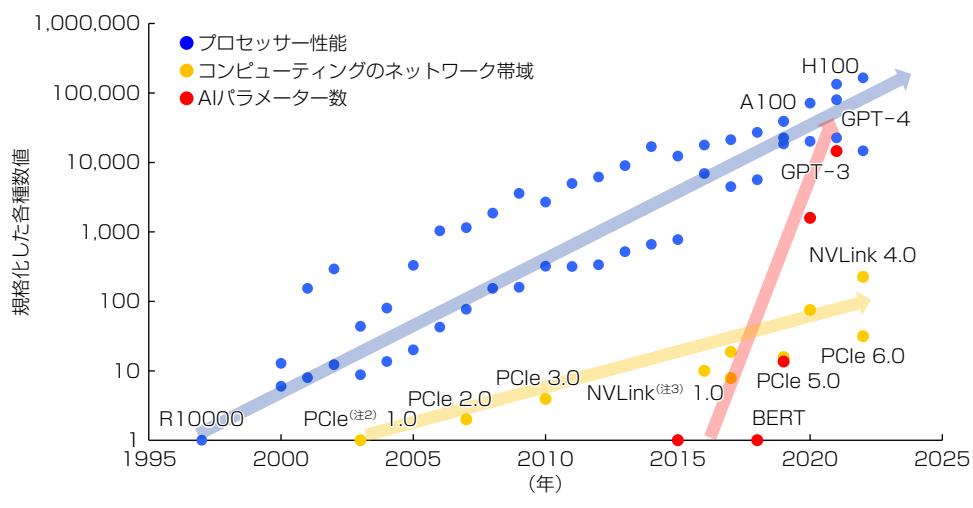

LLMを代表とする生成AIの登場によって、マシンラーニングに必要な演算量が爆発的に増加し続けている。図1はプロセッサーの演算性能(FLOPS)、コンピューティングのネットワーク帯域、マシンラーニングで用いられているパラメーター数をそれぞれ規格化してプロットしたものである<sup>(1)</sup>。マシンラーニングで使用されるパラメーター数は2年で約600倍のペースで増加しており、OpenAI社が開発したGPT-3<sup>(注1)</sup>では機械学習で使用したパラメーター数は1,750億、Switch transformerやGPT-4<sup>(注1)</sup>では1兆以上のパラメーターが使用されている。一方、プロセッサーの演算性能は2年で約2.6倍、コンピューティングに必要なネットワーク帯域も2年で約1.5倍であり、パラメーター数の増加に対してコンピューティングの性能向上は緩やかである。このため、数千を超える多くのGPU(Graphics Processing Unit)を光通信によって並列接続し、クラスター化することで、演算性能を大幅に向上させて、機械学習を実行している。しかし、演算には多くのプロセッサーや光通信機器が必要になり、AIデータセンターでは膨大な電力が必要になっている。

三菱電機はこの課題に対して、光通信の電力効率とネットワーク帯域拡大を両立する光電コパッケージの検討を開始している。本稿では、機械学習に必要なバックエンドネットワークのトレンドや光電コパッケージ形態の技術トレンドを示す。また、これまで開発してきた高速のEML(Electro-absorption Modulator integrated Laser)の特性について述べた後、光電コパッケージへの適用に向けた高集積技術について述べる。

(注1) GPT-3、GPT-4は、OpenAI OpCo, LLCの登録商標である。

(注2) PCIeは、PCI-SIGの登録商標である。

(注3) NVLinkは、NVIDIA Corp.の登録商標である。

図1-プロセッサー性能、コンピューティングネットワーク帯域、AIパラメーター数のトレンド

## 2. AIマシンラーニングのネットワークトレンドと光電コパッケージの導入

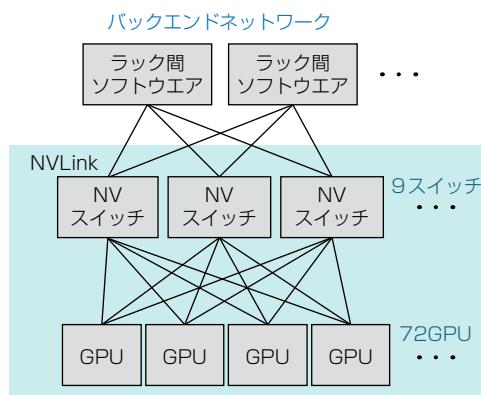

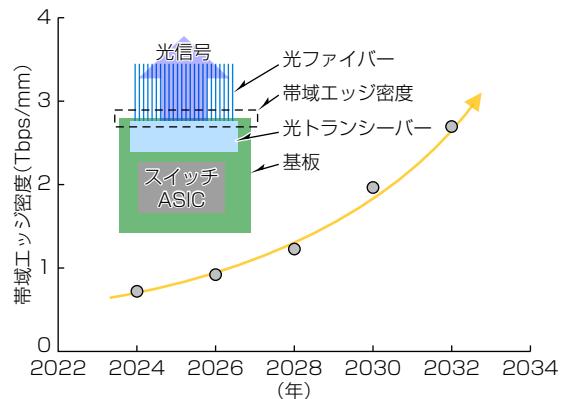

図2にバックエンドネットワークの概念図を示す。複数のスイッチを介することで多くのGPUを並列に接続する構成を取っている。NVIDIA社ではNVスイッチを介して72台のGPUを、NVLinkと呼ばれる独自の高速ネットワークで並列接続しているが<sup>(2)</sup>、今後、演算能力の向上に向けて既存のGPU72台から576台、1,152台にスケールアップが進むと考えられる。GPUやスイッチ間を光通信で接続するための光トランシーバーの数量も増加すると見られており、消費電力が大幅に増加するという課題がある。また、GPUとの接続数が増えることでスイッチASIC(Application-Specific Integrated Circuit)の大容量化も進んで、スイッチASICから出力される信号帯域も合わせて増加する。そのため、光トランシーバーの通信帯域も広帯域化が必要になり、単位長さ当たりどれくらいの信号が取り出せるか、つまり帯域エッジ密度(Tbps/mm)が今後重要な指標になる。図3は、図1に示すトレンドを参考に、帯域エッジ密度を計算した結果である。帯域エッジ密度は2028年には1Tbps/mmが必要になり、2030年には2Tbps/mmと指数関数的に増大する。

図2-バックエンドネットワークの概念図

図3-帯域エッジ密度のトレンド

既存のプラガブル光トランシーバーでは低電力かつ高いエッジ密度を実現することが難しいため、これらの課題を解決する新技術として光電コパッケージが期待されている。表1にプラガブル光トランシーバーと光電コパッケージの比較を示す。プラガブル光トランシーバーはプリント基板上に実装された電気コネクターに接続して使用する構成である。そのため、GPUやスイッチASIC等のロジックICからトランシーバーまで距離が遠く、劣化した電気信号を補正するDSP(Digital Signal Processor)が必要になり、消費電力も大きい。電力効率はおおむね20pj/bitである。また、帯域エッジ

表1-プラガブル光トランシーバーと光電コパッケージの比較

|                   | 実装図 | トランシーバー上面図 | DSP<br>有無 | 電力効率<br>(pj/bit) | 帯域エッジ密度<br>(Tbps/mm) |

|-------------------|-----|------------|-----------|------------------|----------------------|

| プラガブル<br>光トランシーバー |     |            | 有         | 約20              | <0.1                 |

| 光電<br>コパッケージ      |     |            | 無         | 約5               | <2                   |

HBM : High Bandwidth Memory, PIC : Photonic Integrated Circuit

密度は、コネクターによる配線ピッチの制約もあり0.1Tbps/mm以下になる。一方、光電コパッケージはロジックICが搭載されるパッケージ基板上に実装されるため、DSPが不要になり、電力効率は5pj/bitが可能になる。また、微細配線可能な基板上に実装する形態であることから、帯域エッジ密度も2Tbps/mm以下が可能である。さらに将来はSi(シリコン)インターポーラー上に実装する形態も考えられて、その場合、電気のラインアンドスペース上は2Tbps/mmを超える帯域エッジ密度が可能になる。

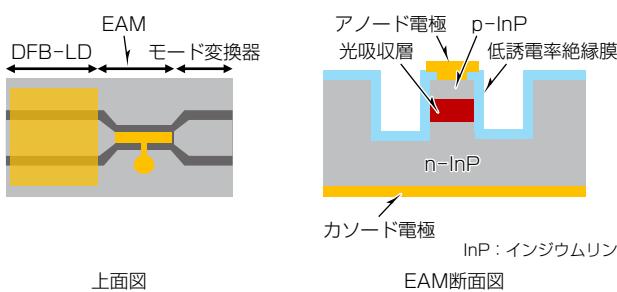

当社はEMLを搭載する光電コパッケージの検討を開始した。EMLはDFB-LD(Distributed Feedback Laser Diode)と、電圧印加によって光を吸収するEAM(Electro Absorption Modulator)をワンチップに集積したレーザー素子である。高密度集積に優れるSiフォトニクス変調器よりも低電力で高速動作が可能であり、更に高い帯域エッジ密度の実現が期待できる。しかしながら、光電コパッケージの場合EMLを高密度に配置する必要があり、高周波配線とEMLをワイヤで接続する従来実装技術では実現困難である。そこで、フリップチップ実装を採用することを検討した。

### 3. 低電力、高エッジ密度実現に向けたEML実装技術

この章では、当社が開発した超高速EML<sup>(3)(4)</sup>について述べて、光電コパッケージへの適用可能なEMLの実装形態とその特性について述べる。

#### 3.1 実装形態

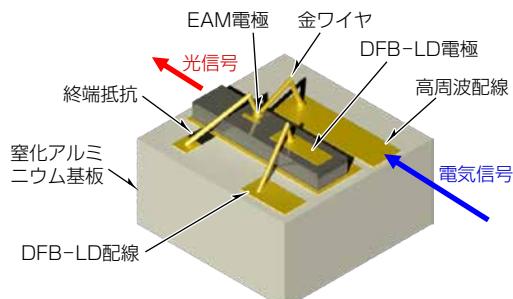

当社EAMは、光吸収層の両側を低屈折率材料で挟んだハイメサ導波路構造を採用した独自構造を持つ(図4)。この構造によって、屈折率の高い光吸収層に光が強く閉じ込められるようになるため、効率的に光を吸収することが可能になる。言い換えると、静電容量の小さなEAMでも十分な光の吸収が得られるため、高速動作が実現できる。EAMはEMLの前方(光信号が出力される側)にあるため、EMLの横側に高周波配線を配置し、金ワイヤを用いてEAM電極へとワイヤボンディングを行うのが一般的である(図5)。ワイヤボンディングは広い実装面積が必要なため、過去の開発ではEML当たり1.25mm程度の幅を占有し、帯域エッジ密度を制約していた。今回、光電コパッケージに求められる高い帯域エッジ密度を達成するため、ワイヤボンディングを用いない実装技術を開発した。

図4-EAMにハイメサ構造を採用したEML

図5-ワイヤボンディングを用いた従来の実装形態

#### 3.2 特性評価

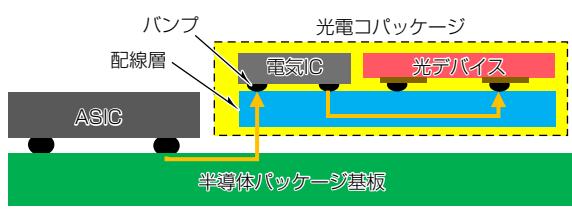

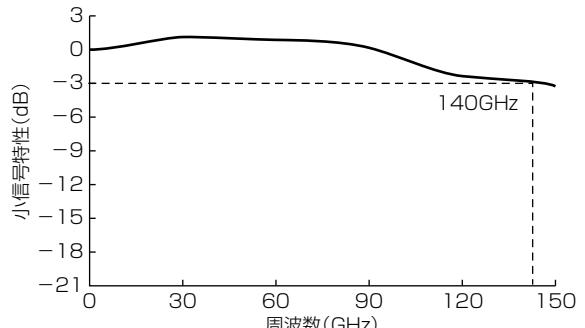

光電コパッケージの形態を図6に示す。光電コパッケージでは、電気ICと光デバイスがフリップチップ技術を用いて実装される。フリップチップ実装では、電極同士をバンプ等によって直接接合するため、図5に示したようなワイヤボンディングを使用しない。これによって、従来の構造に比べて大幅な実装密度の向上が可能になるだけでなく、ワイヤボンディングによる寄生インダクタンス成分がなくなるため、動作速度の向上が期待できる。フリップチップ実装でのシミュレーションでは、145GHzの動作速度が示されている(図7)。

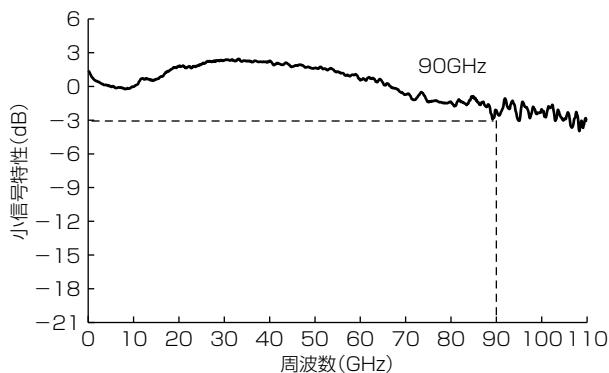

実験的には、窒化アルミニウム基板上へのフリップチップ実装検証によって、90GHzの動作速度を達成した<sup>(5)</sup>。小信号特性を図8に示す。小信号特性には図7では見られない凹凸が観測されており、これは高周波配線でのインピーダンス不整合に起因するものと考えられる。今後、製造技術の進展によってEMLのアレー化が達成されれば、従来の5倍になる0.25mm程度まで高密度化が期待できる。

図6-光電コパッケージでの実装形態

図7-光電コパッケージの動作帯域シミュレーション結果

図8-光電コパッケージを想定した実装でのEMLの小信号特性(5)

### 3.3 今後の展望

次世代データセンターの大容量化に向けた今後の展望として、動作速度の改善に向けたEAM静電容量低減やアレー化を含む素子構造の最適化が必要である。また、低誘電率な基板材料(例：石英基板)を用いることで、更なる動作速度の向上が期待される。これらを達成するとともに、次世代の変調方式である200GBaud PAM4(Pulse - Amplitude - Modulation 4 - Levels)を適用することで、1.6Tbps/mmのエッジ密度達成が見込まれる。

## 4. む す び

バックエンドネットワークと光電コパッケージのトレンドを示すとともに、EMLの特性と光電コパッケージに向けた取組みについて述べた。ハイメサ構造を持つEMLを用いたフリップチップ実装技術によって、光電コパッケージに求められる高い帯域エッジ密度が実現できる。今後、AIマシンラーニングが進展する中で、光電融合技術の重要性は更に増していくと見られており、光デバイス技術の進化に加えて、光エレクトロニクスの実装技術の進化が必要不可欠になる。引き続き次世代の光電融合技術に向けた開発に取り組んでいく。

## 参 考 文 献

- (1) riselab : AI and Memory Wall

<https://medium.com/riselab/ai-and-memory-wall-2cb4265cb0b8>

- (2) NVIDIA : NVLinkとNVSwitch : 最速のHPCデータセンタープラットフォーム

<https://www.nvidia.com/ja-jp/data-center/nvlink/>

- (3) Uchiyama, A., et al. : Demonstration of 155-Gbaud PAM4 and PAM6 Using a Narrow High-Mesa Electro-Absorption Modulator Integrated Laser for 400 Gb/s Per Lane Transmission, Journal of Lightwave Technology, **43**, No.4, 1868~1873 (2025)

- (4) Shirao, M., et al. , High Speed EML and Assembly Techniques for GPU Cluster System, 2025 Optical Fiber Communications Conference and Exhibition, 1~3 (2025)

- (5) Masuyama, K., et al. , EML Assembled with Flip-Chip Technology on AlN Sub-mount Operating at 212.5 Gbps PAM4, OECC 2025, WG2-2 (2025)