## パワー半導体の高効率駆動を実現する最新のデジタルゲート駆動技術

*Cutting-Edge Digital Gate Drive Technology for High-Efficiency Power Semiconductor Operation*

諸熊健一\*

Kenichi Morokuma

高宮 真†

Makoto Takamiya

和田幸彦\*

Yukihiko Wada

山岡祐太\*

Yuta Yamaoka

\*三菱電機(株)先端技術総合研究所

†東京大学

### 要 旨

2050年のカーボンニュートラルの実現に向けて、再生可能エネルギーの利用等、パワーエレクトロニクス機器(以下“パワエレ機器”といふ。)の存在感が増している。現在のパワエレ機器は、パワーデバイスのスイッチング動作を活用した電力変換技術が基盤になる。スイッチング動作で発生する電力損失と電磁ノイズには相反関係があり、この相反関係を改善するデジタルゲート駆動技術が注目されている。

今回、汎用のゲートドライバーICを使って、駆動信号強度を最適なタイミングで3回変化させる駆動方法を東京大学との共同研究で提案した。従来の駆動方式と比較して50Aで25%, 100Aで18%のスイッチング損失(ターンオン時)を低減でき、パワエレ機器の更なる省エネルギーへの貢献が期待できる結果になった。

### 1. まえがき

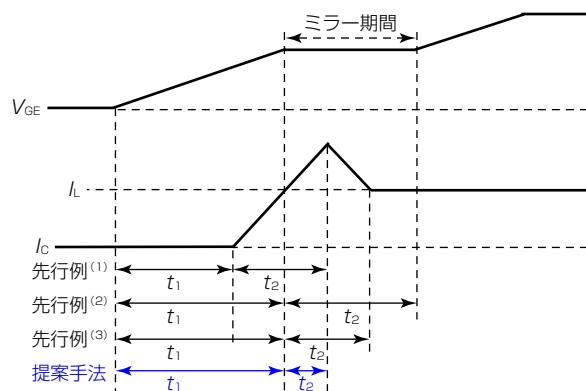

パワーデバイスはゲート駆動信号に応じてスイッチング動作をするが、そのスイッチング動作中に駆動信号強度を複数回離散的に変化させるデジタルゲート駆動技術が注目されている。デジタルゲート駆動技術はパワーモジュールのスイッチング損失と電磁ノイズの相反関係を改善する技術であり、駆動信号強度を変化させるタイミングを負荷電流 $I_L$ や温度等の動作条件に応じて変更できる<sup>(1)</sup>。例えば駆動信号の強度を3回変化させる場合、図1に示すように駆動信号の強度を変化させるタイミング $t_1$ と $t_2$ は、パワーモジュールのターンオン動作時のゲート電圧 $V_{GE}$ とコレクター電流 $I_C$ に対して様々な決定方法が提案されている<sup>(1)(2)(3)</sup>。この開発でのデジタルゲート駆動技術はゲート駆動信号の強度を“強、弱(高インピーダンス), 強”と3回変化させる駆動方法である。この開発では駆動信号の強度を変化させるタイミング $t_1$ と $t_2$ を求める新たな方法を提案し、汎用のゲートドライバーICを用いて $t_1$ と $t_2$ のそれぞれを変化させた評価結果からその妥当性を検証した。

図1-ターンオンでの様々な $t_1$ と $t_2$ の決定方法

### 2. 提案する最適な駆動タイミングの決定手法

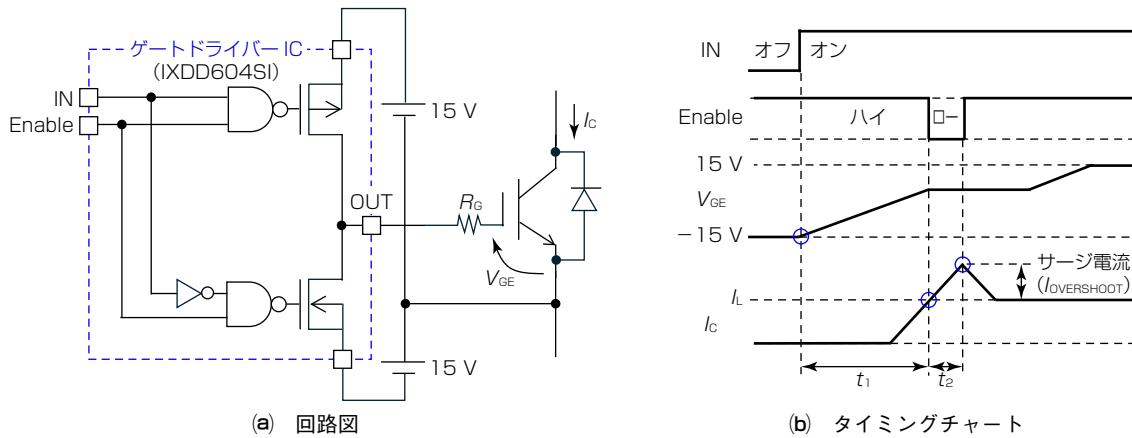

図2に提案手法での回路図とタイミングチャートを示す。Enable付きのゲートドライバーIC(IXDD604SI)を使用し、タイミングチャートの $t_1$ と $t_2$ は入力信号INとEnable信号のタイミングを制御する。Enable信号がローのとき、出力OUT

は高インピーダンスになる。提案手法の $t_1$ は $V_{GE}$ の立ち上がりエッジから $I_c$ が負荷電流 $I_L$ になるまでの時間である。 $t_2$ は $I_c$ が負荷電流 $I_L$ になったときからピーク値になるまでの時間であり、パワーモジュールの動作条件が変わると $t_1$ と $t_2$ も変化する。提案手法の $t_1$ と $t_2$ は、測定した $V_{GE}$ と $I_c$ の波形から算出する。

図2-提案手法の回路図とタイミングチャート

従来のゲート駆動回路(以下“従来手法”という。)では、ゲート抵抗 $R_G$ を変化させながらスイッチング損失 $E_{LOSS}$ とサージ電流 $I_{OVERSHOOT}$ のトレードオフカーブを取得する。提案手法での損失低減率を式(1)で定義する。 $E_{LOSS, DGD}$ は提案手法でのスイッチング損失である。 $E_{LOSS, CONV}$ は従来手法でのスイッチング損失であり、提案手法と同程度のサージ電流で比較するため、従来手法で取得したトレードオフカーブの近似曲線から計算する。

$$\text{損失低減率} = \frac{E_{LOSS, CONV} - E_{LOSS, DGD}}{E_{LOSS, CONV}} \times 100 \quad \dots \dots \dots (1)$$

### 3. 評価方法

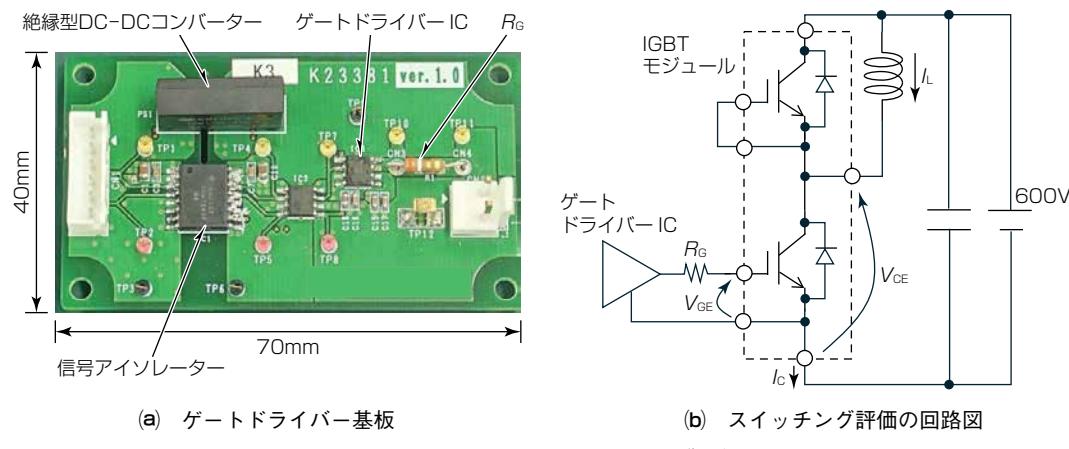

図3にゲートドライバー基板とスイッチング評価の回路図を示す。ゲートドライバー基板は信号アイソレーターと絶縁型DC-DCコンバーターを搭載する。評価対象にはIGBT(Insulated Gate Bipolar Transistor)モジュール(CM100DY-24T, 定格: 1,200V, 100A)を用いた。提案手法と従来手法、及び先行例<sup>(1)(2)(3)</sup>で提案されている $t_1$ と $t_2$ の決定手法でそれぞれ測定した。提案手法では $t_1$ と $t_2$ を2ns間隔で2,400通りの組合せで依存性を測定し、提案手法の妥当性を検証した。

図3-ゲートドライバー基板とスイッチング評価の回路図

## 4. 評価結果

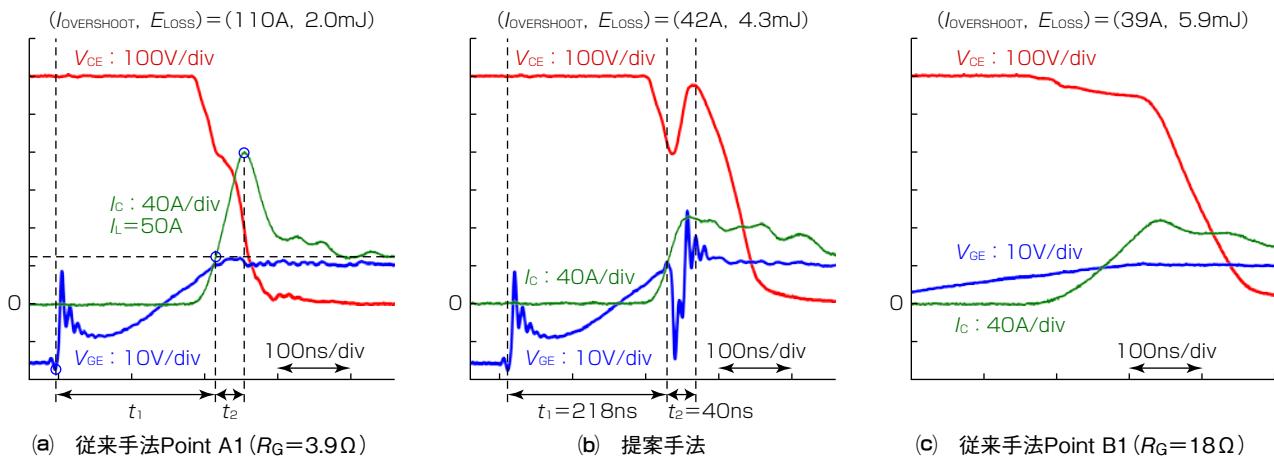

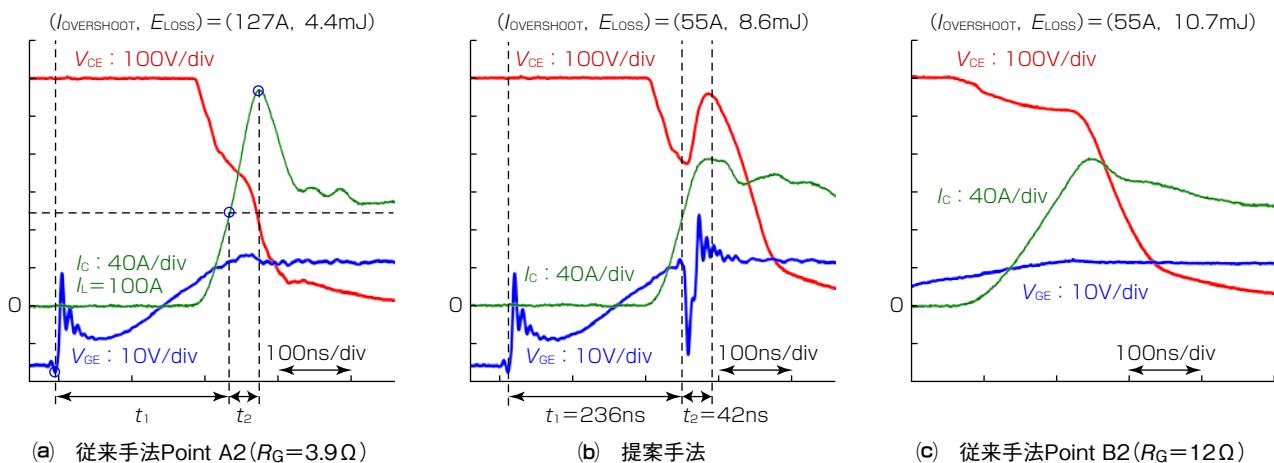

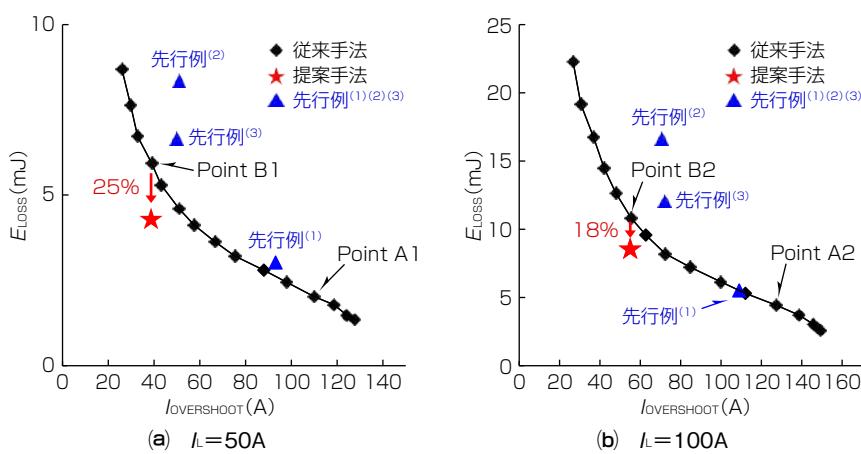

図4と図5に負荷電流  $I_L = 50A$  と  $100A$  での提案手法と従来手法のスイッチング波形をそれぞれ示す。これらのスイッチング波形からスイッチング損失とサージ電流を求めて、先行例<sup>(1)(2)(3)</sup>の結果を含めて相反関係を比較する。提案手法の  $t_1$  と  $t_2$  は従来手法のゲート抵抗  $R_G$  を  $3.9\Omega$  としたときのスイッチング波形から算出した。図6が負荷電流  $I_L = 50A$  と  $100A$

図4-  $I_L = 50A$ での提案手法と従来手法のスイッチング波形

図5-  $I_L = 100A$ での提案手法と従来手法のスイッチング波形

図6-スイッチング損失  $E_{LOSS}$  とサージ電流  $I_{OVERSHOOT}$  の評価結果

での提案手法と従来手法、及び先行例<sup>(1)(2)(3)</sup>でのスイッチング損失 $E_{LOSS}$ とサージ電流 $I_{OVERSHOOT}$ の評価結果である。提案手法では、サージ電流 $I_{OVERSHOOT}$ を従来手法と同程度に維持しつつ、負荷電流 $I_L = 50A$ ではスイッチング損失 $E_{LOSS}$ を25%、100Aでは $E_{LOSS}$ を18%低減した。なお、先行例<sup>(1)(2)(3)</sup>では従来手法よりも $E_{LOSS}$ が増大する結果になった。

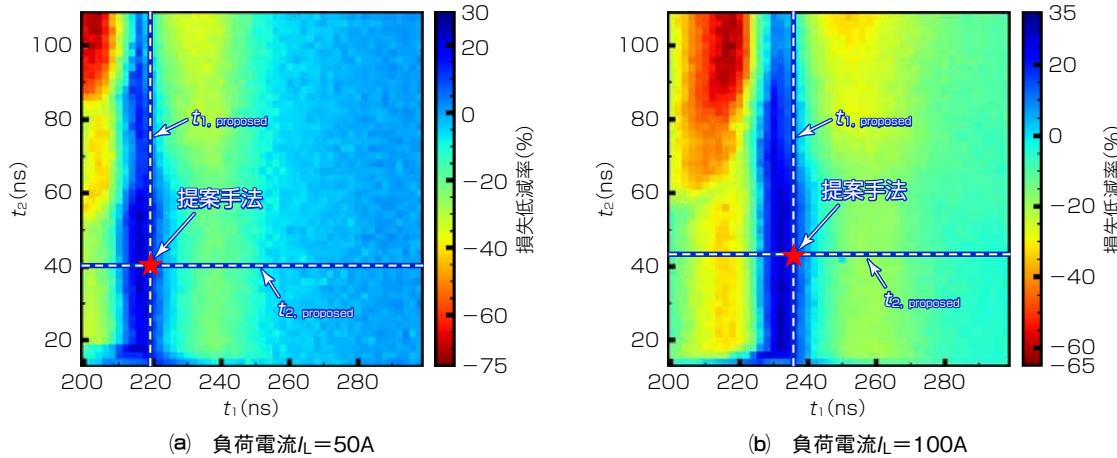

図7に負荷電流 $I_L = 50A$ と100Aでの損失低減率の $t_1$ と $t_2$ の依存性を示す。損失低減率は $t_1$ 依存性が非常に大きく $t_2$ 依存性は小さいことから、 $t_1$ の最適化が重要であることが分かる。提案手法では、損失低減率への影響が大きい $t_1$ の最適値を得ることができて、先行例<sup>(1)(2)(3)</sup>よりも損失の低減効果が高い結果を得ることができた。表1に温度 $T_j$ を25°Cと75°C、及び125°Cとしたときの提案手法と先行例<sup>(1)(2)(3)</sup>での損失低減率の評価結果を示す。温度 $T_j$ を75°Cと125°Cとした条件下でも、提案手法は先行例<sup>(1)(2)(3)</sup>よりも損失の低減効果が高くなることを確認した。

図7-損失低減率の $t_1$ と $t_2$ の依存性

表1-提案手法と先行例<sup>(1)(2)(3)</sup>の損失低減率

|                        | $I_L = 50A$        |                    |                     | $I_L = 100A$       |                    |                     |

|------------------------|--------------------|--------------------|---------------------|--------------------|--------------------|---------------------|

|                        | $T_j = 25^\circ C$ | $T_j = 75^\circ C$ | $T_j = 125^\circ C$ | $T_j = 25^\circ C$ | $T_j = 75^\circ C$ | $T_j = 125^\circ C$ |

| 提案手法(%)                | 25                 | 23                 | 16                  | 18                 | 26                 | 27                  |

| 先行例 <sup>(1)</sup> (%) | -20                | -10                | -9                  | 0                  | -2                 | -1                  |

| 先行例 <sup>(2)</sup> (%) | -84                | -64                | -50                 | -95                | -96                | -70                 |

| 先行例 <sup>(3)</sup> (%) | -43                | -75                | -64                 | -45                | -78                | -90                 |

## 5. む す び

デジタルゲート駆動技術で、駆動信号の強度を変化させるタイミングを決定する新たな方法を提案した。提案手法の損失の低減効果が最も高く、その妥当性を実証した。

今後、提案手法の実用化に向けて継続して開発を進めて、パワエレ機器の省エネルギー化に貢献する。

## 参 考 文 献

- (1) Zhang, F., et al.: Advanced Active Gate Drive for Switching Performance Improvement and Overvoltage Protection of High-Power IGBTs, IEEE Transactions on Power Electronics, **33**, No.5, 3802~3815 (2017)

- (2) Camacho, P.A., et al.: A Novel Active Gate Driver for Improving SiC MOSFET Switching Trajectory, IEEE Transactions on Industrial Electronics, **64**, No.11, 9032~9042 (2017)

- (3) Manuel, R., et al.: Implementation of Current-Source Gate Driver with Open-Loop Slope Shaping for SiC-MOSFETs, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 1~8 (2021)