# 高周波半導体デバイスの自律的バイアス制御技術

Autonomous Bias Control Technology for High-Frequency Semiconductor Devices

\*情報技術総合研究所(博士(工学))

## 要旨

レーダー・通信システムへの適用が検討されている高耐電力なGallium Nitride(GaN:窒化ガリウム)低雑音増幅器(Low Noise Amplifier:LNA)は半導体欠陥(トラップ)の影響で過入力直後のロバストな動作の実現が難しかった。これを解決するために、トランジスター自身のトラップを利用してバイアス電圧を自律的に変化させることによって、出力電力の過渡的な変化 $\Delta P_{out}$ を抑制し、ロバストな動作を可能にする回路を開発した。この回路を試作・検証した結果、室温(300K)で $\Delta P_{out}$ を2.4dBから0.2dBに低減し、高温(350K)でも1.9dBから0.2dBに低減し、この回路の有効性を確認した。

## 1. まえがき

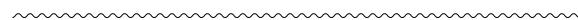

レーダー・通信システムの高周波モジュールで送信側の高出力増幅器(High Power Amplifier:HPA)にGaNを適用するだけでなく、受信側のLNAにもGaNを適用することが検討されている。図1に、LNAにGaNを適用したときの利点と課題を示す。GaN適用の利点は従来のGallium Arsenide(GaAs:ガリウムヒ素)よりも高耐電力なGaNに置き換えることで想定外の過入力からLNAを保護するためのリミッター回路が不要になることである。これによってGaAsに比べてGaNは高周波モジュール全体としての受信感度向上及び低コスト化を実現できる。一方、置き換えに向けたGaN LNAの技術的な課題の一つがリカバリー特性の改善である。リカバリー特性はLNAへの想定外の過入力の直後にGaNトランジスター内のトラップの影響で出力電力 $P_{out}$ が $\mu\text{s}$ からmsのオーダーで過渡的に変化する。これはGaN特有の課題であり、ロバストな動作を阻害する要因になっている。

本稿ではGaN LNAのリカバリー特性の改善のために独自に開発した自律的バイアス制御回路について概要を述べる。詳細については参考文献(1)を参照されたい。

SiN: 塗化ケイ素, AIGaN: 塗化アルミニウムガリウム, SiC: シリコンカーバイド

図1-NAにGaNを適用したときの利点と課題

## 2. 自律的バイアス制御回路

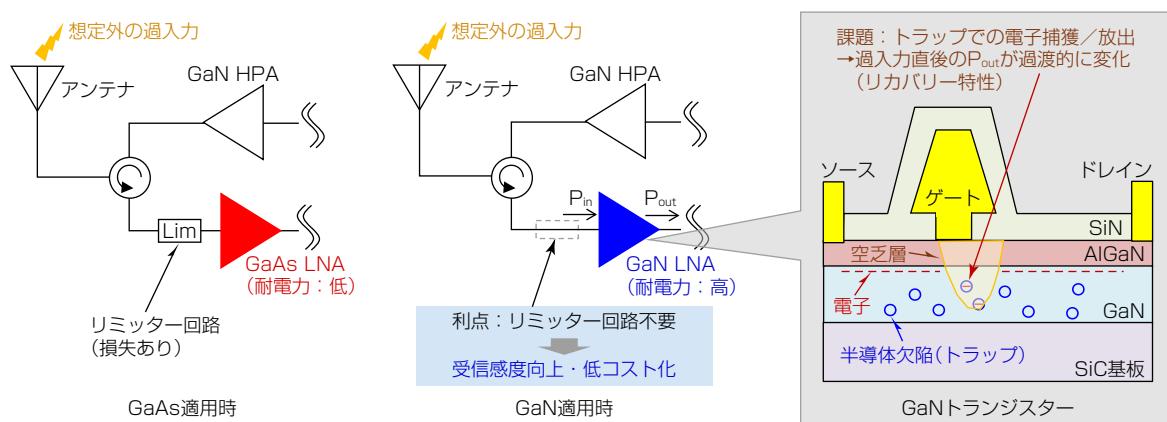

図2に、開発した自律的バイアス制御回路のコンセプトを示す。図2(a)に回路構成を示しており、開発した自律的バイアス制御回路はLNAのゲートバイアス電圧 $V_{g0}$ を自律的に変化させる。入力電力 $P_{in}$ のレベルに応じて電圧レベル調整回

路で  $V_{ga}$  及び  $V_{gb}$  を出力し、それらの電圧がこの回路に入力される。そして、この回路では  $P_{in}$  に基づく  $V_{ga}$  及び  $V_{gb}$  の変化に応じて過入力直後の  $V_{g0}$  のレベルを変化させる。図2(b)に  $P_{in}$ ,  $V_{g0}$ ,  $P_{out}$  のタイムチャートを示す。この回路を適用しない場合、LNAのゲートバイアス電圧  $V_{g0}$  は一定である。その場合、過入力直後トラップの影響でLNAの出力電力  $P_{out}$  が一時的に低下し過渡的に回復するリカバリー特性を示す。すなわち、この回路適用なしの場合、 $\Delta P_{out}$  が大きい。一方、この回路を適用した場合、過入力直後の  $V_{g0}$  は定常状態よりも高くなり、時間経過で定常状態に戻る。また、その時定数はこの回路を適用しない場合に生じる  $P_{out}$  の過渡的変化の時定数と同程度になる。このように  $V_{g0}$  の自律的な変化によってトラップの影響を補償して過入力直後の  $\Delta P_{out}$  を低減し、リカバリー特性を改善することが可能になる。

図2-自律的バイアス制御回路のコンセプト<sup>(1)</sup>

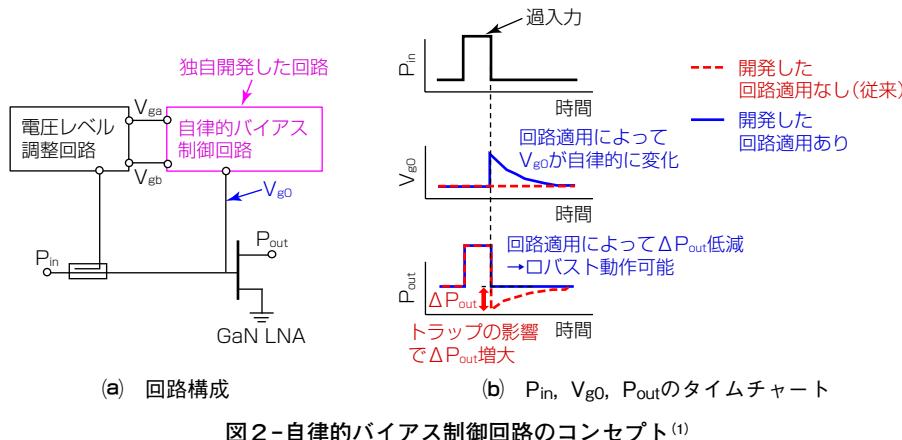

図3に自律的バイアス制御回路の回路図を示す。LNA内の補償対象となるトランジスター(Tr)はTr0とする。自律的バイアス制御回路は主にスイッチング用トランジスターTr1, ストレス印加用トランジスターTr2, 抵抗R0, R1, R2, R3で構成されている。図3に示すように、これらのトランジスターは同じGaNチップ上に製造されるため、それぞれのTrは同じ特性のトラップを持つ。この回路では、 $V_{ga}$  及び  $V_{gb}$  が過入力時にストレスバイアスとしてTr2のドレイン及びゲートに印加され、過入力後にTr2のオン抵抗がトラップの影響によって過渡的に変化する。このTr2のオン抵抗の変化を利用して、過渡的に変化する電圧  $V_{g0}$  を生成できる。Tr2はTr0自身と同じ特性のトラップを持つため、 $V_{g0}$  の時定数は、この回路を適用しないときの  $P_{out}$  の時定数とほぼ同じになる。そのため、この回路は  $V_{g0}$  の適切なバイアス変化を自律的に生み出すことが可能になり、トラップの影響を補償してリカバリー特性を改善できる。さらに環境温度  $T_{amb}$  が変化したときトラップの物理的な特性の変化によって時定数が変化するが、この回路ではTr0内のトラップと同様にTr2内のトラップも物理的に変化するため、環境温度の変化にも自律的に対応することができる。Tr1はスイッチとして用いられ、 $V_{gb}$  をTr1のゲートに印加することで、必要なタイミングで所望の  $V_{g0}$  を得ることができる。抵抗R0, R1, R2, R3はTr0, Tr1, Tr2に所望の電圧が印加されるように設計されるパラメーターである。

図3-自律的バイアス制御回路の回路図<sup>(1)</sup>

### 3. 回路設計

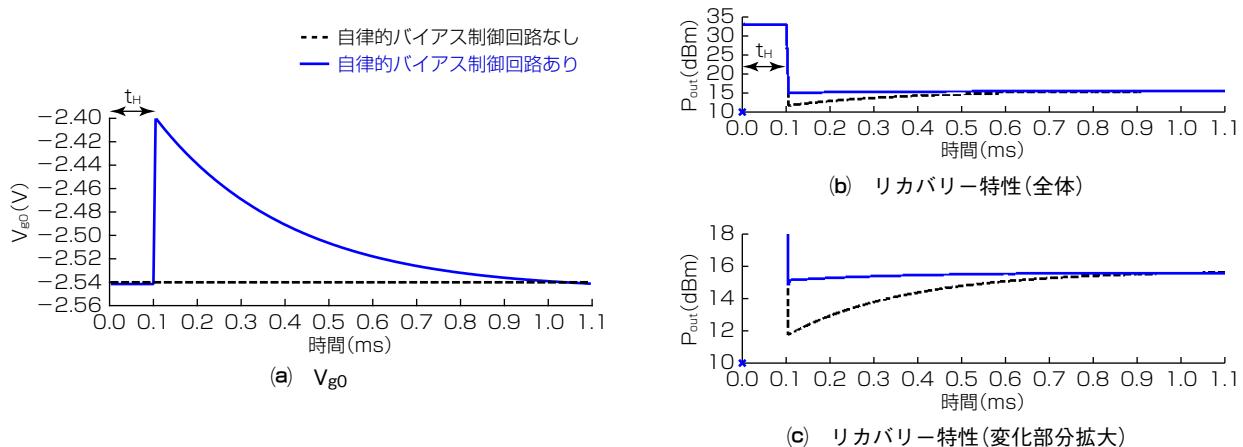

自律的バイアス制御回路を設計し、シミュレーションでその効果を検証した。回路設計でTr0, Tr1, Tr2に所望の電圧が印加されるように抵抗R<sub>0</sub>, R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>を設計した。図4に、設計した回路のリカバリー特性及びV<sub>g0</sub>のシミュレーション結果を示す。シミュレーションにはトラップの影響を考慮した大信号モデルを用いた<sup>(2)</sup>。周波数は28GHz、ドレイン電圧V<sub>d</sub>は24V、アイドルドレイン電流I<sub>dq</sub>は50mA/mm、過入力時間t<sub>H</sub>は100μsである。過入力時のP<sub>in</sub>は25dBmであり、定常時のP<sub>in</sub>は3dBmである。過入力時の(V<sub>ga</sub>, V<sub>gb</sub>)は(13.3V, -8.9V)に設定し、定常時の(V<sub>ga</sub>, V<sub>gb</sub>)は(-5.7V, -1.95V)に設定した。図4(a)に示すように、自律的バイアス制御回路なしのときのV<sub>g0</sub>は一定であるが、回路ありのときは過入力直後のV<sub>g0</sub>は定常状態よりも高く、時間経過で定常状態に戻ることを確認した。また、図4(b)(c)に示すように、この回路を適用することで△P<sub>out</sub>が低減し、リカバリー特性が改善することを確認した。

図4-設計した回路のリカバリー特性及びV<sub>g0</sub>のシミュレーション結果<sup>(1)</sup>

### 4. 試作・検証

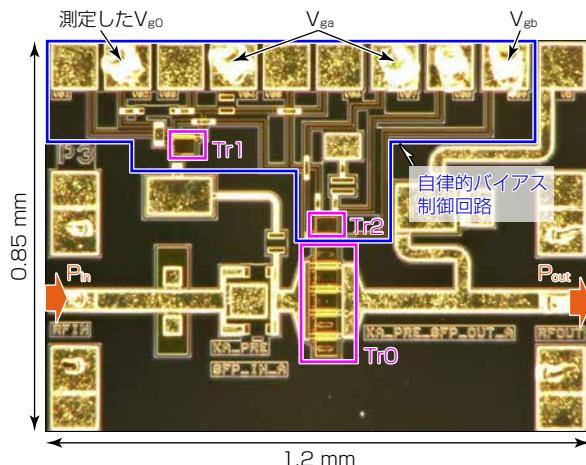

自律的バイアス制御回路を試作し、その有効性について原理検証を行った。図5に試作したGaNチップの写真を示す。チップ内のトランジスター(Tr0, Tr1, Tr2)は三菱電機製のゲート長0.19μmのGaN High Electron Mobility Transistorである。基板は50μm厚のSiCである。このチップはリカバリー特性を測定するためのTest Elementary Groupであり、Tr0の入力と出力に利得整合のプリマッチ回路を接続している。整合回路には薄膜抵抗、エビ抵抗、及び金属絶縁体金属コンデンサーを使用している。図5に示すように、Tr1とTr2を含む自律的バイアス制御回路は、Tr0と同じチップ上に製造され、Tr0のゲートに接続されている。P<sub>in</sub>のレベルに基づいて変化するV<sub>ga</sub>とV<sub>gb</sub>が自律的バイアス制御回路に入力される。Tr0のゲート幅は8フィンガー×52μmであり、自律的バイアス制御回路内のTr1とTr2のゲート幅は1フィンガー×52μmである。

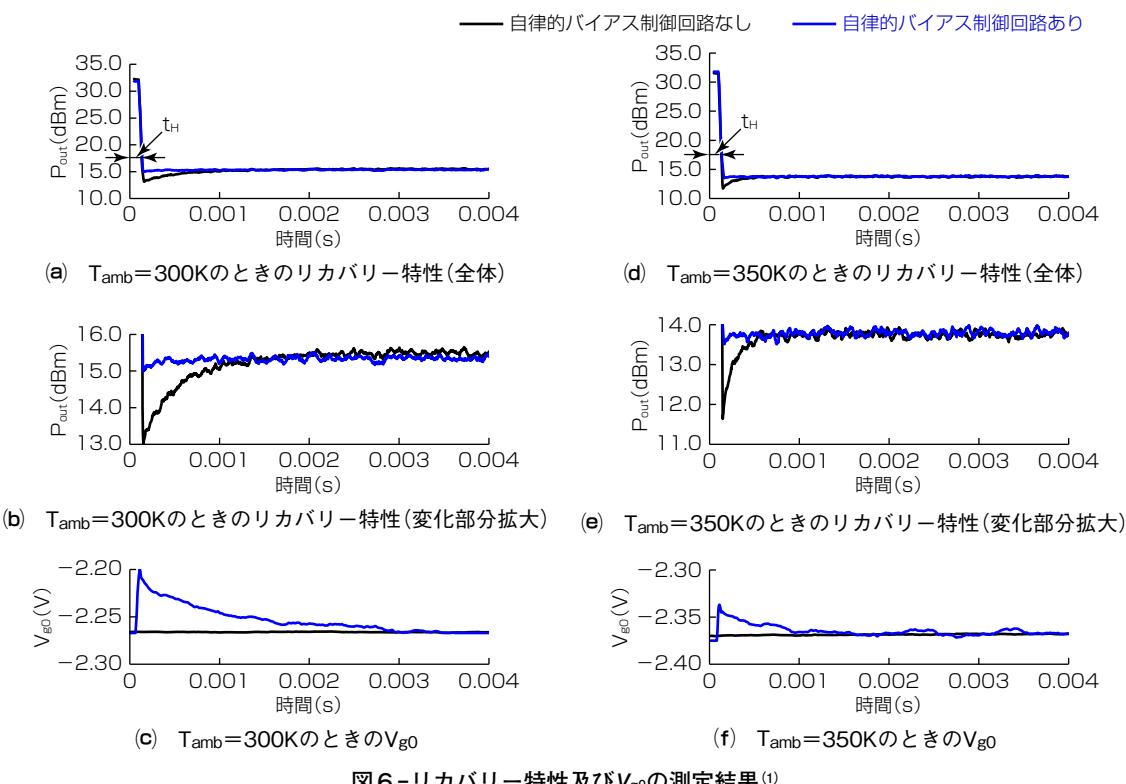

図6にリカバリー特性及びV<sub>g0</sub>の測定結果を示す。周波数は28GHz、V<sub>d</sub>は24V、I<sub>dq</sub>は50mA/mm、過入力時間t<sub>H</sub>は150μsである。過入力時のP<sub>in</sub>は25dBmであり、定常時のP<sub>in</sub>は3dBmである。図6(a)(b)に示すように、T<sub>amb</sub> = 300Kで自律的バイアス制御回路なしの△P<sub>out</sub>は2.4dB程度であるが、回路ありの△P<sub>out</sub>は0.2dB程度まで低減していることを確認した。また、図6(c)で示すように、自律的バイアス制御回路なしのときのV<sub>g0</sub>は常に一定であるが、回路ありのとき、過入力直後のV<sub>g0</sub>は定常状態よりも高く、時間経過で定常状態に戻ることを確認した。その時定数はP<sub>out</sub>の時定数とほぼ同じである。その結果、入力電力に応じたV<sub>g0</sub>の自律的な変化によってTr0のトラップの影響を適切に補償し、リカバリー特性を改善することを確認した。また、T<sub>amb</sub> = 350Kでも自律的バイアス制御回路なしの△P<sub>out</sub>は1.9dB程度であるが、回路ありの△P<sub>out</sub>は0.2dB程度まで低減していることを確認した(図6(d)(e))。高温になると、トラップの電子を放出する時定数が短くなるため、回路なしのときのP<sub>out</sub>の時定数は、T<sub>amb</sub> = 300Kのときよりも短くなるが、回路適用時のV<sub>g0</sub>の時定数も同様に高温で短くなる(図6(f))。そのため、高温時でもこの回路はトラップの影響を適切に補償できる。環境温度が

変化したときでも、環境温度に応じた $V_{g0}$ の自律的な変化によってリカバリー特性が改善することを確認した。これらの結果から、この回路は原理的に有効であることを確認した。

図5-試作したGaNチップ<sup>(1)</sup>

図6-リカバリー特性及び $V_{g0}$ の測定結果<sup>(1)</sup>

## 5. むすび

GaN LNAのリカバリー特性の改善に向けて独自に開発した自律的バイアス制御回路について述べた。この回路は入力電力や環境温度が変化してもトラップの影響を自律的に補償し、ロバストな動作を実現できることを確認した。また、この回路はLNAと同じGaNチップ上に構成されるため、従来必要とされたリミッター回路に比べてコスト面でも有利であり、GaAs LNAに対するGaN LNAの優位性を維持できる。

今後はこの回路のレーダー用高周波モジュールへの実装を検討する。また、この回路を5G(第5世代移動通信システム)基地局GaNモジュールへ応用展開し、トラップが要因で劣化する歪(ひずみ)特性の改善を検討する。

## 参考文献

- (1) Yamaguchi, Y. et. al. : Trapping Compensation for Transient Recovery in GaN LNAs, IEEE Transactions on Microwave Theory and Techniques, **72**, No.7, 4006~4016 (2024)

- (2) Yamaguchi, Y. et. al. : Ka-Band GaN Large-Signal Model Considering Trap Effect on Nonlinear Capacitance by Using Transient S-Parameters Measurement, IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (2018)