# 特集論文

## 基板チェックツールによるEMC・信号伝送設計の業務効率化と品質向上

Improving Operational Efficiency and Quality in EMC and Signal Transmission Design Using Printed Circuit Board Check Tools

中村彰伸\*

Akinobu Nakamura

直海佑司†

Yuuji Naomi

青木俊彦†

Toshihiko Aoki

櫻井浩希‡

Hiroki Sakurai

小林和博†

Kazuhiro Kobayashi

\*三菱電機㈱ 設計システム技術センター

†同社 鎌倉製作所

‡三菱電機エンジニアリング㈱

### 要 旨

製品の高性能化・高機能化に伴い、プリント基板設計に起因するEMC(ElectroMagnetic Compatibility：電磁両立性)・信号伝送の設計手戻りは、従来製品と比較して増大傾向にある。プリント基板設計に起因する設計手戻り抑制のため、従来は目視でプリント基板の部品実装、配線を検証していた。今後、更なる製品の高性能化・高機能化によって目視での検証には膨大な時間を要することが懸念されている。三菱電機ではこの問題を解決するため、基板設計上の設計制約を自動的に検証する基板チェックツールを導入している。

今回、このツールを効率的に運用する手法を開発し、基板検証時間短縮と設計品質向上の見込みを得た。今後は、開発した手法を充実化し、EMC・信号伝送設計業務の効率化、基板設計品質の向上を図る。

### 1. まえがき

三菱電機開発製品での近年の特長として、SDRAM(Synchronous Dynamic Random Access Memory)に代表されるメモリーの通信周波数の高速化や製品の小型化、高機能化に伴う高密度化がある。これによって、EMC及び信号伝送の設計手戻りは、従来製品と比較して増大傾向にある。プリント基板上の部品配置、配線はEMCや信号伝送路の品質を決定付ける重要な要素である。試作前の設計段階で、手戻りを発生させない設計にするため、SI(Signal Integrity)解析や電磁界解析といったシミュレーションを積極的に活用している。SI解析では、使用するIC(Integrated Circuit)とプリント基板配線の簡易モデルを使用したプリ解析と、実際のプリント基板配線モデルを使用するポスト解析を行う方法が主流である。また、電磁界解析では、2.5次元や三次元の電磁界解析を活用してEMCリスクを低減する設計手法の開発が進められている<sup>(1)</sup>。しかし、あらゆる信号伝送路やEMC問題に対して、SI解析や電磁界解析を適用して全てを検証することは技術的にも時間的にも困難である。そのため、プリント基板の設計制約を定めて、EMC・信号伝送の不具合が発生するリスクを低減する方法が取られている。

このようにプリント基板の設計制約を定めた上で、部品実装、基板配線といったプリント基板の設計作業を行い、最終的に設計制約を遵守した基板設計になっているかを検証する必要がある。この検証に関して、一般的にはチェックリストに基づいて目視で確認する手法が取られている。昨今、プリント基板の高速化・高密度化に伴い設計制約は厳しくなり、チェック項目が増大傾向である。このため、目視での検証に膨大な時間を要して、検証漏れや判断ミスなど人為的な理由による設計手戻りが発生しやすい。このままでは、検証要員の増員が必要になり、さらに、増員した人員の教育も不可欠になる。

三菱電機ではこのような状況に対して、基板設計の設計制約を遵守しているか自動的に検証する基板チェックツールの導入を進めている。以前から存在するツールではあったが、設定の煩雑さや検証精度といった問題があり十分活用できていなかった。これらの問題に対して、ツールを効率的に運用する手法を開発し、宇宙事業製品に適用した結果、基板設計の検証時間短縮と品質向上の見込みを得た。

### 2. 基板設計での設計制約

#### 2.1 設計制約

プリント基板上の部品配置と配線は、EMCや信号伝送路の品質を決定づける重要な要素である。基板設計の前工程である回路設計までが十分であっても、基板設計が不十分であればEMC及び信号伝送の設計不具合を引き起こす。これら

の不具合を抑制するために数十種類に及ぶ様々な基板設計制約を規定している。

この章では、設計制約の例を2例述べる。

図1は一般的にスリット跨(また)ぎと呼ばれる設計制約である。信号が同一のリファレンスグランド(以下“GND”という。)になっているかを確認する。図1のNG例のように分断するリファレンスGNDに配線する信号は各種のEMC問題を引き起こす要因になる。そのため、GNDパターンを分断する構成になっていないか確認する必要がある。

図1-スリット跨ぎ配線

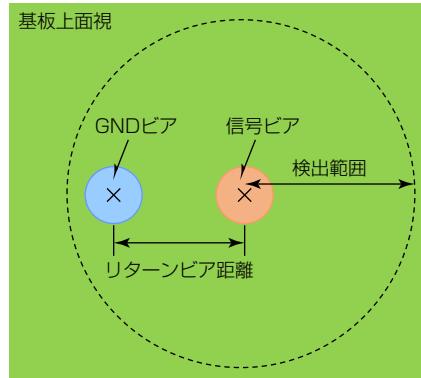

図2はリターンビアと呼ばれる設計制約である。GNDに流れる信号のリターン電流を最短で発生源側に戻すことが品質確保のためには必要であり、GNDビアを信号ビアの近傍に設ける必要がある。複数の層にわたって信号を配線する必要がある場合、信号ビアの所定以内の距離にGNDビアを設けているか確認する。

図2-リターンビア

## 2.2 設計制約検証での問題点

三菱電機製品でのプリント基板は、配線層当たりの信号が数十から数百本、ビアが信号の数倍あり、かつ、信号配線層が多い場合十数層になる。配線層ごとに各々の信号・ビアや実装部品が設計制約を遵守しているか確認する必要があるが、膨大な組合せがある信号・ビア、実装部品と設計制約に対して、一つ一つを目視で検証することは困難な作業である。また、今後、製品の高性能化・高機能化によってプリント基板の設計制約や検証対象になる信号やビアは更に増加し、効率的な開発が困難になる。

## 3. 基板チェックツール

### 3.1 基板チェックツールの概要

2.節に述べた問題を解決する手段として基板チェックツールの活用がある。これによって基板の設計制約を自動的に検証できるようになる。例えば、2.1節に述べたスリット跨ぎやリターンビアを自動的に検証できる。

スリット跨ぎの場合、チェックする対象信号を指定して、信号とGNDパターンが常に層間で隣接している構成になっているかを判定する。隣接していない部分がある場合はNGになる。リターンビアの場合、図3のように、対象信号の信号ビアとGNDビアの距離のしきい値(検出範囲)を決めて検証する。しきい値以内にGNDビアがない場合はNGになる。

図3-リターンビアのチェック内容

### 3.2 基板チェックツールの効果

ツールは、所定の検出ルールに従い、実装部品、配線が制約を満足しているか機械的にチェックしている。そのため、設計制約を満足していない実装部品、配線を短時間で漏れなく抽出できる。例えば、3.1節に記載のリターンビアという設計制約に関して、プリント基板の配線・ビアが多い場合には、全てを目視でチェックすると数時間要するが、ツールでは数分で検証できる。

### 3.3 基板チェックツール運用上の問題

3.2節に述べたように、ツールは検証時間の短縮と確実な検証が期待できる。三菱電機は多種多様のプリント基板を限られた期間内に開発している。限られた期間内に限られた人員で十分な検証をするには、ツールを効率的に運用する必要がある。

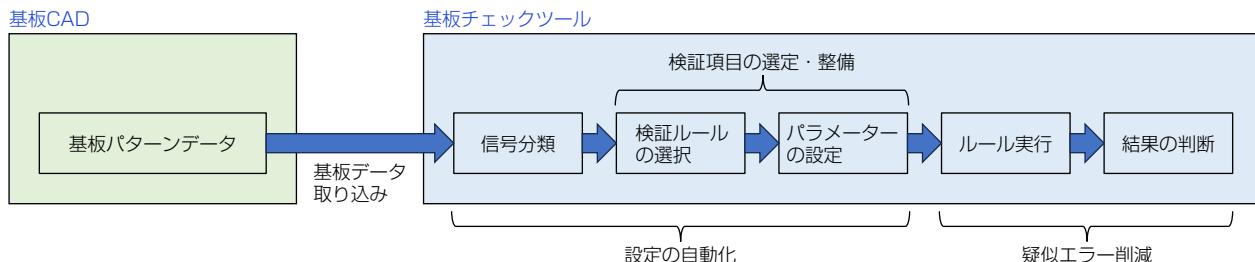

図4は、ツールを用いた検証フローである。まず、基板CAD(Computer Aided Design)で作成した基板データをツールに取り込んで、次に、信号を分類する。信号を分類した後、検証ルールの選択、パラメーターの設定、ルール実行後に結果を判断して修正すべき箇所を確認する。

ツールの効率的な運用のため、この検証フロー上の重要な問題点は次の三点である。一つ目は検証ルールやパラメーターが適切に選択・設定されていないと発生するエラーが増大することである。二つ目はツールの設定に時間を要することである。信号種別ごとに検証ルールを選択してパラメーターを設定するが、信号の分類方法、使用する検証ルール、パラメーターは製品によって異なる。また、基板データが変わると同時に設定する必要がある。全ての信号に同じ検証ルール、パラメーターを使用する場合は不要になるが、検証時間、エラーの増大につながり効率的な運用の妨げになる。三つ目は結果に修正が必要なエラーと修正不要な疑似エラーが混在することである。疑似エラーの件数が多くなると結果の判断に時間を要することになり、本来修正が必要なエラーを見落すことにつながる。

これら三つの主要な問題点に対して、“検証項目の選定・整備”“設定の自動化”“疑似エラー削減”に取り組んで、効率的な運用手法を開発した。

## 4. 基板チェックツール効率化のための手法開発

### 4.1 検証項目の選定・整備

ツールには得手不得手があり、あらゆる設計制約を効果的に検証できるわけではない。まずは製品で遵守すべき設計制約を明確にし、その上でツールで検証すべき設計制約を選定した。選定に当たっては、検証精度、時間といった評価項目を用いる。その後、検証ルールを決めて、使用するパラメーターを最適化した。パラメーターが厳しすぎるとエラーが膨大に発生し、発生したエラーの判断に時間を要する。そのため、原理原則や既存の製品の設計値等を参考にして適切なパラメーターを設定した。

### 4.2 設定の自動化

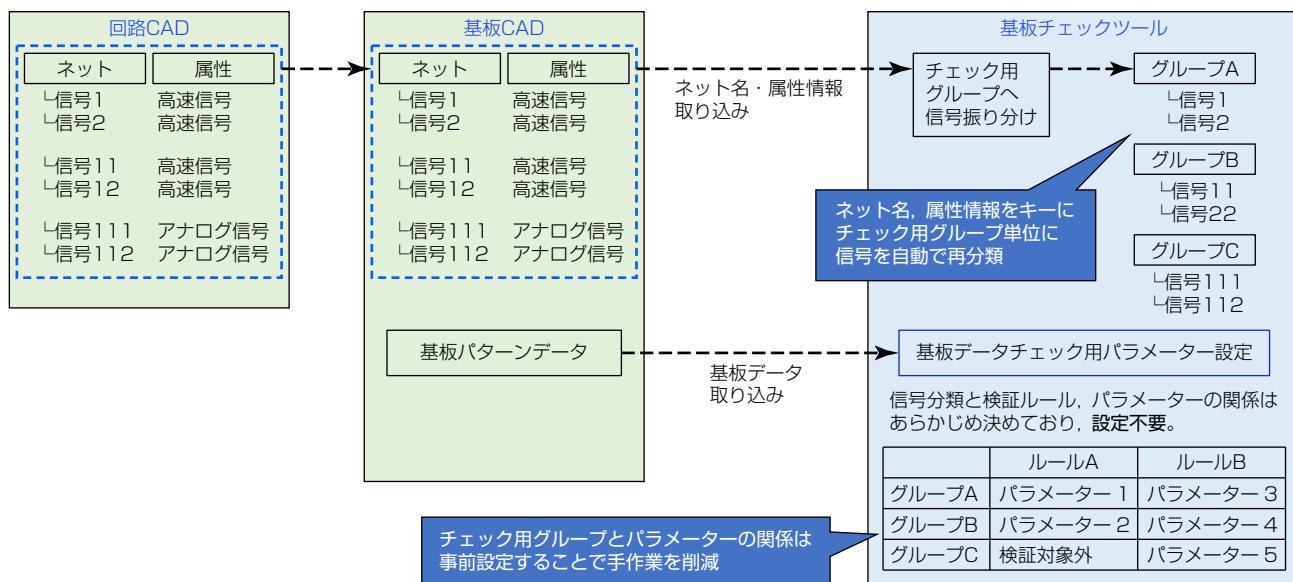

ツールを使うには、図4のとおり、信号の分類、検証ルールの選択、パラメーターの設定が必要になる。信号の分類をせず、全ての信号を対象として、同一ルール・パラメーターで検証すれば設定を省略できる。しかし、検証時間やエラー件数の増大といった問題を引き起こして、製品開発の中でツールの運用が困難であった。また、ツール上でこれらの作業は時間を要していた。この段階での設定ミスを抑制するため自動化が必要になった。具体的には、回路・基板CADの情報と連携して、ツール上で自動的に信号を分類し、検証ルールの選択、パラメーターの設定を自動化した。

図5にツールへのデータ取り込みと分類を示す。信号名であるネット名とそれぞれのネットに付与している属性情報を活用して基板チェックツール上で自動的にグルーピングすることで、ツールでの信号分類の効率を飛躍的に向上させた。また、グルーピングした信号と検証ルールとパラメーターの関係は事前に適切に定めているため、検証段階での設定は不要である。このように、ネット名、属性の付与方法に規則を設けて、信号分類と検証ルール、パラメーターの関係を決めることで、ツールの設定作業を自動化し、作業時間短縮と設定ミス抑制を実現した。

図5-基板チェックツールへのデータ取り込みと分類

### 4.3 疑似エラー削減

3.3節に述べたとおり、ツールで検証すると、修正すべきエラーとともに疑似エラーと呼ばれる修正する必要のないエラーも検出される。ツールでは検証内容ごとに適切なルールを選択して検証するが、適切なルールを選択したとしても修正すべきエラーだけを検出することは難しく、疑似エラーを含んだ結果になる。この対策として対象信号の絞り込み、パラメーターの最適化、検証ルール自体を改修した。例えば、動作周波数の速い高速信号は近傍に配線している信号に対し

て電磁干渉を起こしやすく、周囲の配線との間隔を十分広げる必要がある。周囲配線との距離を検証するルールでは高速信号だけを対象とする、又は、高速信号は周囲との間隔を広めに取って、それ以外の信号は通常の間隔にするなど信号の重要度によってパラメーターを分けて、不要なエラーを出さないようにした。また、ツールに標準搭載されているルールを使用して三菱電機の設計制約を検証すると、検証不要な範囲まで検証され、疑似エラーの増大を引き起こしていた。このようなルールに対しては、三菱電機独自の検証ルールを作成することで疑似エラーを削減した。

#### 4.4 効 果

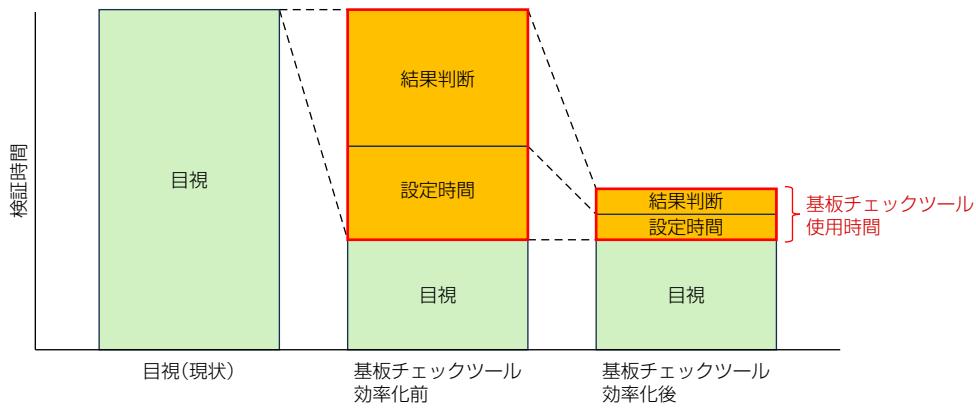

図6は、開発した基板チェックツール活用手法による検証時間削減効果の概念図である。対象になるプリント基板によって効果は変動する。効率化前は、ツール活用によって目視による検証時間は削減できたものの、設定時間や疑似エラーを含む結果判断に時間を要しており、結果的に合計時間は同程度であった。効率化後は、設定時間や結果判断の時間が大幅に低減でき、目視だけで検証した場合より検証時間を削減できた。また、目視では検証漏れが発生するリスクを含んでいるが、ツールは機械的に検証するため、検証漏れを抑制する効果も得た。

今後、製品の高性能化・高機能化に伴い、検証対象になる信号・ビアの増大や検証制約の増加が必至になる。この手法を用いることで時間の削減と精度の確保を両立できる。

図6-基板チェックツール効果

## 5. む す び

三菱電機では、EMC及び信号伝送の設計手戻り抑制や、今後の製品の高性能化・高機能化に伴うEMC・信号伝送設計業務の増大に対応するため、基板チェックツールを効率的に運用する手法を開発した。今後は、開発した手法を三菱電機内で充実化し、EMC・信号伝送設計業務の効率化、基板設計品質の向上を図る。

また、回路・基板CADとツールのデータ連携を進めることで、設定の効率化、検証精度の向上を図る。さらに、目視で検証している項目を基板チェックツールで検証可能になるよう新規ルール作成やデータ連携を進める。

## 参 考 文 献

- (1) 設計フロントローディングに向けた静電気ノイズ可視化技術の活用、三菱電機技報、98、No.1、1-5-01 (2024)