# 特集論文

# 短絡耐量制御を実現する SiCトレンチMOSFET構造

福井 裕\* Yutaka Fukui

**菅原勝俊**† Katsutoshi Sugawara

足立<u>亘</u>平\*

Kohei Adachi

SiC Trench MOSFET Structure for Controlling Short Circuit Capability

\*パワーデバイス製作所

†先端技術総合研究所(博士(工学))

#### 要旨

近年の環境意識の高まりを受けて、パワーエレクトロニクス機器の省エネルギー化が求められており、SiC(シリコンカーバイド)を材料としたパワーデバイスの開発、製品化が進められている。中でもより低損失化が可能なトレンチ型のSiC-MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)への期待が高いが、トレンチ型SiC-MOSFETは導電性が高いため素子短絡時での短絡耐量を確保することが非常に困難であった。スイッチング素子としての幅広いアプリケーションに対応するためには、デバイス構造設計の中で短絡耐量を制御することが重要である。

今回、三菱電機で開発を進めているトレンチ型SiC-MOSFETのデバイス構造を改良し、低抵抗化と高短絡耐量化のトレードオフ制御が可能なトレンチ型SiC-MOSFETを実現した。

### 1. まえがき

環境意識の高まりを受けてパワーエレクトロニクス機器の省エネルギー化が進められている中、次世代のパワー半導体材料としてSiCが注目されてきた。SiCは従来用いられてきたSi(シリコン)に比べてバンドギャップが大きく、絶縁破壊電界が高いことなど、パワーデバイスとして大幅に優れた性質を持っている。当社ではSiCを用いて、SiC-MOSFETやSiC-SBD(Schottky Barrier Diode)の開発及び量産を進めており、これまでに耐圧600Vの家電向けから3.3kVの電鉄向けまで、幅広い耐圧クラスの製品を実用化してきた。

パワーエレクトロニクス機器の省エネルギー化のためには、機器に用いられるパワーデバイスの低損失化が重要であり、より低損失化が可能なトレンチ型のSiC-MOSFETの開発、製品化が進んでいる。トレンチ型MOSFETはゲート電極をトレンチ内に埋め込むことで、セルピッチ縮小によるセル高集積化を実現でき、素子の低抵抗化が可能である。一方で、トレンチ底部で電界が集中しやすいため、十分な素子信頼性を得るためにはこの電界を緩和する必要がある。

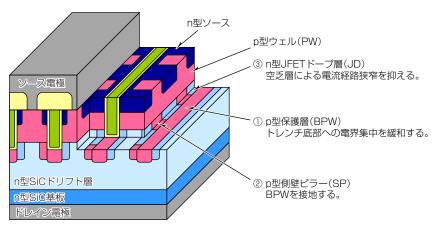

当社はこれまでに低抵抗化・高信頼性化・低スイッチング損失化が可能な独自構造のトレンチ型SiC-MOSFETを開発してきた $^{(1)(2)(3)}$ 。当社で開発したトレンチ型SiC-MOSFETの構造模式図を**図1**に示す。当社のトレンチ型SiC-MOSFETの構造は①トレンチ底部にかかる電界を緩和するp型保護層(BPW:Bottom P-Well), ②BPWを接地するp型側壁ピラー(SP:Sidewall Pillar), ③電流経路狭窄(きょうさく)を防ぐn型JFET(Junction Field Effect Transistor)ドープ層(JD:JFET Doping)の三つの注入層が特徴である。トレンチへの傾斜イオン注入を活用したこの構造は、高集積化による低損失化が容易であり、かつ簡便なプロセスで製作できることが利点である。

図1-当社で開発したトレンチ型SiC-MOSFETの構造模式図

しかしながら、トレンチ型SiC-MOSFETは低損失化が可能である一方、導電性が高いため素子短絡時での短絡耐量を確保することが非常に困難であった。スイッチング素子としての幅広いアプリケーションに対応するためには、短絡耐量を制御することが必要である。

そこで今回、デバイス構造設計を工夫して従来構造のトレンチ型SiC-MOSFETのデバイス構造を改良し、低抵抗化と高短絡耐量化のトレードオフ制御を可能にするトレンチ型SiC-MOSFETを開発した。

# 2. 短絡耐量制御トレンチ型SiC-MOSFET

#### 2.1 デバイス構造コンセプトとプロセスフロー

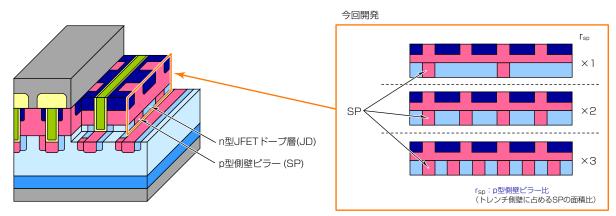

今回開発したトレンチ型SiC-MOSFETの構造模式図を図2に示す。低抵抗化と高短絡耐量化のトレードオフを制御する手段として、トレンチ側壁に占めるSP領域の面積密度比(p型側壁ピラー比: $r_{sp}$ )を調整することを考案した。SP領域はトレンチ側壁に離間して形成されており、1章に述べたとおりBPWを接地しスイッチング安定化を実現する機能を持っている。今回、SP領域の機能として素子導通時(オン時)ではMOS(Metal Oxide Semiconductor)チャネル電流及びJFET領域の電流経路を制限できることに着目した。低抵抗化と高短絡耐量化のトレードオフ制御実現のため、従来構造のSP密度を $r_{sp}$  = 1 とした場合に対して異なる $r_{sp}$ の素子を作り分けて、 $r_{sp}$ がMOSFETの電気特性や短絡耐量に与える影響を評価した。

図2-p型側壁ピラー比を制御したトレンチ型SiC-MOSFETの構造模式図

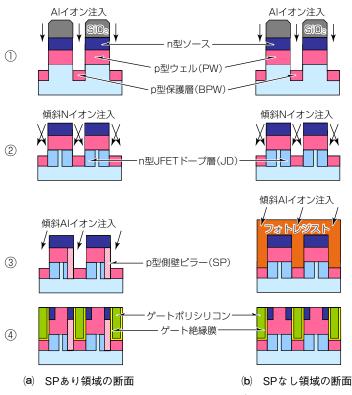

開発したトレンチ型SiC-MOSFETのプロセスフローについて、(a)SPのある領域と(b)SPのない領域に分けてその断面模式図を図3に示す。まずトレンチエッチング前にn型ドリフト層に対してAI(アルミニウム)イオン及びN(窒素)イオンを注入しp型ウェル(PW)及びn型ソースを形成する。その後SiO2(二酸化ケイ素)膜を堆積しフォトリソグラフィーを行い、ドライエッチングによってSiCにトレンチを形成する。トレンチエッチング後に残存したSiO2膜を活用し、トレンチ底部にBPWをセルフアラインAI注入によって形成する(図3①)。SiO2膜を除去したのち、両側のトレンチ側壁に対して傾斜Nイオン注入を行うことでJDを形成する(図3②)。続いてフォトリソグラフィーを行ってから片側のトレンチ側壁に対してだけ傾斜AIイオン注入を行うことでSPを形成する(図3③)。このときフォトリソグラフィーのマスクパターンによって、 $r_{\rm sp}$ を調整できる。p型コンタクト形成、注入後イオンの活性化アニールなどを経たあと、ゲート形成を行う(図3④)。その後、コンタクト形成、電極形成などが行われデバイスが完成する。

図3-トレンチ型SiC-MOSFETのプロセスフロー

#### 2.2 静特性のp型側壁ピラー比依存性

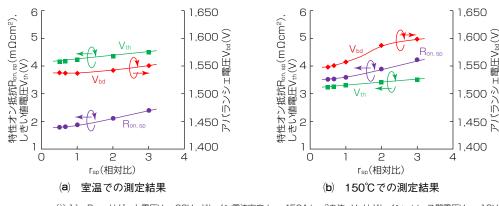

$r_{sp}$ の構造設計が静特性に与える影響を評価するため、試作したトレンチ型SiC-MOSFETの電気的特性を評価した。特性オン抵抗 $R_{on. sp}$ 、しきい値電圧 $V_{th}$ 、アバランシェ電圧 $V_{bd}$ の $r_{sp}$ 依存性について、図 $\mathbf{4}$ (a)に室温での測定結果を、図 $\mathbf{4}$ (b) に150 $\mathbb C$  での測定結果を示す。 $r_{sp}$ の増加すなわちSP領域をトレンチ側壁に密に形成することに伴い、MOSチャネル密度及びJFET領域の電流経路が減少するため、 $R_{on. sp}$ 及び $V_{th}$ はどちらの温度でも緩やかに増加する。それに加えて、高密度に形成されたSP領域によって電界緩和効果が得られるため、 $r_{sp}$ の増加に伴い $V_{bd}$ も増加する。結果として、 $V_{bd}\sim 1,550$  $V_{bd}\sim 1,550$

(注1)  $P_{on,sp}$ はゲート電圧 $V_g$ =20V、ドレイン電流密度 $J_{ds}$ =450A/cm²の値、 $V_{th}$ はドレインーソース間電圧 $V_{ds}$ =10V、ドレイン電流密度 $J_{ds}$ =100mA/cm²の値、アバランシェ電圧 $V_{bd}$ は $V_g$ =0V、 $I_{ds}$ =100μAの値として定義した。

図4-特性オン抵抗Ron, sp, しきい値電圧Vth, アバランシェ電圧Vbdのrsp依存性(注1)

#### 2.3 動特性のp型側壁ピラー比依存性

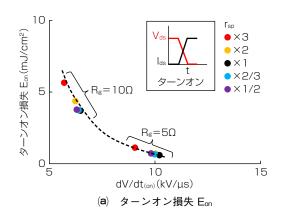

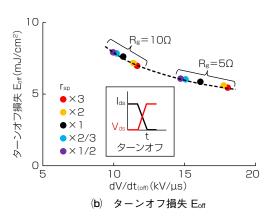

次に動特性として、 $r_{sp}$ の構造設計がスイッチングスピードdV/dtとスイッチング損失のトレードオフ関係に対して与える影響について評価を行った。スイッチング測定はダブルパルス試験で行い、dV/dtは外部ゲート抵抗 $(R_g)$ を変えることで調整した。 $\mathbf{図5}(a)$ にターンオン損失 $E_{on}$ 、 $\mathbf{図5}(b)$ にターンオフ損失 $E_{off}$ のdV/dt依存性について、 $r_{sp}$ を変化させた場合の結果を示す。 $E_{on}$ と $E_{off}$ どちらでも、 $r_{sp}$ を変化させた場合のdV/dtに対するスイッチング損失の関係は同一のトレードオフライン上を推移することが分かる。つまり、スイッチング損失は $r_{sp}$ とは無関係に外部ゲート抵抗 $(R_g)$ によって制御できることを示唆している。

(注2)  $V_{DD}$ =600V, ドレイン電流密度 $J_{ds}$ =260A/cm $^2$ の値。

図5-dV/dt-スイッチング損失トレードオフのrsp依存性(注2)

#### 2.4 短絡耐量のp型側壁ピラー比依存性

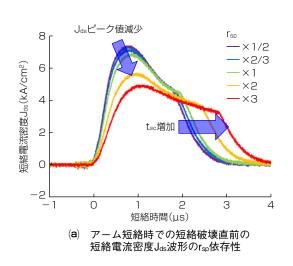

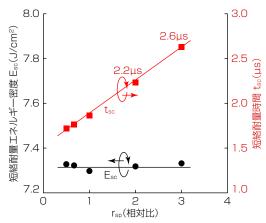

短絡耐量に対する $r_{sp}$ の依存性の結果を**図6**に示す。**図6**(a)はアーム短絡時での素子破壊直前の短絡電流密度 $J_{ds}$ 波形の  $r_{sp}$ 依存性である( $V_{DD}$  = 650V,  $V_{gs}$  = 20V, 150 $^{\circ}$  での値)。 $r_{sp}$ を増加させることによってMOSチャネル密度及びJFET領域 の電流経路が減少するために $J_{ds}$ ピーク値が大きく抑制された結果,短絡耐量時間 $t_{sc}$ が増加していることが分かる。 $r_{sp}$  = 2 の構造では $t_{sc}$  = 2.2 $\mu$ s まで、 $r_{sp}$  = 3 の構造では $t_{sc}$  = 2.6 $\mu$ s まで確保できていることが分かる。

(b) 短絡耐量エネルギー Escと短絡耐量時間tsc のrsc依存性

(注3) どちらもV<sub>DD</sub>=650V, V<sub>gs</sub>=20V, 150℃での値。

図6-アーム短絡時での短絡破壊直前の短絡電流密度Jas波形,及び短絡耐量エネルギーEscと短絡耐量時間tscのrsp依存性(注3)

図**6**(b)に短絡耐量エネルギーEscと短絡耐量時間tscのrsp依存性を示す。rspを増加させた構造設計によってtscを増加させることができる一方で,Escはrspに依存性を持たないことが分かる。これは短絡破壊が短絡電流による熱破壊モードであり,MOSFETの熱伝導設計が同じであるため,Escが一定に律速されていることを示している(rspはMOSFETの熱伝導設計に影響を与えない)。結果として,デバイス構造パラメーターであるp型側壁ピラー比をコントロールすることによって,短絡耐量時間tscを制御できることが分かった。

#### 2.5 DC損失/AC損失比と短絡耐量のトレードオフ制御

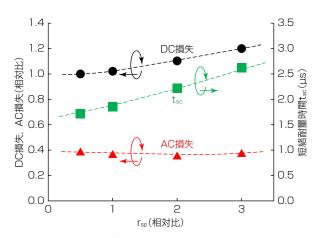

2. 2節, 2. 4節の結果を基に、DC損失及びAC損失と短絡耐量時間 $t_{sc}$ についてのp型側壁ピラー比の依存性を試算した。DC損失は $R_{on, sp}$ 値から、AC損失は $R_{g}$  = 5  $\Omega$ でのスイッチング損失値を参照し、20kHzで駆動させた場合を仮定し算出した。

結果を**図7**に示す。 $r_{sp}$ の高い構造を採用することによって $t_{sc}$ を増加させることができ、その場合DC損失は緩やかに増加するもののAC損失はほぼ一定に保たれている。 $r_{sp}$ はDC損失と短絡耐量時間 $t_{sc}$ を設計する上で鍵となるパラメーターであり、当社のトレンチ型SiC-MOSFETでは $r_{sp}$ 設計を調整することで、SiC-MOSFETに求められる多様なアプリケーションに対応可能であることを見いだした。

図7-DC損失及びAC損失と短絡耐量時間tscのrsp依存性

# 3. む す び

トレンチ型SiC-MOSFETは低損失化が可能である一方、高導電性を持つため素子短絡時での短絡耐量を確保することが困難であった。多様なアプリケーションの要求に対応するためには、短絡耐量をデバイス構造設計を工夫することで制御する手段を得ることが必要である。

今回,当社独自構造のトレンチ型SiC-MOSFETのデバイス構造で、p型側壁ピラー比(rsp)を調整することによって短絡電流のコントロールを行い、低抵抗化と高短絡耐量時間化のトレードオフ制御を実現した。多様なアプリケーションの要求に対応できる当社のトレンチ型SiC-MOSFETについて、引き続き量産適用を進めていく。

## 参考文献

- (1) Fukui, Y., et al.: Effects of Grounding Bottom Oxide Protection Layer in Trench-Gate SiC-MOSFET by Tilted Al Implantation, Materials Science Forum 1004, 764~769 (2020)

- (2) Tanaka, R., et al.: Performance Improvement of Trench-Gate SiC MOSFETs by Localized High-Concentration N-Type Ion Implantation, Materials Science Forum 1004, 770~775 (2020)

- (3) Sugawara, K., et al.: A Novel Trench SiC-MOSFETs Fabricated by Multiple-Ion-Implantation into Tilted Trench Side Walls (MIT2-MOS), PCIM Europe 2021, 504~508 (2021)