家庭から宇宙まで、エコチエンジ

# 三菱電機技報

3

2020

Vol.94 No.3

## パワーデバイス

### 目 次

#### 特集「パワーデバイス」

|                                       |      |    |

|---------------------------------------|------|----|

| 環境・エネルギー課題を背景に拡大する<br>パワーデバイスへの期待     | 卷頭言  | 1  |

| ゴーラブ マジュムダール（鈴木ごうらぶ）                  |      |    |

| パワーモジュールの最新動向と展望                      | 卷頭論文 | 2  |

| 西原秀典・松岡 健                             |      |    |

| 第2世代1.7kV SiC-MOSFET                  |      | 7  |

| 濱野健一・谷岡寿一・折附泰典                        |      |    |

| 低ロスと高いダイナミックな耐久性を<br>兼ね備えた次世代パワー半導体技術 |      | 11 |

| 中村勝光・鈴木健司・西 康一・金田和徳・川瀬祐介              |      |    |

| HVIGBTモジュールの耐湿性確認技術                   |      | 15 |

| 羽鳥憲司・中村圭一・本田成人・田中宜彦                   |      |    |

| 表面実装パッケージ型IPMのパッケージ技術                 |      | 19 |

| 鹿野武敏・作谷和彥                             |      |    |

| パワーモジュールの性能向上を実現する<br>配線技術開発の取組み      |      | 23 |

| 内田祥久・柳本辰則・菊池正雄                        |      |    |

| 自動車用パワーモジュール“J1シリーズ”                  |      | 27 |

| 飯塚 新・猪ノ口誠一郎・波多江慎治                     |      |    |

| 第2世代SiC-MOSFETモジュール                   |      | 31 |

| 宮崎裕二・清水康貴・宇田達也・北林拓也                   |      |    |

| 第2世代ハイブリッドSiC-IPM                     |      | 35 |

| 大月高実・河本啓輔・後藤 亮・井上貴公                   |      |    |

| 並列駆動に適したパワーモジュール                      |      | 39 |

| 津田 亮・梅澤 熊・増岡史仁・酒井純也                   |      |    |

| 普及版600V HVIC“M81776FP”                |      | 43 |

| 羽生 洋・山本晃央・佐野昇平                        |      |    |

| 低容量帯の表面実装パッケージ型IPM                    |      | 47 |

| 横山脩平・山口公輔・野口宏一朗                       |      |    |

| 超小型DIPIPM Ver.7シリーズ                   |      | 51 |

| 柴田祥吾・野口宏一朗・山口公輔                       |      |    |

| 豆知識                                   |      | 55 |

#### 特許と新案

|                   |    |

|-------------------|----|

| 「半導体装置」「半導体モジュール」 | 57 |

| 「パワーモジュール」        | 58 |

#### Power Device

|                                                                                 |  |

|---------------------------------------------------------------------------------|--|

| Expectations for Power Devices Expanding Due to Environmental and Energy Issues |  |

| Gourab Majumdar (Gourab Suzuki)                                                 |  |

|                                                      |  |

|------------------------------------------------------|--|

| Latest Trend and Prospect of Power Module Technology |  |

| Hidenori Nishihara, Toru Matsuoka                    |  |

|                                                   |  |

|---------------------------------------------------|--|

| 2nd Generation SiC-MOSFETs with 1.7kV Rating      |  |

| Kenichi Hamano, Toshikazu Tanioka, Yasunori Orito |  |

|                                                                                             |  |

|---------------------------------------------------------------------------------------------|--|

| Next Generation Power Semiconductor Technology with Low Loss<br>and High Dynamic Ruggedness |  |

| Katsuji Nakamura, Kenji Suzuki, Koichi Nishi, Kazunori Kanada, Yusuke Kawase                |  |

|                                                                                                          |  |

|----------------------------------------------------------------------------------------------------------|--|

| Humidity Robustness Verification Technologies for High Voltage Insulated Gate Bipolar Transistor Modules |  |

| Kenji Hatori, Keiichi Nakamura, Shigeto Honda, Nobuhiko Tanaka                                           |  |

|                                                                          |  |

|--------------------------------------------------------------------------|--|

| Packaging Technologies of Surface-mount Package Intelligent Power Module |  |

| Taketoshi Shikano, Kazuhiko Sakutani                                     |  |

|                                                                     |  |

|---------------------------------------------------------------------|--|

| Wiring Technologies Development to Improve Power Module Performance |  |

| Yoshihisa Uchida, Tatsunori Yanagimoto, Masao Kikuchi               |  |

|                                                |  |

|------------------------------------------------|--|

| Automotive Power Module “J1 Series”            |  |

| Arata Jizuka, Seiichiro Inokuchi, Shinji Hatae |  |

|                                                                  |  |

|------------------------------------------------------------------|--|

| 2nd Generation SiC-MOSFET Module                                 |  |

| Yoji Miyazaki, Yasutaka Shimizu, Tatsuya Uda, Takuya Kitabayashi |  |

|                                                           |  |

|-----------------------------------------------------------|--|

| 2nd Generation Hybrid SiC-IPM                             |  |

| Takami Otsuki, Keisuke Kawamoto, Ryo Goto, Takahiro Inoue |  |

|                                                        |  |

|--------------------------------------------------------|--|

| Power Module for Parallel Operation                    |  |

| Ryo Tsuda, Isao Umezaki, Fumihito Masuoka, Junya Sakai |  |

|                                                                 |  |

|-----------------------------------------------------------------|--|

| Popular Edition 600V High Voltage Integrated Circuit “M81776FP” |  |

| Yo Habu, Akihisa Yamamoto, Shohei Sano                          |  |

|                                                     |  |

|-----------------------------------------------------|--|

| Low Capacity Surface-mount Package Type IPM         |  |

| Shuhei Yokoyama, Kosuke Yamaguchi, Koichiro Noguchi |  |

|                                                   |  |

|---------------------------------------------------|--|

| Super Mini DIPIPM Ver.7 Series                    |  |

| Shogo Shibata, Koichiro Noguchi, Kosuke Yamaguchi |  |

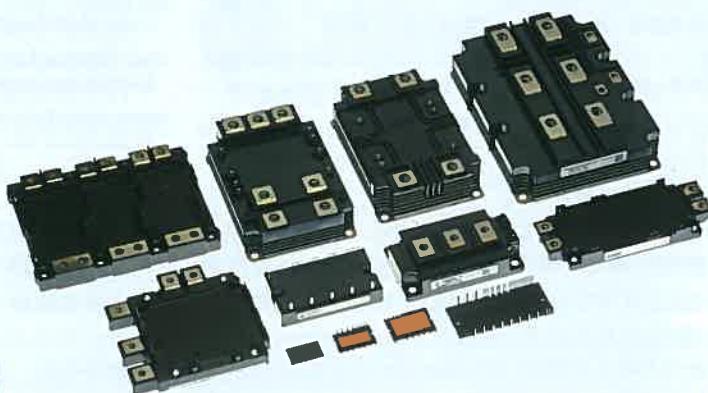

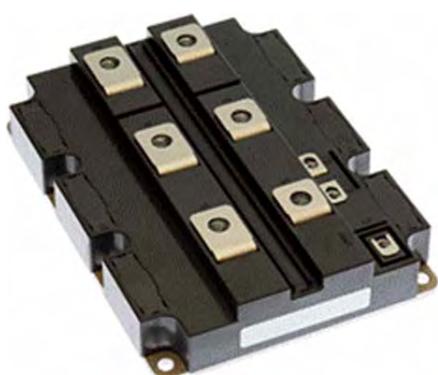

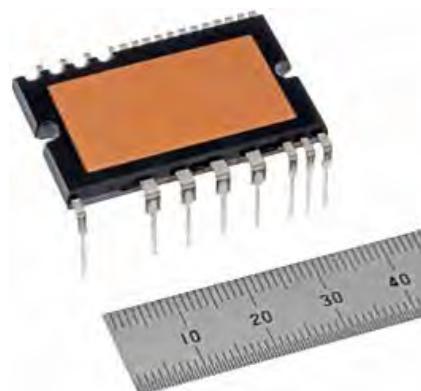

#### 表紙：パワーデバイス

三菱電機は、産業、家電、電力、電鉄、自動車、新エネルギーなど、幅広いパワーエレクトロニクス製品に向けたパワーデバイスを供給している。内蔵される半導体チップは主力のSi(シリコン)に加え次世代チップであるSiC(シリコンカーバイド)のラインアップも充実している。

さらに、それら半導体チップを搭載するパッケージにも樹脂系の絶縁材や硬質樹脂封止、放熱フィン一体型形状など、最先端の技術を採用し、幅広い顧客からの要望に対応できる製品群を充実させている。表紙の写真は代表製品である。

# 巻頭言

## 環境・エネルギー課題を背景に拡大する パワーデバイスへの期待

Expectations for Power Devices Expanding Due to Environmental and Energy Issues

ゴーラブ マジュムダール（鈴木ごうらぶ）

半導体・デバイス事業本部 主席技監（工博）

Senior Fellow, Semiconductor & Device Group

Gourab Majumdar (Gourab Suzuki)

世界規模で対処すべき問題である、エネルギー消費の増加と二酸化炭素(CO<sub>2</sub>)の大量排出が緊急事態に突入しています。増加する電力需要に対応しながらエネルギーを節約するには、発電から電力消費までの全ての段階で、エネルギー変換・貯蔵・利用に適用されているあらゆる機器やシステムのエネルギー効率を改善することが重要となっています。世界中で毎年消費される一次エネルギーの約40%は発電用であり、この数字は今後25年間で50%以上に増加すると予測されています。

また、これらの電力供給チェーン全体で何らかの形のエネルギー変換装置を介して処理される電気の割合は、2030年までに80%に達する可能性があり、現在の割合の約2倍になると推定されています。そのため、エネルギー変換・貯蔵・利用での課題に対処する機能を持つ、パワーエレクトロニクス(以下“パワエレ”という。)、マイクロエレクトロニクス、及びデバイスの役割が大変重要で注目を浴びています。パワーグリッドを利用した電力供給チェーンの各段階での電力制御・変換で、エネルギー効率を高める役割を発揮できるパワエレ技術の普及が望まれています。また、代替エネルギーや新エネルギー用途、及び家電や自動運転を含む電気自動車、電動航空機などの新分野では、パワエレ技術の適用が急増しており、従来の電鉄や産業用途での普及を含め、今後も持続的にその規模が拡大すると予想されています。

これによって、パワエレ適用機器や装置と、そのキーコンポーネントであるパワーデバイスの更なる技術的な革新や進化が重要とされています。パワーデバイスは1W(ワット)レベルの小容量領域から数百MW(メガワット)領域のパワエレ適用のシステムに対応できるよう、長期にわたり様々な種類に分かれて発展し続けてきました。中でも、近年特に注目を浴びているのが中・大容量のパワエレシステムに採用されているIGBT(Insulated Gate Bipolar Transistor)モジュールやIPM(Intelligent Power Module)であり、これらのデバイスファミリーは様々な改良を通してシステムの高効率化、高性能化、小型・軽量化、高信頼性化などに大きく寄与してきました。現在、IGBTモジュールやIPMはパワエレ技術が適用されている産業用回転機器制御装置や電源設備、インバータ家電や他の民生用途、EV(Electric Vehicle)やHEV(Hybrid EV)を含む自動車用途や関連インフラ設備、及び電鉄用途などの様々な分野で採用されています。これらの応用分野では、パワーデバイスに対する共通的な要求である動作損失低減、

小型・軽量化や、高耐久性・高信頼性に加え、高短絡破壊耐量や幅広い安全動作領域を維持した使いやすさとパワー密度向上のニーズが挙げられ、要求レベルが年々高まっています。

三菱電機では、これらの要求に的確なソリューションを適用できるように主役のIGBTモジュールやIPMの性能向上や、新半導体材料として期待されているSiC(シリコンカーバイド)などワイドバンドギャップ(WBG)材料採用の最先端パワーデバイスの研究開発及び実用化を積極的に進めており、業界を牽引(けんいん)し続けられるよう取り組んでいます。

半導体材料としてSi(シリコン)を採用しているIGBTチップ技術はブレーナゲートのセル構造から始まり、トレンチセル構造、“CSTBT<sup>(注1)</sup>”を経て、極限薄ウェーハ技術適用によって高性能化を進めた第7世代CSTBTまでの実用化に至り、次の世代へ突入しようとしています。一方、極限薄ウェーハ技術と裏面パターンニング技術を複合化した新コンセプトの逆導通型IGBTであるRC-IGBT(Reverse Conducting IGBT)，又は優れた性能を持つRFC(Relaxed Field of Cathode)原理を生かした新ダイオードの開発実用化でパワエレ装置の高効率化、小型化など高性能化に大きく寄与しています。

新WBG半導体材料ファミリーの中では、特に、SiCが、その物性の優れた特徴から得られるデバイスの高温・高耐圧化でかつ高速スイッチング動作といったメリットを用いることでハイパワーデバイスの最も適切なポストシリコン材料として注目を浴びており、当社はこの分野では業界のパイオニアとして様々な用途向けの最先端SiCデバイスやモジュールの実用化に成功し、更なる発展を進めています。これら新デバイスの応用によって電力変換損失の大幅な低減や応用システムの飛躍的な小型・軽量化が実現可能になり、パワエレ適用システムの普及やエネルギー変換・貯蔵・利用での課題解決に大幅に寄与し、Siデバイスの適用が困難な用途を新たに創生する可能性を持っています。

このように、パワーデバイスの進化は今後も継続され、SiCやGaN(窒化ガリウム)などのWBG材料を使用して、高度なパッケージングソリューション、及びIPMをプラットフォームとしてIoT(Internet of Things)やAI(Artificial Intelligence)トレンドとの調和を図る新しい機能、及び新しいデバイステクノロジーをもたらすと期待されています。

(注1) キャリア蓄積層を形成したIGBT

# パワーモジュールの最新動向と展望

Latest Trend and Prospect of Power Module Technology

西原秀典\*

Hidenori Nishihara

松岡徹†

Toru Matsuoka

## 要旨

世界的な人口増加や新興国の経済発展などに伴い、エネルギー需要は急拡大を続けており、日本でも二度の石油危機後や近年の不況時を除いて消費量は一貫して増加している。石油危機以降の部門別エネルギー消費量は産業部門が約0.9倍、運輸部門が約1.9倍、住宅・建築物などの民生部門が約2.5倍となっており、従来十分な努力によって省エネルギーを進めてきた産業部門での省エネルギー対策に加え、電鉄や自動車の燃費向上、エアコンや冷蔵庫の消費電力低減など様々な分野で一層の省エネルギーを進める必要がある。

これらを実現するにはパワーエレクトロニクスの更なる発展は必要不可欠であり、新しい変換方式や新たな回路構

成の提案がなされる中、機器性能を大きく左右するキーパーツであるパワーモジュールも、これまで以上に多様化する市場ニーズに応える必要がある。

三菱電機ではシリコン(Si)素材に加え、次世代半導体のシリコンカーバイド(SiC)素材のチップを搭載したパワーモジュール製品のラインアップを拡大してきた。劇的な損失改善を図る一方で更に高い耐電圧素子の開発も進め、市場からの電気的特性の要求に対応している。また、チップ性能を最大限に引き出すパッケージ技術では、耐環境性や寿命向上、ユーザー側での設計・組立ての負荷軽減などにも取り組んでいる。

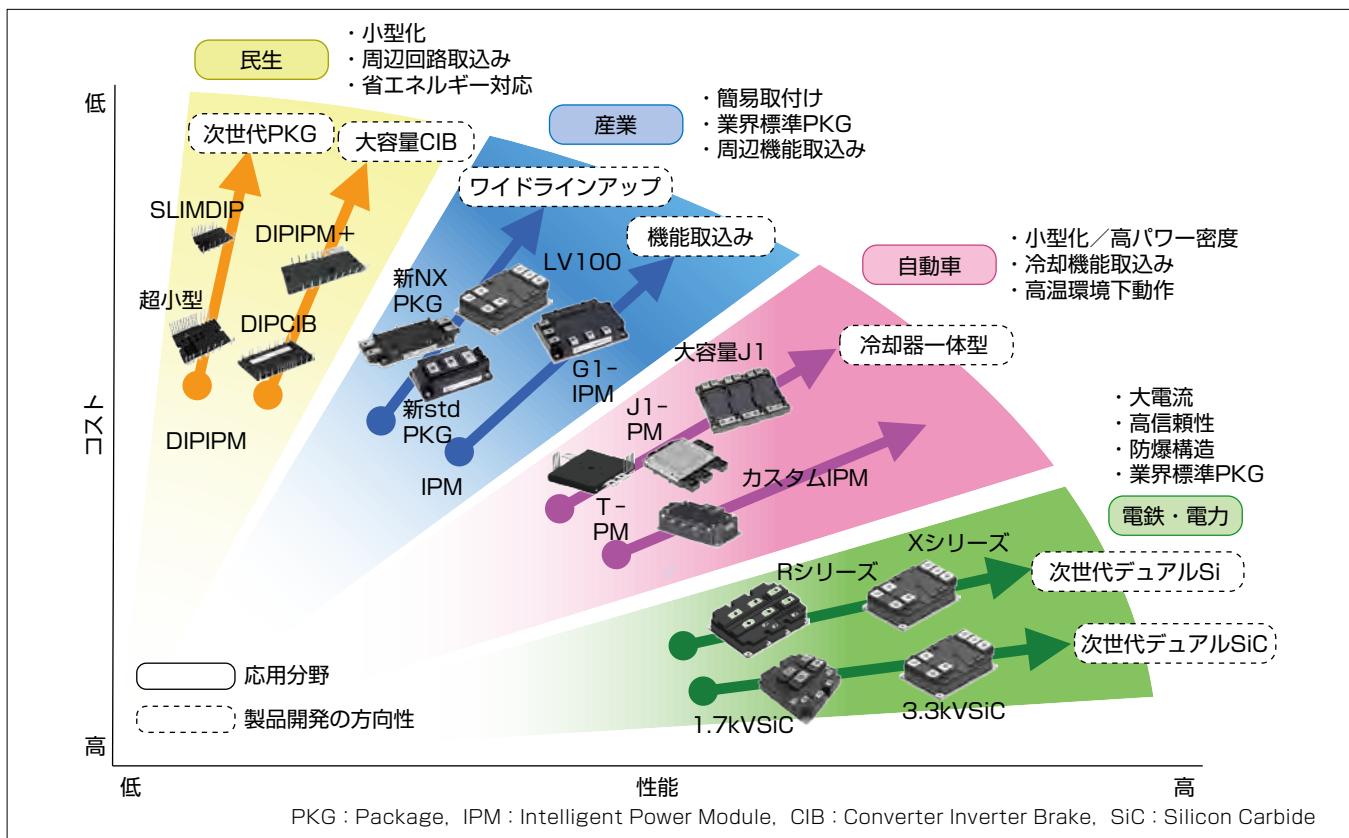

## パワーモジュール製品の普及・拡大に向けた多様な製品群の開発トレンド

定格耐電圧が数百Vから数千V、定格電流が数Aから数千Aの大きな容量域をカバーするパワーモジュールは、民生、産業、自動車及び電鉄・電力などの応用機器に使用されている。応用分野の拡大に伴って、パワーモジュールへの要求が多様化しているが、高性能化技術と低コスト化技術を基盤技術として継続的に改良するとともに、用途に応じた技術の取捨選択を行って製品化を進めていく。

## 1. まえがき

電気エネルギーを効率的に利用し、創エネルギー・省エネルギーに貢献できるパワーエレクトロニクス技術の応用範囲は、産業・民生・自動車・太陽光発電・風力発電など多岐にわたる。このキーパーツとして拡大を続けるパワーデバイスの代表素子であるIGBT(Insulated Gate Bipolar Transistor)は現在第7世代まで進化が進んでおり、更なる高効率化、小型・軽量化、長寿命化など、様々な市場ニーズに対応している。さらに、SiCチップや耐環境性能を向上させたパッケージ、トランスファーモールドパッケージなどと組み合わせ、最適化されたパワーモジュールを市場に展開している。

本稿では、応用分野ごとに選択したバランス設計でコスト低減を図りながら、高性能化、小型・軽量化を進めていく当社パワーモジュールの最新動向と展望について述べる。

## 2. パワーモジュール技術の最新動向

### 2.1 パワーチップ技術

パワーモジュールに搭載されるIGBTは2002年頃、第5世代製品として市場投入された電荷蓄積形トレンチゲートバイポーラトランジスタ“CSTBT”以降、チップ表面加工の微細化技術によるゲート構造の最適化、極薄ウェーハ技術によるn<sup>-</sup>層厚さの最適化などの最新技術を取り込むことによって性能向上を繰り返しながら市場にマッチした最適特性のチップを提供してきた。

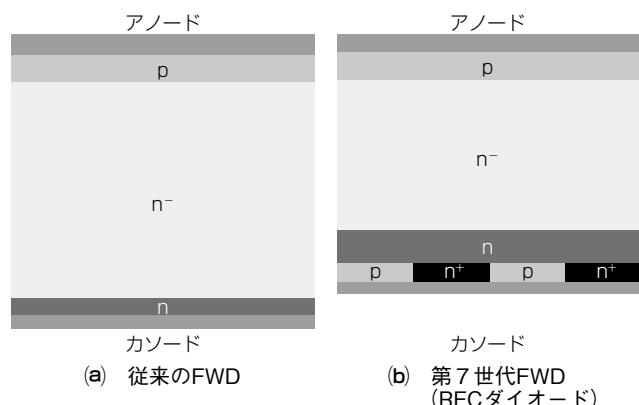

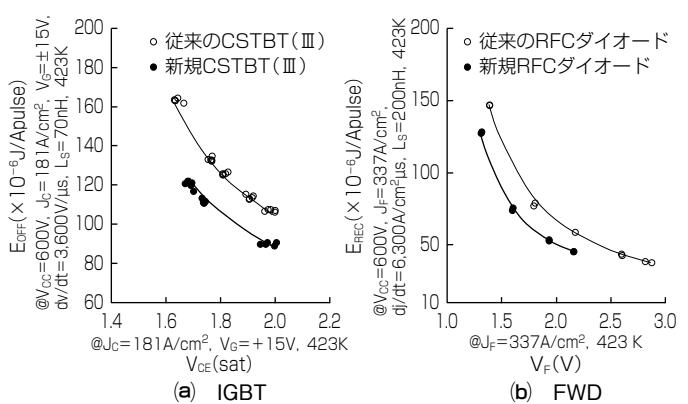

最新の第7世代チップは一世代前の第6世代チップに対して約10%の発生損失の低減を図りながら、ゲート抵抗によるdv/dt制御性を改善した。IGBTと逆並列で接続される還流ダイオード(Free Wheeling Diode : FWD)もRFC(Relaxed Field of Cathode)ダイオードを搭載することで順方向電圧V<sub>F</sub>と逆回復損失Errのトレードオフ改善を図りながら、EMI(Electro Magnetic Interference)ノイズの低減やサージ電圧制御といったユーザーが使いやすい特性を目指した。

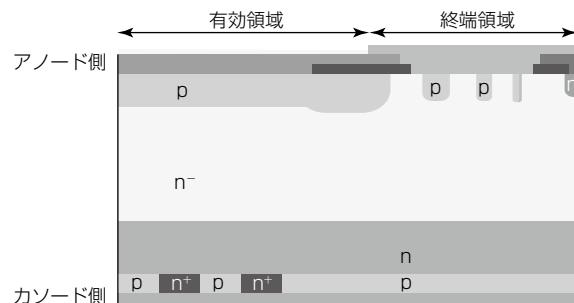

図1に従来構造のFWDと最新のRFCダイオードの断面構造比較を示す。一般的にFWDの特性改善にはn<sup>-</sup>層厚を薄くする手法が用いられていたが、n<sup>-</sup>層を薄くすると逆回復時にリングングが発生しやすくなる背反事項があり、薄厚化には限界があった。

そこで、新たに開発されたRFCダイオードは、カソード部に部分的に設けられたp層が逆回復時に適切な量のホールをn<sup>-</sup>層に注入することで裏面近傍でのキャリアの

急峻(きゅうしゅん)な消滅を抑制する。特に低電流の逆回復時に発生しやすいとされる電圧波形のリングング抑制に効果を發揮する。

また、小型・高パワー密度、高効率、高周波駆動、高温動作など、様々な可能性を秘めた次世代半導体素子として注目されているSiCの基本特性を表1に示す。

特にSiCは絶縁破壊電界強度がおよそ10倍あることから、パワーデバイスとして様々な恩恵を得ることができる。例えば高耐電圧製品では耐電圧保持のためにチップ周辺に構成されるガードリング領域が狭められ、より大容量チップを搭載可能になる。また、ユニポーラ形デバイスのMOSFET(Metal Oxide Semiconductor Field Effect Transistor)やSBD(Schottky Barrier Diode)は高耐電圧化を図ろうとするとn<sup>-</sup>層を厚くしなければならないのにSiではオン抵抗が急増してしまうが、SiCでは理論的にはn<sup>-</sup>層を1/10程度まで薄くでき、高耐電圧領域でも低いオン電圧が実現可能になる。ユニポーラ形デバイスのようにテール電流がなく、高周波動作時でも発生損失が低減できるため、様々なパワーエレクトロニクス機器の小型化・高性能化などに寄与できる。

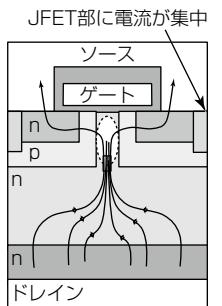

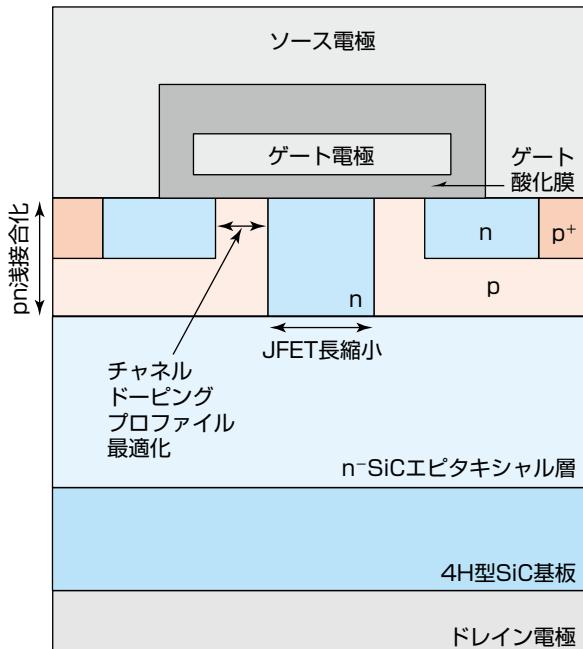

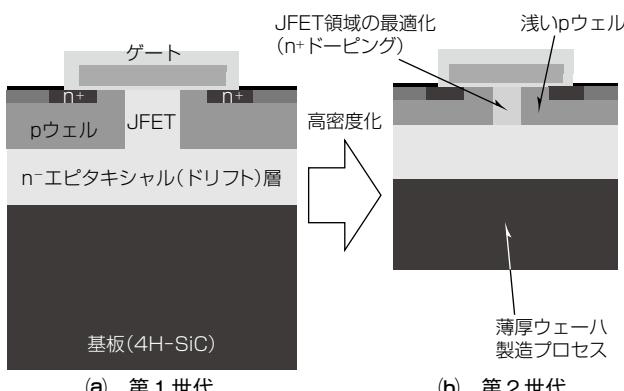

MOSFETの性能向上にはセルの微細化が効果的であるが、図2に示すようにJFET(Junction Field Effect Transistor)長が一定以下になると急激にオン抵抗が上昇する。当社の第2世代SiC MOSFETではこの問題を解決するためにJFET部の濃度プロファイルを最適化させて高性能化を実現している。

SiC MOSFETではボディダイオードへのバイポーラ電流による基底面転位(Basal Plane Dislocation : BPD)を基準にした積層欠陥の拡張が一般的に知られており、使用

図1. 従来品とRFCダイオードの断面構造

表1. SiとSiCの物性値比較

|          | 対Si比 | 効果         |

|----------|------|------------|

| バンドギャップ  | 3倍   | 高温動作       |

| 絶縁破壊電界強度 | 10倍  | 低オン抵抗・高耐電圧 |

| 電子飽和速度   | 2倍   | 高速動作       |

| 熱伝導率     | 3倍   | 高放熱性       |

図2. JFET長・オン抵抗・JFET濃度の関係

中にオン抵抗が増加するものがある(図3)。

SBDをFWDとして逆接続することで、これを回避しているが、次世代技術としてSBDを内蔵したMOSFETの開発を進めている。この技術はボディダイオードの通電劣化を気にせずに安心して使用できるMOSFETパワーモジュールを提供できるだけでなく、FWDの搭載が不要となるため、パワーモジュールの更なる高電力密度化実現の可能性を大いに秘めている(図4)。

また、トレンチゲート化による特性改善も着々と進んでおり、今後600~1,200V耐電圧製品を中心に展開予定である。

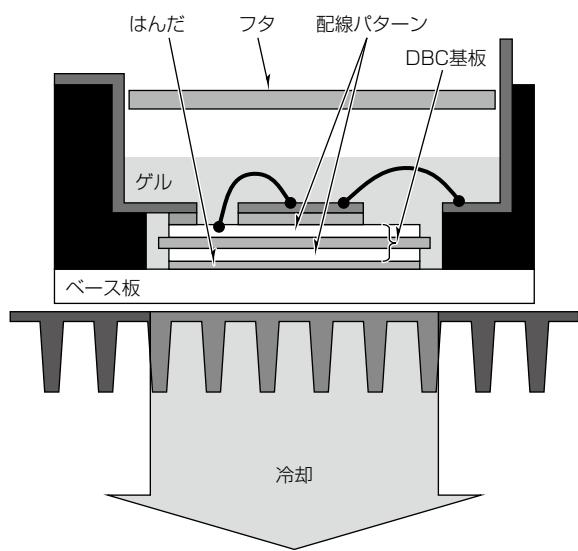

## 2.2 パッケージ技術

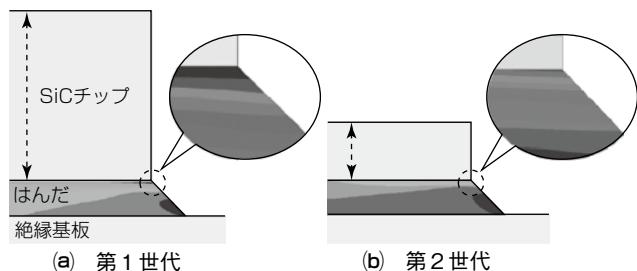

SiベースのIGBTモジュールの $T_j(\text{max}) = 175^\circ\text{C}$ が一般的になり、さらにSiCチップによる高 $T_j$ 化を見据えて、 $T_j > 200^\circ\text{C}$ 達成のためのパッケージの各要素技術を述べる。

### 2.2.1 チップ接合技術

環境規制で鉛(Pb)の使用が規制されたことで現在は、スズ(Sn)合金材料のはんだが主に使用されている。 $T_j > 200^\circ\text{C}$ 達成のための次世代チップ接合としてナノ銀パウダーに代表される微細金属パウダーによる金属焼結結合の採用が開始されている。一般的に金属焼結結合にはチップと絶縁基板とに挟まれた金属粉を高温・高圧にすることで結合させるためチップへのストレスが問題になるが、当社ではチップへのストレス緩和策を講じるとともに、低圧力でも結合可能な金属焼結結合の開発を進めている。

### 2.2.2 ワイヤ配線技術

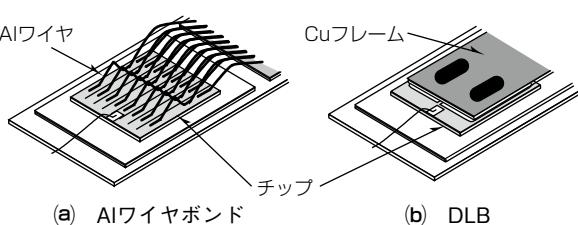

配線にはアルミニウム(Al)又はその合金ワイヤが使用されているが、モジュールの小型化や $T_j > 200^\circ\text{C}$ 達成のための次世代ワイヤ配線技術として一般的には銅(Cu)ワイヤの使用が提案されている。しかし、銅ワイヤをチップに接合させるにはチップ表面に銅やニッケル(Ni)など硬い金属を使用する必要がある。当社では、銅ワイヤをしのぐ通電能力と、寿命向上などを目的に銅リードを使用したDLB(Direct Lead Bonding)構造を一部のパワーモジュールに採用している。

図3. BPDから拡張した積層欠陥

図4. SBD内蔵型MOSFET

### 2.2.3 放熱技術

冷却の際には放熱グリースなどを塗布してヒートシンクに搭載されることが一般的であるが、更なる冷却効率改善とパワーモジュールの長寿命化要求に応えるためにパワーモジュールと放熱フィンを一体化した製品を量産化している。この構造では、絶縁基板下のはんだ層と放熱グリースの層を削減でき、放熱効果を向上させて高パワー密度実装を実現している。

### 2.2.4 封止材料

チップ表面の保護やモジュール内部の絶縁を確保する目的で封止材として使用されるシリコーンゲルだが、高温環境では不安定になることがある。 $T_j > 200^\circ\text{C}$ 達成のために、当社ではシリコーンゲル封止に代わる、ダイレクトボッティング(DP)樹脂封止技術を確立した。DP樹脂は高温環境だけでなく、シリコーンゲルが凝固する $-50^\circ\text{C}$ 以下の環境にも耐えることができる。さらに低気圧環境や腐食性ガスの侵入耐量など高い耐環境性も持ち合わせている。最新の自動車応用や産業応用のパワーモジュールには樹脂封止パッケージを主に採用しており、今後は更に大型の電鉄・電力応用のパワーモジュールにも展開していく。

### 3. 市場別の製品技術と展望

#### 3.1 民生応用製品

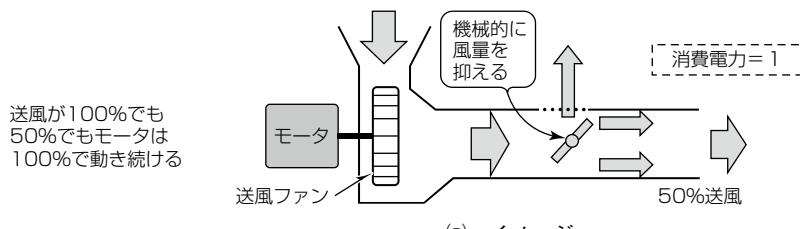

民生用パワーモジュールの最大市場であるルームエアコン市場では、国内のトップランナー基準に基づく省エネルギー性能重視の需要がある一方、中国やインドなどのアジア圏を中心としたコスト重視の需要もあり、今後二極化はますます加速すると考えられる。これに加え、一大マーケットである中国市場で環境規制の高まりからエネルギー効率の低い製品の販売を停止する方向性が出されており、ノンインバータエアコンからの置換需要なども含め、活気ある市場の一つと言える。

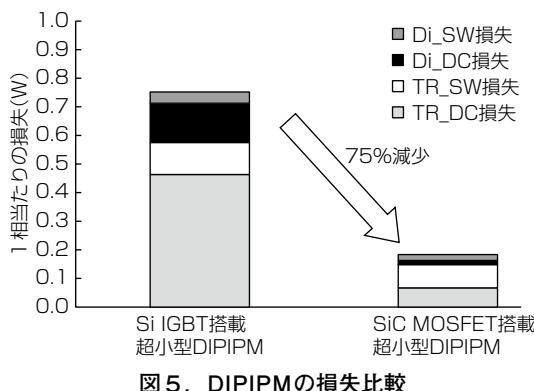

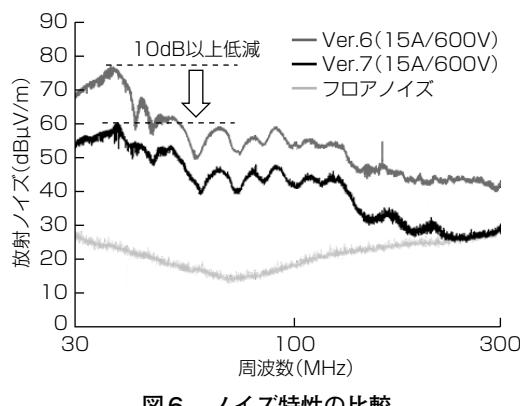

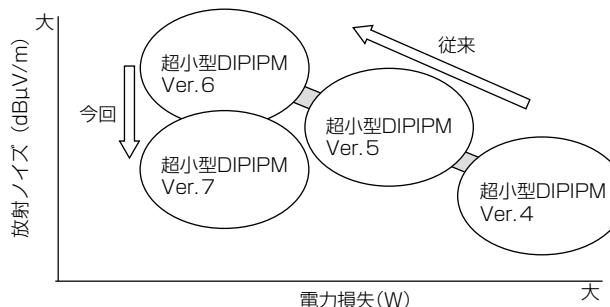

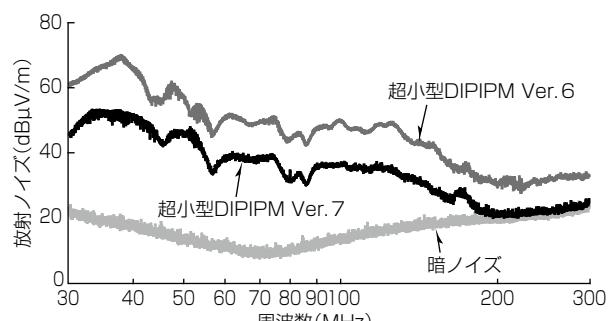

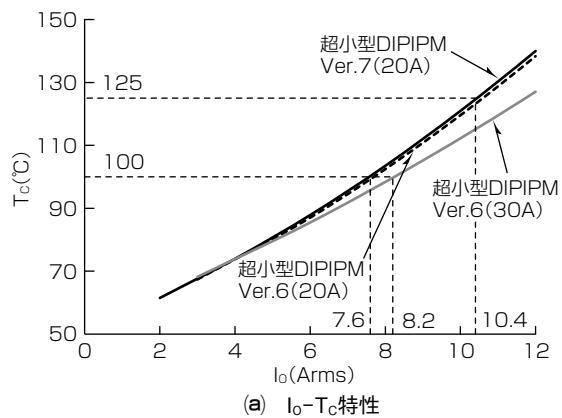

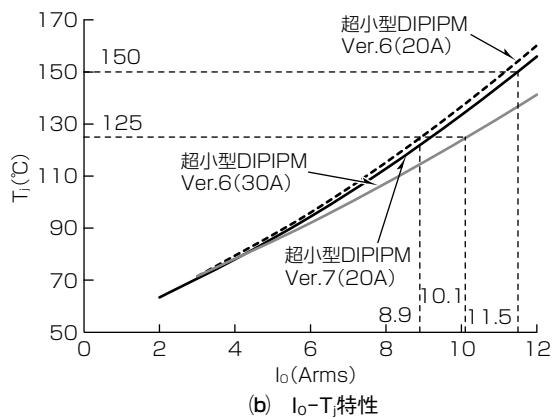

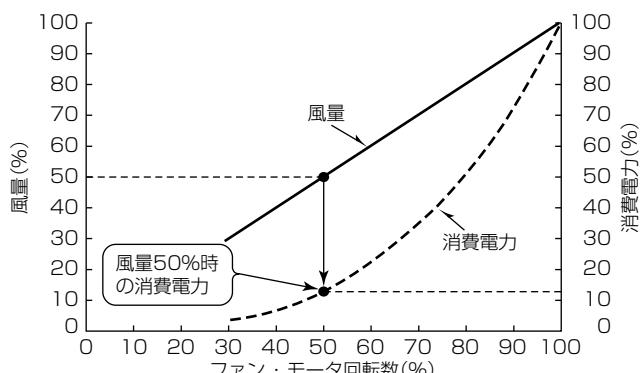

高性能需要に対し、エネルギー効率の指標の一つである通年エネルギー消費効率(Annual Performance Factor: APF)で最高レベルの性能をもたらす技術としてSiC MOSFETを搭載した“SiC DIPIPM”を製品化し、損失を1/4にまで低減させた(図5)。一方、ボリュームゾーンとなる普及機へは、“DIPIPM Ver. 7シリーズ”を展開している。従来製品に比べて発生損失の低減及び動作温度範囲の拡大による熱的な設計自由度向上だけでなく、ノイズ特性も改善されており、対策部品の削減などトータルシステムコスト低減に寄与できる(図6)。

図5. DIPIPMの損失比較

図6. ノイズ特性の比較

洗濯機や冷蔵庫用途には逆導通IGBT(Reverse Conductive IGBT: RC-IGBT)を搭載した“SLIMDIPシリーズ”，ファンモータ用途には“表面実装型IPMシリーズ”を展開している。さらに、パッケージエアコン用途には三相コンバータ、インバータ、ブレーキ回路及びゲート駆動IC、各種保護回路をオールインにした“DIPIPM+シリーズ”を更に大容量化するなど、白物家電のインバータ化をトータルでサポートしていく。

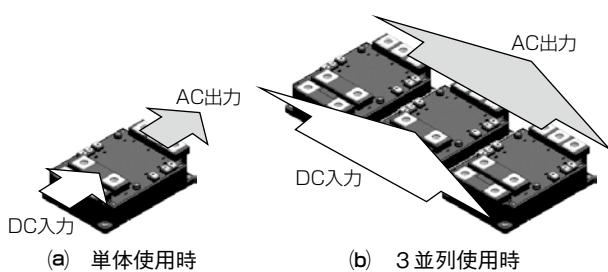

#### 3.2 産業応用製品

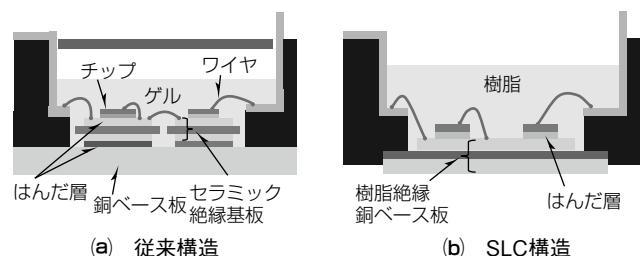

産業応用製品ではBCP(Business Continuity Plan)対策として複数社購買が可能なパッケージ互換性が重要視されている。この市場要求に応えながら“使いやすさ”をキーワードに封止構造、絶縁構造を刷新した。SLC(SoLid Cover)技術を採用した第7世代IGBTモジュール“NXシリーズ”を開発した。SLC技術とは封止材として従来使用していたシリコーンゲルをエポキシ系樹脂に変更し、構成部材の熱膨張率を均一化することで、温度変化に伴うパワーモジュールの反り量を抑制する技術である(図7)。

このSLC技術の最大の特長は、樹脂絶縁銅ベース板を組み合わせることで大幅な温度サイクルの長寿命化が実現できることにある。図8に温度サイクル(条件: -40~125°C: 各1時間保持)の耐量比較結果を示す。従来構造では膨張～収縮による熱起因の機械的ストレスから絶縁基板とベース板を接続するはんだ部分に外周部からクラック(図8(a)で外周部にある黒い箇所がクラック)の進行が確認できる。クラックが更に進行していくと放熱経路を遮断してしまい、

図7. 内部構造の比較

図8. 温度サイクルの耐量比較(超音波探傷画像)

冷却できず破壊にまで至るため寿命設計を行うときに重要なファクタの一つであった。一方、SLC構造では7,000サイクル後でもクラックの前兆は確認できず、非常に高い温度サイクル耐量があることが分かる。

この技術はその他のシリーズにも展開中である。大型インバータや風力発電や太陽光発電などの再生可能エネルギー用途に適した“産業用LV100シリーズ”は市場の高出力化ニーズに応えられるよう、低インダクタンスかつ並列接続が容易な端子配列となっている(図9)。また、IPM“G1シリーズ”は新たに駆動速度切換機能を搭載し、ノイズ源となり得る低電流領域では駆動速度を抑え、効率(=発生損失)に影響する中・大電流領域では高速駆動させることで、ノイズ低減と損失低減を両立させるなど、ユーザーの使いやすさを追求し続けている。

### 3.3 自動車応用製品

移動体の宿命でもある 小さく・軽く・力強く との市場ニーズに伴い、パワーモジュールも小型化・高パワー密度化を進めてきた。小型化要求に対してトランスファーモールド技術を採用した長寿命のパワーモジュール“T-PMシリーズ”を、高パワー密度化要求にはアルミニウム放熱フィンをパワーモジュールのベース板と一体化した“J1シリーズ”を製品化した。チップと電極間の接続にはA1ワイヤボンドを使うのが一般的であったが、DLB(Direct Lead Bonding)を用いることで接合面積を大幅に拡大でき、市場からのパワーサイクル寿命の向上要求に応えている(図10)。

J1シリーズには専用の水冷ジャケットやコントロール基板、スナバコンデンサなどを準備し、ユーザーの設計サポートも充実させている。市場からの更なる出力向上要

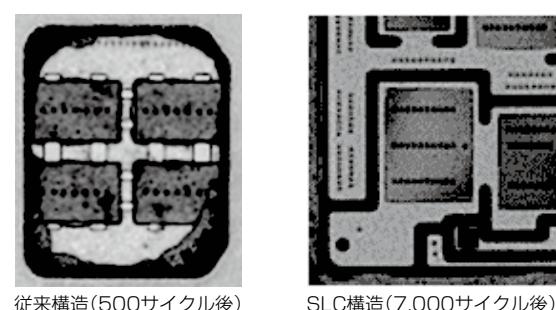

図11. インバータ出力電流比較

求に応えるため、出力電流を拡大させた“大容量J1シリーズ”も追加でラインアップし、さらにSiCチップ化も含め、パワーモジュールの小型化・高パワー密度化を進めていく。

### 3.4 電鉄・電力応用製品

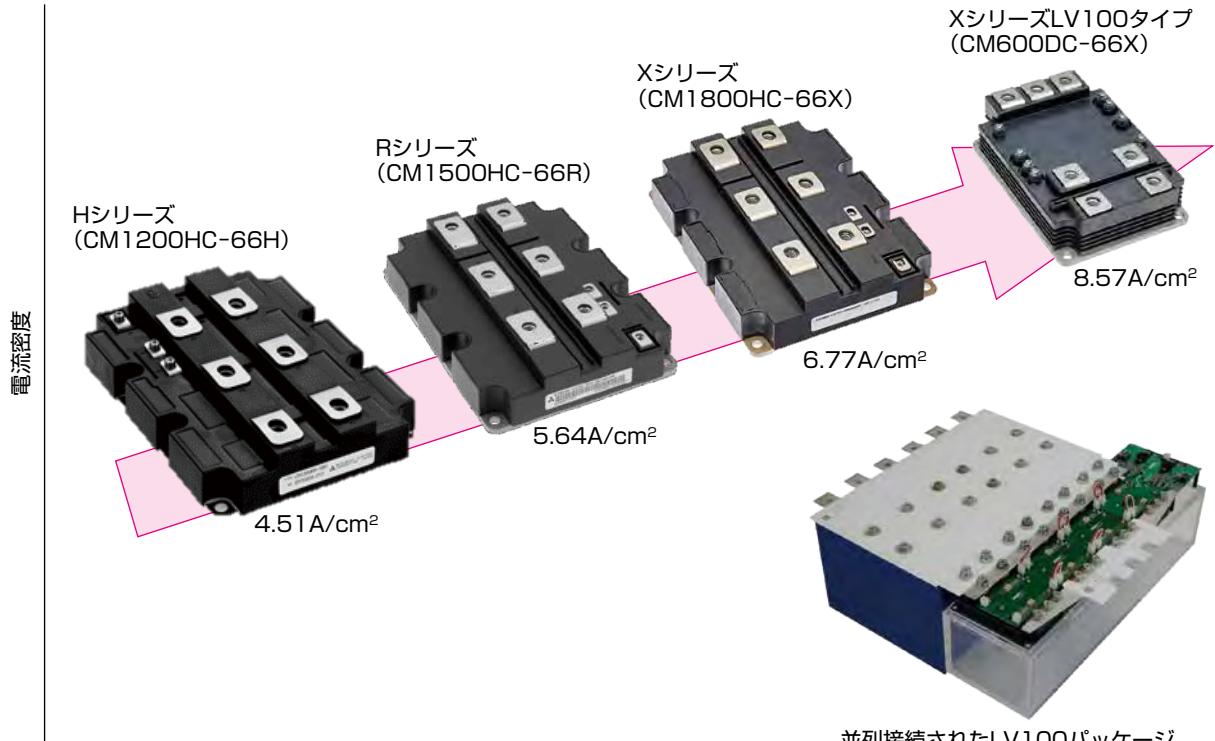

電鉄市場及び洋上風力発電や国際連携直流送電市場では、更なる大容量化・高パワー密度化、パッケージの互換性などの要求があり、当社では従来パッケージと互換性を持った“Xシリーズ・スタンダードタイプ”と、より高パワー密度を実現するために2素子入りの次世代標準パッケージとなる“Xシリーズ・LV100タイプ/HV100タイプ”を展開している。第7世代IGBTチップ技術とRFCダイオードを採用し、従来比20~30%のパワー密度増加を実現した。動作温度Tjopも125°Cから150°Cに拡大したことでインバータ出力電流をRシリーズに比べて50%増加できた(@200Hz動作時)(図11)。

さらにLV100タイプでは3.3kV/750A 2素子入りのSiC製品を開発した。電鉄用途で駆動周波数向上が可能になり、高調波損失の低減などによって大幅なユニットサイズ低減が可能になった。

## 4. むすび

当社はシリコン素材の第7世代チップ、SiCチップを中心とした最新チップ技術とモールドや樹脂封止などの最新パッケージ技術を組み合わせることで、パワーエレクトロニクス市場のどのような要求にも適応できるバランス設計を進めている。タイミングに製品を市場に展開することで、低炭素社会の実現に貢献していく。

### 参考文献

- 島 順洋, ほか:パワーモジュールの最新動向と展望, 三菱電機技報, 90, No.5, 266~270 (2016)

- 岩田明彦, ほか:パワーエレクトロニクス技術の将来展望, 三菱電機技報, 91, No.7, 368~372 (2017)

- ゴーラブ マジュムダール, ほか:パワーモジュールの最新動向と展望, 三菱電機技報, 92, No.3, 158~162 (2018)

図9. LV100の並列例

図10. チップと電極間の接続方法

## 第2世代1.7kV SiC-MOSFET

2nd Generation SiC-MOSFETs with 1.7kV Rating

濱野健一\*

Kenichi Hamano

谷岡寿一\*

Toshikazu Tanioka

折附泰典\*

Yasunori Oritsuki

## 要旨

近年、環境問題などを背景に省エネルギー化のニーズが高まっている。シリコンカーバイド(SiC)デバイスは大幅なエネルギー削減のための次世代デバイスとして、パワーエレクトロニクス機器への適用が始まっている。

三菱電機はSiC-MOSFET(Metal Oxide Semiconductor Field Effect Transistor)やSiC-SBD(Schottky Barrier Diode)の開発を進めており、これまで家電やFA機器、鉄道向けなど幅広い用途でその省エネルギー効果を確認し、製品化を進めてきた。

当社でのSiC-MOSFETの開発は600V, 1,200V, 3.3kVを中心に進んでおり、これまでの開発で培われた技術を適用し、1.7kV耐圧クラスSiC-MOSFETの開発を行った。

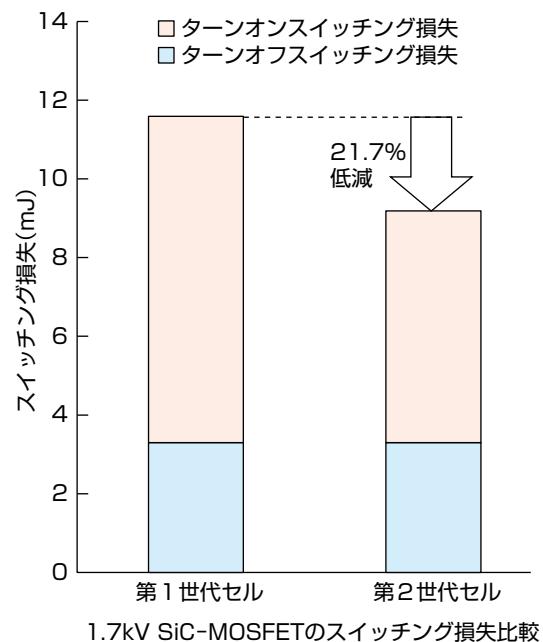

一般産業向けとしては100kHzまでのスイッチングを想定しており、従来のデバイスよりも高い周波数で使用される。そのためスイッチングロス低減を目的として、セルの平面レイアウトの見直しを行った。また今後のSiCデバイス市場の拡大を見据えて、6インチウェーハラインの立ち上げを完了しており、6インチSiCウェーハで試作・検証を実施した。その結果、第2世代セル構造を適用した1.7kV SiC-MOSFETの特性オン抵抗は5.86mΩ・cm<sup>2</sup>、ターンオン及びターンオフのスイッチング損失の合計値は9.2mJを示し、第1世代セル構造と比べてそれぞれ7.9%, 21.7%の低減を実現した。

1.7kV SiC-MOSFETの断面図

JFET : Junction Field Effect Transistor

## 1.7kV SiC-MOSFETの断面図とスイッチング損失

6インチSiCウェーハで試作した1.7kV SiC-MOSFETの断面図(左)と第1世代セルと第2世代セルのスイッチング損失比較(右)を示す。セル構造の変更によって21.7%のスイッチング損失低減を確認した。

## 1. まえがき

SiCデバイスはパワーエレクトロニクス機器の省エネルギー化、小型化を実現するためのキーデバイスとして注目を集めている。

SiCは高い絶縁破壊電界強度を持つため、シリコン(Si)パワーデバイスと比較して、高耐圧かつオン抵抗の低いデバイスを実現できる。ユニポーラ素子でも低オン抵抗が実現できることから、Siバイポーラデバイスと比較して大幅なスイッチング損失の低減が可能になっている。

これまで当社はSiCデバイスを家電やFA機器、鉄道向けなど幅広い用途に適用することで、その省エネルギー効果を確認し、製品化を進めてきた<sup>(1)</sup>。

本稿では1.7kV SiC-MOSFETの開発に当たり、6インチSiCラインで、低オン抵抗化技術を取り入れてデバイス試作を行った結果について述べる。

## 2. 1.7kV SiC-MOSFETの構造

### 2.1 セル構造

プレーナ型nチャネルSiC-MOSFETの断面構造を図1に示す。MOSFETの試作に当たり、次の3点の低オン抵抗化技術<sup>(2)</sup>を適用した。

- (1) チャネルドーピングプロファイルの最適化

- (2) pn接合の浅接合化

- (3) JFET領域へのドーピングとJFET長の縮小

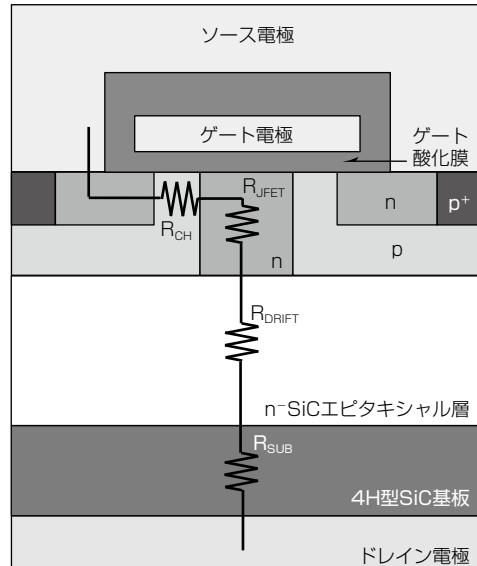

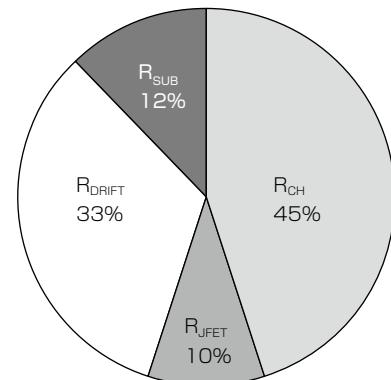

図2に示すとおり、MOSFETのオン抵抗はチャネル領域の抵抗( $R_{CH}$ )、JFET領域の抵抗( $R_{JFET}$ )、SiCドリフト層の抵抗( $R_{DRIFT}$ )、SiC基板の抵抗( $R_{SUB}$ )に大別される。この比率は25°Cでの試算値である。25°Cでの比率としてはチャネル領域の抵抗、及びSiCドリフト層の抵抗が大きな割合を占めている。先に述べたチャネルドーピングプロファイルの最適化によって、チャネル領域の抵抗の低減を実現しており、pn接合の浅接合化によってJFET領域下部の広がり抵抗、及びJFET領域の抵抗を下げている。さらにJFET領域へのドーピング及びJFET長の縮小を行うことで、単位セルを縮小し、デバイス活性領域でのセル密度を向上させている。さらに6インチラインでは基板の裏面を研磨することでデバイスの薄板化を行っており、SiC基板の抵抗を低減することで、更なるオン抵抗低減を実現している。

またスイッチング損失低減を目的として、セルの平面レイアウトの見直しを行っており、第2世代1.7kV SiC-MOSFETに採用した。

図1. プレーナ型SiC-MOSFETの断面構造

図2. 1.7kV SiC-MOSFETのオン抵抗に占める各抵抗の比率

### 2.2 電流センス機能

1.7kV SiC-MOSFETはチップ上に電流センス機能を備えている。SiC-MOSFETは物性上、低オン抵抗が可能であるが、それと引換えに短絡耐量がSi-IGBT(Insulated Gate Bipolar Transistor)と比較して低くなっている。モジュール搭載時に電流センス部で短絡電流を検知することで、短絡発生の際にSiC-MOSFETの迅速な保護を可能にしている。

## 3. 1.7kV SiC-MOSFETの電気特性評価

### 3.1 静特性評価

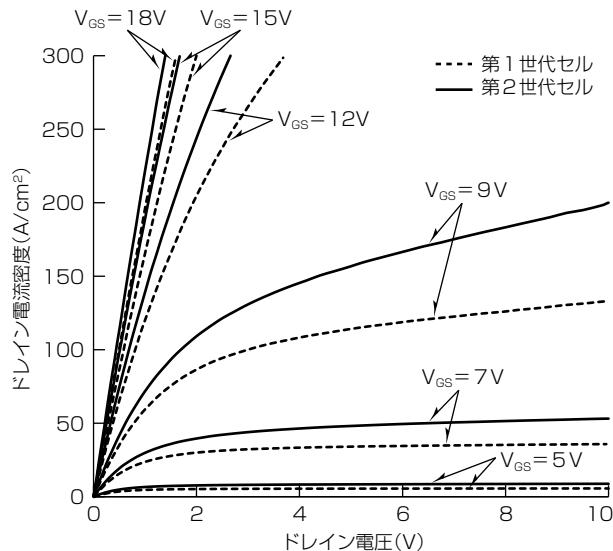

比較のため、第2世代、第1世代のセル構造の1.7kV SiC-MOSFETを試作し、評価を行った。図3に第2世代セル構造と第1世代セル構造のSiC-MOSFETの出力特性の典型例を示す。25°Cでの特性を示しており、ゲート電圧

図3. 1.7kV SiC-MOSFETの出力特性

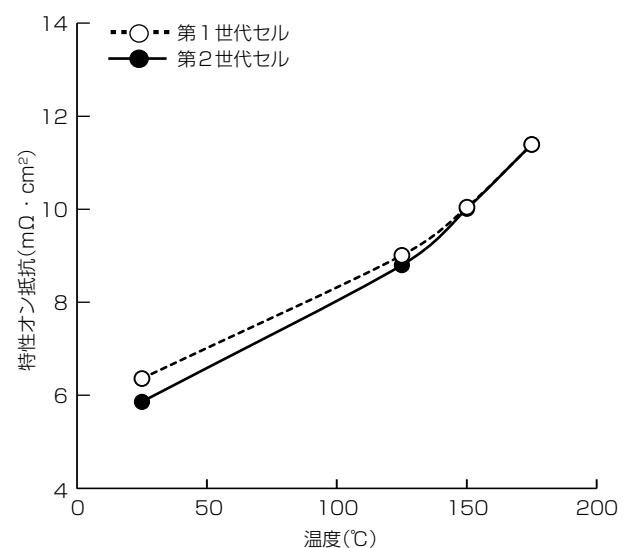

図4. 特性オン抵抗の温度依存性

( $V_{GS}$ )15V時の特性オン抵抗は第2世代セルで5.86mΩ · cm<sup>2</sup>、第1世代セルで6.36 mΩ · cm<sup>2</sup>が得られている。第2世代セル構造を採用することで7.9%のオン抵抗が低減できることを確認した。

また25℃での相互コンダクタンスgmは、ゲート電圧9V付近で第2世代、第1世代セル構造それぞれで135.4S, 96.2Sで第2世代セル構造にすることで改善されていることを確認した。

図4にゲート電圧15V時の特性オン抵抗の温度依存性を示す。温度の上昇につれて特性オン抵抗の低減幅は小さくなる傾向がみられる。これは特性オン抵抗に占める抵抗成分の温度依存性の違いによるものと推察され、温度の上昇に伴って基板や耐圧保持のためのドリフト層の抵抗成分の占める割合が大きくなってくるためと考えられる。

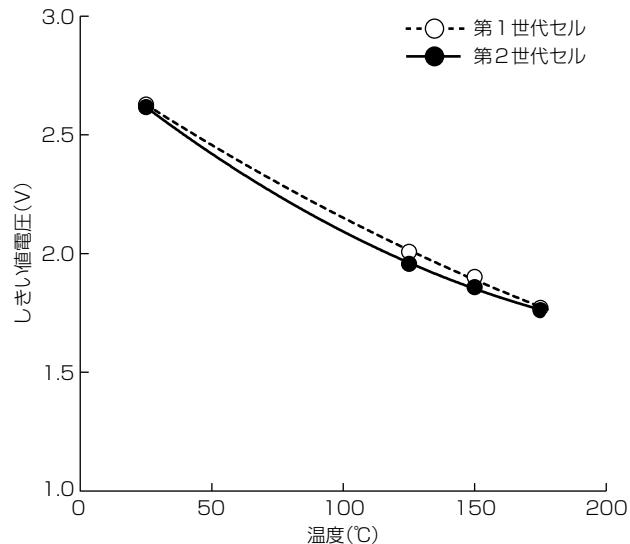

図5にMOSFETのしきい値電圧の温度依存性を示す。この結果はゲート電圧+15V印加、ドレン電流密度100mA/cm<sup>2</sup>時のグラフであり、25℃で2.6V程度、175℃でも1.8V程度のしきい値電圧を保っている。しきい値電圧は温度上昇に伴って単調減少し、第1世代と第2世代のセル構造間の差分は最も開きがある125℃でも2%程度であった。

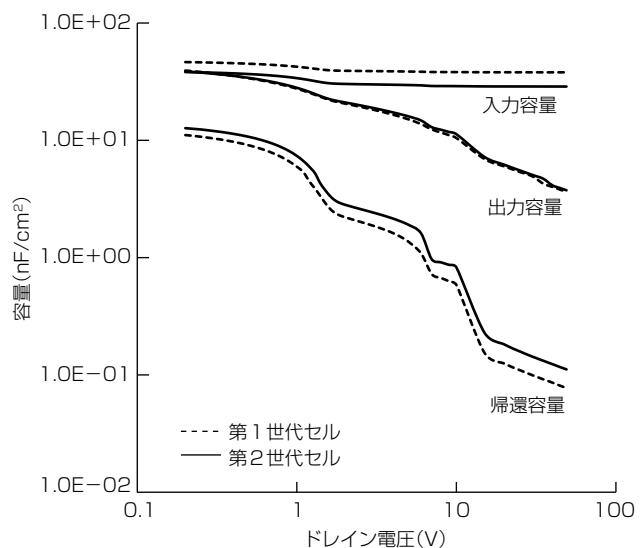

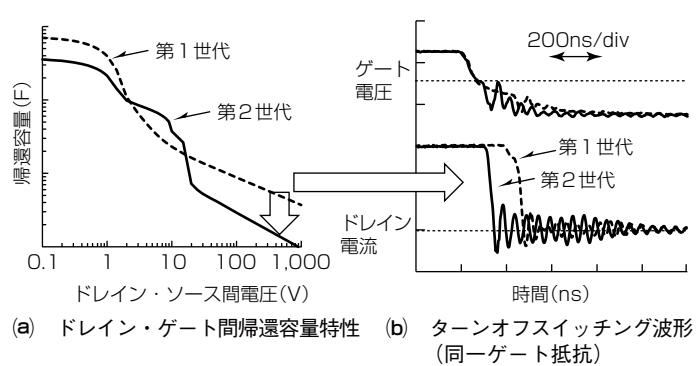

図6にMOSFET容量のドレン電圧依存性を示す。周波数は100kHzで測定を実施しており、出力容量は第1、第2世代セル構造を問わず、ほぼ同様の値を示している。帰還容量は第2世代セル構造/第1世代セル構造の比でドレン電圧10V時に29.3%高くなっている。一方、入力容量は第2世代セル構造/第1世代セル構造の比でドレン電圧10V時に24.0%低減する結果が得られた。デバイスの有効面積に占めるゲート酸化膜領域の割合を下げることで、入力容量の低減を図っており、設計上、第2世代セル構造

図5. しきい値電圧の温度依存性

図6. MOSFET容量のドレン電圧依存性

は第1世代セル構造比でゲート酸化膜領域の割合を20%程度低減している。この結果からおおむね設計値に沿ったデバイスが作製できていることが確認できた。

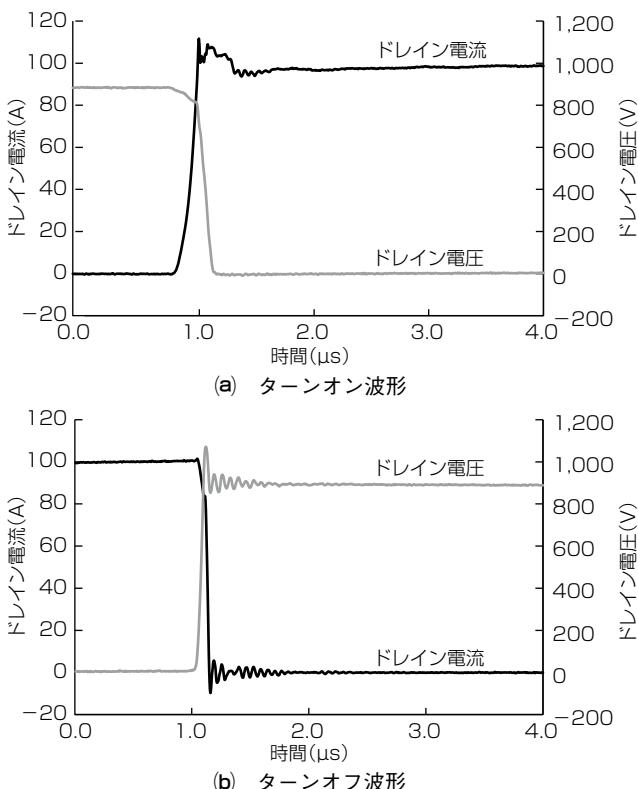

### 3.2 スイッチング特性評価

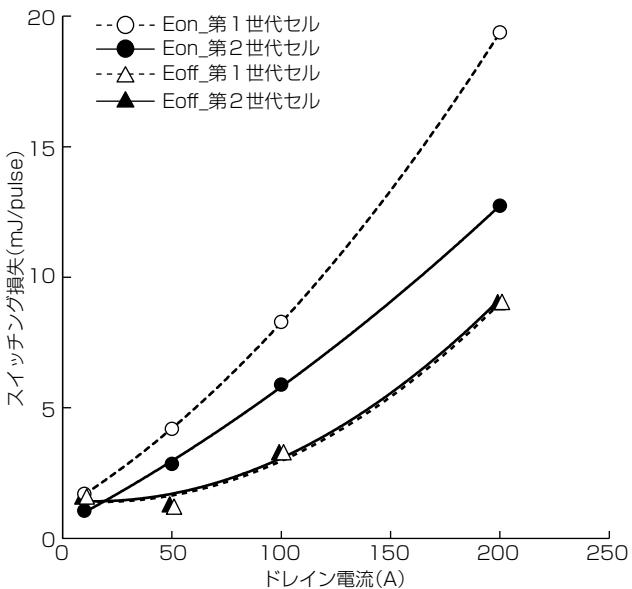

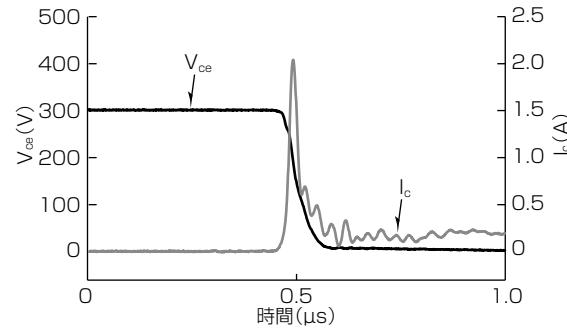

図7にスイッチング波形例と図8にスイッチング損失のドレイン電流依存性を示す。この結果でのゲート抵抗は3.2Ωを使用している。ドレイン電流の増加に伴い、スイッチング損失は単調増加しており、ターンオフ時のスイッチング損失(Eoff)はドレイン電流100A時に3.3mJであり、第1世代、第2世代セル構造間で差はみられない。一方でターンオン時のスイッチング損失(Eon)は、ドレイン電流100A時に第1世代セル構造、第2世代セル構造でそれぞれ8.3mJ、5.9mJとなっており、第2世代セルの採用によって29%程度の低減になることが確認できた。

スイッチング損失の低減については、第2世代セル構造にすることで、ターンオン時のdi/dtに改善がみられて

図7. 1.7kV SiC-MOSFETのスイッチング波形例

図8. スイッチング損失のドレイン電流依存性

いる。第1世代、第2世代セル構造で容量値の変化はあるものの、スイッチング特性に大きな影響は与えておらず、Eonの改善は相互コンダクタンスgmの改善による効果が大きいと推定している。

### 4. むすび

6インチSiCウェーハで1.7kV SiC-MOSFETの試作を行った。低オン抵抗化技術を適用し、高周波向けにセルのレイアウトを見直した結果、特性オン抵抗は $5.86\text{m}\Omega \cdot \text{cm}^2$ 、ターンオン／オフスイッチング損失の合計値は9.2mJを示し、第1世代セル構造比でそれぞれ7.9%、21.7%の特性改善を実現した。

今後はこのSiC-MOSFETをモジュールに搭載し、製品展開をしていくことで、パワーエレクトロニクス機器の省エネルギー化を実現し、環境問題の解決に貢献していく。

### 参考文献

- 1) Imaizumi, M., et al.: Characteristics of 600V, 1200V and 3300V planar SiC-MOSFETs for energy conversion applications, IEEE Trans. Electron Devices, **62**, No.2, 390~395 (2015)

- 2) Hamada, K., et al.: Investigation of Cell Structure and Doping for Low-On-Resistance SiC Metal-Oxide-Semiconductor Field Effect Transistors with Blocking Voltage of 3300V, Jpn. J. Appl. Phys., **52**, 04CP03 (2013)

# 低ロスと高いダイナミックな耐久性を兼ね備えた次世代パワー半導体技術

Next Generation Power Semiconductor Technology with Low Loss and High Dynamic Ruggedness

中村勝光\*

Katsumi Nakamura

金田和徳†

Kazunori Kanada

鈴木健司\*

Kenji Suzuki

川瀬祐介\*

Yusuke Kawase

西 康一\*

Koichi Nishi

## 要旨

21世紀に入り、世界の人口増加による将来へのエネルギー、食料や水等の資源不足や地球温暖化という二つの地球規模での問題に対し、経済発展と地球環境の調和の取れた次世代社会構築という大きな課題が突きつけられている。この目指すべき社会の実現には、エネルギー効率を上げる技術の開発が急務である。エネルギー変換デバイスであるパワー半導体は、パワーエレクトロニクスの低消費エネルギー化や高効率化を担う中核となる構成要素であり、次世代社会で求められる高エネルギー効率化に向け重要な役割を果たす技術の一つである。

期待を集めているパワー半導体のIGBT(Insulated Gate Bipolar Transistor)とFWD(Free Wheeling Diode)のON電圧とスイッチングロスの低減には、デバイス厚みをシリ

ンクする方法が最も効果的である。一方で、最新デバイスには、低ロス化、ターンオフ動作の制御性、高いダイナミックな耐久性や広い動作温度範囲という高性能化と、高コストパフォーマンスというコスト面の継続的な要求がある。よって、パワー半導体の持続的な発展には、安価で大口径( $\geq 200\text{mm}$ )なSi(シリコン)ウェーハを用いてのブレークスルーとなる技術が必要である。

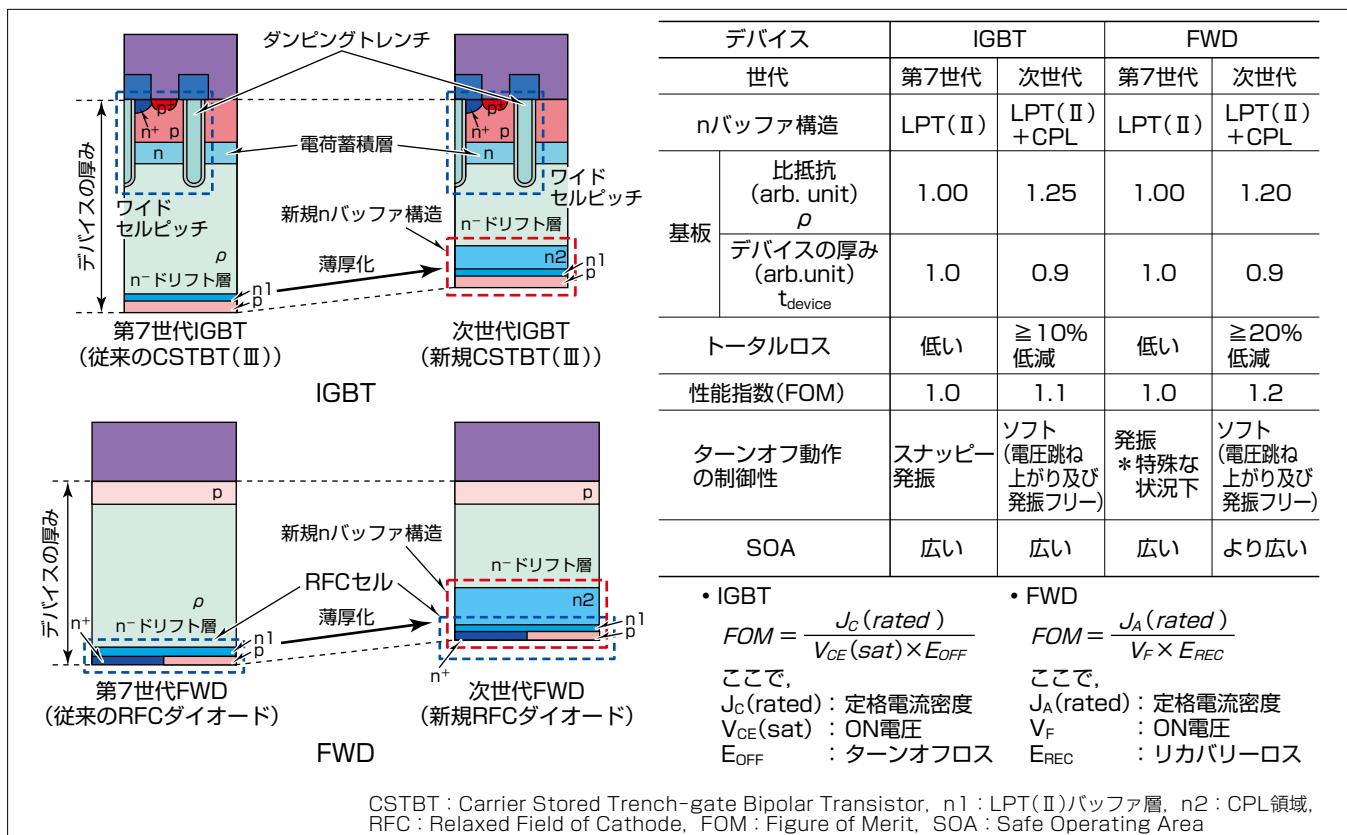

今回、大口径なウェーハの製造技術にマッチングしながら、IGBTとFWDの低ロス化と高いダイナミックな耐久性を実現する新規nバッファ技術を開発した。提案する技術は、今後の次世代パワー半導体のコア技術であり、Si系パワー半導体の更なる飛躍と発展に寄与し、周囲の期待に応える技術である。

## 次世代パワー半導体技術である新規nバッファ構造及びIGBTとFWDの性能面の特徴

新規nバッファ構造は、LPT(Light Punch-Through)(II)バッファ層とCPL(Controlling Carrier-Plasma Layer)領域からなる構造である。LPT(II)バッファ層は、パワー半導体の基本性能である高温下を含めた耐圧保持能力面に寄与し、CPL領域はダイナミック動作時のデバイス内部状態の制御による耐久性向上に寄与する。新規nバッファ構造は、大口径なSiウェーハの製造方法にマッチングした次世代パワー半導体のコア技術である。

## 1. まえがき

パワー半導体は、厳しい使用環境下で使われるパワー電子回路の基本性能や信頼性を担う重要な構成要素である。パワー半導体の縦構造を構成するnバッファ層は、パワー半導体のトータル性能向上や性能間のバランス化の観点から、キーテクノロジーである。一方、パワー半導体のコストパフォーマンス向上の一方向性として、TWP(Thin Wafer Process)技術と組み合わせてのSiウェーハの大口径化( $\geq 200\text{mm}$ )がある。つまり、パワー半導体の持続的な発展には、大口径なSiウェーハを用い、TWP技術とマッチングするnバッファ技術の構築が必要である。

本稿では、最新のパワー半導体の抱える上記課題に対し、LPT(II)バッファ層とCPL領域からなる新規nバッファ構造がその解決策であることを示す。

## 2. 新規nバッファ構造

### 2.1 構造

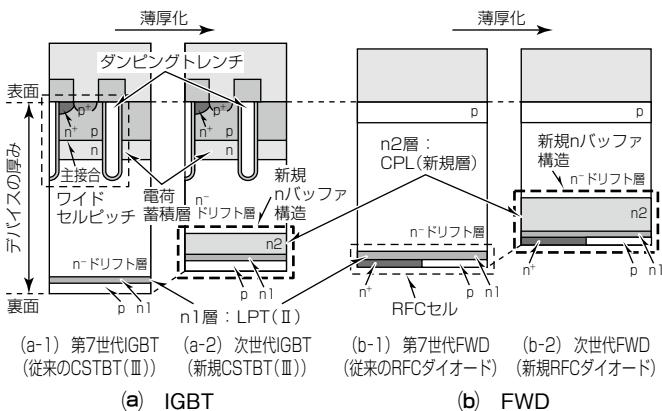

図1(a-2)と図1(b-2)には、それぞれ今回提案するnバッファ構造を持つIGBTとFWDのデバイス構造を示す。表1は、新規nバッファ構造を構成するLPT(II)バッファ層(n1)とCPL領域(n2)の構造パラメータを示す。ここで、従来のnバッファ構造は、LPT(II)バッファ層だけの構造である(図1(a-1)と図1(b-1))。

図1. 1,200V IGBTとFWDのデバイス構造模式図

表1. 新規nバッファ構造の構造パラメータ

| バッファ構造          | LPT(II)(n1)     | CPL(n2)                      |

|-----------------|-----------------|------------------------------|

| ドーピング濃度及びプロファイル | 低濃度で急峻なプロファイル   | n1層より低濃度で緩やかなプロファイル          |

| 深さ              | 浅い              | 深い                           |

| キャリアライフタイム      | 長い              | 中程度(トランジスタが存在する)             |

| 働き              | ・裏面側への空乏層伸びを止める | 裏面側<br>・キャリアアラズマ層制御<br>・電界緩和 |

新規nバッファ層は、次の役割を担う二つの構成要素を組み合わせた構造である。

### (1) LPT(II)バッファ層<sup>(1)</sup>

- ①主接合への逆バイアス条件下の動作時に裏面(コレクターカソード)側へ伸びる電界強度だけを止める。

- ②十分な耐圧保持能力と高温( $\geq 448\text{K}$ )での熱暴走を抑制して高温動作を実現する。

### (2) CPL領域<sup>(2)</sup>

- ①ダイナミック動作時に裏面側に蓄積したキャリアアラズマ層を制御して電界強度の勾配を緩やかにし、寄生pnpトランジスタの増幅率制御やキャリア再結合を促進する。このように二つの構成要素を活用するのは、デバイス性能面だけでなく、製造工程での各構成要素形成時のスループット向上を実現するためでもある。CPL領域は、イオン種として荷電粒子を用い、高エネルギーイオン注入とTWP技術にマッチングする低温アニーリング技術を用いて形成する。

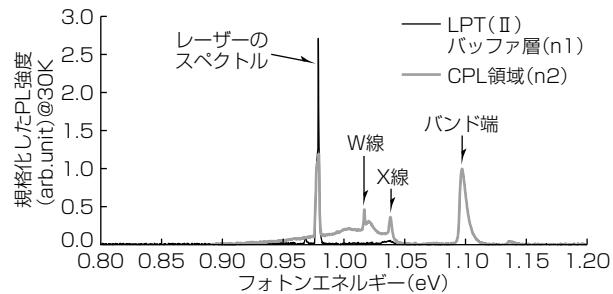

図2は、LPT(II)バッファ層とCPL領域それぞれに関するPL(PhotoLuminescence)法で解析したスペクトル結果である。CPL領域は、LPT(II)バッファ層に比べて二つの特徴的なピークの準位が存在する。この二つの準位は、TWP技術によって制御することで、IGBTとFWDの裏面側のキャリアアラズマ層制御に寄与し、高いダイナミックな耐久性に優れたデバイス性能を実現する。

### 2.2 ダイナミック動作への寄与

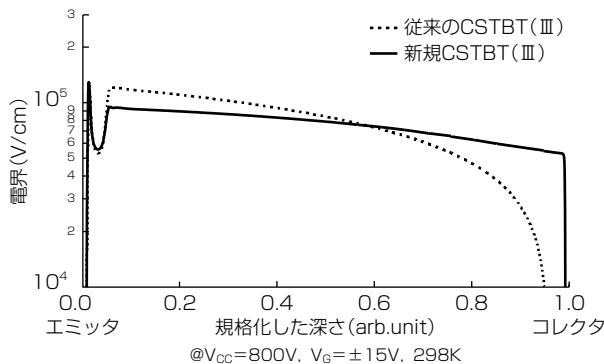

図3は、CSTBT(III)の短絡状態での電界強度分布のシミュレーション結果である。図3から、従来構造では主接合の電界強度上昇による温度上昇を招き、短絡耐量が低下する可能性がある。CPL領域を持つIGBTでは、短絡中の裏面側キャリアアラズマ層制御によって裏面側へ空乏層が伸び、バランスの取れた電界強度分布を実現し、従来構造よりも短絡耐量が向上することが見込める。

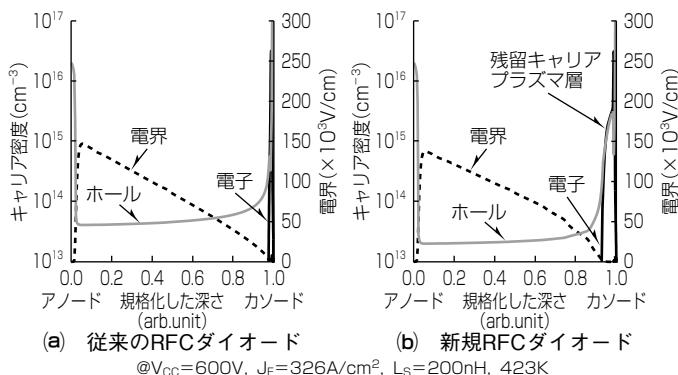

図4は、RFCダイオードのリカバリー動作終焉(しゅうえん)時のデバイス内部状態のシミュレーション結果である。図4から、従来のRFCダイオードに比べてCPL領域を持つ新規RFCダイオードは、カソード側に残留キャリアアラズマ層が存在することでカソード側の電界強度を緩和する。

図2. 新規nバッファ層のPLスペクトル

図3. シミュレーションによる短絡状態でのCSTBT(III)の縦方向の電界強度分布

@ $V_{CC}=800V$ ,  $V_G=\pm 15V$ , 298K

図4. シミュレーションによるリカバリー動作終焉時のRFCダイオード内部状態

@ $V_{CC}=600V$ ,  $J_F=326A/cm^2$ ,  $L_S=200nH$ , 423K

和させる効果がある。この効果は、後述するリカバリー動作後半での電圧跳ね上がり挙動(スナップオフ)を抑制し、制御性の良いスイッチング特性の実現が見込める。

### 3. 新規nバッファ構造の効果

#### 3.1 1,200V IGBTの性能<sup>(3)</sup>

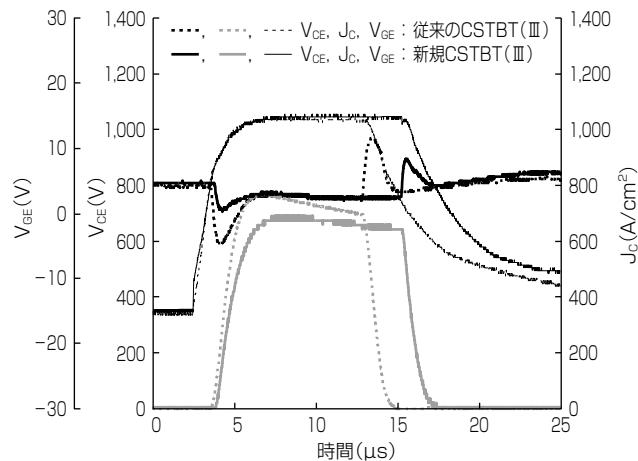

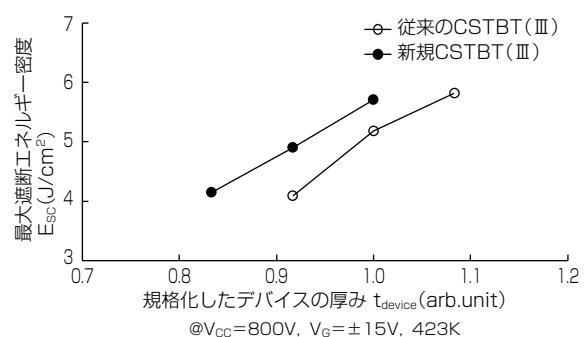

図5は、1,200V CSTBT(III)の短絡波形を示す。図6は、短絡時の最大遮断エネルギー密度( $E_{SC}$ )とデバイスの厚み( $t_{device}$ )との関係のnバッファ構造依存性を示す。図5及び図6から、新規IGBTは、従来構造よりもSCSOA(Short Circuit Safe Operating Area)が向上し、十分なSCSOAを保証しながら、デバイスの厚みのシューリング化が可能である。

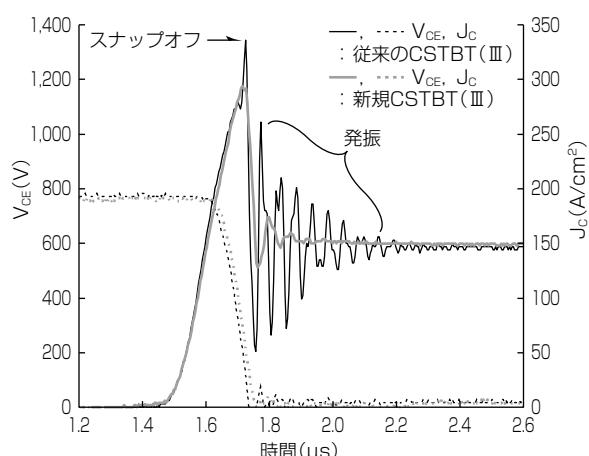

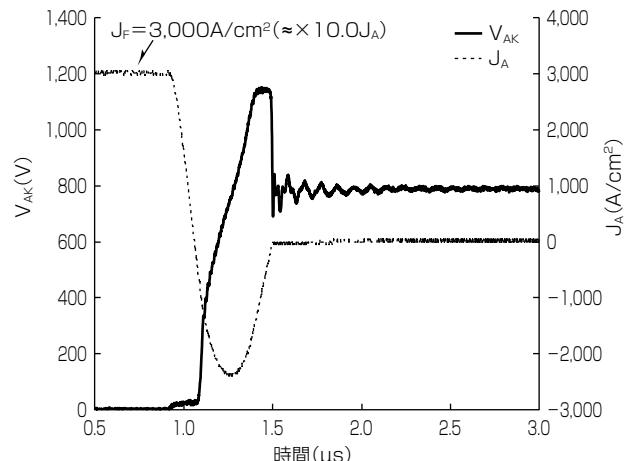

図7は、1,200V CSTBT(III)のターンオフ波形のnバッファ構造依存性を示す。新規nバッファ構造を持つIGBTは、ターンオフ動作後半にコレクタ側に残留キャリアアラズマ層が存在する。その結果、新規IGBTでは、ターンオフ動作時のコレクタ側電界強度を緩和し、従来のIGBTのようなスナップオフ及びその後の発振を抑制し、優れたターンオフ動作を示す。よって、新規IGBTは従来のIGBTに比べ、幅広いアプリケーションに適用可能であることが分かる。

図5. 1,200V CSTBT(III)での短絡波形

@ $V_{CC}=800V$ ,  $V_G=\pm 15V$ , 423K

図6. 種々の1,200V CSTBT(III)の $E_{SC}$ と $t_{device}$ の関係

@ $V_{CC}=800V$ ,  $V_G=\pm 15V$ , 423K

図7. 種々の1,200V CSTBT(III)でのターンオフ波形

@ $V_{CC}=600V$ ,  $J_C=183A/cm^2$ ,  $dv/dt=5,000V/\mu s$ ,  $V_G=\pm 15V$ ,  $L_S=200nH$ , 298K

#### 3.2 1,200V FWDの性能<sup>(2)</sup>

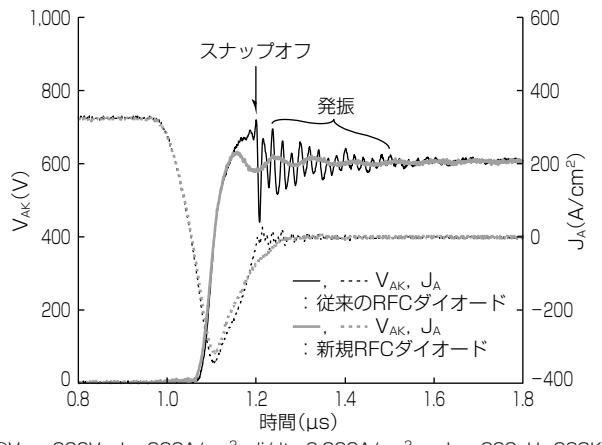

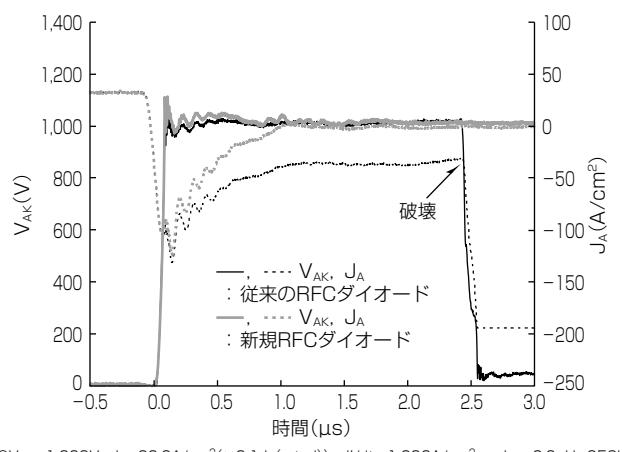

図8は、1,200V RFCダイオードのリカバリー波形のnバッファ構造依存性を示す。新規nバッファ構造を持つRFCダイオードは、CPL領域の働きによって、リカバリー動作終焉時のスナップオフ及びその後の発振現象を抑制し、ソフトリカバリーの挙動を示す。

図9は、1,200V RFCダイオードのスナップオフリカバリー動作に着目したスイッチング条件下でのリカバリー

図8. RFCダイオードでのリカバリーワーク

図10. 新規RFCダイオードのターンオフ遮断能力

図9. RFCダイオードでのスナッピーリカバリーワーク

図11. 1,200V CSTBT(III)とRFCダイオードのON電圧とスイッチングロスのトレードオフ特性

## 4. むすび

LPT(II)バッファ構造に代わるLPT(II)層とCPL領域からなる新規nバッファ構造を開発した。提案するnバッファ構造では、ダイナミック動作時の制御性、耐久性向上や熱的安定性を兼ね備えながら、デバイスの厚みのシーリングによる低トータルロス性能を実現する結果が得られた。

新規nバッファ技術は、IGBT、FWDの性能向上と大口径化( $\geq 200\text{mm}$ )するSiウェーハの製造技術にマッチングすることから、Si系パワー半導体の更なる飛躍と持続的な技術開発を支える有効なコア技術である。

## 参考文献

- (1) Nakamura, K., et al.: The Second State of a Thin Wafer IGBT—Low Loss 1200V LPT-CSTBT™ with Backside Doping Optimization Process—, Proc. of ISPSD, 133~136 (2006)

- (2) Nakamura, K., et al.: Advanced RFC diode utilizing a Novel Vertical Structure for Softness and High Dynamic Ruggedness, Proc. of ISPSD, 117~120 (2017)

- (3) Suzuki, K., et al.: N-buffer Design Optimization for Short Circuit SOA Ruggedness in 1200V class IGBT, Proc. of ISPSD, 128~131 (2018)

- (4) Nakamura, K., et al.: Advanced Si Power Semiconductor with High Dynamic Ruggedness utilizing Novel Vertical Structure, Proc. of JSAP Spring Meeting, 100000001~135 (2019)

# 特集論文

## HVIGBTモジュールの耐湿性確認技術

Humidity Robustness Verification Technologies for High Voltage Insulated Gate Bipolar Transistor Modules

羽鳥憲司\*

Kenji Hatori

田中宜彦\*

Nobuhiko Tanaka

中村圭一\*

Keiichi Nakamura

本田成人\*

Shigeto Honda

### 要旨

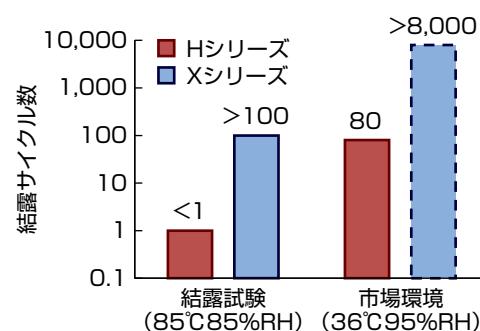

大電力を高速にスイッチングする三菱電機のHVIGBT (High Voltage Insulated Gate Bipolar Transistor)モジュールは、1997年に製品化して以来、高い信頼性が評価され、主に電鉄の駆動システムや工業用大型機器、HVDC(High Voltage DC transmission)などの電力変換装置に広く採用されてきた。これまで当社はHVIGBTモジュールの性能向上に取り組み、2008年に“Rシリーズ”HVIGBT、2015年に“Xシリーズ”IGBTをそれぞれ市場投入し、電流容量の増加や動作温度の拡大を実現し、電鉄・電力市場の発展に大きく貢献してきた。

近年、市場の拡大に伴ってパワー半導体が様々な環境下

で使用されるようになってきた。電鉄・電力市場では、高い信頼性が求められるため、こうした様々な環境に対する耐環境性能を確認することの重要性が高まっている。また、湿度の高い環境については、モジュールが密閉構造ではないため、その影響を完全に排除することは難しく、耐湿性の確認技術が強く求められていた。

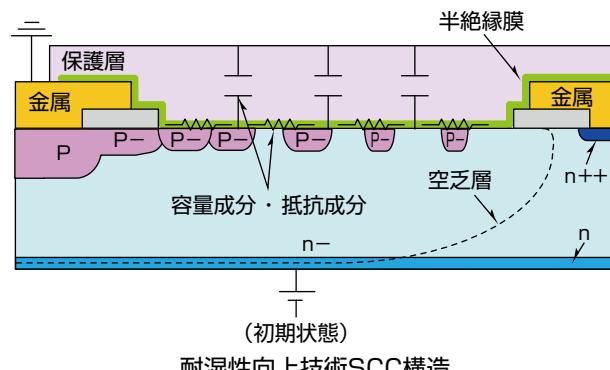

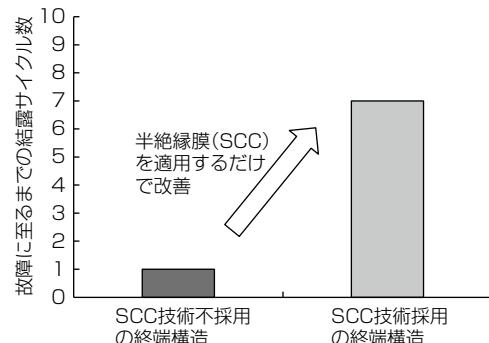

こうした背景を踏まえ、当社ではHVIGBTモジュールの耐湿性確認技術の構築に取り組んできた。湿度による故障メカニズムとして、表面電荷の蓄積による新たな故障モードがあることを確認し、Xシリーズチップで採用しているSCC技術の採用が有効であることを確認した。

| 型名           | 定格電圧   | 定格電流   |

|--------------|--------|--------|

| CM1800HC-66X | 3,300V | 1,800A |

耐湿性向上技術SCC構造を採用した

HVIGBTモジュール“Xシリーズ”

耐湿性向上技術SCC構造

Xシリーズの耐結露性検証試験結果

SCC : Surface Charge Control, RH : Relative Humidity

### 耐湿性向上技術であるSCC技術を採用したHVIGBTモジュール“Xシリーズ”

耐湿性向上技術であるSCC技術を採用したHVIGBTモジュール“Xシリーズ”の“CM1800HC-66X(定格：3,300V/1,800A)”で、耐結露性検証試験を実施した。従来品種の“Hシリーズ(SCC構造不採用)”では結露試験1サイクルでNGであったが、SCC構造を採用することで100サイクルでも問題ないことを確認し、SCC構造が耐結露性に優れていることを確認した。

## 1. まえがき

鉄道は他の交通機関と比較してエネルギー効率に優れており、交通分野全体の環境負荷の軽減に資することから、地球温暖化問題の解決への貢献のため、鉄道の利用が世界的に促進されている。また、低炭素社会の実現の観点から、鉄道の非電化区間の電化や、蓄電池車両の導入などが推進されている。それに伴い、電車が地球上の様々な環境で走行するようになってきた。

鉄道車両用パワーモジュールは小型・低損失であることと加えて、民生・一般産業用途に比べて高い信頼性が要求されている。そのため、こうした様々な環境に対する耐環境性能を確認することの重要性が高まっている。特に湿度の高い環境については、モジュールが密閉構造ではないため、その影響を完全に排除することは難しく、耐湿性の確認技術が強く求められていた。

こうした背景を踏まえ、当社ではHVIGBTモジュールの耐湿性確認技術の構築に取り組んできた。こうした耐湿性確認技術に基づき、耐湿性に優れた構造であるSCC技術の有効性を確認し、当社最新世代HVIGBTモジュールであるXシリーズを開発した。

本稿では、Xシリーズによる検証結果などを交えながら、これまでに当社が培ったHVIGBTモジュールの耐湿性確認技術について述べる。

## 2. 湿度による故障メカニズム

### 2.1 既知の故障メカニズム

パワー半導体チップは、そのチップ外周を囲う終端部での耐圧を保持している。通常、その終端部にはアルミニウム電極がリング状に配置され、各々のリングが電圧を分担する役割を持っているが、湿気の侵入によってこれらのアルミニウム電極が腐食して、その機能を失うことによる故障モードが知られている<sup>(1)</sup>。また、銅や銀などのエレクトロケミカルマイグレーション(ECM)も従来知られている故障モードの一つである<sup>(1)</sup>。

### 2.2 新たな故障メカニズム

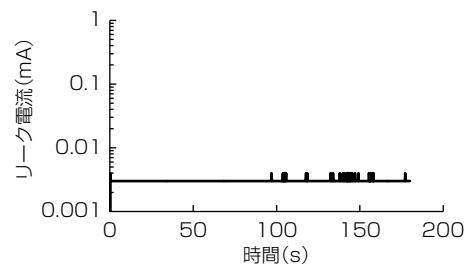

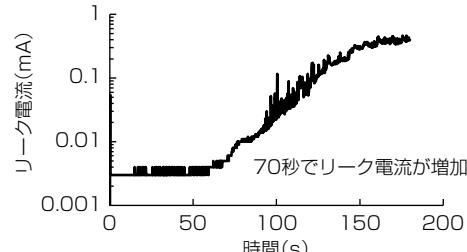

当社がパワー半導体の耐湿性について研究してきた中で、先に述べたアルミニウム腐食やECM以外にも、パワー半導体の故障を引き起こす可能性のある故障モードを新たに発見した。以前から知られているアルミニウム腐食やECMは故障に至るまで一定の時間を要するのに対し、新たに発見した故障モードでは図1に示すように、数十秒

から数百秒でも電圧印加時のリーク電流の増加がみられた。アルミニウム腐食やECMの進行には不十分な時間であり、新たな故障メカニズムであることが確認された<sup>(2)</sup>。

新たに発見された故障モードは、HVIGBTモジュールを吸湿させた後、急冷して結露状態を発生させた上で、DC電圧を印加することで確認することが可能である。図1に示すように、モジュールが乾燥した状態ではDC電圧を印加してもリーク電流の増加はみられなかった素子が、結露状態でDC電圧を印加すると、わずか70秒でリーク電流の増加がみられた。この結果では、破壊に至ってはいないが、DC電圧印加中にみられるリーク電流の増加は耐圧性能が不安定になったものと推定される。

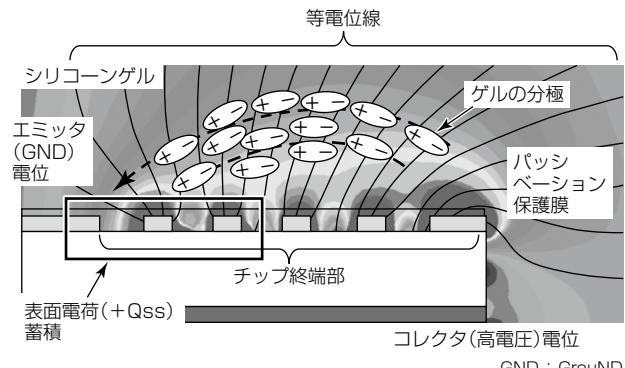

結露によってリーク電流が増加するメカニズムは次のとおりである。素子に電圧を印加すると、誘電体であるゲルがモジュール内部の電界に沿って分極する。また、同時にモジュールが吸湿すると、ゲルの分極との相乗効果によって、パワー半導体チップの終端部に表面電荷(+Qss)が蓄積する(図2)。

(a) 乾燥状態で電圧印加

(b) 結露状態で電圧印加

図1. 結露状態での電圧印加試験

図2. 結露状態でのモジュール内部の挙動

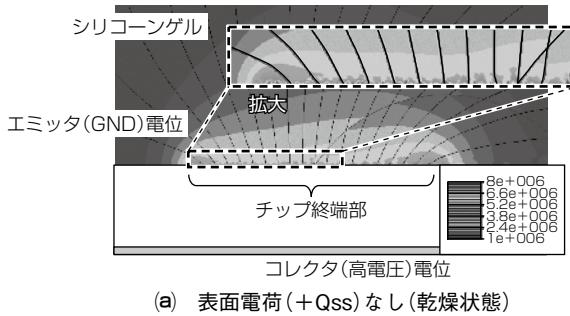

(a) 表面電荷(+Qss)なし(乾燥状態)

(b) 表面電荷蓄積(結露状態)

図3. 結露状態でのモジュール内部の挙動

図3に表面電荷(+Qss)が存在しない場合と、+Qssが蓄積する場合のチップ終端部の電界分布を示す。チップ終端部に表面電荷(+Qss)が蓄積すると、チップ終端部の電界が高くなり、素子耐圧が劣化し、リーク電流が増加し、最悪の場合素子故障に至るおそれがあることを確認した。

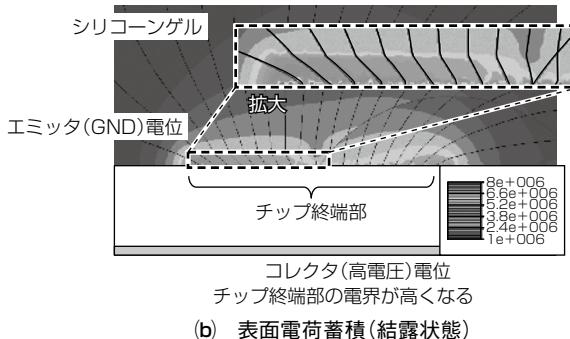

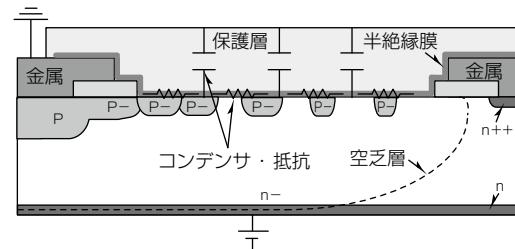

### 3. 耐湿性向上技術：SCC

こうした新たに発見された故障モードについて、当社ではSCC技術<sup>(3)</sup>を開発し、耐湿性を向上させたHVIGBTモジュール“Xシリーズ”をリリースした。図4に従来のチップ終端構造、図5にSCC技術を採用したチップ終端構造を示す。従来構造ではチップ終端部を絶縁膜で被覆していたが、SCC技術を採用した終端構造ではチップ終端部を半絶縁膜で被覆している。

従来構造ではチップ終端部が絶縁膜で覆われているために、蓄積された表面電荷(+Qss)が解放される経路がないのに対し、SCC技術を採用した終端構造では表面電荷(+Qss)が半絶縁膜を介して解放されるために、表面電荷がチップ終端部の電界に悪影響を及ぼすことがない。そのため、結露状態でも、良好な耐圧性能を保持できる。

SCC技術の効果について、先に述べた結露状態の電圧印加試験で確認した結果を図6に示す。図に示すように、同じチップ構造であっても、SCC技術を採用していない場合には1サイクルでリーク電流の増加がみられたものが、SCC技術を採用することで7サイクルまでリーク電流の増加がみられないことを確認した。

図4. 従来のチップ終端構造(絶縁膜で被覆)

図5. SCC技術を採用したチップ終端構造(半絶縁膜で被覆)

図6. 結露状態での電圧印加試験結果

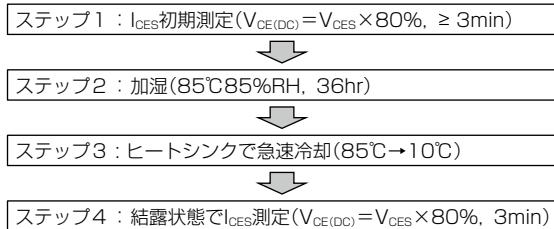

### 4. 耐結露性確認試験(結露サイクル試験)

これまで述べてきた結露試験方法を図7に示す。この方法では、高温高湿槽内で85°C 85%RHの環境下で吸湿させた後に、槽から取り出してヒートシンクで冷却するため、繰り返し試験に不向きであった。しかしながら、耐結露性を評価するには繰り返し試験の構築は不可欠である。また、従来の結露試験では、市場における高湿度環境下で発生する結露に対して、どの程度の加速試験になっているか不明であった。そこで、当社ではこれらの課題の解決に取り組んだ。

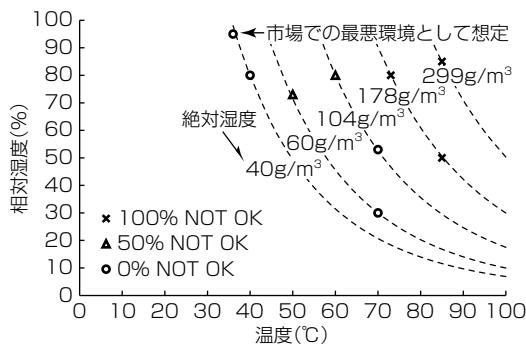

#### 4.1 市場での最悪環境の調査

当社では、市場での最悪環境を確認するため、様々な環境下でモジュールを吸湿させた後に、急冷・結露させて電圧印加する結露試験を実施した。試験に用いた素子は3.3kV-IGBT(定格：3,300V/1,200A)である。その結果を図8に示す。

図8に示すように、絶対湿度(Absolute Humidity: AH)

図7. ヒートシンクによる単発結露試験方法

図8. 様々な環境で吸湿させての結露試験結果

が高いほど結果が悪く、同じ絶対湿度であっても相対湿度 (Relative Humidity : RH) が高いほど結果が悪いことを確認した。つまり、絶対湿度と相対湿度がともに高い条件が市場での最悪条件と言える。環境条件に関する規格IEC 60721-3-5に規定される5K2クラスでは、温度変化がある場合の最悪条件は30°C 95%RH29g/m<sup>3</sup>と規定されており、これに約10g/m<sup>3</sup>のマージンを加えて、ここでは36°C 95%RH40g/m<sup>3</sup>を市場での最悪環境として想定した。

#### 4.2 市場環境に対する結露試験の加速率調査

4.1節で設定した市場での最悪環境に対して、結露試験がどの程度の厳しさとなっているか確認するため、市場環境最悪条件で吸湿後に急冷する結露試験を実施し、85°C 85%RHで吸湿させた後に急冷する通常の結露試験との比較評価を実施した。表1に示す結果から、市場の最悪条件と比較しても、構築した結露試験は少なくとも80倍の加速を得られていることを確認した。なお、この試験は、後述する結露サイクル試験で評価している。

#### 4.3 結露サイクル試験方法の構築

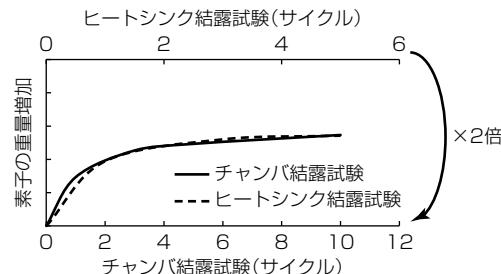

先に述べたとおり、従来の結露試験方法では、槽から取り出してヒートシンクで冷却するというプロセスを経るため、サイクル試験に向きであった。サイクル試験を実現するため、高温高湿チャンバでの冷却によるサイクル試験を導入し、従来のヒートシンク冷却と同等の効果を得られるか確認した。サイクル数に対する素子の吸湿量の推移を比較した結果を図9に示す。図に示すように、ヒートシンク結露試験と比較して、チャンバ結露試験では2倍のサイ

表1. 市場環境最悪条件vs結露試験条件

|                           |           |

|---------------------------|-----------|

| 市場環境最悪条件(36°C 95%RHからの冷却) | 1サイクルでNG  |

| 結露試験条件(85°C 85%RHからの冷却)   | 80サイクルでNG |

図9. サイクル数に対する素子の吸湿量の推移

表2. Xシリーズ結露サイクル試験結果

|                        |            |

|------------------------|------------|

| 従来素子(3,300V/1,200A)    | 1サイクルでNG   |

| Xシリーズ素子(3,300V/1,800A) | 100サイクルでOK |

クル数にすることで、同等の効果を得られることを確認し、サイクル試験化に目処(めど)をつけた。

#### 4.4 Xシリーズ結露サイクル試験結果

既に述べてきたように、Xシリーズでは耐湿性に優れたSCC技術を適用している。Xシリーズについて、結露サイクル試験で評価した結果を表2に示す。その結果によって、従来素子に比べて100倍以上の耐結露性を持つことを確認した。先に述べた加速係数を考慮すると、市場での最悪環境相当での8,000回の結露に相当する。

## 5. むすび

湿度による故障メカニズムとして、表面電荷の蓄積による新たな故障モードがあることを確認し、Xシリーズチップで採用しているSCC技術の採用が有効であることを確認した。また、サイクル試験が可能な結露試験方法を構築し、Xシリーズが結露試験100サイクルに耐え、市場での最悪環境相当でも8,000回の結露に耐え得ることを確認した。

当社はこれらの耐湿性評価技術や耐湿性向上技術を用いて、パワー半導体モジュールの高い信頼性を実現し、低炭素社会と豊かな生活の両立の実現に貢献していく。

## 参考文献

- Zorn, C., et al.: Acceleration of Temperature Humidity Bias (THB) Testing on IGBT Modules by High Bias Levels, ISPSD, 385~388 (2015)

- Tanaka, N.: Robust HVIGBT module design against high humidity, PCIM Europe, 368~373 (2015)

- Honda, S.: High Voltage Device Edge Termination for Wide Temperature Range plus Humidity with Surface Charge Control(SCC) Technology, ISPSD, 291~294 (2016)

- Nakamura, K.: The test method to confirm robustness against condensation, EPE, No.17 (2019)

# 表面実装パッケージ型IPMの パッケージ技術

鹿野武敏\*

Taketoshi Shikanai

作谷和彦\*

Kazuhiko Sakutani

Packaging Technologies of Surface-mount Package Intelligent Power Module

## 要旨

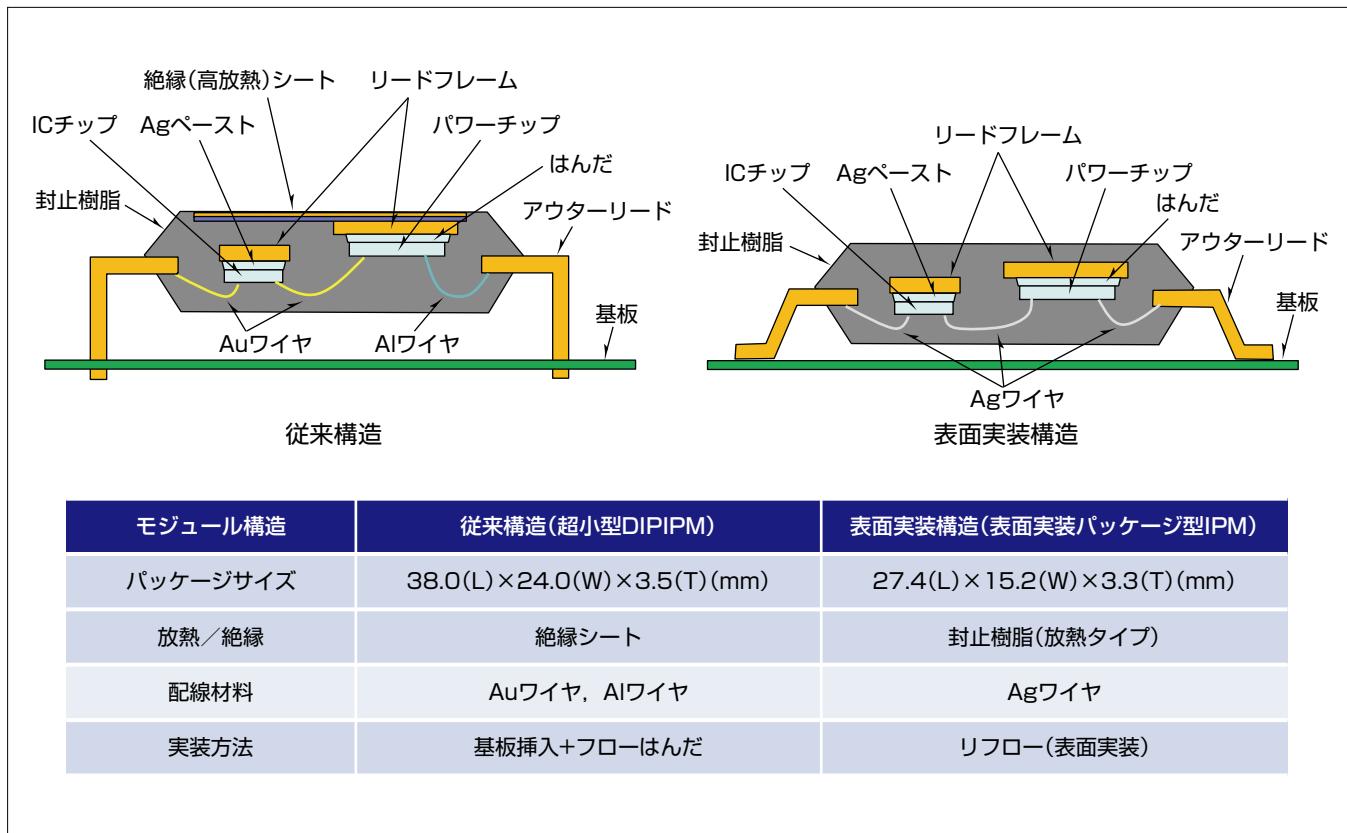

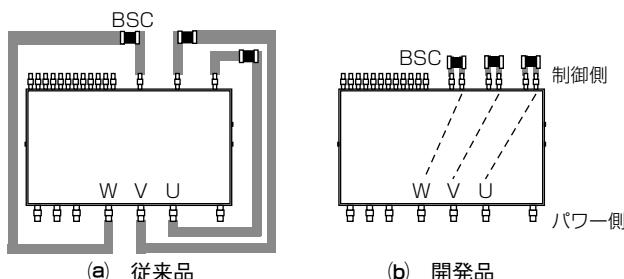

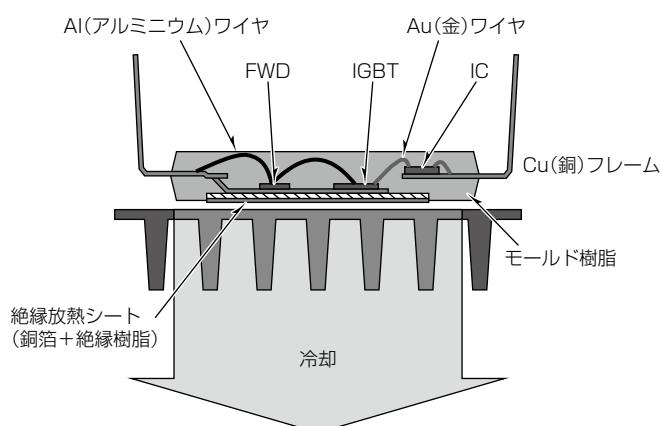

近年、環境負荷低減や低炭素社会への貢献が求められており、エアコンなどに代表される家電向けパワーモジュールは全世界的に更に普及が進むことが予想される。パワーモジュールに対しては小型化、低コスト化が求められており、三菱電機では、エアコン内部や室外機に使用される小型モータ向けにリフロー実装が可能なモジュールの開発を進めてきた。

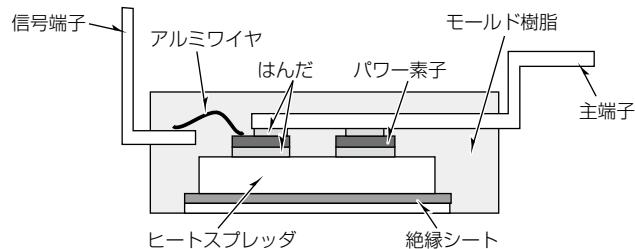

絶縁シートを使用した従来のトランスファーモールド型パワーモジュールでは、リフローによって基板に実装される他の部品とは別に、別工程で端子を挿入して実装する必要があったが、パワーモジュールもリフローによる表面実

装が可能になれば、他の実装部品と同時に基板実装が可能になる。

このたび、実装にリフローが使用できるパッケージ構造と、それに必要な高放熱封止樹脂を開発した。さらに、配線技術としてIC、パワーチップとリードフレームを結線する配線材料であるAu(金)、Al(アルミニウム)ワイヤに対する代替材として、パワーモジュールの使用に十分耐え得るAg(銀)ワイヤ技術を開発し、これらのパッケージ技術を、当社初の表面実装パッケージ型IPM(Intelligent Power Module)に適用して製品化した。

## 表面実装パッケージ型IPMのパッケージ技術

当社が開発した表面実装パッケージ型IPMと従来モジュール(絶縁シート構造)の比較を示す。開発したモジュールには表面実装に対応するため耐リフロー性を持つ高放熱封止樹脂によるフルモールド構造の適用と、チップとリードを結線する内部配線材全てにAgワイヤを採用した。

## 1. まえがき

近年、世界中で環境負荷低減や低炭素社会への貢献が求められ、産業機器、自動車、電鉄、家電の各産業、風力、太陽光などに代表される発電事業などパワーエレクトロニクス機器を代表するパワーモジュールの用途は多岐にわたり、社会全体の省エネルギー推進と、持続可能な循環型社会の形成に向け、更に普及が見込まれている。

また、パワーエレクトロニクス機器の高密度化が市場要求であり、パワーモジュールに対して高性能化、高機能化及び小型軽量化が期待される。特に、エアコン、冷蔵庫などに代表される民生用のパワーモジュールは、各家電メーカーでの取り扱いやすさ、コスト面でも重要視される<sup>(1)</sup>。

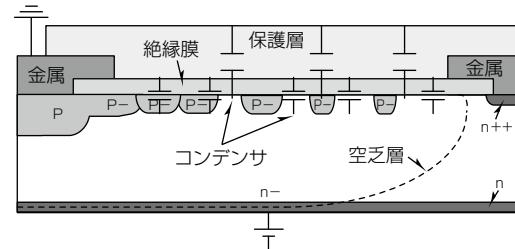

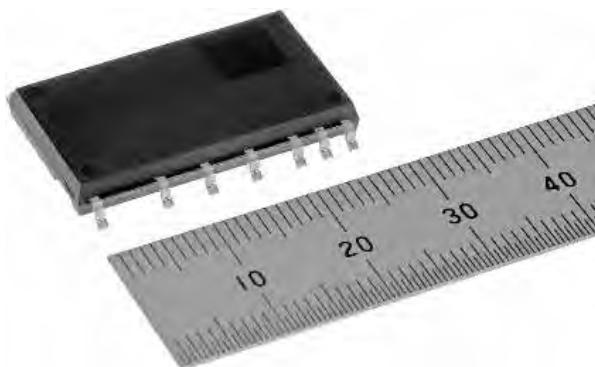

このような要求に対して、当社では、小容量(2~3A)の表面実装タイプの小型パワーモジュールを上市した(図1)。

従来の当社IPMである“DIPIPIM”では、基板に対して挿入型のモジュールであるため、リフローで実装する他の実装部品とは別工程で基板に端子を挿入してフローはんだ等で実装する必要があったが、小型、表面実装対応にすることで、他の搭載部品と同時に実装することが可能になった。

当社では、この製品のパッケージ開発に当たり、はじめてとなる耐リフロー性への対応と、IC、パワーチップとリードフレームを結線するAu、Alワイヤの代替材となるAgワイヤボンド技術を開発した。

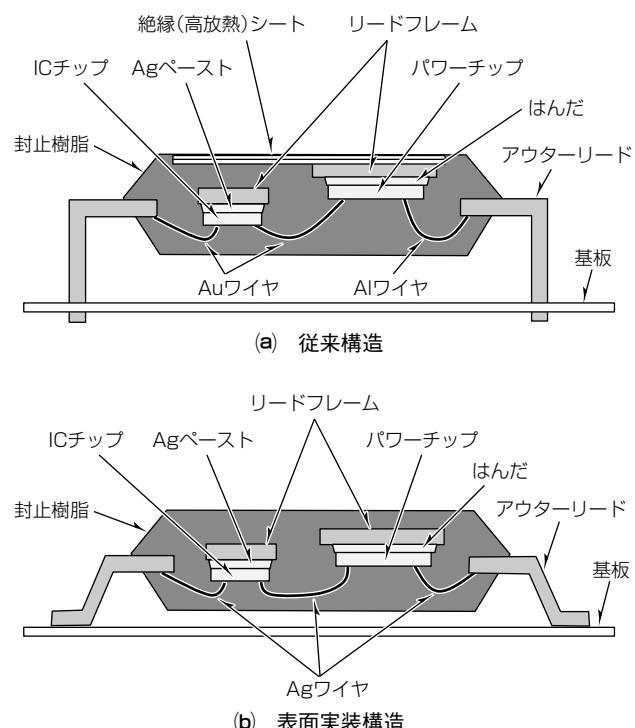

## 2. 表面実装パッケージの特長

当社では、超小型DIPIPIMで採用した高放熱の絶縁シートを使ったモジュール構造が主流である(図2(a))。従来構造の特徴として、パワーチップを載せたリードフレームの裏面に薄い(約0.2mm)絶縁層を持つ絶縁シートを配置し、パワーモジュールで重要な機能である放熱特性、絶縁性を絶縁シートが担っている。また、同じパッケージでもIGBT(Insulated Gate Bipolar Transistor)容量ごとに絶縁シートの放熱特性を変えることで、幅の広い容量帯のラインアップを増やせることが特長である。

今回、表面実装パッケージ型IPMの開発に当たり、実装での耐リフロー性に対して、絶縁シートのような薄い絶縁層では強度的にリフロー時に受ける熱ストレスに耐えられないことが予想されたため、構造の見直しを行った。

開発したパッケージ構造を図2(b)に示す。モジュール全体をトランスマルチモールドする構造をベースにして、耐リフロー性を持ち、環境、信頼性を配慮したハロゲン性難燃剤レスの高放熱タイプの封止樹脂を開発した。

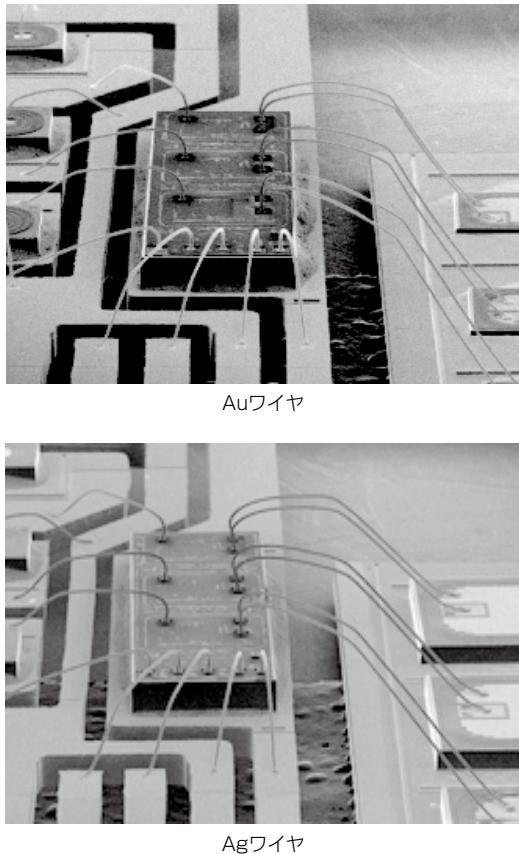

また、このパッケージを開発する中で、パッケージ内部

図1. 表面実装パッケージ型IPM

図2. トランスマルチモールド型パワーモジュール断面模式図

では、IC、パワーチップ-リードフレーム間を結線する配線材料であるAu、Alワイヤの代替材として全ての配線をAgワイヤに統一した。ワイヤの接合面積の縮小によるパワーチップの小型化、及びそれぞれのワイヤ材料に対応したワイヤボンド装置を、生産性の高い細線ワイヤボンド装置に統一できた。

## 3. パッケージ要素技術

表面実装パッケージ型IPMで採用したパッケージ要素技術である耐リフロー性を持つ高放熱封止樹脂の開発と、制御用ICの結線を行うAuワイヤと、パワーチップの結線を行うAlワイヤ代替材として、Agワイヤの適用について述べる。

### 3.1 耐リフロー性<sup>(2)</sup>

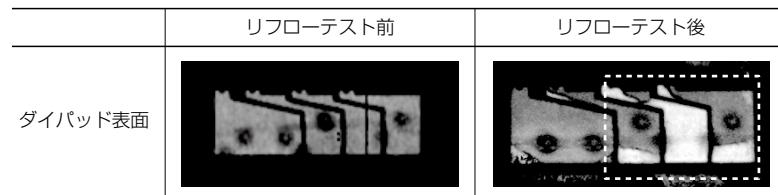

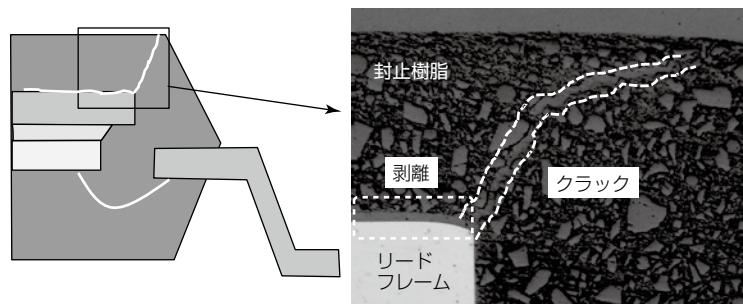

表面実装パッケージ型IPMに対する耐リフローについて述べる。表面実装パッケージを基板に実装する際にリフロー装置を使い実装するが、パッケージが長期に外気にさらされると水分を吸湿し、リフロー時に受ける熱ストレストレスによってパッケージクラックが発生することがある(ポップコーン現象)。図3に開発時に行ったリフロー前後のSAT(Scanning Acoustic Tomograph)画像とパッケージ表面に発生したクラックを示す。パッケージ表面に発生したクラックはリードフレームとモールド樹脂との剥離が起點となり進展することが確認された。

このようなリフローに対するパッケージの耐性を一般的に耐リフロー性と呼び、試験方法がJEDEC(半導体技術協会)によって決められている。耐リフロー試験の標準規格としてJEDEC規格J-STD-020に定められた温度プロファイルを用いた。また、評価条件についても、同様にJ-STD-020に定めたMSL(Moisture Sensitive Level)を参照し、評価サンプルを前処理として30°C/70%RH(Relative Humidity)に設定した恒温恒湿槽に規定の時間吸湿させた後に耐リフロー評価を実施した。耐リフロー用の封止樹脂は、リードフレームとの剥離及び吸湿に伴うリフロー時のクラックを抑制することが求められる。

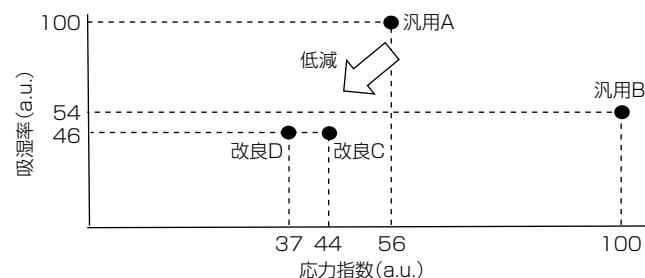

図4に今回の開発で評価した封止樹脂の吸湿特性-応力指数の特性相関図と表1に吸湿クラックの結果を示す。応力指数とは、封止樹脂の線膨張係数と弾性率を掛け合わせた独自の指標である。クラックを抑制するため樹脂の低弾性、低線膨張係数化による低応力化と低吸湿化を図るために、高熱伝導化とともに封止樹脂の改良を進めた。図4に示すように改良前の汎用樹脂Aの吸湿率を100とした際に改良樹脂C及びDの吸湿率は46まで低減した。

また、モールド樹脂のベースレジン変更やモールド樹脂中に含まれるフィラーの種類の変更、添加剤の調整によって改良することで、汎用樹脂Bの応力指数を100とした場合の改良樹脂Cの応力指数は44、改良樹脂Dの応力指数は37にまで低減できた。

これによって、汎用樹脂からの改良でダイパッドへの剥離が抑えられ耐リフロー性の高い表面実装パッケージ型IPMを開発できた。

### 3.2 細線(Ag)ワイヤ技術<sup>(3)</sup>

パワーモジュール内に搭載するICチップの結線に用いられるボンディングワイヤは導電性が良く、加工性に優れた金属であることが必要である。大気中での化学的な安定

図3. パッケージのポップコーン現象

図4. 耐リフロー性封止樹脂の改良相関図

表1. 改良封止樹脂と吸湿クラック結果

| 封止樹脂      | 汎用A   | 汎用B | 改良C | 改良D |

|-----------|-------|-----|-----|-----|

| 相対値(a.u.) | 吸湿率   | 100 | 54  | 46  |

|           | 応力指数  | 56  | 100 | 44  |

| 剥離率(%)    | ダイパッド | 87  | 24  | 0   |

性や、取り扱いやすさから従来素材としてAuが用いられてきた。しかし、元々高価な素材である上に、近年の価格高騰もあり、安価な材料への転換が求められてきた。代表的な代替材としてCu(銅)ワイヤがある。ICでは一般的に使われているが、ボンディングプロセス中に酸化を防止するため、水素と不活性ガスの混合雰囲気が必要であり、水素を用いる点で安全面での対策が必要であった。当社ではCuやAuと同程度の電気伝導率を持ち、酸化に耐性があるAgを代替材として検討した(表2)。

ただし、Agには酸化の耐性がある一方、空気中に放置されることで金属表面が硫化し、ボンディング時の接合性が悪化する懸念があった。この問題を解決するため、材料メーカーで、Ag材料に改良を加えてきた結果、大気放置による硫化の抑制と、不活性ガス雰囲気中でボール形成が可能なAgワイヤが開発された。素材のコスト面では、AgはCuと比較して高くなるが、細線への加工コストを含め

表2. Auワイヤ代替材相対比較

|              | Au | Ag    | Cu                   |

|--------------|----|-------|----------------------|

| 化学的安定性(表面変質) | ◎  | ○     | △                    |

| ボンディング性      | ○  | ○     | △                    |

| コスト(材料+加工)   | ×  | ○     | ○                    |

| ボール形成時雰囲気    | 大気 | 不活性ガス | 不活性ガス+H <sub>2</sub> |

図5. Au, Agワイヤループ性形状比較

た全体的なコストで見れば差は小さい。設備面では既存のワイヤボンド装置の改造で対応が可能であること、水素などの還元ガスが不要であることによって、安全面を含めてメリットが大きい。

図5に、同じチップリードフレームのレイアウトでのAuワイヤとAgワイヤのループ形状の比較を示す。ワイヤボンド装置によってワイヤ材質にかかわらず同様なループ形状を形成することが可能であり、レイアウトなど設計的な制約は従来のAuワイヤと同じであることが確認できた。

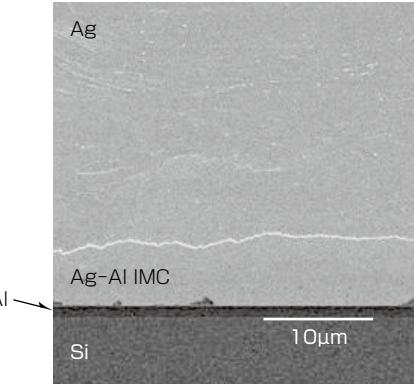

図6は、モジュールを高温保存(200°C/2,000hr)したAgワイヤボール-チップ接合部断面のSEM(Scanning Electron Microscope)写真である。AgワイヤボールとAlパッド間に、Ag-Alの金属間化合物(IMC)が形成されているが、高温保存によって発生する現象として知られ

図6. 高温保存後(200°C/2,000hr)のAg-Al金属間化合物断面

ている金属間化合物中にカーケンダール効果(Kirkendall effect)によるボイドの発生も見られず非常に良好な接合界面を保っていることが確認できた。

#### 4. む す び

小型・小容量のカテゴリーに対して従来の絶縁シートタイプのパワーモジュールから、フルモールドタイプに変更し、表面実装に対するJEDEC規格を満足するパッケージ構造を開発した。また、内部配線であるAu・Alワイヤに対して全てにAgワイヤを採用することで、ユーザーでの組立て工程の取り扱いやすさ、コスト面でも改善されたパワーモジュールを実現することができた。今後も、市場要求に応じたモジュール構造を実現するために材料及び製造プロセスを含めたパッケージング技術によって、次世代のパワーモジュールの開発を加速して省エネルギー化社会への貢献を目指していく。

#### 参 考 文 献

- (1) ゴーラブ マジュムダール, ほか:パワーモジュールの最新動向と展望, 三菱電機技報, 92, No.3, 158~162 (2018)

- (2) 原田啓行, ほか:パワーモジュールにおける表面実装パッケージング技術の開発, エレクトロニクスにおけるマイクロ接合・実装技術シンポジウム論文集, 25, 35~38 (2019)

- (3) 作谷和彦, ほか:トランスマルチモールド構造のモジュールへのAgワイヤ適用, エレクトロニクスにおけるマイクロ接合・実装技術シンポジウム論文集, 23, 35~38 (2017)

# パワーモジュールの性能向上を実現する配線技術開発の取組み

Wiring Technologies Development to Improve Power Module Performance

内田祥久\*

Yoshihisa Uchida

柳本辰則†

Tatsunori Yanagimoto

菊池正雄\*

Masao Kikuchi

## 要旨

活用分野が拡大しているパワーモジュールでは、高電流密度化、長寿命化などの性能改善が求められている。これらの要求を達成する上で、製品寿命やパッケージサイズを大きく左右する内部配線技術の開発が重要となる。

パワーモジュールの内部配線では、Al(アルミニウム)ワイヤを用いたワイヤボンディング法が一般的で、三菱電機の多くの製品にも適用されている。しかし、Alワイヤの接合部寿命が信頼性のボトルネックとなる場合や、ワイヤ接合に必要な面積を確保するために、パッケージ小型化の制約になる場合が多い。この課題に対して、当社では、外部端子をチップ上に直接はんだ接合することで、小型化と高信頼性を実現したDLB(Direct Lead Bonding)技術を開発し、製品展開してきた。

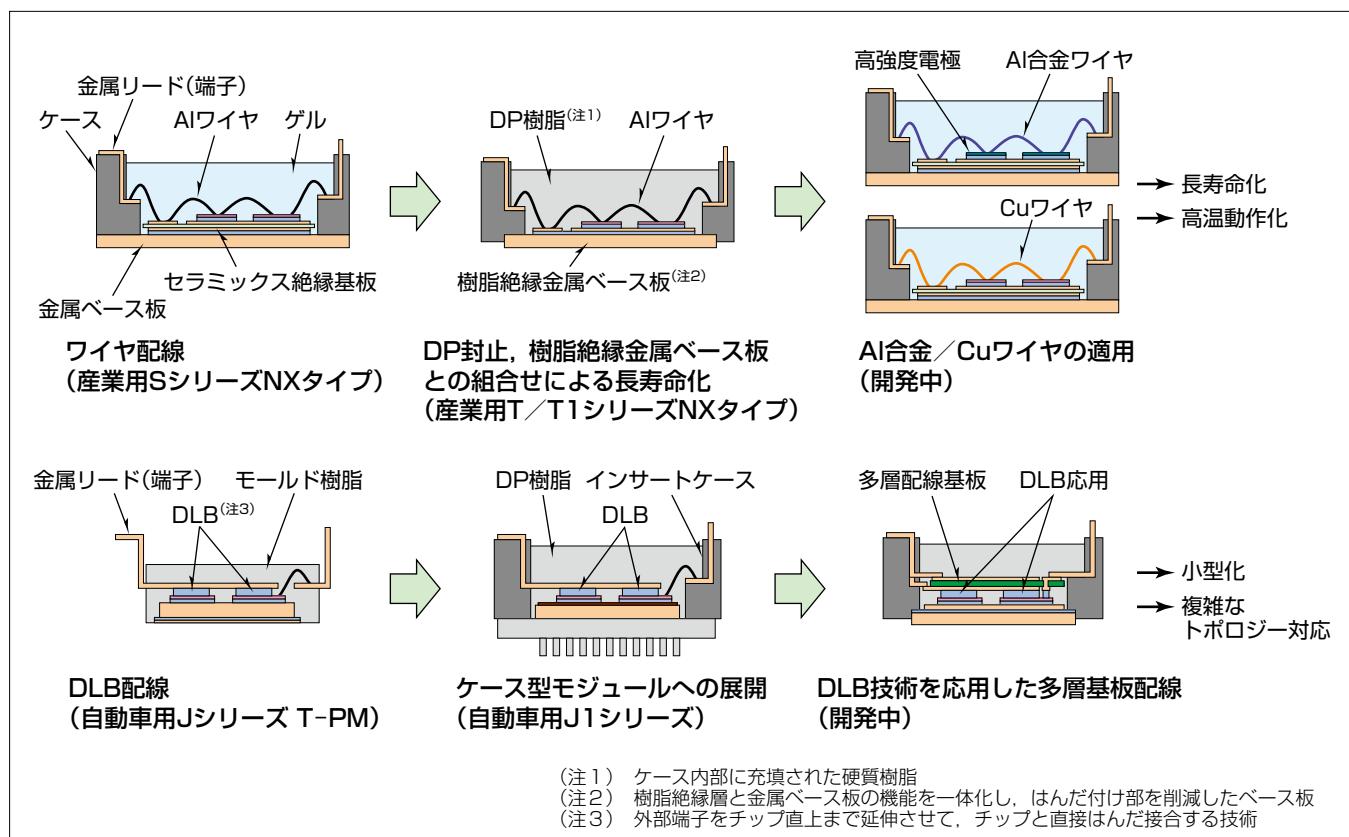

今後、厳しくなる市場要求を満たすために、これら配線技術の進化が必要となる。産業用“T/T1シリーズ”では、Alワイヤの剥離を加速させる放熱経路の劣化を抑制し、製品寿命を改善した。さらに、より高強度なAl合金ワイヤやCu(銅)ワイヤを用いることで、更なる長寿命化が可能なことを実証した。自動車用“J1シリーズ”では、トランスマルチモード型モジュールに適用していたDLB技術をケース型モジュールに適用し、小型・高信頼性の利点を別パッケージへ展開した。チップ上に多層配線基板を直接接合し、小型かつ複雑な配線にも対応するDLB技術を応用した新しい配線構造も検討中である。

当社は、高電流密度化、長寿命化などを狙いとした配線技術開発を継続し、市場の要求に応える製品を提供していく。

## パワーモジュールの内部配線技術トレンド

産業用T/T1シリーズNXタイプでは、DP(Direct Potting)樹脂封止と樹脂絶縁金属ベース板との組合せによって、従来のAIワイヤのまま製品寿命を向上させた。自動車用J1シリーズでは、トランスマルチモード型モジュールで適用していたDLB技術をケース型モジュールに展開した。さらに、AI合金/Cuワイヤ適用による長寿命化、DLB技術を応用して多層配線基板をチップ上に接合することで、更なる小型化や複雑なトポロジーに対応した配線技術を開発中である。

## 1. まえがき

パワーエレクトロニクス分野で、省エネルギー・環境保護の観点から、家電製品を始め、産業機器・自動車・鉄道車両など、パワーモジュールの活用分野が拡大している。パワーモジュールでは、用途に応じて高電流密度化、長寿命化などの性能改善が求められるが、それらの要求に対応するためには、電流密度や製品寿命、パッケージサイズを左右する内部配線技術の開発が重要になる。

パワーモジュールでの代表的な内部配線材料を表1に示す。従来、Alワイヤを用いたワイヤボンディング法が一般的であったが、電流密度・接合部寿命の向上を目的に、Al合金ワイヤや、Cuワイヤの適用が本格化しつつある。さらに、チップ上に端子を直接はんだ付けするDLB構造の適用が拡大している。

本稿では、これらの内部配線技術を中心にしたパッケージング技術について述べる。

## 2. ワイヤボンディング技術

パワーモジュールの内部配線では、Alを主材料とした直径200~500μmの金属ワイヤの両端を超音波接合するワイヤボンディング法が一般的である。この手法は、配線自由度が高い一方で、製品寿命がワイヤ接合部のリフトオフ寿命によって決定される場合が多い。リフトオフとは、ワイヤとチップの線膨張係数差に起因した応力によってワイヤ接合部に亀裂が進展し、最終的にワイヤが剥離する現象である。この課題に対して、モジュール構造の適正化や、ワイヤ材の変更による方策を検討してきた。

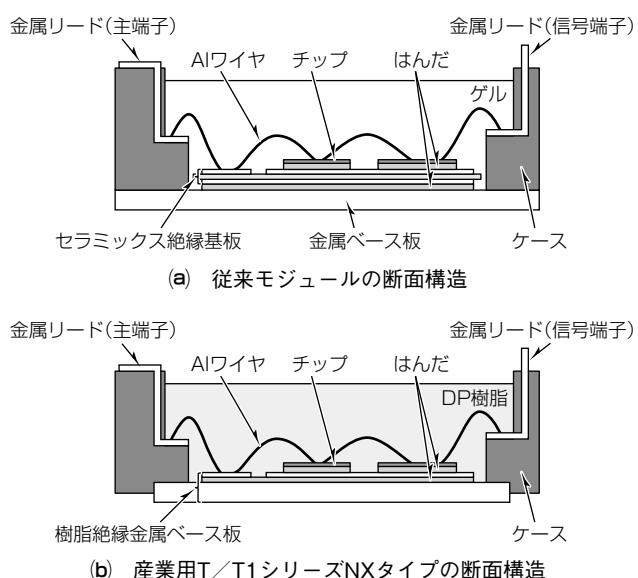

### 2.1 Alワイヤ

図1に示す従来構造のパワーモジュールで、ワイヤ接合部のリフトオフ寿命は、放熱経路の劣化による影響が大きい。主な発熱体であるチップで発生した熱は、金属ベース板裏面に取り付けられた冷却フィンへ放熱される。このとき、チップ/絶縁基板間及び絶縁基板/金属ベース板間のはんだ層が劣化すると、放熱性能が悪化してワイヤ接合部がより高温に晒(さら)され、リフトオフを加速させる。

そのため、第7世代IGBT(Insulated Gate Bipolar Transistor)モジュール“T/T1シリーズNXタイプ”では、金属ベース板上に高放熱性の樹脂絶縁層と配線パターンを一体化した樹脂絶縁金属ベース板を採用することで、信頼性への影響因子の一つである絶縁基板/金属ベース板間のはんだ接合部を取り除いた<sup>(1)</sup>。さらに、封止方法を従来のゲル封止から、硬質エポキシ樹脂を用いたDP樹脂封止に変

更することで、チップ/樹脂絶縁金属ベース板間のはんだ層に生じるひずみを低減させた。表2は、温度サイクル試験(85~175°C)で、従来のゲルと、DP樹脂で封止したサンプルのチップ/樹脂絶縁Cuベース板間のはんだ層の劣化状態を比較した結果である。DP樹脂封止サンプルでは、応力分散効果によって、はんだ層の剥離を大幅に改善できていることが確認できる。

このように、ワイヤ以外の構成部材やパッケージ構造を適正化することで、ワイヤ接合部寿命を低減させる放熱経路の劣化を抑制し、安価で汎用性の高い従来のAlワイヤを使用したまま長寿命化を実現できた。

表1. パワーモジュール内部配線材料

| 配線材料 | Alワイヤ              | Al合金ワイヤ                     | Cuワイヤ                             | Cu端子             |

|------|--------------------|-----------------------------|-----------------------------------|------------------|

| 構造   | AIワイヤ<br>電極<br>チップ | AI合金ワイヤ<br>高強度<br>電極<br>チップ | Cuワイヤ<br>厚膜めっき又は<br>電極+緩衝板<br>チップ | はんだ<br>端子<br>チップ |

| 接合方法 | ワイヤ<br>ボンディング      | ワイヤ<br>ボンディング               | ワイヤ<br>ボンディング                     | はんだ接合<br>(DLB)   |

| 電流密度 | Ref.               | AIワイヤ同等                     | +                                 | ++               |

| 接合寿命 | Ref.               | +                           | ++                                | ++               |

+ : 性能改善の大きさを示す

図1. モジュール断面構造

表2. 温度サイクル前後のチップ下はんだ層超音波探傷画像

|        | 初期 | 5kサイクル | 15kサイクル | 50kサイクル |

|--------|----|--------|---------|---------|

| ゲル封止   |    |        |         |         |

| DP樹脂封止 |    |        |         |         |

## 2.2 Al合金ワイヤ

Alワイヤに意図的に異種金属を微量添加し、ワイヤ材を高強度化することで、ワイヤ接合部の亀裂進展を抑制し、寿命改善を図ったAl合金ワイヤを開発している。

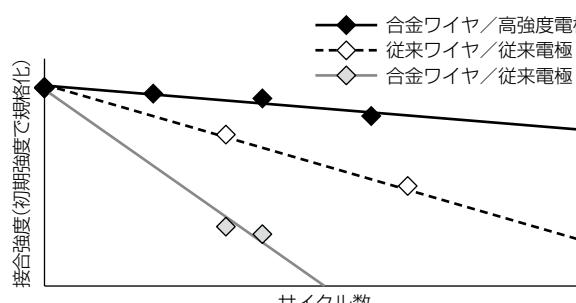

従来電極、めっき処理を施した高強度電極上に、従来のAlワイヤとAl合金ワイヤをそれぞれワイヤボンドしたサンプルで、温度サイクル試験(50~150°C)後の接合強度の低下率を比較した結果を図2に示す。従来電極上にAlワイヤを接合した従来構造に対して、ワイヤ材をAl合金ワイヤに変更しただけでは、接合寿命の改善がみられないが、電極材も高強度電極にすることで大幅にワイヤ接合部寿命を改善できることを実証できた。図3に示す温度サイクル試験後の接合部断面画像から、従来電極上にAl合金ワイヤを接合したサンプルは、電極部にひずみが集中したことによって、選択的に亀裂が進展している。一方、電極も高強度材料に変更することで、ワイヤ側に亀裂進展位置が変わり、合金化によるワイヤ材の高強度化の効果が発揮され、接合部寿命の改善が可能なことを確認できた。

## 2.3 Cuワイヤ

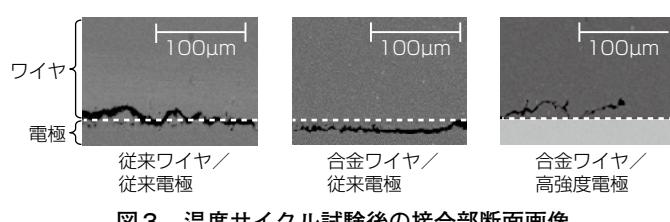

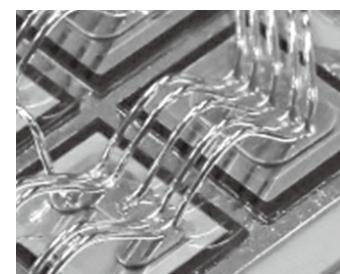

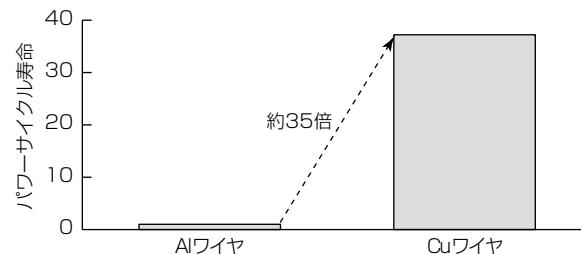

Alワイヤと比較して、Cuワイヤの再結晶温度は高く、チップとの線膨張係数差も小さいため、大幅な寿命改善が期待できる<sup>(2)</sup>。寿命改善効果の確認のため、従来構造のモジュールを用いて、AlワイヤとCuワイヤ配線でパワーサイクル寿命を比較した。図4にCuワイヤボンディング完了後のサンプル外観写真、図5にパワーサイクル試験結果を示す。Cuワイヤ配線したサンプルは、約35倍の寿命になり、大幅な寿命向上を確認できた。なお、このサンプルは、チップ接合部の劣化抑制のために、Ag(銀)焼結接合

図2. Al合金ワイヤの温度サイクル試験結果

図3. 温度サイクル試験後の接合部断面画像

図4. Cuワイヤボンディング完了後のサンプル外観写真

図5. Cuワイヤサンプルのパワーサイクル試験結果

を採用している<sup>(3)</sup>。

CuワイヤはAlワイヤと比較して硬く、接合に大きなエネルギーを要する。接合時にチップの素子構造が破壊されないように、チップ電極に厚膜めっきを施す方法や、電極上に緩衝板を搭載する方法が提案されている<sup>(2)</sup>。Cuワイヤを用いて製品寿命を改善する場合、Cuワイヤの延命効果を活用するためには、パッケージ構造の最適化が必要になる。

## 3. Direct Lead Bond技術

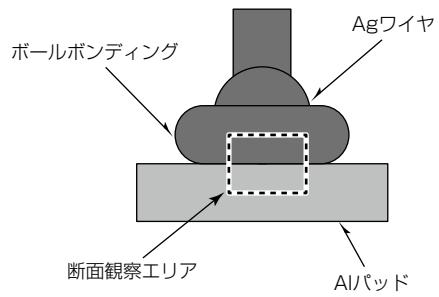

当社では、図6に示すように、外部端子をチップ直上で延伸させ、チップ表面に直接はんだ付けするDLB技術を開発し<sup>(4)</sup>、自動車用“JシリーズT-PM(Transfer-molded Power Module)”に適用して2011年にリリースした。

DLB構造によって、主配線にワイヤボンドが不要となるため、ワイヤボンドに必要なスペースを削減でき、パッケージの小型化に有利となる。また、ワイヤと比較して大面积で接合できるため、配線の大電流化が期待できる。さらに、モールド封止による応力分散効果によってはんだ接合部のひずみを低減でき、長寿命化も可能になる。

### 3.1 ケース型モジュールへの展開

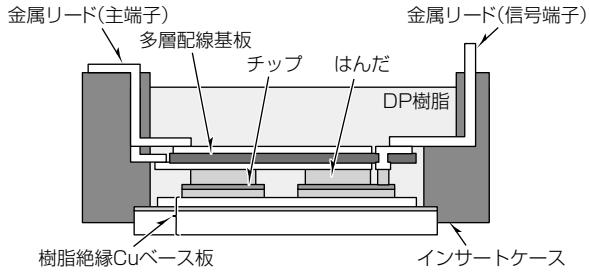

図7に断面構造を示す自動車用J1シリーズでは、DP樹脂封止技術との組合せによって、ケース型モジュールにDLB構造を適用した。これによって、より大型のモジュールでもDLBのメリットを活用した小型・高出力のモジュールの供給が可能になった。

大型のインサートケースタイプモジュールでDLB構造

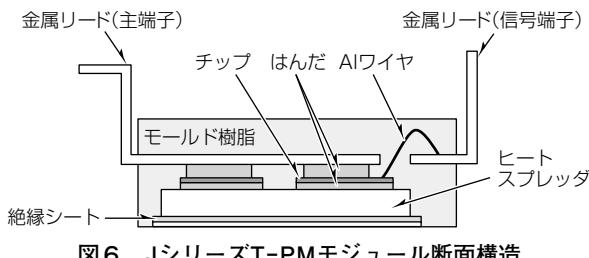

図6. JシリーズT-PMモジュール断面構造

図7. J1シリーズモジュール断面構造

を適用するとき、端子を把持しているケースから端子先端までの距離が長くなるため、チップと端子のギャップの制御が課題になった。この課題に対する方策の一つとして、表3に示すように、端子のはんだ接合部に貫通穴を設けた。ギャップが小さくなった場合、余剰はんだを貫通穴に逃がすことで、電極外周へのはんだのはみ出しを防止できる。ギャップが大きくなった場合は、貫通穴直下のはんだが凹(へこ)むことでチップ電極外周まではんだが濡(ぬ)れ広がり、所望のはんだ付け面積が確保できる。このケース型モジュールでのDLB技術を他分野の製品にも適用し、より小型・長寿命なモジュールを展開する。

### 3.2 DLB技術を応用した多層基板配線構造

これまでCuリードを用いて二次元的に配線していたDLB技術を発展させ、図8、図9に示すような、大電流に耐え得る多層配線基板をチップ上に直接はんだ付けする配線構造を開発中である。絶縁層の上下に配線パターンを重ねて設計した基板は、信号配線も含めて上下2層で配線できるようになる。これによって、モジュールの更なる小型化と、電気的特性の最適化が可能になる。基板上下配線パターン間の相互インダクタンスを利用した寄生インダクタンスの低減や、配線長の調整によるチップ間の分流やスイッチングタイミングの適正化が容易になることを確認済みである。

このように、多層配線基板を用いることで、モジュールの小型化に加えて、電気的特性の最適化や、将来的な複雑なトポロジーへの対応が期待できる。

表3. 電極貫通穴の効果を示す模式図

|       | 貫通穴なし | 貫通穴あり |

|-------|-------|-------|

| ギャップ小 |       |       |

| はみ出し  |       |       |

| ギャップ大 |       |       |

| はんだ不足 |       |       |

図8. 多層配線基板を用いた試作モジュールの外観写真

図9. DLB技術を応用した多層基板配線構造

## 4. む す び

当社は、高電流密度化、長寿命化などを目的とした次のような配線技術の開発を継続し、市場要求に応える製品を提供していく。

- (1) ワイヤボンディングへの新素材の適用と電極構造とのマッチングによる長寿命化

- (2) ケース型モジュールに対応したDLB技術の他製品群への展開による小型・長寿命化

- (3) DLB技術を応用した多層基板配線構造による小型化、特性向上、複雑なトポロジー対応

## 参 考 文 献

- (1) 浅田晋助, ほか: 産業用高信頼性パッケージ技術, 三菱電機技報, 90, No.5, 291~294 (2016)

- (2) 内田祥久, ほか: パワーモジュールにおけるCuワイヤを用いた高耐久接合構造の検討, エレクトロニクスにおけるマイクロ接合・実装技術シンポジウム論文集, 24, 91~94 (2018)

- (3) 中原賢太, ほか: 高温動作パッケージ構造, 三菱電機技報, 92, No.3, 167~170 (2018)

- (4) Ueda, T., et al.: Simple, Compact, Robust and High-performance Power module T-PM(Transfer-molded Power Module), Proc. of The 22nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 37~40 (2010)

## 自動車用パワーモジュール“J1シリーズ”

Automotive Power Module "J1 Series"

飯塚 新\*

Arata Iizuka

猪ノ口誠一郎\*

Seiichiro Inokuchi

波多江慎治\*

Shinji Hatae

## 要旨

近年、自動車排ガス規制強化や環境保全に対する意識の高まりなどによってxEVが市場へ浸透してきた。環境保全を担うxEVは今やスマートグリッドや自国産業活性化策など各国それぞれの視点で広がりを見せており。このように、xEVの将来的な市場拡大に伴い自動車のモータ駆動用や発電用のインバータに用いられるパワーモジュールの広がりもこの先加速していくことが期待される。

三菱電機は1997年からパワーモジュールの内部に制御回路を搭載した自動車用IPM(Intelligent Power Module)の製品化を皮切りに、2001年には小型・高信頼性を特長とするトランスファーモールドタイプの“Jシリーズ”を市

場投入し、xEV発展に貢献してきた。また、2015年には最新世代の自動車用パワーモジュールとしてフィン一体型タイプの“J1シリーズ”の量産を開始しており、生産規模を順次拡大する計画である。この製品は“小型・軽量・高性能”パッケージとして自動車用途に最適なことから、J1シリーズの構造をベースに対応するモータ出力定格を向上させた“大容量J1シリーズ”も製品化し、2017年から量産を開始している。

更なるxEVの本格化に備え、小型・高性能パワーモジュールの実現のため、自動車向けに特化した高信頼性・低熱抵抗パッケージ開発を推進している。

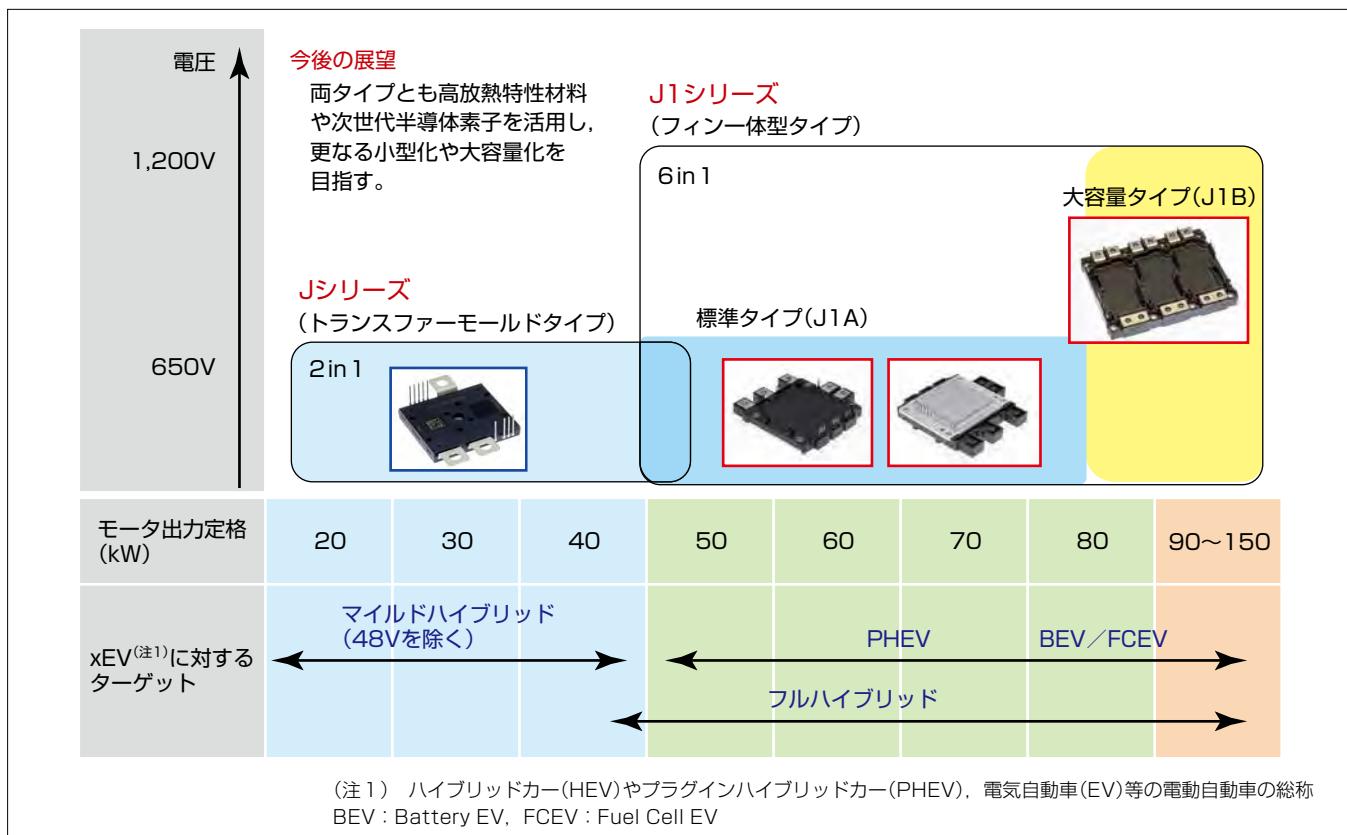

## 自動車用パワーモジュールのラインアップと今後の展望

小型・低背で信頼性も高いトランスファーモールドタイプと、小型・大容量のフィン一体型タイプを展開することで幅広いモータ出力定格をカバーしてきた。両タイプとも更なる小型化や大容量化を目指し、ラインアップを拡充するために新製品の開発を進めていく。

## 1. まえがき

近年、自動車排ガス規制強化や環境保全に対する意識の高まりなどによってxEVが市場へ浸透してきた。環境保全を担うxEVは今やスマートグリッドや自国産業活性化策など各国それぞれの視点で広がりを見せており、CO<sub>2</sub>削減だけでなく災害時の給電設備といった新たな価値としての需要も生まれている。

このようなxEVの将来的な市場拡大に伴い、自動車のモータ駆動用や発電用のインバータに用いられるパワーモジュールの広がりもこの先加速していくことが期待される。

当社は1997年に自動車用パワーモジュールを量産化して以来、様々な製品を世に送り出してきた。

## 2. 自動車用パワーモジュールのラインアップ

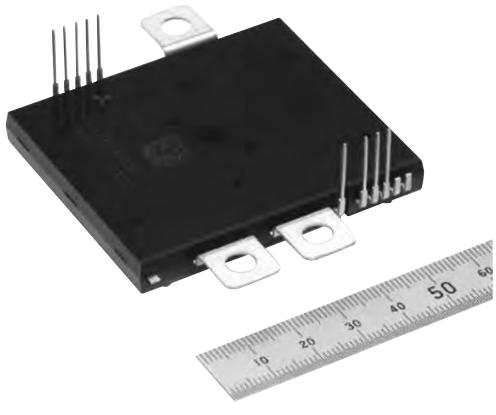

### 2.1 トランスファーモールドタイプのJシリーズ

小型、低背、高信頼性のニーズに応えるための製品がトランスファーモールドタイプのJシリーズである(図1)。トランスファーモールド構造を採用してチップと樹脂の線膨張係数のマッチングを図ることで温度サイクル性を格段に向上させている。また、モールド樹脂で封止する構造によって機械的構造と強度、絶縁性、環境耐久性を一度に確保している。さらにパワー素子との電気的接続をワイヤボンディングからDLB(Direct Lead Bonding)にすることでパワーサイクルの長寿命化のほか、配線抵抗と自己インダクタンスの低減を達成した。また、Jシリーズはパワー素子の下にヒートスプレッダを配置しており、その下面にはモールド封止樹脂よりも熱伝導率の高い絶縁シートを配置している。パワー素子で発生した熱を厚いヒートスプレッダで広げた後に絶縁シートを通過させる構造にすることで、低熱抵抗に加えて自動車アプリケーションで重要な過渡熱

図1. Jシリーズの外観

抵抗を低減できる構造にしている(図2)。また、Jシリーズは2 in 1構成にしているため、ディスクリートデバイスのようにアプリケーションに応じて出力を増やすことなどフレキシブルに回路を構成できる特長を持つ。

### 2.2 フィン一体型タイプのJ1シリーズ<sup>(1)(2)(3)(4)</sup>

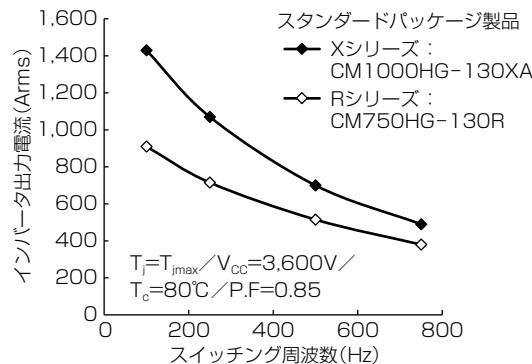

xEV市場の拡大に伴い、車載用パワーモジュールに対して小型化に加えて実装性向上のための6 in 1化や、モータ出力定格アップのための大容量化のニーズが高くなってきた。

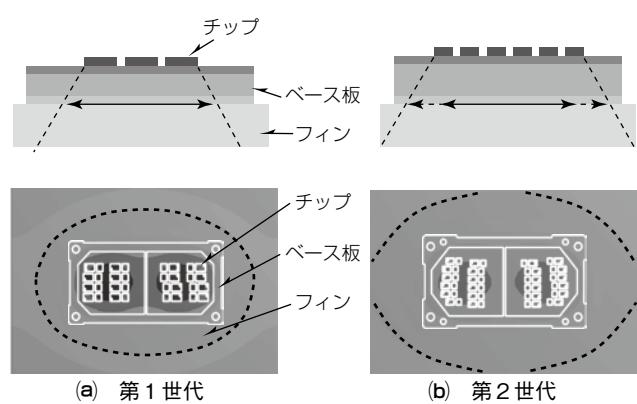

そのようなニーズに応えるために開発した製品がフィン一体型タイプのJ1シリーズである(図3)。Al(アルミニウム)製冷却フィンとケースタイプモジュールを一体化することによって放熱層の削減に加えて絶縁基板下はんだ層を削減することで、低熱抵抗化と小型化、温度サイクル性向上を果たしている。

さらに独自の第7世代IGBT(Insulated Gate Bipolar Transistor)とダイオードを適用し、Jシリーズで培ったDLBを採用することで更なる小型・高信頼性を実現しながらも、大容量化を達成した。

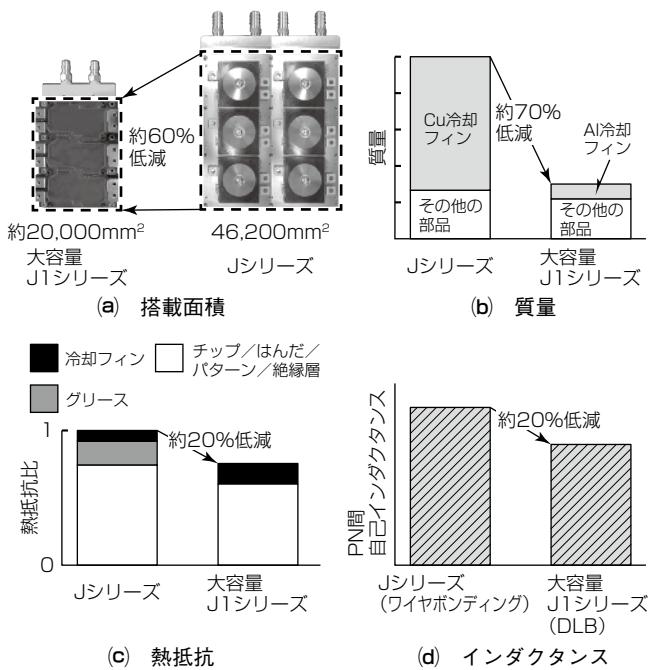

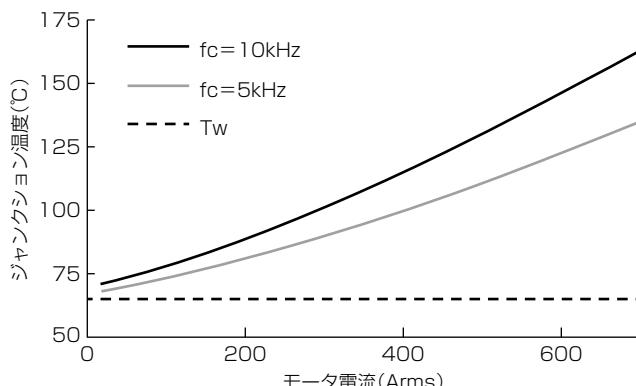

また、DLB等の内部配線の最適化を進めることで“J1シリーズ”から出力容量をおよそ2倍にしながらサイズを約1.5倍に抑えた大容量J1シリーズも開発しており、これらのパッケージをベースにしたラインアップ拡充を進めている(表1、図4、図5)。

図2. Jシリーズの構造

図3. J1シリーズの構造

表1. J1シリーズのラインアップ

|               | モデル           | 定格          | パッケージ仕様                                         |

|---------------|---------------|-------------|-------------------------------------------------|

| J1シリーズ        | CT600CJ1A060  | 600A/650V   | 120.0×115.2×32.5(mm)<br>(ピンフィン・制御端子含む、6 in 1構造) |

|               | CT700CJ1A060  | 700A/650V   |                                                 |

| 大容量<br>J1シリーズ | CT1000CJ1B060 | 1,000A/650V | 163.0×124.5×33.6(mm)<br>(ピンフィン・制御端子含む、6 in 1構造) |

|               | CT600CJ1B120  | 600A/1,200V |                                                 |

図4. J1シリーズ

図5. 大容量J1シリーズ

### 3. J1シリーズ<sup>(1)(3)</sup>

#### 3.1 構 造

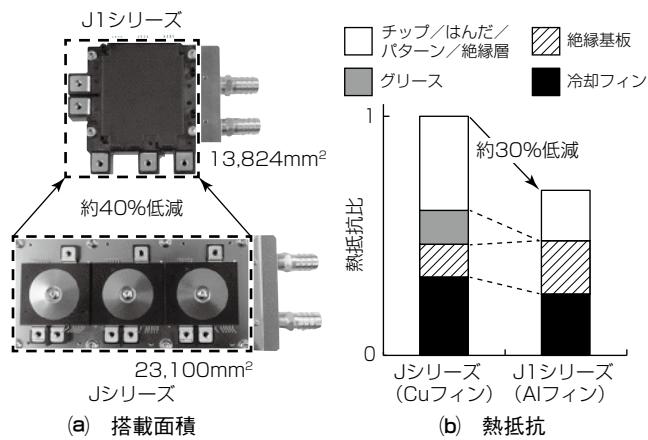

J1シリーズは先に述べたDLBやフィン一体型の採用等によって小型化と高出力化の両立を果たしており、従来の同等出力のJシリーズと比較した場合で搭載面積は約40%、熱抵抗は約30%低減を達成している(図6)。大容量J1シリーズでは内部配線構造の最適化も取り入れることで搭載面積を従来製品の約60%低減し、質量は約70%、熱抵抗及びインダクタンスも約20%低減している(図7)。

#### 3.2 出 力 特 性

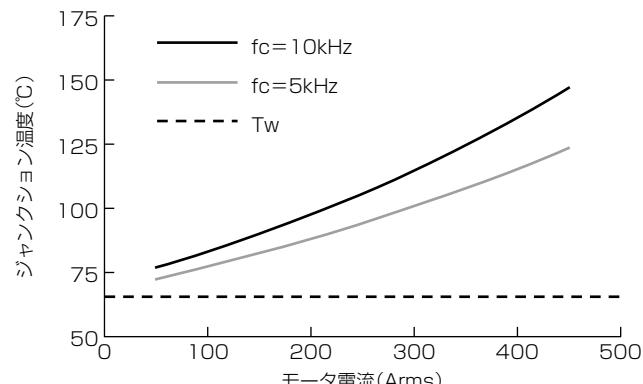

J1シリーズは当社第7世代の“CSTBT”とRFC(Relaxed Field of Cathode)ダイオードを採用することで損失特性の改善を図り、DLBの採用や配線経路の最適化を行うことでインダクタンスも抑制している。これらの効果によって、インバータ動作を想定した通電シミュレーションで

図6. JシリーズとJ1シリーズの比較

図7. Jシリーズと大容量J1シリーズの比較

製品：CT600CJ1A060、バッテリー電圧：350V、冷却水温度：65°C、冷却水流量：10L/min.

図8. J1シリーズの通電シミュレーション

J1シリーズはジャンクション温度150°C以下で450Armsの通電能力(モータ出力定格80kW相当)を(図8)、大容量

図9. 大容量J1シリーズの通電シミュレーション

J1シリーズでは600Arms(モータ出力定格120kW相当)の通電能力を実現している(図9)。

## 4. 自動車用パワーモジュールの将来技術

### 4.1 今後の展望

xEVの市場拡大に伴い、様々なニーズに応じるために多様な開発が進められている。コントロールユニットの小型化や走行モータのインホイール化、トランスマッショントransmissionとインバータの一体化等によるキャビンスペースの拡大などはパワーモジュールの更なる高出力化・小型化の要求につながる。

ユニットの小型化についてはフィン一体型タイプで、インホイール化やトランスマッショントransmission一体化といった水冷が困難で搭載エリアの制限や振動等の信頼性要求が厳しいニーズに対しては小型・低背なトランスマッショントransmissionタイプも選択肢の一つとして開発を進めている。また、パワー素子でも、損失特性の大幅な改善が期待されるSiC(シリコンカーバイド)や、インバータの小型化が期待できるRC-IGBT(Reverse Conductive IGBT)の自動車分野への展開も進めていく(図10)。

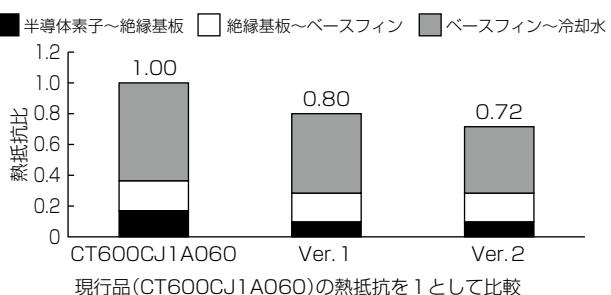

### 4.2 フィン一体型タイプでの低熱抵抗化<sup>(2)(4)</sup>

フィン一体型タイプでの開発のアプローチの一つとして、モジュールの熱抵抗低減による更なる小型化や大容量化を検討している。

J1シリーズのパッケージをベースに、モジュール内部の回路パターンや冷却フィンの材料をより放熱性能の高いものにすることで、現行製品から20~30%の熱抵抗の改善を確認している(図11)。

- ◎トランスマッショントransmission構造での狙い

- ・小型・低背構造を突き詰め、搭載制限の厳しいニーズへ応える。

- ・モールド構造による高信頼性を活用し、過酷な使用環境下でも提案可能にする。

- ・現行のサイズを維持したまま定格の向上。

- ◎フィン一体型構造での狙い

- ・直接水冷による高放熱性を活用した更なる小型化・高出力化。

- ・電極配置の最適化による取付け性の向上。

図10. 今後のパワーモジュールのターゲット

図11. 現行品と開発品の熱抵抗比較

## 5. むすび

当社は、20年来のxEVの発展とともに様々な自動車用パワーモジュールを開発・製品化してきた。これから先の市場の発展・要求に応えるためにも、当社は更なる損失低減、小型軽量化、信頼性向上等パワーデバイスの進化のための要素技術開発と自動車用SiCや第8世代の素子開発も行い、これらを組み合わせた高性能パワーモジュールをタイミングリードでxEV市場へ提供していくことで、環境保全や持続可能社会の実現に貢献していく。

### 参考文献

- (1) Iizuka, A., et al. : A new Versatile Compact Power Module Family for EV and HEV Applications, PCIM ASIA 2016 (2016)

- (2) Kawase, T., et al. : J1-Series modules with integrated cooler for electric and hybrid vehicles, PCIM Europe 2017, 1767~1770 (2017)

- (3) 猪ノ口誠一郎：自動車用パワーモジュールの開発動向、三菱電機技報、92, No.3, 199~202 (2018)

- (4) Miyamoto, N., et al. : Prototype of high heat dissipation J1-Series modules for electric and hybrid vehicles, ISSAP 2019 (2019)

## 第2世代SiC-MOSFETモジュール

2nd Generation SiC-MOSFET Module

宮崎裕二\*

Yuji Miyazaki

北林拓也\*

Takuya Kitabayashi

清水康貴\*

Yasutaka Shimizu

宇田達也\*

Tatsuya Uda

### 要旨

電力変換システムの省エネルギー及び小型化が重要性を増す中、従来のSi(シリコン)に比べ優れた材料特性を持つSiC(シリコンカーバイド)は、今後の更なる展開が期待できる半導体材料である。三菱電機はこれまで培ってきたSiCデバイス技術を使い、2010年にモジュール製品への応用に着手した。2014年にはSiCモジュールとして第1世代となるMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)モジュール、及びSi-IGBT(Insulated Gate Bipolar Transistor)とSiC-SBD(Schottky Barrier Diode)を組み合わせたハイブリッドモジュールなど、パワーエレクトロニクス機器の省エネルギーに貢献する製品をリリースし、鉄道用補助電源、空調機器、太陽光発電用パワーコンディショナ、無停電電源(UPS)、医療用X

線CT(Computed Tomography)／MRI(Magnetic Resonance Imaging)など幅広い産業分野で応用されている。

それらに替わる製品として、パワーエレクトロニクス機器の高周波化を高いレベルで実現する次のような特長を持った1,200V系第2世代SiC-MOSFETモジュールを開発した。

- (1) 第2世代高集積プレーナゲートMOSFETデバイス技術によって低いオン電圧を実現し、低損失化に貢献

- (2) 帰還容量特性の改善やゲートしきい値の引上げなど高速スイッチング性能を重視した設計

- (3) 従来品“第1世代MOSFETモジュール”との外形互換性を維持したまま、フィンの放熱効率を改善可能な放熱構造を採用して冷却機器の簡略化に貢献

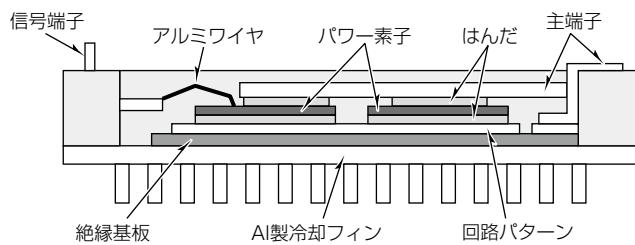

### 第2世代SiC-MOSFETモジュール

4種類の第2世代SiC-MOSFETモジュールの外観を示す。高速スイッチングとの親和性を重視した設計と先進的な低損失SiCデバイス技術の組合せによって、パワーエレクトロニクス機器の動作高周波化を可能にする。システムのダウンサイジング及び軽量化、トータルコスト削減など、多くのメリットを引き出すポテンシャルを持っている。

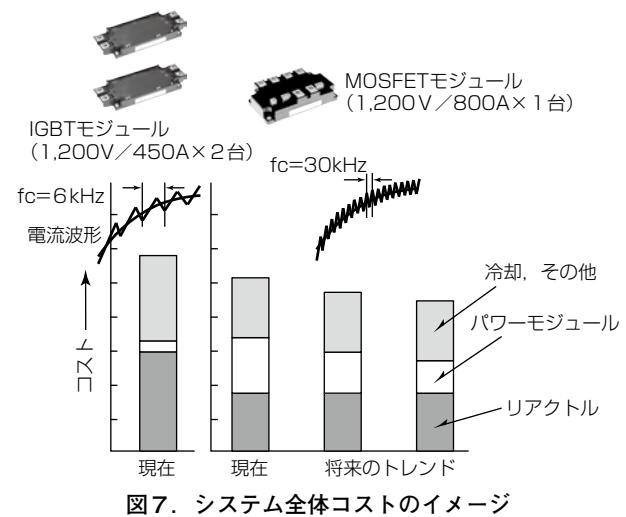

## 1. まえがき

パワーエレクトロニクス機器では、絶縁及び電力変換を目的としたトランジスタ、非絶縁の昇圧回路を構成する直流リニアクトル、高調波の抑制を目的とした交流リニアクトルやフィルタ回路など、受動部品であるリニアクトルの併用が多い。一般にこれらは体積と質量が大きいため、システムの多くの部分を占有し、また大容量システムになるほど顕著になっているので、パワーエレクトロニクス機器の更なる小型・軽量化及び低コスト化を阻む要因の一つになっている。この問題の解決方法として、機器の動作高周波化がある。パワーモジュールのスイッチング周波数を高くすることで、磁気飽和の問題を軽減でき、又はより小さいインダクタンス値の部品を選定できることから、リニアクトル部品の簡略化が可能である。これによって機器の小型・低コスト化はもとより、従来外付けであったリニアクトル部品の機器への内蔵やフィルタの高性能化など新しい付加価値の提供も可能になる。第2世代SiC-MOSFETモジュール(以下“第2世代MOSFETモジュール”という。)は、このような市場ニーズを捉え、パワーエレクトロニクス機器の高周波化を高いレベルで実現するため、低損失と高速スイッチング性能を追求した製品になっている。

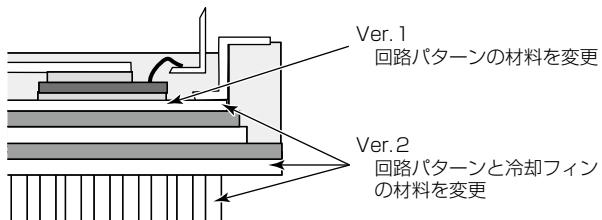

## 2. チップの高性能化

### 2.1 低損失設計

第2世代MOSFETモジュールに搭載したMOSFETチップでは、ユニットセルを更に高密度化するとともに、pウェルを浅くし、JFET領域への高濃度ドーピングによって導通時の電圧降下を抑えた(図1)。さらに基板部分の厚みを従来のおよそ1/3にして、オン抵抗は1,200V/800A定格品で2.4mΩ( $T_j = 150^\circ\text{C}$ ,  $V_{gs} = 15\text{V}$ )と、第1世代に

比べて約15%改善した。また、ウェーハ径6インチの製造プロセスによって、従来の4インチ製造プロセスに対して製造効率と品質の向上を狙った。

### 2.2 高速スイッチング設計

パワーエレクトロニクス機器の高周波化に対応するため、高速スイッチングとの親和性を重視したチップ設計にした。図2に、第1世代と第2世代の特性比較を示す。JFET領域幅と濃度を最適化することで空乏層の分布を制御し、帰還容量特性を改善した。スイッチング過渡期のドレイン・ソース間電圧(数十から数百ボルト)で急激に帰還容量が小さくなるため、スイッチングスピードをより向上させた。また、ゲートしきい値電圧については、小さくすると低いオン抵抗が得られる一方で、 $dv/dt$ による誤動作(ゲート誤オン)が発生しやすくなる。反対に大きくするとターンオフスイッチング損失が増加し、高速スイッチング性が失われるという関係がある。第2世代MOSFETではゲートしきい値電圧を2.3V(代表値)に調整することで低いオン抵抗と高速スイッチング性能を両立させた。

### 2.3 特性の安定性

MOSFETのpウェルとn-ドリフト層間の接合で形成される寄生のボディダイオードが導通すると、SiC単結晶基板の基底面にあらかじめ存在する転位欠陥を起点に欠陥が次第に拡張し、オン電圧を増加させるなど特性の安定性に影響することが一般に知られている。産業応用は多様な用途があり、広い使用条件に対応するには、MOSFETとは逆並列にSBDを設け、ボディダイオードへの流入を阻止するのが最も有効である。しかしながら、SBD面積を大きくするほどボディダイオードへの流入が減少して特性の安定性が得られる一方で、コストは増加する。そこで、第2世代MOSFETではドリフト層のプロファイルを最適化し、欠陥の拡張を起こりにくくした。その結果、SBD面積が第1世代に比べて20%縮小され、コストへの影響を軽減できた。

図2. 高速スイッチング性能の比較

### 3. パッケージ構造

#### 3.1 低インダクタンス設計

パワーモジュールでは、スイッチング時の高い電流変化率 $di/dt$ と回路の寄生インダクタンス $L_s$ によるスパイク状のサージ電圧や、デバイスの寄生容量と $L_s$ に起因した振動が発生する。スイッチングスピードが速いSiCデバイスはその傾向が顕著である。第2世代MOSFETモジュールでは第1世代と同様に、チップ多並列接続で低インダクタンス化が可能なパッケージを採用し、SiCデバイスの高速スイッチングに相応した仕様になっている(図3)。また第1世代品と取付け寸法や外形寸法を同等にしているので、第1世代からの置き換え使用が可能である。

#### 3.2 放熱性の改善

SiCデバイスは高電流密度化が可能であるが、モジュールの放熱性に影響する場合がある。第1世代MOSFETモジュールでは横方向への熱の広がりが比較的少なく、フィンの持つ冷却能力を十分に発揮できないという問題があった。第2世代MOSFETモジュールではまず、チップサイズの最適化及びその分散配置によって発熱体同士の熱干渉を軽減した。さらに横方向への熱の広がりに大きく寄与する銅ベース板の厚みを増加させた。

図4は、発熱の状況をシミュレーション解析したものであり、パワーチップの配置とフィン表面での熱の広がりの対応を示している。第2世代MOSFETモジュールは熱の広がりがより広範囲にわたっており、冷却フィンをより効率的に使用できる。

#### 3.3 高信頼性(パワーサイクル寿命の向上)

要求されるモジュールの性能としてパワーサイクル寿命がある。通電時のON/OFFによる短時間の温度スイング

図3. 低インダクタンスパッケージ

を繰り返すことでチップと絶縁基板間の接合材に熱ストレスが発生し、構成部材間の線膨張係数やヤング率の違いによって接合材であるはんだ層の劣化(クラック)が進行する。特にSiCはSiに比べてヤング率が約4倍であり、はんだ層の劣化が顕著である。その結果、Si材料を用いたIGBTモジュールと比べてパワーサイクル寿命が短いという問題があった。ジャンクション温度の到達点が高い場合は更に厳しくなるので、SiC材料自体は優れた高温動作能力があるにもかかわらず、第1世代MOSFETモジュールでは使用可能な最大ジャンクション温度( $T_{jmax}$ )を150°Cに制限せざるを得なかった。 $T_{jmax}$ を引き上げるためには、まずパワーサイクル寿命の改善が不可欠である。第2世代MOSFETモジュールではチップの厚みを第1世代に比べて1/3に薄くしているが、これはオン抵抗の低減のほか、パワーサイクル寿命の改善に貢献する。熱ストレスによるはんだ層のひずみをシミュレーション解析した結果(図5)によると、第1世代に比べて歪値が20%低減する。はんだ組成を最適化し、熱ストレス耐量より高くした接合材と組み合わせることでクラックに対する耐量を向上させ、パワーサイクル寿命を改善した。さらに、高温動作に対応した封止部材の採用や電極設計の最適化を行い、使用可能な $T_{jmax}$ を175°Cにすることことができた。

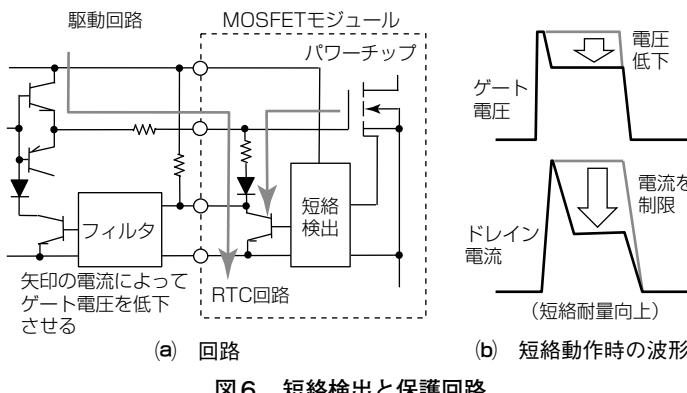

#### 3.4 短絡耐量への配慮

応用機器によっては上下アーム短絡動作又は負荷短絡動作に対して、一定時間破壊しないことを要求される場

図4. フィン表面での熱の広がり

図5. 热ストレスによるはんだ層のひずみ

合がある。MOSFETはオン抵抗特性と短絡耐量の間に強いトレードオフ相関を持っている。第2世代MOSFETモジュールは、電流センシング機能を備えたチップと、RTC(Real Time Control)回路をモジュール内に搭載することによってこのトレードオフを解消する(図6)。大電流状態を検知すると即座にゲート電圧を低下させてドレイン電流を制限する。その結果、オン抵抗特性を損なうことなく短絡耐量を飛躍的に向上させることができる。また同時に、異常フラグ出力端子を各アームに備えており、これをモニタすることで大電流状態の検知が可能である。外部駆動回路で最終的な遮断を行って、安全に遮断できる。

#### 4. 適用のメリット

SiC-MOSFETモジュールを使用するに当たって性能の改善とともに、コスト面も重要視される。特に、IGBTモジュールからの置き換えを考えるユーザーにとってはその費用対効果が切実な問題となる。パワーエレクトロニクス機器の高周波化を高いレベルで実現する第2世代MOSFETモジュールは、コストメリットを引き出すポテンシャルを持っている。優れた低損失性能は冷却器の簡略化を実現する。また、高密度に集積されたモジュールの小型化は、機器のダウンサイジングにつながる。さらに、高いスイッチング周波数で動作させることによって、フィルタやトランスなどのリアクトル部品の小型・軽量化が可能になる。それらは全て、機器全体の直接的コスト削減に貢献する。それだけでなく、間接的なコスト削減にも特筆すべき点がある。機器のダウンサイジングによる設置・保守メンテナンスの容易性、軽量化による輸送費の削減などが挙げられる。図7に、システム全体の直接的コスト試算結果のイメージを示す。160kWクラスの電力変換で、DC-DC部分の絶縁トランス、及び出力フィルタリアクトルを備えた電源システムを想定した。SiCウェーハ材料はSiに比べて高価であり、また結晶欠陥密度も高いため、パワー

モジュールの製造コストの面ではSi材料を用いたIGBTなどに比べて劣っているのが現状である。しかしながら、前述したように、リアクトルや冷却部品を含めたコストメリットはモジュール価格の増分を打ち消し、むしろシステム全体コストが下がることが考えられる。今後、SiCウェーハの高品質化及びデバイス技術の発展によってモジュールの製造コストが更に下がれば、メリットは一層拡大する。

最後に、製品ラインアップについて述べる。ユーザーの利便性を考え、それぞれのクラスの応用回路で最適と思われるパッケージ及び回路形態を選択した。1,200V/1,200A, 800A, 600Aでは、100kW前後の3相コンバータ及びインバータで使い勝手の良い2in1とした。また、1,200V/300A, 400Aでは2in1のほか、4in1も選択でき、単相の電源システムに最適である。また、電源応用ではシステム上、モジュールに短絡耐量を持たせることを重視しないケースがあることから、一部の品種で、先に述べた短絡保護回路を備えないタイプも加えた。さらに、1,200V/100A, 150A, 200Aでは、3相ハーフブリッジをワンパッケージ化した6in1にし、配線や組立ての利便性を持たせた。

#### 5. むすび

電源システム等に用いられる、高周波スイッチング動作に最適な第2世代SiC-MOSFETモジュールを開発した。今後も、多様化するユーザーからのニーズを反映した付加価値の高い製品開発を行っていく。

#### 参考文献

- 宮崎裕二、ほか：高周波用IGBTモジュール“NFMシリーズ”，三菱電機技報，80, No.6, 411~414 (2006)

- 山口義弘、ほか：高温動作パッケージ構造，三菱電機技報，92, No.3, 167~170 (2018)

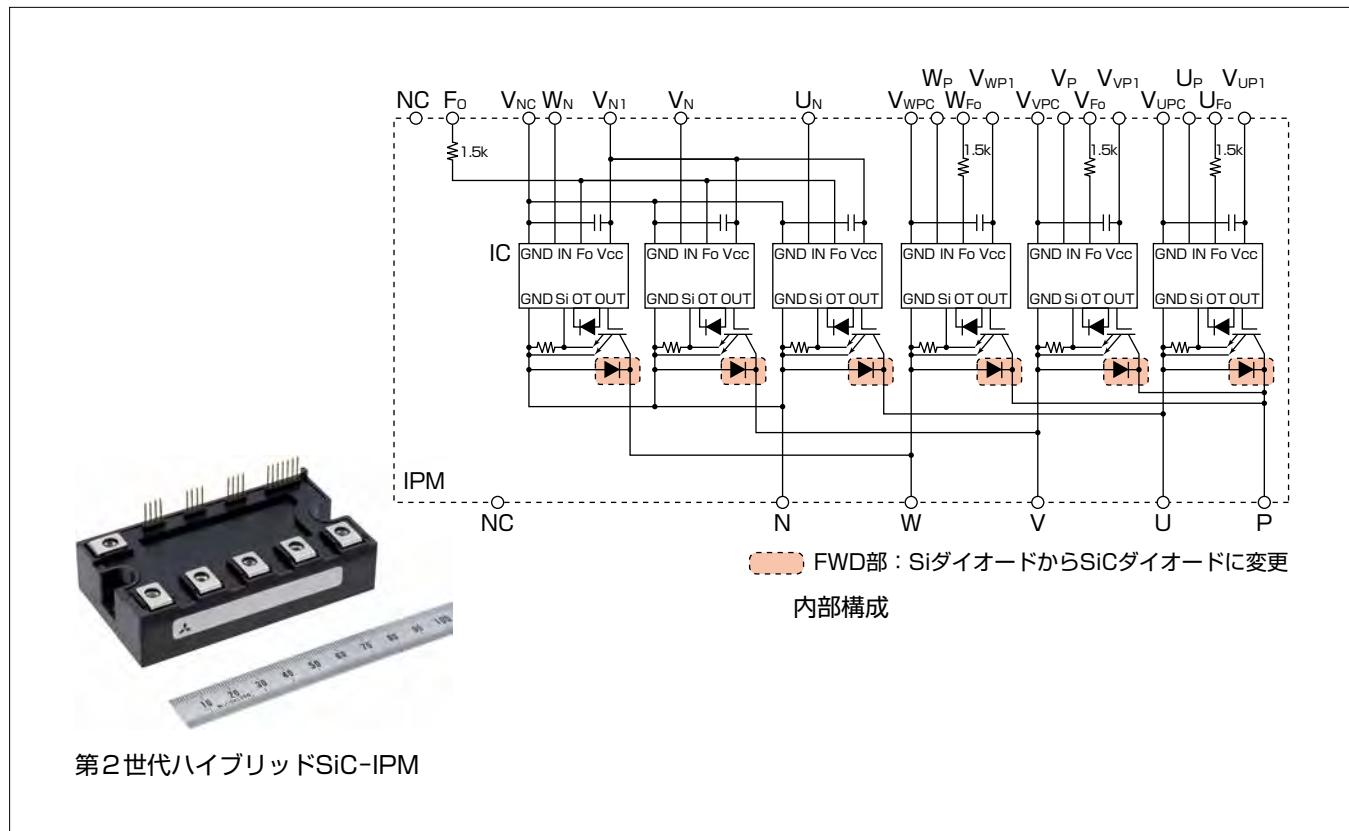

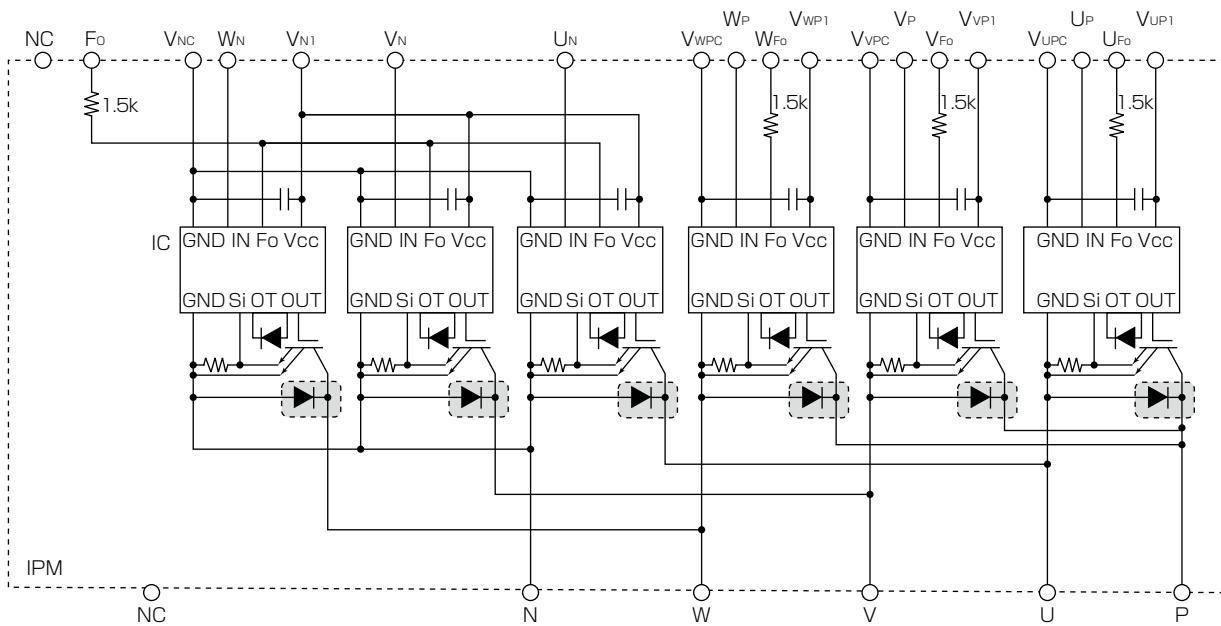

## 第2世代ハイブリッドSiC-IPM

2nd Generation Hybrid SiC-IPM

大月高実\*

Takami Otsuki井上貴公\*

Takahiro Inoue河本啓輔\*

Keisuke Kawamoto後藤 売\*

Ryo Goto

## 要旨

近年、低炭素化社会に向けて、FA、家電、電鉄等のパワーエレクトロニクス機器の省エネルギー化・小型化競争が進んでいる。そのため、それら機器に搭載されるパワーデバイスに対しても、高性能化・小型化が求められるようになっている。そのような状況の中、大幅な電力損失低減が期待できるSiC(シリコンカーバイド)は、次世代半導体デバイス材料として注目されており、パワーデバイスメーカー各社でSiCデバイスを搭載したパワーモジュール製品の開発が行われている。

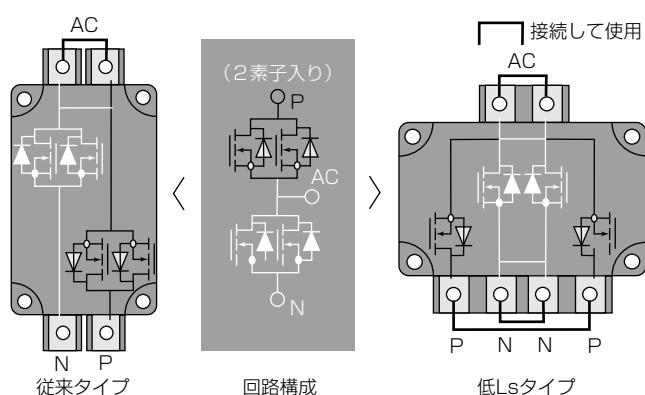

三菱電機では、これまで、産業機器向けのインテリジェ

ントパワーモジュール(IPM)についても、FWD(Free Wheeling Diode)部にSiCダイオードを搭載した第1世代ハイブリッドSiC-IPMを提供してきた。現在、その後継としてSi-IPMの上位互換が可能な、第2世代ハイブリッドSiC-IPMを開発中であり、その主な特長は次のとおりである。

- (1) 外形はSi-IPM“G1シリーズ”のAパッケージと同等

- (2) 第2世代SiCダイオード搭載

- (3) 制御・保護回路はG1シリーズを踏襲

- (4) 電力損失は第1世代比約10%低減

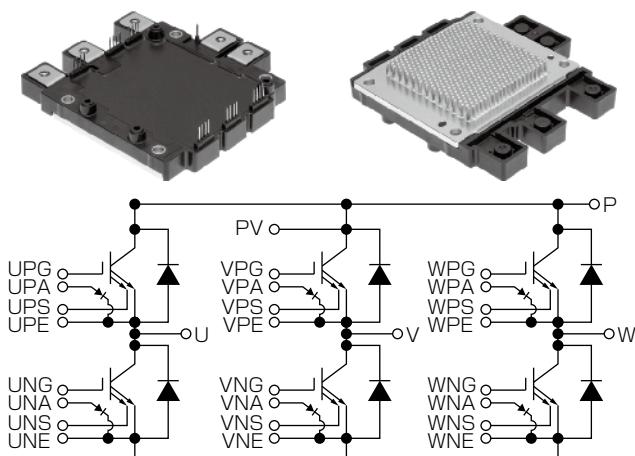

## 第2世代ハイブリッドSiC-IPMの外観及び内部構成

開発中の第2世代ハイブリッドSiC-IPMは、Si-IPMの上位互換が可能で、①外形はSi-IPM“G1シリーズ”的Aパッケージと同等、②第2世代SiCダイオード搭載、③制御・保護回路はG1シリーズを踏襲、④電力損失は第1世代比約10%低減、の四つの特長を持つ。左はその外観、右は内部構成である。

## 1. まえがき

省エネルギー化の機運がますます高まる中、パワーデバイスが注目されて久しいが、現在主に使用されているSi(シリコン)デバイスはその材料物性で決まる理論限界に近付いている。今後そのSiに代わると期待されているものに、ワイドギャップ半導体であるSiCやGaN(窒化ガリウム)がある。当社では、全社的なプロジェクト体制を構築してSiCデバイスを搭載したパワーモジュールの開発を進めており、これまで、産業用IPMについても、市場への提供を行ってきた。

現在は、第2世代のSiCダイオードを搭載したIPMの開発を進めており、本稿ではその内容について述べる。

## 2. 第2世代ハイブリッドSiC-IPM

### 2.1 ラインアップ

第1世代のSiCダイオードを搭載したIPMの外形は、Si-IPMからの置き換えが容易にできるようにという観点から、当時の量産主力機種であったIPMの“L1シリーズ”と同一にした。今回、第2世代のSiCダイオードを搭載したIPMの開発を進めるに当たっても、同様の理由から、外形についてはSi-IPMと互換性を持たせることにした。

図1に、現在当社で量産している産業用Si-IPMの最新パッケージ“G1シリーズ”での1,200V系のラインアップ

を示す。今回、最も小型であるAパッケージの最大定格(1,200V/50A)の上位互換版という位置付けで、第2世代SiCダイオードを搭載した製品の開発を進めている。

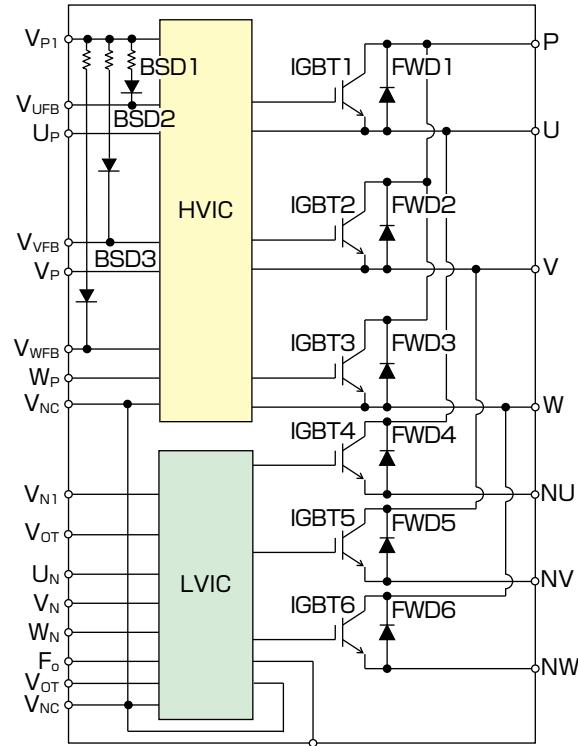

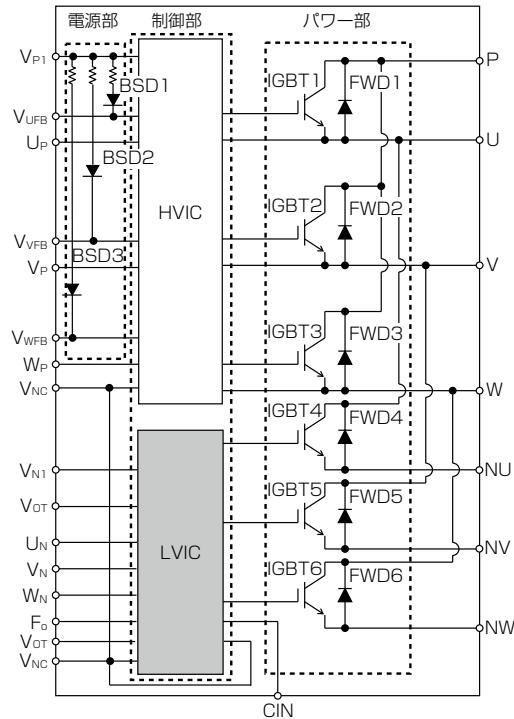

### 2.2 IPMの内部構成

IPMの内部構成を図2に示す。本稿で述べる製品は3相ブリッジタイプの6 in 1であり、制御/保護回路についてはG1シリーズを踏襲している。

### 2.3 ハイブリッドSiC-IPM適用のメリット

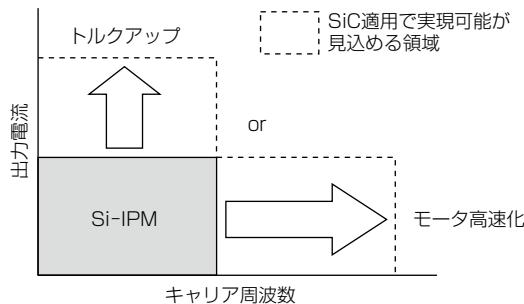

ハイブリッドSiC-IPM適用によるメリットの一例として、モータ用途に対する事例を図3に示す。外形が変わることなく損失低減が期待できることから、ユーザーとしては、基板設計や放熱設計を変更することなく、高速化又はトルクアップの実現が見込める。

| 定格電圧   | パッケージ | 定格電流       |     |            |             |      |      |      |

|--------|-------|------------|-----|------------|-------------|------|------|------|

|        |       | 25A        | 35A | 50A        | 75A         | 100A | 150A | 300A |

| 1,200V | A     | 50×90(mm)  |     |            |             |      |      |      |

|        | B     | 55×120(mm) |     |            |             |      |      |      |

|        | C     |            |     | 85×120(mm) |             |      |      |      |

|        | D     |            |     |            | 110×142(mm) |      |      |      |

図1. Si-IPM“G1シリーズ”での1,200V系のラインアップ

図2. ハイブリッドSiC-IPMの内部構成図

### 3. 第1世代ハイブリッドSiC-IPMとの相違点

これまで、産業機器向けに第1世代ハイブリッドSiC-IPMを提供してきたが、先に述べたメリットを更に活用するため、高キャリア周波数用途により適した仕様を目標として第2世代ハイブリッドSiC-IPMの開発を進めている。この第2世代品について、機能と性能面という観点から、第1世代品と大きく異なる次の2点について述べる。

- (1) エラーモード識別機能搭載

- (2) ダイオードの変更

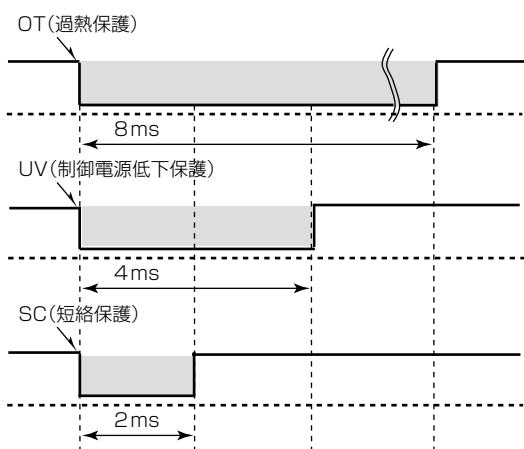

#### 3.1 エラーモード識別機能搭載

第1世代品では、保護機能が働いている際にどの保護機能が動作しているかを、エラー信号だけからは識別できなかった。今回G1シリーズの保護回路を踏襲した第2世代品の保護回路では“エラーモード識別機能”を追加しており、各種保護でエラー信号出力時間が異なるように設計をしている(図4)<sup>(1)</sup>。この機能は、ユーザーのパワーエレクトロニクス機器開発時間の削減に寄与する。

#### 3.2 ダイオードの変更

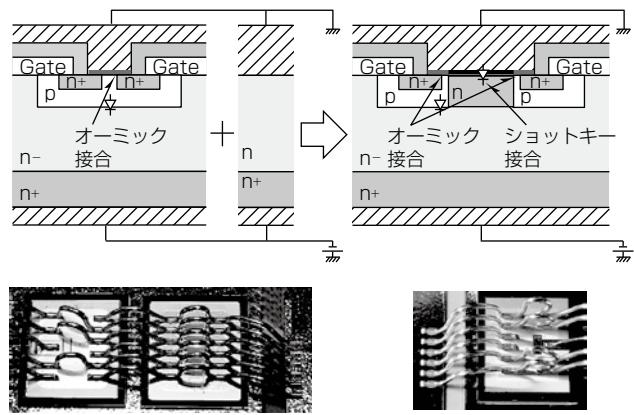

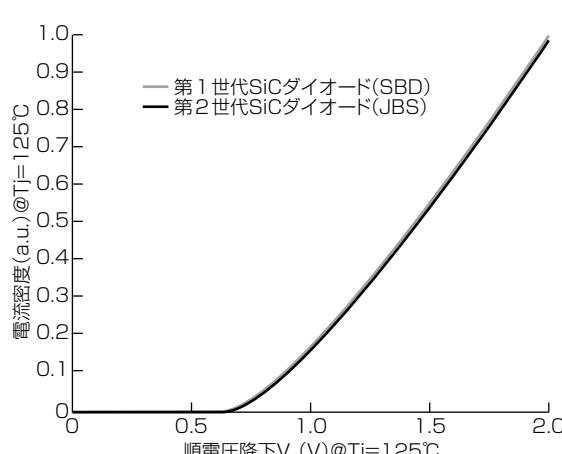

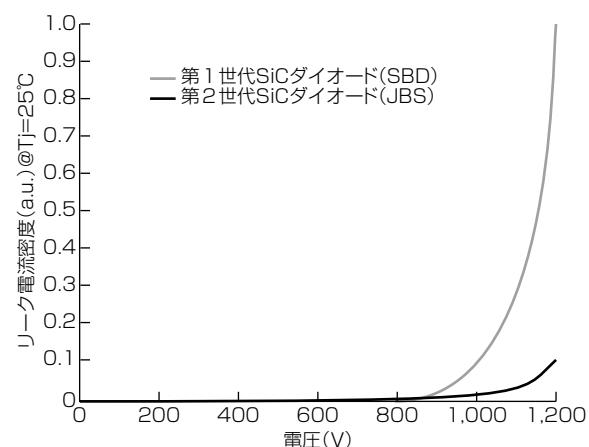

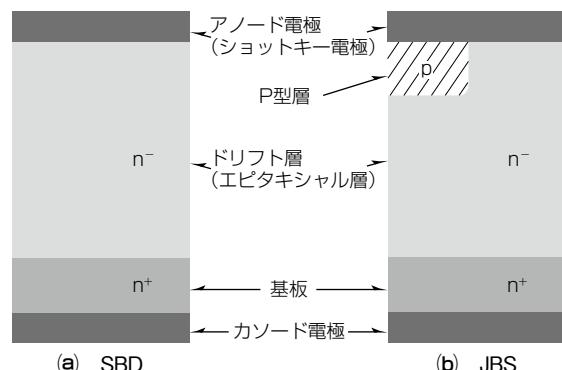

IPMのFWD部のSiCダイオードについて、第1世代

品ではSBD(Schottky Barrier Diode)を採用していたが、第2世代品ではJBS(Junction Barrier controlled Schottky diode)を採用することとした。JBS構造を採用することでショットキー電極界面の電界強度が緩和でき、逆バイアス時のリーク電流低減が見込まれる。SBDとJBSの断面模式図を図5に示す。

また、JBS構造の採用及び第2世代化に伴うエピタキシャル層の厚み・濃度の最適化によって、定格電圧印加時のリーク電流抑制を実現しつつ、従来比同等の電圧-電流特性を実現した。(図6、図7)

## 4. 第2世代ハイブリッドSiC-IPMの特性

### 4.1 スイッチング波形

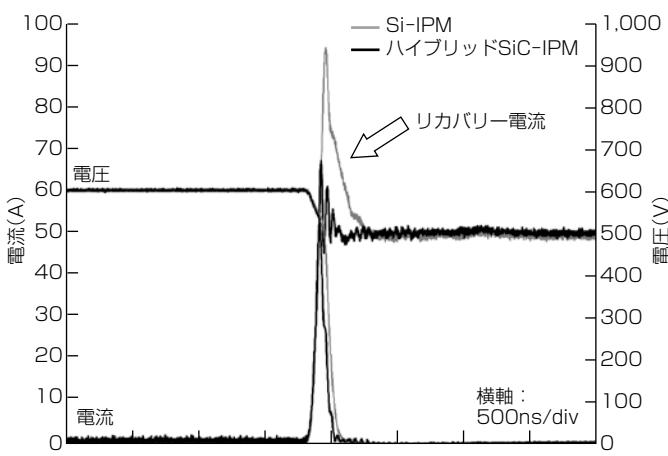

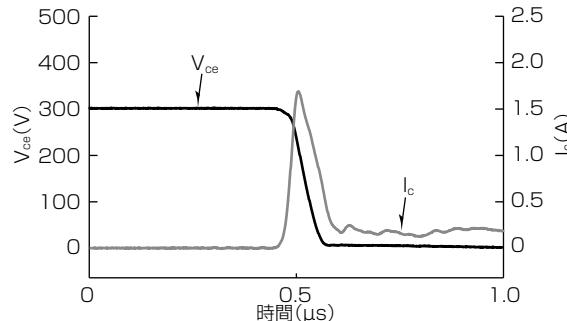

一般的に、IPMのFWD部のダイオードをSiからSiCに変更することで、IGBT(Insulated Gate Bipolar Transistor)のターンオンスイッチング時に発生するFWD部のリカバリー損失を減らせることが知られている。これによって、Si-IPMと比較して電力損失低減が見込まれる。図8に、Si-IPMとハイブリッドSiC-IPMの誘導負荷スイッチング時のターンオン波形の比較を示す。この波形から、Si-IPMではターンオン時にリカバリー電流が重畳されているが、ハイブリッドSiC-IPMでは、リカバリー電流重畠がほとんどなくなっていることを確認できる。

### 4.2 電力損失

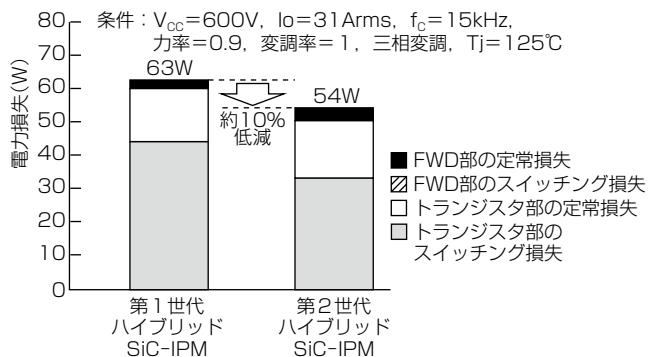

一例として、15kWのインバータ動作を想定した条件では、先に述べたリカバリー電流低減効果によって、第1世代ハイブリッドSiC-IPMではSi-IPM比で約25%の電力損失低減効果を得られていた<sup>(3)</sup>。

今回、同条件で、第1世代ハイブリッドSiC-IPMと第2世代ハイブリッドSiC-IPMの電力損失を試算した結果を図9に示す。第2世代ハイブリッドSiC-IPMは高キャリア周波数用途に適した仕様にしていることもあり、この条件では電力損失を第1世代品比で約10%低減できていることが確認できる。

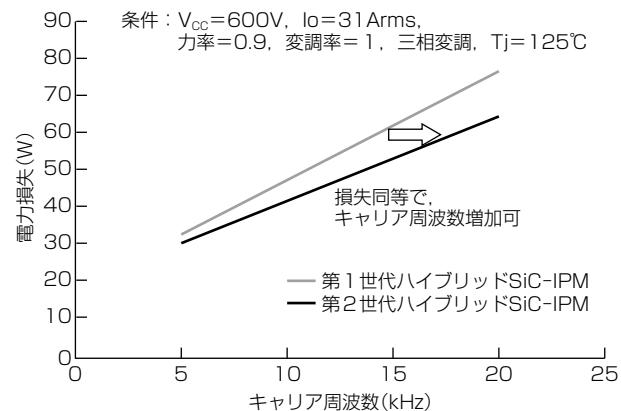

また、上記条件で、キャリア周波数以外の条件を固定して、キャリア周波数と電力損失の関係について試算した結果を図10に示す。この図から、損失同等を許容範囲とした場合には、第2世代ハイブリッドSiC-IPMは第1世代ハイブリッドSiC-IPMに対して、より高いキャリア周波数で動作可能であることが確認できる。

図8. 誘導負荷スイッチング時のターンオン波形の比較

図9. 電力損失試算結果

図10. キャリア周波数と電力損失の関係

## 5. むすび

開発中の産業用第2世代ハイブリッドSiC-IPMについて述べた。SiCを適用した今後の製品としては、ハイブリッドSiC-IPMに対して、さらにFWD部に逆並列接続されているSi-IGBTをSiC-MOSFETに置き換える第2世代フルSiC-IPMの提供を考えている。フルSiC-IPMではターンオフ時間の低減が見込まれ、より低損失なIPMの実現が可能と考える。また、ターンオフ時間が短くなることで、より高キャリア周波数での動作実現が見込まれ、トランジスタの小型化実現が期待できる。

限りある資源を有効活用する省エネルギー製品のニーズが高まる中、SiCを適用した製品の開発は市場の期待に添うものであると考えている。将来的にはSiに代わるデバイスとして期待されていることもあり、様々なニーズを満たすSiC適用製品を市場に送り出していくことで、更なる省エネルギー社会の実現に貢献していく。

### 参考文献

- 木村義孝, ほか: 産業用第7世代IPM“G1シリーズ”, 三菱電機技報, 90, No.5, 299~302 (2016)

- 松波弘之, ほか: 半導体SiC技術と応用, 日刊工業新聞社 (2003)

- 大月高実, ほか: SiCパワーモジュール化技術, 三菱電機技報, 88, No.5, 301~304 (2014)

## 並列駆動に適したパワーモジュール

Power Module for Parallel Operation

津田 亮\*

Ryo Tsuda

酒井純也\*

Junya Sakai

梅崎 勲\*

Isao Umezaki

増岡史仁\*

Fumihito Masuoka

## 要旨

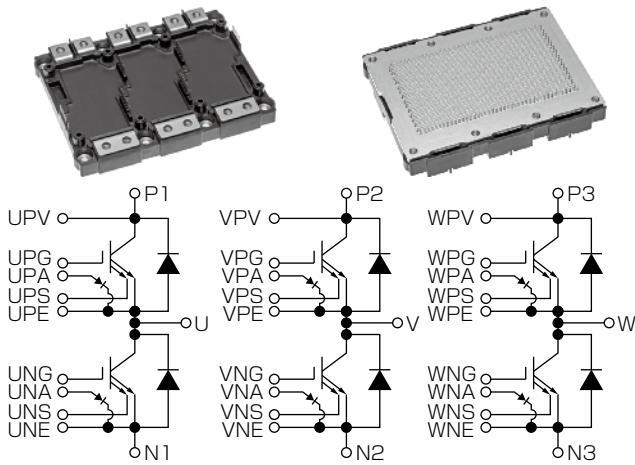

三菱電機はSi(シリコン)チップを搭載するHVIGBT(High Voltage Insulated Gate Bipolar Transistor)モジュールとして業界最大の電流密度<sup>(注1)</sup>となるHVIGBTモジュール“XシリーズLV100タイプ”を開発した。LV100タイプはインバータの標準化、スケーラビリティ(コアとなるLV100タイプ製品を並列駆動することによって各アプリケーションに必要な電流定格を形成する)、モジューラビリティを基本コンセプトとして開発された世界標準パッケージであり、パワーモジュールの並列駆動に必要な要求を満足するように設計されている。また、当社ではLV100タイプ

に搭載するチップについても並列駆動に適したチップ開発を実施しており、本稿では、ゲート駆動条件によって電流バランスの補正が行えるIGBTではなく、駆動条件等での補正が不可能なダイオード側に焦点を当てる。並列駆動でダイオードに必要な条件として、ロバスト性、低損失、順方向特性が正の温度係数を持つことなどがある。この要件を満足するため、高耐圧・大電流密度・並列駆動に適したRFC(Relaxed Field of Cathode)ダイオードを開発し、LV100タイプとの組合せによって並列駆動に適したパワーモジュールの開発を行った。

(注1) 2017年5月11日現在、当社調べ

## LV100タイプを採用したHVIGBTモジュール

Hシリーズから始まった当社のHVIGBTは市場ニーズに応え、高電流密度化を推進している。HVIGBTモジュールXシリーズLV100タイプでは業界最大の電流密度となる8.57A/cm<sup>2</sup>を達成した。同時に、LV100タイプでは並列動作に適した電極配置を採用するとともに、ダイオードチップにRFC構造を採用し、並列動作に必要とされる高いロバスト性、高サージ電流耐量、低損失を達成して製品のモジューラビリティとスケーラビリティを実現した。

## 1. まえがき

パワーモジュールに搭載されるIGBTとFWD(Free Wheeling Diode)の進歩はパワーエレクトロニクスの開発に不可欠である。また、様々な構成・定格容量の応用製品に対応するためには、モジュールのコンセプト、ターゲット仕様に適したチップの開発が必要になる。LV100タイプの基本コンセプトの一つであるスケーラビリティを満足するためには、モジュール内の電流分担の均一化が重要な要素の一つに挙げられる。これに対して、IGBT側の動特性はゲート電圧などによってコントロールすることが可能である一方、ダイオード側はこのような機能が存在しないことから、当社はLV100タイプの並列駆動に適したダイオードとして次の特性を持つRFCダイオードを開発した。

- (1) 高RRSOA(Reverse Recovery Safe Operating Area)

- (2) 高サージ電流耐量

- (3) 低損失

- (4) 並列接続の容易性(スケーラビリティとモジューラビリティの実現)

スケーラビリティの実現のためにモジュールの並列駆動が必須となる。一方で並列駆動でのモジュール数が増加するほどモジュールの設計は難しくなる。この課題に対応するためモジュールの電力密度の増加を検討し、同時に電流密度の増加によって引き起こされる問題への対応として、ダイオードチップのロバスト性と性能の改善を行った。

2章ではRFCダイオードの技術的進歩とロバスト性について、3章ではRFCダイオードを使用したモジュールの並列駆動評価結果を述べる。4章ではLV100タイプを使用した製品のスケーラビリティについて述べる。

## 2. RFCダイオードチップの性能

### 2.1 RFCダイオードチップの構造

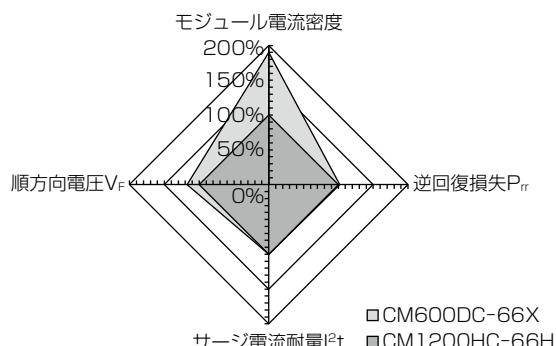

図1にRFCダイオードチップの構造断面図を示す。有効領域カソード側のp/n繰り返しパターンを最適化することで、スナップオフ現象を抑制しつつ、並列駆動に有利な正の順方向電圧降下( $V_F$ )温度特性を実現した。また、終端領域カソード側のp層とアノード端バラスト構造、終端構造にLNFLR(Linearily-Narrowed Field Limiting Ring)<sup>(2)</sup>とSCC構造(Surface Charge Control)<sup>(3)</sup>を採用し、高RRSOAと低熱抵抗を両立させた。このダイオードをLV100パッケージに搭載し、定格電流600A、最大定格電圧3,300VとしたHVIGBTモジュールXシリーズLV100タイプ“CM600DC-66X(フットプリント:140×

100(mm))”は従来品である定格電流1,200A、最大定格電圧3,300VのHVIGBTモジュール“CM1200HC-66H(フットプリント:140×190(mm))”に対し、1.9倍の電流密度(4.51A/cm<sup>2</sup>から8.57A/cm<sup>2</sup>)を達成した。

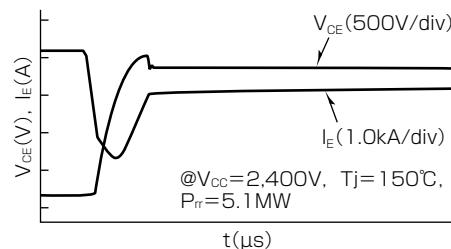

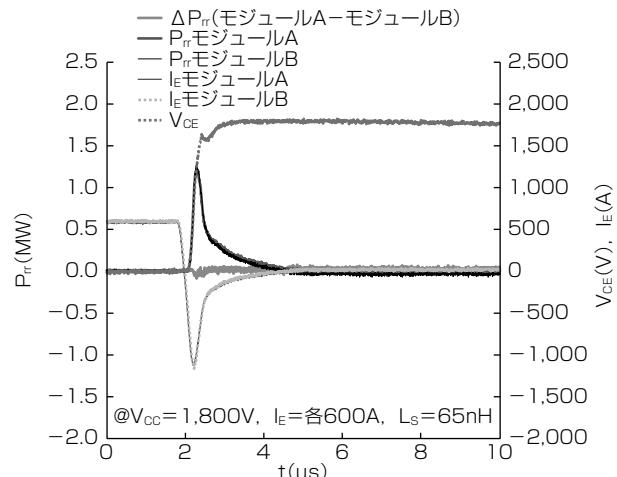

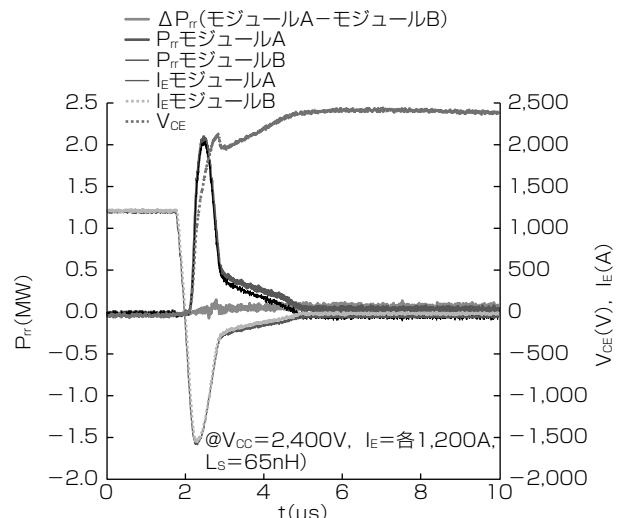

### 2.2 逆回復損失耐量

並列駆動時にモジュール間で発生する電流アンバランスを考慮すると、ダイオードのRRSOAの確保が一層重要である。図2に最大リカバリー条件での電流・電圧波形を示す。RFCダイオード搭載のHVIGBTモジュール(CM600DC-66X)は、従来品(CM1200HC-66H)比1.9倍の高電流密度化に加えて、最大動作温度を125°Cから150°Cに、最大DC-Link電圧を2,200Vから2,400Vに高めているにも関わらず、逆回復損失( $P_{rr}$ )は5.1MWと従来品と同等のRRSOA耐量を示し、十分なロバスト性を持っている。

### 2.3 サージ電流耐量

電鉄用途などのHVIGBTモジュールのダイオードには高いサージ電流耐量( $I^2t$ 耐量)が要求される。CM600DC-66Xを用いて $I^2t$ 耐量を評価した結果、 $P_{rr}$ と同様に高い電流密度にも関わらず、従来品と同等のサージ電流で破壊のないことを確認した。

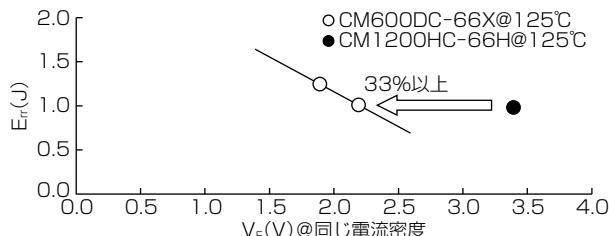

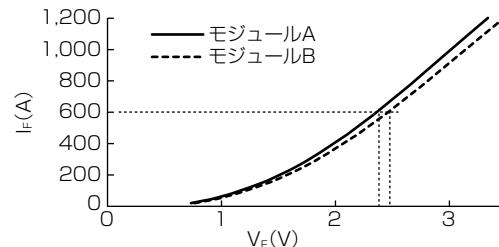

### 2.4 順方向電圧とリカバリー損失のトレードオフ特性

RFCダイオード搭載のHVIGBTモジュール(CM600DC-66X)と従来品(CM1200HC-66H)の順方向電圧( $V_F$ )とリカバリー損失( $E_{rr}$ )のトレードオフ特性の比較を図3に示す。デバイス構造を最適化したRFCダイオードは、従来品と比較して33%以上の $V_F$ 改善をもたらした。

図1. RFCダイオードチップの構造断面図

図2. RRSOAの評価結果

図3.  $V_F$ - $E_{rr}$ トレードオフ特性の比較

図4. RFC適用製品と従来品の性能比較

図4では、RFCダイオード搭載のCM600DC-66XとCM1200HC-66Hをモジュール電流密度、逆回復損失、サージ電流耐量、順方向電圧の四つの指標で比較した。CM600DC-66Xのモジュール電流密度は従来品の1.9倍であるにもかかわらず、逆回復損失とサージ電流耐量を損なうことなく順方向電圧( $V_F$ )が改善していることが分かる。先に述べたとおり、RFCダイオードの選定に際してはモジュールの並列駆動における自己電流バランスのため、ダイオードには正の $V_F$ 温度特性が必要とされる。CM600DC-66Xで使用されるRFCダイオードは広範囲の電流範囲にわたって正の温度特性を示すため、その点でも並列駆動に適している。

### 3. 3.3kV HVIGBT並列駆動の評価結果

並列駆動の評価にはダイオード順方向特性のそろった2台のCM600DC-66Xを使用した。図5はリカバリー評価結果(定格電圧、定格電流条件)を示している。モジュールA、モジュールBの電流、P<sub>rr</sub>波形はいずれも良く一致しており、その差異はP<sub>rr</sub>で±3.2%となっている。

図6のRRSOA評価結果(電圧2,400V、定格電流の2倍)でもモジュールAとBの各波形が良く一致し、バランスの取れた動作であることを示している。RRSOAでの重要なパラメータとされるP<sub>rr</sub>の差はわずか±1.4%である。

これらの結果は、順方向特性をそろえて並列駆動させたモジュールは、定格スイッチング条件だけでなくRRSOAについても十分に一致することを示している。

図5. リカバリー評価結果

図6. RRSOA評価結果

図7. RRSOA評価結果(CMH600DC-66X)

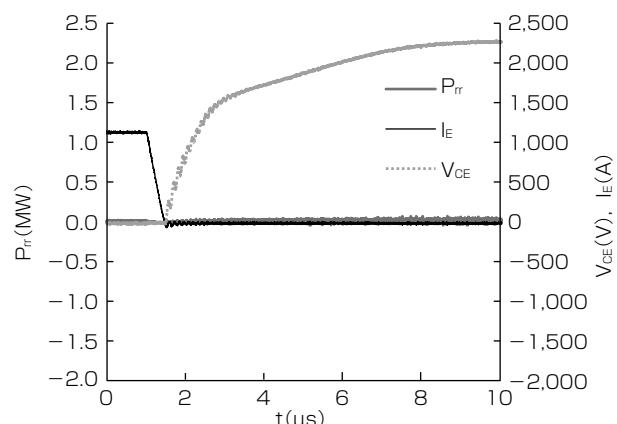

Si-pinダイオードの場合は先に述べたとおり、並列動作でP<sub>rr</sub>に配慮が必要なのに対して、ハイブリッドSiC(Si IGBTとSiC SBD(Schottky Barrier Diode)の組合せ)モジュールの場合はP<sub>rr</sub>が非常に小さく、P<sub>rr</sub>の差異に注意を払う必要がない。図7に当社が開発したLV100タイプを

用いたハイブリッドSiC(シリコンカーバイド)モジュールである“CMH600DC-66X”のRRSOA波形を示す。 $P_{rr}$ はCM600DC-66Xに比べて非常に小さいことが分かる。

#### 4. 並列駆動での電流の分担

一般的に並列駆動によって得られる電流はディレーティングを考慮する必要がある。このディレーティングはダイオードの順方向電圧特性の差異によって引き起こされる電流アンバランスによって必要とされる。この章ではRFCダイオードの順方向特性の差異によって発生する電流アンバランスについて述べる。

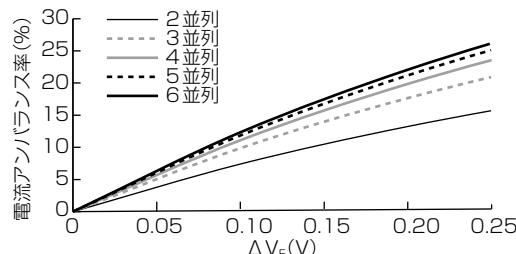

図8は2台のCM600DC-66Xのダイオード順方向特性を示しており、2台のモジュールは定格電流(600A)で順方向電圧が約100mV異なることが確認できる。この差は2台のモジュールが並列駆動される際の電流アンバランスを引き起こす。したがって、電流アンバランスを抑えるためにはダイオード順方向特性のそろった製品の選定が必要とされる。並列駆動時にモジュール間で発生する電流アンバランスは図9のように、並列モジュール数、及び $\Delta V_F$ の二つのパラメータによって電流アンバランス率が変化する。

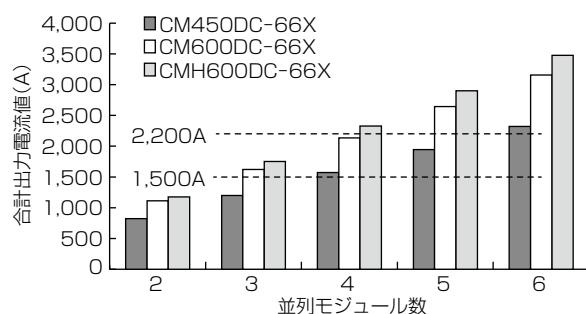

図10では、図9で確認した電流アンバランス率を用いて、製品ごとに並列モジュール数と合計の出力電流値を示す。この図はコンバータやインバータが必要とする出力電流値に対し、必要な並列モジュール数を示しており、Si IGBT適用品種である“CM450DC-66X(CM600DC-66Xの低電流定格品であり、定格電流は450A)”, CM600DC-66X、及びハイブリッドSiC製品であるCMH600DC-66Xについて示している。この確認から、CM600DC-66Xを使用すると、CM450DC-66Xを使用する場合に比べてより多くの出力電流が得られることが分かる。例えば、図10に示すように1,500Aの出力電流が必要な場合、CM450DC-66Xでは4台が必要となるのに対し、CM600DC-66Xでは3台で実現が可能である。この試算によるとシステム設計者はCM600DC-66Xを用いることによってより高いシステム電流をターゲットにすることが可能になる。又は同じシステム電流とし、使用する並列モジュール数を減らすことが可能になる。

さらにCMH600DC-66Xでは定格電流がCM600DC-66Xと同じ600Aであるにも関わらず、SiC-SBDの特性によって並列駆動時の合計出力電流はCM600DC-66Xよりも高くなる。図10に示すように出力電流2,200Aが必要な場合、CM450DC-66Xで6台が必要なのに対してCMH600DC-66Xでは4台で実現が可能である。

図8. ダイオード順方向特性の差異( $\Delta V_F$ )による電流アンバランスの例(CM600DC-66X)

図9. 並列モジュール数と電流アンバランス率(CM600DC-66X)

図10. 合計出力電流値と並列モジュール数の関係(電流アンバランス考慮あり)

#### 5. む す び

HVIGBTモジュールXシリーズLV100タイプに対して並列駆動に適したRFCダイオードを搭載することで、並列動作に適した製品を開発した。当社は今後もLV100タイプ製品の開発を通じて、よりフレキシブルなシステム開発の実現を進めるとともに、HVIGBTを始めとするパワーモジュールによって低炭素化社会の実現と豊かな生活の両立に貢献する。

#### 参考文献

- (1) Tsuda, R., et al.: LV100 High Voltage Dual Package in Paralleling Operation, PCIM Europe 2018-International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 1~6 (2018)

- (2) Chen, Z., et al.: ISPSD'13, 37~40 (2013)

- (3) Honda, S., et al.: ISPSD'16, 291~294 (2016)

## 普及版600V HVIC“M81776FP”

Popular Edition 600V High Voltage Integrated Circuit "M81776FP"

羽生 洋\*

Yo Habu

山本晃央\*

Akihisa Yamamoto

佐野昇平†

Shohei Sano

### 要旨

近年、世界的な地球環境保護基調の高まりを受け、省エネルギーや高性能化を目的に、電動自転車や家電製品、産業用機器でのモータ駆動部のインバータ化が進展している。これに伴い、インバータシステムで使用されるパワー半導体を駆動するHVIC(High Voltage Integrated Circuit)の需要も拡大している。また、日本では省エネ法に基づくトップランナー制度に2013年から産業用モータが追加され、モータのエネルギー効率向上に加え、インバータシステムにも小型化・低コスト化が求められるようになった。

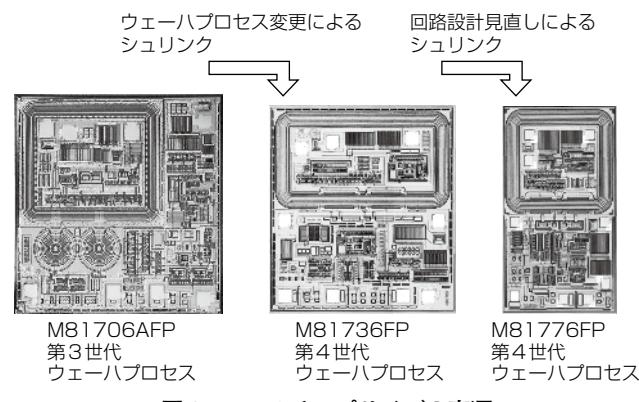

三菱電機は今回、高いノイズ耐性と低価格化を両立させた“普及版600V耐圧ハーフブリッジドライバM81776FP”を開発した。これによって、インバータシステムの小型化

と更なる普及に貢献することを目的にしている。

このHVICの特長は次のとおりである。

- (1) サイズやピン配置などの互換性を確保し、従来のドライバICからの置き換えが容易になる。

- (2) 高いノイズ耐性と低価格化を両立させ、インバータシステムの信頼性を向上させた。

- ①回路設計や材料の見直しによって、低価格化を実現

- ②スイッチング時のラッチアップ誤動作を抑制する埋め込み層の採用によって、高いノイズ耐性を実現

- ③フローティング回路内の構造最適化によって、ハイサイド側の信号伝達の精度を向上

M81776FP

M81776FPチップ

### 600V HVIC“M81776FP”の外観及びチップ

高いノイズ耐性と低価格化を両立させた、“普及版600V耐圧ハーフブリッジドライバM81776FP”を開発した。インバータシステムの小型化と、更なる普及に貢献することを目的にしている。

## 1. まえがき

近年、世界的な地球環境保護基調の高まりを受け、省エネルギーや高性能化を目的に、電動自転車や家電製品、産業用機器でのモータ駆動部のインバータ化が進展している。これに伴い、インバータシステムで使用されるパワー半導体を駆動するHVICの需要も拡大している。また、日本では省エネ法に基づくトップランナー制度に2013年から産業用モータが追加され、モータのエネルギー効率向上に加え、インバータシステムにも小型化・低コスト化が求められるようになった。

三菱電機のHVIC技術として、1997年に独自技術である分割リサーフ構造(第1世代)の開発によって1,200V HVICの製品化を開始した。2008年には第1世代分割リサーフ構造へN+埋め込み層の微細パターン形成によって、耐圧・誤動作耐量を向上させた第2世代分割リサーフ構造を600Vクラスで開発・製品化を実施した<sup>(1)</sup>。また、この第2世代分割リサーフ構造に独自のフィールドプレート技術を適用し、耐圧の1,200V化を実現し、製品化も進めている<sup>(2)</sup>。分割リサーフ構造は、HVICでの高圧レベルシフトと呼ばれる、ハイサイド回路を駆動する電圧レベルへの変換動作に用いるLDMOSFET(Laterally Double-diffused Metal-Oxide-Semiconductor Field-Effect-Transistor)に適用する構造である。分割リサーフ構造の適用は耐圧・誤動作耐量の向上と合わせて、チップ上で占有する面積が大幅に縮小され、チップコスト低減に大きく寄与する。このように性能(耐圧)・品質(誤動作耐量)を維持・向上させ、さらに製造コストの低減(低価格化)との両立を図る活動を継続して行ってきた。

本稿では今回開発した高いノイズ耐性と低価格化を両立させた“普及版600VハーフブリッジドライバM81776FP”について製品概要、及び性能・品質と製品価格の両立化技術について述べる。

## 2. 普及版600VハーフブリッジドライバM81776FP

### 2.1 M81776FP機能及び従来製品との互換性

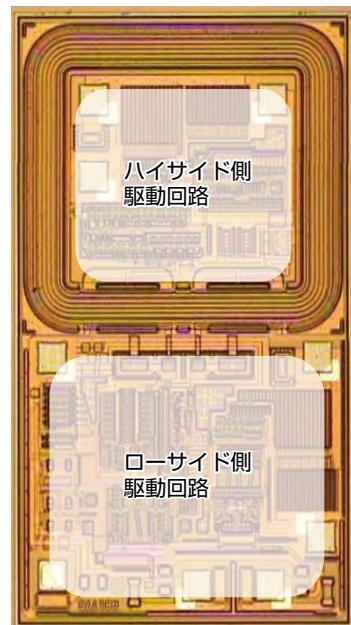

“普及版600VハーフブリッジドライバM81776FP”は基本機能に絞ったシンプルな回路構成であり、HVICのベーシックモデルとなる製品である。M81776FPの機能ブロック図を図1に示し、その機能を次に挙げる。

- (1) ハーフブリッジ駆動

- (2) 3.3V/5.0Vロジック入力対応インターフェース(HIN, LIN)

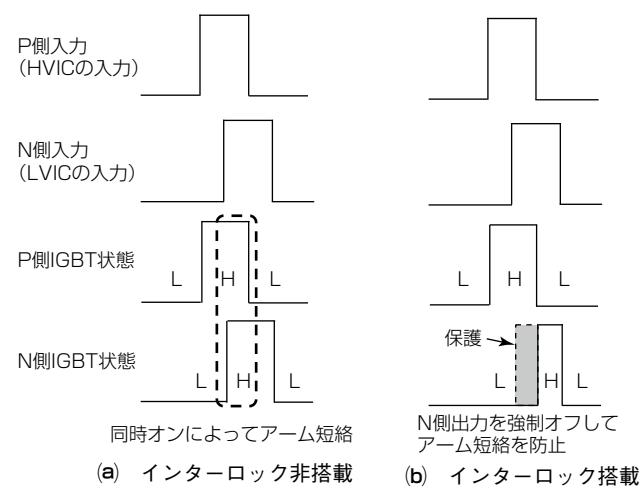

- (3) 入力インタロック(出力の同時オン防止)

- (4) 600Vの高圧レベルシフト回路

- (5) 出力電流能力(+200mA/-350mA)

- (6) 電源電圧低下保護回路(UV:VCC/VBS)

M81776FPは従来製品“M81706AFP/M81736FP”からの置き換えを容易にするためにサイズやピン配置、諸特性がコンパチブルとなるように設計している。

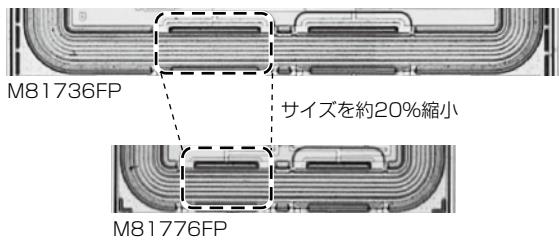

### 2.2 普及版としての製品開発

#### 2.2.1 チップサイズシルクリングによる低コスト化

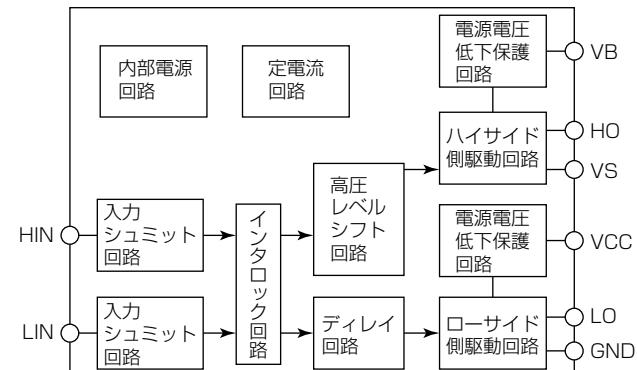

図2に従来製品であるM81706AFP/M81736FPから今回開発したM81776FPに至るまでのチップサイズの変遷と、サイズシルクリングの経過を示す。

M81706AFPは三菱電機の第3世代ウェーハプロセスを適用しており内部回路を構成するCMOS(Complementary Metal-Oxide-Semiconductor)のサイズも比較的大きい。また、第3世代ウェーハプロセスは高圧レベルシフトに用いるLDMOSFETに分割リサーフ構造が適用されていないため、チップ上での面積占有率が高くなっている。図に示す製品では、最も大きなチップサイズとなる。

M81736FPは三菱電機の第4世代ウェーハプロセスを適用しており、この世代から600V耐圧ウェーハプロセスで第2世代分割リサーフ構造がLDMOSFETに適用され、

図1. M81776FPの機能ブロック図

図2. HVICチップサイズの変遷

高圧レベルシフト回路部での面積占有率の改善が顕著になる。また、内部回路を構成するCMOSについてもデザインルールの微細化から縮小効果を得ることができ、前世代品M81706AFPと比較した場合にチップサイズがシリンクされる。

今回開発したM81776FPは、M81736FPと同じく第4世代のウェーハプロセスを適用しているが、縮小効果は約30%以上を達成している。M81776FPはM81736FPとの特性コンパチブル製品ではあるが、HVIC内部回路構成について同一ではなく、チップコスト低減を目的にした回路設計の見直しを行っている。具体的な内容を次に述べる。

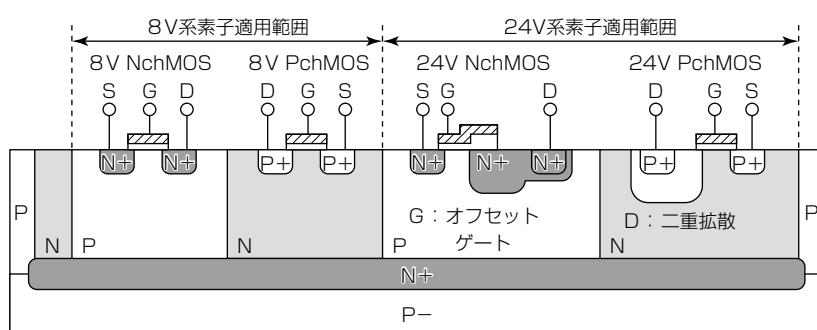

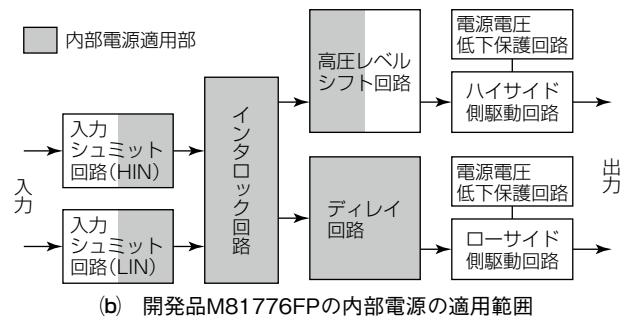

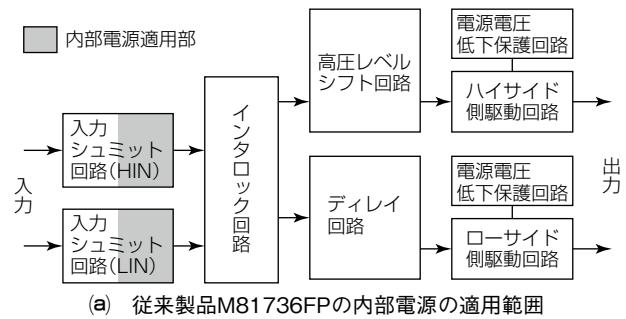

#### (1) 内部回路を構成するCMOSの8V系素子適用拡大

HVIC内部回路のCMOSは、インバータシステムでよく用いる制御系電圧(VCC)15Vに対応するため、その耐圧が24Vになっている。耐圧を確保するために、二重拡散やオフセットゲート構造を探るが、サイズとしては大きくなる。チップサイズを縮小するために、サイズの小さな耐圧8V系素子で構成するCMOSの適用範囲拡大を行った。図3に耐圧別のCMOS断面構造を示す。8V系素子の適用範囲拡大には、CMOSの電源を内部電源(<8V)とする回路の範囲拡大が必要となる。図4に従来製品M81736FPと開発品M81776FPでの内部電源の適用範囲を、図5に内部回路に使用するトランジスタ数と耐圧別(8V/24V)の割合をそれぞれ示す。内部回路で使用するトランジスタの総数は、両品種共にほぼ同数であるが、サイズの小さな耐圧8V系素子の適用範囲を拡大することで、チップサイズ縮小の効果を得ている。また、内部電源は電源電圧(VCC)の依存性が少ない回路構成となっており、内部電源を適用した回路部では、特性の安定化という利点もある。

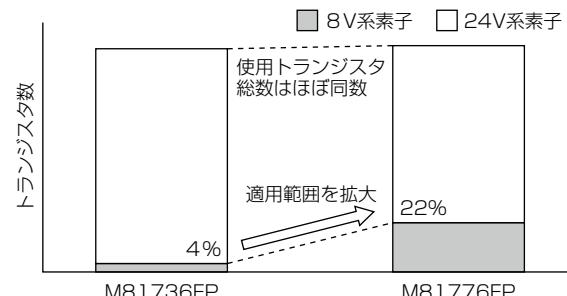

#### (2) 特性安定化によるトランジスタサイズの縮小

M81776FPでは、内部電源を適用した回路部の特性安定化に加え、新たに定電流回路を適用することで、特性の更なる安定化を図っている。この定電流回路は内部電源と同様に電源電圧(VCC)の依存性が少なく、さらに温度依存性も少ない回路構成にしている。従来製品では外的要因(電圧/温度)に対するマージンを確保したトランジスタ

図3. 耐圧別CMOSの断面構造

図4. 内部電源の適用範囲

図5. 内部回路の耐圧別使用トランジスタ数

サイズ設計になっていたが、ロバスト性の向上によって、M81776FPではトランジスタサイズの縮小が可能になった。一例として図6に高圧レベルシフト用LDMOSFETの従来品種とのサイズ比較を示す。レベルシフト用電流の最大値を抑制することによってLDMOSFETのサイズを約20%縮小した。高圧レベルシフト部でのLDMOSFETのサイズ縮小は、ハイサイド回路を構成するリサーフ領域のサイズに直結し、大幅なチップサイズ縮小が可能になる。

#### 2.2.2 性能・品質の維持と向上

##### (1) 定電流制御による特性安定化

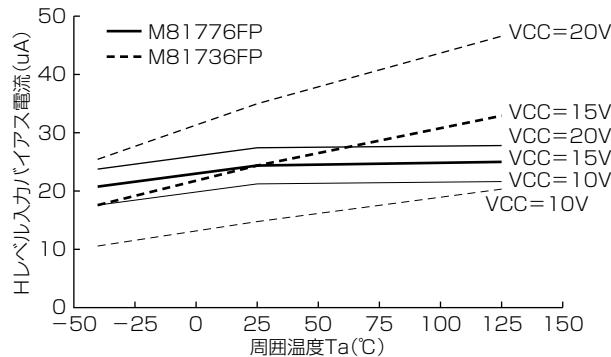

2.2.1項(2)でも述べたが、M81776FPは特性の安定化を目的として、新たに定電流回路の適用を行っている。電源電圧依存性と温度依存性の改善から、製品機能のロバスト性が向上する。定電流回路の特性が顕著に表れる電気的特性として、Hレベル入力バイアス電流が挙げられる。図7にその温度/電源電圧依存性の特性を示す。特性の標準条件であるVCC = 15V・Ta = 25°Cで

図6. 高圧レベルシフト用LDMOSFETのサイズ比較

図7. Hレベル入力バイアス電流

は、従来製品との互換性を確保するために同一特性となっているが、温度／電源電圧に対する特性の安定性が向上していることが分かる。

安定化の効果が特に顕著に表れるのが、電源電圧が高く、周囲温度が高い場合となる。先に述べた高圧レベルシフト回路にも定電流回路を適用しているため、この安定化の効果が同様に得られる。すなわち高キャリアでの駆動損失が問題になる高温領域で、損失低減することを意味しており、M81776FPでは駆動に対する余裕度が拡大している。

## (2) 製品品質の維持・向上

M81776FPは従来製品M81736FPと同一世代(第4世代)ウェーハプロセスを採用している。このウェーハプロセスはCMOS領域にN+埋め込み層を設けており、ラッチアップ誤動作抑制に有効に作用する。これによって従来製品と同等の品質を確保できる。

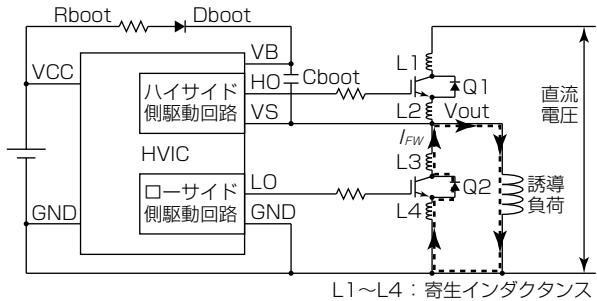

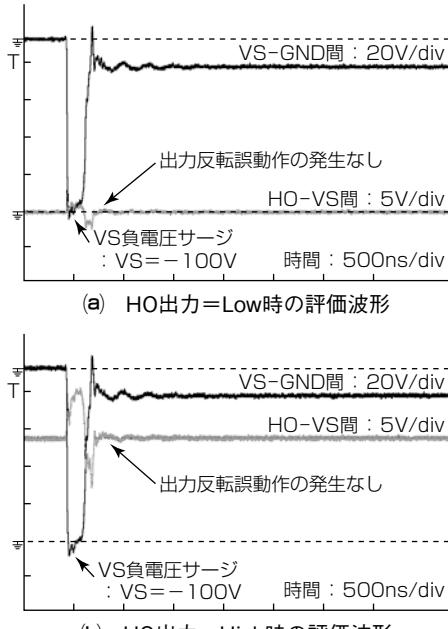

さらにM81776FPでは、誤動作抑制を目的にフローティング回路内の構造最適化によって、ハイサイド側の信号伝達の精度の向上を行っている。ハイサイド側回路は、VS端子の電位を基準としているため、インバータの出力状態によって回路の基準が常に変動する。基準が変動した場合でも、誤動作耐量を確保することが製品品質を維持する上で重要になる。図8にハーフブリッジタイプのHVICを用いた応用回路の接続例を示す。ハイサイド側のトランジスタQ1がターンオフすると、ローサイド側駆動回路のフリーホールドオードが還流モードになり電流が流れる。このとき、寄生インダクタンスによってHVICのVS端子に負電圧サージが発生する。この負電圧サージはHO端子のハイラッチ誤動作や破壊を引き起こす場合がある。

図8. 応用回路の接続例

図9. VS負電圧サージ耐量評価

図9にM81776FPでVS負電圧サージを印加した場合のHO出力について評価結果の一例を示している。図ではVS端子に-100Vを印加した場合の評価結果を示しているが、HO出力の状態によらず誤動作は発生せず、また破壊も発生していない。これは従来製品M81736FPと同等の耐量であり、チップサイズシュリンクによる誤動作耐量への影響懸念をフローティング回路内構造最適化で払拭していることを示している。

## 3. むすび

今回、高いノイズ耐性と低価格化を両立させた“普及版600V耐圧ハーフブリッジドライバM81776FP”を開発した。これによって、インバータシステムの小型化と更なる普及に貢献する。

## 参考文献

- 清水和宏, ほか: 第2世代分割RESURF構造を適用したHVIC技術, 三菱電機技報, 84, No.4, 228~231 (2010)

- 羽生 洋, ほか: 高信頼性1,200V HVIC“M81738FP”三菱電機技報, 88, No.5, 289~292 (2014)

## 低容量帯の表面実装パッケージ型IPM

Low Capacity Surface-mount Package Type IPM

横山脩平\*

Shuhei Yokoyama

山口公輔\*

Kosuke Yamaguchi

野口宏一郎\*

Koichiro Noguchi

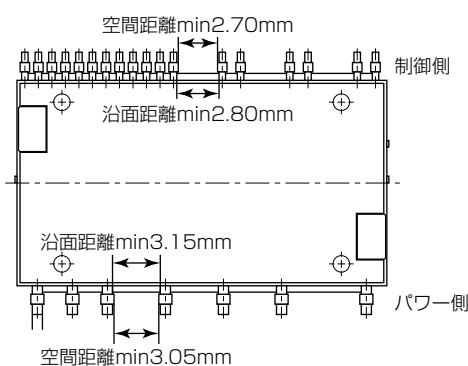

## 要旨

近年のエネルギー問題から環境保護と節電への意識がより高まり、一般家庭での消費電力量が高いエアコン、洗濯機などの白物家電の省エネルギー化が求められている。これまで白物家電の省エネルギー化のため主にコンプレッサのインバータ化が進んできたが、今後は更なる省エネルギー化のためにファンモータまでインバータ化が進むと予想される。

三菱電機のIPM(Intelligent Power Module)“DIPIPIM”は1997年に製品化して以来、アジア市場の白物家電を中心にコンプレッサ向けインバータ機器に採用されてきたが、低容量帯では表面実装型IPMが広く使われ、ファンモータ用途にはピン挿入タイプのDIPIPIMのままでは市場参入が困難であった。そこでこの市場に対応するために低容量

帯の表面実装パッケージ型IPMを開発した。

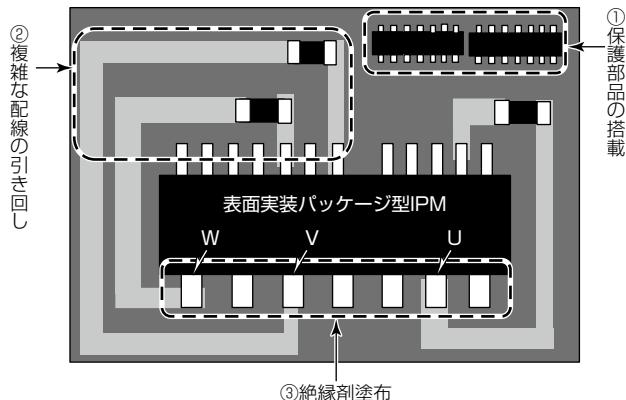

開発品は顧客の組立て工程を含む実装基板レベルでのコスト低減を念頭に置き、搭載機能及びパッケージ形状の両面から開発を実施した。機能面ではインターロック機能を新たに搭載するとともに、必要な保護機能を全て内蔵することで周辺部品の削減を可能にした。パッケージ面では端子間絶縁距離を確保することで組立て時の絶縁対策コストを削減、さらに“SLIMDIPシリーズ”と同様にP側駆動電源のGND(GrouND)端子を制御側に設けることで基板配線パターンを簡易化し、基板面積削減を可能にした。これらの特長によって開発品は顧客の組立て工程を含む実装基板レベルでのコスト低減に貢献する。

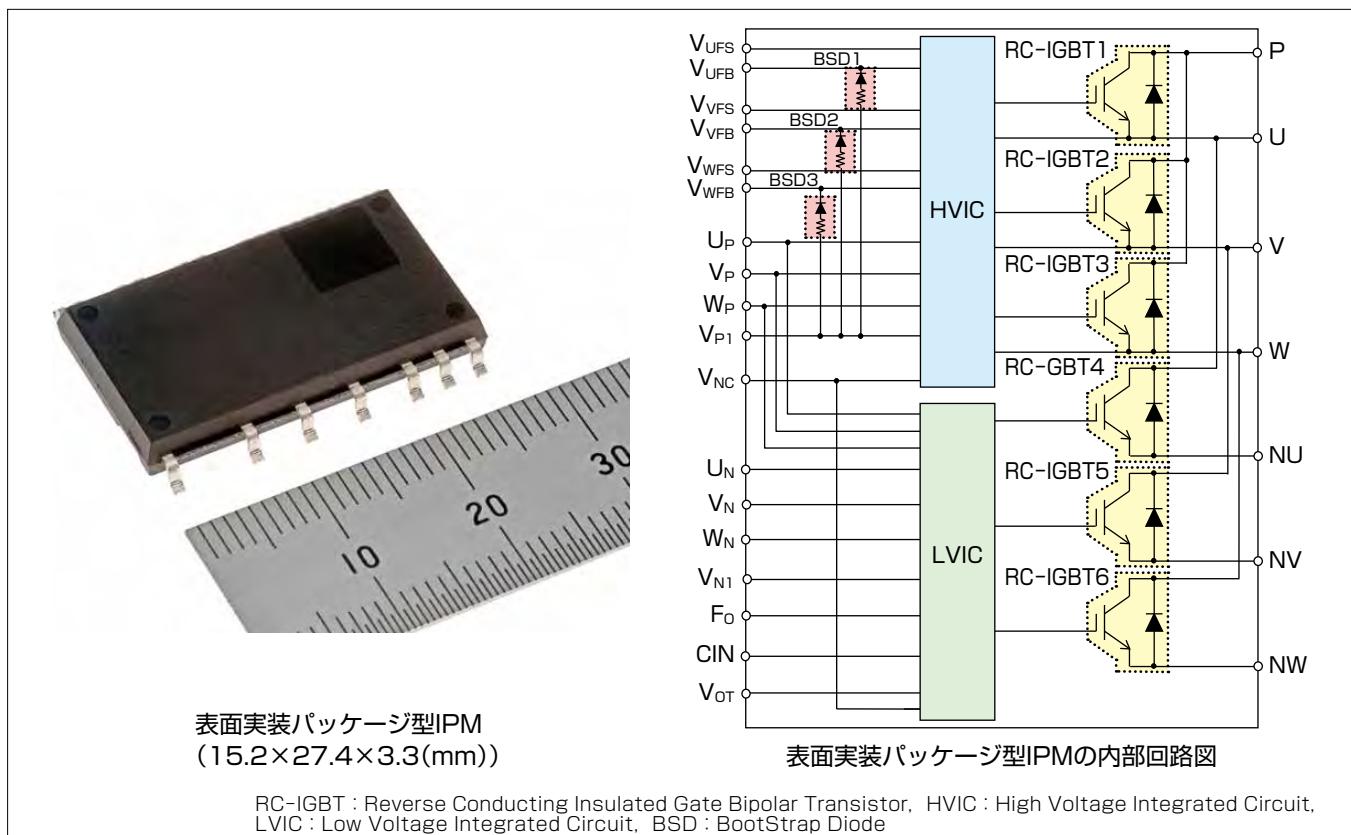

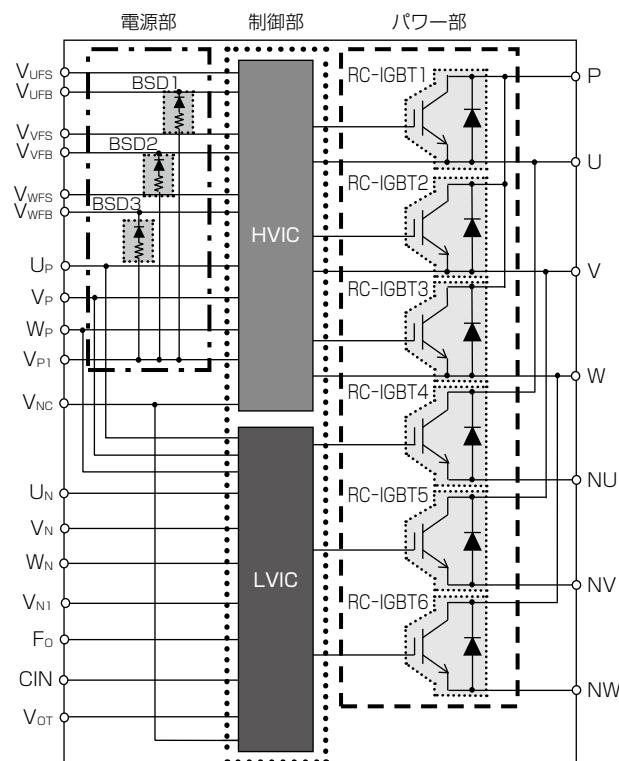

## 低容量帯の表面実装パッケージ型IPMの外観及び内部回路図

低容量帯の表面実装パッケージ型IPMはRC-IGBT×6素子によるインバータ回路と、それを駆動するHVIC、LVIC及びBSD×3素子によって構成される。

## 1. まえがき

近年、世界的な省エネルギー意識の高まりによって、幅広い分野・市場でインバータシステムが普及し、省エネルギー化が進んでいる。一般家庭では消費電力量が高いエアコンが最初にインバータ化され、当社はエアコンのコンプレッサ向けに業界に先んじて<sup>(注1)</sup>トランスファーモールドタイプのIPMであるDIPIPMの製品化を実現し、家電のインバータ化に貢献してきた。

近年は、更なる省エネルギー化のためにコンプレッサだけでなくファンモータまでインバータ化される事例が増えている。しかしながらDIPIPMは主にコンプレッサ向けとして電流定格5A以上のラインアップにしており、低電流域(許容電流1 Arms以下)が動作条件であるファンモータ用途には適していない。さらに、ファンモータ用途では顧客の実装コスト低減及び実装基板の小サイズ化のために表面実装パッケージ型のIPMが広く利用されており、挿入型のDIPIPMでは顧客の要求に応えることができなかつた。

そこで、ファンモータ用途向けに低容量帯の表面実装パッケージ型IPM<sup>(1)</sup>を開発した。開発に当たり、組立て工程を含む実装基板レベルでのコスト低減を念頭に置き、搭載機能及びパッケージ形状の両面を工夫した開発を行った。

本稿では開発した表面実装パッケージ型IPMの概要と特長について述べる。

(注1) 1997年8月25日現在、当社調べ

## 2. 低容量帯の表面実装パッケージ型IPMの概要

今回開発した低容量帯の表面実装パッケージ型IPMの構成と電気特性について述べる。

### 2.1 構成

表面実装パッケージ型IPMはパワー部、電源部、制御部で構成している(図1)。パワー部にはIGBTとダイオードを1チップ化したRC-IGBTを採用し、このチップを6素子内蔵して三相AC出力インバータ回路を構成した。電源部は電流制限抵抗付きBSD 3素子をモジュール内に内蔵してブートストラップ回路を形成し、15V単一電源だけでHVICへの電源供給が可能な構成にした。制御部はP側IGBTを駆動するHVICとN側IGBTを駆動するLVICで構成した。HVICはIGBT駆動回路、高圧レベルシフト回路、フローティング電源電圧低下保護回路(UV)を内蔵した。LVICはIGBT駆動回路、制御電源電圧低下保護回路(UV)、短絡電流保護回路(SC)、過熱保護回路(OT)、アナログ温

度出力回路(VOT)に加えて新たにインターロック機能を内蔵した。

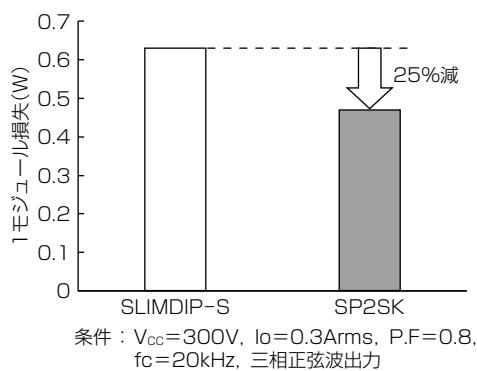

### 2.2 電気特性

開発品と従来品の損失比較を図2に示す。キャリア周波数20kHz,  $I_o = 0.3$  Armsの動作条件で開発品の2A定格品“SP2SK”は従来品の“SLIMDIP-S<sup>(2)</sup>”に対して25%損失を低減した。これによって、100Wクラスのファンモータに要求される低電流駆動条件で大きな省エネルギー効果が期待される。

開発品SP2SKの飽和電圧などそのほかの電気特性を表1に示す。SP2SKは主にスイッチング時間をSLIMDIP-Sに比べて改善(例えば $t_{c(on)} = 0.35\mu s \rightarrow 0.2\mu s$ と約40%高速化)することで先に述べた損失低減を実現した。保護機能についてはSLIMDIP-Sと同等にして仕様の統一を図った。

図1. 内部回路図

図2. 従来品と開発品の損失比較

表1. SP2SKの電気特性

| 項目             | 記号                   | 条件                                                                                                                                                                    | 最小値                                         | 標準値  | 最大値  | 単位   |

|----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|------|------|

| コレクタ・エミッタ間飽和電圧 | V <sub>CE(sat)</sub> | V <sub>D</sub> = V <sub>DB</sub> = 15V, V <sub>IN</sub> = 5V                                                                                                          | I <sub>C</sub> = 2A, T <sub>j</sub> = 25°C  | —    | 2.30 | 3.10 |

|                |                      |                                                                                                                                                                       | I <sub>C</sub> = 2A, T <sub>j</sub> = 125°C | —    | 2.60 | 3.55 |

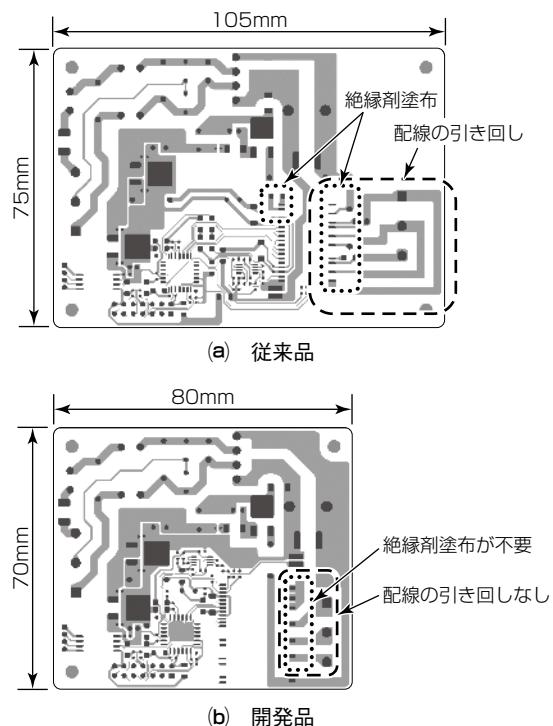

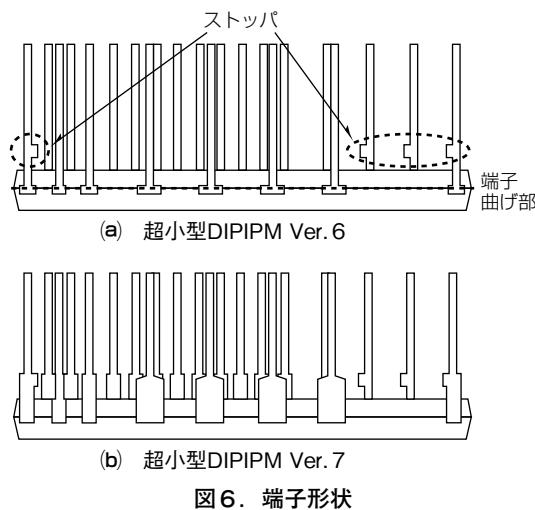

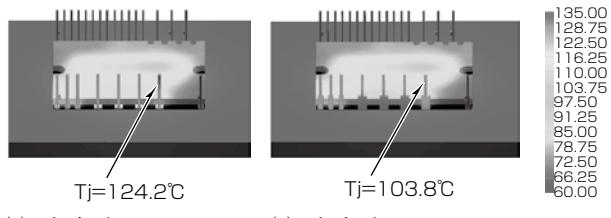

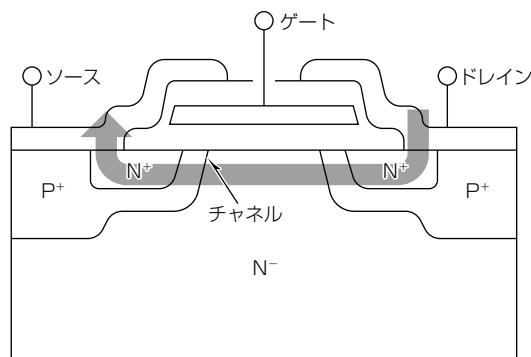

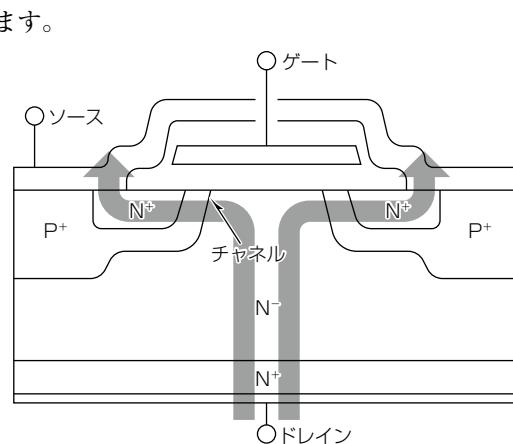

| FWD順電圧降下       | V <sub>EC</sub>      | — I <sub>C</sub> = 2A, V <sub>IN</sub> = 0V                                                                                                                           | —                                           | 2.30 | 3.00 | V    |