# GaN HEMTのオン状態ゲート電流の低減

佐々木 肇\* 加茂宣卓\*\* 門岩 薫\*

Decrease in On-state Gate Current of GaN HEMT

Hajime Sasaki, Yoshitaka Kamo, Kaoru Kadoiwa

#### 要旨

GaN(窒化ガリウム)HEMT(High Electron Mobility Transistor)は高い絶縁破壊耐圧を持ち、高温動作が可能なことから、高出力・高効率デバイスとして期待されているとともに、高い信頼性を持つデバイスとして注目されている。ただ、ゲート端に高電界が印加されると、ウルツ鉱構造特有の逆ピエゾ効果によって結晶欠陥が発生し、ゲート電流が増加するという課題がある。

そこで、このゲート電流の発生機構を明らかにするとともに、ゲート電流の低減方法を提案してその機構を解明した。ゲート形成時のドライエッチングでAlGaN(窒化アルミニウムガリウム)層内にドナー型のトラップが生成されると、ショットキー障壁が擬似的に薄層化してしまう。このとき、デバイスをオン状態で動作させると、チャネル温

度が上昇して電子の熱励起が盛んになり、ゲート電極から AIGaN層内に熱電界放出によって電子が流れ込み、ゲート電流として検出されることを実験結果とデバイスシミュレーションから明らかにした。

次に、このデバイスに適度なストレスを印加することで、 ゲート電流が低減できることを見いだした。この条件では 衝突イオン化によるホットキャリアが大量に発生している ことが発生観察とシミュレーションから確認できた。発生 したホットキャリアがトラップにエネルギーを与える、非 発光再結合促進反応と言われる現象でトラップをアニール アウトしているものと推測できる。トラップが消滅するこ とで薄膜化していた空乏層が厚くなり、熱電界放出量が減 少してオン状態のゲート電流が減少したものと考えられる。

### GaN HEMTのゲート電流の発生及び低減機構

GaN HEMTがオン状態で動作した場合,ゲート電流が流れる。これはチャネル温度の上昇で熱励起された電子がゲート端の高電界領域で熱電界放出を起こすことで流れている。ホットキャリアが発生する条件でストレスを印加すると,ゲート電流を減少させることができた。ホットキャリアの非発光再結合のエネルギーで結晶欠陥がアニールアウトされて,空乏層が拡張することでトンネル確率が減少し,ゲート電流が減少している。

## 1. まえがき

GaN HEMTはGaAs(ガリウムヒ素)デバイスに比べ絶縁 破壊耐圧が高いため, 高電圧での動作が可能で, 飽和ドリ フト速度も高いため、高効率・大電力デバイスとして期待 されている(1)。また、バンドギャップが広い(3.4eV)こと から、アバランシェ効果が小さく、基板に用いているSiC (炭化ケイ素)の熱伝導率が高いことから、高温大電力での 動作が可能で、ガリウムと窒素の原子結合力が強いことか ら耐放射線性にも優れ、化学的にも安定であるという優れ た信頼性も持つデバイスである。キャリアの供給はドーピ ングではなく、AlGaNとGaNのヘテロ接合を用い、ウルツ 鉱構造の異方性を利用して自発分極とピエゾ効果で二次元 電子ガス(2DEG)を誘発させている。しかし、ゲート・ド レイン間に高電界を印加すると、ピエゾ効果を利用してい るがゆえに、特に電界が集中するゲート端のAIGaN層に 逆ピエゾ効果による結晶欠陥が発生するという課題がある (2)。この結晶欠陥を通してゲートリーク電流が流れ、この ゲート電流がさらに欠陥を増加させ信頼性を低下させてし まう。これまで、これらの解析はオフ状態の動作で行われ てきたが、実際に使用されるオン状態での動作時の解析は 行われていなかった。

本稿では、オン状態で流れるゲート電流の発生機構を明 らかにするとともに、そのゲート電流の低減機構を解明し て最後にゲート電流の低減方法の提案を行う。

#### 2. オン状態ゲート電流発生機構

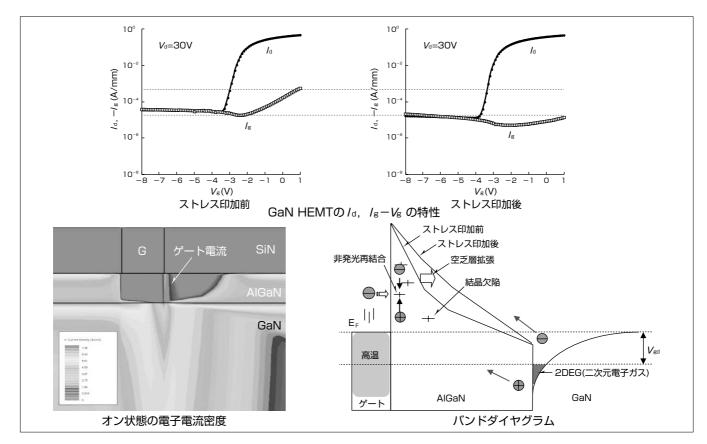

図1にGaN HEMTの $I_d$ ,  $I_g$ - $V_g$ 特性を示す (3)。印加しているドレイン電圧 ( $V_d$ )は30Vである。(a)は初期特性で,ピンチオフ電圧よりも深いゲート電圧領域ではゲート電流とドレイン電流が一致し,ゲート電圧が正にシフトするにつれゲート・ドレイン間の電圧が低下するため,ゲート電流が減少している。しかし,ゲート電圧が-2Vより浅くなりドレイン電流が流れ出すオン状態で再びゲート電流が増加する現象が見られた。このゲート電流の温度特性を測定するとアレニウスプロットから活性化エネルギーEa=0.4eVが得られ,この値は通常のショットキー障壁よ

図1. GaN HEMTの /。, /gーVg特性

#### りも小さい値である。

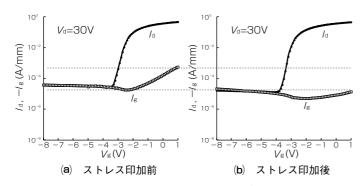

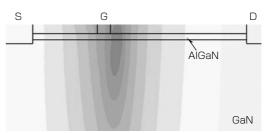

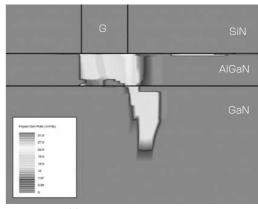

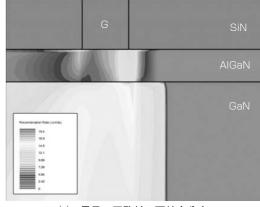

そこで、AlGaN層内にEa=0.4eVの深いドナートラップを仮定してデバイスシミュレーションを行った(図2)。図の(a)はチャネル温度分布を示す。オン状態のためドレイン電流が流れ、特にドレイン側のゲート端の2DEG付近の温度が上昇している。図の(b)は電界分布である。特にドレイン側のゲート端のAlGaN層領域の電界が高くなっている。図の(c)は電子電流密度分布である。オン状態のため2DEGの電流が大きいのは当然だが、ゲート端からAlGaN層を通過してAlGaN/GaN界面まで到達する電子電流が流れていることが分かった。高温かつ高電界領域で電子電流が流れ、ショットキー障壁よりも低い活性化エネルギーを持つことから、この電子電流が熱電界放出で流れるオン状態のゲート電流であると推測できる。

ゲート電極形成工程ではドライエッチングでマスクを加工することが多い。このときAlGaN層内に窒素空孔などの結晶欠陥が誘起されると言われている。窒素空孔はドナ

(a) チャネル温度分布

(b) 電界分布

(c) 電子電流密度

図2. オン状態動作のデバイスシミュレーション

ートラップとして働き、ポテンシャルを押し下げ、見かけ上の空乏層の厚さを薄くする効果として働く。この薄膜化した空乏層内をトンネル効果で熱電子が通過することでゲート電流が流れる。この現象は二端子のショットキー障壁のオフ状態でのゲート電流発生機構であるTSB(Thin Surface Barrier)モデル(4)で説明されており、三端子動作のオン状態でも同様の原理でゲート電流が流れているものと考えられる。

# 3. ストレス印加によるゲート電流の変動

図 1 (b)に  $V_d$ =35V, $V_g$ =+1V,30分のストレスを室温で印加した後の電気特性を示す。図 1 (a)の初期特性と比べると,明らかにオン状態のゲート電流が減少している。従来,ストレス印加でゲート電流が増加する例は多数報告されているが,逆にストレス印加で減少する例は珍しい。

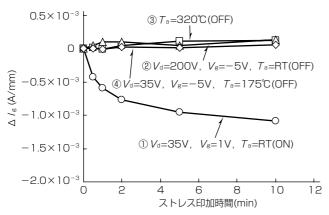

図3に各種ストレスを印加した時のオン状態のゲート電流の変化を示す。図の①ではゲートを正にし、周囲温度(Ta)を室温(RT)で、高いドレイン電圧、大きなドレイン電流を流すことで、初期にゲート電流が急激に減少し、その後徐々に飽和している。一方、②の高いドレイン電圧でオフバイアス、③の高温状態、④のオン状態のチャネル温度を模擬した高温でのオフバイアス条件では、いずれもゲート電流の変化は見られなかった。このことは、温度や電圧だけではゲート電流が減少できないことを意味している。

# 4. ゲート電流低減機構

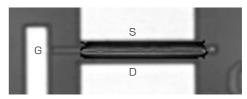

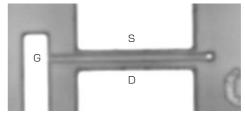

ストレス印加によるゲート電流の変動機構を解明するため、デバイスから発生するフォトンの観察を行った。図4に観察結果を示す。ゲート電流が減少したストレス(a)ではゲート電極のドレイン側に強い発光が見られる。一方、オフバイアスでは顕著な発光は見られなかった。同様に図3で示した高温状態や高ドレイン電圧のオフ条件でも(a)のような強い発光は見られなかった。

オン状態のストレス条件でのデバイスシミュレーションを行った(図5)。図の(a)は衝突イオン化率の分布である。AlGaN層内のゲート電極端のドレイン側で特に激しい衝突イオン化が発生している。これは、オン状態で加熱され

図3. ストレス印加時のゲート電流の変動

たチャネルによる熱電界放出電子が、高いゲート・ドレイン間電圧で加速され衝突イオン化を発生させているものと考えられる。また、ゲート電極のドレイン側の2DEG領域にも衝突イオン化が見られている。これはチャネルを流れるドレイン電流が電界集中の激しいゲート端で衝突イオン化を起こしているものと考えられる。印加電圧が高いため、電子、正孔ともに高いエネルギーを持つホットキャリアになっているものと考えられる。

図5(b)に電子・正孔対の再結合分布を示す。本来GaN

(a)  $V_d=35V$ ,  $V_g=1V$ ,  $T_a=RT(ON)$

光度

(b)  $V_d=35V$ ,  $V_g=-5V$ ,  $T_a=175^{\circ}C$  (OFF)

図4.発生フォトンの観察結果

(a) 衝突イオン化率の分布

(b) 電子・正孔対の再結合分布

図5. ストレス条件のデバイスシミュレーション

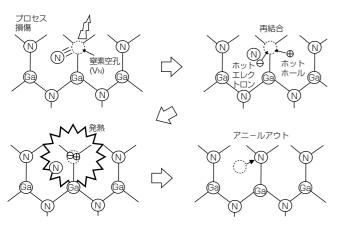

図 6. 非発光再結合促進反応

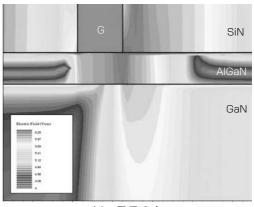

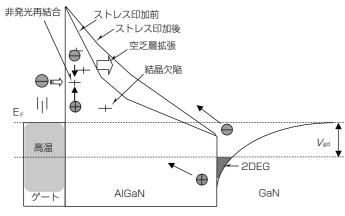

図7. GaN HEMTのバンド構造の変化

HEMTは電子のみで動作しているため正孔は存在しないが、衝突イオン化によって電子・正孔対が発生するため再結合として現れてくる。この再結合分布もゲート端のドレイン側に集中している。図4(a)で見られた発光は電子・正孔対の再結合や高速電子が格子などで散乱される際の制動放射によって発生するため、発光観察の結果とシミュレーション結果は良く一致し、オン状態ではゲート近傍で再結合が盛んに発生していることが明らかになった。

図6に結晶欠陥部分で電子・正孔対が再結合を起こした際の反応を模式的に示す。ドライエッチングなどのウェーハプロセスで窒素空孔のような点欠陥が発生する。オン状態で発生した電子・正孔対が欠陥部分で再結合する。このとき、再結合が発光を伴わない現象の場合、そのエネルギーを欠陥に与えるため微視的に高温状態になり、欠陥がアニールアウトされる。この反応は非発光再結合促進反応(5)と呼ばれている。この反応は欠陥を増殖させる場合もあるが、今回はアニールする方向に働いているようだ。

図7にストレス印加前後のバンドダイヤグラムを示す。 プロセス直後は窒素空孔などの深いドナートラップによっ てバンドが低下し空乏層が薄膜化し、トンネルによってゲート電流が流れる。このゲート電流と大きなドレイン電流 で発生した電子・正孔対が結晶欠陥部分で非発光再結合し、 欠陥をアニールアウトする。ドナートラップが減少したこ とで、空乏層が厚くなり、トンネル確率が減少することで オン状態のゲート電流が減少したものと考えられる。

このストレス印加後に、320℃の高温アニール、1,000時間の高温高周波通電や高温逆バイアスストレスを印加したが、再びゲート電流が増加することはなく、電気特性の変化は見られなかった。このことはゲート電流の低減が、単純な電荷のトラップによる電界分布の変調に伴う一時的な挙動ではなく、結晶品質自体が改善され物理的に安定化したことを示している。

# 5. む す び

デバイスが実際に動作するオン状態で発生するゲート電 流の解析を行った。ウェーハプロセス時に形成されたドナ ートラップによってゲートのショットキー空乏層厚が薄膜 化される。ドレイン電流の電力消費でチャネル温度が高温 になり、ゲート電極から熱励起電子が発生し、印加されて いるゲート・ドレイン間電圧によって、薄膜化した空乏層内 を電子がトンネルする熱電界放出でゲート電流が流れること を, 実験結果とデバイスシミュレーションから明らかにした。 高ドレイン電圧で高ドレイン電流を印加することで、ゲ ート電流を低減することができた。このストレス条件では 衝突イオン化によって大量のホットキャリアが発生してい る。発生した電子・正孔対が非発光再結合反応促進効果で 欠陥をアニールアウトすることで, 空乏層厚が厚くなり, トンネル確率が減少し、オン状態のゲート電流が低減でき たものと考えられる。この反応は不可逆であり、適切なス トレス印加によって、安定した信頼性の高いデバイスを作 製することができた。

## 参考文献

- (1) 三輪真一, ほか:衛星搭載用C帯高効率100W GaN増幅器, 三菱電機技報, **87**, No. 2, 109~112 (2013)

- (2) del Alamo, J.A., et al.: GaN HEMT reliability, Microelectronics Reliability, 49, 1200~1206 (2009)

- (3) Sasaki, H., et al.: Decrease in On-State Gate Current of AlGaN/GaN HEMTs by Recombination-Enhanced Defect Reaction of Generated Hot Carriers Investigated by TCAD Simulation, Microelectronics Reliability, **54**, 2662~2667 (2014)

- (4) Hasegawa, H., et al.: Mechanisms of current collapse and gate leakage currents in AlGaN/GaN heterostructure field effect transistors, Journal of Vacuum Science & Technology B, 21, 1844~1855 (2003)

- (5) Hoshi, S., et al.: The Recovery Process of RIE-Damage in InGaAs/AlGaAs PHEMT Using Recombination Enhanced Defect Reaction, IEICE Trans. Electronics, E84-C, 10, 1350~1355 (2001)