# 高効率GaNスイッチング増幅器技術

新庄真太郎\* 中溝英之\*\* 向井謙治\*\*\*

Technologies for High Efficiency GaN Switching-mode Amplifiers

Shintaro Shinjo, Hideyuki Nakamizo, Kenji Mukai

#### 要旨

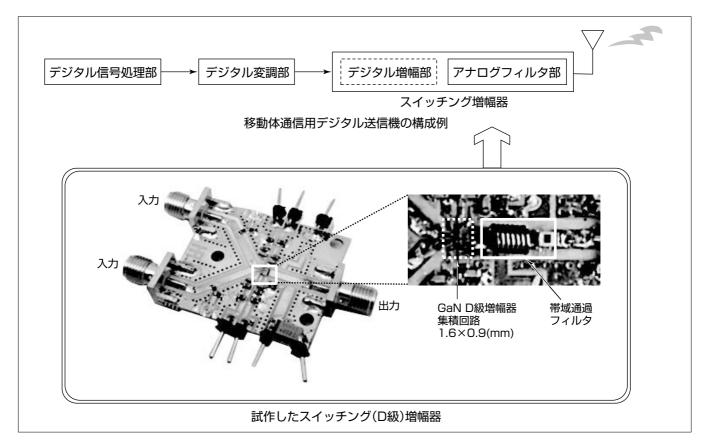

今後ますますの高性能・多機能が求められる移動体通信では複数規格への対応が容易であり小形・低消費電力化が可能なデジタル送信機構成が注目をあびている。デジタル送信機実現のためには、高周波動作する高効率・高出力なスイッチング増幅器がキーコンポーネントの1つとなる。

スイッチング増幅器の高周波化のため微細Si-CMOS (Complementary Metal Oxide Semiconductor)トランジスタを用いる場合、耐圧低下に伴い高出力特性との両立が困難となる。そこでGaN(窒化ガリウム)プロセス技術の進展をうけ、高周波かつ高耐圧特性を持つGaNトランジスタを用いた高効率スイッチング増幅器の実現が期待されている。

本稿ではGaN HEMT (High Electron Mobility Transistor) を用いた動作周波数465MHz. 出力電力 3 Wのスイッチン

グ(D級) 増幅器の試作結果について述べる。GaN HEMT を用いてD級増幅器を構成する場合,しきい値電圧近傍から電源電圧(約30V)までの大電圧振幅をトランジスタのゲート端子に供給する駆動回路の構成とその高効率化が課題となる。この課題に対し,電荷を充放電する容量を備えたブートストラップ形駆動回路の適用によって,駆動回路まで含めたD級増幅器全体の高効率特性を実現した。

さらに、提案の駆動回路を備えたD級増幅部に低域通過フィルタを接続した信号帯域幅20MHzの高速変調信号に対応するエンベロープ増幅器の試作も行った。これらのGaNスイッチング増幅器の良好な各試作結果は、移動体通信用デジタル送信機への早期適用と、新たな展開の可能性を示すものである。

### 移動体通信用デジタル送信機に適用可能なGaN D級増幅器

移動体通信用デジタル送信機を構成するスイッチング増幅器の一例として、D級増幅器を試作した。このD級増幅器は、GaN D級増幅器集積回路と帯域通過フィルタによって構成し、GaN D級増幅器集積回路にはスイッチング増幅回路と駆動回路を内蔵する。駆動回路として電荷を充放電する容量を備えたブートストラップ形の適用によって、高周波・高効率・高出力なD級増幅器を実現した。

## 1. まえがき

高性能・多機能化が進む移動体通信用途の送信機で、デジタルベースバンド部はSi-CMOSプロセスの微細化に伴い小形・低消費電力化が進んでいるものの、アナログ高周波部は顕著な進展が難しい状況にある。そのためアナログ高周波部領域を削減し、高周波信号をデジタル処理するデジタル送信機構成が注目をあびている。デジタル送信機構成の特長は、(1)プログラマブルで適用性が高いため複数規格への対応が容易、(2)高集積化・外部部品の削減によって小型化が可能、(3)スイッチング増幅器の採用によって低消費電力化が可能等であり、近年多方面で研究開発が進められている。

移動体通信用デジタル送信機の実現で、スイッチング増幅器の高周波・高効率・高出力化は主要な技術課題の1つである。スイッチング増幅器は電圧と電流の時間波形の積をゼロにすることによって理論上100%の効率が得られる回路構成であり、出力波形や高次インピーダンス処理方法によってD級・E級・F級などに分類される。従来1ビットデジタル送信機などで用いられているD級増幅器では、微細化に伴い高周波化が進むSi-CMOSプロセスを採用してGHz帯で動作する高周波・高効率特性が既に報告されている。しかしながら、微細Si-CMOSトランジスタは、通常、耐圧が低下するため高出力特性との両立は困難であった。そこで高周波かつ高耐圧な特性を持つGaNトランジスタをD級増幅器に適用し、移動体通信用デジタル送信機に求められる高周波・高効率・高出力なスイッチング増幅器の実現が期待されている<sup>(1)</sup>。

今回、GaN HEMTを用いて動作周波数465MHz、出力電力3WのD級増幅器を試作した。GaN HEMTを用いたD級増幅器では、しきい値電圧近傍から電源電圧(約30V)までの大電圧振幅をトランジスタのゲート端子に供給する駆動回路の構成とその効率特性が増幅器全体に大きな影響を及ぼすが、電荷を充放電させる容量を備えたブートストラップ形駆動回路の適用によって、この課題を克服した。さらに、提案の駆動回路を備えたD級増幅部に低域通過

フィルタを接続した信号帯域幅20MHzの 高速変調信号に対応するエンベロープ増 幅器の試作も行った。これらの試作した スイッチング増幅器はいずれも良好な高 周波・高効率・高出力特性を実現し<sup>(2)(3)(4)</sup>, GaNデバイスの新たな展開の可能性を示 すものである。

#### 2. GaN D級増幅器の駆動回路

## 2.1 回路図

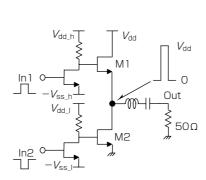

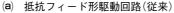

図1にGaN D級増幅器の簡易回路図を示す。D級増幅器はトランジスタM1, M2からなるトーテンポール形スイッチング

増幅回路と、M1、M2をそれぞれ駆動する駆動回路で構成する。ここでM1のドレイン電圧を $V_{\rm dd}$ 、M1の駆動回路の電源電圧を $V_{\rm dd_l}$ 、 $-V_{\rm ss_l}$ 、M2の駆動回路の電源電圧を $V_{\rm dd_l}$ 、 $-V_{\rm ss_l}$ とする。

図1(a)はトランジスタM1の駆動回路として抵抗フィード形を用いている $^{(5)}$ 。図中に示すように0から $V_{dd}$ まで変化する理想的な出力電圧波形を得るためには,しきい値電圧近傍付近から電源電圧 $V_{dd}$ までの大電圧振幅をゲート電圧に供給する必要があり,その結果, $V_{dd}$ ,は $V_{dd}$ とほぼ等しい電圧値となる。したがって,スイッチング増幅回路の効率に対し,駆動回路まで含めたD級増幅器全体の効率は大きく低下する。

一方、図1(b)はM1の駆動回路として、ブートストラップ形を用いている。同様に0から $V_{\rm dd}$ まで変化する理想的な出力電圧波形を得るためには、M1のゲート電圧はしきい値電圧近傍から電源電圧 $V_{\rm dd}$ までの大電圧振幅を供給する必要があるが、電圧を充放電する容量を用いることによって、 $V_{\rm dd_h}$ を $V_{\rm dd}$ と比べ低下させることができる。その結果、駆動回路まで含めたD級増幅器全体の効率を大きく改善する。

#### 2.2 動作原理

図1(b)の回路図を用いてブートストラップ形駆動回路を備えたGaN D級増幅器の動作原理について述べる。M1がオフ状態/M2がオン状態の場合,M1の駆動回路を構成するトランジスタとダイオード間の電圧は低下し,ダイオードはオン状態となる。したがって,容量では電荷が充電される。一方,M1がオン状態/M2がオフ状態の場合,M1の駆動回路を構成するトランジスタとダイオード間の電圧は上昇し,ダイオードはオフ状態となる。したがって,容量からは電荷が放電され,抵抗を介してM1のゲート端子にVda程度の電圧が供給される。

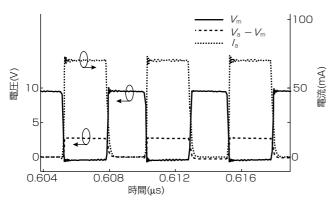

図2に電圧波形・電流波形のシミュレーション結果を示す。入力信号のスイッチング周波数は200MHz, Vddは10Vとした。電荷を充放電する容量を備えたブートストラップ形駆動回路を用いることによって,入力信号に追従して正常にスイッチング動作することを確認した。

(b) ブートストラップ形駆動回路(提案)

図1. GaN D級増幅器の簡易回路図

図2. 電圧波形・電流波形のシミュレーション結果

# 3. 試作結果

## 3.1 GaN D級增幅器

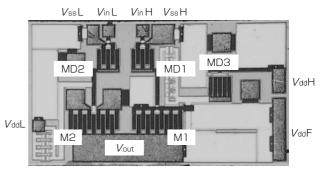

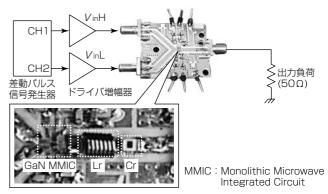

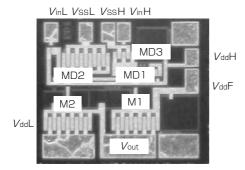

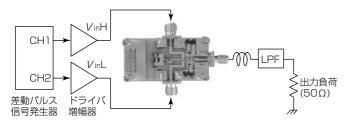

図3に試作したGaN D級増幅器集積回路のチップ写真,図4にこのチップを実装した評価基板を含む評価系ブロック図をそれぞれ示す。集積回路は図1(b)の出力部に接続している帯域通過フィルタを除く全素子を内蔵しており,チップサイズは1.6×0.9(mm)である。入力信号は差動パルス信号発生器から出力し,市販ドライバ増幅器によって所望の入力電圧に増幅した後,試作したGaN D級増幅器に入力する。出力負荷は50Ωとした。

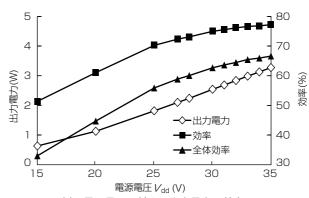

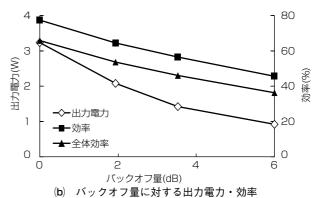

図5に試作したGaN D級増幅器の評価結果を示す。入力信号として周波数465MHz,デューティ比0.5のパルス波を用いた。図5(a)は電源電圧 Vddを15~35Vまで変化させた際の出力電力,効率(駆動回路除く)と全体効率(駆動回路含む)の評価結果、図5(b)は電源電圧35V時のバックオフ量に対する出力電力,効率(駆動回路除く)と全体効率(駆動回路含む)の評価結果をそれぞれ示す。電源電圧35V時に出力電力3.3W,全体効率66.6%の良好な特性を得ており、また6dBバックオフ時でも全体効率36.3%を達成した。この評価結果はブートストラップ形駆動回路を備えたGaN D級増幅器の有意性を示すものであり、今後の移動体通信用デジタル送信機の実現に向けた有効な回路手法の1つであることが確認できた。

## 3.2 GaNエンベロープ増幅器

次に、提案のブートストラップ形駆動回路を備えたD級 増幅部に低域通過フィルタを接続したエンベロープ増幅器 を試作した。エンベロープ増幅器は、高周波増幅器の電源 電圧をエンベロープ信号に追従させ変化させることによって大バックオフ時の高効率化を図るエンベロープトラッキング増幅器に用いられる回路である。従来、エンベロープ増幅器にはCMOSプロセスが用いられてきたが<sup>(6)(7)(8)</sup>、GaNを採用することによって、小形かつ高速・高効率・高出力なエンベロープ増幅器が実現可能となる。

図6に試作したGaNエンベロープ増幅器集積回路のチップ写真,図7にこのチップを実装した評価基板を含む評価

図3. 試作したGaN D級増幅器集積回路のチップ

図4. 評価系ブロック図

(a) 電源電圧に対する出力電力・効率

図5. GaN D級増幅器の評価結果

系ブロック図をそれぞれ示す。集積回路は図3と同様に出力部に接続する低減通過フィルタ(LPF)を除く全素子を内蔵しており、チップサイズは1.1×1.0(mm)である。入力信号は差動パルス信号発生器から出力し、市販ドライバ増幅器によって所望の入力電圧に増幅した後、試作したエン

図 6. 試作したGaNエンベロープ増幅器集積回路のチップ

図7.評価系ブロック図

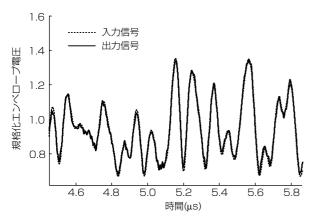

図8. 規格化エンベロープ電圧波形

表 1. エンベロープ増幅器の性能比較

| エンベロープ 増幅器 | 信号帯域幅<br>(MHz) | 全体効率<br>(%) | 最大出力電圧<br>(V) | 出力電力<br>(W) |

|------------|----------------|-------------|---------------|-------------|

| 参考文献(6)    | 5              | 84          | 32            | 27          |

| 参考文献(7)    | 10             | 70          | 28            | 26          |

| 参考文献(8)    | 15             | 79          | 2.4           | 0.9         |

| 参考文献(2)    | 20             | 64          | 20            | 1.9         |

| 今回試作       | 20             | 73          | 28            | 3.3         |

ベロープ増幅器に入力する。出力負荷は50Ωとした。

図8は市販シミュレータによって生成した信号帯域幅20MHz,ピーク対平均電力比7.7dBのLTE(Long Term Evolution)信号入力時の規格化エンベロープ電圧波形,表1はエンベロープ増幅器の性能比較をそれぞれ示す。図8から、評価した規格化出力波形は入力波形とほぼ重なっており、試作したエンベロープ増幅器が20MHzのLTE信号に追従できていることを確認した。また試作したエンベロープ増幅器は、全体効率73%、出力電力3.3Wを達成しており、小形かつ高速・高効率・高出力なエンベロープ増幅器の実現を確認した。

## 4. む す び

ブートストラップ形駆動回路を備えたGaN D級増幅器,及びGaNエンベロープ増幅器をそれぞれ試作した。評価の結果,ともに良好な高周波・高効率・高出力特性を実現し,移動体通信用デジタル送信機の実現に向けた有効な手法の1つであることを確認するとともに,GaNデバイスの新たな展開の可能性を示した。

なお、この内容は、University of California、San Diegoが組織するCenter for Wireless Communicationsとの共同研究プロジェクトによる成果である。

# 参考文献

- (1) Motoi, K., et al.: Digital doherty transmitter with envelope  $\Delta\Sigma$  modulated class-D GaN power amplifier for 800MHz band, IEEE Inter. Microwave Symp.,  $1{\sim}4$  (2014)

- (2) Shinjo, S., et al.: High Speed, High Analog Bandwidth Buck Converter Using GaN HEMTs for Envelope Tracking Power Amplifier Applications, IEEE Topical Conf. on Wireless Sensors and Sensor Networks, 13~15 (2013)

- (3) Hong, Y. P., et al.: High efficiency GaN switching converter IC with bootstrap driver for envelope tracking applications, IEEE Radio Frequency Integrated Circuits Symp., 353~356 (2013)

- (4) Nakamizo, H., et al.: Over 65% PAE GaN Voltage-Mode Class D Power Amplifier for 465MHz Operation Using Bootstrap Drive, IEEE Radio Wireless Symp., TU3P-8 (2015)

- (5) Shinjo, S., et al.: High Speed Buck Converter Using GaN HEMTs for Envelope Tracking Applications, IEEE Topical Symp. on Power Amplifiers for Wireless Communications, Sessin4-1 (2012)

- (6) Yan, J. J., et al.: A High Efficiency 78MHz GaN Envelope Tracking Power Amplifier, IEEE Compound Semiconductor Integrated Circuit Symp., 1~4 (2012)

- (7) Hsia, C., et al. Digitally assisted dual-switch high-efficiency envelope amplifier for envelopetracking base-station power amplifiers, IEEE Trans. Microw. Theory and Tech., 59, No.11, 2943 ~2952 (2011)

- (8) Bathily, M., et al.: Design Flow for High Switching Frequency and Large Bandwidth Analog DC/DC Step-Down Converters for a Polar Transmitter, IEEE Trans. Power Electronics, 27, No.2, 838~847 (2012)