**MITSUBISHI**

*Changes for the Better*

家庭から宇宙まで、エコチエンジ

# 三菱電機技報

5

2014

Vol.88 No.5

## 「パワーデバイス」

## 目 次

### 特集「パワーデバイス」

|                                |    |

|--------------------------------|----|

| パワーデバイス技術の現状と展望                | 1  |

| ゴーラブ マジュムダール                   |    |

| パワーデバイス技術の現状と展望                | 2  |

| 眞田 享・佐藤克己                      |    |

| 高性能・高破壊耐量第7世代パワーチップ技術          | 7  |

| 鈴木健司・増岡史仁・久我正一                 |    |

| 超小型DIPIPM "Ver.6シリーズ"          | 11 |

| 加藤正博・柴山祥吾                      |    |

| 高信頼性1,200V HVIC "M81738FP"     | 15 |

| 羽生 洋・山本雅裕                      |    |

| 双方面のレベルシフト機能を搭載した1,200V HVIC技術 | 19 |

| 吉野 学・羽生 洋                      |    |

| 高しきい値電圧SiC-MOSFET製造技術          | 23 |

| 谷岡寿一・古橋壯之・海老池勇史                |    |

| SiCパワーモジュール化技術                 | 27 |

| 大月高実・井上貴公・玉木恒次・大開美子            |    |

| 高周波用ハイブリッドSiCモジュール             | 31 |

| 宮崎裕二                           |    |

| 3.3kV耐圧SiC-MOSFETの低抵抗化技術       | 35 |

| 濱田憲治・日野史郎・木谷 剛                 |    |

| 高耐熱パワー半導体モジュールパッケージング要素技術      | 39 |

| 日野泰成・長谷川 澄・山田浩司・巽 裕章・横村伸緒・畠中康道 |    |

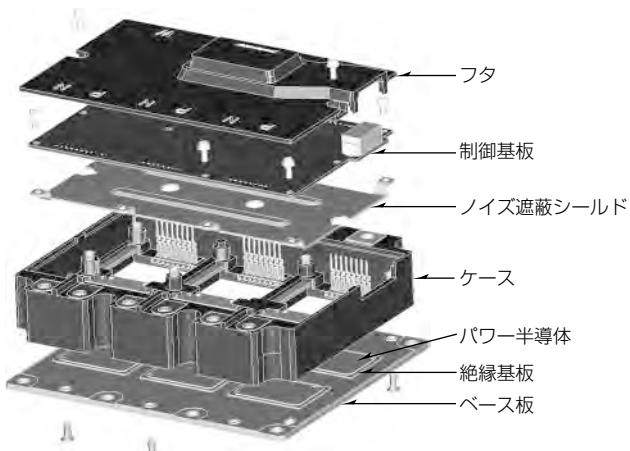

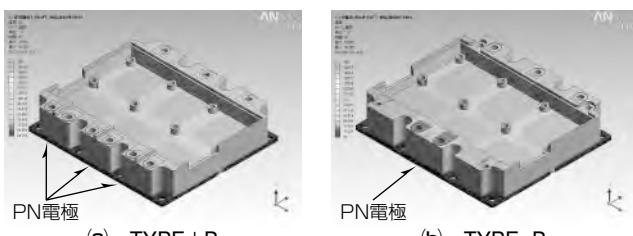

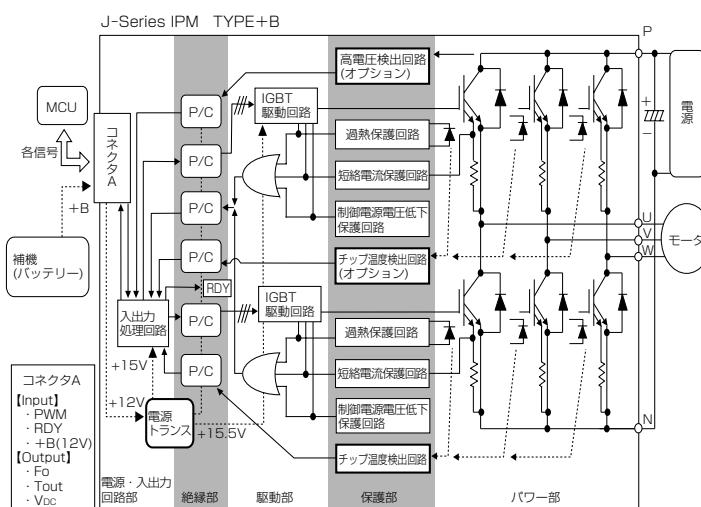

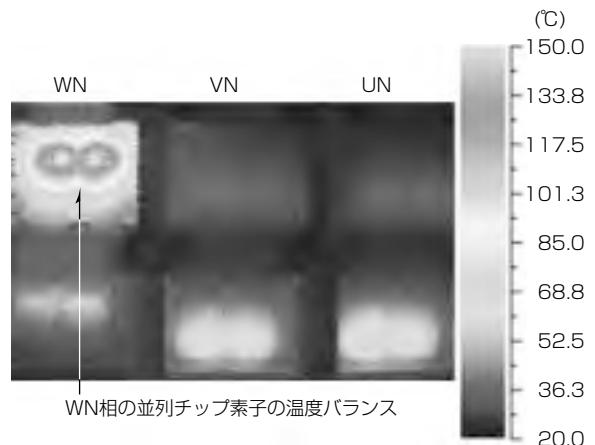

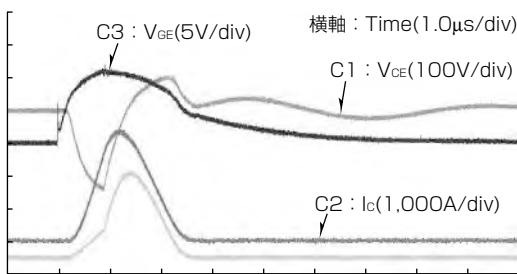

| 自動車用パワー半導体モジュール                |    |

| "J1シリーズ"のパッケージ技術               | 43 |

| 吉松直樹・碓井 修・井本裕児・石山祐介            |    |

| 次世代自動車用パワー半導体モジュール"J1シリーズ"     | 47 |

| 石原三紀夫・日山一明・川瀬達也・山田一樹・中野俊哉      |    |

| 自動車用パワー半導体モジュール                |    |

| "JシリーズIPM/T-PM"                | 51 |

| 齊藤省二・飯塚 新・ハリッド・フセイン・波多江慎治      |    |

### Power Device

#### Status Quo and Prospects of Power Semiconductor Technologies

Gourab Majumdar

#### Present State and Prospect of Power Semiconductor Device Technologies

Toru Sanada, Katsumi Satoh

#### 7th Generation Power Chip Technologies of High Performance with Wide Safe Operating Area

Kenji Suzuki, Fumihito Masuoka, Shioichi Kuga

#### Super Mini DIPIPM "Ver.6 Series"

Masahiro Kato, Shogo Shibata

#### High Reliability 1,200V HVIC "M81738FP"

Yo Habu, Masahiro Yamamoto

#### Technology of Bi-directional High Voltage Level-shifting for 1,200V HVIC

Manabu Yoshino, Yo Habu

#### Fabrication Technology of High Threshold Voltage SiC-MOSFETs

Toshikazu Tanioka, Masayuki Furuhashi, Yuji Ebiike

#### Technologies for SiC Power Module

Takami Otsuki, Takahiro Inoue, Koji Tamaki, Yoshiko Obiraki

#### Hybrid SiC Module for High Frequency Application

Yuji Miyazaki

#### Low On-resistance SiC-MOSFET with Blocking Voltage of 3.3kV

Kenji Hamada, Shiro Hino, Takeshi Kitani

#### Packaging Technologies for High Temperature Power Modules

Yasunari Hino, Shigeru Hasegawa, Koji Yamada, Hiroaki Tatsumi, Nobuo Yokomura, Yasumichi Hatanaka

#### Packaging Technologies of Power Module "J1 Series" for EVs and HEVs

Naoki Yoshimatsu, Osamu Usui, Yuji Imoto, Yusuke Ishiyama

#### Next Generation Power Module for EVs and HEVs "J1 Series"

Mikio Ishihara, Kazuaki Hiyama, Tatsuya Kawase, Kazuki Yamada, Toshiya Nakano

#### Power Module "J Series IPM/T-PM" for EV and HEV

Shojo Saito, Arata Iizuka, Khalid Hussein, Shinji Hatae

### 特許と新案

|                          |    |

|--------------------------|----|

| 「電力半導体装置」「半導体装置及びその製造方法」 | 55 |

| 「パワーモジュールおよびその製造方法」      | 56 |

### 表紙：パワーデバイス

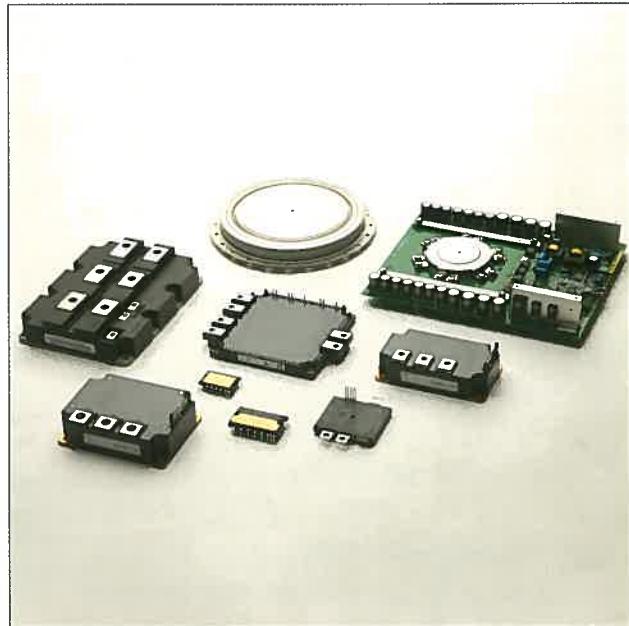

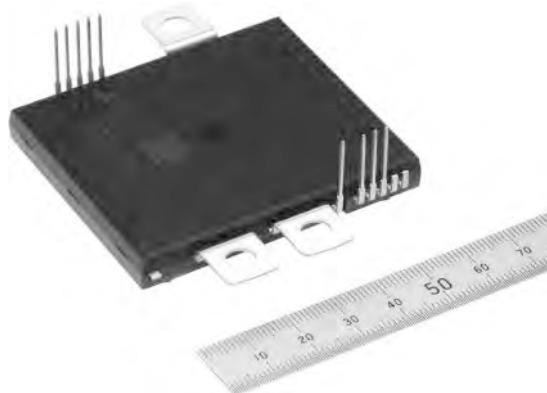

三菱電機は、家電、産業、電力、電鉄、自動車等、幅広いパワーエレクトロニクス製品に向けてその核となるパワーデバイスを供給している。幅広い製品ラインアップをそろえ、顧客の期待に応えられるよう、優れた性能で喜ばれる製品開発を進めている。表紙の写真は代表製品である。

## 巻/頭/言

## パワー・デバイス技術の現状と展望

Status Quo and Prospects of Power Semiconductor Technologies

ゴーラブ マジュムダール

Gourab Majumdar

地球人口の増加、デモグラフィの変化、新興国の経済発展などに伴い、エネルギー需要は増加の一途である。米国のシェールガス革命が大きなエネルギーソリューションとして注目を浴びているが、温暖化のソリューションにはなり得ない。両者のソリューションとして新エネルギーと言われる風力・太陽光などの再生可能エネルギーにも注目が集まっている。加えて、エネルギーの効率的な運用も重要な要素になっている。2次エネルギーの4割以上が電力として幅広く利用されており、電力エネルギーの有効利用については、パワーエレクトロニクス(PE)電力変換技術の発展が必要不可欠である。

三菱電機では、省エネルギー化に貢献する様々なPE装置・機械のみならず、これら用途の核となるパワー・デバイスを市場に供給し、持続的な発展を視野に研究開発を進めている。特にIGBT(Insulated Gate Bipolar Transistor)モジュール及び最適な保護・駆動機能を含む周辺回路を取り込んだインテリジェントパワーモジュール(Intelligent Power Module:IPM)の性能・機能向上を進めている。これらパワーモジュールは、半導体チップの構造・プロセス設計だけでなく、高温化・高信頼性を追求したパッケージ技術もあわせて重要な技術要素を基に成り立っている。Si-IGBTチップ技術はプレーナゲートのセル構造から始まり、トレンチセル構造、CSTBT(キャリア蓄積層を形成したIGBT)を経て、極限薄ウェーハ技術適用によって高性能化を進めた第7世代CSTBTに至っている。一方、Si(Silicon)高速形ダイオードについては極限薄ウェーハ技術と裏面パターンニング技術を複合化した新コンセプトの

RFC(Relaxed Field of Cathode)技術で低損失と高スイッチング性能を実現している。

近年、パワー半導体の素材をSiからSiC(Silicon Carbide)ウェーハに代えることで、高温・高耐圧化でかつ高速スイッチング動作に優れたデバイスの実現を目指してパワーMOSFET(Metal Oxide Semiconductor Field Effect Transistor)やパワーSBD(Schottky Barrier Diode)チップを適用した600V～3.3kV／15～1,200A定格のパワーモジュールやIPMの開発・製品化を進めている。これら新デバイスの応用によって電力変換損失の大幅な低減やパワーモジュール及びその応用システムの飛躍的小型・軽量化が実現可能となりパワーエレクトロニクス機器の大幅な進化に寄与し、Siデバイスの適用が困難な用途を新たに創生する可能性を持つ。例えば、高周波AC／AC変圧器リンクを組み込んだDC／DC変換装置適用のHV・MV・LVDC送電ネットワークや高周波電力変換制御適用の太陽光発電システム、又は、高温動作環境のHEV・EV用トラクション・システムといった応用である。そのため応用開発・設計側とデバイス開発側の強い連携が期待される。

機能の観点からは、IPMの進化によって、デジタル・アナログ混在の高機能HVIC・LV-ASIC技術や周辺回路技術を搭載した自己動作診断機能や上位制御回路との高度な通信機能及び周辺回路の内蔵化など、更なるユーザーフレンドリーな製品を目指していく。このように幅広い応用分野で使用されるパワー・デバイスは、チップ・パッケージ・制御回路の集積化など幅広い技術を駆使することで今後の安定した社会の発展に寄与していく。

## 巻頭論文

## パワーデバイス技術の現状と展望

真田 享\*

佐藤克己\*\*

Present State and Prospect of Power Semiconductor Device Technologies

Toru Sanada, Katsumi Satoh

## 要 旨

90%以上を輸入に頼っている日本の1次エネルギーは、その40%以上が電気エネルギーに変換され、利用されている。1次エネルギーから電気エネルギーへの変換や、電気エネルギーから使用機器に適合した電気エネルギーへ形態を変換するパワーエレクトロニクス(PE)技術は、省エネルギー化に貢献している。低炭素社会の実現に向けて、PE機器の一層の高性能化・高機能化に対する期待がますます高まっている<sup>(1)(2)</sup>。

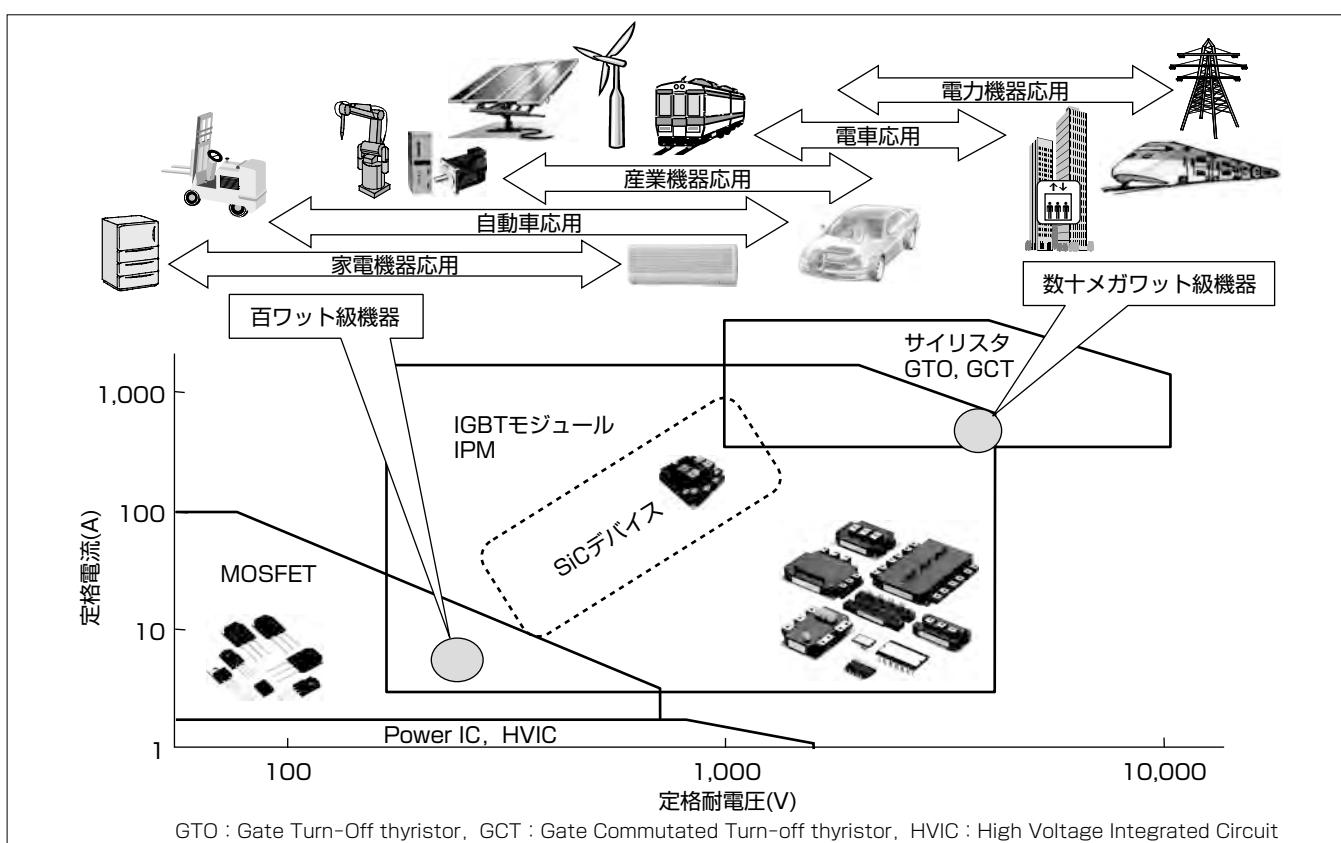

近年、PE機器のキーパーツであるパワーデバイスにおいて、バイポーラデバイスの優れた通電性能を持つIGBT(Insulated Gate Bipolar Transistor)とモジュール化技術と組み合わせたパワーモジュールは、百ワット級から数十メガワット級までの幅広いPE機器出力容量に対応でき、家電から自動車、産業、電車、電力までの分野で使われている。

三菱電機では、それぞれの分野の市場ニーズに応えるために、パワーモジュールは高効率・大容量化、小型・軽量化、高信頼度化、高機能化を柱とした技術開発を多方位から進めている。材料では、低損失で高速動作可能なSiC(Silicon Carbide)ウェーハを用いたSBD(Schottky Barrier Diode)の実用化を始めた。製品では、第7世代の600V IGBTとそれを組み立てる技術を開発し、制御・保護回路と最適に組み合わせたIPM(Intelligent Power Module)の量産を始めている。

SiC-MOSFET(Metal Oxide Semiconductor Field Effect Transistor)の実用化開発や7世代IGBTのシリーズ化開発、高性能パッケージの開発を進めており、これらの技術を搭載した先進パワーモジュールが更なるPE機器の進化に寄与するものと期待されている。

## 現在のパワーデバイスの容量と応用機器の関係

定格耐電圧が数百ボルトから数千ボルト、定格電流が数アンペアから数千アンペアの大きな容量領域をカバーするIGBTモジュールは、社会インフラの一翼を担う電力機器や電車応用機器、産業機器、日常生活に欠かせない自動車機器、家電機器等に使用されている。また、風力発電機器や太陽光発電機器等の再生エネルギー機器にも使用されており、適用範囲がますます拡大している。

## 1. まえがき

環境維持・改善のための低炭素社会を目指した動きに加え、1次エネルギーの90%以上を輸入に頼る日本では、エネルギーの有効利用が重要課題であり、社会インフラを支える電気エネルギーの生成、備蓄、輸送(送配電)、消費を支えるパワーエレクトロニクス(PE)技術とPEを支えるパワーデバイスに注目が集まっている。

1次エネルギーから2次エネルギーである電気エネルギーに変換するPE機器は、数十ワットから数十メガワットまでの容量で幅広く存在している。パワーデバイスは、PE機器の容量に合わせて使い分けされており、100ワット級以下の小容量帯ではMOSFETが、メガワット級の大容量帯ではサイリスタやGCTが、100ワット級から数メガ

ワット級までの広範囲にわたる中容量帯では、IGBTモジュールが一般的に使用されている。

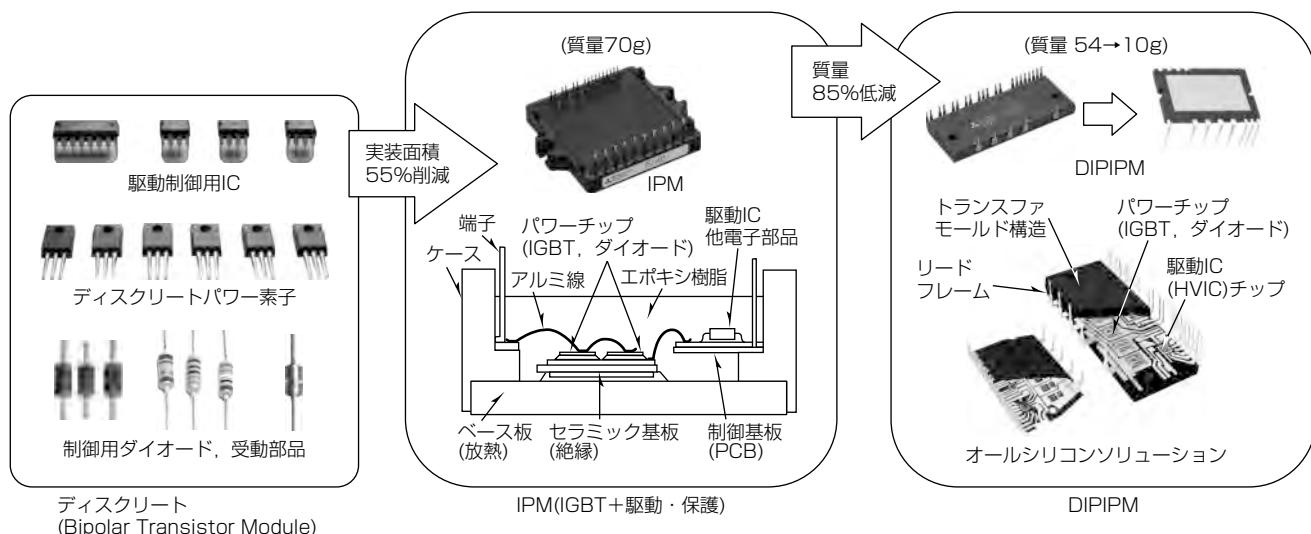

PE機器の小型・軽量化要求に応えて来たパワーデバイスのディスクリートパワーデバイスからパワーモジュールへの進化を図1に示す。1980年頃までのPE機器には、ディスクリート形状のパワーデバイスが使用されていたが、その後バイポーラデバイスの優れた通電性能を持つIGBTを中心とするデバイスとして、ブリッジ構成や並列構成を内蔵するモジュール化技術によって、さらには、IGBTモジュールに保護・駆動回路を内蔵したIPM技術<sup>(3)</sup>、良好な信頼性と生産性を提供するトランスマウルド技術によって、小型・軽量化が進められてきた。

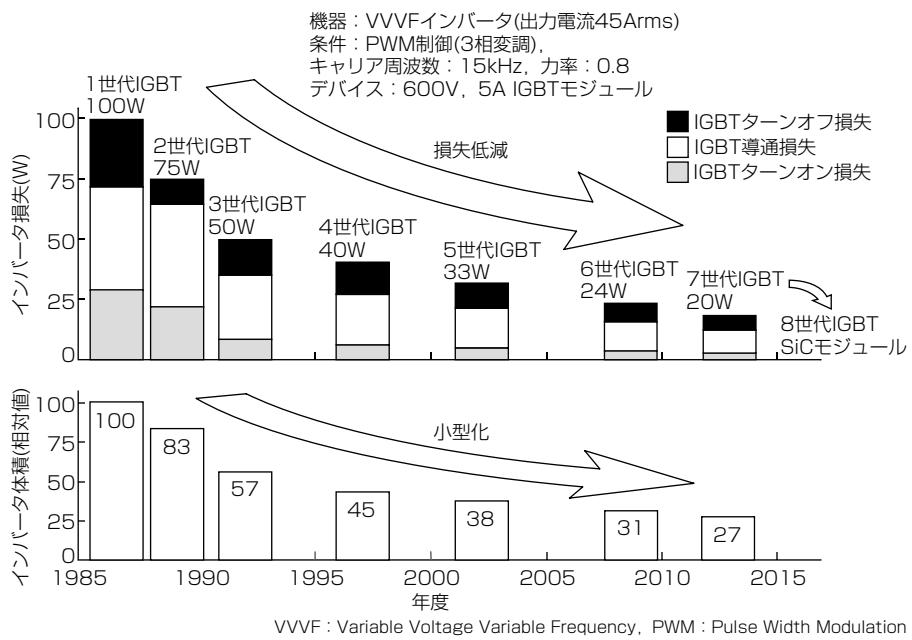

図2にIGBTモジュールの進化に伴ったPE機器の小型化の推移を示す。1980年代半ばの第1世代IGBT搭載モジュ

図1. パワーモジュールの進化

図2. IGBTの進化とPE機器の小型化の推移

ールに対して、最新の第7世代IGBT搭載モジュールでは、損失が5分の1まで低減改善され、インバータを始めとするPE機器の小型・軽量化に貢献している。今後も高効率・大容量化、小型・軽量化、高信頼度化、高機能化に向けた製品開発を進めていく。

本稿では、パワーデバイス技術の現状と展望について述べる。

## 2. パワーモジュールの現状

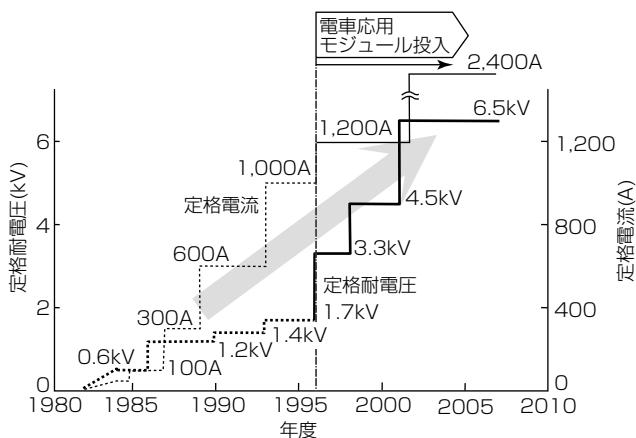

パワーデバイス(チップ)は、電流を流しているオン状態で“抵抗がゼロ(通電損失ゼロ)”，電流を遮断しているオフ状態で“抵抗が無限大(遮断損失ゼロ)”“スイッチング動作が瞬時(スイッチング損失がゼロ)”となる理想的なスイッチを目指して損失改善が続けられている。加えて、非定常動作でも機能を維持し応用機器との協調性を高めるために、安全に動作可能な電流・電圧領域(安全動作領域(Safety Operation Area: SOA))の拡大改善が進められている。損失の低減改善とSOAの拡大改善は、背反関係にあることから、背反関係の改善がパワーデバイスの最大の技術課題であり、その解決策がモジュールの大容量化や小型・軽量化に大きく影響する。図3はパワーモジュールの大容量化の変遷である。これまでには、電車応用が大容量化を牽引

図3. パワーモジュールの大容量化の変遷

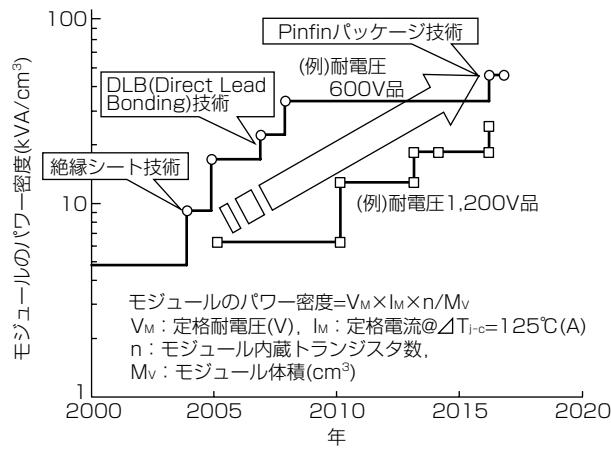

図4. トランスマールド型パワーモジュールの制御容量密度の変遷

(けんいん)してきたが、新エネルギー関連への適用や電力系統応用への適用が検討され始めるなど、多用途で大容量化への期待が高まっている。図4はモジュールの小型・軽量化の指標であるモジュールの制御容量密度の変遷を示しており、小型・軽量化に向けた取組みが継続的に進められている。中でも、小型・軽量化を最優先の技術課題とするPE機器では、低損失で小型・軽量化を可能にするSiC-SBDとSi-IGBTを混載したハイブリッドモジュールが適用され始めている。

## 3. パワーチップ

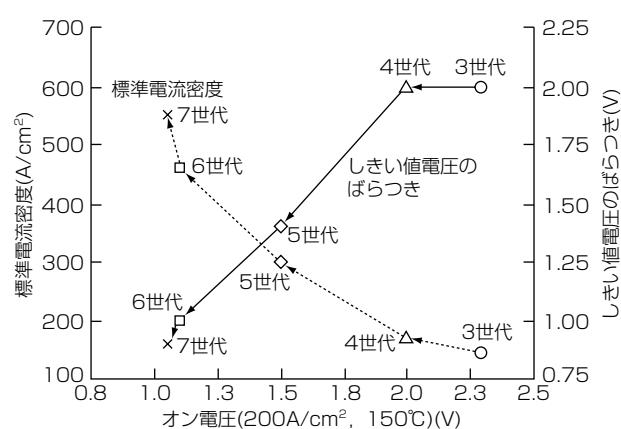

チップは電流を流す有効領域を、定格耐電圧を安定的に保持するための無効領域(終端構造)が取り囲む構造であるため、チップの小型化には両領域の縮小技術が必要になる。有効面積の縮小には、先に述べた背反特性を改善する必要がある。これまでにトレンチ構造技術を含む微細化技術、キャリア分布の最適化構造設計技術、電流経路を短くするための薄ウェーハ化技術等が損失改善の手法として用いられてきた。並行して、通電性能を決める伝達特性の安定化技術(ばらつき改善)がSOA改善のために進められてきた。

図5は家電製品に応用される600V定格耐電圧のDIPIPMに搭載されるIGBTチップの主要特性値の変遷を示す。コレクタ・エミッタ間飽和電圧( $V_{CE(sat)}$ 、オン電圧とも言う)を低減しながら、伝達特性を示すしきい値電圧( $V_{GE(th)}$ )のばらつきを低減させることでSOAを確保しながら制御電流密度を高めています。

耐電圧特性は最重要性能の一つであり、終端構造はその品質を決定する。当社では、これまで、ガードリングにFLR(Field Limiting Ring)を組み合わせた終端構造を踏襲してきたが、IGBTチップの第7世代化に当たって、終端構造の改善による無効領域の縮小にも取り組み、最新の微細加工技術を適用した新規終端構造(VLD(Variation of Lateral Doping)構造)を開発した。新規終端構造の適用効果を従来構造と比較して表1に示す。新規終端構造は耐電

図5. 600V定格耐電圧のIGBTチップの主要特性値の変遷

表1. 新規終端構造の適用効果

| 世代   | 終端構造       | 終端領域幅(μm)        | 有効面積率(%) | 備考                                                                     |

|------|------------|------------------|----------|------------------------------------------------------------------------|

| ~6世代 | ガードリング+FLR | 450              | 77       |                                                                        |

| 7世代  | VLD        | 230<br>(49%縮小改善) | 84       | <p>ゲート電極パッド<br/>無効(終端)領域<br/>(電圧阻止)<br/>有効領域<br/>(電流通電)<br/>( )は機能</p> |

・有効面積率 =  $\frac{\text{有効領域}}{\text{チップ総面積}}$

= 有効面積 + 無効面積 + ゲート電極パッド面積

図6. 600V, 10A IGBTチップの特性

圧安定性を高めながら、無効領域の半減を実現している。

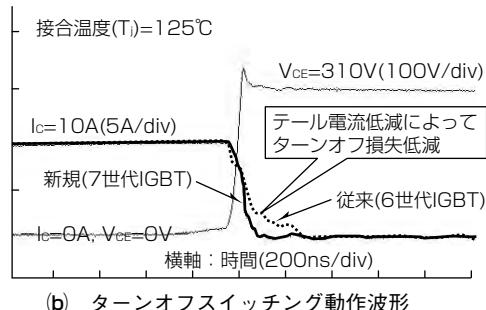

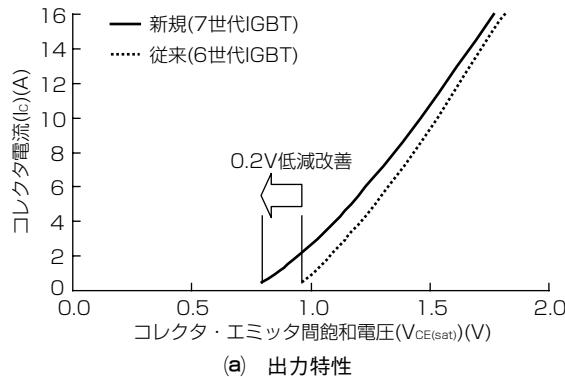

背反関係改善及び無効領域縮小の両技術を統合した最新の7世代IGBTチップ<sup>(4)</sup>は、600V DIPIPIMに搭載されている。図6はDIPIPIMに搭載の600V IGBTの出力特性とターンオフスイッチング動作波形であり、従来品と比較して損失が改善されていることが読み取れる。現在、定格耐電圧1,200Vから6.5kVまでの7世代IGBTのシリーズ化を進めている。

更なる性能改善に向けて、物理限界に迫る究極の薄さのパワーチップ技術開発やこれまで回路を形成することがほとんどなかった裏面にも回路を形成する設計・プロセス技術の開発を進めている。これらの技術はIGBTとともに使用するダイオードの特性改善やIGBTとダイオードを集積化した逆導通型IGBTの実現にも寄与する。

#### 4. パワーモジュール

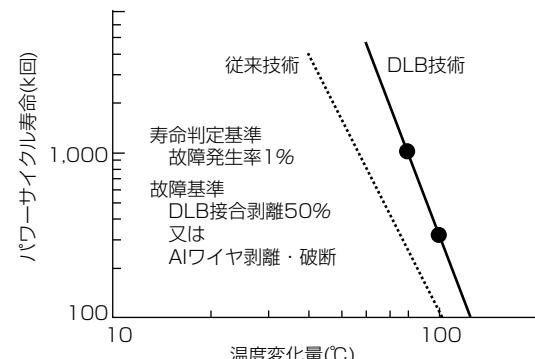

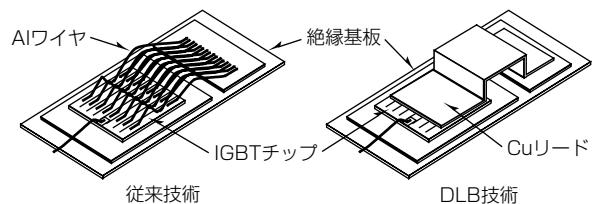

パワーモジュールは小型・軽量化に向け、①高温度耐性のチップ・パッケージ間接合技術、②発熱するチップの冷却を高める低熱抵抗設計技術の開発が進められている。従来、チップ上面の電極とパッケージ電極間はアルミニウムワイヤ接続が用いられてきたが、新たな接続技術である

熱抵抗( $R_{th(j-W)}$ ) : 40%改善 → フットプリント : 20%低減

図8. Pinfinモジュール(冷却ピンフィン一体型パッケージ)

Cuワイヤ接合技術やDLB技術<sup>(5)</sup>等が用いられ始めた。図7はチップ上面電極とパッケージ電極間を直接はんだ付けるDLB技術を示している。DLB技術の採用によって接合面積を拡大でき、接合寿命を従来のチップ上面電極・パッケージ電極間アルミニウムワイヤ接続に比べて数倍改善している。

図8は冷却フィンとモジュールを一体化したPinfinモジュールである。一体化によってパッケージと冷却フィンを接続するためのグリスが不要となり、チップ・フィン間熱抵抗を約40%低減し、冷却性能が高まっている。この効果によって従来モジュールに比べてフットプリントを20%低減し、PE機器の小型化を実現できる。

更なる小型・軽量化を目指し、チップ下面電極とパッケージ電極をはんだ接合に代わり銀などを用いて接合する技術の開発を進めている。

大容量モジュールはIGBTチップを数十チップ多並列接

続して使用するため、チップ特性の均一化が求められるとともに多チップを均等に動作させるための電極配線設計技術や制御技術が必要になる。当社の大容量モジュールはモジュールの構造解析シミュレーション技術を構築し、最適活用することで配線構造やチップレイアウトを最適設計し、均一動作性や低ノイズ性を高めている。

加えて、動作診断機能や通信機能及び周辺回路の取り込みを図り、機能充実化を進めていく。

## 5. ワイドバンドギャップ半導体

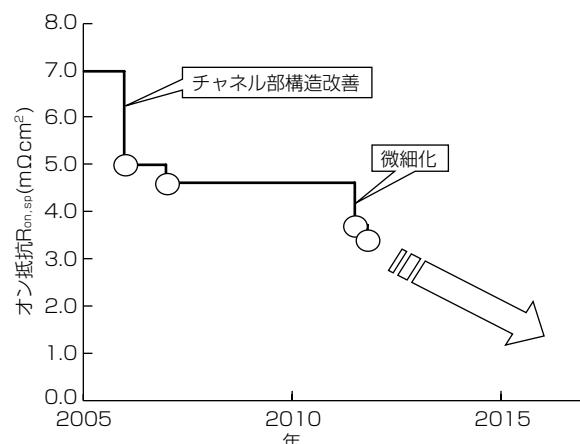

WBG(Wide Band Gap)半導体は絶縁破壊電界強度が大きいことから、電流を流す経路を短くできるなどの理由によって低損失化が可能であり、スイッチングスピードも速いことからPE機器を劇的に高性能化できると期待されている<sup>(6)</sup>。WBG半導体にはSiC以外にもGaN(Gallium Nitride), Ga<sub>2</sub>O<sub>3</sub>(Gallium(Ⅲ)oxide), AlN(Aluminum Nitride), ダイヤモンド等もあるが、ウェーハの開発状況やデバイス実現のためのプロセス技術の構築状況等の観点から、現在はSiCデバイス開発に注力している。これまで600Vから1,700VまでのSiC-SBDチップのシリーズ化を行い、Si-IGBTと組み合わせたハイブリッドモジュールを製品化している。図9は1,200V SiC-MOSFETのオン抵抗の進化

の進化を示しており<sup>(7)</sup>、SiC-MOSFETの製品化を目指して、低損失化開発を進めている。

## 6. む す び

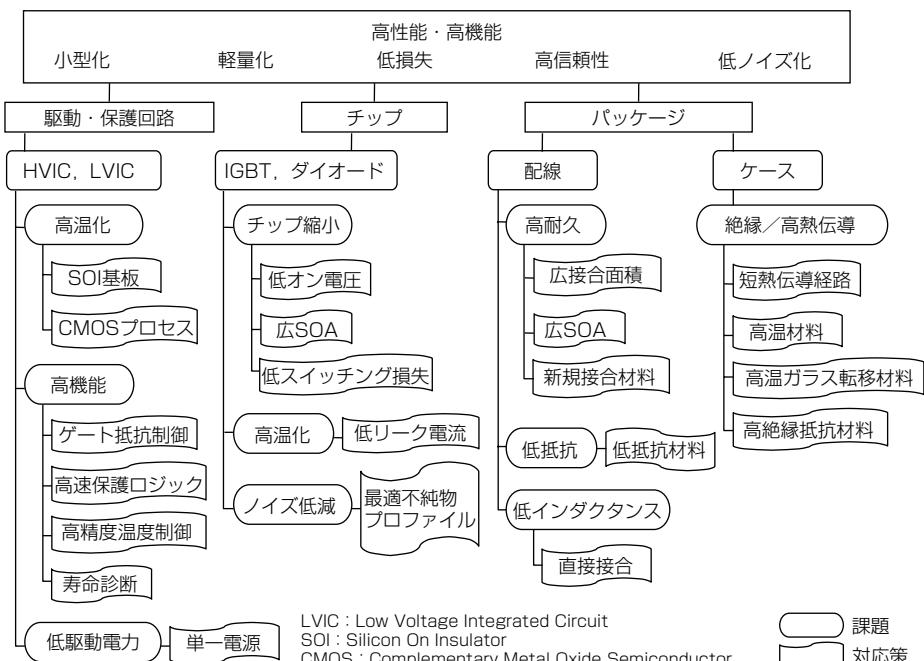

電気エネルギーを使う場合の様々な形態(電圧・電流・周波数)に対応して、発電・送電・変電・蓄電等の変換効率を高めるには、PE技術の進展が不可欠である。そのキー・コンポーネントであるパワーモジュールは信頼性・性能・体積・質量・価格等の市場要求に応えていくために、図10に示す要素技術及びその統合化技術を進歩させ、低炭素社会、持続可能な社会の実現に貢献していく。

## 参考文献

- (1) Sakuyama, M.: The role of IEEJ in development of secure energy infrastructure, The journal of IEEJ, 132, No.7, 400~404 (2012)

- (2) Yamamoto, M., et al.: Development of secured energy

図9. 1,200V SiC-MOSFETのオン抵抗の進化

図10. モジュール進化に必要とする技術

- infrastructure in Japan, ISPSD2013, 3~7 (2013)

- (3) Majumdar, G., et al.: A New Series of smart Controller, IEEE-IAS, 2, 1356~1362 (1989)

- (4) Haraguchi, Y., et al.: 600V LPT-CSTBT™ on Advanced Thin Wafer Technology, ISPSD2011, 68~71 (2011)

- (5) Ueda, T., et al.: Simple, Compact, Robust and High-performance Power module T-PM(Transfer-molded Power Module), ISPSD2010, 47~50 (2010)

- (6) 三菱電機ニュースリリース：三菱CNC対応ドライブユニット「MDS-DM2-SPHV3-20080」発売のお知らせ <http://www.mitsubishielectric.co.jp/news/2012/1029.html>

- (7) Yonezawa, Y., et al.: Low Vf and Highly Reliable 16kV Ultrahigh Voltage SiC Flip-Type n-channel Implantation and Epitaxial IGBT, IEDM Tech.Dig., 661~664 (2013)

鈴木健司\*

増岡史仁\*

久我正一\*

# 高性能・高破壊耐量第7世代パワーチップ技術

7th Generation Power Chip Technologies of High Performance with Wide Safe Operating Area

Kenji Suzuki, Fumihiro Masuoka, Shoichi Kuga

## 要旨

現在のSiパワーデバイスの中核を担っているパワーチップは、IGBT(Insulated Gate Bipolar Transistor)とダイオードである。地球環境問題への関心が高まる中で、太陽光・風力等の新エネルギー発電用途や、ハイブリッド・電気自動車等のエコカー向けに、市場が拡大している。三菱電機は、製品の省エネルギー性能向上につながる定常損失及びスイッチング損失の低減を実現するため、平面型IGBT、トレンチ型IGBT、電荷蓄積型IGBT(CSTBT(Carrier Stored Trench-gate Bipolar Transistor))、セル構造微細化第6世代IGBT、及び薄ウェーハダイオード等の各種のパワーチップを開発してきた。今回、更に高性能で高破壊耐量の第7世代パワーチップを開発した。

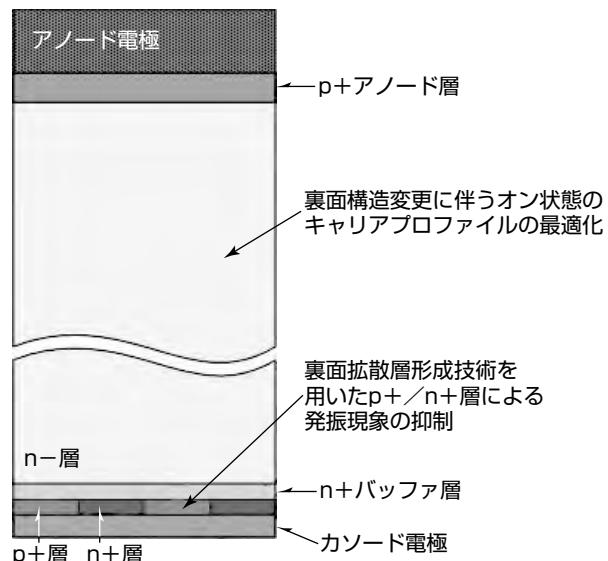

耐圧600V級第7世代IGBTは、当社として初めて極薄ウェーハ化プロセス技術を適用し、第6世代IGBTに比べ、性能指数FOM(Figure Of Merit)で1.8倍の高い性能を実現した。また、MOS(Metal Oxide Semiconductor)構造を最適化することで破壊耐量を改善した。第7世代ダイオードには、新しい裏面拡散層形成技術を開発し、RFC(Relaxed Field of Cathode)効果が得られる裏面構造を適用した。これによって、snap-off(電圧跳ね上がり)とそれに誘発される発振が抑制できる高リカバリーSOA(Safe Operating Area)性能を可能にし、前世代品よりも薄ウェーハ化することでFOM値2.7倍となる高性能ダイオードを実現した。これら第7世代パワーチップを各耐圧級の製品に順次展開する。

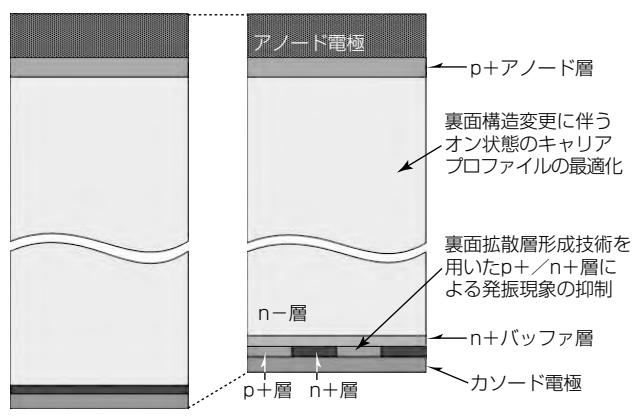

## 第7世代IGBTとダイオードの構造と特長

第7世代IGBTは、極薄ウェーハ化プロセスを用いたLPT(Light Punch-Through)構造による低損失化と、MOS構造の最適化による破壊耐量改善が特長である。また、第7世代ダイオードにはRFC効果を適用し、裏面拡散層形成技術を用いたカソード部のp+/n+層による発振現象の抑制と、カソード部p+/n+層によるオン状態でのキャリアプロファイルの最適化をしている。

## 1. まえがき

パワーモジュールに搭載されているIGBT、ダイオードの性能向上がパワーエレクトロニクスの発展には不可欠である。当社では、1980年代後半からIGBTでは、プロセスの微細化やCSTBT<sup>(1)</sup>などの低損失IGBT構造を開発してきた。また、ダイオードでは薄ウェーハ化やカソードプロファイルの最適化等による性能向上を行ってきた。

本稿では、更なる性能改善と高い破壊耐量を持つ極薄ウェーハ方式を適用した第7世代IGBTとRFC効果を適用した第7世代ダイオードの開発について述べる。

## 2. 第7世代IGBT

## 2.1 IGBTの性能向上<sup>(2)</sup>

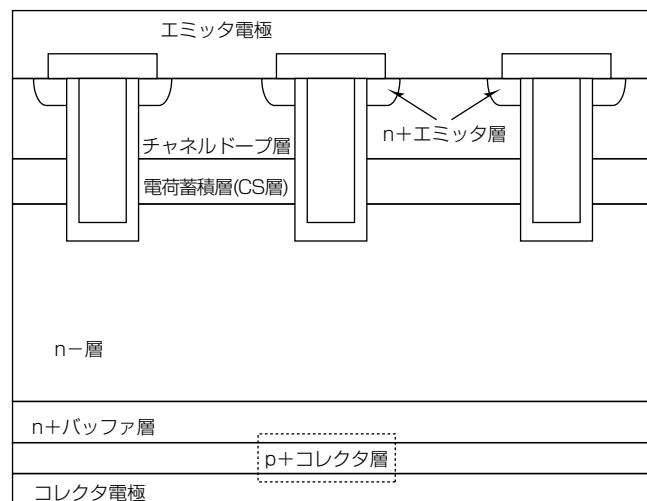

第1～第3世代IGBTは平面型で、セル構造を微細化することで特性の向上を図ってきた。第4世代からはトレンチ型を採用し、平面型IGBTのセル間に発生するJFET (Junction Field Effect Transistor) 抵抗成分をなくすることで、劇的な損失低減を実現した。また第5世代からは、チャネルドープ層の下に電荷蓄積層(CS層)を設け、ボンシャル障壁を発生させる、当社独自のCSTBT構造を採用した。これによって、オン状態でエミッタ側により多くのキャリアを残存させることができ、オン電圧の低減を実現した。第6世代ではトレンチゲートを狭ピッチ化し、キャリア蓄積効果を更に高め性能を上げるとともに、CS層を高エネルギー注入で形成することで、しきい値電圧のばらつき低減も実現した。

IGBTの性能はしばしば性能指数FOMで議論される。FOMはチップサイズを決める主要素であるコレクタ電流密度 $J_c$  ( $A/cm^2$ )、定常損失を決めるコレクター-エミッタ間飽和電圧(オン電圧) $V_{CE(sat)}$  (V)、ターンオフ損失 $E_{off}$  ( $mJ/A$ )の値を用いて式(1)で示される数値である。

耐圧1,200V級のIGBTの場合、第1世代IGBTのFOMを1にした場合、第6世代IGBTでは10以上になり、飛躍的な性能向上を実現している。

また、高温動作や高破壊耐量等の高い信頼性を実現するために、MOS構造だけではなく、終端構造や裏面構造にも改良を積み重ね、製品としての性能要求に応えてきた。

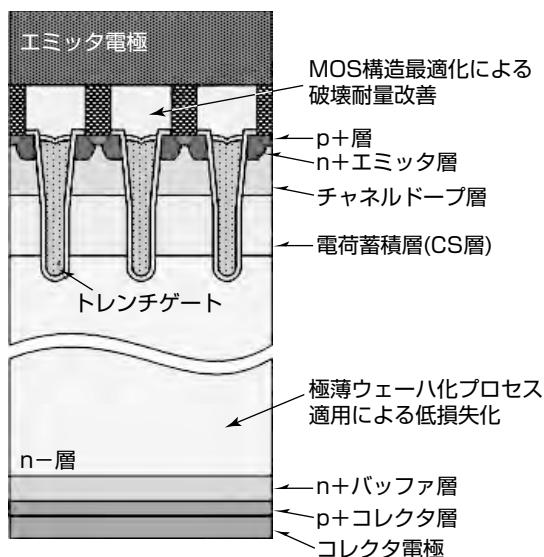

## 2.2 第7世代IGBTの構造の特徴<sup>(3)</sup>

図1に第6世代IGBTと第7世代IGBTの断面図を示す。耐圧600V級の第7世代IGBTは、極薄ウェーハ化プロセスを用いたLPT(Light Punch-Through)構造を適用することで、オン電圧とターンオフ損失のトレードオフ性能を改善した。同時に表面のn+エミッタ層とp+層の面積比率を変更し、MOS構造を最適化することで、飽和電流を抑

え、製品に必要な破壊耐量を確保できるようにした。

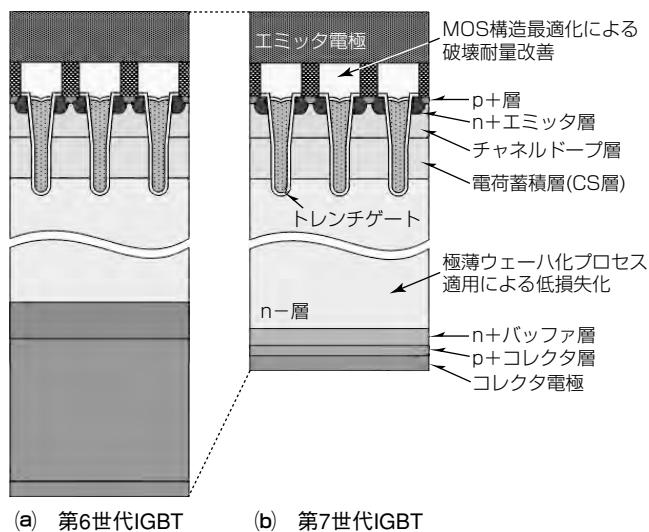

## 2.3 第7世代IGBTの電気特性

図2に、耐圧600V級の第6世代IGBTと第7世代IGBTの出力特性を示す。第7世代IGBTでは、LPT構造を採用しp+コレクタ層とn+バッファ層を低濃度に設計したことによって、第6世代IGBTよりもビルトイン電圧を低く抑えることが可能となっている。定格電流密度付近の500A/cm<sup>2</sup>で見た場合、第7世代IGBTは第6世代IGBTに比べて、オン電圧が0.1V以上改善されており、損失性能が優れている。また、第7世代IGBTではオン電圧とターンオフ損失のトレードオフを裏面コレクタ注入量で調整しており、クロスポイントが低く並列動作に適している。電子線照射などのライフタイム制御プロセスが不要で、Si内部に余分なトラップ準位を形成することがなくなるため、電気特性の長期安定性に優れ、高温・大電流での動作に適している。

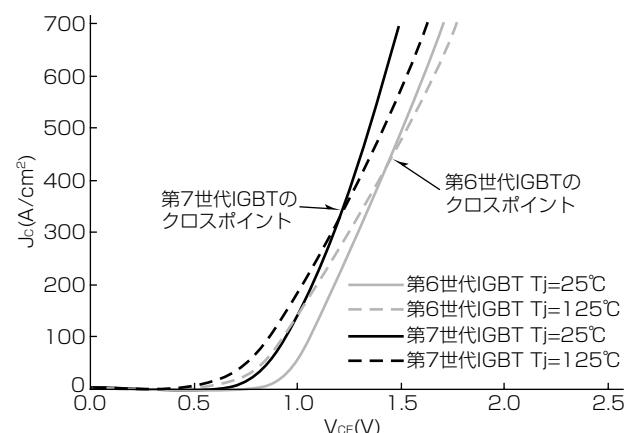

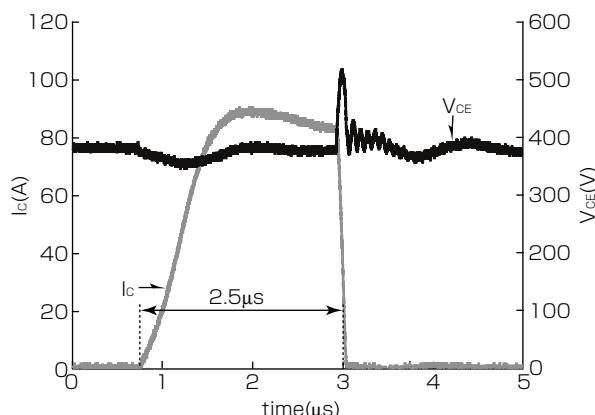

次に、図3に第6世代IGBT及び第7世代IGBTのターンオフ波形を示す。いずれも定格600V/10Aのチップを用いており、測定条件は、コレクタ-エミッタ間電圧 $V_{CE} = 300V$ 、

図1. 第6世代IGBTと第7世代IGBTの断面図

図2. 第6世代IGBTと第7世代IGBTの出力特性

図3. 第6世代IGBTと第7世代IGBTのターンオフ波形

図4. 第7世代IGBTのSCSOA波形

ゲート-エミッタ間電圧  $V_{GE} = 15V / 0V$ , コレクタ電流  $I_c = 10A$ , 温度  $T_j = 125^\circ C$  である。第7世代IGBTは第6世代IGBTに比べてテール電流が少なくなっている。これは、LPT構造のため、オン状態でのコレクタ側からのキャリアの注入を必要最小限に抑制できているからである。さらに、裏面コレクタ注入量を最適化し、第6世代IGBTと同様に、ターンオフ時の波形の発振も抑制させている。

図4に第7世代IGBTのSCSOA (Short Circuit Safe Operating Area)の波形を示す。MOS構造を極薄ウェーハでのLPT構造に最適なパターンに変更し、飽和電流の適正化及びラッチアップ耐量を向上させた。その結果、 $V_{CE} = 400V$ ,  $V_{GE} = 15V / 0V$ ,  $T_j = 125^\circ C$  の条件で、パルス幅が  $2.5\mu s$  まで非破壊となり、製品要求を満足できる高耐量性を確保した。

このように、第7世代IGBTは、第6世代IGBTと同等以上の破壊耐量を確保しつつ、対第6世代比でFOMが1.8倍の優れた性能を実現した。

### 3. 第7世代ダイオード

#### 3.1 ダイオードの性能向上<sup>(4)</sup>

従来型ダイオードでは、薄ウェーハ化プロセスの適用、

(a) 従来型ダイオード (b) 第7世代ダイオード

図5. 従来型ダイオードと第7世代ダイオードの断面図

及びカソードプロファイルの最適化を行うことで、順方向電圧降下  $V_F$  を低減してきた<sup>(5)</sup>。ダイオードもIGBTと同様に、低  $V_F$  化にはウェーハの薄厚化が有効であるが、リカバリー時のsnap-offに対する余裕度を削ることになり、素子破壊のリスクが高くなってしまう。これを回避するためには、カソード側のキャリアを制御して、リカバリー時のsnap-offを抑制することがキーポイントの一つである。そこで、今回薄ウェーハ化プロセスと裏面パターンニングプロセスを組み合わせた裏面拡散層形成技術を適用することによって、高性能第7世代ダイオードを開発した。

図5に従来型ダイオードと第7世代ダイオードの断面図を示す。第7世代ダイオードは、カソード側に部分的に  $p+$  層を持つ構造となっており、高電圧 ( $V_{CC}$ )、高インダクタンス ( $L_s$ )、低電流密度 ( $J_A$ )、高di/dtといった、snap-off及びそれに続く発振現象を引き起こしやすい厳しいリカバリー条件下でも、電子と正孔をカソード側に滞留させることができる。これによって、カソード側の電界を緩和し、発振現象の抑制が可能となる。

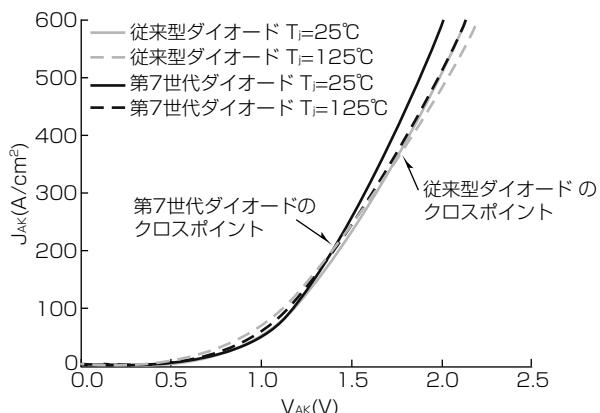

#### 3.2 第7世代(RFC)ダイオードの電気特性

図6に耐圧1,200V級の従来型ダイオードと第7世代ダイオードの出力特性を示す。第7世代ダイオードは、カソード側のキャリア注入効率を下げて、室温と高温での出力特性の電流値のクロスポイントを低く抑えた。つまり、定格電流付近で高温になれば電流が抑制される傾向となることから、並列動作に適するというメリットが得られている。

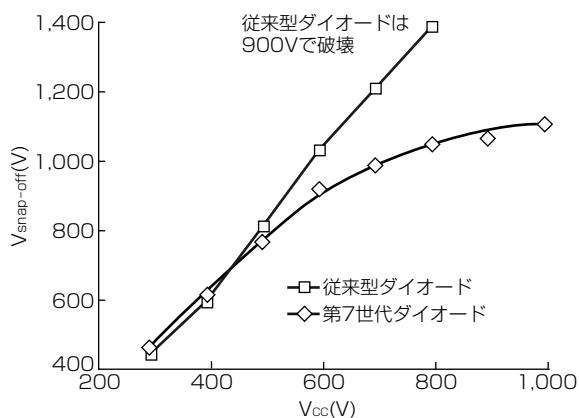

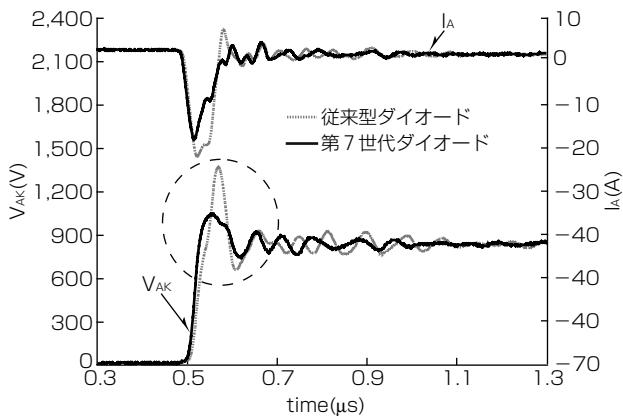

従来型ダイオードと第7世代ダイオードのリカバリー波形を図7に示す。両者とも定格1,200V/10Aのチップを用いて、発振現象が発生しやすい高電圧、低電流、常温の測定条件  $V_{AK} = 800V$ ,  $I_A = 0.6A$ ,  $T_j = 25^\circ C$  で実施した。従来型ダイオードはテール電流の急激な遮断とともに高い電圧ピークが発生(snap-off)しているが、第7世代ダイオードでは電圧サージはほとんど見られず、優れた  $V_{snap-off}$  抑制効果が得られている。このときのピーク電圧を  $V_{snap-off}$  と定義し、リカバリー時の印加電圧  $V_{cc}$  を上昇させて、限界特性

図6. 従来型ダイオードと第7世代ダイオードの出力特性

図8. 発振現象が発生しやすいリカバリー条件下での従来型ダイオードと第7世代ダイオードのV<sub>cc</sub>とV<sub>snap-off</sub>の相関

図7. 発振現象が発生しやすい条件下での従来型ダイオードと第7世代ダイオードのリカバリー波形

を評価した結果を図8に示す。従来型ダイオードのV<sub>snap-off</sub>はV<sub>cc</sub>に対して大きく依存し、V<sub>cc</sub>=800VでV<sub>snap-off</sub>が定格耐圧値を超える。一方の第7世代ダイオードはV<sub>cc</sub>が高いほどV<sub>snap-off</sub>の抑制効果が現れ、V<sub>cc</sub>=1,000Vでもリカバリー動作ができる素子破壊しない、高い耐量性能が得られている。その結果、発振抑制効果を維持させながら、対第6世代比でウェーハ厚を約21%薄くすることが可能となり、オン電圧とリカバリー損失を低減させることができた。

ダイオードに関する性能指標FOMは、式(1)のコレクタ電流密度J<sub>C</sub>(A/cm<sup>2</sup>)をアノード電流密度J<sub>A</sub>(A/cm<sup>2</sup>)、定常損失を決めるコレクタ-エミッタ間飽和電圧V<sub>CE(sat)</sub>(V)を125°Cの順方向電圧降下V<sub>F</sub>(V)、ターンオフ損失E<sub>off</sub>(mJ/A)を125°Cのリカバリー損失E<sub>rr</sub>(mJ/A)で読み替えて定義できる。FOMで比較すると、第7世代ダイオードは従来ダイオードに比べて2.7倍という大幅な性能向上を達成している。

このように、第7世代ダイオードは発振を抑制しながら、ウェーハを薄くすることが可能となり、従来型ダイオードと比べてオン電圧とリカバリー損失のトレードオフを大幅に改善し、低損失化を実現した。

#### 4. むすび

極薄ウェーハ化プロセス技術、裏面拡散層形成技術等の新規技術を適用することによって、高性能・高破壊耐量を持つ第7世代IGBT及び第7世代ダイオードを開発した。現在、極薄ウェーハ化プロセス技術を耐圧600Vから1,200V級のIGBT・ダイオードに展開するための開発を行っている。また、6,500V級を含むすべての耐圧級のダイオードに第7世代技術を適用予定である。今後も、高性能・高品質なSiパワーチップを市場に送り出していく。

#### 参考文献

- (1) Takahashi, H., et al.: Carrier Stored Trench-Gate Bipolar Transistor(CSTBT)-A Novel Power Device for High Voltage Application, ISPSD1996, 349~352 (1996)

- (2) Sato, K., et al.: New chip design technology for next generation power module, Proceedings of PCIM 2008, 673~678 (2008)

- (3) Haraguchi, Y., et al.: 600V LPT-CSTBT™ on advanced thin wafer technology, ISPSD2011, 68~71 (2011)

- (4) Masuoka, F., et al.: Great Impact of RFC Technology on Fast Recovery Diode towards 600V for Low Loss and High Dynamic Ruggedness, ISPSD2012, 373~376 (2012)

- (5) 高橋徹雄, ほか: 新型パワーモジュール用第6世代IGBTと薄ウェーハダイオード, 三菱電機技報, 84, No4, 224~227 (2010)

# 超小型DIPIPM “Ver.6シリーズ”

加藤正博\*

柴田祥吾\*

*Super Mini DIPIPM "Ver.6 Series"*

Masahiro Kato, Shogo Shibata

## 要 旨

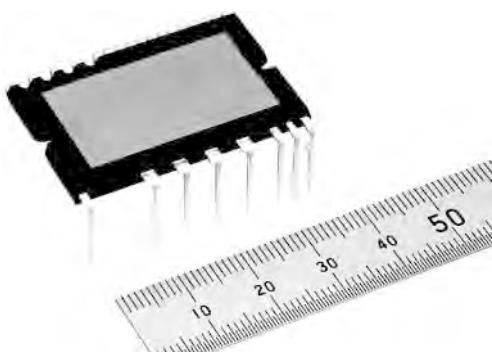

三菱電機のDIPIPM(Dual In-line Package Intelligent Power Module)はパワーチップとそれを駆動し、かつ保護機能を持つ制御用ICチップを内蔵したトランシスファモールド構造のIPMである。2004年から第5世代IGBTを搭載した超小型DIPIPM“Ver.4シリーズ”，2011年からは第6世代IGBTを搭載した超小型DIPIPM“Ver.5シリーズ”を製品化し、エアコン、洗濯機、冷蔵庫等白物家電機器のインバータユニットの小型化と省エネルギー化に貢献してきた。

近年、世界的な地球環境保護の高まりの中で、省エネルギー化がより一層重要視されはじめた。日本では、2010年以降空調機器業界に新たに省エネルギー基準としてAPF(Annual Performance Factor：通年エネルギー消費効率)

が導入され、軽負荷時など実際の使用状態に近いエアコンの運転効率が重要視されてきた。

このような市場要求に対応するため、当社では超小型DIPIPM“Ver.6シリーズ”を2013年8月から量産している。このシリーズは当社独自の第7世代IGBTを搭載することで、従来の超小型DIPIPM Ver.5シリーズに対して、通年での消費電力の大半を占める低電流域の飽和電圧を15%低減するとともに、ターンオフのスイッチング損失を40%低減させて白物家電の低消費電力化に貢献する。また、低温動作範囲の拡大や短絡電流検出精度の向上、瞬時通電範囲の拡大等の性能改善によってインバータシステム設計の自由度を向上させた。

超小型DIPIPM Ver.6シリーズ

IGBT : Insulated Gate Bipolar Transistor

FWD : Free Wheeling Diode

HVIC : High Voltage Integrated Circuit

LVIC : Low Voltage Integrated Circuit

BSD : Bootstrap Diode

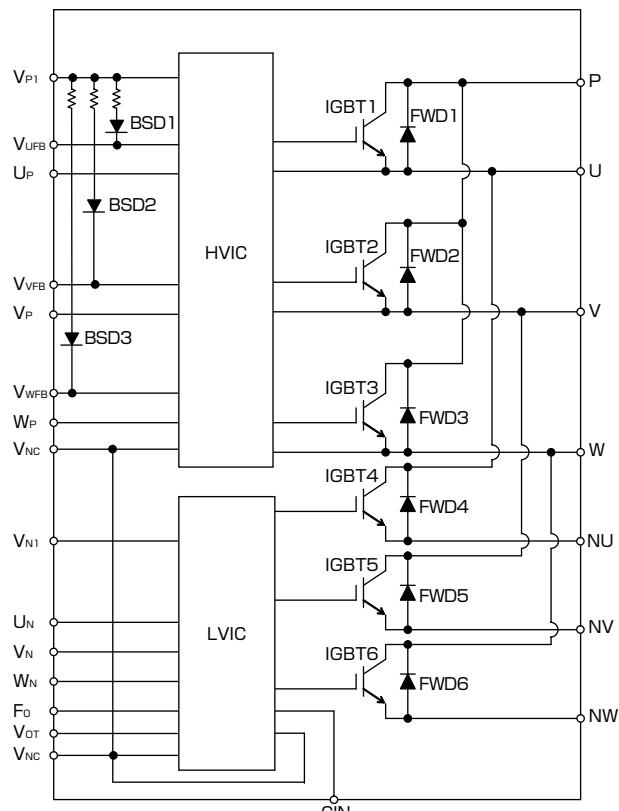

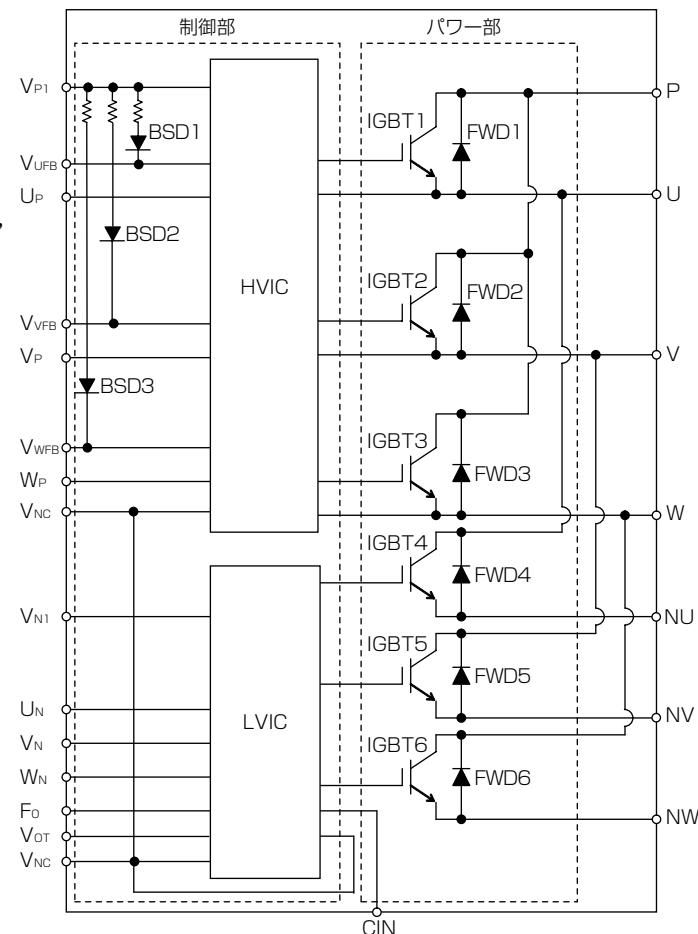

超小型DIPIPM Ver.6シリーズの内部回路図

## 超小型DIPIPM “Ver.6シリーズ”の外観と内部回路図

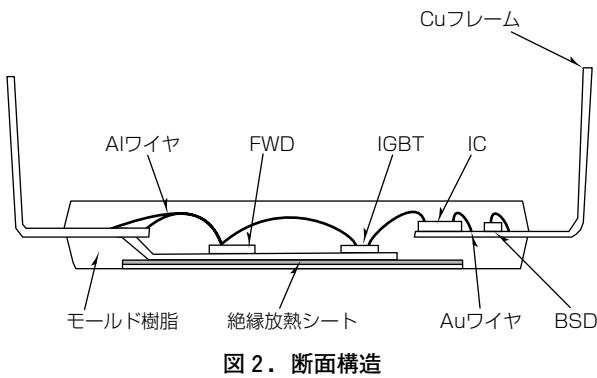

超小型DIPIPM Ver.6シリーズはIGBT×6素子、FWD×6素子によるインバータ回路と、それを駆動するHVIC、LVIC及びBSD×3素子によって構成される。なお、従来の超小型DIPIPM Ver.5とパッケージサイズ及びピン配列が同じである。

## 1. まえがき

当社は業界に先駆け1997年からDIPIPIMを製品化し、エアコン、洗濯機、冷蔵庫等の白物家電や産業用モータのインバータ駆動に多数採用されてきた。

2011年からは、ブートストラップダイオード(BSD)を内蔵した超小型DIPIPIM Ver.5シリーズを製品化し、インバータユニットの小型化、省エネルギー化に貢献してきた。

近年、世界的に地球環境保護活動が重要視され、省エネルギー化の必要性がより一段と高まっている。2010年以降空調機器業界で、エアコンの定格運転時だけでなく、実際の使用状態に近い軽負荷時の損失が重要視され、この条件での省エネルギー性能を表す新たな省エネルギー基準としてAPFが導入され、その改善が強く求められてきた。

このような市場要求に対応するため、従来の超小型DIPIPIM Ver.5シリーズに対して、低電流域の飽和電圧及びターンオフのスイッチング損失の低減によって低消費電力化を可能とした第7世代IGBT搭載の超小型DIPIPIM Ver.6シリーズを開発した。

本稿では、超小型DIPIPIM Ver.6シリーズの概要、特長、及び開発のベースとなったキーテクノロジー等について述べる。

## 2. 超小型DIPIPIM Ver.6シリーズの概要

内部回路は三相AC出力インバータ構成のパワーハーフ部と制御用HVIC、LVIC及びBSDから構成される。表1に超小型DIPIPIM Ver.6シリーズのラインアップを、図1に内部回路図をそれぞれ示す。

### 2.1 パワー部

IGBT(6素子)及びFWD(6素子)による三相AC出力インバータ回路を構成している。

### 2.2 制御部

- (1) HVIC(1素子)：P側IGBT用駆動回路、高圧レベルシフト回路、フローティング電源電圧低下保護(UV, Fo出力なし)を内蔵し、ブートストラップ回路方式の採用によって、15V単一電源駆動が可能となる。

- (2) LVIC(1素子)：N側IGBT用駆動回路、制御電源電圧低下保護回路(UV)，短絡電流保護回路(SC)に加え、過

熱保護回路(OT)又はアナログ温度出力回路(VOT)を内蔵した。短絡電流保護は、外部接続シャント抵抗で過電流を検出し、LVICにフィードバックしてIGBTを遮断する。制御電源電圧低下保護回路動作時、短絡電流保護回路動作時にエラー信号を出力する。

- (3) BSD(3素子)：ブートストラップ回路のダイオード(電流制限抵抗付き)を内蔵した。外付け部品が不要となるため、基板の小型化につながる。また15V単一電源駆動が可能となる。

### 2.3 内部構造

図2に超小型DIPIPIM Ver.6の断面構造を示す。パッケージサイズや端子の配置及び配列は、従来の超小型DIPIPIM Ver.5シリーズと同じであるため、超小型DIPIPIM Ver.6シリーズへの切替え設計、評価工数を抑えることができる。

図1. 内部回路図

表1. 超小型DIPIPIM Ver.6シリーズのラインアップ

| 形名    | PSS05S92E6/F6                                                                                                                       | PSS10S92E6/F6 | PSS15S92E6/F6 | PSS20S92E6/F6 | PSS30S92E6/F6 | PSS35S92E6/F6 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|

| 定格    | 5A / 600V                                                                                                                           | 10A / 600V    | 15A / 600V    | 20A / 600V    | 30A / 600V    | 35A / 600V    |

| 外形サイズ | 24.0×38.0×3.5(mm)(超小型DIPIPIM Ver.4/Ver.5シリーズと同じ)                                                                                    |               |               |               |               |               |

| 内蔵チップ | 三相インバーターを構成するIGBTチップ、FWDチップ、HVICチップ、LVICチップ、電流制限抵抗付きBSDチップ                                                                          |               |               |               |               |               |

| 内蔵機能  | 制御電源電圧低下(UV)保護機能：N側保護動作時Fo出力<br>短絡(SC)保護機能(外付けシャント抵抗による)：保護動作時Fo出力<br>過熱保護機能(OT, N側だけ)：PSS□□S92E6だけ<br>アナログ温度出力機能(VOT)：PSS□□S92F6だけ |               |               |               |               |               |

| その他   | インバーターN側分割エミッタ(3シャント)方式                                                                                                             |               |               |               |               |               |

図2. 断面構造

### 3. 超小型DIPIPM Ver.6 シリーズの特長

#### 3.1 第7世代IGBTのAPF改善

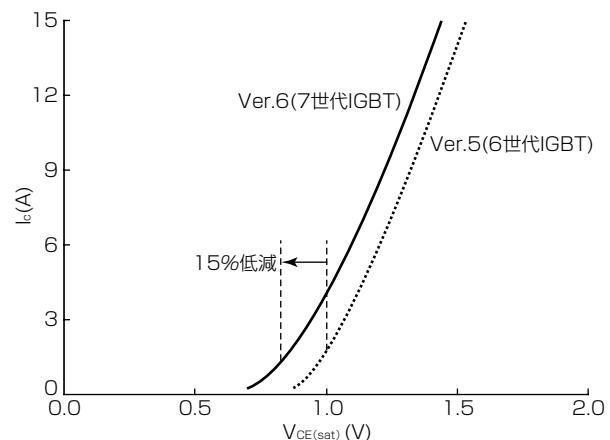

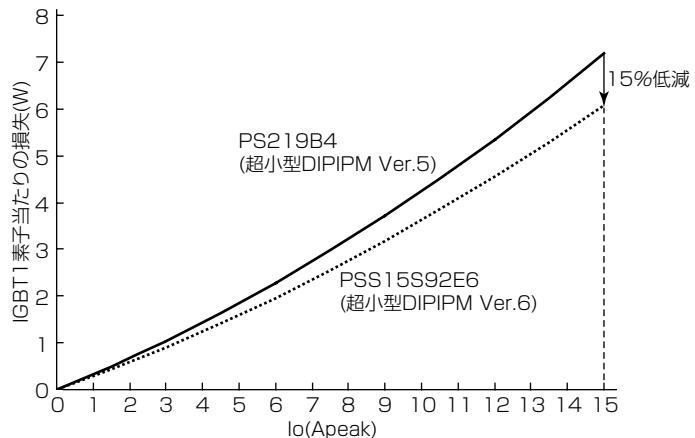

超小型DIPIPM Ver.6シリーズでは、従来シリーズよりもIGBT性能を改善した第7世代IGBTを採用している。従来の世代でも当社独自のCSTBT(Carrier Stored Trench-Gate Bipolar Transistor)構造を用いることで高い省エネルギー性能を持っていた<sup>(1)</sup>が、第7世代ではAPFで重要なファクタとなる軽負荷時における省エネルギー性能を追求した。図3に示すCSTBT構造のP+層の厚みを大幅に削減するとともに、デバイス構造を最適化することで、低電流域(定格電流の10分の1程度)の飽和電圧を15%低減することができた。

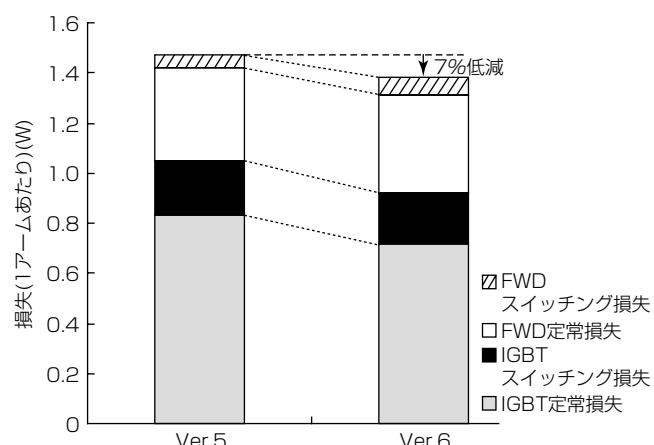

図4に代表例として15A品のコレクタ電流Ic-飽和電圧V<sub>CE(sat)</sub>特性比較( $T_j=25^\circ\text{C}$ )を示す。また、図5に同じく15A品の損失比較を示すが、先に述べた飽和電圧の低減によって軽負荷時を想定した条件で従来のVer.5に対して7%の損失低減を実現した。

さらに、ターンオフのテール電流を最小化することによってスイッチング時に発生する損失を40%低減することができ、エアコンの定格運転の損失低減に大きく貢献する。

#### 3.2 ラインアップの拡張

従来の超小型DIPIPMシリーズは、最大定格電流が30Aまでのラインアップであり、その中でもBSD搭載品は最も市場要求の高い5Aから15Aまでとしていた。Ver.6シリーズでは、第7世代IGBTの搭載による単位面積あたりの通電能力拡大で、新たに定格電流35Aタイプをラインアップに加え、さらに5Aから35Aまでの6品種をBSD搭載品として開発した。

#### 3.3 過負荷運転領域の拡大

LVICに内蔵している短絡保護機能で、この製品ではトリミング回路を用いて特性を補正する方式を適用しているため、従来のVer.5に対して短絡保護検知電圧のばらつきの抑制を実現( $\pm 10 \Rightarrow 5\%$ )させた。この検出精度の向上によって、インバータの過負荷運転範囲を10%拡大させることが可能となる。加えて、デバイス構造の最適化を実施した第7世代IGBTの搭載によって、飽和電流を従来保証の定

図3. CSTBT構造

図4. 超小型DIPIPM(15A品)のコレクタ電流Ic-飽和電圧V<sub>ce(sat)</sub>特性比較

(条件:  $T_j=125^\circ\text{C}$ ,  $V_{cc}=300\text{V}$ ,  $P.F=0.8$ ,  $f_c=5\text{kHz}$ , 二相正弦波出力)

図5. 超小型DIPIPM(15A品)の損失比較

格電流の2倍から3倍へと拡大し、インバータの瞬時通電許容値を拡大することが可能となった。

この2点の改善によって、従来品に対して過負荷運転領域を大幅に拡大することができ、システムでのモータ電流通電可能範囲の増加に寄与できる。

表2. PSS15S92E6の電気的製品仕様

| 項目                 | 記号                   | 条件                                                                                                                                         |                                                                                                                        | 最小      | 標準    | 最大    | 単位   |

|--------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|------|

| コレクターエミッタ間<br>飽和電圧 | V <sub>CE(sat)</sub> | V <sub>D</sub> =V <sub>DB</sub> =15V<br>I <sub>C</sub> =15A, V <sub>IN</sub> =5V                                                           | T <sub>j</sub> =25°C<br>T <sub>j</sub> =125°C                                                                          | —       | 1.45  | 1.75  | V    |

| FWD順電圧降下           | V <sub>EC</sub>      | — I <sub>C</sub> =15A, V <sub>IN</sub> =0V                                                                                                 |                                                                                                                        | —       | 1.70  | 2.20  |      |

| スイッチング時間           | t <sub>on</sub>      | V <sub>CC</sub> =300V, V <sub>D</sub> =V <sub>DB</sub> =15V<br>I <sub>C</sub> =15A, T <sub>j</sub> =125°C<br>V <sub>IN</sub> =0⇒5V<br>誘導負荷 |                                                                                                                        | 0.70    | 1.10  | 1.50  | μs   |

|                    | t <sub>rr</sub>      |                                                                                                                                            |                                                                                                                        | —       | 0.30  | —     |      |

|                    | t <sub>(ton)</sub>   |                                                                                                                                            |                                                                                                                        | —       | 0.40  | 0.65  |      |

|                    | t <sub>off</sub>     |                                                                                                                                            |                                                                                                                        | —       | 1.20  | 1.70  |      |

|                    | t <sub>(loff)</sub>  |                                                                                                                                            |                                                                                                                        | —       | 0.15  | 0.30  |      |

| 回路電流               | I <sub>D</sub>       | V <sub>P1</sub> -V <sub>NC</sub> , V <sub>N1</sub> -V <sub>NC</sub><br>の総和                                                                 | V <sub>D</sub> =15V, V <sub>IN</sub> =5V<br>V <sub>D</sub> =15V, V <sub>IN</sub> =0V                                   | —       | —     | 2.80  | mA   |

|                    | I <sub>DB</sub>      | V <sub>UFB</sub> -U, V <sub>VFB</sub> -V,<br>V <sub>WFB</sub> -W                                                                           | V <sub>D</sub> =V <sub>DB</sub> =15V, V <sub>IN</sub> =0V<br>V <sub>D</sub> =V <sub>DB</sub> =15V, V <sub>IN</sub> =5V | —       | —     | 0.10  |      |

|                    | V <sub>SCref</sub>   | V <sub>D</sub> =15V                                                                                                                        |                                                                                                                        | 0.455   | 0.480 | 0.505 |      |

|                    | UV <sub>DBt</sub>    | T <sub>j</sub> ≤125°C                                                                                                                      |                                                                                                                        | トリップレベル | 7.0   | 10.0  | 12.0 |

| 制御電源電圧低下保護         | UV <sub>DRt</sub>    |                                                                                                                                            |                                                                                                                        | リセットレベル | 7.0   | 10.0  | 12.0 |

|                    | UV <sub>Dt</sub>     |                                                                                                                                            |                                                                                                                        | トリップレベル | 10.3  | —     | 12.5 |

|                    | UV <sub>Dr</sub>     |                                                                                                                                            |                                                                                                                        | リセットレベル | 10.8  | —     | 13.0 |

| BSD順電圧降下           | V <sub>F</sub>       | I <sub>F</sub> =10mA, 内蔵抵抗Rの電圧降下を含む                                                                                                        |                                                                                                                        | 1.1     | 1.7   | 2.3   | V    |

### 3.4 特性ばらつきの軽減

先に述べたとおり第7世代IGBTはウェーハプロセスの最適化を実施し、飽和電圧のばらつきの要因となる工程を削減した。これによって、従来の飽和電圧のばらつき33%に対して、超小型DIPIPM Ver.6シリーズでは約20%まで軽減し、低消費電力化とともに設計自由度の向上にも貢献する。

### 4. 超小型DIPIPM Ver.6シリーズの性能と特性

超小型DIPIPM Ver.6シリーズの電気的特性について、表2に代表品種として“PSS15S92E6(15A／600V)”の主な電気的製品仕様を示す。

また、図6に超小型DIPIPM Ver.6 PSS15S92E6(15A／600V)と、同じ定格電流である従来の超小型DIPIPM Ver.5 “PS219B4(15A／600V)”のIGBT 1素子当たりの定格運転損失比較を示す。

超小型DIPIPM Ver.6シリーズは、従来の超小型DIPIPM Ver.5シリーズに対してI<sub>O</sub>=15Apeak時におけるIGBT 1素子あたりの損失を約15%低減した。

### 5. む す び

今回開発・製品化した超小型DIPIPM Ver.6シリーズの機能、特長等について述べた。今回開発したキーテクノロ

(条件: T<sub>j</sub>=125°C, V<sub>CC</sub>=300V, P.F.=0.8, f<sub>c</sub>=5kHz, 二相正弦波出力)

図6. 超小型DIPIPM(15A品)のIGBT 1素子当たりの定格運転損失比較

ジエを展開し、今後も市場ニーズに適した製品を開発していくことで、家電機器や産業機器のインバータ化の拡大、省エネルギー化に貢献していく。

### 参 考 文 献

- (1) 白水政孝, ほか:超小型DIPIPM“Ver.4新シリーズ”, 三菱電機技報, 84, No.4, 255~258 (2010)

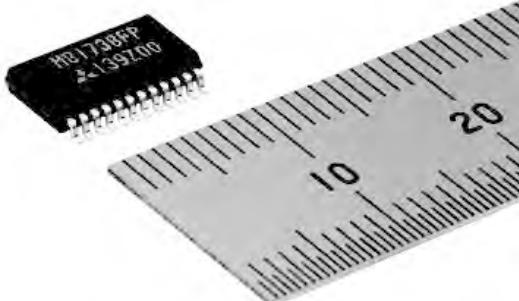

# 高信頼性1,200V HVIC “M81738FP”

羽生 洋\*

山本雅裕\*

*High Reliability 1,200V HVIC "M81738FP"*

Yo Habu, Masahiro Yamamoto

## 要 旨

HVIC(High Voltage Integrated Circuit)は、産業及び民生機器のインバータ駆動に普及しているIGBT(Insulated Gate Bipolar Transistor)モジュールのゲート駆動や保護の機能を果たすデバイスである。近年、産業及び民生機器向けのインバータ市場は、省エネルギー需要の高まりから堅実な成長が見込まれており、AC200V系電源を使用する市場では600V HVICが、AC400V系電源を使用する市場では1,200V HVICが必要とされる<sup>(1)</sup>。

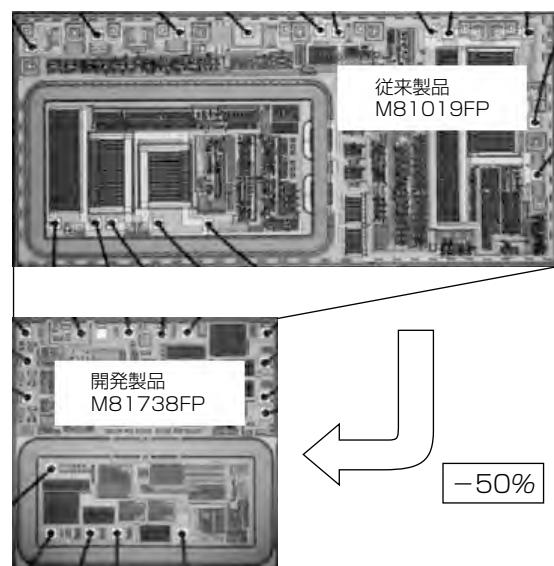

特に、AC400V系電源を使用する場合、AC200V系電源に比べ高ノイズ環境となるため、より高信頼性の1,200V耐圧HVICが求められる。このような市場要求に対応するため、IGBTモジュール駆動に最適で高信頼性の1,200V耐圧のゲートドライバHVIC“M81738FP”を開発した。この

HVICの特長は次のとおりである。

- (1) 新微細プロセスを用いたM81738FPは、従来製品“M81019FP”的後継製品であり、特性がコンパチブルとなるように設計しており、置き換えが容易である。

- (2) 第2世代型分割リサーフ構造及びN+埋め込み層を採用することによって、従来製品の課題であったラッチアップ耐量を向上させた。

- (3) 負電圧サージ評価で、誤動作及び破壊は発生せず、負電圧サージに対して高耐量を得ている。

- (4) 新プロセス適用によって、従来製品に比べ大幅にチップサイズを縮小した。

- (5) 新微細プロセスを用いているが、アクティブクランプ回路を採用することで電源サージ耐量を向上させた。

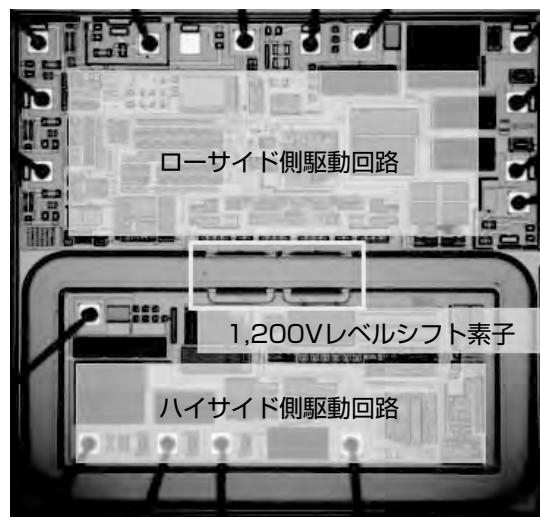

## 1,200V HVIC“M81738FP”的外観及びチップ

第2世代型分割リサーフ構造を適用した、IGBTモジュール駆動に最適で高信頼性の1,200V耐圧のゲートドライバHVIC“M81738FP”を開発した。

## 1. まえがき

三菱電機では、1997年に独自技術である分割リサーフ構造の開発によって1,200V HVICの製品化を開始し、2005年にIGBTモジュール駆動用HVIC“M81019FP”をリリースしている。さらに、2008年には第1世代型分割リサーフ構造に微細加工技術を導入した第2世代型分割リサーフ構造を600Vクラスで開発し、600V HVICを製品化している。今回、この第2世代型分割リサーフ構造を、独自のフィールドプレート技術によって1,200Vへ高耐圧化し、M81019FPの後継製品となるIGBTモジュール駆動に最適で高信頼性の1,200V耐圧のゲートドライバHVIC“M81738FP”を開発した。

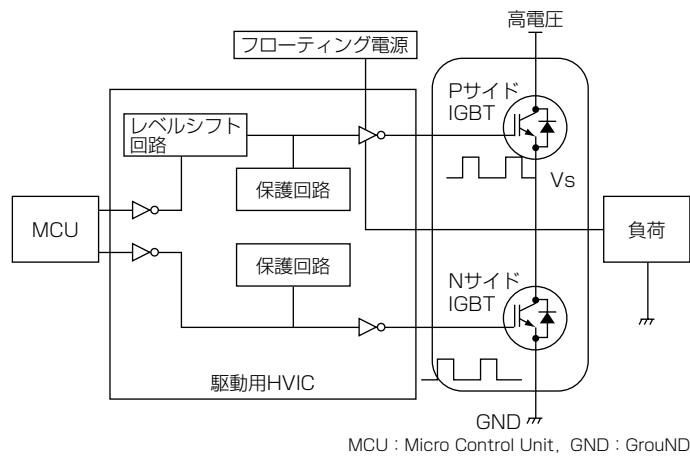

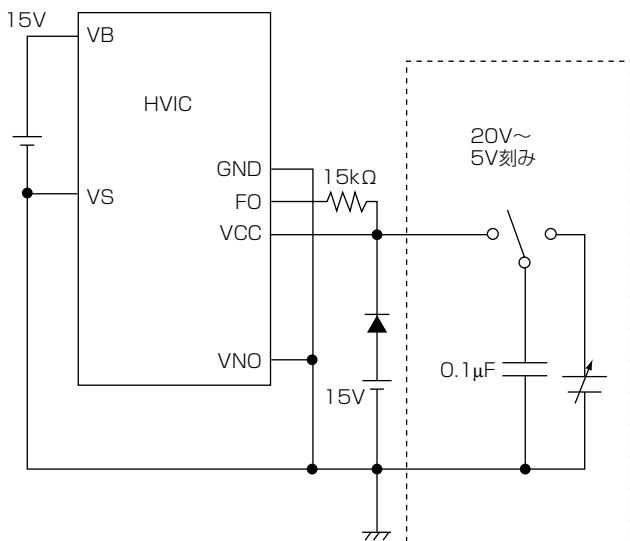

ハーフブリッジタイプのHVICを用いた接続を図1に示す。インバータシステムでは多様なスイッチングノイズ環境下で使用されるため、高信頼性のHVICが求められる。特に、AC400V系電源を使用する場合、AC200V系電源に比べ高ノイズ環境となるため、より高信頼性の1,200V耐圧HVICが求められる。インバータ駆動にHVICを用いるメリットは次のとおりである。

- (1) HVICに保護回路を内蔵できる。

- (2) 実装部品数の削減によって、プリント基板面積を小さくできる。

- (3) ブートストラップ回路によって、容易にフローティング電源を得ることができる。

## 2. 高信頼性1,200V HVIC “M81738FP”

### 2.1 M81738FPの概要

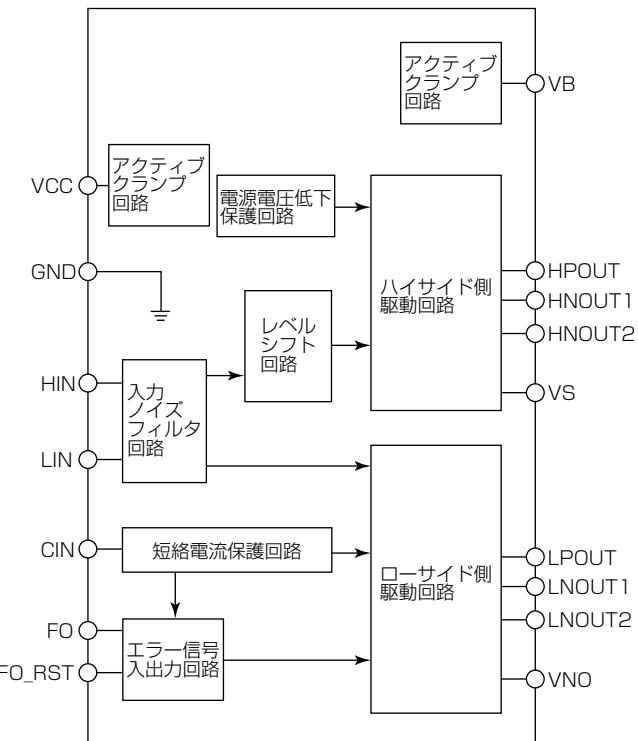

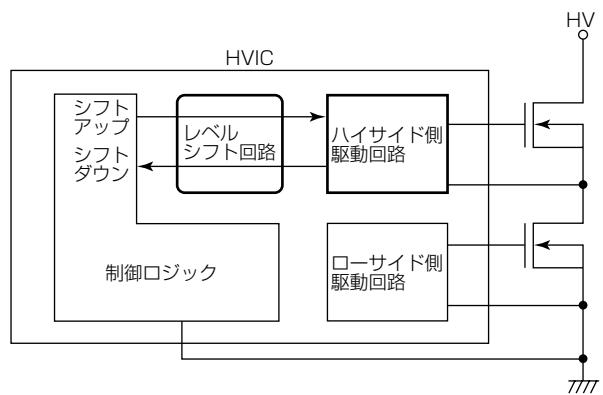

新微細プロセスを用いたM81738FPは、従来製品M81019FPからの置き換えを容易にするため、M81019FPと特性がコンパチブルになるよう設計している。M81738FPのブロック図を図2に示し、各機能について次に示す。

- (1) 5 Vロジック入力(HIN, LIN)

- (2) 1,200Vのレベルシフト回路

- (3) 出力電流±1A

- (4) ゲートクランプ電流-1A

- (5) 短絡電流保護回路(CIN)

- 外部接続のシャント抵抗で過電流を検知し、IGBTを遮断する。

- (6) 電源電圧低下保護回路: UV(VB)

- 制御電源電圧低下時にIGBTを遮断する。

- (7) エラー信号入出力回路(FO, FO\_RST)

- 短絡電流保護回路動作時にエラー信号を出力する。また、エラー信号の入力によってIGBTを遮断する。

- (8) 入力ノイズフィルタ回路

- 狭幅の入力ノイズを取り除く。

- (9) アクティブクランプ回路

- 電源サージによるノイズを吸収する。

図1. HVICを用いた接続

図2. M81738FPのブロック図

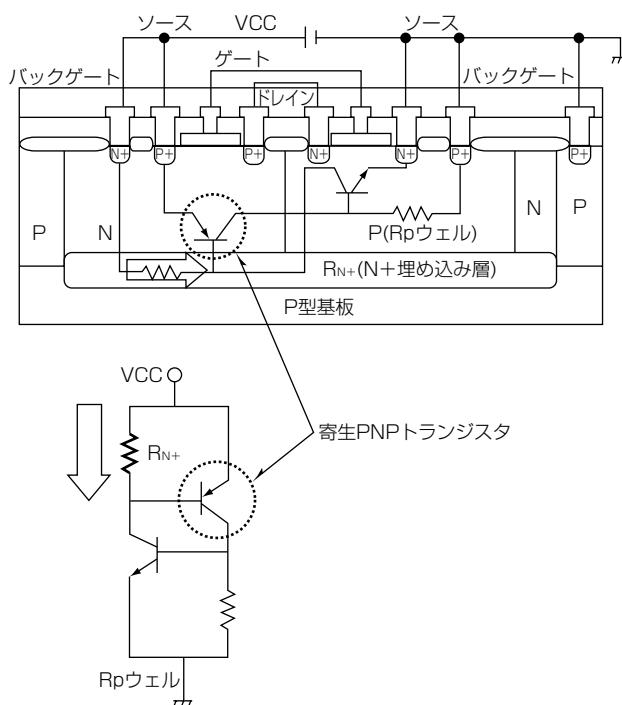

### 2.2 ラッチアップ対策<sup>(2)</sup>

NchMOS, PchMOSを内蔵しているCMOS(Complementary Metal Oxide Semiconductor)型ICは、構造上、IC内部にバイポーラ型の寄生トランジスタ回路が構成されてしまう。この回路はサイリスタと同じ構成となっているため、サイリスタ動作と同様に電源からのスイッチングノイズなどで過渡電流が流れると寄生PNPトランジスタがターンオンし、過大な電流が流れ続ける。この現象はラッチアップ現象と呼ばれており、一旦ラッチアップ現象が発生すると、電源を遮断しない限り電流が流れ続け、誤動作や破壊に至る。ラッチアップ現象を防止するためには、トランジスタ間の距離を大きくする必要があり、チップサイズが大きくなる要因となっていた。

図3にM81738FPのCMOS領域断面を示す。M81738FPのウェーハプロセスでは、CMOS領域にN+埋め込み層を設け、N領域抵抗値を低減させている。これによって、寄生PNPトランジスタのベース電位低下を防ぎ、寄生PNPトランジスタのターンオンを防止している。

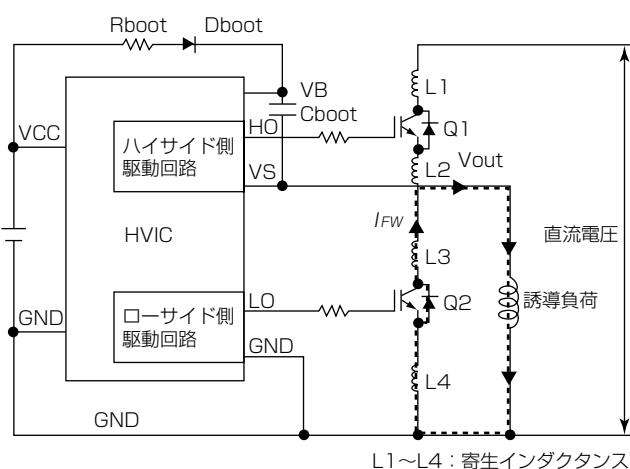

### 2.3 負電圧サージ耐量

図4に、ハーフブリッジタイプのHVICを用いた応用回路の一般的な接続例を示す。ハイサイド側駆動回路のトランジスタQ1がターンオフすると、ローサイド側駆動回路のフリーホイールダイオードが還流モードとなり、L負荷に電流 $I_{FW}$ が流れる。このとき、寄生インダクタンスによって、HVICのVS端子に負電圧サージが発生する。この負電圧サージは、HO端子のハイラッチ誤動作及び破壊を引き起こす場合がある。

図3. CMOS断面

図4. 応用回路の接続例

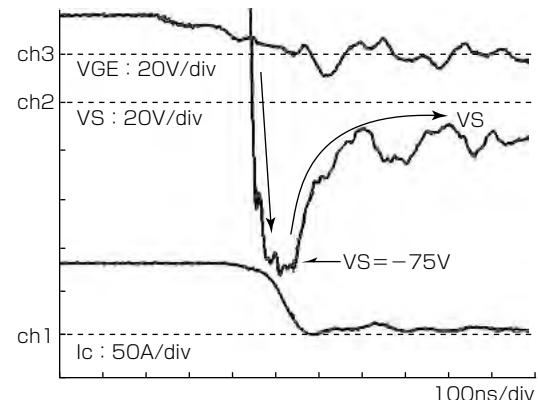

図5に、M81738FPによってDIPCB(Dual Inline Package Converter Inverter Brake)を駆動した際の負電圧サージ評価波形を示す。ゲート抵抗0Ωでの評価を実施し、誤動作及び破壊は発生せず、高耐量が得られている。

### 2.4 チップサイズ

図6に従来製品M81019FPと今回開発したM81738FPのチップを示す。第1世代型分割リサーフ構造を用いた従来製品M81019FPは、その構造上、先に述べたラッチアップを抑制するために、素子間距離を大きくとる必要があった。第2世代型分割リサーフ構造では、既に量産中の600V微細化プロセスのリサーフ領域を高压化しており、N+埋め込み層によってラッチアップ耐量を向上させた上で、チップサイズを大幅に縮小することができている。また、素子自体の縮小によって素子自体の動作速度は速くなるが、遅延回路を付加することで従来製品M81019FPの入出力伝達遅延時間に合わせており、置き換えが容易である。新たな製品ラインアップ展開では、入出力伝達遅延時間を速くす

評価条件：

Ta=25°C, VS=600V, Rg=0Ω, VGE=15V

図5. VS負電圧サージ評価波形

図6. チップサイズの比較

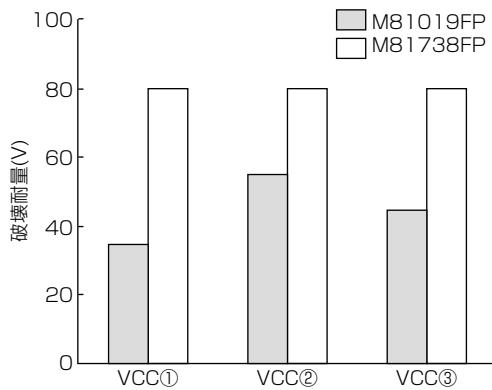

評価条件：

VCC=VBS=15V, C=0.1μF

帶電圧：20V~(5V刻み)

(a) 評価回路

(b) 評価結果

図7. 電源サージ耐量の評価

ることが可能であり、デッドタイムの設定が容易となる。

## 2.5 電源サージ

M81738FPは、プロセス(素子)が微細化されているが、従来製品M81019FPにはないアクティブクランプ回路を新たに追加し、電源ノイズによる電源サージ耐量向上を図った。サージが印加される電源端子(VCC, VB)に直結した最適なサージ吸収回路であるアクティブクランプ回路を設けることで、図7に示すように、従来製品に比べ耐量を向上させることができた。このアクティブクランプ回路は電源電圧が所望の設定電圧を超えると、電流シンク能力の大きなMOSトランジスタがオン状態となり、サージエネルギーを吸収して、内部回路を保護する。電流シンク能力が大きくなる程、MOSトランジスタサイズも大きくなるため、アクティブクランプ回路のサージエネルギー吸収能力とチップサイズは相反する。よって、最適なサイズ設計が重要であり、M81738FPでは複数のサイズの回路評価結果から最適な素子サイズを選択している。

## 3. むすび

第2世代型分割リサーブ構造を適用した、IGBTモジュール駆動に最適で高信頼性の1,200V耐圧のゲートドライバHVIC“M81738FP”を開発した。これによって、インバータシステムで小型化、高機能化を実現させるキーデバイスとして省エネルギー化に貢献することができる。

## 参考文献

- (1) 吉野 学, ほか: インバータシステム用1,200V HVIC技術, 三菱電機技報, **86**, No.5, 271~274 (2012)

- (2) Yamamoto, M., et al: High reliability 1200V High Voltage Integrated Circuit (1200V HVIC) for half bridge applications, Proc. PCIM, 466~472 (2012)

# 双方向のレベルシフト機能を搭載した 1,200V HVIC技術

吉野 学\*

羽生 洋\*

Technology of Bi-directional High Voltage Level-shifting for 1,200V HVIC

Manabu Yoshino, Yo Habu

## 要 旨

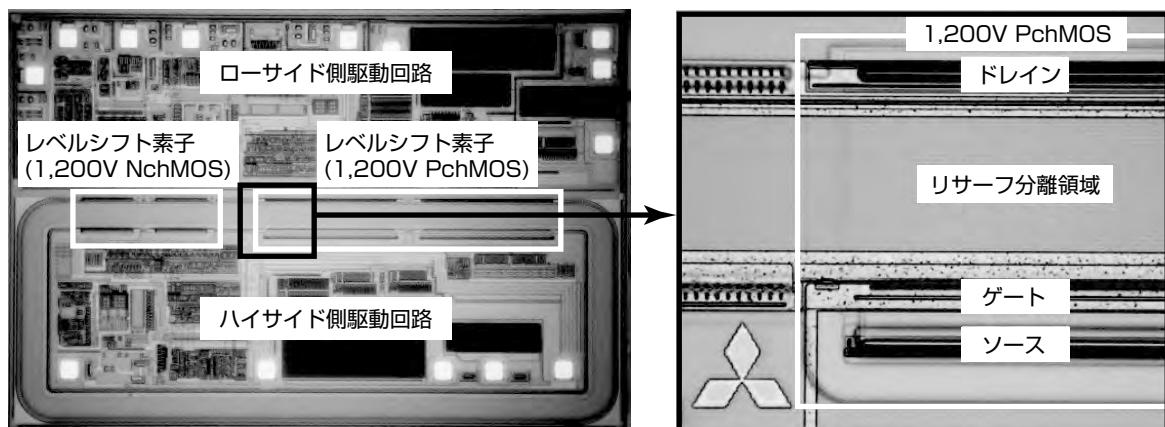

産業、民生機器のインバータ駆動に普及しているIPM (Intelligent Power Module)で、HVIC (High Voltage Integrated Circuit)はパワーチップのゲート駆動や保護の機能を果たすキーデバイスである。HVICはローサイド側駆動回路(以下“ローサイド”という。)と高電圧で分離されたハイサイド側駆動回路(以下“ハイサイド”という。)を併せ持ち、互いの回路間をレベルシフト回路によって信号伝達している。このレベルシフト回路で、ローサイドからハイサイドへ信号伝達するシフトアップ機能は、高耐圧NchMOS(N-channel Metal Oxide Semiconductor)を用いて一般的に実用化されている。一方でハイサイドからローサイドへ信号伝達するシフトダウン機能は、ハイサイドで発生した信号をローサイドへフィードバックすることができるところからHVICの高機能化に大きく寄与する。しかし、

その機能を担う高耐圧PchMOS(P-channel MOS)の構造上の課題によってこれまでに実用化された例がない。今回、特に実現が困難であった1,200Vクラスの高耐圧 PchMOSを開発し、シフトアップ機能とシフトダウン機能を併せ持つ1,200V HVICを実現した。今回開発した1,200V PchMOSは次の特長を持っている。

- (1) 従来の1,200V HVIC<sup>(1)</sup>からプロセスステップを追加することなく形成することが可能である。

- (2) 同一のリサーフ分離領域上に1,200V NchMOSとの混載が可能であり、レイアウト上の制約がない。

これらの特長を持った1,200V PchMOSを搭載することによって、今後更に幅広い機能を備えた1,200V HVICのラインアップが期待できる。

## シフトアップ機能とシフトダウン機能を併せ持つ1,200V HVIC

従来の1,200V NchMOSだけを搭載する1,200V HVICプロセスを用いて1,200V PchMOSを実現した。1,200V NchMOSと1,200V PchMOSを同一チップ内に搭載することによってシフトアップ、シフトダウンの双方向のレベルシフト機能を可能にした。

## 1. まえがき

HVICは通常の基板電位を基準とした制御回路(ローサイド側駆動回路)に加えて、基板電位から高電圧に分離されたフローティング回路(ハイサイド側駆動回路)とローサイド側駆動回路-ハイサイド側駆動回路間の信号伝達を行うレベルシフト回路を搭載しており、1チップでパワー・チップの最適駆動、保護を可能にする。図1に一般的なゲート駆動用HVICの構成を示す。ここでレベルシフト機能には、信号の伝達方向によってローサイド側駆動回路からハイサイド側駆動回路へ信号が伝達されるシフトアップ機能とハイサイド側駆動回路からローサイド側駆動回路へ信号が伝達されるシフトダウン機能がある。

シフトアップ機能はCPU(Central Processing Unit)からHVICへの入力信号をハイサイドのパワーチップのゲートへ出力する上で不可欠な機能であり、高耐圧NchMOSを用いて広く実用化されている。一方、シフトダウン機能はハイサイド側駆動回路内で発生したエラー信号などをローサイド側駆動回路へフィードバックすることが可能であり、HVICの高機能化に大きく寄与する。シフトダウン機能は高耐圧PchMOSを用いて実現することが可能であるが、高耐圧PchMOSは高耐圧NchMOSと比べて①低い電流能力、②寄生PNP動作による基板へのリークといった課題があり、特に高耐圧になるほどその課題は顕著となるため、1,200V HVICでシフトダウン機能を搭載することができなかった。

今回、これらの課題を解決した1,200V PchMOSを開発し、シフトダウン機能を備えた1,200V HVICを実現した。本稿では今回開発した1,200V PchMOSについて述べる。

## 2. 1,200V PchMOS

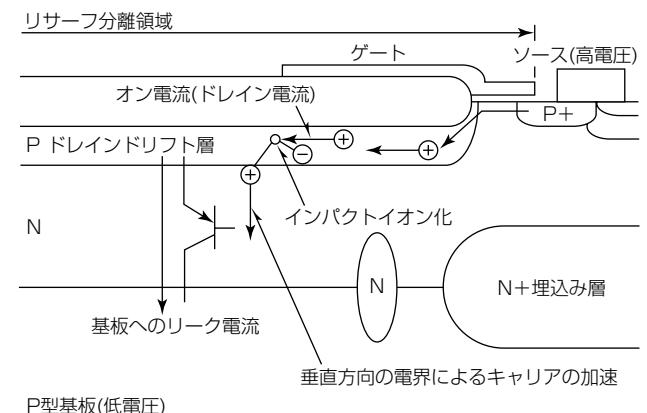

### 2.1 高耐圧PchMOSの構造

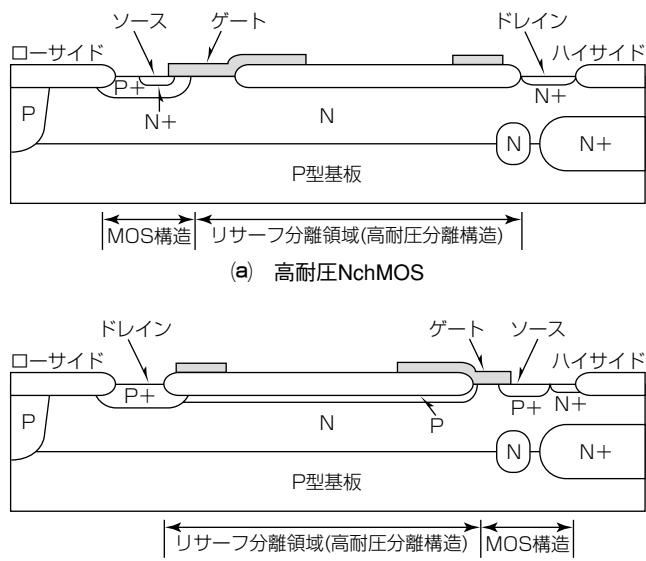

図2に高耐圧NchMOSと高耐圧PchMOSの断面模式図を示す。高耐圧NchMOS/PchMOSとともにリサーフ分離によって高電圧を保持している。高耐圧NchMOSはリサーフ分離領域に対してローサイド側にゲートを形成しており、シフトアップ機能を可能にしている。一方、高耐圧PchMOSはリサーフ分離領域に対してハイサイド側にゲートを形成しており、シフトダウン機能を可能にしている。また、高耐圧NchMOSはN型のリサーフ分離領域がオン電流の流れるドレインドリフト層となるのに対し、高耐圧PchMOSはN型のリサーフ分離領域表面にP型のドレインドリフト層を形成している。

これら高耐圧NchMOSと高耐圧PchMOSは、高電圧を保持する基本構造が同じであるため、三菱電機が開発した第2世代型分割リサーフ構造によって<sup>(2)</sup>、一つの高耐圧分離構造上に混載することが可能である。しかし、リサーフ

図1. ゲート駆動用HVICの構成

図2. 高耐圧MOSの断面模式図

分離領域表面に形成される高耐圧PchMOSのドレインドリフト層は、高耐圧PchMOSと高耐圧NchMOSを一つの高耐圧分離構造上に混載可能なメリットを持つ一方、デメリットとしてその構造起因の課題がある。次の節では高耐圧PchMOSの構造起因の課題とその解決構造について述べる。

### 2.2 耐圧-ドレイン電流トレードオフの改善

高耐圧PchMOSのドレインドリフト層はリサーフ分離領域表面に形成されるため、高耐圧NchMOSのドレインドリフト層と比べてその断面積が小さく、ドレイン電流は小さい。ドリフト層の不純物濃度を上げることでドリフト抵抗を低下させドレイン電流を上げることができが、同時に高電圧印加時のドリフト層内の空乏化が抑制されるため耐圧は低下する。そのため、高電圧を保持するためにはドリフト層の不純物濃度を上げることができない。

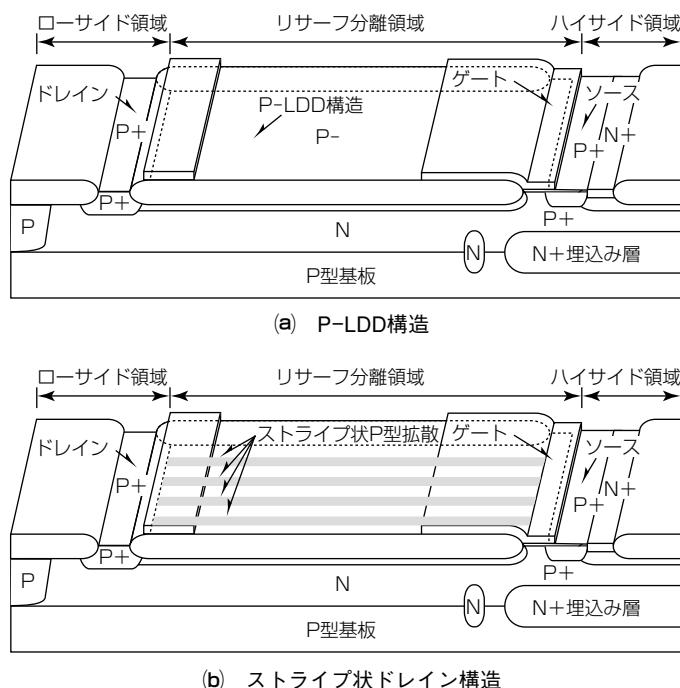

この耐圧-ドレイン電流のトレードオフを改善するため、今回開発した高耐圧PchMOSでは図3(a)に示す従来のP-LDD(P-Lightly Doped Drain)構造に対し<sup>(3)</sup>、図3(b)に示

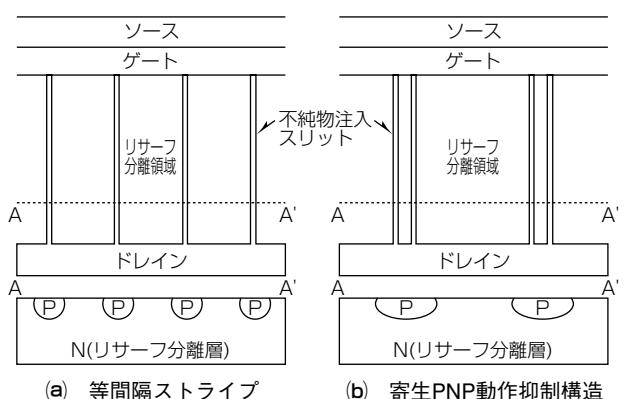

すP-ドレイン層をストライプ状に形成する構造を採用した。ドリフト層をストライプ状にすることで、ストライプと垂直方向の断面でドリフト層は縦横2方向からPN接合で囲われる。縦方向のPN接合からだけ空乏層が伸びる従来のP-LDD構造に対して、縦方向に加え横方向のPN接合からも空乏化が伸びるストライプ状構造によって、より高い不純物濃度でも高電圧を保持することが可能となり、耐圧-ドレイン電流のトレードオフを改善することができる。

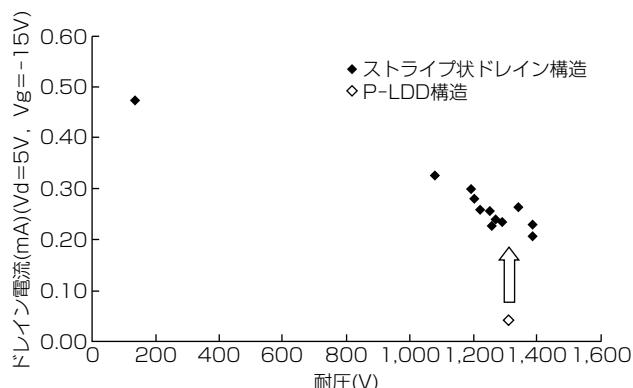

図4にP-LDD構造の高耐圧PchMOSとストライプ状ドレイン構造の高耐圧PchMOSの耐圧-ドレイン電流のトレードオフを示す。ストライプ状ドレイン構造は一定の不純物注入量でストライプ(不純物注入スリット)の幅、ピッチを振り分け耐圧、ドレイン電流を調整している。図4からドレイン構造をストライプ状することで従来のP-LDD構造と比べて耐圧を低下させることなくドレイン電流を約4倍まで向上させたことが分かる。

図3. 高耐圧PchMOSドレイン構造

図4. 耐圧-ドレイン電流のトレードオフ

### 2.3 寄生PNP動作の抑制

リサーフ分離領域表面に形成されるドレインドリフト層は、図5に示すようにN型のリサーフ分離領域、P型基板と縦型の寄生PNP構造を形成する。高耐圧PchMOSがオンすると、ドレインドリフト層にオン電流が流れる。このときドレインドリフト層からリサーフ分離領域へキャリアの移動が生じると、寄生PNP構造のエミッタからベースへ流れるベース電流となって寄生PNP動作を引き起す。その結果、オン電流の一部は寄生PNPのコレクタ電流としてドレインドリフト層から基板へ向けて流れ始め、それに伴い高耐圧PchMOSの本来のドレイン電流は減少する。

ここで寄生PNP動作のベース電流となるキャリアは、ドレイン-ソース間に高電圧が印加される際にドレインドリフト層に生じる高電界と、そこを流れるオン電流によって引き起こされるインパクトイオン化で生じる。そのためドレイン-ソース間が高電圧になるほどインパクトイオン化で生じるキャリアが増え、基板へ流れる電流は増加する。ドレイン-ソース間電圧を上げていくと、最終的にオン電流は全て基板へ流れドレイン電流は消滅する。

寄生PNP動作のベース電流となるキャリアの発生を抑えるため、今回開発した高耐圧PchMOSは、図6(b)に示すようにストライプ状ドレイン構造を形成する不純物注入スリットの配列を、図6(a)に示す等間隔のものから隣接する

図5. 高耐圧PchMOSの寄生PNP動作

図6. 寄生PNP動作改善ドレイン構造

図7. 改善ドレイン構造のId, Isub-Vd特性

2本のスリットが近付いた構造にしている。この構造によって、ストライプは隣接する2本の注入スリットからの不純物拡散の重ね合わせによって形成される。その結果、単独のスリットからの拡散によって形成されるストライプに対して、不純物濃度分布が変わりドレイン電流の経路がずれることでインパクトイオン化を抑制している。

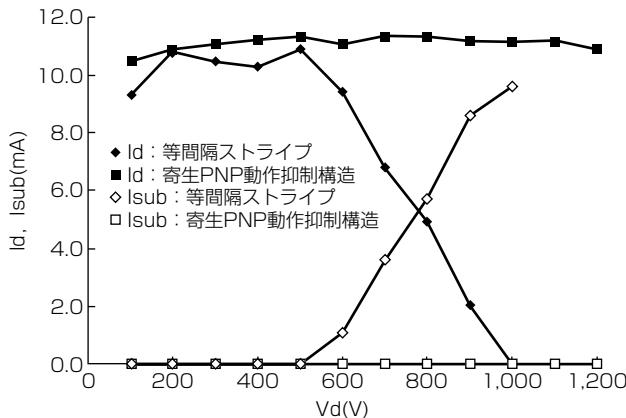

図7に等間隔のストライプ構造の高耐圧PchMOSと開発したストライプ構造の高耐圧PchMOSのId, Isub-Vd特性を示す。等間隔のストライプ構造では印加電圧(Vd)が高くなるにつれて基板へのリーク電流(Isub)が生じ、それに伴いドレイン電流(Id)が減少し、1,000V以上の印加電圧ではドレイン電流が消滅する。一方、今回開発したドレイン構造では印加電圧1,200Vでも基板へのリーク電流は発生せず、正常にドレインへ電流が流れている。

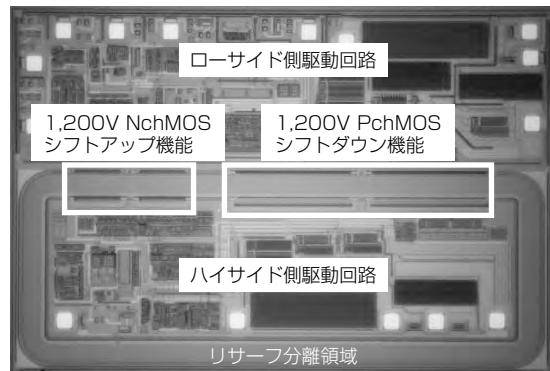

### 3. 1,200V PchMOS搭載1,200V HVIC

図8に1,200V PchMOSと1,200V NchMOSを搭載し、双方のレベルシフト機能を持つ1,200V HVICを示す。1,200V NchMOSと1,200V PchMOSは同一のリサーフ分離領域内に搭載している。

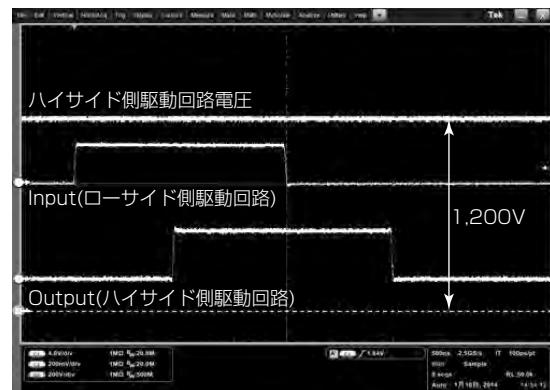

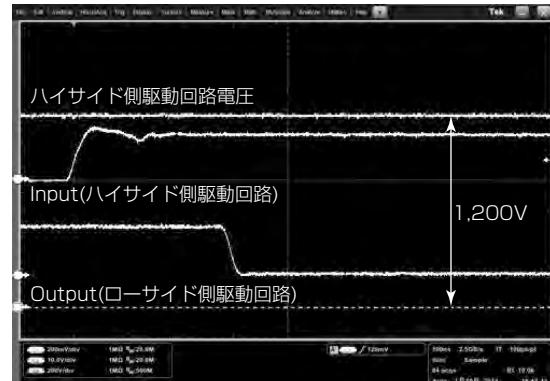

図8の1,200V HVICのレベルシフト動作波形を図9に示す。高圧側に1,200Vが印加された状態で、シフトアップ機能とシフトダウン機能が正常に動作していることが分かる。

### 4. む す び

新規ドレイン構造の開発によって高耐圧PchMOSの課題であった電流能力、寄生PNP動作を改善し、1,200Vまで動作可能な高耐圧PchMOSを実現した。従来の1,200V NchMOSに加えて1,200V PchMOSを搭載することで、1,200V HVICで初めてシフトアップ機能とシフトダウン機能の双方の信号伝達が可能となり、今後の高機能品種の展開が期待される。

図8. 1,200V PchMOS搭載HVIC

(a) シフトアップ機能動作波形

(b) シフトダウン機能動作波形

図9. 1,200V HVICのレベルシフト動作波形

### 参 考 文 献

- (1) 吉野 学, ほか: インバータシステム用1,200V HVIC技術, 三菱電機技報, **86**, No.5, 271~274 (2012)

- (2) Shimizu, K., et al.: The 2nd Generation divided RESURF structure for High Voltage ICs, Power Semiconductor Devices and IC's 2008, 20th International Symposium, 311~314 (2008)

- (3) Terashima, T., et al.: Structure of 600V IC and A New Voltage Sensing Device, Power Semiconductor Devices and IC's 1993, 5th International Symposium, 224~229 (1993)

谷岡寿一\*

古橋壮之\*\*

海老池勇史\*

# 高しきい値電圧SiC-MOSFET製造技術

Fabrication Technology of High Threshold Voltage SiC-MOSFETs

Toshikazu Tanioka, Masayuki Furuhashi, Yuji Ebiike

## 要旨

新しい半導体材料のSiC(Silicon Carbide)を用いたパワーデバイスは、パワーエレクトロニクス機器の低損失化、小型化等を実現する次世代のキーデバイスとして注目を集めている。

三菱電機では、以前からSiC-SBD(Schottky Barrier Diode)やSiC-MOSFET(Metal Oxide Semiconductor Field Effect Transistor)のデバイス開発を積極的に行っており、SiCパワー半導体モジュールの製品化を加速している。家電製品向けでは既に、ダイオードにSiC-SBDを使用したハイブリッドSiC DIPIPIM(Dual In-line Package Intelligent Power Module)を商品化した。

現在、トランジスタにSiC-MOSFET、ダイオードにSiC-SBDを用いたフルSiC DIPIPFC(Dual In-line Package Power Factor Correction)の開発を行っている。通常、DIPIPFCは正バイアス電源だけでスイッチング駆動しているため、従来のSiデバイスからの置き換えだけでモ

ジュールの動作を保証するには、SiC-MOSFETのしきい値電圧をSi-IGBT(Insulated Gate Bipolar Transistor)と同程度まで高くする必要がある。しかし、従来の製造方法によって作製されたSiC-MOSFETでは、しきい値電圧とオン抵抗の間にトレードオフが存在することから、所望のしきい値電圧を得るためにオン抵抗を犠牲にする必要があった。

今回、低いオン抵抗と高いしきい値電圧を両立できる新しいゲート酸化膜形成技術の開発に成功した。ゲート酸化膜形成工程における酸窒化処理後に水蒸気雰囲気で熱酸化を実施する“再酸化処理”工程を追加することによって、トレードオフを改善することができ、オン抵抗の増大を伴わずにしきい値電圧を上昇させることができた。

本稿では、今回開発したゲート酸化膜形成技術とSiC-MOSFETの試作結果について述べる。

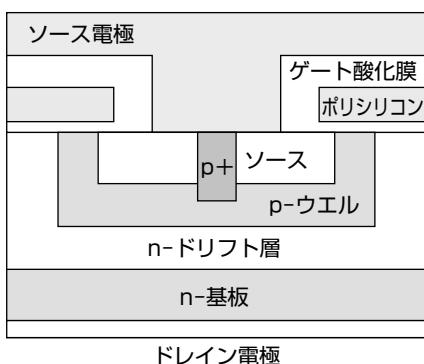

試作したMOSFETの断面図

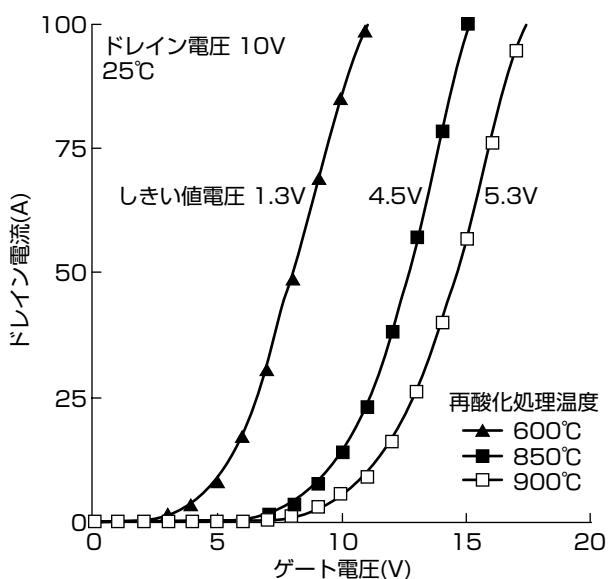

再酸化処理工程を適用したMOSFETの伝達特性

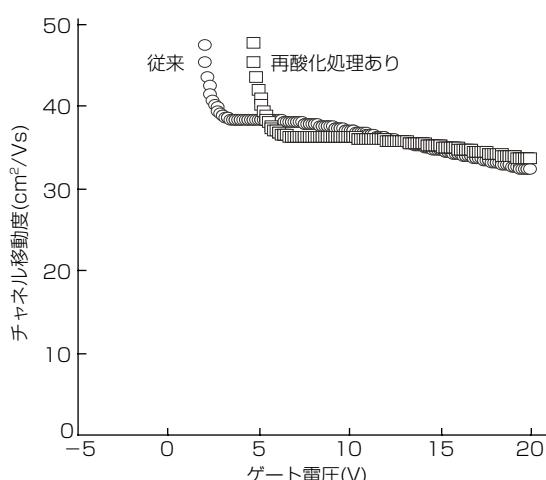

## 再酸化処理工程を適用したMOSFETの特性

左図は今回開発したゲート酸化膜形成技術を用いて試作したMOSFETの断面模式図である。右図は600～900℃で再酸化処理したMOSFETの伝達特性である。ゲート電圧に対するドレン電流の勾配を変えずに、しきい値電圧だけを上昇させることができた。

## 1. まえがき

低炭素社会を実現するため省エネルギー、省資源化に向けた取組みが世界規模で進められている。半導体パワーデバイスは電力を効率よく制御するために家電製品から産業、宇宙製品にいたる広い分野で使用されており、パワーデバイスを用いた電力変換器の低損失化や小型・軽量化による省資源化は持続可能な社会の構築に向けて大きな効果が期待される。

新しい半導体材料のSiCを用いたパワーデバイスは、パワーエレクトロニクス機器の低損失化、小型化等を実現する次世代のキーデバイスとして注目を集めている。SiCはSiよりも高い絶縁破壊電界強度を持つので、SiCを使うことによって低抵抗で高電圧なデバイスが実現できる。また、高電圧域でユニポーラデバイスのMOSFETとSBDが使用できるので、Siのバイポーラデバイスに比べてスイッチング損失を大幅に低減することができる。

当社では、以前からSiC-SBDやSiC-MOSFETのデバイス開発を積極的に行っており<sup>(1)</sup>、SiCパワー半導体モジュールの製品化を加速している。家電製品向けでは既に、ダイオードにSiC-SBDを使用したハイブリッドSiC DIPIPMを商品化し、2010年10月にSiC DIPIPMを搭載したルームエアコン“霧ヶ峰 ムーブアイ”を発売した<sup>(2)</sup>。

現在、トランジスタにSiC-MOSFET、ダイオードにSiC-SBDを用いたフルSiC DIPPFCの開発を行っている。通常、DIPPFCは正バイアス電源だけでスイッチング駆動しているため、従来のSiデバイスからの置き換えだけでモジュールの動作を保証するには、SiC-MOSFETのしきい値電圧をSi-IGBTと同程度まで高くする必要がある。しかしながら従来の製造方法では、SiC-MOSFETのオン抵抗の増大が懸念される。

本稿では、高しきい値電圧で低オン抵抗のSiC-MOSFET特性を実現するための新しいゲート酸化膜形成法と、新技術によって得られたSiC-MOSFETの特性について述べる。

## 2. 高しきい値電圧SiC-MOSFETのゲート酸化膜形成技術

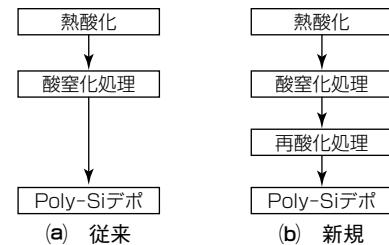

### 2.1 ゲート酸化膜形成方法

図1に従来のゲート酸化膜形成工程と新たに開発したゲート酸化膜形成工程の比較を示す。酸素雰囲気での熱酸化によって、ゲート酸化膜を形成する。熱酸化直後のSiO<sub>2</sub>/SiC界面には、チャネル移動度を低下させる界面準位が多く存在する。界面準位のうち伝導帯に近いエネルギー準位に電子がトラップされることでクーロン散乱が起こり、MOSFETのチャネル移動度はバルク中の電子移動度に比べて極めて小さいため、オン抵抗が理想的な値よりも高くなる。この界面準位を不活性化するために、当社ではNO

(一酸化窒素)雰囲気での酸窒化処理を採用している<sup>(3)</sup>。しかし、界面準位の低減とともにMOSFETのしきい値電圧は低下する。チャネル表面近傍のドーパントプロファイルを調整することによって、しきい値電圧を上昇させることは可能であるが、SiC-MOSFETが持つしきい値電圧とチャネル移動度のトレードオフによってチャネル移動度は大幅に低下する。

新規ゲート酸化膜形成工程では、酸窒化処理後に800°C程度の水蒸気雰囲気で熱酸化を実施する“再酸化処理”工程を追加した。これによってチャネル移動度への影響が小さい深いエネルギーの界面準位を導入でき、トレードオフを改善することができる<sup>(4)</sup>。深いエネルギー準位の導入量は再酸化処理条件によって制御可能であり、高しきい値電圧を再現良く得ることができる<sup>(4)</sup>。

### 2.2 メカニズム検証

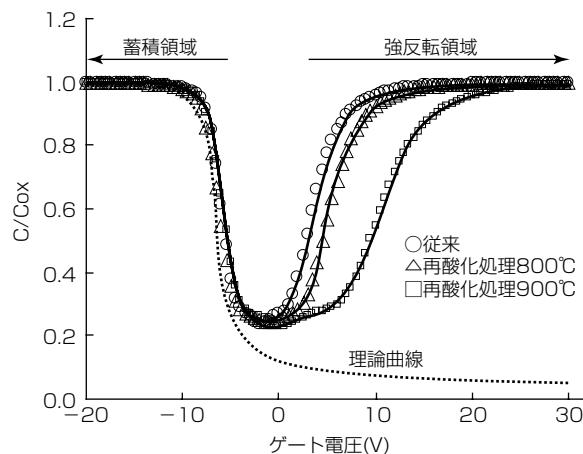

新規ゲート酸化膜形成工程を適用したMOS界面を評価するために、MOSキャパシタを作製した。通常のSiCによるMOSキャパシタでは、強反転状態で少数キャリアは室温ではほとんど生成されない。今回作製したMOSキャパシタは、強反転状態における少数キャリアの周波数応答を測定するために、キャリアを外部から供給できるn<sup>+</sup>層とp<sup>++</sup>層をp層表面に形成する構造とした。図2に従来のゲート酸化膜形成工程によって作製したMOSキャパシタと800及び900°C、30分間の再酸化処理を実施したMOSキャパシタのCV特性を示す。容量測定の条件は室温、測定周波数

図1. 従来と新規のゲート酸化膜形成工程

図2. MOSキャパシタのCV特性

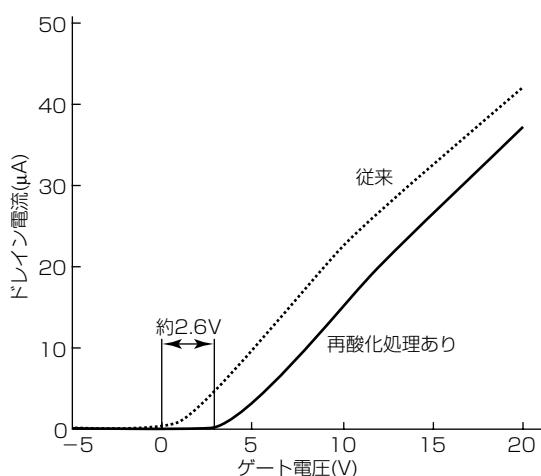

図3. 横型MOSFETの伝達特性

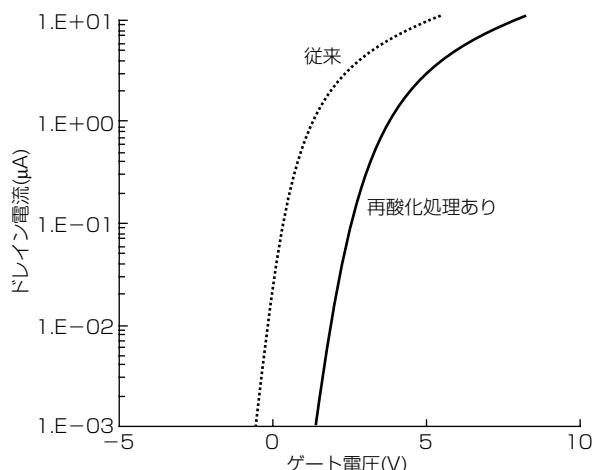

図4. 横型MOSFETのサブスレッショルド特性

図5. 横型MOSFETのゲート電圧に対するチャネル移動度

10kHzとした。CVカーブの少数キャリアの蓄積領域では、再酸化処理の有無による差は見られない。一方、CV特性の強反転領域では、再酸化処理温度が高くなるにつれ、CVカーブはゲート電圧のプラス側へシフトしている。このことから、再酸化処理工程の追加によって深いエネルギー準位が界面に導入されていることが確認できる。

図6. 高しきい値電圧SiC-MOSFETの特性

従来のゲート酸化膜形成工程によって作製した横型MOSFETと、800°C、30分間の再酸化処理を実施した横型MOSFETの伝達特性を図3に、サブスレッショルド特性を図4に、ゲート電圧に対するチャネル移動度の関係を図5に示す。800°C、30分間の再酸化処理によって、サブスレッショルド特性の変化やゲート電圧に対するドレイン電流の勾配の低下及びチャネル移動度の低下ではなく、しきい値電圧を約2.6V増加させることができた。

チャネル移動度を維持しつつ、しきい値電圧が高められており、再酸化処理工程の追加によってアクセプタ型の深いエネルギー準位が導入されていることが示されている。

### 3. SiC-MOSFETの特性としきい値電圧の安定性

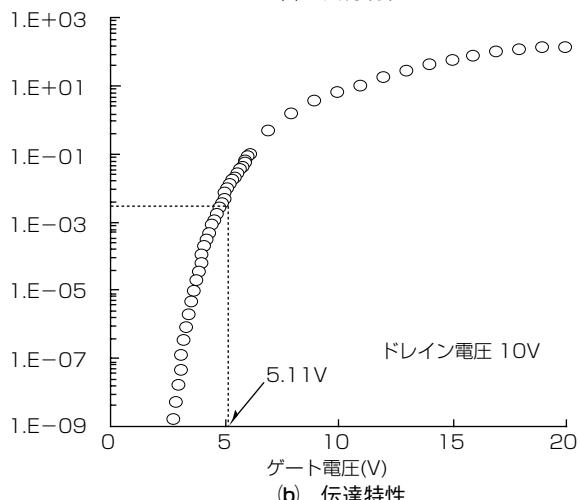

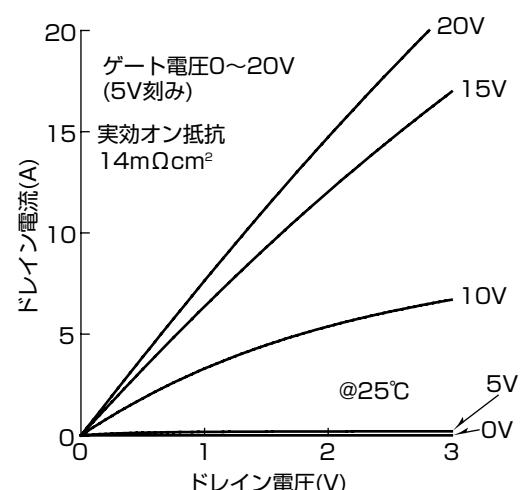

新規ゲート酸化膜形成工程を適用し、定格電圧600V、定格電流20AのSiC-MOSFETを作製した。SiC-MOSFETの活性領域、チャネル長及び、セルピッチはそれぞれ、 $7.8\text{mm}^2$ 、 $0.5\mu\text{m}$ 、 $10\mu\text{m}$ である。今回作製したSiC-MOSFETのしきい値電圧はDIPPFCでのSi-IGBTとの置き換えを前提としているため、狙いはSi-IGBTに近い5Vとした。

図6に作製したMOSFETの典型的な出力特性と伝達特

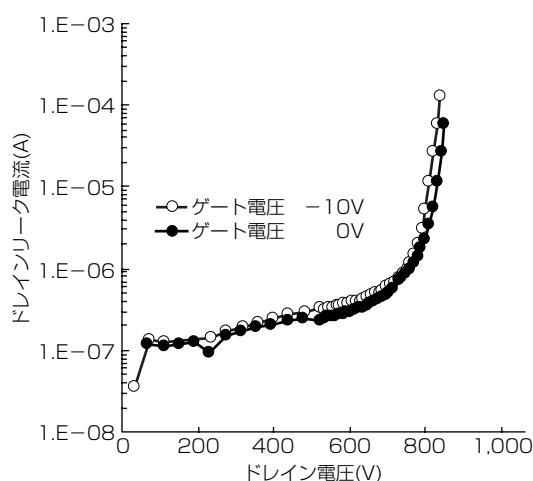

図7. 高しきい値電圧SiC-MOSFETの遮断特性

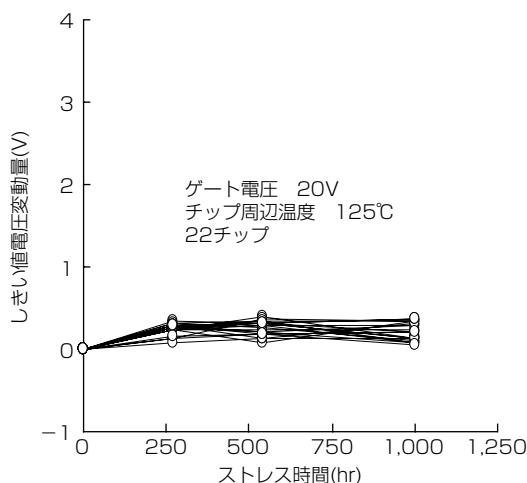

図8. HTGBストレス試験結果

性を示す。ゲート電圧15Vの場合、定格電流20A(ドレイン電流密度256A/cm<sup>2</sup>)でのオン電圧は1.68V、ゲート電圧18Vの場合は1.06Vが得られた。ドレイン電流密度100A/cm<sup>2</sup>(ドレイン電流7.8A)でのオン抵抗は5.2mΩcm<sup>2</sup>である。しきい値電圧の目安としてドレイン電圧10Vのときにドレイン電流密度100mA/cm<sup>2</sup>(ドレイン電流7.8mA)となるゲート電圧をしきい値電圧と定義した場合、得られたしきい値電圧は5.11Vである。

図7にSiC-MOSFETの室温での遮断特性を示す。ゲート電圧が-10Vと0Vの場合を比較しても、ドレインリーキ電流に差異は見られない。しきい値電圧を高めたことによって、ゲート電圧が0Vの場合でも十分な耐圧を持って

いることが確認できた。

次に高しきい値電圧SiC-MOSFETのゲート酸化膜安定性を確認するため、HTGB(High Temperature Gate Bias)試験を行った。今回作製したSiC-MOSFETはゲート電圧+15V／0Vの駆動を想定して設計したため、HTGB試験条件としては、チップ周辺温度125°Cで、ゲート電圧+20Vと-5Vを印加し、その特性の変化を調べた。図8にゲート電圧+20Vでの試験結果を示す。1,000時間経過後のしきい値電圧の変動量は最も大きいものでも+0.35Vであり、高い安定性を実証できた。

#### 4. むすび

SiC-MOSFETの課題であったしきい値電圧とオン抵抗のトレードオフを改善する新しいゲート酸化膜形成技術を開発した。従来のゲート酸化膜形成工程の酸窒化処理後に、新たに800°C程度の水蒸気雰囲気で熱酸化する再酸化処理工程を追加することで、SiC-MOSFETのしきい値電圧とチャネル移動度のトレードオフ関係が大きく改善される。この技術を適用して600V級SiC-MOSFETを作製した結果、しきい値電圧5.11V、オン抵抗5.2mΩcm<sup>2</sup>が得られ、Si-IGBTを凌駕(りょうが)するSiC-MOSFETを実現できた。またゲート酸化膜安定性の検証として、1,000時間のHTGB試験を実施し、高い安定性を確認した。今後は、特性の更なる向上によって適用製品の拡大を目指す。

#### 参考文献

- (1) 油谷直毅, ほか: SiCパワーデバイスの現状, 三菱電機技報, **86**, No.5, 267~270 (2012)

- (2) 三菱電機ニュースリリース: 三菱ルームエアコン「霧ヶ峰ムーブアイ発売のお知らせ」

<http://www.mitsubishi-electric.co.jp/news/2010/0824-d.html>

- (3) 谷岡寿一, ほか: 高温窒化処理におけるNO濃度がSiC-MOSFET特性に与える影響, 応用物理学関係連合講演会講演予稿集, Yoo54A, 56th, No.1, 438 (2009)

- (4) Furuhashi, M., et al.: Breakthrough in trade-off between threshold voltage and specific on resistance of SiC-MOSFETs, ISPSD2013, 55~58 (2013)

# SiCパワーモジュール化技術

*Technologies for SiC Power Module*

Takami Otsuki, Takahiro Inoue, Koji Tamaki, Yoshiko Obiraki

大月高実\* 大開美子\*\*\*

井上貴公\*

玉木恒次\*\*

## 要 旨

低炭素化社会の実現に向けて、FA(Factory Automation)、家電、電鉄等のパワーエレクトロニクス機器の省エネルギー・小型化競争の加速が予想される。パワーデバイスに対しても、これら要求への対応としてワイドギャップ半導体であるSiC(Silicon Carbide)を用いたパワーデバイスの開発が不可欠となっている。三菱電機では全社的なプロジェクト体制を構築し、社内パワーエレクトロニクス事業部門との連携によってSiCデバイスを搭載したパワーモジュールの開発に取り組んでいる。

本稿では、SiCパワーモジュール化技術として次の2点について述べる。

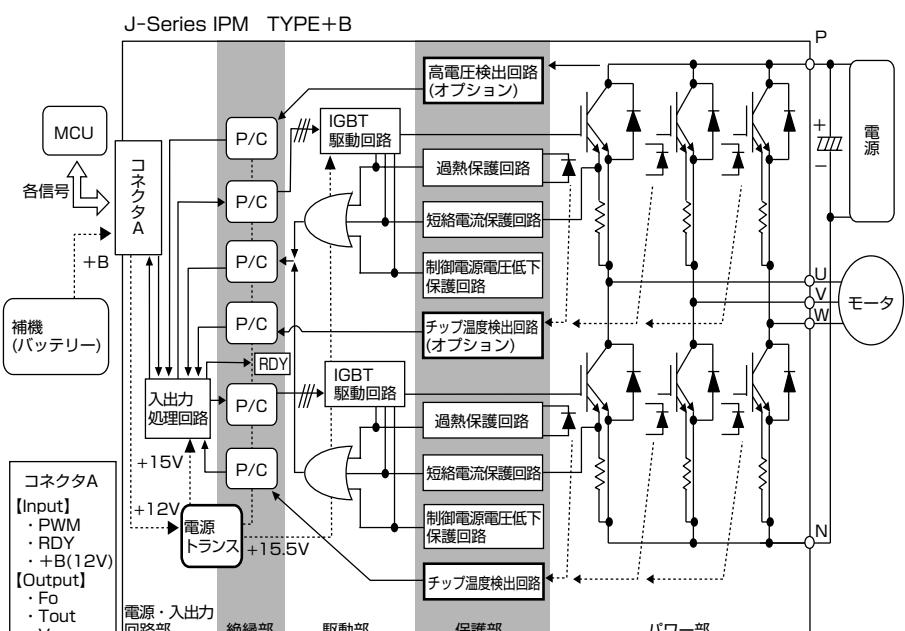

- (1) インテリジェントパワーモジュール(IPM)化

従来のSiパワーモジュールと同じ保護機能を搭載。

・制御電源電圧低下保護／過熱保護／短絡保護

- (2) 小型化・大容量化

モジュールの小型化と大容量化に伴う課題と解決案の提示。

・サージ電圧抑制(インダクタンスの低減)

・並列間電流均等化(電流アンバランスの抑制)

フルSiC-IPM(1,200V/75A/6in1)

フルSiCパワーモジュール(1,200V/800A/2in1)

## 産業用フルSiC-IPMとフルSiCパワーモジュール

大幅な電力損失低減で産業機器の高効率化・小型化に貢献するパワーモジュール。

## 1. まえがき

省エネルギー化の気運がますます高まる中、パワーデバイスが注目されて久しいが、現在使用されているSiデバイスはその材料物性で決まる理論限界に近付いている。今後そのSiに代わると期待されているものに、ワイドギャップ半導体であるSiCやGaN(Gallium Nitride)がある。当社では、全社的なプロジェクト体制を構築し、SiCデバイスを搭載したパワーモジュールの開発を進めてきた。

本稿では、SiCデバイスを搭載したパワーモジュール化の技術として、①従来のSiデバイス搭載品と同じ保護機能を搭載したインテリジェントパワーモジュール(IPM)化、②モジュールの小型化・大容量化、の2点について述べる。

## 2. IPM化

### 2.1 IPMの特徴と内部構成

従来のSiデバイスを搭載したIPM(Si-IPM)は、各種保護機能(制御電源電圧低下保護／過熱保護／短絡保護)を持っている。SiCデバイスを搭載したIPM(SiC-IPM)に対してもそのコンセプトを踏襲し、各種保護機能を搭載させる。

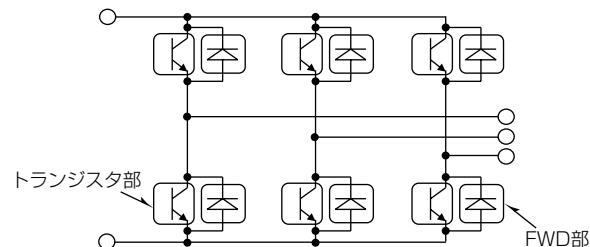

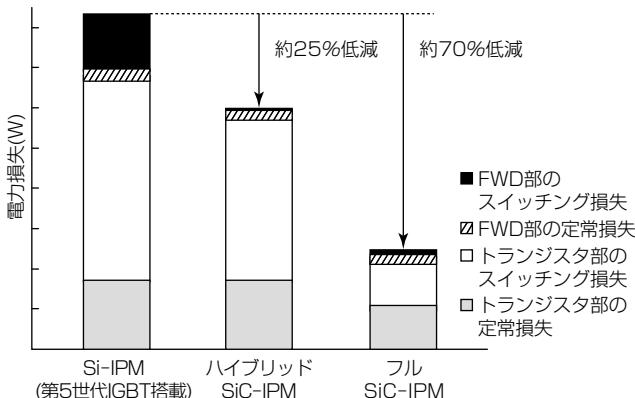

IPMの内部構成を図1に示す。SiC化については、主にFWD(Free Wheeling Diode)部にSiC-SBD(Schottky Barrier Diode)を搭載するハイブリッドSiC化(ハイブリッドSiC-IPM)と、トランジスタ部にSiC-MOSFET(Metal Oxide Semiconductor Field Effect Transistor)、FWD部にSiC-SBDを搭載するフルSiC化(フルSiC-IPM)がある。ハイブリッドSiC-IPMすることで、FWD部のリカバリ一損失低減が可能であり、フルSiC-IPMすることで、さらにトランジスタ部のスイッチング損失及び定常損失低減が可能となる。以降では、フルSiC-IPMについて述べる。

### 2.2 保護機能の搭載

#### 2.2.1 保護機能

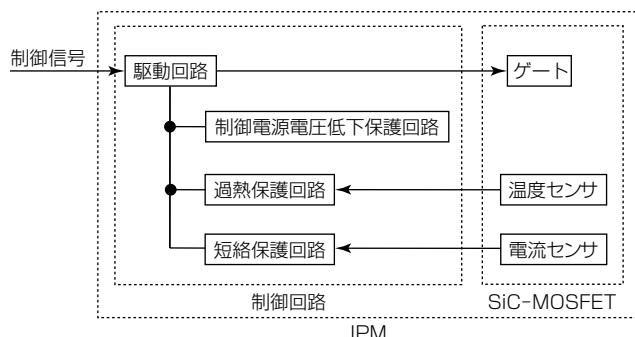

図2にIPMのブロック図を示す。SiC-IPMで搭載している保護機能は、次の3種類がある。

- ①制御電源電圧低下保護

- ②過熱保護

- ③短絡保護

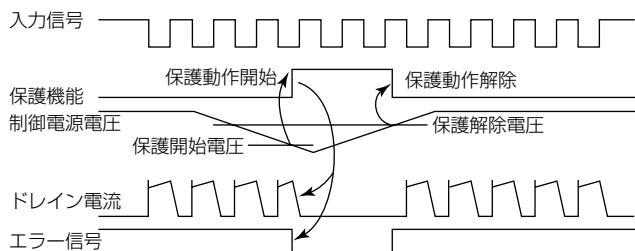

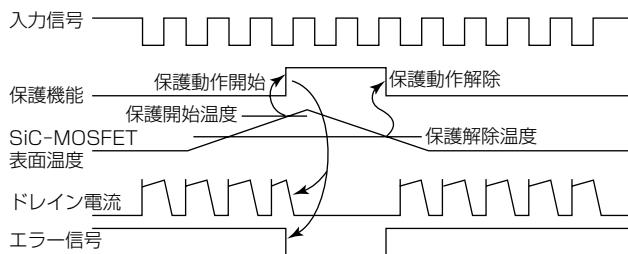

制御電源電圧低下保護とは、制御電源電圧が低下したときに生じるSiC-MOSFETのドレイン・ソース間電圧VDS(on)損失増加(=熱破壊)を防止するために、制御電圧を検出し、設定電圧以下になると、SiC-MOSFETを強制的にオフする機能である(図3)。

過熱保護とは、熱破壊を防止するため、SiC-MOSFETの表面温度を直接検出(温度センサ)し、設定温度以上になると、SiC-MOSFETをオフする機能である(図4)。

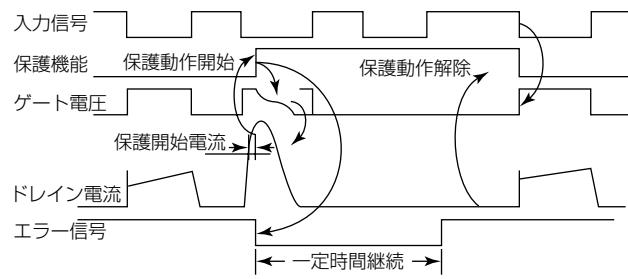

短絡保護とは、短絡破壊を防止するために、SiC-MOSFETのドレイン電流を検出し(電流センサ)、設定電流以

上になるとSiC-MOSFETをオフする機能である(図5)。

今回、従来のSi-IPMと同じこれら3種類の保護機能を搭載したSiC-IPMを開発した。

図1. Si-IPM(6in1)内部構成

図2. IPMブロック図

図3. 制御電源電圧低下保護シーケンス

図4. 過熱保護シーケンス

図5. 短絡保護シーケンス

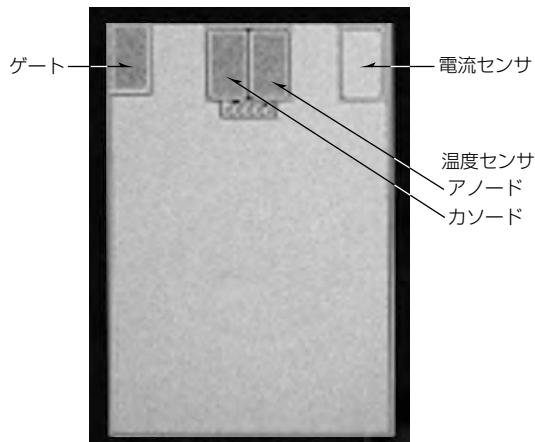

## 2.2.2 チップの外観

先に述べた保護機能を実現するための、各種センサを搭載したSiC-MOSFETの外観を図6に示す。Si-IGBT(Insulated Gate Bipolar Transistor)と同じように、電流センサ及び温度センサを搭載している。なお、温度センサはチップ上に設けており、表面温度をいち早く検知することが可能である。

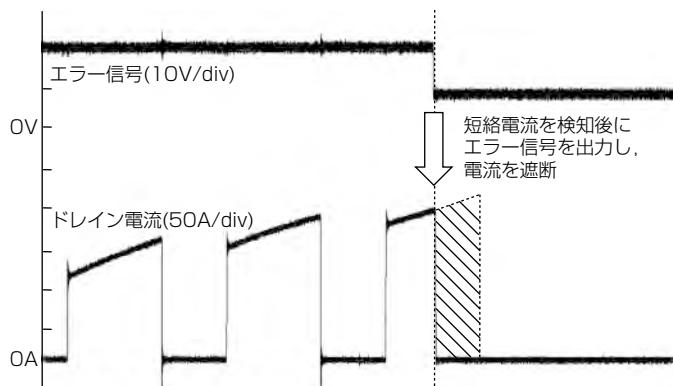

## 2.2.3 保護機能動作の実例

保護機能動作の一例として、図7に誘導負荷短絡保護時

図6. SiC-MOSFET

図7. 誘導負荷短絡保護時の波形

条件:  $V_{cc}=600V$ ,  $I_0=31Arms$ (インバータ15kW想定),  $f_c=15kHz$ , 効率=0.9, 變調率=1, 三相変調,  $T_j=125^\circ C$

図8. 損失低減効果

の波形を示す。短絡電流を検知した際にエラー信号が出力され(上段の波形が“高”→“低”へ切り替わり)，同時に電流(下段の波形)が遮断されており，短絡保護機能が動作していることが確認できる。

## 2.3 損失低減効果

先に述べたようにトランジスタ部及び／又はFWD部をSiからSiCに切り替えることで、損失の低減が見込まれる。

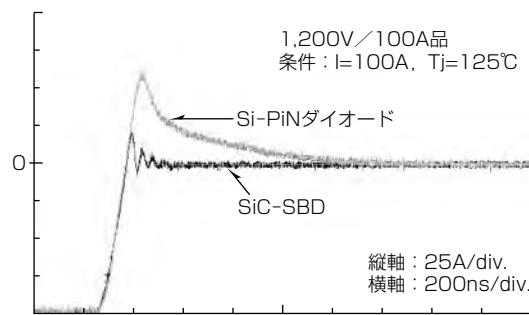

第5世代のIGBTを搭載した定格1,200V/75AのSi-IPMに対する、ハイブリッドSiC-IPM、フルSiC-IPMの損失比較結果を図8に示す。Si-IPMと比較して、ハイブリッドSiC-IPMは約25%低減、フルSiC-IPMは約70%低減を実現している。この図から、ハイブリッドSiC化によってFWD部のスイッチング損失つまりリカバリー損失が低減できており、フルSiC化によって、さらにトランジスタ部のスイッチング損失及び定常損失を低減できていることが確認できる。

このように、Si-IPMのコンセプトを継承しつつ、低損失を実現するSiC-IPMの開発を進めている。

## 3. モジュールの小型化・大容量化

### 3.1 小型化

SiCを適用することのメリットとして、損失低減以外にもモジュールの小型化が図れることが挙げられる。

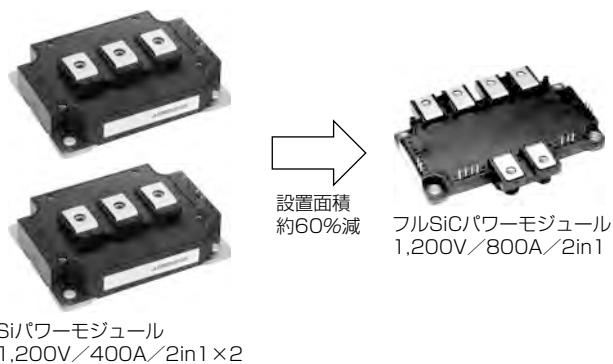

SiCはSiと比較して絶縁破壊電界強度が10倍程度高いので、ドーピング密度を高めてオン抵抗を小さくすることができる<sup>(1)</sup>。このため、ある一定の電流値を得ようとする場合、Siと比較してチップサイズの縮小が可能である。その結果、モジュールサイズの小型化が可能となる。

その一例を図9に示す。SiパワーモジュールをフルSiCパワーモジュールに置き換えることで、設置面積が約60%削減可能となった。

### 3.2 大容量化

#### 3.2.1 課題

図9で示したようにSiパワーモジュールでは2並列必要であった容量を、フルSiCパワーモジュールでは1並列で構成できる。つまり、小型化に加え大容量化が可能となっ

図9. モジュール小型化

図10. モジュール内部並列化

図12. 電磁界解析モデル

図11. モジュール内電磁干渉による電流アンバランス

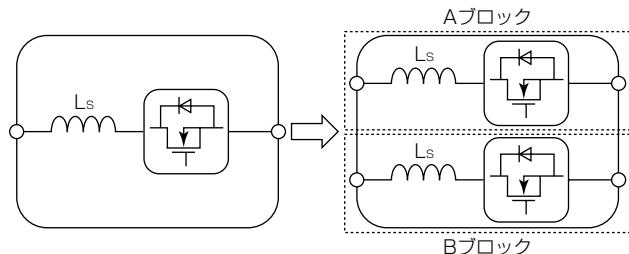

た。一方で、大容量化する際にはターンオフ時の電流変化率増大に伴うサージ電圧が課題となる。インダクタンスはSiパワーモジュールでは2並列によってそれ自体の約半分となるが、1並列のフルSiCパワーモジュールではSiパワーモジュールと比較して、インダクタンスが大きくなるため、より高いサージ電圧が発生する可能性がある。このため、大容量化する際にはモジュール内部のインダクタンスを低減する必要がある。

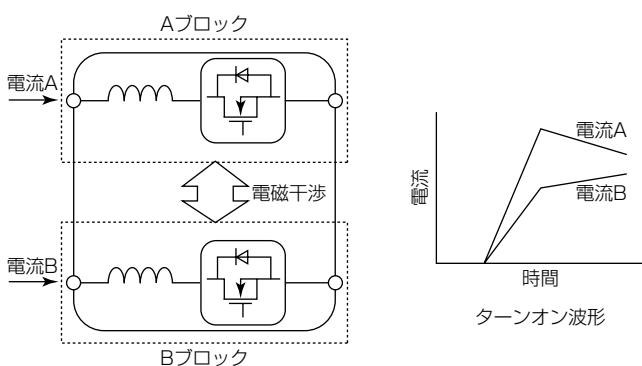

### 3.2.2 モジュール内部インダクタンス低減

モジュール内部を2ブロックに分け並列化することで、インダクタンスの低減を実現した(図10)。これによってサージ電圧を抑制でき、高速スイッチングが可能となった。

### 3.2.3 並列化に伴う課題と解決策

モジュール内部を2ブロックに分け並列化した場合、2ブロック間の電磁干渉に不均一があると電流がアンバランスとなる。特に、SiC-MOSFETではSi-IGBTと比較して高速スイッチングとなるので、アンバランスがより顕著となる(図11)。

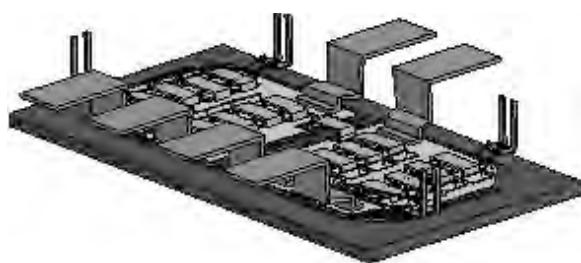

図13. 並列間電流解析

そこで、電磁界解析を用いて、2ブロック間の電磁干渉が均一となるよう、チップ、各種配線を構成した(図12)。この解析の結果、電流アンバランスが小さくなっていることを確認した(図13)。

このように、SiC適用による新たな課題を解決しつつ、大容量SiCパワーモジュールの開発を進めている。

## 4. むすび

SiCパワーモジュール化技術について述べた。省エネルギー製品のニーズが高まる中、この技術は市場の期待に沿うものであると考える。将来的にはSiに代わるデバイスとして期待されていることもあり、今後はSiC搭載製品を市場に送り出していくことで、更なる省エネルギー社会の実現へ貢献していく所存である。

## 参考文献

- (1) 松波弘之, ほか: 半導体SiC技術と応用, 日刊工業新聞社 (2003)

# 高周波用ハイブリッドSiCモジュール

宮崎裕二\*

*Hybrid SiC Module for High Frequency Application*

Yuji Miyazaki

## 要 旨

省エネルギーが単なる経済性の問題ではなく、地球規模の環境保護と結びつけて人々に意識され始めるようになって久しい。三菱電機はモータ駆動用のインバータや電源等に幅広く使用されるパワー半導体デバイスの分野で省エネルギー性能を追求した製品を提供してきた。IGBT (Insulated Gate Bipolar Transistor) は幅広いニーズに応えることのできる汎用性の高いパワーデバイスである。現在、当社はIGBTの最新形態であるCSTBT(Carrier Stored Trench-Gate Bipolar Transistor)の製品開発を行い、多くの応用分野で高いシェアを持っている。その一方で、新しい半導体材料を用いたパワーデバイスの開発を進め、市場への投入を果たしてきた。従来のSi(Silicon)に比べ優れ

た材料特性を持つSiC(Silicon Carbide)は、今後の更なる展開が期待できる半導体材料である。

本稿では、電源システムなどに用いられる、高周波スイッチング動作に最適なパワーモジュールの開発について述べる。次のような特長によって、ターゲット市場の要求にベストフィットした製品となっている。

- (1) Si-IGBTの従来技術と、SiC-SBD(Schottky Barrier Diode)の組合せによるハイブリッド構成とした。

- (2) ソフトスイッチング技術との親和性を確保した。

- (3) 従来品“NFHシリーズ”との外形互換性を持たせ、かつSiCデバイスの高速スイッチングに対応した低インダクタンスパッケージを採用した。

## 高周波用ハイブリッドSiCモジュール

既存の技術と先進的なSiCデバイス技術を組み合わせることによって、高周波スイッチング用パワーモジュールとして優れたパフォーマンスを実現した。太陽光発電用パワーコンディショナ、無停電電源(UPS)、医療機器用電源等への適用でメリットが大きい。

## 1. まえがき

パワーエレクトロニクス機器へのパワーデバイスの適用範囲は広いが、おおまかにモータ駆動用途と電源用途に大別される。電源用途のうち主なものとしては、太陽光発電用パワーコンディショナ、無停電電源(UPS)、X線CT(Computed Tomography)／MRI(Magnetic Resonance Imaging)等の医療機器用電源、溶接機、誘導加熱機、レーザ加工機等がある。これらの電源システムでは、高調波の抑制を目的とした交流リアクトルやフィルタ回路、電力変換を目的とした出力トランス、また昇圧回路を構成する直流リアクトルを併用することが多い。このようなりアクトル部品は一般に体積と質量が大きいため、システムの多くの部分が占有され、また大容量になるほど顕著となっているのが現状である。このことが、パワーエレクトロニクス機器及び周辺システムの更なる小型・軽量化及び低コスト化を阻む要因の一つとなっている。

## 2. スイッチングの高周波化

### 2.1 市場におけるメリット

パワーエレクトロニクス機器設計の立場からすると、パワーデバイスのスイッチング周波数を大きくすることは、単に周波数を可聴域外に設定すること以上の重要な意味合いを持っている。すなわち、スイッチング周波数を大きくすることで、磁気飽和の問題を軽減することができ、又はより小さいインダクタンス値の部品を選定できることから、リアクトル部品をより小型化することができる。これによって機器の小型化、低コスト化はもちろんのこと、外付けリアクトル部品の機器への内蔵やフィルタの高性能化等、新しい付加価値を与えることも可能となる。

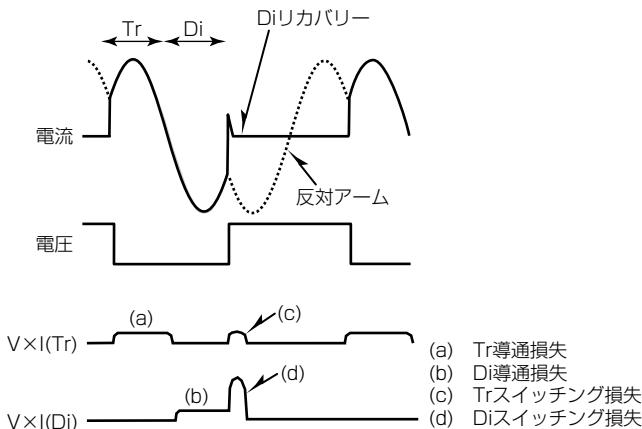

### 2.2 パワーモジュールの対応

しかしながら通常の場合、パワーデバイスにとってスイッチング周波数を大きくすることは、オン・オフの切り替わり時に過渡的に発生するスイッチング損失が増加するため、発熱や効率の低下につながる。したがって、インバータやサーボアンプ等のモータ駆動に一般的に用いられる導通損失重視型のパワーデバイスを適用した場合、スイッチング損失が支配的となり、高周波化への対応に無理が生じる。このため当社は、第五世代IGBT(CSTBT)を最適化することによって高周波スイッチングに対応したIGBTモジュールNFHシリーズを2004年から提供してきており<sup>(1)</sup>、太陽光発電用パワーコンディショナ、UPS、医療機器用電源等の高周波スイッチングを行う応用機器で多くの実績を積んでいる。

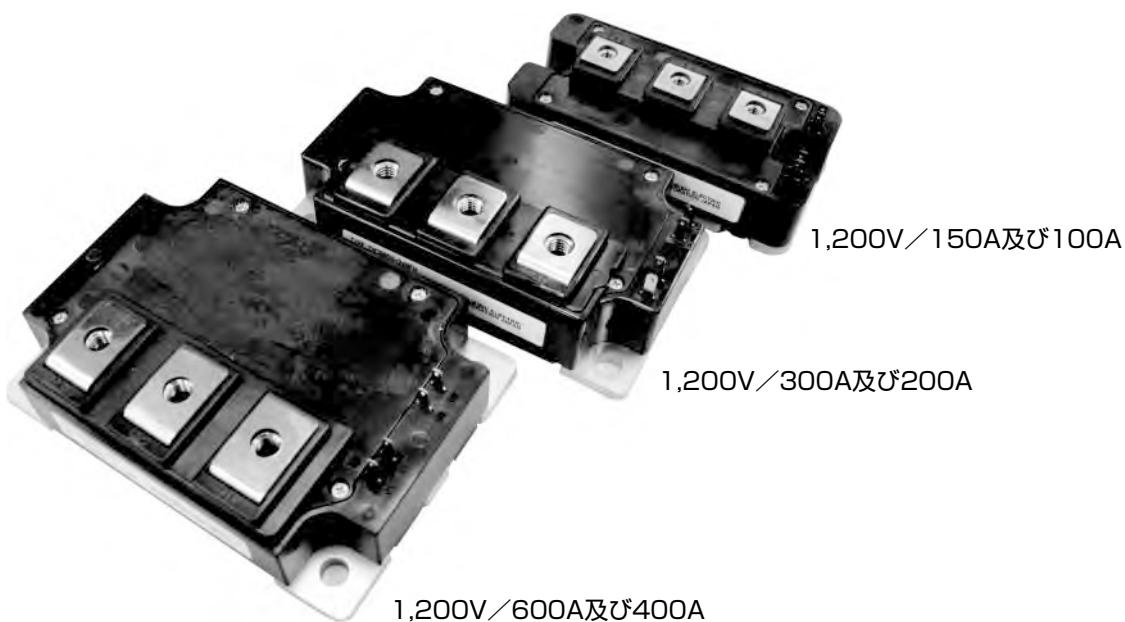

## 3. ハイブリッドSiCモジュールの開発

### 3.1 SiCデバイス

SiCは、パワーデバイスで従来のSiに代わる新しい半導体材料である。絶縁破壊電界強度がSiに比べておよそ一桁高いという特長を生かし、Siデバイスでは実現不可能であった高耐圧のユニポーラデバイスを実現できる。当社はSiC材料を用いたパワーデバイスとしてSiC-MOSFET(Metal Oxide Semiconductor Field Effect Transistor)とSiC-SBDの開発を行い、実用化してきた。SiC-MOSFET及びSiC-SBDのパワーエレクトロニクス機器への適用で、モータ駆動用のインバータや電源等、様々な用途で電力損失の大規模な低減が可能になる。特に、スイッチング損失が非常に小さいというユニポーラデバイスの特長から、高周波用のデバイスとして一層優れたパフォーマンスが期待できる。図1はターンオンスイッチング時の電流波形を、Si-PiN(P-intrinsic-N)ダイオードとSiC-SBDで比較したものである。PN接合を備えたバイポーラデバイスであるSi-PiNダイオードでは、導通時に蓄積された少数キャリア(ホール)がスイッチング時に印加された電界によって排出されるため、スパイク状の過渡的な電流(リカバリー電流)が存在し、スイッチング損失増加の一要因となっている。一方SiC-SBDではユニポーラ動作であるためリカバリー電流は存在せず、デバイスに寄生する静電容量の充電電流だけとなるため、スイッチング損失は極めて小さい。

### 3.2 モジュール設計

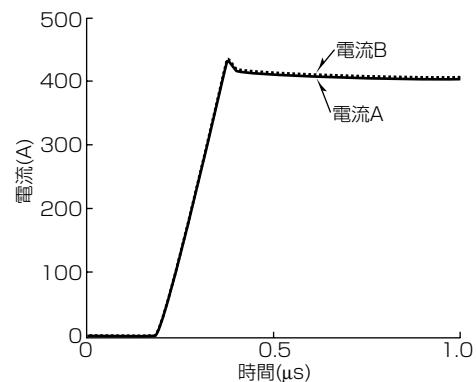

高周波用IGBTモジュールNFHシリーズの後継となる高周波用ハイブリッドSiCモジュールを開発した。電源機器システムの更なる高周波化に対応するため、ダイオード部分にはSiC-SBDを搭載した。一方、スイッチ部分については応用機器の動作上、全損失に対する導通損失の占める割合が比較的小ないことから、導通損失低減を狙ったSiC-MOSFETを使用する意味合いは薄い。コストとの両立性を重視しNFHシリーズで実績のあるSi-IGBTを採用した。ライフタイムコントロール技術の適用によってターンオフ損失と飽和電圧特性を制御し、高周波用IGBTデバイスとして最適化を行っている。

図1. ターンオンスイッチング時の電流波形比較

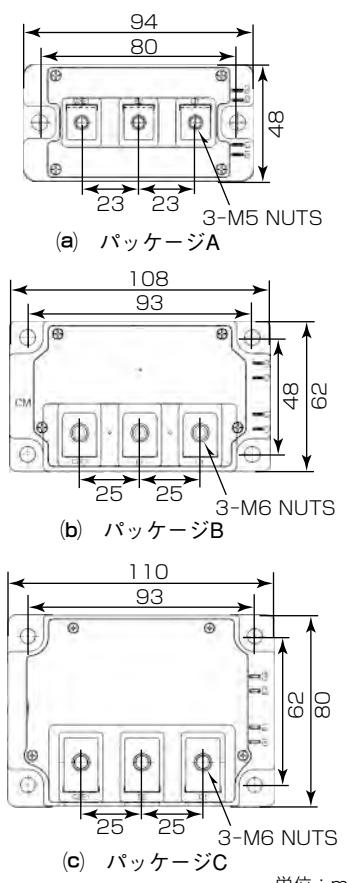

製品ラインアップは、市場要求の高い定格電圧1,200V、定格電流100~600Aとした(表1)。またパッケージ形状(図2)については、従来のNFHシリーズと完全に互換性を持たせた結果、従来品からの置き換え使用が可能である。また、IGBTの特性は従来品と同等であるため、置き換えに当たっては駆動回路の見直しも不要である。

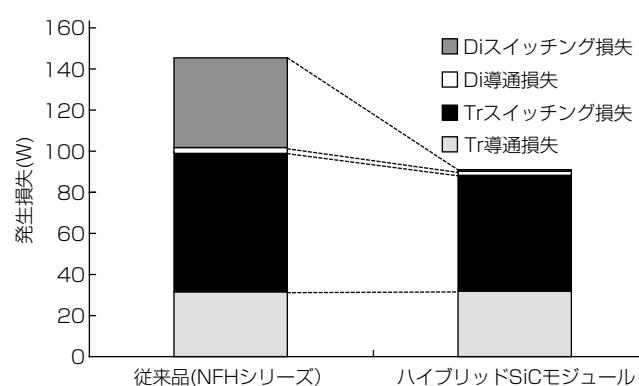

### 3.3 発生損失の低減とスイッチングの高周波化

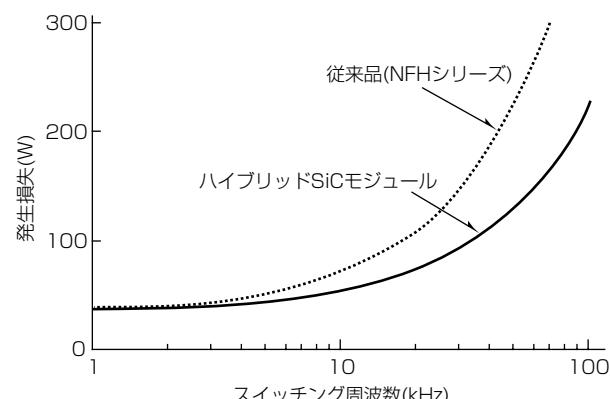

素子定格1,200V/100Aのパワーモジュールを動作させたときの発生損失(1/2モジュールあたり)の内訳を図3に示す。一般的な電源システムへの応用を想定し、正弦波出力電流30A(実効値)、スイッチング周波数は30kHzとした。ハイブリッドSiCモジュールを使用することで、主にダイオードスイッチング損失を大幅に低減した。この動作条件で、従来品(NFHシリーズ)に比べ、パワーデバイスにおける損失を40%近く削減することが可能である。これはパワーエレクトロニクス機器全体の電力変換効率の向上に貢

献するのに十分な量である。その一方で、損失低減をスイッチングの高周波化に充てることも可能である。図4は、スイッチング周波数と発生損失の関係を比較したものである。周波数以外の動作条件は図3と同じとした。これによると、パワーモジュールの発生損失が同等という前提で、ハイブリッドSiCモジュールのスイッチング周波数を従来品(NFHシリーズ)のおよそ2倍まで大きくすることができる。

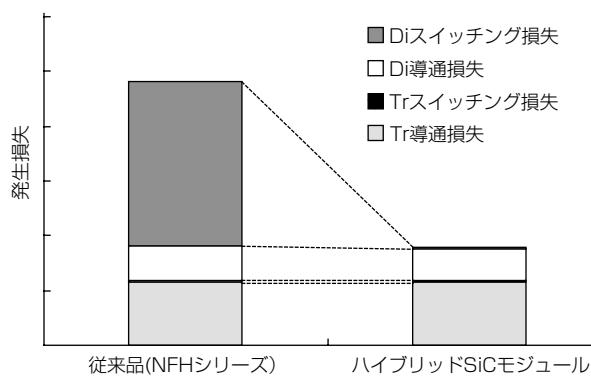

### 3.4 ソフトスイッチング技術との親和性

パワーエレクトロニクスの分野では、高周波化によるスイッチング損失増加の問題を軽減する回路的手段としてソフトスイッチング技術が導入されている。代表的なものにZVS(Zero-Voltage Switching)があり、LC共振現象を利用することでスイッチング時の電流・電圧の交差を避け、パワーデバイスにおけるスイッチング損失を大幅に改善することができる<sup>(2)</sup>。しかしながら、従来品ではトランジスタにおけるスイッチング損失を劇的に低減できても、Si-PiNダイオードにおけるリカバリー電流のため、ダイオードスイッチング損失低減に限界があった。図5に示す発生損失内訳は、医療X線CT用電源などに一般的に用いられる電流共振型インバータの動作を模擬したシミュレーション結果である。図6に示す動作で、負荷の共振周波数を50kHz、正弦波出力電流のピーク値をモジュール電流定格の60%としてある。Siを用いた従来品(NFHシリーズ)で

表1. 製品ラインアップ

| 形名             | 電圧定格   | 電流定格 | 回路     | パッケージ |

|----------------|--------|------|--------|-------|

| CMH100DY-24NFH | 1,200V | 100A | 2 in 1 | A     |

| CMH150DY-24NFH |        | 150A |        |       |

| CMH200DU-24NFH |        | 200A |        | B     |

| CMH300DU-24NFH |        | 300A |        |       |

| CMH400DU-24NFH |        | 400A |        | C     |

| CMH600DU-24NFH |        | 600A |        |       |

図2. パッケージ形状

図3. 発生損失の内訳(30kHz)

図4. スイッチング周波数と発生損失の関係

図5. 発生損失の内訳(電流共振型インバータ)

図6. 電流共振型インバータの動作

は、モジュールの全損失に対してダイオードのスイッチング損失の占める割合が非常に大きい。それに対し、ハイブリッドSiCモジュールはリカバリーディオードが存在せず、ダイオードスイッチング損失をほぼゼロとすることができます。つまりモジュールでの損失はほぼ導通損失だけとなり、高周波化による損失悪化がほとんどなくなる。このことから、高周波化を目的として採用されているソフトスイッチング技術との組合せでも、効果は極めて大きい。

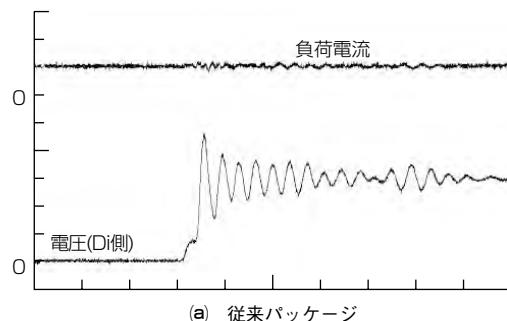

### 3.5 パッケージインダクタンスの低減

パワーモジュールでは、スイッチング時の高い電流変化率 $di/dt$ と回路の寄生インダクタンス $L_s$ によるスパイク状のサージ電圧や、デバイスの寄生容量と $L_s$ に起因した振動波形が発生する。スイッチングスピードが速い高周波用パワーモジュールで、この現象はより顕著となり、過電圧や誤動作等を引き起こす場合がある。高周波用パワーモジュールに必要な高速スイッチング性能を維持したままこれらを軽減するためには、パッケージ内の寄生インダクタンスを低減することが望ましい。高周波用ハイブリッドSiCモジュールでは一部品種で、パッケージ内の電極配線の引き回しを最小化することによってパッケージ内の $L_s$ を30%以上低減した。ハイブリッドSiCモジュールのチップ組合せ(Si-IGBT及びSiC-SBD)を、従来パッケージ及び $L_s$ 低減パッケージの両方に搭載した場合のターンオン

(a) 従来パッケージ

(b) Ls低減パッケージ

1,200V/100A品 測定条件:  $I_c=100A$ (ターンオン),  $V_{cc}=600V$

負荷電流(100A/div), 電圧(200V/div), 時間(100ns/div)

図7. インダクタンスの低減による効果

スイッチング時の波形比較を図7に示す。SiC-SBD側の電圧に現れるサージピーク電圧と、継続的な振動波形が大幅に改善された。SiCデバイスの高速スイッチングに相応したパッケージに仕上がっている。

## 4. むすび

高周波用ハイブリッドSiCモジュールは電源機器への適用をターゲットとしたパワーモジュールである。既存のSiデバイスと先進的なSiCデバイス技術及びパッケージの低インダクタンス設計を組み合わせることによって、従来の高周波モジュール(NFHシリーズ)とは一線を画す性能を得ることに成功した。周波数30kHzの動作で、パワーデバイスにおける損失は約40%低減し、電力変換効率の向上に貢献する。また、高周波領域での低損失性能を生かし、スイッチング周波数を従来品のおよそ2倍にすることが可能である。リアクトル部品を更に小型化することが可能となり、機器の小型・軽量化、低コスト化に貢献する。今後も多様化するユーザーからのニーズを反映した、付加価値の高い製品開発を行っていく。

## 参考文献

- (1) 田畠光晴, ほか:低駆動電力新トレンチIGBTモジュール“NFシリーズ”, 三菱電機技報, 77, No.9, 563~566 (2003)

- (2) 宮崎裕二, ほか:高周波用IGBTモジュール“NFMシリーズ”, 三菱電機技報, 80, No.6, 411~414 (2006)

濱田憲治\*

日野史郎\*\*

木谷 剛\*\*\*

# 3.3kV耐圧SiC-MOSFETの低抵抗化技術

Low On-resistance SiC-MOSFET with Blocking Voltage of 3.3kV

Kenji Hamada, Shiro Hino, Takeshi Kitani

## 要 旨

昨今、Siに代わる新しい半導体材料としてSiC(Silicon Carbide)が注目されている。SiCをパワーデバイスとして用いることで現状のSiパワーデバイスを凌駕(りょうが)する低抵抗化・高電圧化が可能になる。

三菱電機は600Vから1.7kV耐圧のSiCユニポーラデバイスとして、SiC-MOSFET(Metal Oxide Semiconductor Field Effect Transistor)及びSiC-SBD(Schottky Barrier Diode)の低電力損失化や高機能化・大電流化の開発を進めている。同時にSiCパワーデバイスのインバータへの適用といった応用技術開発を並行して進めており、効率改善や機器の小型化を実証している。

さらに、高耐圧が要求される産業用や電鉄車両用として

も、SiCユニポーラデバイス技術を享受することができる。当社はこれまでにSiC-SBD及びSi-IGBT(Insulated Gate Bipolar Transistor)を組み合わせた3.3kV耐圧のハイブリッドSiCモジュールを試作し、1.5kV／2kAのスイッチング動作を実証している。モジュールの更なる高効率化を図るためにには、Si-IGBTのSiCスイッチング素子への置き換えが必要であり、3.3kV耐圧のSiC-MOSFETの実現が切望されている。

本稿では、独自に開発した低抵抗化技術を含め、当社における3.3kV耐圧のSiC-MOSFETの開発内容について述べる。

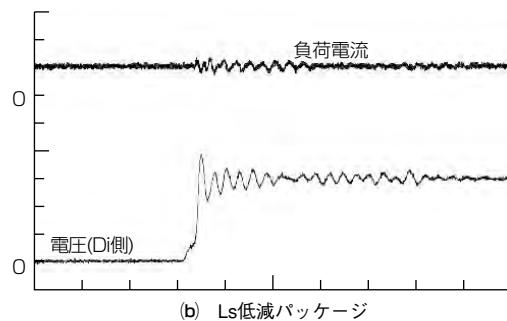

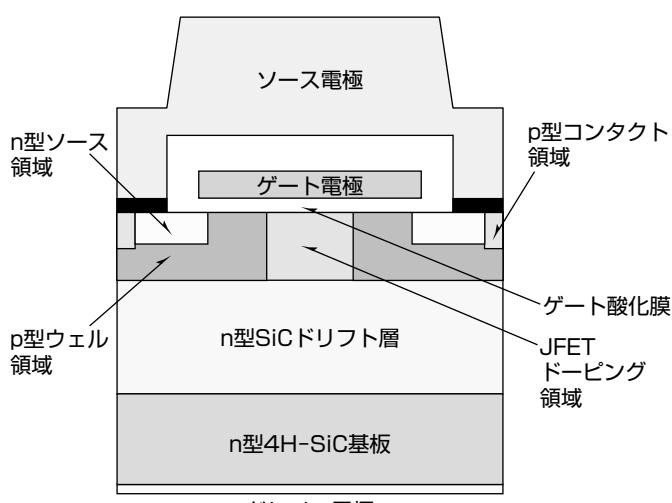

## 3.3kV耐圧SiC-MOSFETのデバイス構造と電気特性

n型SiCドリフト層表面の不純物濃度を部分的に高濃度化する独自の低抵抗化技術を用いて、3.3kV耐圧SiC-MOSFETを開発した。セル構造パラメータ及びイオン注入条件を最適に設計することで、実効オン抵抗 $14\text{m}\Omega\text{cm}^2$ 、アバランシエ降伏電圧約3.9kVを持つMOSFETが得られ、3.3kV耐圧を十分に確保しつつ低抵抗なMOSFETを実現した。

## 1. まえがき

電力エネルギーを高効率で最適に制御するパワーエレクトロニクス技術は、これまで省エネルギー、省資源に大きく貢献してきた。その中で中心的役割を果たしているのがパワーデバイスである。パワーデバイスに用いられる半導体材料としてはSiが一般的であるが、その材料物性に起因する性能限界に近づきつつあるのが現状である。

昨今、Siに代わる新しい半導体材料としてSiCが注目されている。ワイドバンドギャップ半導体であるSiCは、Siに比べて絶縁破壊電界強度や熱伝導度が高いといった特長を持つ。SiCをパワーデバイスとして用いることでSiパワーデバイスを凌駕する低抵抗化・高電圧化が可能になる。

最近では耐圧が10kVを超えるSiCパワーデバイスの試作例が報告されており、これはSiパワーデバイスでは実現不可能な電圧領域である。10kV以上の電圧領域では、デバイスの低抵抗化のために電子と正孔による伝導度変調の効果を利用したIGBTやPiN(P-intrinsic-N)ダイオード等のSiCバイポーラデバイスが用いられるのが一般的である。

一方で、3.3kV以下の低い電圧領域では、Siバイポーラデバイスに比べて低抵抗かつ高速スイッチング動作が可能なMOSFETやSBD等のSiCユニポーラデバイスが注目を浴びている。600Vから1.7kV耐圧のSiC-MOSFETに関しては数多くの報告例があり、これらをインバータモジュールに適用することで、効率改善や機器の小型化が実証されている。3.3kV耐圧のパワーデバイスが要求される産業用や電鉄車両用としても、SiCユニポーラデバイス技術を享受することができる。当社はこれまでに、SiC-SBD並びにSi-IGBTを組み合わせた3.3kV耐圧のハイブリッドSiCモジュールを試作し、1.5kV／2kAのスイッチング動作を実証している<sup>(1)</sup>。モジュールの更なる高効率化を図るために、Si-IGBTのSiCスイッチング素子への置き換えが必要であり、3.3kV耐圧のSiC-MOSFETの実現が切望されている。

本稿では、独自に開発した低抵抗化技術を含め、当社における3.3kV耐圧のSiC-MOSFETの開発内容について述べる。

## 2. 3.3kV耐圧SiC-MOSFETの作製

### 2.1 デバイス構造

SiC-MOSFETの基本構造は、SiのパワーMOSFETに広く採用されているDMOSFET(Double-diffused MOSFET)構造である。Siでは不純物の熱拡散によってこの構造を形成するのに対して、SiCでは不純物の拡散係数が小さいことから、選択的なイオン注入によってこの構造を形成する。実際のMOSFETは、単位セルトランジスタを同一チップ内に複数個並列接続して形成される。なるべく抵抗を下げるため高濃度にドーピングされたn型SiC基板を支持基板

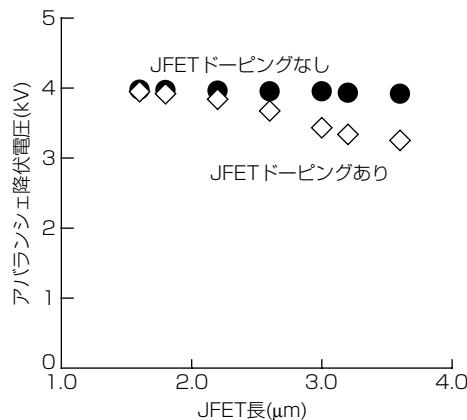

として、高耐圧を維持するための低濃度なn型SiCドリフト層を形成し、選択的イオン注入、活性化アニール、ゲート酸化膜形成、電極形成プロセスを経てMOSFETが作製される。今回は、3.3kV耐圧SiC-MOSFETとして、n型4H-SiC基板上にエピタキシャル成長させた、不純物濃度 $3 \times 10^{15}/\text{cm}^3$ 、厚み30μmのn型SiCドリフト層上にMOS構造を形成した。ドリフト層の不純物濃度及び厚みは、3.3kV耐圧を十分に確保できるよう、耐圧シミュレーションによって設計した。素子周辺部の耐圧終端構造には、約4kVのドレイン電圧印加時に安定したアバランシェ降伏が生じるよう独自に開発したFLR(Field Limiting Ring)構造を採用した<sup>(2)</sup>。

MOSFETのセル構造パラメータとして、チャネル長を0.4～1.6μm、p型ウェルで挟まれたJFET(Junction Field Effect Transistor)領域の幅、すなわちJFET長を1.6～3.6μmの範囲で変化させた。セルピッチは11μmとし、有効面積の異なる3種類( $4.8 \times 10^{-5}\text{cm}^2$ ,  $2.0 \times 10^{-3}\text{cm}^2$ ,  $9.0 \times 10^{-2}\text{cm}^2$ )の素子を作製した。p型ウェル領域、n型ソース領域、p型コンタクト領域、JFETドーピング領域にイオン注入された不純物の活性化のために、1,700°Cで熱処理を実施した。ゲート酸化膜は熱酸化及び窒化処理によって形成し、酸化膜厚は50nmとした。ソース／ドレンのコンタクト電極としてNiシリサイドを形成した。

### 2.2 MOSFETの低抵抗化技術(JFETドーピング)

3.3kV耐圧SiC-MOSFETでは、高耐圧を確保するためドリフト層の不純物濃度を比較的低く設計しているので、JFET領域の抵抗成分、すなわちJFET抵抗が高くなりやすい。JFET抵抗を低減する方法として、JFET長の拡大やJFET領域における不純物濃度の高濃度化(JFETドーピング)が挙げられるが、これらはどちらもゲート酸化膜電界の増大をもたらし、MOSFETの耐圧や長期的な信頼性に悪影響を及ぼす。すなわち、JFET抵抗とゲート酸化膜電界はトレードオフの関係にあり、ゲート酸化膜電界の増大を抑制しつつJFET抵抗を低減するために、JFET長／JFETドーピングを最適に設計することが極めて重要になる。

今回、プロセス／デバイスシミュレーションを活用して、JFETドーピングのパラメータを、不純物濃度 $1 \times 10^{17}/\text{cm}^3$ 、厚み約1μmに最適化した。JFETドーピングはn型不純物である窒素の多段イオン注入によって形成した。厚み方向のプロファイルに関しては、MOSFETのチャネル特性やゲート酸化膜電界に影響を及ぼさないよう、ドリフト層の表面近傍を避けてイオン注入を施した。

## 3. 3.3kV耐圧SiC-MOSFETの電気特性

### 3.1 静特性のMOSFETセル構造依存性

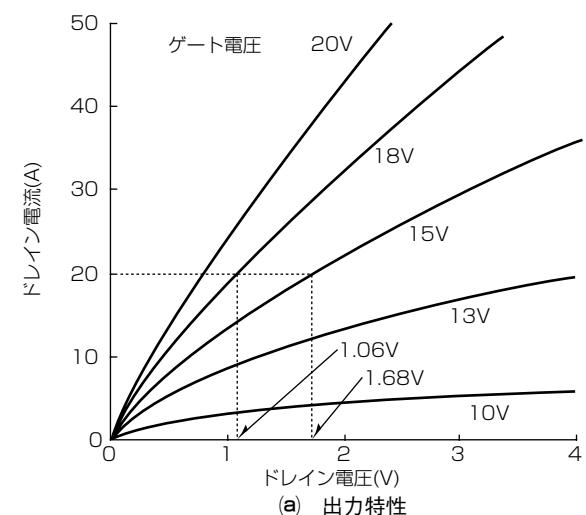

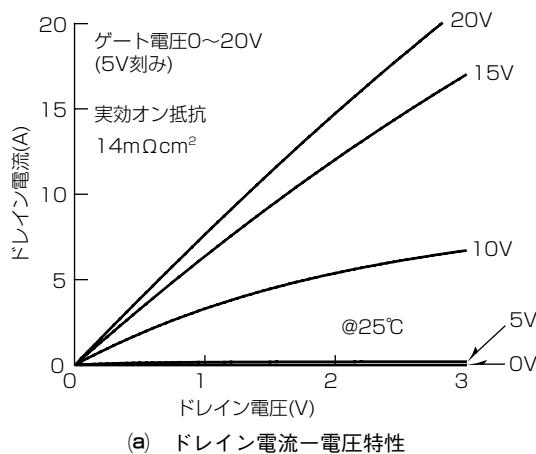

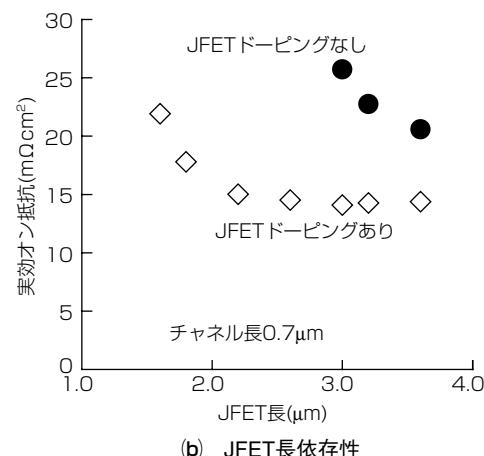

作製したMOSFETの静特性を室温で評価した。有効面積 $9.0 \times 10^{-2}\text{cm}^2$ を持つ3.3kV耐圧SiC-MOSFETのドレイン

電流-電圧特性及び耐圧特性を図1に示す。ゲート電圧15V、ドレイン電流密度 $100\text{A}/\text{cm}^2$ における実効オン抵抗は $14\text{m}\Omega\text{cm}^2$ 、ゲート電圧-10Vにおけるアバランシェ降伏電圧は約3.9kVが得られており、3.3kV耐圧を十分に確保しつつ低抵抗なMOSFETが実現できていることが分かる。

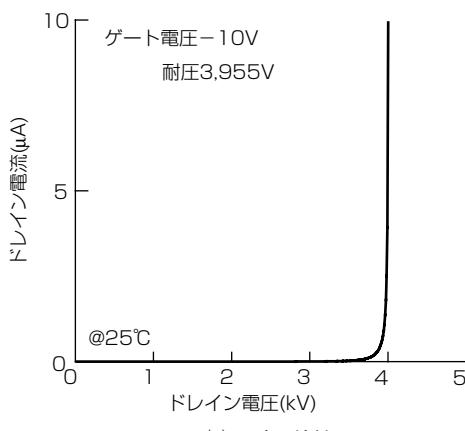

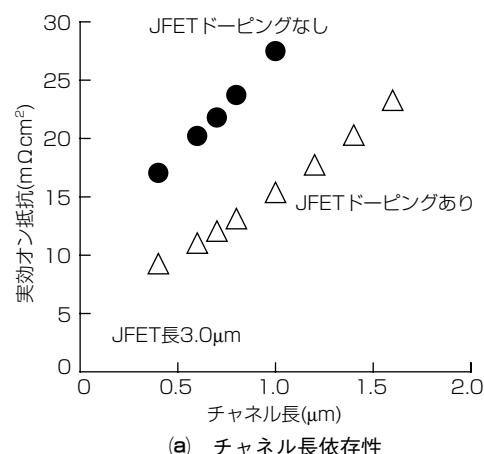

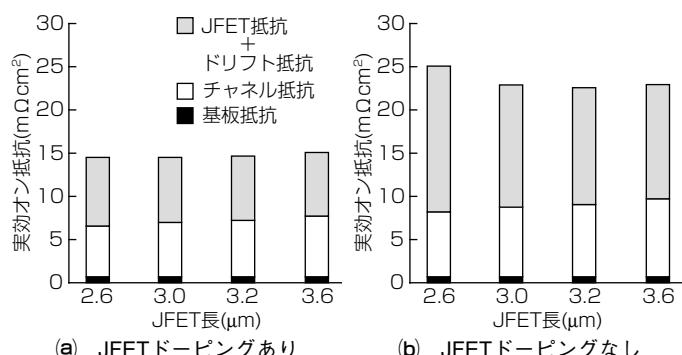

図2に実効オン抵抗のチャネル長依存性及びJFET長依存性を示す。図中にはJFETドーピングを実施した素子と実施しない素子の特性を併せて示している。素子の有効面積はどちらも $2.0 \times 10^{-3}\text{cm}^2$ である。図2(a)から、実効オン抵抗はチャネル長の縮小に伴い単調減少し、JFETドーピングの有無によらず同様の傾向を示すことが分かる。また、JFETドーピングを実施することで、JFETドーピングを実施しない素子に比べて実効オン抵抗を $8\sim 12\text{m}\Omega\text{cm}^2$ 低減できることが分かる。どちらの素子についても、実効チャネル移動度は約 $22\text{cm}^2/(\text{V}\cdot\text{s})$ であった。

図2(b)から、JFET長を縮小するとJFETドーピングの有無によらず実効オン抵抗は顕著に増大し、JFETドーピングを実施しない素子ではJFET長が比較的長い場合でも実効オン抵抗の増大が著しいことが分かる。今回試作したJFET長の範囲(1.6~3.6μm)すべてにおいて、JFETドーピングを実施した素子の方が実効オン抵抗が低減することから、JFET領域の空乏化が実効オン抵抗に与える影響が大

(a) ドレイン電流-電圧特性

図1. ドレイン電流-電圧特性及び耐圧特性

きいことを示唆している。

実効オン抵抗の抵抗成分内訳を図3に示す。チャネル抵抗は、それ以外の寄生抵抗を十分に低減したMOSFETを評価することで算出した。JFET抵抗及びドリフト抵抗は、チャネル部分を電気的に短絡したMOSFETを評価して求めた。JFETドーピングの有無によらず、JFET長を縮小するとチャネル抵抗が減少することが分かる。これは、セルピッチを $11\mu\text{m}$ 、チャネル長を $0.7\mu\text{m}$ に固定しているので、JFET長の縮小に伴いチャネル幅密度が増加することに起因する。その一方で、JFET抵抗及びドリフト抵抗は、JFET長の縮小に伴い増大し、JFETドーピングを実施し

(a) チャネル長依存性

(b) JFET長依存性

図2. 実効オン抵抗のチャネル長依存性及びJFET長依存性

図3. 実効オン抵抗の抵抗成分内訳

図4. アバランシェ降伏電圧のJFET長依存性

図5. 実効オン抵抗の温度依存性

ない素子で特に顕著な増加を示すことが分かる。3.3kV耐圧SiC-MOSFETでは、素子全体の抵抗を低減するために、JFETドーピングを実施してJFET抵抗を低減することが極めて有効であると考えられる。

ゲート電圧-10Vにおけるアバランシェ降伏電圧のJFET長依存性を図4に示す。JFETドーピングを実施した素子ではJFET長の拡大に伴い降伏電圧が低下することが分かる。これは、p型ウェルの端部に生ずる電界強度が高くなることに起因すると考えられる。実効オン抵抗の低減と高耐圧を両立させるためには、JFET長及びJFETドーピングを最適に設計することが極めて重要である。

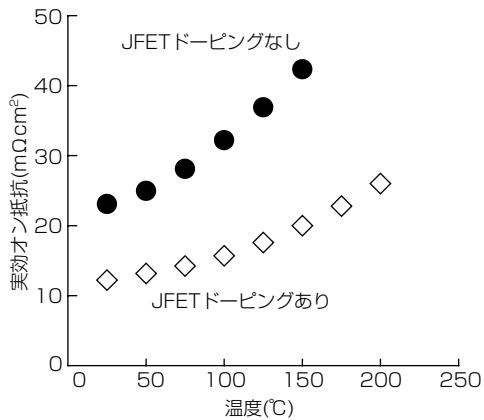

### 3.2 実効オン抵抗の温度依存性

先に述べたMOSFETの温度依存性を調査した。チャネル長0.7μm, JFET長3.0μm, 有効面積 $4.8 \times 10^{-5} \text{ cm}^2$ の素子に対する実効オン抵抗の温度依存性を図5に示す。JFETドーピングを実施した素子では、JFETドーピングを実施しない素子に比べて、室温~175°Cの範囲における実効オン抵抗の変化が12~23mΩcm<sup>2</sup>と小さいことが分かる。これは、JFETドーピングを実施することによりイオン化不純物散乱の影響が大きくなり、JFET領域における電子移動度の温度係数が小さくなるためと考えられる。また、ドレン電圧10VにおけるMOSFETのしきい値電圧は、JFETドーピングの有無で有意差が見られず、室温で約2V, 175°Cで約1Vであった。

これらのことから、3.3kV耐圧SiC-MOSFETの低抵抗化技術として適用したJFETドーピングは、室温だけでなく高温でもMOSFETの低抵抗化を実現できる、極めて有効な手法であると言える。

## 4. むすび

既存の産業用や電鉄車両向けモジュールの更なる高効率化を図るために、Si-IGBTのSiCスイッチング素子への置き換えをねらい、3.3kV耐圧のSiC-MOSFETを開発した。低抵抗化技術としてJFETドーピングを適用し、ドーピング条件及びセル構造パラメータを最適に設計することで、3.3kV耐圧を十分に確保しつつ、室温だけでなく高温でも実効オン抵抗を大幅に低減できることを実証した。これらの技術を活用して、当社は1,500A定格の大容量フルSiCパワー モジュールを適用したDC1,500V架線対応の鉄道車両用インバータ装置を世界で初めて製品化した<sup>(注1)</sup>。今後もデバイス性能の更なる向上に向けた開発を継続する。

この研究は経済産業省/NEDO(New Energy and industrial technology Development Organization)から委託された“低炭素社会を実現する新材料パワー半導体プロジェクト”的成果を含んでいる。

(注1) 2013年12月25日現在、当社調べ

## 参考文献

- (1) 渡邊 寛, ほか: 3.3kV SiC-SBDの試作評価, 平成24年電気学会全国大会講演論文集, No.4, 254 (2012)

- (2) 濱田憲治, ほか: 二重FLR構造を有する13kV級4H-SiC PiNダイオードの特性評価, SiC及び関連半導体研究第22回講演会予稿集, B-31 (2013)

# 高耐熱パワー半導体モジュール パッケージング要素技術

日野泰成\* 翼 裕章\*\*

長谷川 滋\* 横村伸緒\*\*\*

山田浩司\* 畠中康道\*\*\*

Packaging Technologies for High Temperature Power Modules

Yasunari Hino, Shigeru Hasegawa, Koji Yamada, Hiroaki Tatsumi, Nobuo Yokomura, Yasumichi Hatanaka

## 要 旨

近年、環境保護と省エネルギーを背景にパワーエレクトロニクスは民生、産業用のインバータだけでなく、電鉄、自動車、太陽光発電、風力発電へと適用範囲が拡大している。

その中でパワーエレクトロニクスの基幹部品であるパワー半導体モジュールに対して、効率的な電流制御、厳しい使用環境下における耐久性及び小型化が要求されている。

特にSiC(Silicon Carbide)を用いたパワー半導体モジュールは、高速動作が可能で動作時の損失が少なく、飛躍的に特性の向上を図ることができる。さらに高温動作化が可能であり、冷却構造の小型化を図るために、一段とパワー半導体モジュールの小型化が実現可能となる<sup>(1)</sup>。

しかしながら、パワー半導体モジュールの高温動作化を実現するためには、チップの高温動作化だけでなく、パッケージ構造及び材料の高耐熱化が重要な技術課題となっている。

そこで、三菱電機では高耐熱パワー半導体モジュールの製品化に向けて、パッケージ構造、材料及びその要素技術開発を加速している。

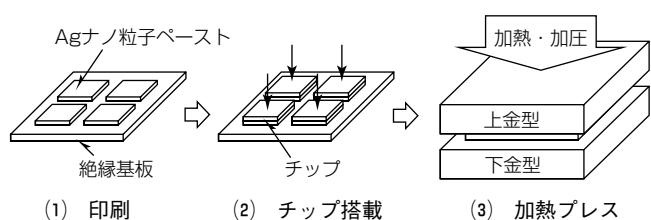

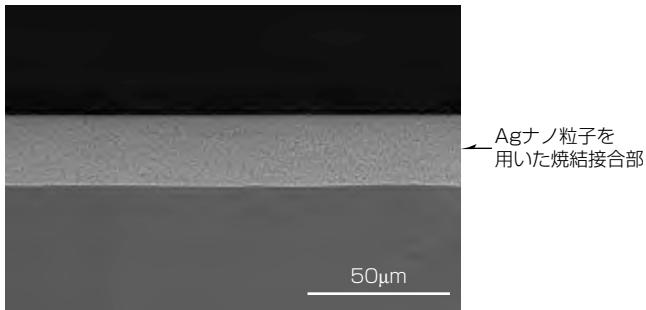

本稿では、高耐熱化のために必要な高耐熱パワー半導体モジュールのパッケージング要素技術として、Agナノ粒子の低温焼結性を用いた接合技術及び封止技術について述べる。

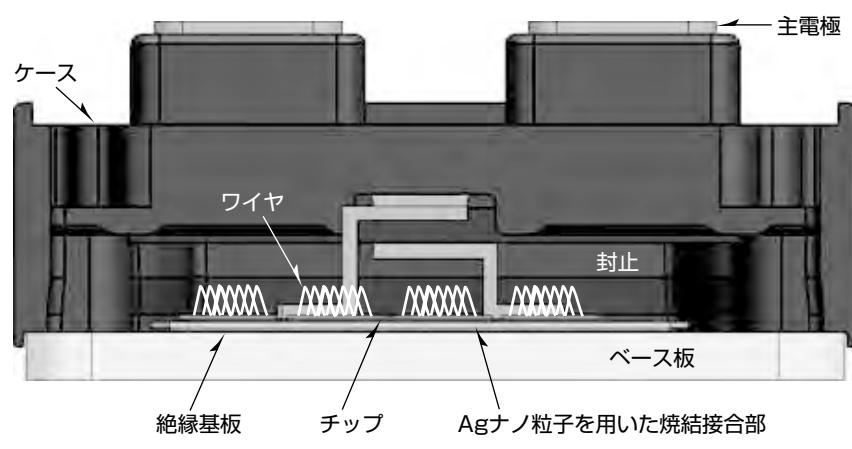

高耐熱パワー半導体モジュールの構造

(1) 印刷

(2) チップ搭載

(3) 加熱プレス

Agナノ粒子を用いた焼結接合プロセス

## 高耐熱パワー半導体モジュール

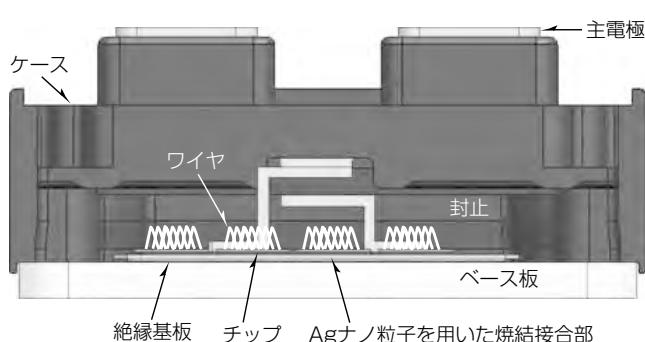

高耐熱パワー半導体モジュールの構造を示す。絶縁基板上にチップを搭載する組立手法として、Agナノ粒子を用いた焼結接合を実施し、また高耐熱性の封止材でモジュール内部を充填する。これによって、高耐熱、高信頼性の接合部を得るとともに、高耐熱、高絶縁性を満たすモジュールを得ることができる。

## 1. まえがき

近年、環境保護と省エネルギーを背景にパワーエレクトロニクスは民生、産業用のインバータだけでなく、電鉄、自動車、太陽光発電、風力発電へと適用範囲が拡大している。

その中でパワーエレクトロニクスの基幹部品であるパワー半導体モジュールに対して、効率的な電流制御、厳しい使用環境下における耐久性及び小型化が要求されている。

特にSiCを用いたパワー半導体モジュールは、高速動作が可能で動作時の損失が少なく、飛躍的に特性の向上を図ることができる。さらに高温動作化が可能であり、冷却構造の小型化を図ることができるために、一段とパワー半導体モジュールの小型化が実現可能となる。

しかしながら、パワー半導体モジュールの高温動作化を実現させるためには、チップの高温動作化だけでなく、パッケージ構造及び材料の高耐熱化が重要な技術課題となっている。

そこで、当社では高耐熱パワー半導体モジュールの商品化に向けて、パッケージ構造、材料及びその要素技術開発を加速している。

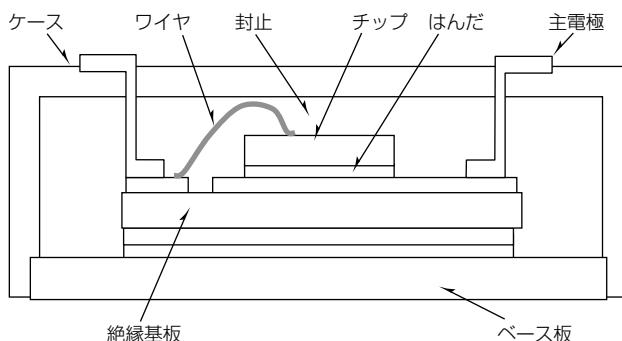

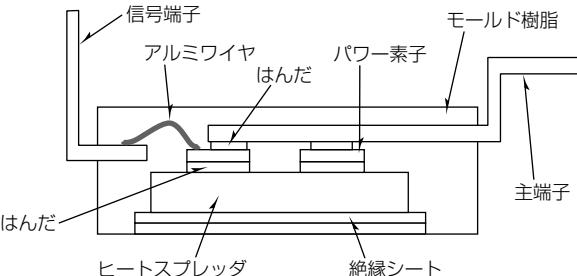

## 2. パワー半導体モジュール

パワー半導体モジュールのパッケージ外観を図1に、主要構造を図2に示す。ベース板上に絶縁基板が接合され、絶縁基板上にはチップが接合されている。チップ上面電極と絶縁基板上の配線パターン間はアルミなどのワイヤで配

図1. パワー半導体モジュール

図2. パワー半導体モジュールの構造

線接続され、主電極が絶縁基板上の配線パターンに接合されている。ベース板には全体を覆うケースが嵌合(かんごう)／接合され、内部には封止材が充填されている。また絶縁基板上のチップ接合は、主にはんだ接合が適用されていた<sup>(2)</sup>。

そこで、パワー半導体モジュールの高温動作化のために、接合材、封止材等各部材の耐熱性向上とともに、特に温度サイクルに対する接合部の信頼性、接合寿命の向上が必要となる<sup>(3)(4)</sup>。3章以降、高耐熱化のためのパッケージング要素技術として、Agナノ粒子の低温焼結性を用いた接合技術及び封止技術について述べる。

## 3. パッケージング要素技術

### 3.1 焼結接合技術

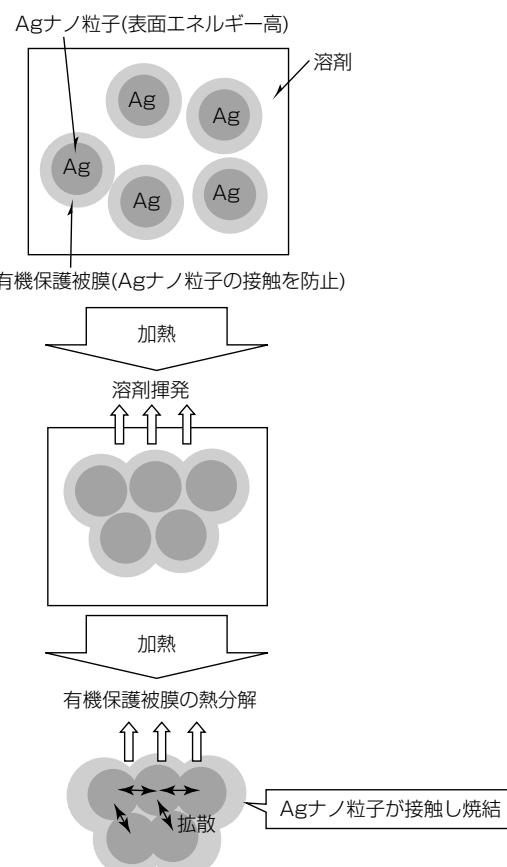

パワー半導体モジュールの動作温度の高温化に伴い、従来のSn系はんだ材では限界が予測される。そこで、有機保護被膜で覆われたナノサイズの金属微粒子を用いて、粒径が小さくなると融点が低下するという“融点降下現象”を用いた焼結接合を検討した。

接合材料は、有機保護被膜に覆われたAgナノ粒子に加えて、焼結分散性、粘性、耐乾燥性を考慮した数種類の溶剤から構成されている。加熱によって溶剤が揮発し、有機保護被膜を熱分解させることで、Agナノ粒子が接触し、Agの融点以下で焼結し合い接合するという原理である(図3)。これによって、金属固有の融点を持った高耐熱の

図3. Agナノ粒子の焼結接合模式図

接合部を得ることができる。今回、ナノサイズのAg粒子を適用しているため、従来のSn系はんだ材と同等レベルの加熱温度で接合が可能であり、接合後は900°C以上の融点を持った接合部を得ることができた。

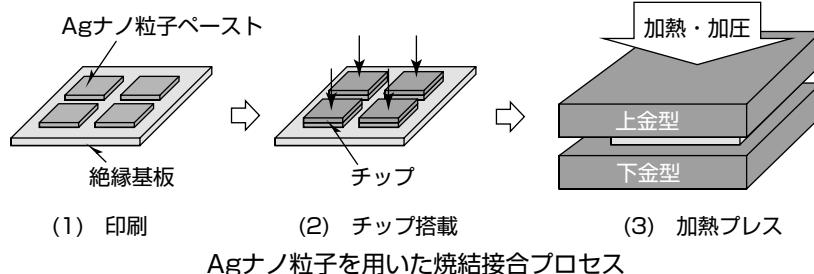

### 3.1.1 Agナノ粒子を用いた焼結接合プロセス

図4に示すように、Agナノ粒子が分散されたペースト状の材料を用いて、絶縁基板上にスクリーン印刷する。次に、チップを所定の位置に搭載し、加熱プレスすることによって、焼結接合させる。なおチップ搭載及び加熱プレス工程は、焼結接合専用の試作設備を開発・導入し、複数チップの搭載及び一括加熱プレスを可能としている。チップ搭載機及び加熱プレス機を図5に示す。

次に、上記接合プロセス手法に基づいて、基礎評価用サンプルを作製し(図6)、Agナノ粒子を用いた焼結接合部に対する信頼性を確認した。

図4. Agナノ粒子を用いた焼結接合プロセス

図5. 焼結接合の試作設備

図6. 高耐熱パワー半導体モジュールの構造

### 3.1.2 信頼性試験

電鉄、自動車向け等、より厳しい温度環境下でパワー半導体モジュールを用いる場合、構成されるパッケージ内の各部材間の熱膨張差に起因した熱応力が、接合部に対し亀裂を生じさせるため、今回、信頼性試験として、パワーサイクル試験及び温度サイクル試験を実施した。

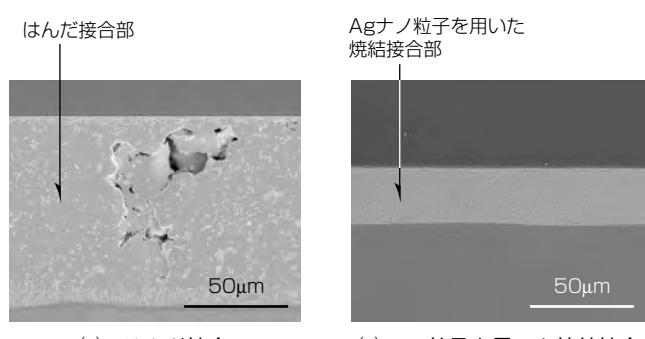

#### (1) パワーサイクル試験

Agナノ粒子を用いた材料に加えて、今回比較対象として、はんだ材(Sn-Ag-Cu-Sb系)を用いた基礎評価用サンプルを準備し、Agナノ粒子を用いた焼結接合同様にパワーサイクル試験( $T_{jmax} = 175^\circ\text{C}$ ,  $\Delta T_j = 90\text{K}$ )を実施して検証を行った。その結果、Agナノ粒子を用いて焼結接合したサンプルは、はんだ材を用いて接合したサンプルと比較して約5倍のパワーサイクル寿命があることが分かった。次に、パワーサイクル試験後の接合部を検証するため断面観察を実施した。その結果を図7に示す。はんだ接合部では網目状の亀裂が認められたが、一方Agナノ粒子を用いた焼結接合部では、亀裂進展はなく良好な結果を得た。つまりAgナノ粒子を用いた焼結接合は、パワーサイクル寿命に対し支配因子にならないと考えられる。

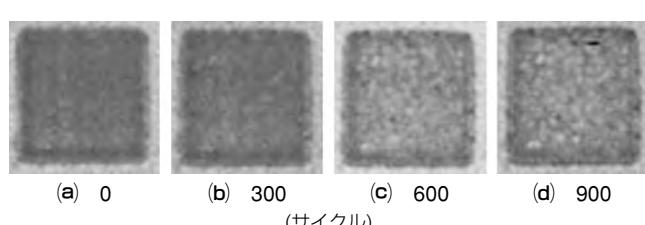

#### (2) 温度サイクル試験

$-40\sim175^\circ\text{C}$  ( $\Delta T = 215\text{K}$ )の温度変化を与える温度サイクル試験で、Agナノ粒子を用いた焼結接合部に対する亀裂進展を検証した。初期、300サイクル、600サイクル、900サイクル耐久後のSAT(Scanning Acoustic Tomography)画像を図8に示す。耐久サイクル数の増加に伴い接合部に対し極微小な白色部が確認されたが、目立った剥離はないことを確認した。次に、温度サイクル試験後(900サ

図7. パワーサイクル試験後の断面

図8. 温度サイクル試験後のSAT画像

図9. 温度サイクル試験後(900サイクル耐久後)の断面

表1. 高耐熱性封止材の特性及び試験結果

|        | 現行封止材                                   | 高耐熱封止材                |                         |

|--------|-----------------------------------------|-----------------------|-------------------------|

| 耐熱付与剤  | A                                       | B                     |                         |

| 接着性    | Cu箔(はく)ピール強度(gf/cm)                     | 80                    | 159                     |

| 耐熱性    | 針入度 <sup>(注1)</sup> 変化(215°C - 1,000hr) | 半減                    | 変化なし                    |

| 部分放電特性 | 175°C測定r/n <sup>(注2)</sup>              | 5 hr<br>10hr<br>100hr | 0 / 6<br>0 / 6<br>0 / 6 |

(注1) ゲル硬度を表す指標

(注2) 部分放電NG発生確率

イクル耐久後)の断面画像を図9に示す。Agナノ粒子を用いた焼結接合部で顕著な剥離進展は確認されなかった。

### 3.2 封止技術

パワー半導体モジュールの絶縁性を確保するために、封止(ゲル)が必要である。そこで、絶縁性を確保するとともに、高耐熱性の封止材を検討した。耐熱付与剤を改良することによって耐熱性を向上させ、また組成の適正化を図ることによって接着性を向上させ、剥離を抑制することによって、部分放電特性の向上を図った。高耐熱性の封止材の特性及び試験結果を表1に示す。その結果、高耐熱、高絶縁性の封止を得ることができた。

## 4. むすび

パワー半導体モジュールの高温動作化を実現するために、高耐熱パワー半導体モジュールのパッケージング要素技術として、Agナノ粒子の低温焼結性を用いた接合技術及び封止技術について述べた。高信頼性、高寿命を達成したAgナノ粒子を用いた焼結接合技術、高耐熱、高絶縁性を達成した封止技術のように、高耐熱パワー半導体モジュールの製品化実現には、革新的なパッケージ設計、材料及び製造プロセスの開発が必要であると考える。

今後、長年蓄積してきた、当社のパワー半導体モジュールのパッケージング要素技術及び量産技術を踏まえ、次世代の高耐熱パワー半導体モジュールの開発をさらに加速させ、製品化の推進に引き続き取り組み、環境保護及び省エネルギー社会構築に貢献していく所存である。

## 参考文献

- (1) マジュムダール ゴーラブ, ほか: パワーモジュールの最新技術動向, 三菱電機技報, 86, No.5, 262~266 (2012)

- (2) 長谷川 滋, ほか: 1.7kV大容量ハイブリッドSiCモジュール, 三菱電機技報, 86, No.5, 287~290 (2012)

- (3) 加柴良裕, ほか: 半導体年鑑2014, 日経BP, 217~227 (2013)

- (4) 日経エレクトロニクス編: 次世代パワー半導体, 日経BP, 160~185 (2012)

# 自動車用パワー半導体モジュール “J1シリーズ”のパッケージ技術

吉松直樹\* 石山祐介\*

碓井修\*

井本裕児\*

Packaging Technologies of Power Module "J1 Series" for EVs and HEVs

Naoki Yoshimatsu, Osamu Usui, Yuji Imoto, Yusuke Ishiyama

## 要旨

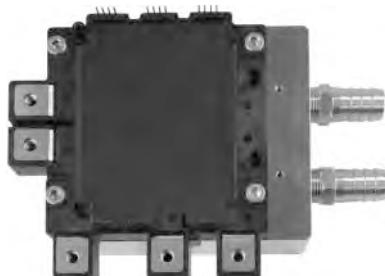

自動車メーカーによる電気自動車(EV)・ハイブリッド車(HEV)の市販化に伴い、三菱電機ではケースタイプの大容量パワーモジュールを車載用途として1997年に上市した。そして、300Aクラス以下の中低電流容量では、高信頼性の“トランスファーモールド型パワーモジュール(Transfer-molded Power Module : T-PM)”を2004年に上市、さらにその改良版として、内部配線構造を従来のアルミワイヤから、銅フレームをパワー素子に直接はんだ接合させる“ダイレクトリード接合型パワーモジュール(Direct Lead Bonding : DLB T-PM)”へと進化させてきた。

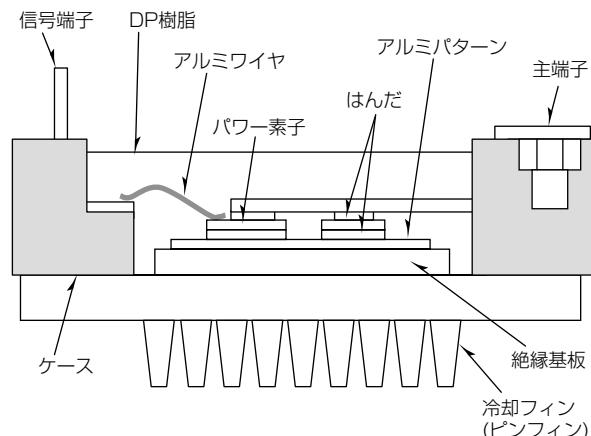

今回、“高性能”“小型・軽量化”をコンセプトとして開発した自動車用パワー半導体モジュール“J1シリーズ”的パッ

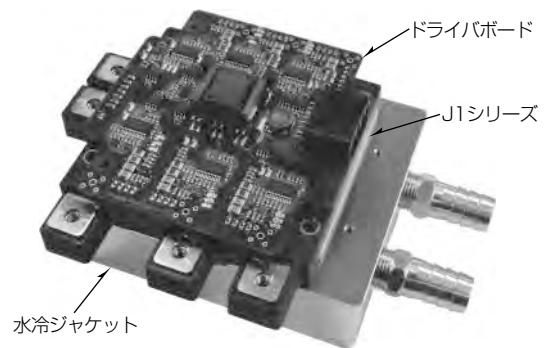

ケージには、T-PMで培った高信頼性技術を活用して、ケースタイプにデバイスや内部配線を硬質樹脂で封止するダイレクトボッティング構造を採用した。さらに、主回路配線のDLB化による大電流容量への対応と、アルミピンフィンをモジュールと一体化して冷却性能を向上させることによるモジュールの大幅な小型化・軽量化を実現した。そして、このピンフィン一体モジュールと並行開発した水冷ジャケットを組み合わせることで、冷却水均流化のためのヘッダ部分の配置による面積ロスをなくしつつ、その冷却性能を最大限に発揮できるものとした。

本稿では、J1シリーズのパッケージの構造、性能、信頼性について述べる。

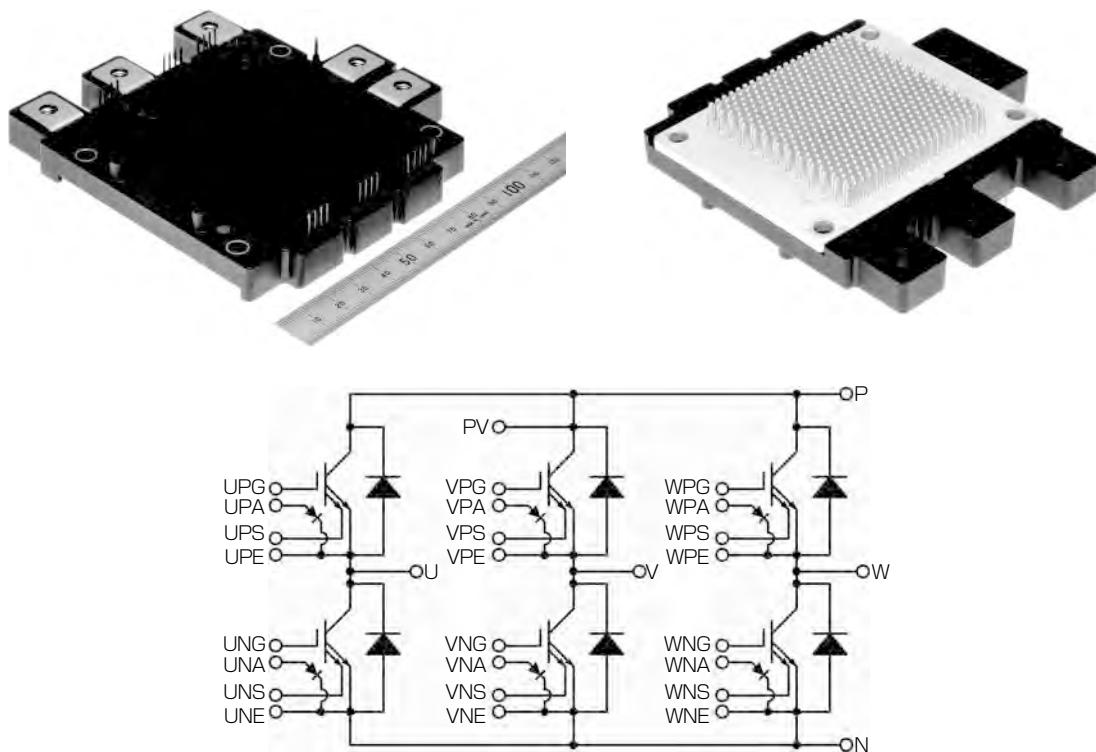

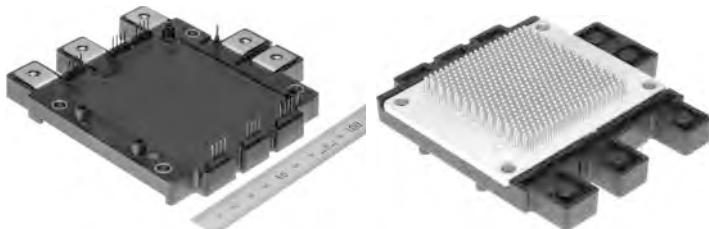

自動車用パワー半導体モジュール“J1シリーズ”の上側外観と下側外観及び回路

外形寸法：120×115.2×13(mm)(フィンベース下面～主端子上面)、全高32.5mm

定格電流／定格電圧：(1)600A／650V、(2)400A／900V

## 1. まえがき

自動車メーカーのEV・HEV市販化に伴い、当社では車載用パワーモジュールを1997年に上市し、その後、EV・HEVの進化に対応するために、パワーモジュールも高性能化、小型・軽量化、高信頼性・高品質化、低コスト化を進めてきた。

今回、自動車用パワー半導体モジュール“J1シリーズ”では、“高性能”“小型・軽量化”をコンセプトに開発を行った。

本稿ではJ1シリーズの構造、性能、信頼性について述べる。

## 2. 構造の特徴

### 2.1 パッケージ外形

従来型の当社製DLB T-PMの銅ピンフィン冷却器への実装状態と比較したJ1シリーズを図1に示す。

従来型DLB T-PMはハーフブリッジ回路の2 in 1構造のパッケージを、冷却器上に3個並べてそれぞれ固定することで三相インバータの回路構成を成す。一方、J1シリーズでは、アルミピンフィン一体化による冷却性能の向上と、バスバー配線をインサート成形したケースを使用することによって回路の集積化を容易にし、三相インバータ回路を1パッケージ化した6 in 1構造とすることができた。これによって、水冷ジャケットを含めた実装面積を従来品に比べ40%縮小し、76%の軽量化を実現した。

J1シリーズに使用している水冷ジャケットは小型化、高効率化を目的に、モジュールと並行開発したものであり、水路内を均流化させるためのヘッダ部分によって発生する冷却器設置面積のロスをなくしている。

(a) 従来製品

(b) J1シリーズ

図1. パッケージ外形の比較

さらに、DLB T-PM 3個のそれぞれに設置されたP, N電極はバスバーでの接続が必要であるが、J1シリーズでは、1対のP, N電極をモジュールの1辺に近接配置しているため、平行平板型バスバーを接続し、配線のインダクタンスの上昇を抑制できる。また、バスバー接続用のナットボックスと制御基板固定用の支柱を、ケースと一体化することで周辺部品の組み付けを容易にし、機能の向上を図っている。

### 2.2 DLB+ダイレクトポッティング構造

当社では、パワーモジュールとして主流であったシリコーンゲル封止構造の数倍の寿命を持つトランスファモールド構造を開発し、さらに主回路配線である太線アルミワイヤを、通電能力向上、配線抵抗低減、インダクタンス低減等を目的としたDLB構造へと進化させた。J1シリーズには、これらの利点を活用するために、DLB構造をケースタイプへ応用し、モールド樹脂と同様の硬質樹脂で封止するダイレクトポッティング(DP)構造を採用した。

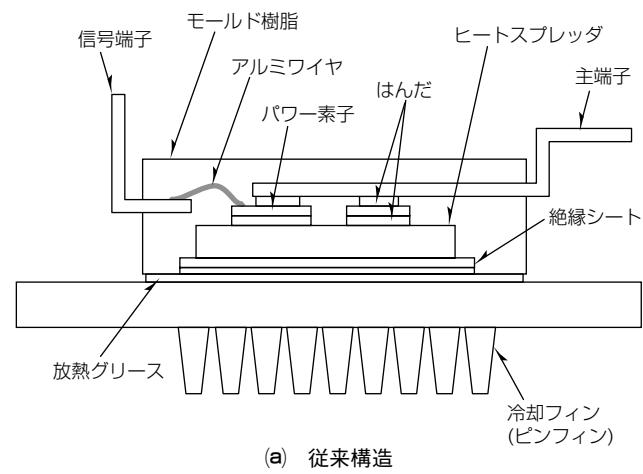

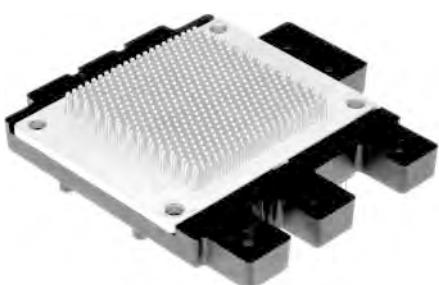

### 2.3 ピンフィン一体化

J1シリーズでは、冷却性能を向上させるために、放熱グリースを廃止し、ピンフィンをモジュールと一体化した。図2に従来構造との断面構造の比較を示す。

(a) 従来構造

(b) J1シリーズ構造

図2. 断面構造の比較

従来構造では、モジュールの放熱面と冷却フィンの実装面の間に放熱グリースを塗布して組み立てられる。この放熱グリースによって、2面間の隙間を埋め、パワー素子動作時に発生する熱を冷却水へと伝導させている。放熱グリースの熱伝導率はアルミや銅等の金属に比べて低く、その厚みは熱抵抗に大きく影響する。そこで、モジュールの放熱面、冷却フィンの実装面は、通常その隙間をできるだけ小さくするためにフラット形状、又は凸形状となるような加工や工夫が施される。しかし、その面形状のばらつき、放熱グリース塗布状態のばらつき、実製作業のばらつき等によって安定した冷却性能を得ることが困難であった。

J1シリーズでは、このような熱抵抗の増大とばらつきの主要因となる放熱グリースを廃止し、セラミックス絶縁基板をピンフィンに一体化した“セラミックス絶縁アルミフィン”を採用した。これによって、冷却性能を改善することができた。その冷却性能については、3.1節で述べる。

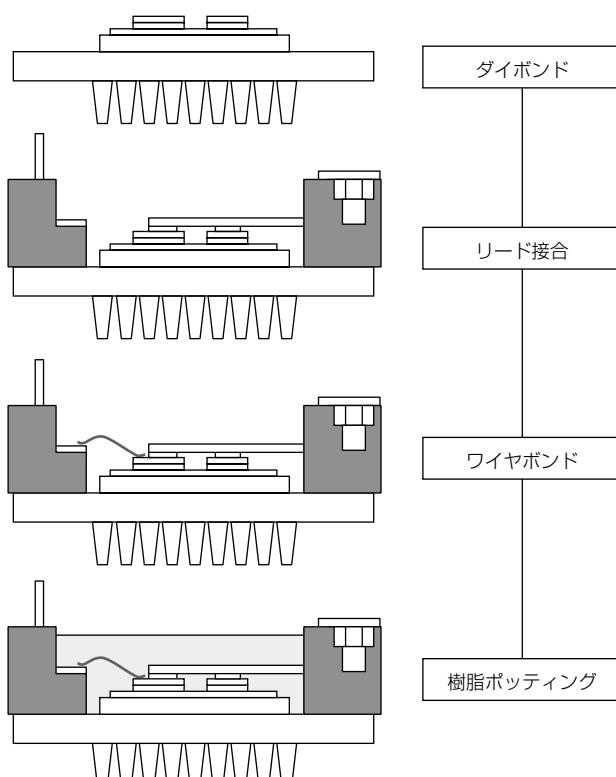

#### 2.4 製造プロセス

J1シリーズでは、部品のサブアセンブリ化を進め、この組立て工程をシンプルにすることで、車載用途として特に重要な品質安定化を図る。

J1シリーズの製造フローは、次のような必要最小限の4工程を軸に構成されている(図3)。

- (1) ダイボンド：パワー素子の裏面接合

- (2) リード接合：パワー素子の表面主回路配線

- (3) ワイヤボンド：パワー素子の信号配線

- (4) 樹脂ポッティング：パワー素子と周囲の配線等を封止

図3. J1シリーズの製造フロー

### 3. 性能・信頼性

#### 3.1 冷却性能

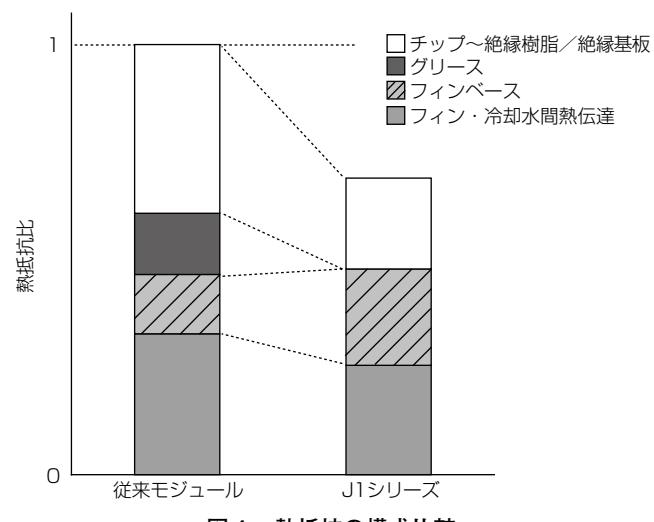

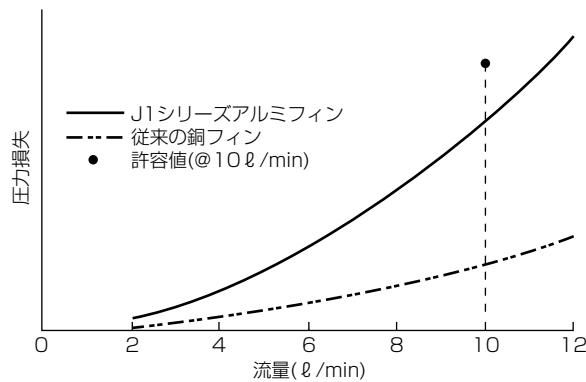

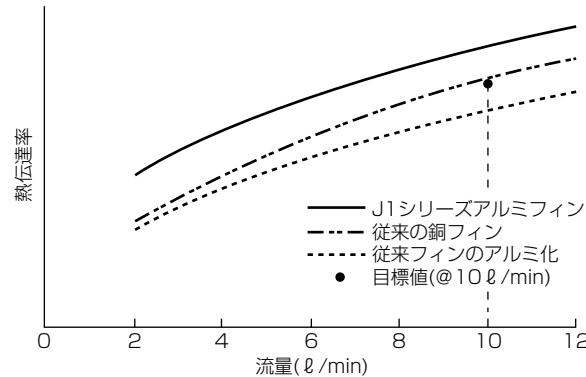

従来モジュール用の冷却フィンには、冷却性能を重視して材料に銅材を使用し、耐腐食性能向上のため表面にニッケルめっきを施している。しかし、J1シリーズでは、セラミックス絶縁基板との一体化、及び軽量化を目的にアルミ材を採用した。

アルミの熱伝導率は銅に比べて約60%と低いため、従来構造のフィンを単に銅からアルミに材料変更した場合、その熱伝達率は88%程度に低下する。

そこでJ1シリーズでは従来の銅フィンと同等の冷却性能とすることを目標として、ピン形状・配置、流路設計の最適化を実施し、その結果、フィン部分で従来の銅と同等の熱抵抗を達成、さらにモジュール全体の熱抵抗を約30%改善した。

図4に縦構造における各層の熱抵抗の構成を従来品と比較したものと示す。このように、セラミックス絶縁基板をピンフィンに一体化させて放熱グリースを廃止した効果は非常に大きい。

熱抵抗を低減した具体的な方策は次のとおりである。

- (1) 絶縁材に熱伝導率の高いセラミックスを採用した。これに伴い、パワー素子から発する熱を絶縁材通過前に拡散させる必要がなくなったため、ヒートスペレッダを廃止した。

- (2) セラミックス絶縁基板をピンフィンに一体化した“セラミックス絶縁アルミフィン”的採用によって、放熱グリースを廃止した。

- (3) ピンの形状・配置を最適化することでピンフィンの冷却性能を向上させた。

- (4) 専用の水冷ジャケットとの組合せによって、冷却水の流速を均一化し、冷却効率を向上させた。

図4. 熱抵抗の構成比較

図5. 圧力損失の比較

図6. 热伝達率の比較

(5) 冷却水流路の断面積を小さくすることで圧力損失の許容される範囲内で冷却水の流速を高め、冷却能力を向上させた。

図5に従来品とJ1シリーズの圧力損失の比較、図6に熱伝達率の比較を示す。

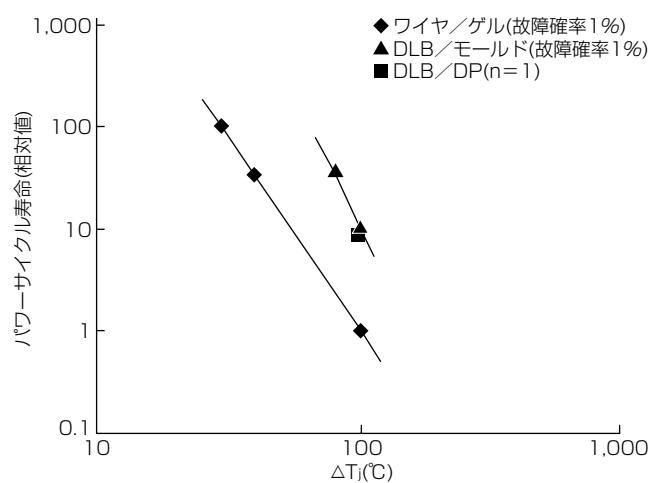

### 3.2 パワーサイクル寿命

T-PMではパワー素子とアルミワイヤをモールド樹脂で封止することで、シリコンパワー素子とアルミワイヤの線膨張係数差によって接合界面近傍に発生する熱ひずみを抑制し、シリコーンゲル封止構造に対してパワーサイクル寿命を温度変化量 $\Delta T_j = 80^\circ\text{C}$ の条件で約3倍まで延ばした。そして、配線構造をDLB化することによって、ワイヤボンドタイプのシリコーンゲル封止構造に対して約10倍まで延ばした。

図7. パワーサイクル寿命<sup>(1)(2)</sup>

J1シリーズの構造は、2.2節で述べたようにDLB+ダイレクトポッティング構造を当社製品で初めて採用し、DLB T-PMと同様にパワー素子周辺に発生する熱ひずみの抑制効果を狙っている。

図7に従来構造のパワーサイクル試験の寿命カーブと、J1シリーズの $\Delta T_j = 100^\circ\text{C}$ におけるパワーサイクル試験の結果( $n=1$ )のプロットを示す。

### 4. むすび

J1シリーズでは従来品に対し、大幅な小型化・軽量化と放熱性能の向上を達成することができたが、まだ開発の中段階であり、構造及び製造プロセスには課題がある。

今後、これらを解決し、製品を完成させることで、車載用途としてのニーズに適合した製品を提供していく所存である。

### 参考文献

- (1) 菊池正雄, ほか: ダイレクトリード接合型大容量パワーモジュール, 三菱電機技報, 84, No.4, 232~235 (2010)

- (2) 篠原利彰, ほか: トランスファモールド形大容量パワーモジュール, 三菱電機技報, 81, No.5, 325~328 (2007)

# 次世代自動車用パワー半導体モジュール“J1シリーズ”

石原三紀夫\* 山田一樹\*\*

日山一明\* 中野俊哉\*

川瀬達也\*

*Next Generation Power Module for EVs and HEVs "J1 Series"*

Mikio Ishihara, Kazuaki Hiyama, Tatsuya Kawase, Kazuki Yamada, Toshiya Nakano

## 要 旨

地球環境保護意識の高まりを受け、市場が拡大している電気自動車(EV)・ハイブリッド車(HEV)で、それらのモータを駆動するパワー半導体モジュールが車両性能をつかさどる重要な部品となっている。三菱電機は業界に先駆け、1997年から自動車用パワー半導体モジュールの量産を開始しており、その後、三菱電機製品は様々なEV・HEVに搭載されている。

近年のEV・HEVの進化は目覚ましく、キーパーツであるパワー半導体モジュールについても、高性能・小型・軽量化が求められている。

こうした中、三菱電機は“高性能”“小型・軽量化”をコンセプトとした次世代自動車用パワー半導体モジュール

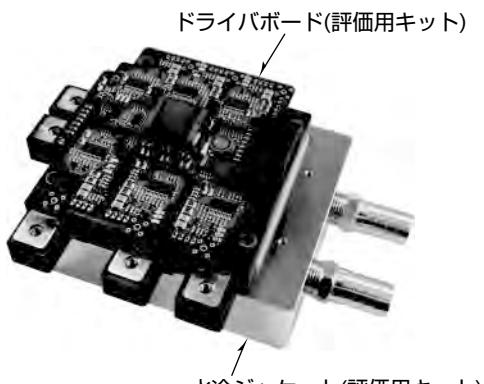

“J1シリーズ”を開発している。コンセプト実現のために冷却フィン一体型の直接水冷構造パッケージを開発し、従来製品(“JシリーズT-PM(Transfer-molded Power Module) CT600DJH060<sup>(1)</sup>” 3台をCu冷却フィンに放熱グリスを介して取り付けたもの)に比べて熱抵抗30%削減、実装面積40%縮小、製品質量76%軽量化を実現した。

また、この製品をユーザーで評価してもらうための評価用キットとして“ドライバボード”“DC-Linkキャパシタ”“水冷ジャケット”を製品と併せて新規に設計・開発した。ドライバボードは、新たに開発したSC(過電流保護)トリップレベル温度補正回路などを追加しながら、J1シリーズの外形サイズ以下に収めている。

J1シリーズ

J1シリーズ用評価キットの実装例

J1シリーズ(裏面側)

J1シリーズ製品ラインアップ

| 製品名    | 形名           | 定格電圧 | 定格電流 | 結線方式   |

|--------|--------------|------|------|--------|

| J1シリーズ | CT600CJ1A060 | 650V | 600A | 6 in 1 |

|        | CT400CJ1A090 | 900V | 400A | 6 in 1 |

## “J1シリーズ”製品の外観とラインアップ及びJ1シリーズ用評価キットの実装例

“高性能”，“小型・軽量化”をコンセプトとしたEV・HEV向けのパワー半導体モジュール“J1シリーズ”を開発している。製品ラインアップは650V／600A及び900V／400Aの2品種でJ1シリーズ評価キットを併せて開発し、ユーザーでの製品評価をサポートしている。

## 1. まえがき

電気自動車(EV)やハイブリッド車(HEV)等の環境適合車には省エネルギーの観点から低損失で小型・軽量なパワー半導体モジュールが求められている。

三菱電機はこうした市場要求に応える新たな自動車用パワー半導体モジュールとして“J1シリーズ”的開発を行っている。また、様々なユーザーにこの製品を評価するための評価キットも併せて開発している。

本稿では、“J1シリーズ CT600CJ1A060(定格電圧／定格電流：650V／600A)”及びJ1シリーズ用評価キットの特長について述べる。

## 2. J1シリーズの特長

### 2.1 J1シリーズ開発コンセプト

J1シリーズはIGBT(Insulated Gate Bipolar Transistor)とダイオードを各6素子搭載し(6 in 1), 冷却フィンと一体化した直接冷却構造を持った自動車用パワー半導体モジュールである(図1)。この製品の開発に当たっては、多数のユーザーから三菱電機製車載用パワーモジュールに対する要望を集め、分析することで次の(1)～(3)の開発コンセプトを策定した。これらのコンセプトの達成によって、シェア拡大を実現することを目的として開発を行っている。

#### (1) 高性能

冷却フィン一体型の直接冷却構造によって、従来製品“JシリーズT-PM”で必要であった放熱グリスが不要となり、放熱性能を改善した。さらに、フィン形状・配列の最適化やパッケージ内部構造の見直し等によって、チップ-冷却水間の熱抵抗R<sub>th(j-w)</sub>を30%以上改善した。これによって、通電能力向上などの高性能化を実現することができた。

#### (2) 小型・軽量化

搭載スペース小容量化や燃費性能向上のために、パワーモジュールには小型で軽量な製品が求められている。J1シリーズでは、従来製品(JシリーズT-PMCT600DJH060 3台をCu冷却フィンに放熱グリスを介して取り付けたもの)に対して、①6 in 1結線構造採用によるチップ配置の高集積化、②アルミ放熱フィンの採用によって、実装面積の40%縮小<sup>(注1)</sup>と製品質量の76%軽量化<sup>(注2)</sup>を実現した。

図1. J1シリーズ

#### (3) 市場ニーズにマッチした製品ラインアップの整備

市場ニーズを分析した結果，“650V／600A 6 in 1” “900V／400A 6 in 1”的2品種を先行機種として開発を開始した。今後は、更なるニーズに応じた定格の製品をラインアップすることを予定している。

(注1) J1シリーズ120×115(mm), 従来製品220×105(mm)

(注2) J1シリーズ335g, 従来製品1,380g

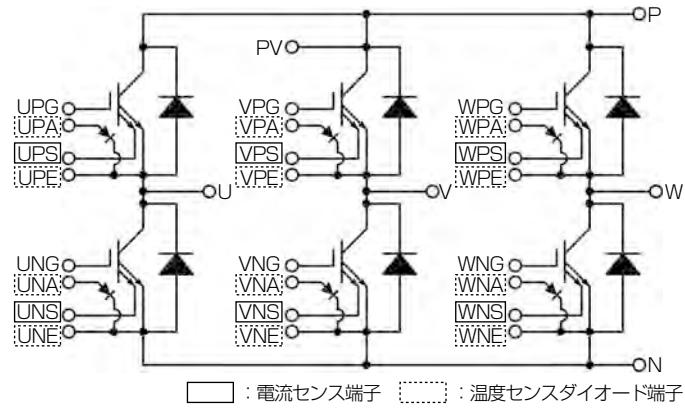

## 2.2 回路構成

図2にJ1シリーズの回路構成を示す。J1シリーズは製品外形サイズの小型化及びユーザーでの効率的な取付けを実現するために、6 in 1結線方式を選択した。また、各IGBTすべてに、短絡保護を行うための電流センスと過熱保護のためにチップ温度を直接モニタ可能なオンチップ温度センスダイオードを配置した。

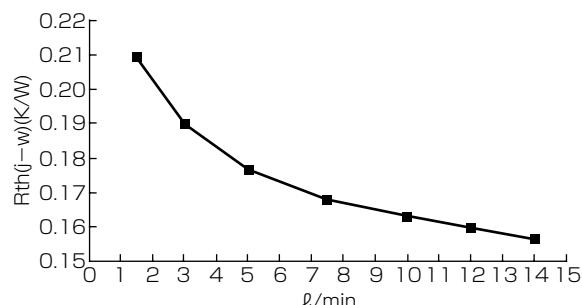

## 2.3 热抵抗

図3に冷却水流量に対する、CT600CJ1A060のチップ-冷却水間の熱抵抗R<sub>th(j-w)</sub>の測定結果を示す。評価に用いた水冷ジャケットはJ1シリーズ用評価キットを用いた。冷却水はLLC(Long Life Coolant)50%, 冷却水の流量が10(l/min)の条件で、R<sub>th(j-w)</sub>=0.163(K/W)を達成し、従来製品に対して30%以上の熱抵抗改善を実現した。

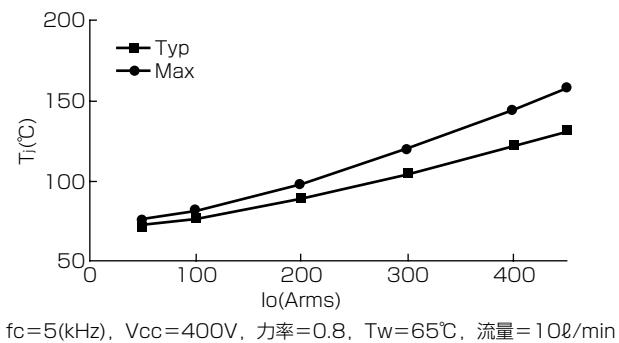

## 2.4 通電能力検証結果

電気的特性と熱抵抗の評価結果からJ1シリーズの通電能力を検証した。キャリア周波数f<sub>c</sub>=5(kHz), 冷却水温度T<sub>w</sub>=65(℃), 冷却水流量=10(l/min)の条件で、電気的

図2. J1シリーズ等価回路

図3. CT600CJ1A060の熱抵抗測定結果(IGBT側)

図4. CT600CJ1A060の通電能力検証結果

特性と熱抵抗をともに最大値とした場合でも、 $T_j = 150^\circ\text{C}$ 以下に収まり、出力電流600A(実効値で424(Arms))以上の通電が可能である(図4)。

### 3. J1シリーズ用評価キットの特長

評価キットはドライバボード、DC-Linkキャパシタ、水冷ジャケットで構成しており、J1シリーズの“高性能”“小型・軽量化”という特長を更に高めるために最適化している。評価キットはテストベンチでのJ1シリーズ評価用として開発している。図5にドライバボードと水冷ジャケットをJ1シリーズに組み合わせた写真を示す。ここではドライバボードと水冷ジャケットについて述べる。

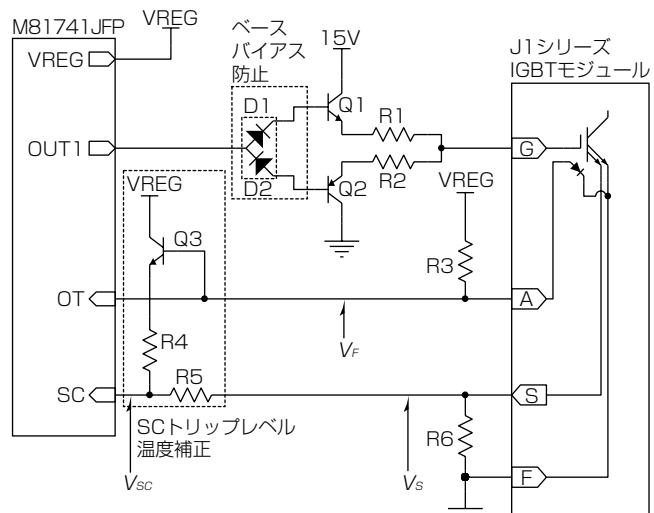

### 3.1 評価用ドライバボード

評価用ドライバボードは、三菱電機製ゲートドライバIC“M81741JFP”によるIPM(Intelligent Power Module)相当のIGBTゲート駆動・保護機能(過熱保護(OT), 過電流保護(SC), 制御電源電圧低下保護(UV))と, ゲート駆動用のDC／DC電源, 短絡保護回路, インターロック回路, PN間過電圧保護回路等を搭載する。OTとSCは, IGBTオンチップ電流センスとオンチップ温度センスダイオード出力を用いて実現している。

M81741JFPは、JシリーズT-PM及びJ1シリーズのゲート駆動・保護用として販売している。ドライバボードは、このM81741JFPの機能評価用としても活用できるよう、M81741JFPの主要出力信号モニタ用のテストポイントを設けている。

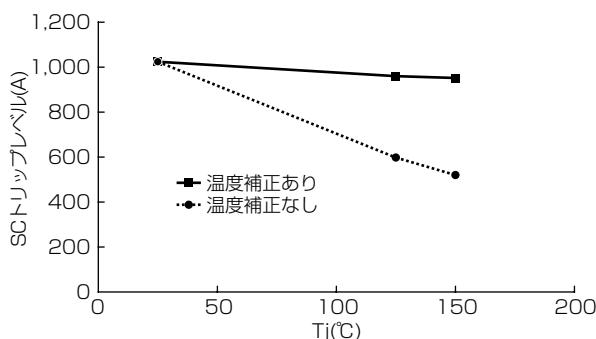

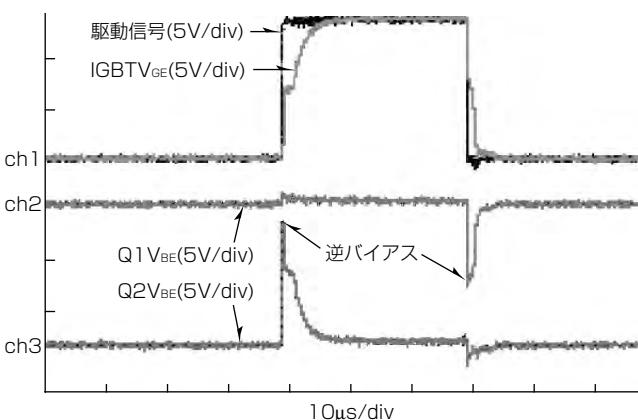

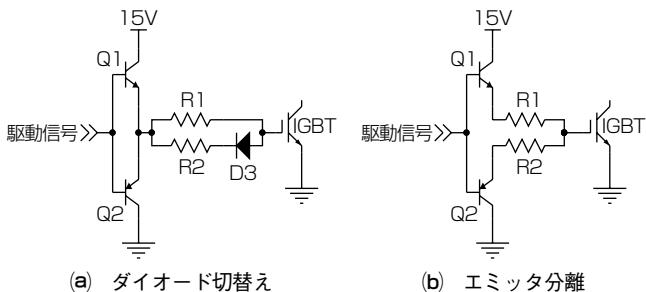

このドライバボードに採用したSCトリップレベル温度補正とゲートドライブバッファによるゲート駆動周辺回路を図6に示す。

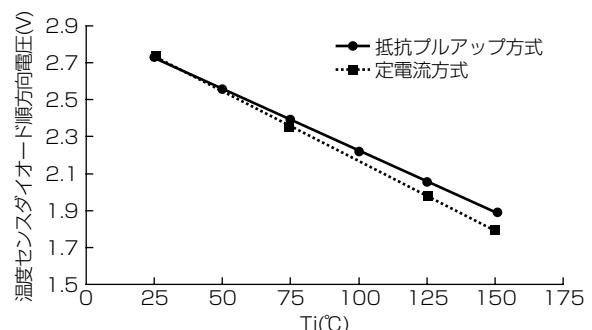

従来IPMではIGBTオンチップ温度センスダイオードのバイアス電流を定電流回路から供給していたが、このドライバボードでは定電圧源（VREG：M81741JFPから供給）と抵抗だけ（抵抗プルアップ）で供給している。CT600CJ1A060のオンチップ温度センスダイオードの順方向電圧 $V_F$ 値を、このドライバボードの抵抗プルアップと従来の定電流で測定した結果を図7に示す。抵抗プルアップ

図5. 評価キットの実装例

図6. ゲート駆動周辺回路

図7. オンチップ温度センスダイオードV<sub>F</sub>値