**MITSUBISHI**

*Changes for the Better*

家庭から宇宙まで、エコチェンジ

# 三菱電機技報

4

2013

Vol.87 No.4

## 製品の設計初期段階で品質を作りこむ 設計検証技術

### 目 次

|                                  |    |

|----------------------------------|----|

| 特集「製品の設計初期段階で品質を作りこむ設計検証技術」      |    |

| 設計システム技術センター20周年に寄せて             | 1  |

| 藤井雅雄                             |    |

| 製品の設計初期段階で品質を作りこむ設計検証技術          | 2  |

| 中岡邦夫                             |    |

| 品質改善のためのプロセス診断技術                 | 8  |

| 近藤聖久・久野倫義・中島 納                   |    |

| 定量的品質管理の効率化による                   |    |

| ソフトウェア設計品質の向上                    | 12 |

| 鈴木 博・塙本裕嗣・矢野雅嗣・高橋洋一・徳本修一         |    |

| ハードウェア模擬環境を活用した                  |    |

| 開発上流におけるソフトウェア品質向上               | 17 |

| 金井健太郎・大河原 繁・吉村 学・日比野慎也・原川雅哉・庄 晓杰 |    |

| 仕様書間のトレーサビリティ管理技術                | 22 |

| 宗像浩一・平井浩司・安江 悟                   |    |

| 大規模LSIの機能可視化手法                   | 26 |

| 山口啓太・山元浩幸・楠原崇史・石田仁志              |    |

| FPGAの定量的開発プロセス管理手法               | 30 |

| 古茂田典夫・城崎雅美・星 直之                  |    |

| 無線通信向け低消費電力アナログLSIの設計検証技術        | 34 |

| 上杉美喜夫・大野正輝・平峰正信                  |    |

| 冷熱空調家電でのCFD活用による                 |    |

| 省エネルギー上流設計・検証解析技術                | 38 |

| 小林 孝・中津哲史・衛藤 浩・濱田慎悟・児玉拓也         |    |

| 制御盤の放熱・耐震設計検証技術                  | 42 |

| 吉沢二郎・外池恵大・沖西佳雄                   |    |

| 変更影響分析による設計課題抽出プロセスの構築           | 47 |

| 菅ヶ谷貴也・長江雅史・西島暁生・山本順司             |    |

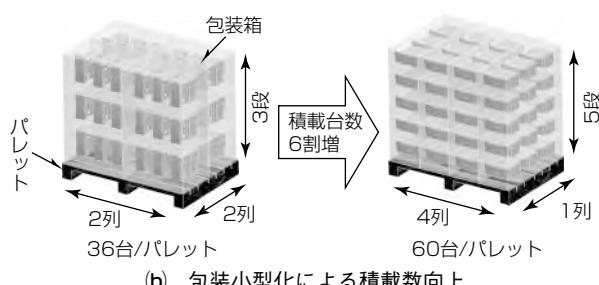

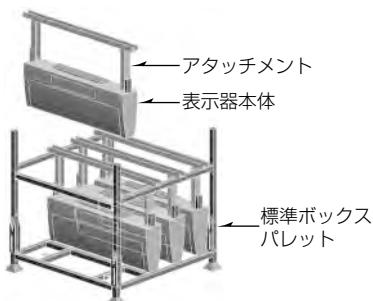

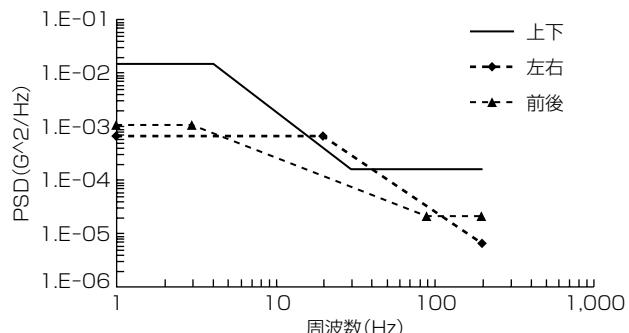

| 包装設計における設計検証技術                   | 51 |

| 潮 敬之・佐々木栄二・室園 透・武田正臣・山崎正博        |    |

### 特許と新案

|                         |    |

|-------------------------|----|

| 「低消費電力回路の設計支援装置」        |    |

| 「静的解析結果の分析表示装置」         | 55 |

| 「3次元CADモデル作成装置およびプログラム」 | 56 |

Design and Verification Technologies to Build in Quality in Early Stages of Product Design

Preface to the 20th Anniversary Design Systems Engineering Center

Masao Fujii

Design and Verification Technologies to Build in Quality in Early Stages of Product Design

Kuniaki Nakajima

Process Assessment Technique for Quality Improvement

Kiyohisa Kondo, Noriyoshi Kuno, Tsuyoshi Nakajima

Improvement of Software Design Quality by Effective Quantitative Quality Management

Hiroshi Suzuki, Hiroshi Tsukamoto, Masatsugu Yano, Yoichi Takahashi, Shuichi Tokumoto

Improvement of Software Quality in Upper Process of Development by Using Hardware Simulation

Kentaro Kanai, Shigeru Okawara, Manabu Yoshimura, Shinya Hibino, Masaya Harakawa, Gyoketsu So

Traceability Management Technique for Specification Documents

Koichi Munakata, Koji Hirai, Satoru Yasue

Visualization Technique in LSI Specification

Keita Yamaguchi, Hiroyuki Yamamoto, Takashi Kusuhara, Hitoshi Ishida

Quantitative Process Management Method of FPGA Development

Norio Komoda, Masami Shiroaki, Naoyuki Hoshi

Analog LSI Design Verification Techniques for Low-power Wireless Communication

Mikio Uesugi, Masaki Ono, Masanobu Hiramine

Energy Saving Design and Verification Method for Home Appliances Products using CFD

Takashi Kobayashi, Satoshi Nakatsu, Hiroshi Eto, Shingo Hamada, Takuya Kodama

Thermal and Earthquake Resistant Design and Verification Technologies for Control Console

Jiro Yoshizawa, Keita Tonoike, Yoshiro Okinishi

Frontloading Design Verification Technology by Change Impact Analysis

Yoshinari Sugiyama, Masashi Nagae, Akio Nishijima, Junji Yamamoto

Design Verification Technologies for Packaging

Takayuki Ushio, Eiji Sasaki, Toru Murozono, Masaomi Takeda, Masahiro Yamazaki

### 表紙：製品の設計初期段階で品質を作りこむ設計検証技術

三菱電機では、設計段階で品質を作りこむ“設計フロントローディング型開発プロセス”を推進しており、近年は、設計フロントローディング型開発で重要な設計検証技術のさらなる高度化に取り組んでいる。

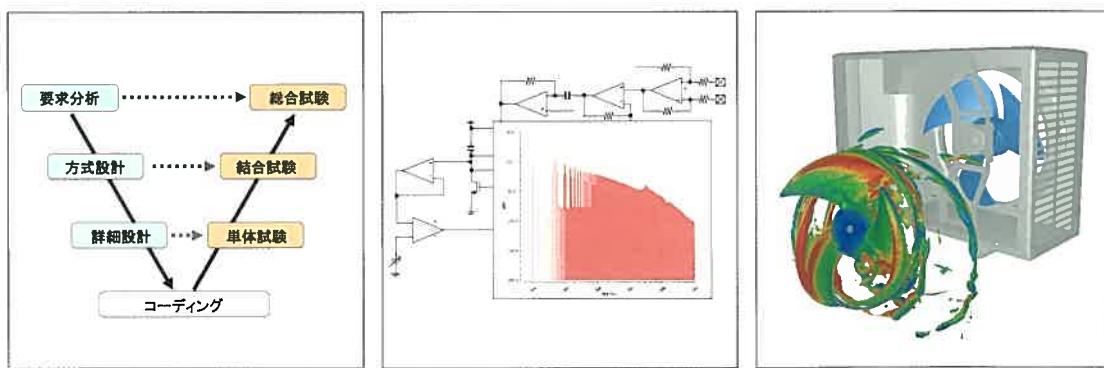

表紙は、“ソフトウェア”“LSI”“ハードウェア”的3分野の設計検証技術の中から、

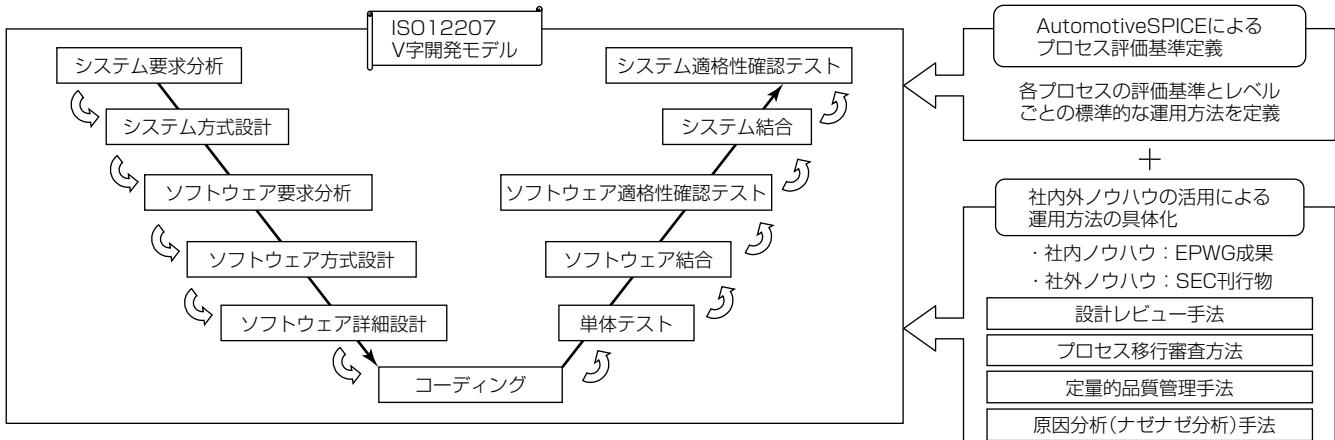

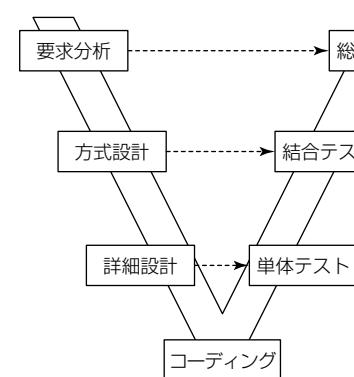

- ①ソフトウェア開発とデジタルLSI開発に適用しているV字開発モデル

- ②アナログLSIの回路図と出力波形

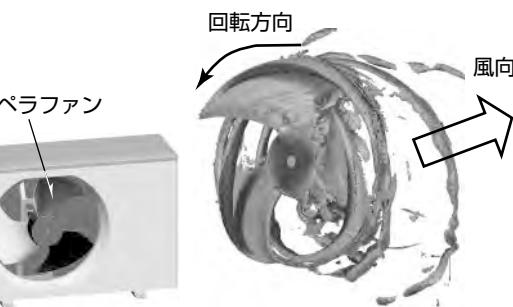

- ③ルームエアコン室外機の空力騒音の可視化図

を示す。

## 巻/頭/言

## 設計システム技術センター20周年に寄せて

Preface to the 20th Anniversary Design Systems

Engineering Center

藤井雅雄

*Masao Fujii*

新しい組織の誕生と発展には、多くの方々の期待と努力が凝縮されている。発足時から自らも在籍して期待にこたえるべく活動してきたことを振り返り、三菱電機設計システム技術センターの更なる発展の参考になればとの思いで綴る。

製品開発のグローバル化と企業間競争の激化は、革新的な製品開発とそれを実現するための飛躍的なQCDの向上、すなわち，“品質(Quality)の向上”，“費用(Cost)の低減”，“納期(Delivery)の短縮”を常に求める。

製品企画、設計、製造、販売、後対応(保守など)に至るモノづくりの全プロセスで、設計品質は全プロセスのQCDに多大な影響を与える。設計にはモノづくりに係る全プロセスの情報が集まり、設計者はその情報をベースに新たな情報を創出し、設計から全プロセスに発信する。設計はモノづくりの全プロセスにおける要となる存在である。また、製品開発の上流段階での十分な設計品質の作りこみは、コストオーバーランの抑制、設計手戻りの削減、試作回数の削減、試験工数の削減などを実現する。

設計システム技術センターの設立当時は、半導体技術の進展によって、デジタル化によるICT(Information & Communication Technology)技術がハード、ソフト両面で飛躍的な進歩を遂げつつあった。人間の知的な作業である設計のQCDを向上させるために、個々の製品開発の現場では、CAD(Computer Aided Design), CAE(Computer Aided Engineering)などの設計支援技術の導入、製品開発時に創出された知識の形式知化(設計便覧、図面など)と一部デジタルデータ化による共有、また、オンデマンド教育やOJT(On-the-Job Training)による暗黙知の伝承などが実施され、設計者の能力向上と新知識の創造に役立てられていた。

情報化の波は、工業化の波よりはるかに速い。設計システム技術センターの役割は、ICT技術の進歩を先取りし、モノづくりに関する設計・技術情報が集まりやすい仕組み、信頼できる情報の整理・統合・付加価値の創出、及び必要な情報を受け取りやすい仕組みを創り出すことにある。すなわち、設計・技術情報のハブを創り出すことである。そ

して、知識を創造する設計者の生産性を向上させ、製品開発における設計フロントローディングを加速させる目的で設立されたのが全社組織の設計システム技術センターである。設技セに継続して進めて欲しい業務は三つある。

一つ目は、本社組織として、全社的な設計・技術情報の共有化を実現するインフラの整備と進化である。特に、ソフトウェア設計、LSI(Large Scale Integrated Circuit)設計、ハードウェア設計分野での先進的な汎用設計支援ツールと設計技術の普及、データの共有化を進める。それによつて様々な組織間と製品群の統合や流用設計の容易化、コンカレントエンジニアリングの促進などが図れる。

二つ目は、製品固有の設計・技術情報の形式知化とデジタル化による共有化の促進である。設計ノウハウなどの暗黙知の獲得は、当該製品の設計者と一体となった活動が必須である。すなわち、製品開発の全プロセスの業務分析と設計業務の位置づけ、及び各プロセス間での情報の入出力の明確化を行い、デジタル化による設計・技術情報の統合と各設計支援ツールの知的化を図る。現場での業務分析は、技術者の生産性向上に対する意識改革と新たな課題の創出にもつながる。

三つ目は、社内外の研究機関との連携を密にする。各機関から発信される研究成果や新技術を自ら獲得して咀嚼(そしゃく)し、現場設計者への普及を図ることである。最先端のICT技術は学校教育にも浸透しつつある。20年前には皆無に近かった三次元CADとデジタルマネキンを用いたユニバーサルデザイン教育などが行われている。将来を担う技術者の育成は学産連携で行うことを進める。新たな知識、技術を持った人材の育成と活用は、企業内での人のローテーションも含め重要である。

最後に、バーチャルな世界での設計支援技術がいかに進化浸透しても、全ての設計を含むモノづくりのヒントはリアルな現場にあることを忘れてはならない。また、設計支援技術のゴールは、その技術を現場の設計者が使いこなし、全生産プロセスにおいてQCDの向上が実現されている状況を作り出すことにある。大局を忘れず、現場に密着した攻めの活動を今後とも期待したい。

# 巻頭論文

## 製品の設計初期段階で品質を作りこむ 設計検証技術

中岡邦夫\*

*Design and Verification Technologies to Build in Quality in Early Stages of Product Design*

Kunio Nakaoka

### 要 旨

設計システム技術センターは、三菱電機における製品設計の生産性向上と品質向上を目的に、設計システム技術で事業部を牽引(けんいん)する技術者集団として1993年に設立された。設立当初から一貫して当社製品のQCD(Quality:品質, Cost:開発コスト, Delivery:納期)改善を目的に設計業務の革新を推進してきた。設立20周年を迎えるにあたり、設立当初から現在までの設計業務革新の取組みについての変遷と最新設計検証技術について述べる。

製品ライフサイクルの中で最上位に位置する設計部門は、製品開発に必要な情報を作り出す発信源であり、製品コストの大半を決定することから設計の生産性向上と品質向上は極めて重要である。また、電子機器は半導体技術の進歩

によってシステムの大規模化や装置の小型化が目覚しい進化を遂げており、製品への要求事項が多様化しつつある。

そこで、電子機器の機能・性能を左右する“ソフトウェア”“LSI”“ハードウェア”的3分野における最新設計技術の開発と実用化を行い、事業部の設計現場と一体となり設計プロセスの改善を図ってきた。

設立当初は、IT技術を駆使した“トップダウン協調設計”に取り組み、次のステップとして、機能設計を中心とした設計業務の効率化に取り組み、さらに設計段階で品質を作りこむ“設計フロントローディング型開発プロセス”を推進してきた。近年は、設計フロントローディング型開発で重要な設計検証技術のさらなる高度化に取り組んでいる。

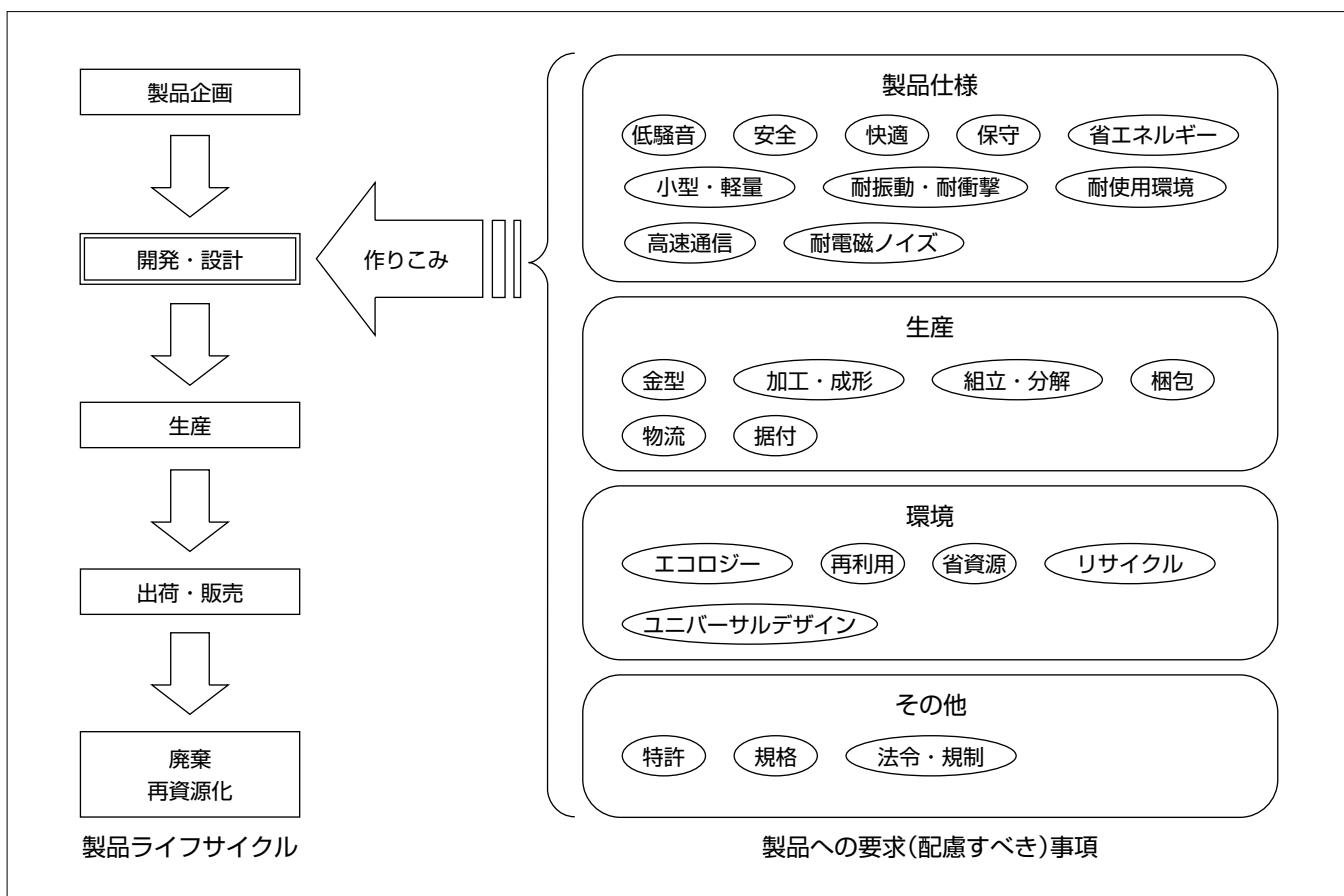

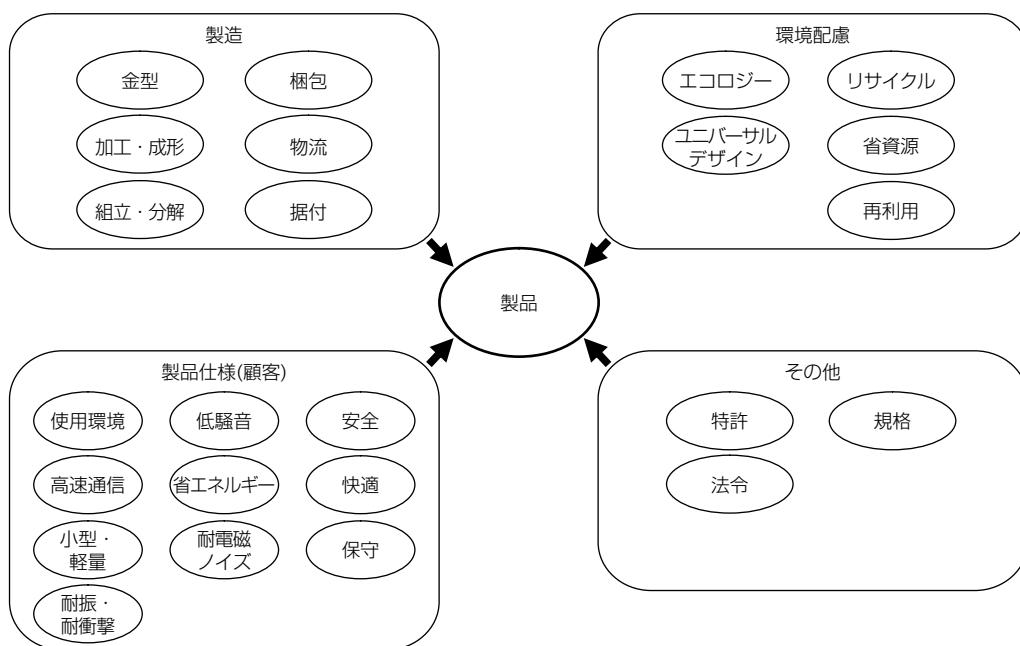

### 製品への要求事項例

小型・軽量・高性能・高機能化をはじめ、生産面での要求事項、さらには環境負荷低減や各国の法令準拠等、設計段階で配慮すべき事項が多様化しつつある。

## 1. まえがき

設計システム技術センターは、当社における製品設計の生産性向上と品質向上を目的に、設計システム技術で事業部を牽引する技術者集団として1993年に設立された。設立当初より一貫して当社製品のQCD改善を目的に設計業務の革新を推進してきた。

時代の変化とともに、設計段階で作りこむ事項は機能・性能だけでなく、環境への影響、各種規制への対応等にまで拡大した。この多様化した要求事項の相互関連性を考慮しながら、設計段階で確実に品質を作りこむためのプロセスを継続的に革新することが当センターの役割である。

設立20周年を迎えるにあたり、本稿では、設立当初から現在までの設計業務革新の取組みについての変遷と最新設計検証技術について述べる。

## 2. 設計システム技術センターの活動

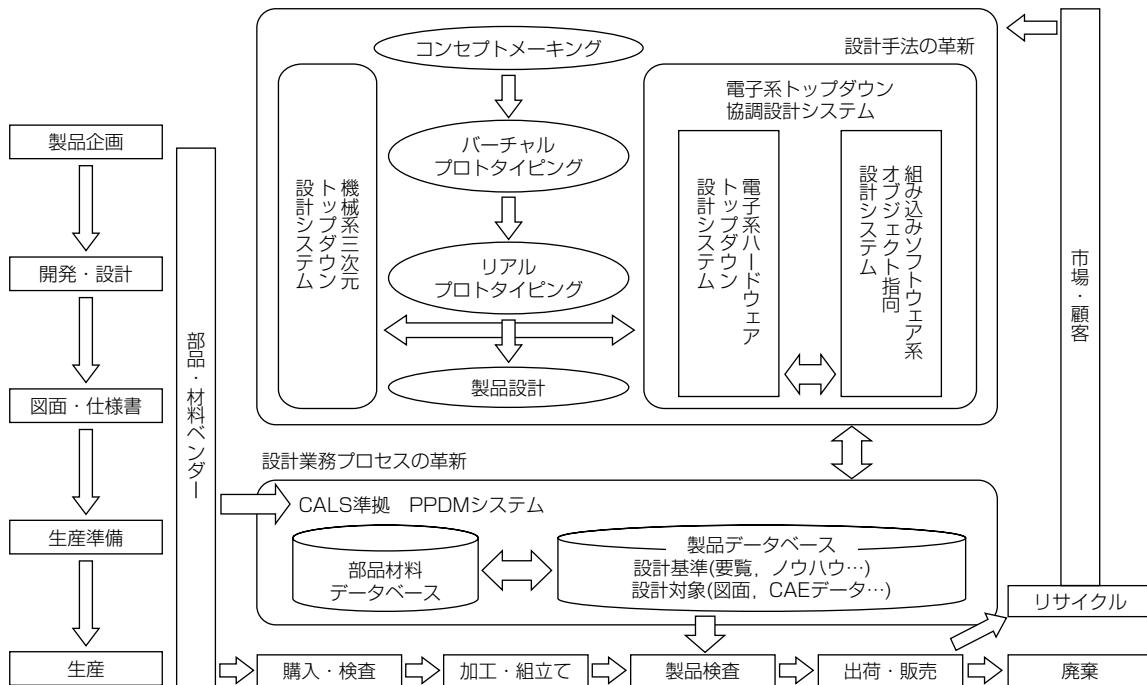

### 2.1 トップダウン協調設計の推進<sup>(1)</sup>

設立当初は、IT技術を駆使した“トップダウン協調設計”に取り組み、大規模化、複雑化するシステム設計の設計生産性向上を図った。電子系では、オブジェクト指向組み込みソフトウェア設計やプロセッサのソフトウェア化、大規模システムLSI化、大規模FPGA(Field Programmable Gate Array)化に取り組んだ。機械系では、製品の三次元CAD(Computer Aided Design)データを用いたデザインレビューやラピッドプロトタイピング、金型設計、組立設計等が実施できる環境を整備した。これらの取組みによっ

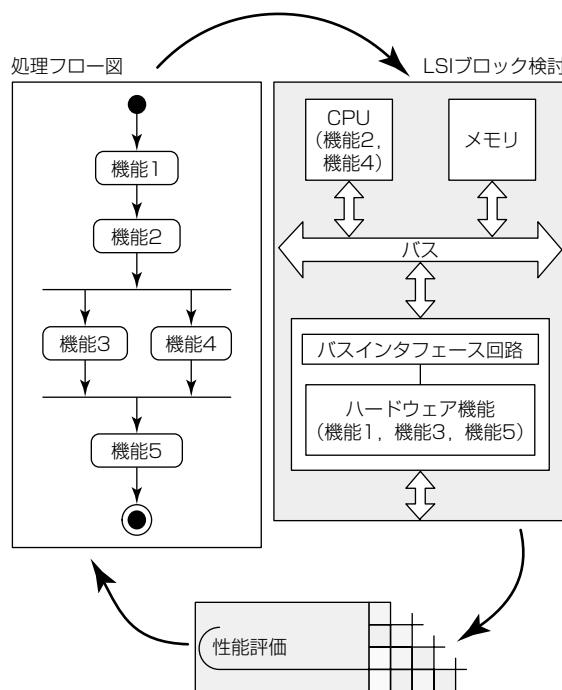

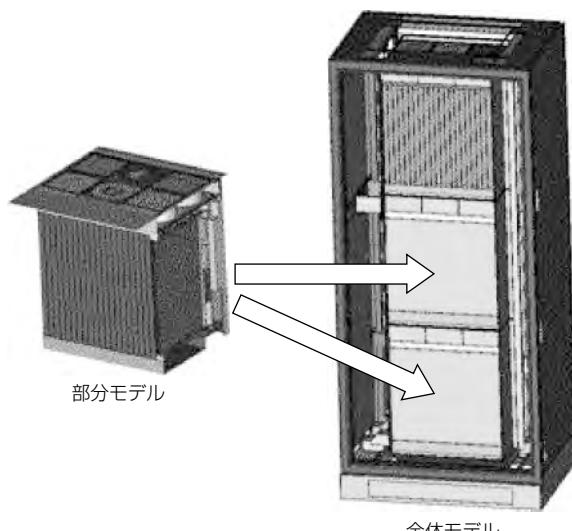

て、製品ライフサイクルにかかる部門間でコンカレントに設計業務が遂行できる環境を整備してきた(図1)。

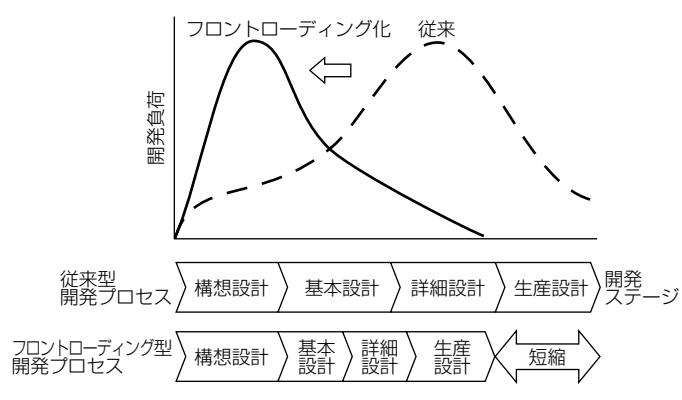

### 2.2 設計フロントローディング型開発プロセスの推進<sup>(2)(3)</sup>

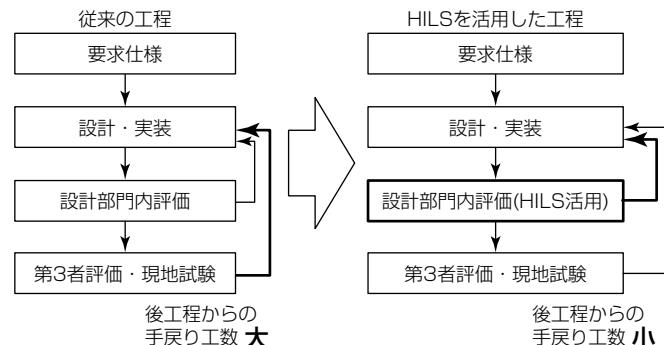

半導体の微細化は継続的に進展し、集積度と動作速度が増大し、システムの大規模化が進展してきた。それに伴い、開発の最終段階からの設計の見直しは事業に致命的な影響をもたらすようになってきた。

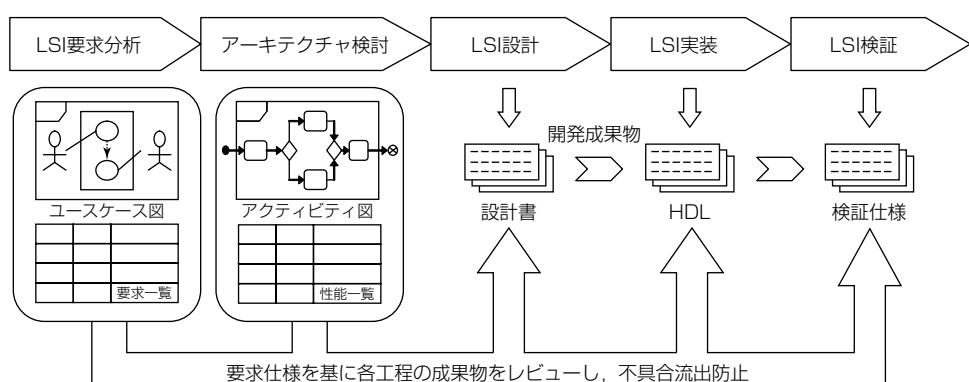

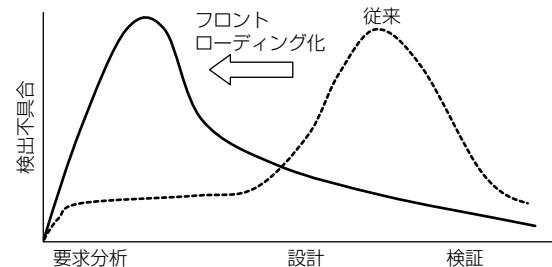

次のステップとして、機能設計を中心とした設計業務の効率化の取組みから、ソフトウェア開発、LSI開発、ハードウェア開発の設計初期段階で徹底的に機能検証を実施して、品質を作りこむ設計フロントローディング型開発プロセスを推進した(図2)。試験工程や部品加工、組立の後工程への不具合流出を防止し、手戻りの抑制や設計全体の効率化を図った。

ソフトウェア分野では、図式表現の適用によって仕様の見える化を実施し、要求仕様の定義段階でレビュー性を向

図2. 設計フロントローディング型開発

CALS : Continuous Acquisition and Life-cycle Support, PPDM : Process and Products Data Management

図1. トップダウン協調設計システム

上させた。

LSI分野では、ソフトウェア開発に用いられている図式表現を仕様設計に適用し機能可視化に活用した。また、アーサーション検証手法を適用して機能検証漏れを防止した。

ハードウェア分野では、製品全体の三次元CADモデルを用いた配線性や組立性の検証方法の実用化や、大規模解析のモデル化技術の構築による製品丸ごとの冷却検証や構造強度検証を実用化した。

## 2.3 設計検証技術の高度化

近年、グローバル化、モバイル機器や車載機器の用途拡大に伴う使用環境の多様化、通信量の増大、ソフトウェア量の増大、リサイクルや省資源等の環境配慮、省エネルギー、耐震、国際物流等、設計で検証すべき事項が増大しており、製品に要求される品質は更に厳しくなっている(図3)。このため、設計フロントローディング型開発で重要な設計検証力の更なる高度化に取り組んでいる。

## 3. ソフトウェア分野の設計検証技術

近年、交通・通信システムに代表される社会インフラシステムから、冷蔵庫やルームエアコン等の家電製品にいたるまで、機能の高度化は著しく、製品のライフサイクルも非常に短くなっている。そのため、従来ハードウェアで実現されていた機能がソフトウェアで実現される傾向が大きくなり、ソフトウェアの重要性がますます高まっている。

このような状況の下、製品に対するユーザー要求にこたえるには、ソフトウェア開発でQCDを適切に計画し達成する必要がある。そのためには、ソフトウェアの開発プロセスの確立と製品開発における設計検証が最重要項目である。

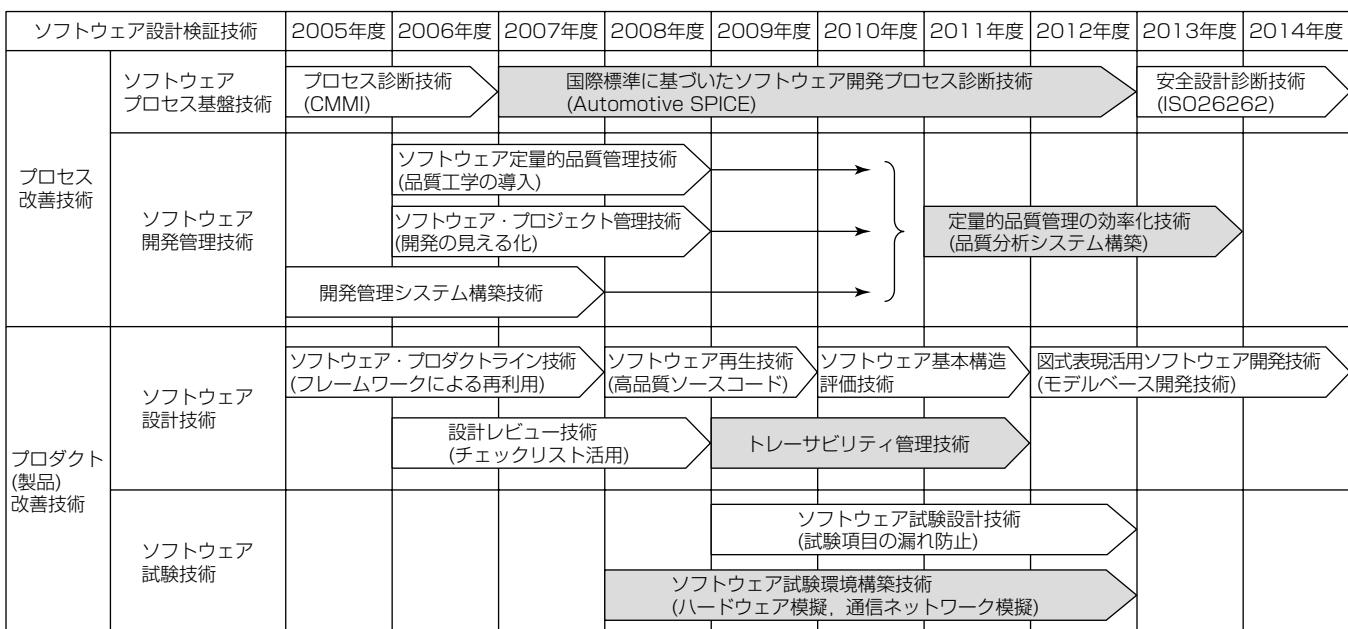

当社では、ソフトウェア開発プロセス確立のためのプロ

セス改善技術と製品の設計検証のためのプロダクト製品改善技術の開発に継続的に取り組んでいる(図4)。

### 3.1 プロセス改善技術への取組み

開発プロセス改善技術として、プロセス診断などの“ソフトウェアプロセス基盤技術”とプロジェクト管理などの“ソフトウェア開発管理技術”的開発に取り組んでいる。

#### (1) ソフトウェアプロセス基盤技術

2006年度まではCMMI(Capability Maturity Model Integration : 能力成熟度モデル統合)を基にプロセス改善に取り組んで来たが、2007年度以降はCMMIに加えエンジニアリング分野に重点を置いたAutomotive SPICE<sup>(注1)</sup> (Software Process Improvement and Capability dEtermination : SPICE)を基に標準プロセスを整備して、当社の各事業部に展開している。A-SPICEは設計から試験までの全プロセスを規定しているが、この特集号の論文“品質改善のためのプロセス診断技術”では、A-SPICE適用による設計段階のプロセス改善事例を中心に述べる。

#### (2) ソフトウェア開発管理技術

プロジェクト管理技術、及び計画品質確保のための定量的品質管理技術や計画コスト・開発進捗を監視・制御するための開発管理システム等の技術開発に継続的に取り組んでおり、基本開発は完了した。2011年度以降は定量的品質管理効率化のためのシステム開発を行い、実プロジェクトに適用している。この特集号の論文“定量的品質管理の効率化によるソフトウェア設計品質の向上”では、開発したシステムの概要と設計フェーズに適用した事例について述べる。

(注1) Automotive SPICEは、Verband der Automobilindustrie e.V. の登録商標である。

図3. 製品への要求事項

図4. ソフトウェア設計検証技術のロードマップ

### 3.2 プロダクト(製品)改善技術への取組み

製品開発では、3.1節で述べた開発プロセスを効率的に実施し、製品に要求される品質を短期間で設計し確認する必要がある。プロダクト改善技術として、品質作りこみ段階の設計技術と品質確認段階の試験技術の開発に取り組んでいる。

#### (1) ソフトウェア設計技術

当社のソフトウェア開発は流用開発が大部分を占め、流用開発の品質向上と開発効率化が課題となっている。そのため、これまでソフトウェアフレームワーク再利用による品質確保やソフトウェア基本構造検証による開発効率化等に取り組んで来た。また近年のソフトウェア規模の増大に伴い、複数仕様書間のトレーサビリティ確保も新たな課題となっている。この特集号の論文“仕様書間のトレーサビリティ管理技術”では、多数の設計仕様書間のトレーサビリティを確保し、仕様変更などに伴う影響範囲を短時間で確認可能にして設計品質を改善した事例について述べる。

#### (2) ソフトウェア試験技術

当社では組み込み型ソフトウェア開発が主流であり、ハードウェアと組み合わせた環境で、設計段階で作りこんだ品質を早期に効率的に確認することが重要である。この特集号の論文“ハードウェア模擬環境を活用した開発上流におけるソフトウェア品質向上”ではハードウェア模擬によって、ハードウェア入手前に短期間で試験環境を構築し、効率的に試験を実施して品質を確保した事例について述べる。

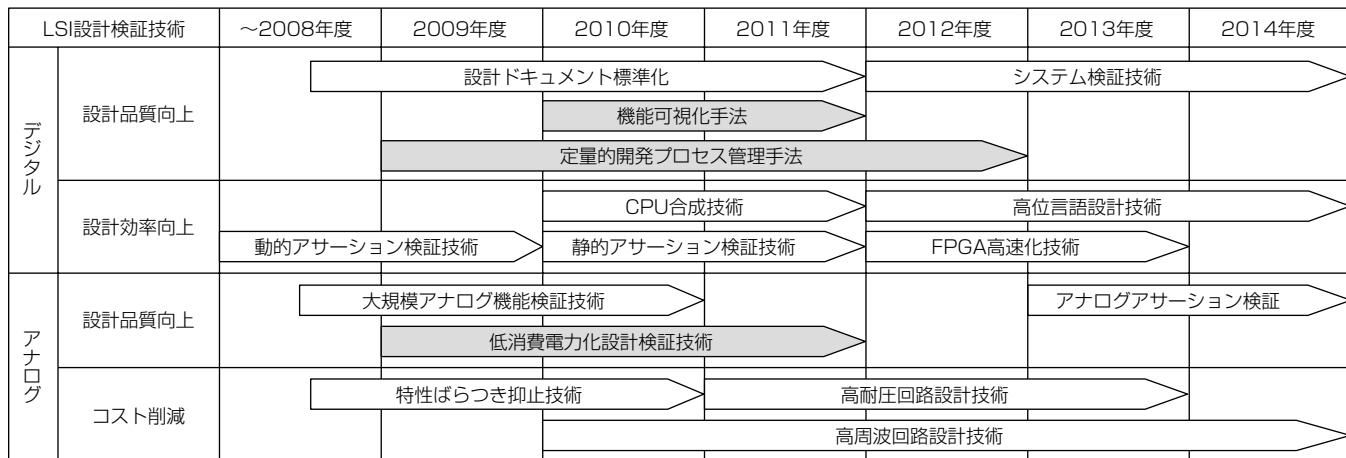

## 4. LSI分野の設計検証技術

近年、LSIは製造プロセスの微細化によって開発費が高騰しており、サンプルLSI製造後に不具合が判明した場合、

大きなロスコストが発生する。また、FPGAは回路を書き換えできるため、設計品質低下を招きやすく製品評価が長期化するという問題が発生している。これらの問題に対処するためには、設計の上流で品質を向上させ、下流工程に設計不具合を流出させない設計フロントローディングの取組みが重要となっている。

当社では、LSI開発における設計品質の向上と設計効率化と低コスト化のため、設計フロントローディングを推進する設計検証技術の開発と整備に取り組んでいる(図5)。

### 4.1 デジタルLSI設計検証技術への取組み

デジタルLSIに関しては大規模化、複雑化に対応するために、設計上流で設計品質を向上させ、下流工程に機能漏れや不具合を流出させない設計手法の取組みが重要である。そのために設計の源流で図的表現を用いた仕様の可視化手法やテンプレートを用いたドキュメント標準化、開発プロセスの定量的管理手法等を開発し、実開発に適用することで開発工数の削減と工期短縮の成果を得た。

#### (1) 大規模LSIの機能可視化手法

設計上流での品質向上の施策として、ソフトウェアで利用されているUML<sup>(注2)</sup> (Unified Modeling Language:統一モデリング言語)をLSIの仕様検討に適用し、仕様漏れや性能未達を防止した。この特集号の論文“大規模LSIの機能可視化手法”では、ソフトウェアの手法をLSI開発用に工夫した点を中心に述べる。

#### (2) FPGAの定量的開発プロセス管理手法

デジタル回路設計は言語ベース設計が主流となっており、ソフトウェアの開発に類似している。そのためソフトウェア分野で用いられている開発プロセス管理手法をLSI開発に適用した。この結果、上流の設計・検証段階における不

図 5. LSI設計検証技術のロードマップ

具合の検出率が高まり、製品評価からの手戻りが削減し、開発工数削減と工期短縮の効果が得られた。この特集号の論文“FPGAの定量的開発プロセス管理手法”では、その適用事例について述べる。

(注2) UMLは、Object Management Group Inc. の登録商標である。

#### 4.2 アナログLSI設計検証技術への取組み

アナログLSIに関しては、より安価なシリコン製造プロセスでアナログ性能を達成するために、2008年度から、次の設計フロントローディングの取組みを実施している。

##### (1) 大規模アナログ機能検証技術

アナログ回路はデジタル回路と混載してLSI化することによって、製品全体の低コスト化が可能となる。2009年にアナログHDL(Hardware Description Language)を用いてデジタル回路との混在検証に取り組み、デジタル回路とアナログ回路の仕様不整合を削減した。

##### (2) 高耐圧アナログ回路設計技術

アナログLSIは、製品の入出力機能に応じて多様な動作電圧が必要となる。5V以上の動作電圧に対応するためにLDMOS(Laterally Diffused Metal-Oxide-Semiconductor)を用いて高耐圧アナログ回路をLSIに集積化し、低コスト化を推進している。

##### (3) 低消費電力アナログLSI設計検証技術

携帯用無線機器などは、電池駆動のため低消費電力化が重要である。この特集号の論文“無線通信向け低消費電力アナログLSIの設計検証技術”では、トランジスタを弱反転領域で動作させることによって低消費電力化を行った事例について述べる。

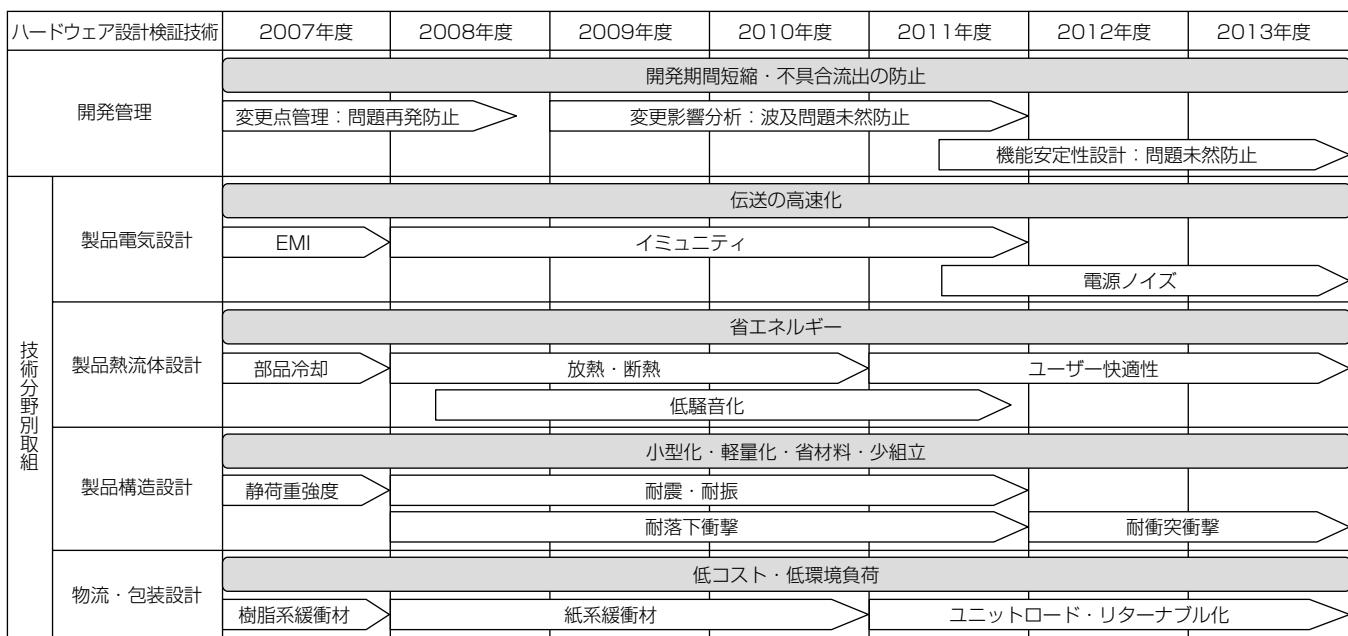

### 5. ハードウェア分野の設計検証技術

設計は必要な機能の実現に向かって1から演繹(えんえき)法的に進められれば美しい。しかし、現実のハードウェア設計では、決定すべき事柄が多すぎて、そのすべてを論理的に1から導出していくことが非現実的である場合

が多い。例えば、筐体(きょうたい)の設計で、部品を結合・固定するための正確なねじ締結位置を計算式で割り出して寸法値決定している設計者はほとんどいないだろう。

ねじ締結位置の例では、構造全体の状況や制約事項を考慮して設計者の感覚で仮に位置を決め、後でその締結位置で強度や剛性に問題がないか“検証”して決定するのが普通の進め方である。つまり多くの設計は“仮決めと検証”という帰納法的アプローチで進められている。

このアプローチは設計という行為そのものであるが、その中の検証の部分だけを指して我々は“設計検証”と呼称し、より高い精度、高い信頼性をもって設計検証を行うために必要な技術を“設計検証技術”と呼称している。

図6にハードウェア設計検証技術への取組みロードマップを示す。この特集号の論文でこの中のいくつかの取組み事例を述べるが、技術分野ごとの取組みは

- (1) 急速に進歩、高速化する半導体・通信関連

- (2) 環境負荷低減への要求、事業環境悪化(低コスト化)

- (3) 自然災害の脅威

- (4) グローバル化に伴う物流の変化

等に駆動されて年々進化・高度化を余儀なくされている。

電子機器や通信機器の高速化は目覚しく、先端的機器は数十Gbps以上の伝送速度になってきている。こうした超高速な機器ではEMI(Electro-Magnetic Interference)やイミュニティが常に問題となり、信号電圧の低下に伴って電源ノイズが深刻な課題になっている。

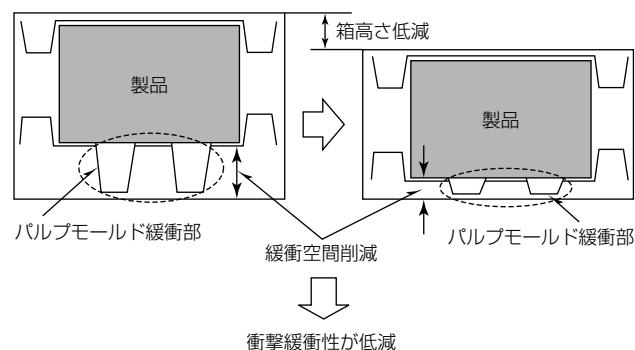

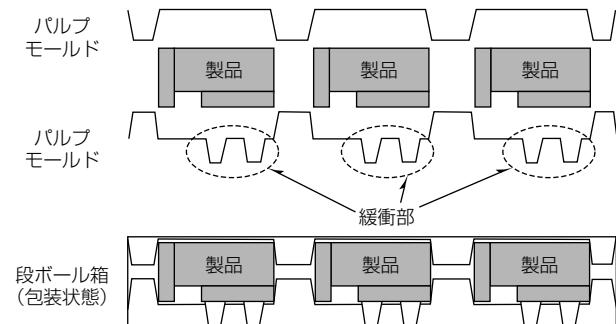

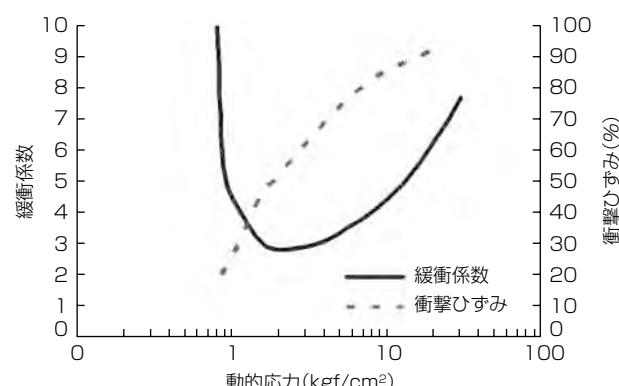

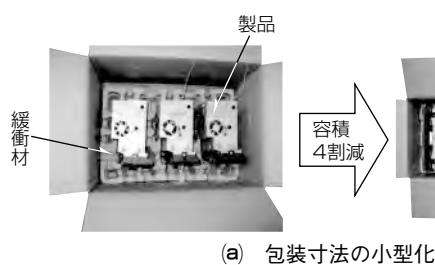

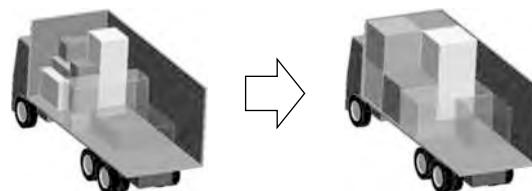

また、事業のグローバル化に伴って物流路が延び、物流のコスト低減が重要になってきている。さらに、環境負荷低減は企業の責務となってきており、包装材を低環境負荷のものに切り換える、1台のトラックでより多くの製品が運べるようにする等に必要となる設計検証技術に取り組み、低コスト、低環境負荷の物流を目指してきた。環境視点では冷熱機器の省エネルギー化が常に求められ、使用者にとっての環境であるファン騒音低減も含め設計段階での熱

図6. ハードウェア設計検証技術のロードマップ

流体に関する検証技術を継続的に構築している。

自然災害の脅威、とりわけ東日本大震災に代表されるように巨大地震に対する製品信頼性は重要となる。耐震設計の技術者は高齢化して年々減少しているが、当センターでは東日本大震災の数年前から耐震設計における設計検証技術の蓄積に注力してきている。

一方、当社製品はもちろんのこと、日本製品の重要なアピールポイントである“品質”は決して失うことができない要素である。品質については、“再発防止”から“未然防止”へと進化させるために、設計段階で機能の安定性を検証しておくことに取り組んでいる。

## 6. む す び

製品の設計初期段階で品質を作りこむ設計検証技術について述べた。今後は、設計フロントローディングを更に追求し、アイデア発想法などを適用した機能設計の革新にも取組みを拡大していく。

## 参 考 文 献

- (1) 藤井雅雄：設計業務を革新する設計システム技術，三菱電機技報，73，No.9，613（1999）

- (2) 竹垣盛一，ほか：フロントローディング型開発設計への取り組み，三菱電機技報，80，No.10，636～638（2006）

- (3) 山下昭裕，ほか：設計プロセス革新による開発効率化，三菱電機技報，84，No.12，660～663（2010）

# 品質改善のためのプロセス診断技術

Process Assessment Technique for Quality Improvement

Kiyohisa Kondo, Noriyoshi Kuno, Tsuyoshi Nakajima

近藤聖久\*

久野倫義\*

中島毅\*\*

## 要旨

近年、ソフトウェア開発を評価する枠組みであるISO/IEC 15504<sup>(1)</sup> (Software Process Improvement and Capability dEtermination : SPICE)を活用して、ソフトウェア開発プロセスを改善する組織が多くなっている。

特に、欧州の自動車メーカーは、Automotive SPICE<sup>(2)(注1)</sup>という自動車用SPICEによる能力水準達成を調達条件の一つとしており、加えて車載電子機器の機能安全規格ISO26262に準拠した開発プロセス確立のためにもAutomotive SPICEへの対応が必須となりつつある。

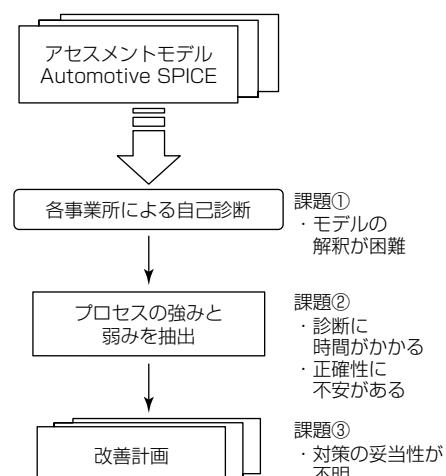

しかしながら、Automotive SPICEは、抽象的な記述内容の解釈やアセスメント方法の具体化が困難なため活用が難しく、自動車メーカーから要求される能力水準3の達成に3~4年を必要とする組織が多い。そこで、三菱電機グ

ループは、アセスメント及びアセスメント結果に基づくプロセス改善を効率的に行う技法を開発し、能力水準3の達成期間を約2年に短縮した。

最大の課題であった記述内容の解釈は、三菱電機グループ内の有識者が具体化してグループ内用語で書き換えることで解決し、三菱電機グループ向けのプロセス診断モデルを作成した。これによってグループ内のソフトウェア技術者による自己診断を可能とした。さらに、設計システム技術センターにプロセス改善の専門家であるアセッサを育成し、各事業所のアセスメントに加え、アセスメント結果に基づくプロセス改善も支援する体制を構築した。

(注1) Automotive SPICEは、Verband der Automobilindustrie e.V. の登録商標である。

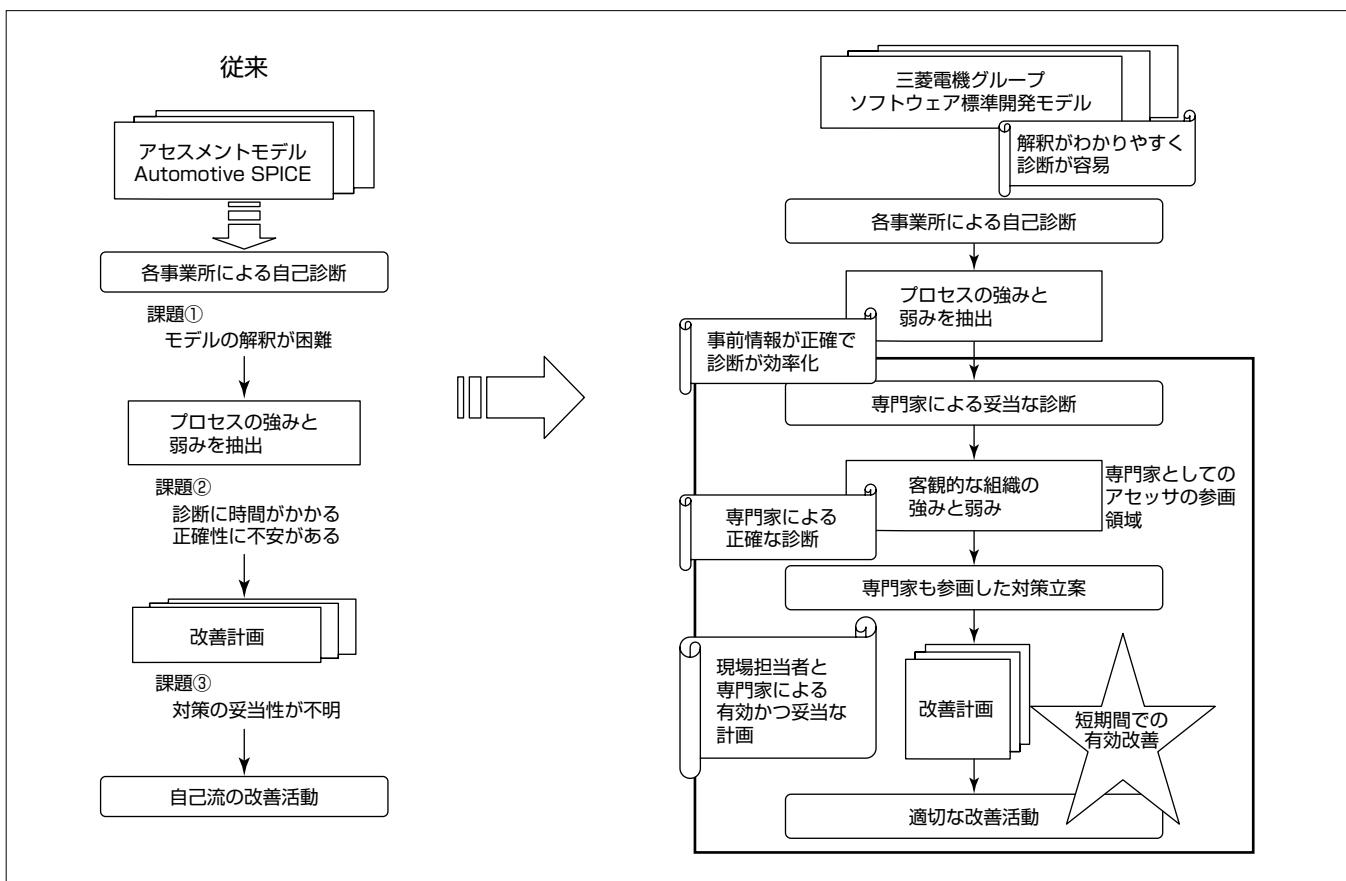

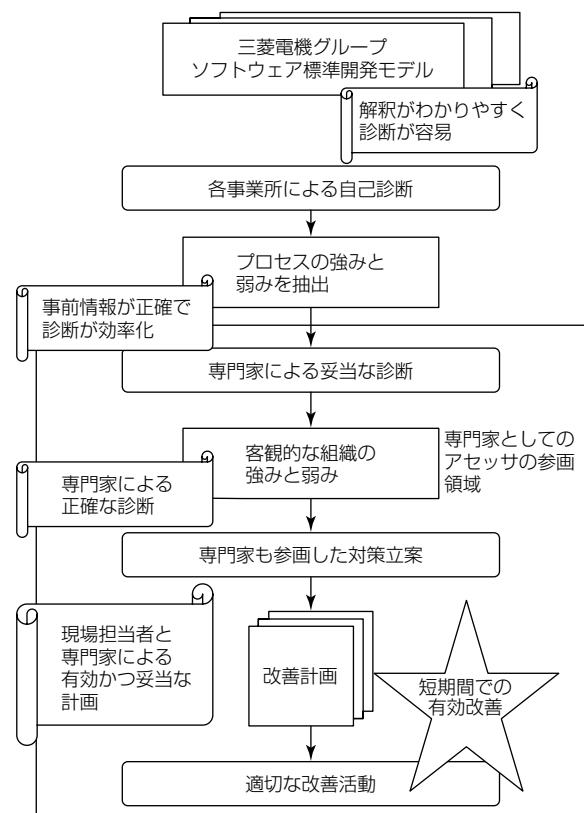

## Automotive SPICEを活用したプロセス診断活用技術

従来のアセスメントの課題に対し、三菱電機グループソフトウェア標準開発モデルを策定し、事業所の自己診断及び専門家による診断と改善施策を行う“品質改善のためのプロセス診断技術”を確立した。

## 1. まえがき

国際標準であるISO/IEC15504に準拠のAutomotive SPICEは、自動車分野におけるアセスメントモデルであり、主には欧州自動車メーカーで、調達条件として利用されることが多い。三菱電機グループの自動車分野のソフトウェア開発でも、アセスメントモデルに適合したプロセスに基づくソフトウェア開発が必要となっている。

Automotive SPICEは、開発プロセスに対する目標・成果、測定と制御等を求めており、自動車以外の分野でも、ソフトウェア品質向上、生産性の向上に有効なアセスメントモデルである。

そこで、三菱電機グループでは、Automotive SPICEによるプロセス診断を活用し、プロセス改善を効率的に行う技法を開発した。

## 2. Automotive SPICEの有効性と課題

### 2.1 活用上の有効性

三菱電機グループでは、ソフトウェアプロセス改善活動をAutomotive SPICEをベースに推進している。

Automotive SPICEは、欧州自動車業界がソフトウェア調達のために制定したものである。しかしながら、自動車のソフトウェアに特化した部位は少なく、次のように、他分野のソフトウェア開発にも活用できる特徴を持っている。

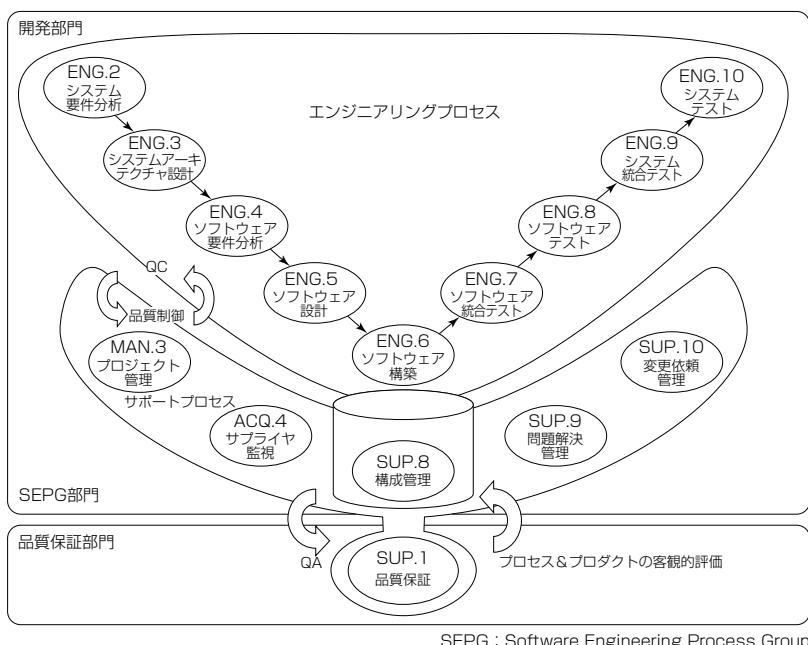

(1) 調達管理、構成管理、品質保証等の支援プロセスを含め、ソフトウェア開発に必要なプロセスを漏れなく定義している(図1)。

(2) 各プロセスに対して、目標、成果、成果に対する作業、成果物を定義している。

図1. Automotive SPICEのプロセス概要

(3) 要求-設計-試験のプロセスに対して、一貫性を確保する枠組みの必要性を定義している。

### 2.2 活用上の課題

Automotive SPICEは、2.1節に述べたように有効な点が多いものの、実際に活用するには次の課題があった(図2)。

#### (1) モデルの解釈

Automotive SPICEはソフトウェア開発を評価する枠組みであり特定モデルへの適用を意図したものではないため、表現が抽象的であり記述内容の解釈が困難である。さらに、モデル構造自体が初心者には分かりにくい。また、セミナー・や解説書が少ないため、知識の獲得やスキルの向上が困難である。

#### (2) 診断時間と正確性

自己診断によって強みと弱みを抽出する際に、診断に時間がかかる。また、抽出した強みと弱みが、モデルと整合しているか不安がある。

#### (3) 対策の妥当性

弱みから改善点を抽出して改善計画を策定するが、根本的な対策になっているかが不明である。

## 3. プロセス診断活用技術

### 3.1 ソフトウェア開発標準プロセスモデルの開発

2.2節の課題を解決するため、三菱電機グループの有識者を集め、Automotive SPICEをベースとして、グループ内外のソフトウェア開発に関するノウハウを盛り込んだソフトウェア開発標準プロセスモデルを開発した(図3)。

その特徴は次のとおりである。

#### (1) 用語の統一

三菱電機グループ内のソフトウェア開発で活用している用語を用いて、Automotive SPICEを再定義した。例えば、グループ内でも解釈が異なる“設計レビュー”という用語を検討し、

図2. アセスメントモデル活用上の課題

## (1) Automotive SPICEの導入による標準開発モデルの構築

## (2) 製品特性に応じたカスタマイズと実工事適用

- ①繰り返し型開発用のV字開発モデル定義

- ②ソフトウェア規模や流用率に応じたプロセス変更

- ③プロセス移行基準の見直し 等

EPWG : 全社横断でプロセス改善活動を実施するワーキンググループ

SEC : Software Engineering Center (経産省が管轄する独立行政法人)

図3. ソフトウェア開発標準プロセスモデル

“成果物に焦点を当てた品質保証活動として、自己チェックから照査、検認までを含む一連の活動”と定義するなど、用語の統一を図った。

## (2) 開発ライフサイクルモデルの定義

ソフトウェア開発のベースとなる開発ライフサイクルモデルは、一般的なウォーターフォール型開発モデルだけでなく、開発現場で多く使われている繰り返し型の開発モデルにも対応できるようにプロセスを定義した。さらに、段階リリース、複数回の試作サイクルによる一部プロセスの繰り返し開発を定義し、各プロセスへの入力成果物と出力成果物を確実に整合させることを利用条件とした。また、段階リリースの計画は初期計画段階でプロジェクト計画書に記載し、要求を明確に定義することとした。

## (3) 開発工程内における品質確保の仕組み定義

各プロジェクトで定義したソフトウェア開発工程の区切りごとに、設計レビューや工程移行の妥当性を確認する移行審査方法等を定義した。

## (a) 設計レビュー手法

設計レビューは、セルフレビュー(RO), ピアレビュー(R1), 書面レビュー(R2), 及び会議レビュー(R3)を段階的に組み合わせ、品質確保を確実なものとする手法として定義した。また必須活動とテラリングしても良い活動を明確化し、開発の現場で柔軟に適用できるようにした。

## (b) プロセス移行審査方法

プロセス移行審査とは、プロジェクトの品質、コスト、スケジュールの状況、リスクの状況、及び関係者間の関与の状況等について、計画(意図)したとおりの結果が得られるよう進んでいるかを、QCD(Quality(品質), Cost(費用), Delivery(納期))に関する総合的な視点と事業遂行上の視点、経営的観点から確認し、プロジェク

トに関する意思決定をするレビューである。

このレビューの視点を次のように定義した。

- (i) 計画と実績との差異の影響を特定できているか。

- (ii) Qを遵守した上で、Dを優先するか、Cを優先するかの判断。

- (iii) 計画と実績の差異を、工程延期やリソース追加によって挽回(ばんかい)可能か、リスク回避策(コンテンション)を明確にして計画(Work Breakdown Structure : WBS(作業分割構成)工程表含む)に組み込むことが可能であるか 等。

## (c) 定量的品質管理手法

ソフトウェアを含む製品の要求品質目標を達成するためには、定量的品質管理の実践が重要である。定量的品質管理活動は、最終製品品質を達成するために、開発の各プロセスにおけるプロダクト品質(成果物そのものの品質)及びプロセス品質(成果物の品質確保のための作業の品質)の定量的目標値を計画し、各プロセスで計画値と実績値の差異を把握・分析し、必要な場合には適切な正処置をとる活動とした。

## (d) 原因分析(ナゼナゼ分析)手法

ソフトウェア開発プロセスの各段階で確実に品質を確保するためには、発生したソフトウェア障害に対して、その発生原因と流出原因を突き詰め、類似の原因を取り除くとともに、その障害を生み出したソフトウェア開発プロセスへ確実にフィードバックすることで再発防止を行うことが必要である。

三菱電機グループでは、従来、根本原因分析手法を利用している。利用における課題は、その効果が実施者のスキルに依存することが多いことであった。そこで、ソフトウェア開発に効率的・効果的に適用できる“ナゼナゼ分析手法”を開発した。

### 3.2 プロセス診断活用技術

プロセス診断結果をプロセス改善に有効活用するためプロセス診断の枠組み定義と体制構築を行った。

#### 3.2.1 プロセス診断の枠組み定義

##### (1) 自己診断

ソフトウェア開発標準プロセスモデルを活用した自己診断方法を確立し、従来は困難であった自己のプロセス診断を容易に行えるようにした。自己診断方法の特徴は、プロセスごとに、プラクティス、解釈例、インプット例、アウトプット例を一覧化し、自己診断時に解釈と課題を記載することである。これによって、特に有資格のアセッサが居なくても自己組織の強みと弱みを抽出し、自ら改善を推進することができるようになった。

##### (2) 有資格アセッサによる客観的なプロセス診断

自己診断だけでは点検者によって診断結果にばらつきが出ることがある。また顧客からAutomotive SPICEの有資格アセッサによるプロセス診断を受注条件として要求されることがある。そこで設計システム技術センター内に、有資格アセッサによる公式アセスメントを行える体制を構築した。加えて、自己診断結果を入力情報として利用することで、詳細な組織内部の状態を把握するための細やかで精度の高い診断が可能となった。また、事前に情報が多く得られるので、短期間でプロセス診断を実施することが可能になり、公式アセスメント時の受診組織の負担も軽減できる。

一般にアセスメントでは、プロセス診断だけを行い、具体的なプロセス改善までは実施しない。三菱電機グループでは、アセッサは各事業所のプロセス診断だけでなく、プロセス改善にも参加し、改善施策の検討、改善計画の策定、施策の効果の確認、施策展開の支援等、事業所と一体となった改善を推進し、短期間で改善の効果をあげている(図4)。

#### 3.2.2 プロセス診断の体制構築

これらの枠組みによってプロセス診断・改善を行うため、次の役割を定義し、プロセス診断・改善実施者を育成した。

##### (1) 有資格アセッサ

外部アセッサに頼らず、客観的に各事業所のプロセスを診断するのにプロセス改善の専門家である有資格アセッサを設計システム技術センター内に育成した。

##### (2) 自己診断者

標準開発モデルと実開発プロセスの差異を自己診断する方法をガイド化し、点検方法を設計システム技術センターの有資格アセッサが指導し、自己診断者を育成した。

##### (3) SEPG

SEPG(ソフトウェアプロセスの改善活動を行うグループ)の役割を計画、実装、確認、維持、定着のフェーズに分類し、具体的活動を定義した。さらに、定義した活動に基づき、教育プログラムを構築し事業所のSEPGを育成し

図4. アセスメント診断活用技術

た。教育では、問題点の本質を突き止め、改善策を検討し、対策するまでをケーススタディで実施することで、実践的な改善力を習得させた。

## 4. む す び

現在、Automotive SPICEによるプロセス改善を推進するため、当社では設計システム技術センターに専門家である有資格アセッサを育成し、グループ内の各事業所に対するプロセス診断とプロセス改善支援を強化することによって、次の成果をあげている。

- (1) 三菱電機グループ内の有識者を集めAutomotive SPICEをベースに、三菱電機グループのプロセス診断モデルを開発した。

- (2) 設計システム技術センターの有資格アセッサが、各事業所の改善活動を支援し、能力水準3相当に達する期間を3~4年から、約2年に短縮した。

- (3) 各事業所のベストプラクティスを収集し、改善事例を各事業所に展開し、グループ全体のシナジーを活用することで、ソフトウェア生産力を向上させた。

## 参考文献

- (1) ISO/IEC15504-5 (2004)

- (2) Automotive SPICE Process Assessment Model V2.5 (2010)

# 定量的品質管理の効率化による ソフトウェア設計品質の向上

鈴木 博\* 高橋洋一\*\*\*

塚本裕嗣\*\* 徳本修一\*\*\*

矢野雅嗣\*\*\*

*Improvement of Software Design Quality by Effective Quantitative Quality Management*

Hiroshi Suzuki, Hiroshi Tsukamoto, Masatsugu Yano, Yoichi Takahashi, Shuichi Tokumoto

## 要旨

近年、ソフトウェアが大規模・複雑化する中、計画されたQCD(Quality(品質), Cost(費用), Delivery(納期))を達成することはソフトウェア開発における大きな課題の一つとなっている。計画QCDを達成するためには、設計段階で品質を作りこみ、試験段階ではその品質を確認するという開発プロセスを短期間で効率的に実施することが重要である。そのためには、設計時に作成する仕様書などの品質を定量的に把握・分析し、弱点を早期に抽出して設計品質を確保する必要がある。

品質の定量的把握・分析に必要なソフトウェア品質データの収集・分析は、これまで人手によって表計算ソフトウェアなどのツールを使って行われていたため、データ収

集・分析に時間がかかり開発のホールドポイントで定量的な品質の把握が十分にできないという課題があった。

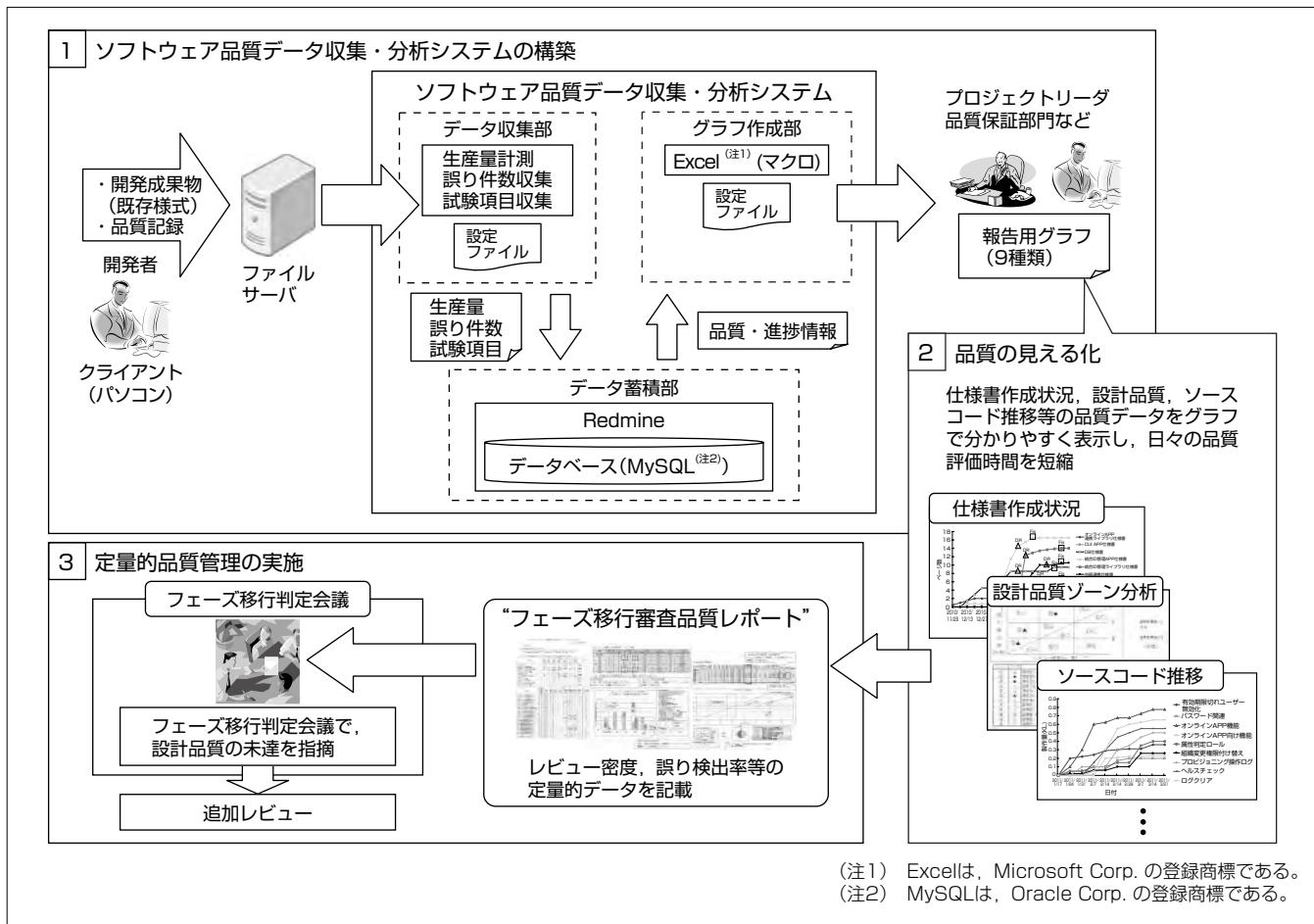

この課題を解決するため、効率的な定量的品質管理の実現を支援する“ソフトウェア品質データ収集・分析システム”を開発し、ソフトウェアの設計品質向上を実現した。

このシステムは開発者が作成する仕様書などの開発成果物、及び仕様書のレビュー結果等の品質記録を入力とし、仕様書作成状況などを表す複数のグラフを自動生成する。既存の仕様書様式を変更することなく品質状況を表すグラフの作成が可能であり、品質管理のための開発者への負担を最小限に抑え、開発フェーズごとに必要な品質情報を短時間で提供することで、品質向上を実現した。

## “ソフトウェア品質データ収集・分析システム”を活用した定量的品質管理

開発者は作成した仕様書、及びそれらに関わる品質記録をサーバに格納する。このシステムはこれらを入力として、仕様書作成状況などの品質に関わる複数のグラフを自動生成する。開発フェーズ移行判定会議ではこれらのグラフを用いて作成した品質レポートを基に移行判定を行う。

## 1. まえがき

近年、ソフトウェアが大規模・複雑化する中、計画されたQCDを達成することはソフトウェア開発における大きな課題の一つとなっている。計画QCDを達成するためには、設計段階で品質を作りこみ、試験段階ではその品質を確認するという開発プロセスを短期間で効率的に実施することが重要である。そのためには、設計時に作成する仕様書などの品質を定量的に把握・分析し、弱点を早期に抽出して設計品質を確保する必要がある<sup>(1)</sup>。

品質の定量的把握・分析に必要なソフトウェア品質データの収集・分析は、これまで人手によって表計算ソフトウェアなどのツールを使って行われていたため、データ収集・分析に時間がかかり開発のホールドポイントで定量的な品質の把握が十分にできないという課題があった。

この課題を解決するため、効率的な定量的品質管理の実現を支援する“ソフトウェア品質データ収集・分析システム”を開発し、実開発へ適用してソフトウェアの設計品質を向上させた。

本稿では、このシステムの概要、機能、及びそれらの機能によって解決される問題点を中心に述べる。

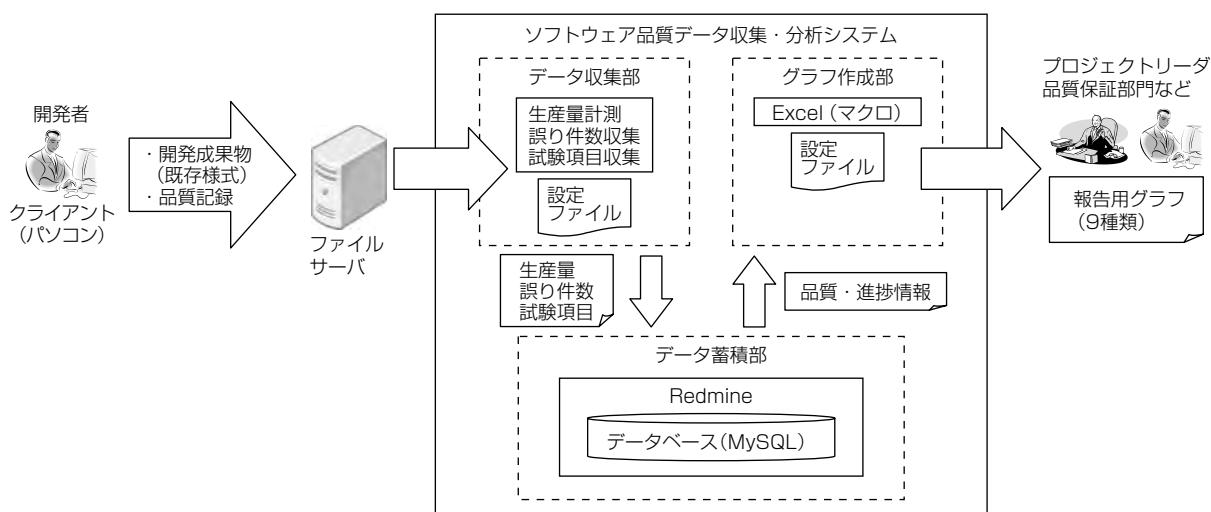

## 2. ソフトウェア品質データ収集・分析システム

### 2.1 システム構成

このシステムは図1に示すように、“データ収集部”“データ蓄積部”“グラフ作成部”的3つの要素で構成した。

開発者は設計仕様書などの開発成果物をクライアントパソコンで作成し、サーバに格納する。また、仕様書のレビュー結果などの品質記録も合わせてサーバに格納する。これらの開発成果物及び品質記録をこのシステムへの入力とする。

#### 2.1.1 データ収集部

データ収集部では、サーバに格納された仕様書のページ

数などの生産量を計測する。また、品質記録データから誤り件数や誤り種別などの情報を取り出し、生産量と併せてCSV(Comma Separated Values)ファイルを生成する。このCSVファイルはRedmine<sup>(2)</sup>(データ蓄積部で使用しているプロジェクト管理ソフトウェア)の管理単位である1チケット分の情報に相当する。

ファイルサーバ上の品質記録は通常表計算ソフトウェアのデータとして格納され、次のような状況が想定される。

- (1) 開発プロジェクトごとに書式やファイル名称、ファイル数が異なる可能性がある。

- (2) 開発プロジェクトごとに、ファイルの存在するサーバ上のディレクトリが異なる可能性がある。

- (3) 開発フェーズによって書式が異なる可能性がある。

そのため、データ収集部では、その設定ファイルでデータの抽出元を品質データファイルのセル単位まで指定可能としている。さらに、開発プロジェクトごとに別の設定ファイルを用意することで、プロジェクトによる仕様書などの書式の違いに対応し、複数プロジェクトでの品質データの同時計測も可能としている。

#### 2.1.2 データ蓄積部

データ蓄積部では、データ収集部で生成した品質関連のCSVデータをRedmineで処理可能なチケット形式に変換して、データベースに格納する。

Redmineはオープンソースソフトウェアであり、三菱電機での使用実績もあることから、このシステムの開発期間短縮及び開発コスト削減のために採用した。また、Redmineを使用することで障害管理や進捗管理などのRedmineの持つ各種機能を直接使用することも可能となり、プロジェクト管理・品質管理方法に柔軟性を持たせることができた<sup>(3)</sup>。

#### 2.1.3 グラフ作成部

グラフ作成部ではデータ蓄積部に格納されている品質データを基に、仕様書作成状況や仕様書の品質評価状況を表

図1. ソフトウェア品質データ収集・分析システム

すグラフ(表1)を作成する。グラフ作成部の設定ファイルにどのグラフを作成するかを指定することで、プロジェクトリーダーや品質保証部門が必要とするグラフを作成することができる。また、将来プロジェクトマネージャーがブラウザ経由でリアルタイムに品質状況を確認できるようにするために、イメージファイル出力機能も実現した。

## 2. 機能

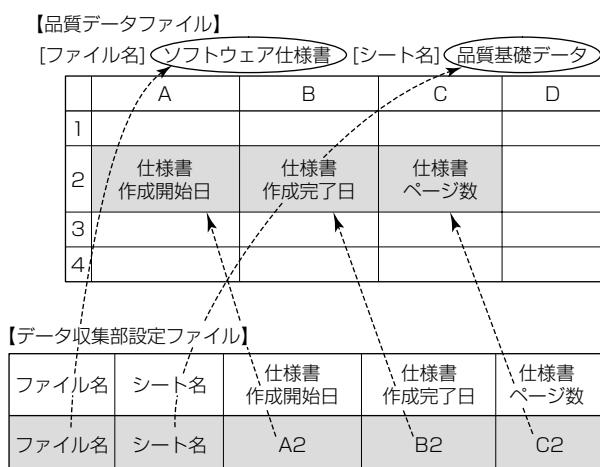

### 2.2.1 既存様式の仕様書から品質データを自動収集

異なるプロジェクトでは、使用する品質データの記録様式などが異なる場合が多く、品質状況を表すグラフを生成する場合は、システム仕様に合わせて入力ファイルを作成し直す必要がある。しかしながら、プロジェクトごとに入力ファイルを作成し直すことは、開発工程上大きなオーバヘッドとなり、工程遅延を引き起こす要因にもなりかねない。そのため、このシステムでは品質データを収集する際に設定ファイルに各種情報を設定することで、既存様式で作られた仕様書などを変更することなく、品質データの自動収集を実現している。

設定ファイルの記載例を図2に示す。この例では、“仕様書作成開始日”“仕様書作成完了日”“仕様書ページ数”等のデータが“ファイル名：ソフトウェア仕様書”“シート名：品質基礎データ”に格納されており、それらの位置を示すデータを“データ収集部設定ファイル”に設定すること

で、対応する値を参照している。このように、設定ファイルでデータの所在を指定することで、異なる様式の仕様書にも柔軟に対応することができる。

また、“仕様書作成開始日”などの追加属性はRedmineの標準チケットのカスタムフィールドを使用して拡張し、一つのチケットで品質情報まで含めて一元管理した。

### 2.2.2 品質状況をグラフで分かりやすく表示

既存様式で作成された仕様書から自動収集したデータを基に複数のグラフを自動生成することで、短時間で品質状況を見える化することができる。このシステムで作成するグラフは、設計段階だけでなく製造・試験段階での品質確認も考慮して作成した。今回、設計段階で実開発へ適用した主なグラフは次のとおりである。

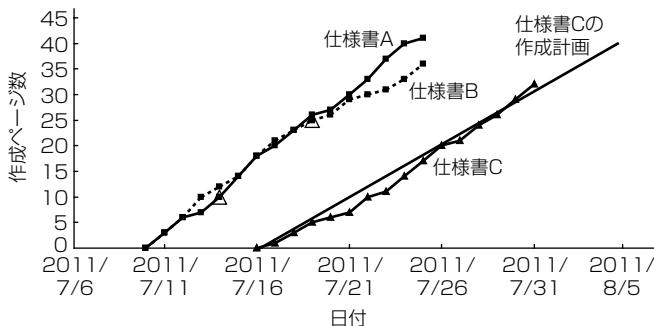

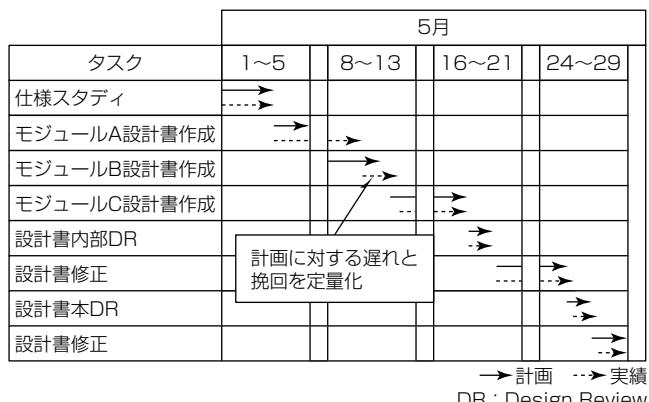

#### (1) 仕様書作成状況

サーバに格納されている仕様書のページ数を自動的にカウントし、日次・週次の仕様書の作成状況をグラフ化する(図3)。図から、作成開始日から作成完了予定日までの計画線と比較することで、例えば仕様書Cは作成当初は計画より遅延していたものの、後半は計画通りの進捗に挽回(ばんかい)していることが分かる。このようにして、作成業が遅延している仕様書を把握し、改善を図ることができる。

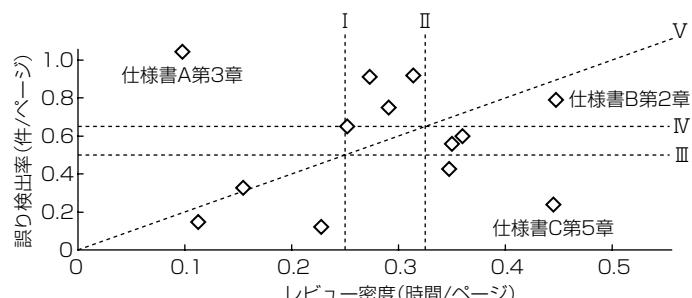

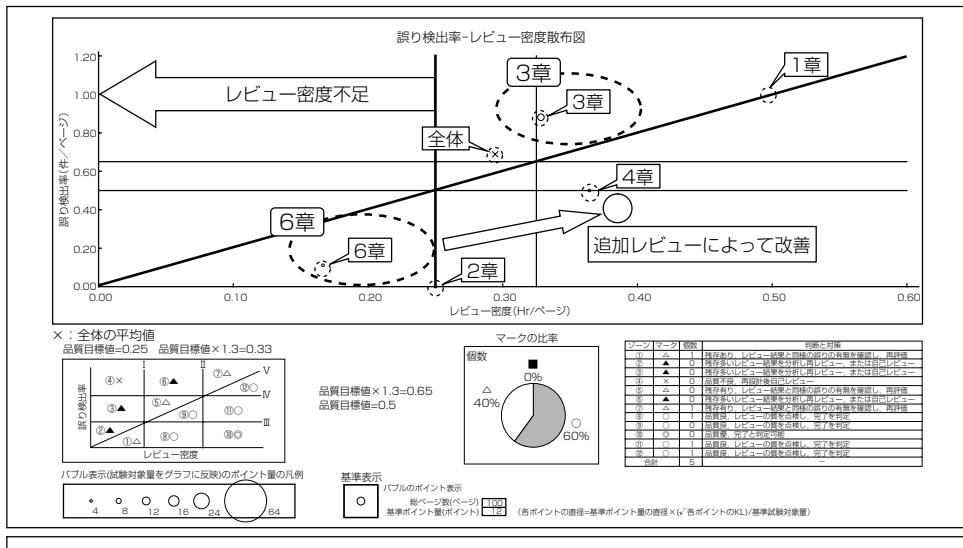

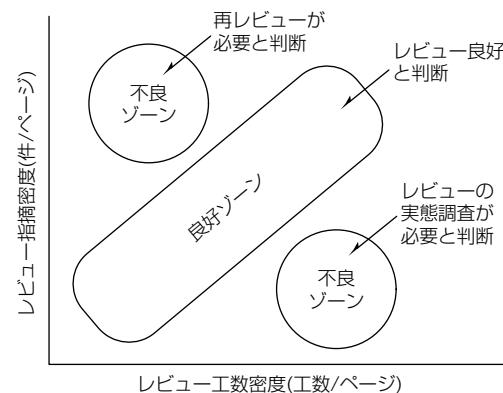

#### (2) 設計品質ゾーン分析

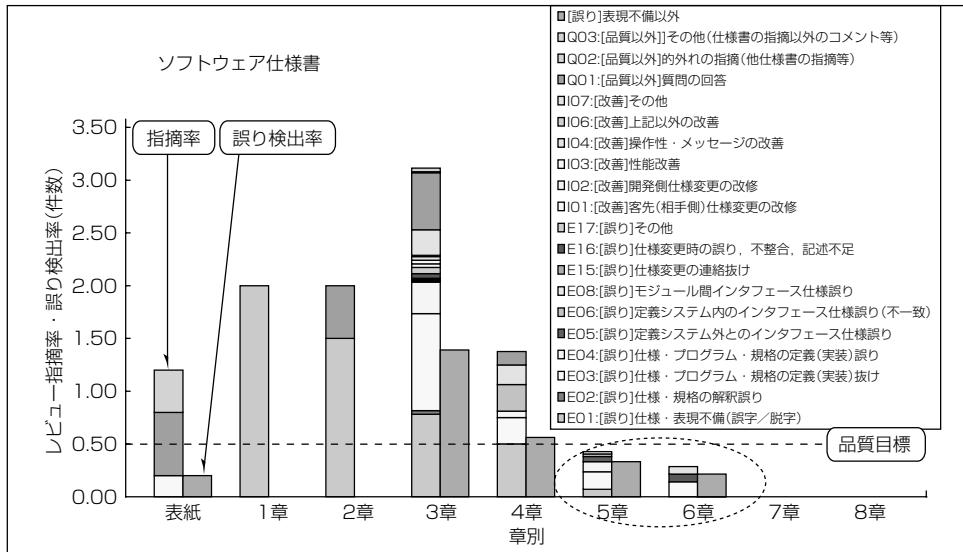

仕様書のレビュー結果を基に、1ページあたりのレビュー密度(時間/ページ)と1ページあたりの誤り検出率(件/ページ)を指標として、仕様書の品質状況を見える化している(図4)。図から、“仕様書A第3章”はレビュー密度が低く誤り検出率が高いため、品質不良であり、再レビュー

表1. 作成グラフ一覧

| グラフ名称         | 内容                      |

|---------------|-------------------------|

| 1 仕様書作成状況     | 日次・週次での仕様書作成状況          |

| 2 設計品質ゾーン分析   | 仕様書の品質状況                |

| 3 ソースコード推移    | 日次・週次でのソースコード作成状況       |

| 4 試験進捗管理      | 試験項目数(計画・実績)等の推移        |

| 5 機能別誤り発生推移   | 日次・週次での機能モジュールごとの誤り発生推移 |

| 6 試験品質ゾーン分析   | 機能モジュールごとの品質状況          |

| 7 開発フェーズ別誤り推移 | 開発フェーズごとの誤り発生推移         |

| 8 累積工数推移      | 作業工数(計画・実績)推移           |

| 9 残存誤り推定      | 開発フェーズごとの残存誤り推移         |

図2. データ収集部の設定ファイル記載例

図3. 仕様書作成状況

図4. 設計品質ゾーン分析

による改善が必要であることが分かる。また、"仕様書C第5章"はレビュー密度が高く、誤り検出率が低いことから、品質は良好であると判断できる。このようにして、レビューが不足している仕様書(又は仕様書内の章)が明らかになり、再レビューを行うことで設計品質を向上させることができる。

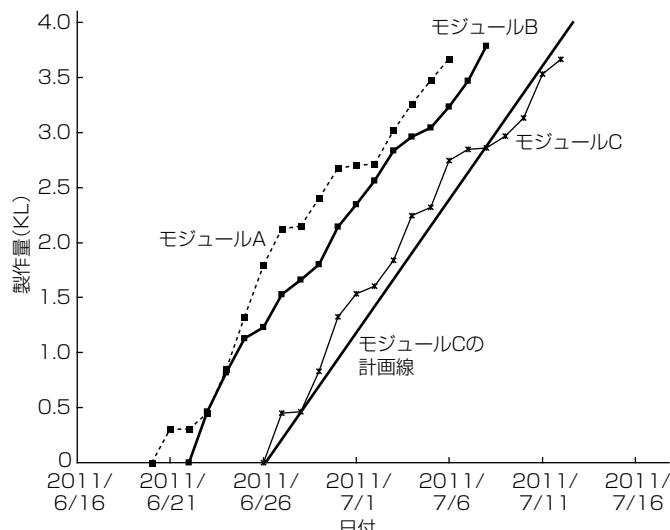

### (3) ソースコード推移

仕様書作成状況と同様に、サーバに格納されたソースコードからそのライン数を自動的にカウントし、ソースコードの作成状況をグラフ化する(図5)。図から、作成開始日から作成完了日までの計画線と比較することで、例えばモジュールCは作成当初は計画を上回る進捗であったが、後半は計画より遅延しており、対策が必要であることが分かる。このようにして、作成遅延が発生しているモジュールの把握が可能となる。

## 3. 定量データに基づく品質確認

このシステムを実開発に適用し、出力される各種グラフを活用して、定量的品質管理を実践した。具体的な取組み

図5. ソースコード推移

を次に示す。

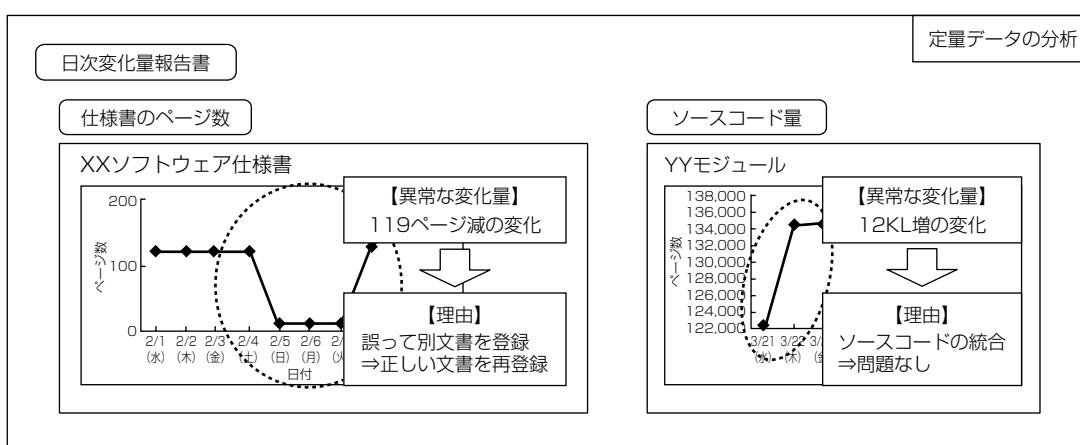

### 3.1 日次変化量による品質確認

"仕様書作成状況" "ソースコード推移" 等を日次変化量報告書としてまとめ、仕様書及びソースコードの日々の変化量を監視した(図6)。仕様書・ソースコードの作成量が急減に変化している場合は、異なる仕様書・ソースコードの誤った登録や仕様書・ソースコードを誤って削除したなどの可能性が考えられる。また、ソースコードの正常な統合によっても異常な変化量を示す場合もあるため、開発担当者に異常な変化量の理由を聞くことで品質上の問題有無を確認した。問題があった場合は原因分析を行い、是正処置を立案・実施することで品質を確保するとともに、誤操作などの再発を防止した。

### 3.2 週次品質レポートによる品質確認

仕様書の章ごとの"レビュー指摘率"や"誤り検出率"、及び"設計品質ゾーン評価"等を基に、週次品質レポートを作成し、品質状況が一目で確認できるようにした(図7)。品質確認の結果、"レビュー密度"が不足している場合は仕様書の追加レビューを実施して設計品質を向上させた。また、"誤り検出率"が目標値を大幅に上回っている場合は誤りが残存している可能性が大きく、誤りの内容確認などの品質再評価を実施して弱点部分を明確にし、追加レビューを実施した。

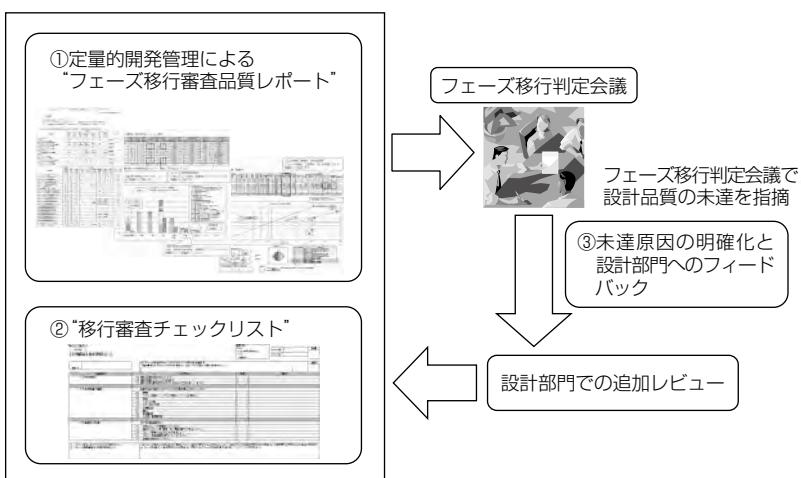

### 3.3 開発フェーズ移行判定会議による品質確認

日次・週次での品質確認に加え、このシステムから出力される各種グラフを基に作成した資料に基づき、マネジメント及び品証部門による開発ホールドポイントでの品質評価を"開発フェーズ移行判定会議"として実施した(図8)。人手で品質に関するレポートを作成していた際には、品質確認のための資料作成に時間がかかり移行判定会議に定量的データが提示できない場合もあった。このシステムはその問題を解決し、品質確認対象の仕様書が多い場合でも定量的品質データの短時間での提供が可能となり、次の項目を実施することで、設計段階での品質を確保することができた。

図6. 日次変化量による品質確認

週次品質レポート

### 章別の“指摘率”“誤り検出率”

## 5章／6章の“指摘率”“誤り検出率”が品質目標未達

## 設計品質ゾーン評価

- ・6章の“レビュー密度”不足

- ・3章の“レビュー密度”は品質目標達成であるが、“誤り検出率”も高い⇒残存誤りあり、再評価が必要

- (1) “フェーズ移行審査品質レポート”による定量的品質評価

- (2) “移行審査チェックリスト”による移行条件の確認

- (3) 品質目標が未達の場合には、その原因を明確化し設計部門へフィードバック

## 4. む す び

“ソフトウェア品質データ収集・分析システム”を開発して実開発に適用したことで、品質管理のための開発者の負荷を最小限に抑え“品質の見える化”を実現した。グラフによる分かりやすい品質データを提供することで弱点部分を短期間で明確化し、設計部門による改善を実施することで、設計段階での品質作りこみを可能とした。

今後は、このシステムの適用を複数のソフトウェア開発に拡大するとともに、設計段階だけでなく、実装・試験段階での品質確認・改善にも適用し、製品品質の向上を図っていく。

参 考 文 献

図8. 開発フェーズ移行判定会議による品質確認

- (1) 山下昭裕, ほか: ソフトウェア開発環境の現状と展望, 三菱電機技報, 84, No.5, 266~270 (2010)

- (2) Redmineホームページ:

<http://redmine.jp/>

- (3) 小川明彦, ほか: Redmineによるタスクマネジメント実践技法, 翔泳社 (2010)

# ハードウェア模擬環境を活用した 開発上流におけるソフトウェア品質向上

金井健太郎\* 日比野楳也\*\*

大河原 繁\* 原川雅哉\*\*

吉村 学\*\* 庄 晓杰\*\*

*Improvement of Software Quality in Upper Process of Development by Using Hardware Simulation*

Kentaro Kanai, Shigeru Okawara, Manabu Yoshimura, Shinya Hibino, Masaya Harakawa, Gyoketsu So

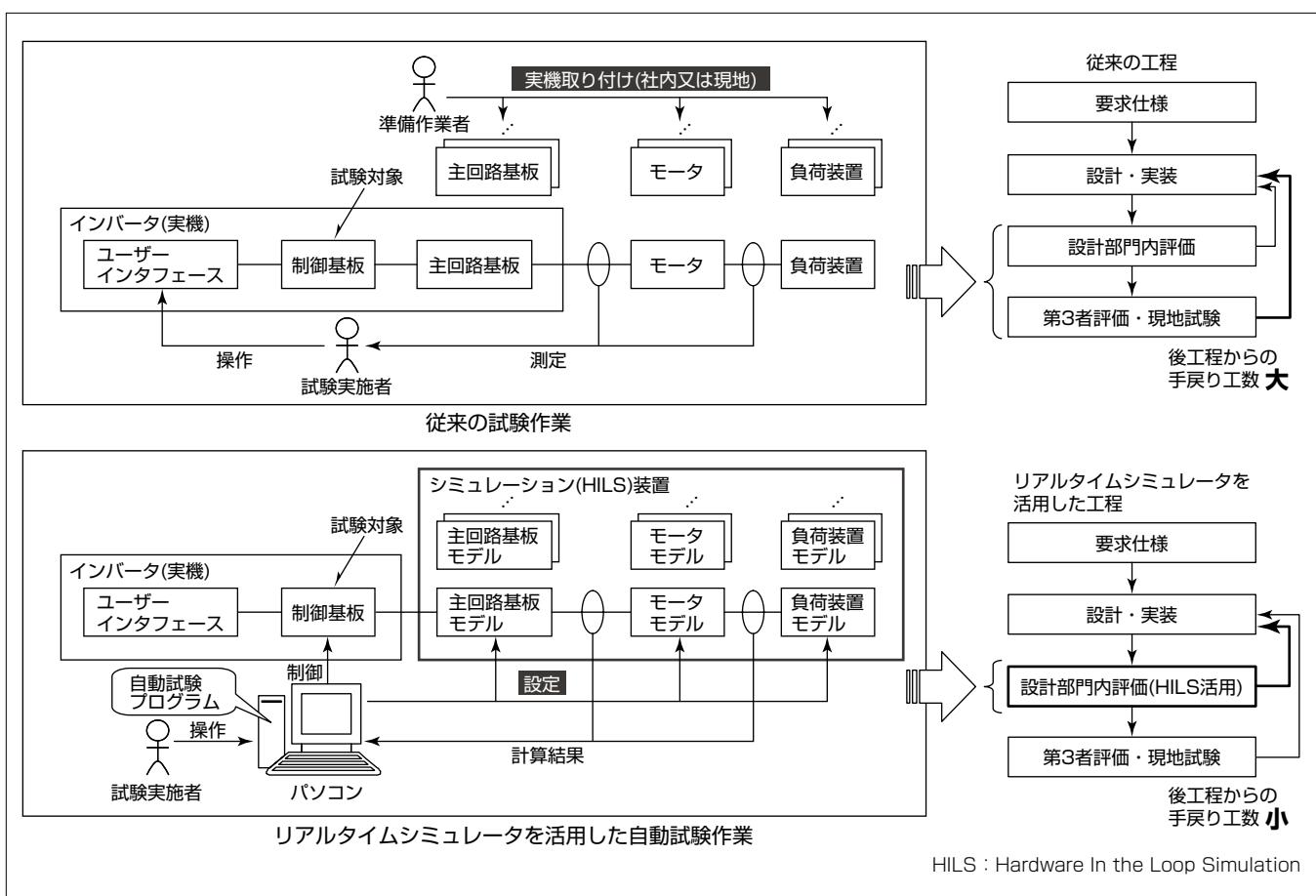

要旨

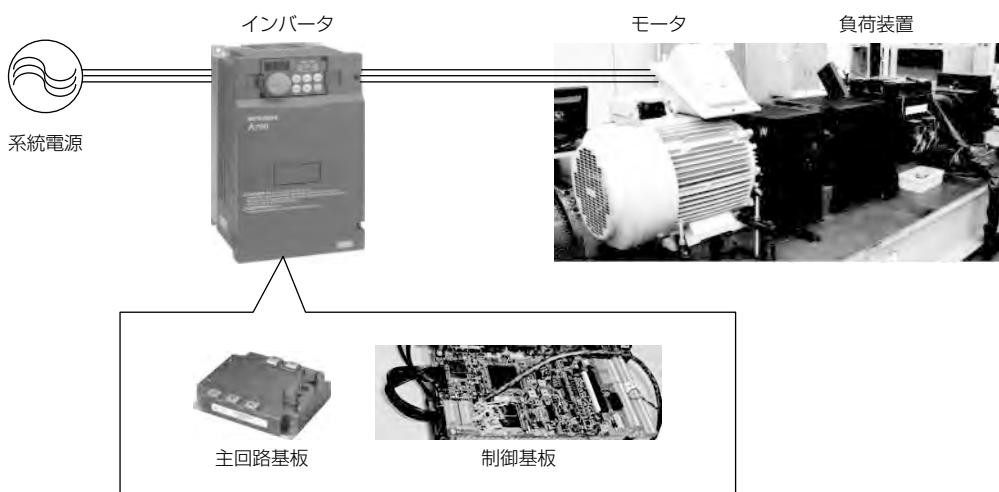

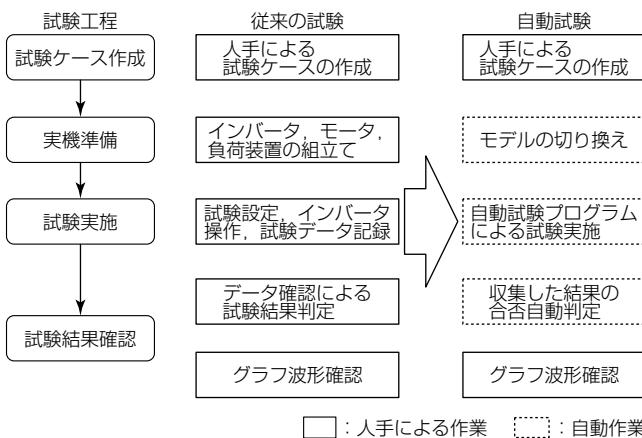

組込みソフトウェアの試験では、実時間で動作する対象物への制御を確認する必要があり、従来実機を用いた試験が主流であった。特に、インバータ制御ソフトウェアの機能評価試験では、汎用インバータの製品ラインアップ充実化によって、出力容量の異なる多数のモータを用意する必要がある。しかし入手や設置が困難なモータの場合、現地で試験せざるを得ず、開発上流の品質確保が課題であった。また、試験環境の準備、実機操作や試験結果の目視確認等、増加傾向の試験工数抑制が課題であった。

本稿では、対象物の実時間動作を模擬するリアルタイムシミュレータを活用し、次の(1), (2)の取組みによって試験

環境準備作業と試験実施作業を効率化したことについて述べる。

- (1) モータ、負荷装置などの制御対象をリアルタイムシミュレータ上でモデル化することで実機準備を不要とし、実機置き換えによって発生する段取り時間を削減した。

- (2) モータやインバータの動作条件設定と試験実行によるインバータ出力結果の合否判定を自動化した。

さらに、実機の入手性によらず、多種多様な実機を想定した試験を前倒して実施可能であるため、開発上流におけるインバータ制御ソフトウェアの品質確保が可能となった。

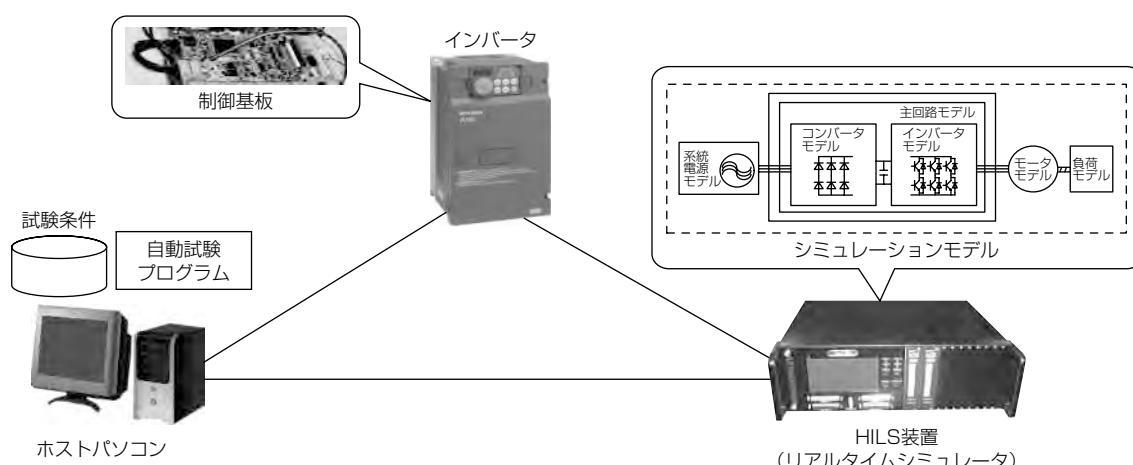

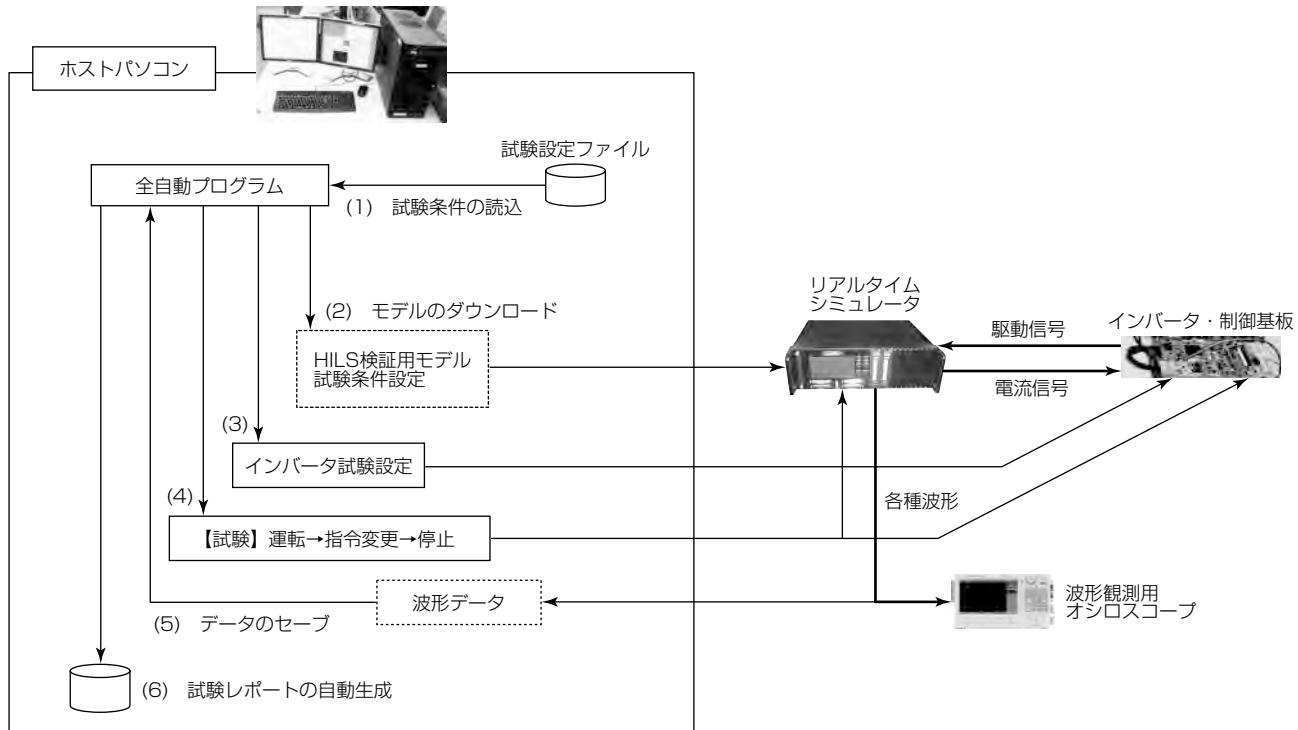

インバータの自動試験環境

従来のインバータ機能試験では、インバータに実機モータと負荷装置を取り付けて試験環境を準備し、試験実施者の手作業で試験を実施していた。今回の取り組みでは、インバータ主回路基板とモータと負荷装置をモデル化することで、リアルタイムシミュレータ上における動作を可能にした。さらに、ホストパソコンからインバータとリアルタイムシミュレータを制御することによって試験を自動的に実行できるようにした。

## 1. まえがき

組込みソフトウェアの試験では、実時間で動作する対象物への制御を確認する必要があり、従来実機を用いた試験が主流であった。特に、インバータ制御ソフトウェアの機能評価試験では、適用業種拡大に伴う汎用インバータの製品ラインアップの充実化(41種類→46種類)によって、出力容量の異なる多数のモータを試験環境として準備する作業に多くの時間を要していた。また、インバータが持つ機能の増加に伴い、インバータ設定など試験条件の手動変更やインバータ出力など試験結果の目視確認といった試験実施工業が増加しており、試験環境準備工数と試験実施工数を合わせた試験工数の抑制が課題であった。

本稿では、モータと負荷装置の特性を実時間で模擬するリアルタイムシミュレータを核とした自動試験環境による、試験環境の準備の容易化、試験条件の変更と試験結果データの合否判定の自動化の取組みについて述べ、開発上流で品質を確保するプロセスへ改善したことを述べる。

## 2. 課題

### 2.1 試験環境準備工数の抑制

従来、インバータ制御ソフトウェアの機能評価試験では、評価試験装置の準備工数の抑制が課題であった。インバータには出力容量の異なる製品バリエーションが存在し、それぞれの出力容量に対して複数種類のモータを駆動することができる。このため、評価試験では数多くの組合せを確認する必要がある。また、様々な出力容量における試験に合わせて、インバータの主回路、インバータが駆動するモータ、及びモータに負荷を与える負荷装置を交換する必要がある。このため評価試験では、モータと負荷装置で構成する試験装置(図1)の準備に多くの手作業を必要とする。これらの要因から試験環境の段取りに多くの工数がかかっており、試験環境準備工数の抑制が課題であった。

### 2.2 試験実施工数の抑制

従来のインバータの機能評価試験では、インバータを操作し、結果を観測・測定する試験実施工業に多くの工数がかかっていた。試験中、試験作業者は、インバータの出力やデジタルオシロ波形表示を確認しながら、インバータの操作をしなければならず、長時間拘束された。また、試験の結果得られたデータを確認して、試験の合否判定を行う工数が多くかかっていた。この試験実施工数の抑制が課題であった。

## 3. 対策

先に述べた2つの課題である試験環境準備工数の抑制と試験実施工数の抑制のための取組みを述べる。

### 3.1 仮想環境導入

ここでは、試験環境準備工数の抑制のための取組みについて述べる。試験環境の中には、インバータの出力容量に依存する部分(図1のインバータ内部の主回路基板、モータ、負荷装置)と依存しない部分(図1のインバータ内部の制御基板)が存在する。このため、インバータとモータと負荷装置をインバータの出力容量ごとに準備する必要がある。そこで、インバータの出力容量によらず共通な制御ソフトウェアを搭載した制御基板は実機を使用し、異なるインバータ主回路・モータ・負荷装置をHILSと呼ばれるシミュレーション技術を用いてモデル化した。このシミュレーションモデルを切り換えることで、インバータの出力容量を切り換えられる仮想的な試験環境を実現した。これにより、試験装置準備工数を抑制した。

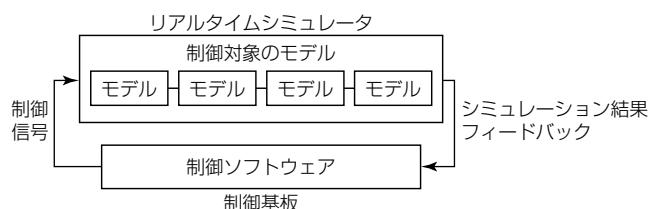

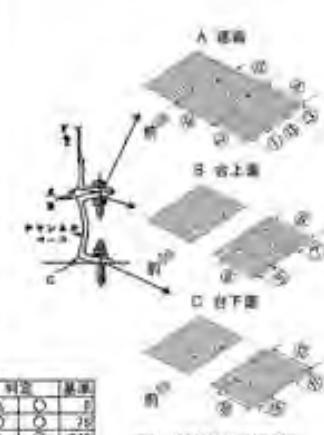

#### 3.1.1 HILS技術

HILSとは、制御対象をリアルタイムシミュレータ上にモデル化し、制御ソフトウェアによって動作させることで試験対象の制御ソフトウェアを検査する技術である(図2)<sup>(1)</sup>。HILSは、実インバータや実モータなどの実機を準備する必要がなく駆動制御系開発には非常に有用な手法である。

図1. 従来の試験装置の構成

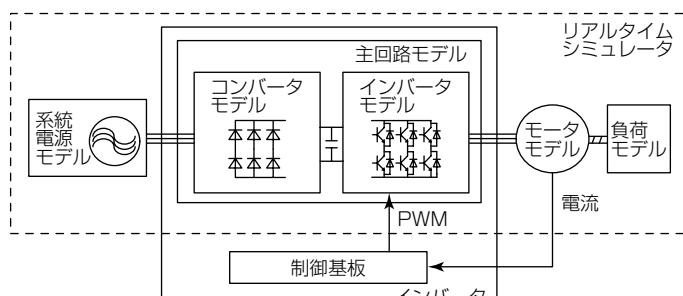

### 3.1.2 HILS用検証モデル

この施策では、インバータ主回路・モータ・負荷装置をモデル化してリアルタイムシミュレータ上に実装し、インバータ制御基板と接続した(図3)<sup>(2)</sup>。インバータ主回路をシミュレーションモデルに組み込むことで、インバータの出力容量によらず共通なインバータ制御基板と出力容量によって異なるインバータ主回路を切り離すことを可能とした。これによって、出力容量の異なるインバータの試験をインバータ主回路モデルの切り換えによって可能とし、段取りを容易にした。

### 3.2 試験の自動化

ここでは、試験実施工数の抑制のための取組みについて述べる。インバータの機能評価試験では、試験実施者がインバータの操作、試験結果の確認のために多くの工数がかかっていた。そこで、3.1.2項のHILS用検証モデルの動作環境であるリアルタイムシミュレータを核とした自動試

図2. HILSの構成

図3. HILS用検証モデル

図4. 自動試験環境の構成

験環境を構築した。自動試験環境の入力として、インバータの設定、負荷条件、試験の出力結果の期待値を記載した試験ケースを複数用意する。自動試験環境は、試験ケースを1ケースずつ読み込んで、ホストパソコンにプログラムした手順に従って、インバータ制御基板を制御し、実行の結果得られたデータを期待値と比較することを連続して実行する。これによって、従来人手で実施していた試験作業を自動化でき、試験実施工数を抑制した。

### 3.2.1 自動試験環境の構成

自動試験環境は、インバータ制御基板、HILS装置、及びホストパソコンで構成する(図4)。

#### (1) インバータ制御基板

インバータ制御基板は、インバータに内蔵されたもので、試験対象であるインバータ制御ソフトウェアを搭載している。インバータ制御基板から、HILS装置にPWM(Pulse Width Modulation)信号を出力してインバータ主回路モデルを通じて、モデル化した仮想モータを回転させる。

#### (2) HILS装置

HILS装置は、3.1.2項のシミュレーションモデルの動作環境であるリアルタイムシミュレータである。

#### (3) ホストパソコン

ホストパソコンには、自動試験のプログラムを格納している。また、ホストパソコンは、試験ケースの入力、試験の期待値を保持する。

ホストパソコンからインバータ制御基板には、試験ケースに入力したインバータの設定値の設定や、運転指令を設定することができる。また、ホストパソコンはインバータ制御基板からインバータが出力している周波数、電流値などの制御数値やインバータのエラー状態を受信して、その結果に基づいてインバータ制御基板を制御する。

ホストパソコンからリアルタイムシミュレータには、試験ケースに記述したインバータ主回路モデルの容量、モータモデルの容量を設定することができる。さらに、モータ

モデルの回転中に負荷を与えることができる。ホストパソコンは、リアルタイムシミュレータからモータモデルの回転数を受信して、その結果に基づいてインバータ制御基板を制御する。

### 3.2.2 自動試験環境の処理フロー

自動試験環境の処理フロー例を図5に示す。自動試験環境を起動すると次の(1)～(6)を自動的に実行する。

- (1) インバータ主回路やモータの容量、電源電圧などの試験環境、インバータの動作を決定するインバータ制御ソフトウェアのパラメータ、及び試験結果の期待値を記載した試験設定ファイルを読み込む。

- (2) (1)で読み込んだ試験設定ファイルに記述している出力容量のモデルをホストパソコンからリアルタイムシミュレータに設定する。また、電源電圧などの試験環境をリアルタイムシミュレータ上のモデルに設定する。

- (3) (1)で読み込んだインバータ制御ソフトウェアのパラメータをインバータに設定する。

- (4) 機能試験の種類に応じて、あらかじめプログラムしてあるインバータの操作手順や負荷モデルの操作手順に従い、ホストパソコンからインバータ制御基板に運転指令を送信する。機能試験の種類ごとの操作手順は、加減速試験と速度－トルク特性試験について述べる。

- (a) 加減速試験

- ① インバータに運転指令を送る。

- ②(3)で設定してある運転周波数に加速するまでインバータの状態をモニタし、運転周波数に達するまでにかかる時間を測定する。

- ③ インバータに停止指令を送る。

- ④ インバータが停止するまでインバータの状態をモニタし、インバータが停止するまでにかかる時間を測定し、1試験ケースを終了する。

- (b) 速度－トルク特性試験

- ① インバータに運転指令を送る。

- ②(3)で設定してある運転周波数に加速するまでインバータの状態をモニタする。

- ③ 定速となったところで、インバータが負荷に耐えられなくなりストール状態(過負荷などによってインバータがモータを正常に回転させることができなくなる状態)となるまで、徐々に負荷モデルの負荷を上げていく。

- ④ ストール状態となったところで、負荷モデルの負荷をリセットし、インバータの制御基板のストール状態を解除して1試験ケースを終了する。

- (5) 1試験ケース終了後、リアルタイムシミュレータ上に記録してあるモータ速度や電流値といったデータをホストパソコンに出力する。

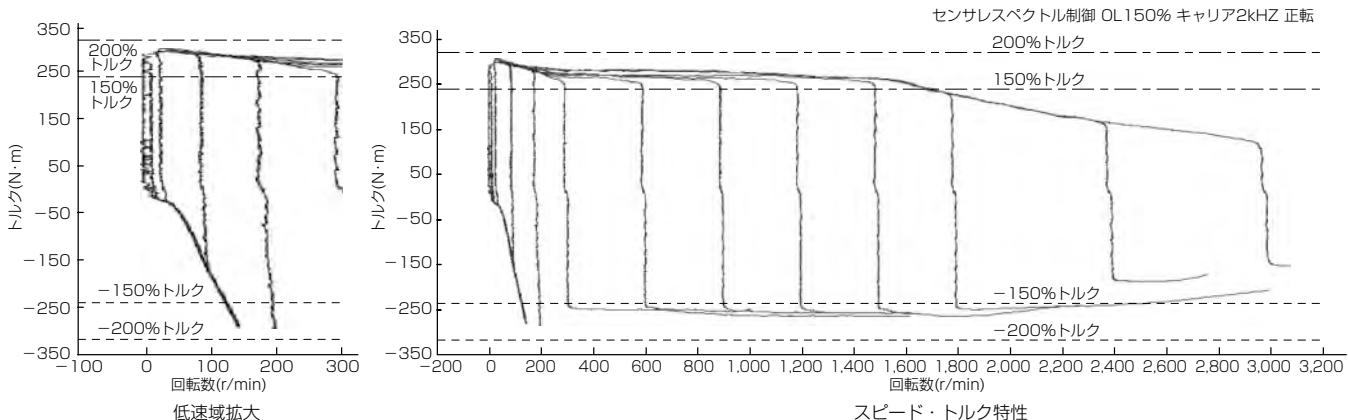

- (6) 試験の測定値や(5)で得たデータのグラフを出力して試験結果のレポートを作成する。図6は、速度－トルク特性試験の結果として得られた、速度と負荷トルクを二次元グラフに出力した試験結果レポートの一例である。開発者がこのレポートを参照し、速度－トルクの特性の合否判定を行う。

図5. 自動試験環境の処理フロー例

|         |           |          |            |                |            |

|---------|-----------|----------|------------|----------------|------------|

| 機台      | FR-A820   | 容量       | 30.0kW     | ソフトウェア         | 8380_v0.37 |

| 使用モータ   | SF-JR-30k | 定格回転速度   | 1,800r/min | 制御方法           | センサレスベクトル  |

| キャリア周波数 | 2.0kHz    | 配線長      | 5m         | オフラインオートチューニング | あり         |

| すべり補正   | なし        | モータ定格トルク | 159.17N·m  | 電源電圧           | 工場電源       |

図6. 速度・トルクの二次元グラフ

図7. 従来の試験との作業の比較

#### 4. 効 果

##### 4.1 自動化による工数抑制

モータやインバータの切り換えをシミュレーションモデルの切り換えによって行えるようになったため、試験の準備工数を抑制可能となった。

また、従来人手で実施していた試験の設定・インバータ操作・試験の結果判定を自動化でき、グラフの取得を自動化した(図7)。その結果、試験実施工数を抑制可能となつた。

##### 4.2 フロントローディング化による開発上流における品質確保

従来は、設計部門内で特殊なモータや超大容量モータの試験環境準備が困難であった。このため、設計部門内で網羅的に試験を実施することが困難であり、結果として後工程からの手戻りが発生していた。

図8. 自動試験環境導入前後のプロセス

HILS装置を活用した試験では、特殊なモータや超大容量モータを仮想的に構築でき、設計部門内における評価が容易となつたため、上流工程における品質確保が可能となつた(図8)。

#### 5. む す び

リアルタイムシミュレータを活用したインバータにおける自動試験環境の取組みについて述べた。この取組みにおける技術は、インバータに限らず他の駆動制御機器にも適用可能である。今後は、他の駆動制御機器に適用していくことによって、ユーザーニーズにマッチした製品を迅速に市場提供していく。

#### 参 考 文 献

- (1) Harakawa, M., et al.: Real-Time Simulation of a Complete PMSM Drive at 10 μs Time Step, IPEC Niigata 2005, S27 (2005)

- (2) 寺田 啓, ほか: 駆動制御機器の連成シミュレーション, 三菱電機技報, 79, No.11, 715~718 (2005)

宗像浩一\*

平井浩司\*\*

安江 悟\*\*\*

# 仕様書間のトレーサビリティ管理技術

*Traceability Management Technique for Specification Documents*

Koichi Munakata, Koji Hirai, Satoru Yasue

## 要 旨

製品のライフサイクルで様々な仕様書が作成される。要求に適合した品質の高い製品を製造するには、これら仕様書間で対応する記載箇所が双方向に追跡可能で、整合性が維持されていることが重要である。仕様書間の追跡可能性をトレーサビリティと呼ぶ。双方向トレーサビリティが近年ISOの機能安全規格などで求められており、トレーサビリティ管理の仕組み構築の必要性が高まっている。

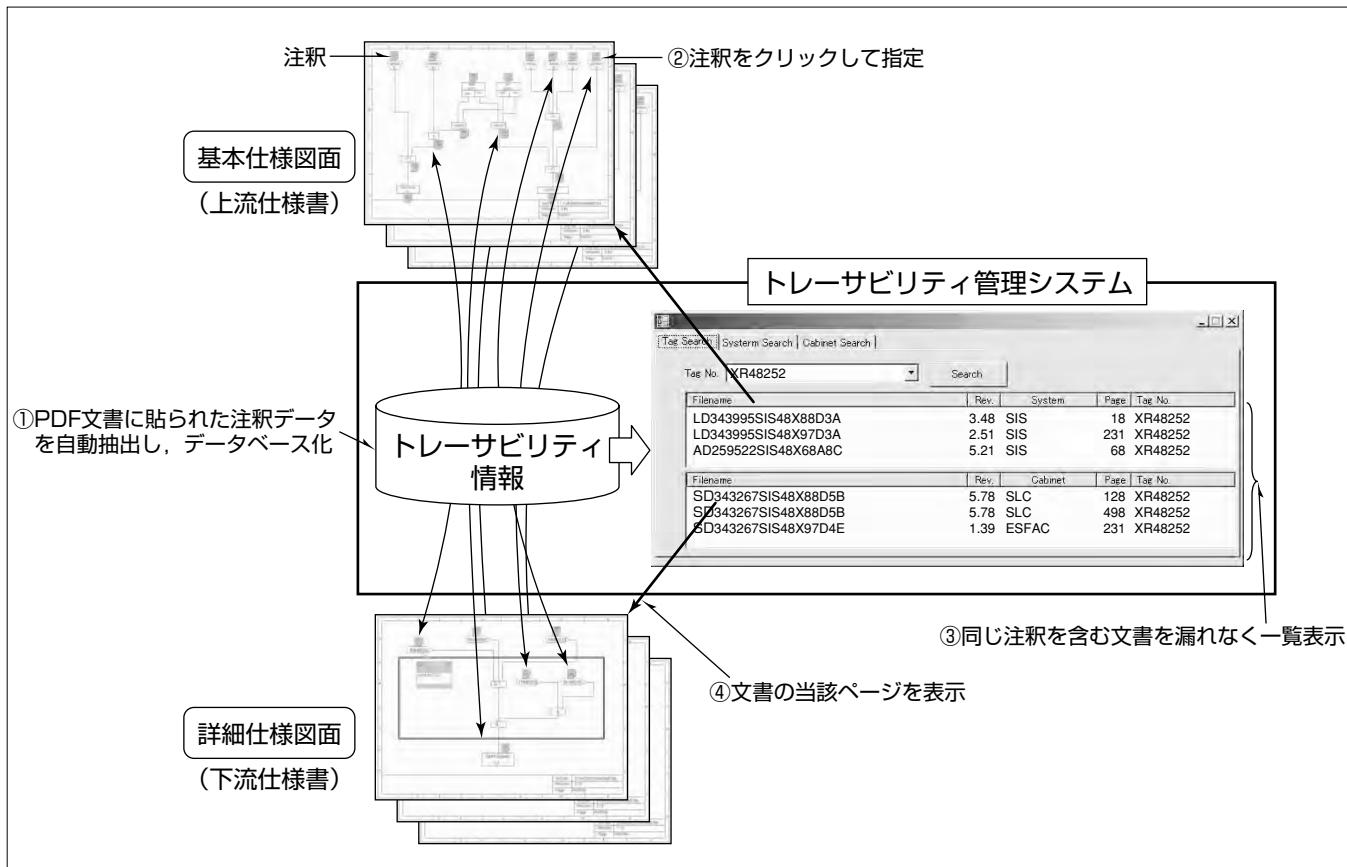

今回ISO32000-1で規定されたPDF(Portable Document Format)形式の仕様書を対象に双方向トレーサビリティを管理する技術を開発した。上流・下流の仕様書間で互いに関連する箇所に、同一の識別子を記載した注釈を貼り、これをトレーサビリティ情報としてデータベース化する。あ

る文書の注釈をマウスでクリックすると、その注釈に記載した識別子を含む文書一覧を即座に表示し、そこから任意の文書を選択することで識別子を含むページを表示する。

これによって仕様書が大量になっても、指定部位に関する箇所を瞬時に網羅的に検索できる。そのため目視確認によって生じる漏れを抑制できる。また仕様変更があった際に影響範囲を容易に特定でき、変更漏れを防止できる。

開発した技術を原子力プラントの図面管理に適用した。PDF形式の基本仕様図面と詳細仕様図面とを結ぶ約8万個の注釈をデータベース化した。これによって設計者以外で実施される、レビュー、試験、保守といった工程でも図面間の対応箇所を容易に検索できるようになった。

## トレーサビリティ管理システム

基本仕様図面と詳細仕様図面はPDF形式であり、仕様書間で対応する箇所の“注釈”(青色で表示)に同一の識別子が埋め込まれている。どちらかの仕様図面の注釈をマウスでクリックすると、トレーサビリティ管理システムに、同じ識別子が埋め込まれた箇所の文書一覧を表示する。一覧から文書を指定すると、識別子を含むページを即座に表示し、対象の注釈をハイライト表示する。

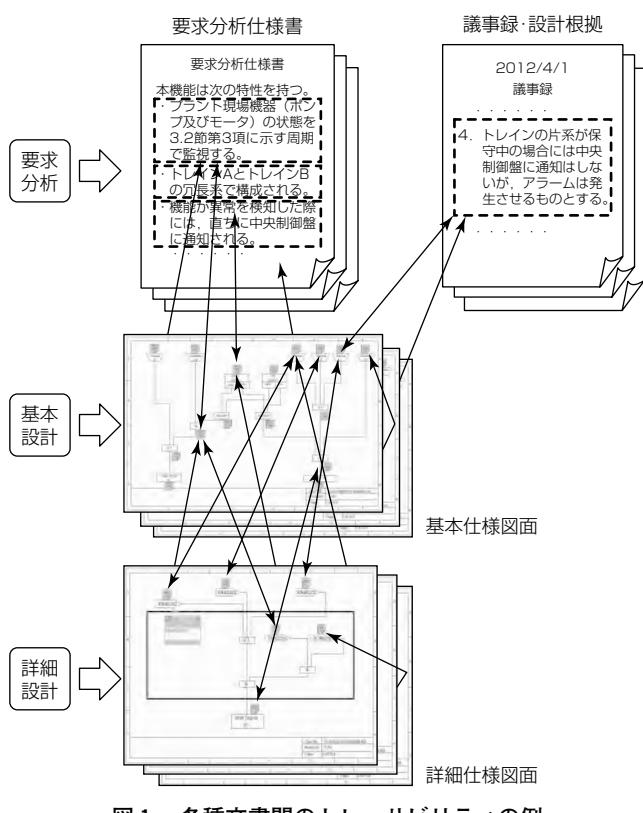

## 1. まえがき

製品の開発・製造は要求分析、設計、製造、試験、保守といったライフサイクルで構成され、各段階で様々な仕様書が作成される。要求に適合した製品を製造するには、これら仕様書間で対応する記載箇所が双方向に追跡可能で、整合性が維持されていることが重要である。図1に示すように、例えば要求分析で特定された機能は、基本設計で基本仕様の複数モジュールによって実現される。更に設計が進んだ詳細設計では、要求機能は詳細仕様のあちこちに分散して実装されることになる。そのような場合に各種仕様書間の対応項目の記載箇所が明確に対応付けられており、仕様書の読者が双方向に行き来して整合性を確認・検証できる必要がある。仕様書に加えて、仕様変更要求を含む議事録などとの整合性も必要となる。このような仕様書間の追跡可能性をトレーサビリティと呼ぶ<sup>(1)</sup>。従来ソフトウェア開発では、要求分析仕様書と設計仕様書との関係をトレーサビリティ・マトリックスを使って管理してきた<sup>(2)</sup>。近年は対象が製品のライフサイクルにわたる仕様書に拡大してきている。特に安全性を重視する自動車分野などでトレーサビリティ確保が必須条件として規定され、ソフトウェアだけでなくハードウェア分野でも注目を集めている。

本稿では複雑化するシステムのトレーサビリティ管理の課題を指摘し、それを解決するための管理技術について述べる。最後に同技術を原子力プラントの図面管理に適用した例について述べる。

図1. 各種文書間のトレーサビリティの例

## 2. トレーサビリティ管理の課題

製品の高機能化に伴い構築するシステムが大規模化すると、仕様書が大量となる。そのため仕様書間の関連が複雑になり、手作業でのトレーサビリティ確保、目視での整合性の確認・検証・維持が困難となる。その結果、整合性が欠如し、成果物が要求仕様と異なる不具合が発生する。

整合性の欠如に起因する不具合を未然に防止して高い品質を確保するため、近年ISO/IEC15504(Automotive SPICE (Software Process Improvement and Capability dEtermination))やISO26262(機能安全規格)で仕様書間の双方向トレーサビリティが要求されるようになった。この要求によってトレーサビリティ管理の仕組み構築のニーズが高まっており、仕様書間のトレーサビリティを管理するツールが市販されるようになった。

一方仕様書は組織によってパソコン上の文書作成用各種アプリケーションやCADなど、様々な形式で作成されている。このためアプリケーションやファイル形式のバージョンの違いによって、組織間で文書を共有できない場合がある。この問題を回避するための共通形式として、文書形式の国際規約であるISO32000-1(PDF1.7)が普及している。ISO32000-1はアドビシステムズ社の製品である文書アプリケーションAdobe Acrobat<sup>(注1)</sup>のファイル形式を2008年に国際規約化したものである。以下この形式を“PDF”という。

しかしPDF仕様書を対象として、任意の箇所間でトレーサビリティを確保し、文書をワンクリックすることで関連文書を表示するといった操作性の高いツールが実用化されていない。このためPDF仕様書で大規模なシステムのトレーサビリティを確保するのが困難である。

(注1) Acrobatは、Adobe Systems Inc. の登録商標である。

## 3. トレーサビリティ管理技術

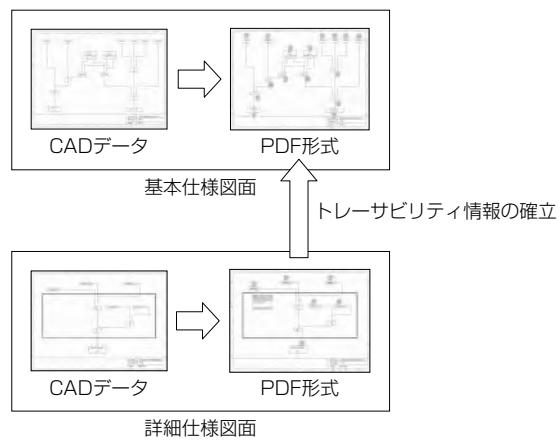

今回PDF仕様書の双方向トレーサビリティを管理する技術を開発した。この技術はソフトウェア、ハードウェアを問わず、様々な仕様書に適用できる。

### 3.1 技術内容

開発した技術を次の順に適用することによって、トレーサビリティ情報を用いて仕様書間の対応箇所を網羅的かつ迅速に検索可能となる。

#### (1) トレーサビリティ情報の収集・貼付

PDFは文書の保存に適するが、データ形式が複雑であり文書作成には適さない。このため通常、文書の作成には各種アプリケーションを利用し、それをPDFに変換する。この技術では各種アプリケーションで作成された仕様書で、トレーサビリティを明確化する最小単位(例えば節、図、表等)ごとに定められた形式の識別子が振られていることを前提とする。

トレーサビリティ情報の収集・貼付では、PDFに変換前の文書から識別子を抽出し、変換後の文書の同じ位置にPDF文書の“注釈”として貼り付ける。図1の基本仕様図面と詳細仕様図面に複数個貼り付けた長方形が注釈である。注釈にはPDF本文とは別に文字列を記載・編集でき、別のファイルやページにコピー・ペーストできる。

#### (2) トレーサビリティ情報のデータベース化

トレーサビリティ情報の収集・貼付で作成されたPDF文書から識別子を記載した注釈を抽出し、そのPDF文書名と、注釈ごとのページ番号及び識別子をデータベースに格納する。

#### (3) トレーサビリティ情報の検索

PDF文書に貼った注釈をマウスでクリックすると、データベースを検索し同じ識別子を持つ注釈一覧を表示する。注釈一覧から任意の注釈を選択すると、その注釈を含むPDF文書が開かれ、注釈を貼ったページを表示する。

データベースに識別子以外の属性情報として文書種別(要求分析、設計等)や対象種別(本文、図、表等)を格納しておくことによって、注釈一覧から所望の情報への絞り込みが可能となる。

### 3.2 技術の適用効果

先に述べたトレーサビリティ管理技術によって、PDF文書に関して次のことが可能となる。

#### (1) 仕様書間整合性の確認

製品のライフサイクルで段階的に作成される上流・下流の仕様書間で双方向に、対応箇所を容易に確認できる。これによって、次のような不具合を防止できる。

- ①仕様の記載漏れ(例えば要求事項が設計仕様書に反映されていない、設計項目の試験が漏れている)

- ②仕様間の不整合(例えば要求事項が正確に設計されていない)

#### (2) 仕様変更時の影響範囲特定

任意の仕様書で仕様変更が発生した場合、それに関連する上流・下流仕様書の箇所を網羅的に検索することができる。これによって、変更漏れによる不具合を防止できる。

## 4. 適用例

トレーサビリティ管理技術を原子力プラント安全系DCS(Digital Control System)の図面管理に適用して、トレーサビリティ管理システムを構築した。

### 4.1 原子力プラント安全系DCSにおける仕様書

今回適用対象とした原子力プラントの主要な仕様書の構成は図1に示すとおり、上流に要求分析仕様書があり、これを受けて下流に基本仕様図面、さらに、詳細仕様図面がある。これ以外にも仕様書があるが、今回は最も複雑で仕様変更が多い基本仕様図面と詳細仕様図面間のトレーサビリティを管理対象とした。図2に示すとおり、基本仕様図

図2. PDF仕様書作成とトレーサビリティ情報確立の手順

面がCADを利用して作成される。それを更に詳細化して詳細仕様図面がやはりCADを利用して作成される。これらの文書はPDFに変換して保管される。

詳細仕様図面で、原子力プラント安全系を作動させるための信号が最も詳細な粒度で記載される。各信号にはシステムで一意の線番が付与されている。また詳細仕様図面の各ページには、どの基本仕様図面を参照しているかが記載されている。そのため、詳細仕様図面から基本仕様図面への片方向トレーサビリティは、ページ単位の粒度で確保されている。しかし詳細仕様図面の作成が完了した段階では、この線番を基本仕様図面に記載することはしていない。そのため、基本仕様図面から詳細仕様図面へのトレーサビリティを明確化するのに多大な工数がかかる。

### 4.2 技術の適用

#### (1) トレーサビリティ情報の収集・貼付

ここでは基本仕様図面と詳細仕様図面間の双方向トレーサビリティを信号の線番の粒度で確保する方法について述べる。トレーサビリティ情報の収集・貼付順序を図2で示す。CADデータをまずPDF形式に変換する。次に詳細仕様図面のCADデータから線番とそのX, Y座標を自動抽出する。そしてCADデータからPDFに変換したファイルに対し、座標変換したうえで注釈として自動的に貼り付ける。

次に詳細仕様図面のPDF注釈の中で基本仕様図面に現れるものを、PDF形式の基本仕様図面の対応する位置にコピー・ペーストする。基本仕様図面に詳細仕様図面と同じ線番が記載されていないため、この作業は図面間の対応箇所を理解した技術者が実施する。

これによって、詳細仕様図面の線番と同じ文字列を持つ注釈が基本仕様図面に貼り付けられ、対応箇所が明確になる。

#### (2) トレーサビリティ情報のデータベース化

基本仕様図面と詳細仕様図面に全ての注釈が貼り付けられると、これらをトレーサビリティ情報として自動的に抽出してデータベースに格納する。データベースには注釈ご

とに、PDF文書名、バージョン、ページ番号、識別子、各種属性を蓄積した。格納した注釈は約8万個である。

### (3) トレーサビリティ情報の検索

PDF文書に貼られた注釈をマウスでクリックすると、トレーサビリティ管理システムがその注釈に記載された識別子(例えば“XR48252”といった線番)を取得する。その文字列が図3のトレーサビリティ管理システムの表示画面の左上に自動的に入力される。その下には同じ識別子を持つ基本仕様図面の注釈一覧、更に下には詳細仕様図面の注釈一覧が表示される。一覧の項目は、左からPDF文書名、バージョン、属性、ページ番号、識別子である。

仕様書の注釈一覧から所望の項目をクリックすると、瞬時に指定された仕様書のページが開き、一覧表にある識別子を含む注釈がハイライト表示される。

これらの人手以外に、識別子の文字列又はその部分文字列を図3の左上のテキストボックスに手動入力しても、それを含む識別子を持つ仕様書の注釈一覧を検索して表示される。

### 4.3 システム導入効果

基本仕様図面と詳細仕様図面の間で対応箇所を示す注釈の数は先に述べたとおり約8万個にのぼる。そのため、対応箇所の整合性を目視で確認・検証・維持するには膨大な工数がかかる。トレーサビリティ管理システムを導入することで、指定した識別子を含む全ての仕様書一覧が図3の画面に瞬時に表示されるため、漏れなく関係する仕様書を確認することができるようになった。

また基本仕様図面と詳細仕様図面の間の対応付けは、これらを設計した技術者自身にとっては時間がかかるても困難な作業ではない。しかしこれらの仕様書は下流工程のレビュー、試験、保守といった工程で参照される。その際に設計者以外が対応付けするのは困難な作業である。その場合にこのシステムを利用することによって、即座に対応付けが可能となり、思い違いに起因する不具合が減少する。

### 4.4 今後の課題

詳細仕様図面に対し、CADデータの識別子貼り付けを自動化することによって高速処理できた。しかし詳細仕様図面から基本仕様図面へのトレーサビリティ確保には手作

図3. トレーサビリティ管理システムの表示画面

業で注釈をコピー・ペーストしたために手間がかかった。

今後は設計を段階的に詳細化する際に、対応する箇所を自動的に関係付けすることによって、トレーサビリティ情報対応付けの手間を削減することが課題である。

## 5. む す び

システムの大規模化に伴って仕様書が増加し、トレーサビリティが複雑化している。そこでトレーサビリティを確保して仕様書間の整合性を確保するために開発したトレーサビリティ管理技術について述べた。

次にこの技術を原子力プラントの図面管理に適用した事例について述べた。現在、試運用の評価を踏まえ課題を整理したところである。今後、本格適用に向けて課題を解決し適用拡大を図っていく。

今後とも、システムの大規模化及び安全性要求の高度化に伴い、要求分析から保守にいたる各種仕様書のトレーサビリティ確保はますます重要となってくる。トレーサビリティ管理技術を更に進化させ、製品の品質向上に貢献していく。

## 参 考 文 献

- (1) Jürgen Börstler, et al.: Traceability Between Requirements and Design: A Transformational Approach, Computer Software and Applications Conference, 1992. COMPSAC '92. Proceedings., 362 ~368 (1992)

- (2) 清水吉男：「派生開発」を成功させるプロセス改善の技術と極意、技術評論社（2007）

# 大規模LSIの機能可視化手法

Visualization Technique in LSI Specification

Keita Yamaguchi, Hiroyuki Yamamoto, Takashi Kusuhara, Hitoshi Ishida

山口啓太\* 石田仁志\*\*

山元浩幸\*

楠原崇史\*

## 要旨

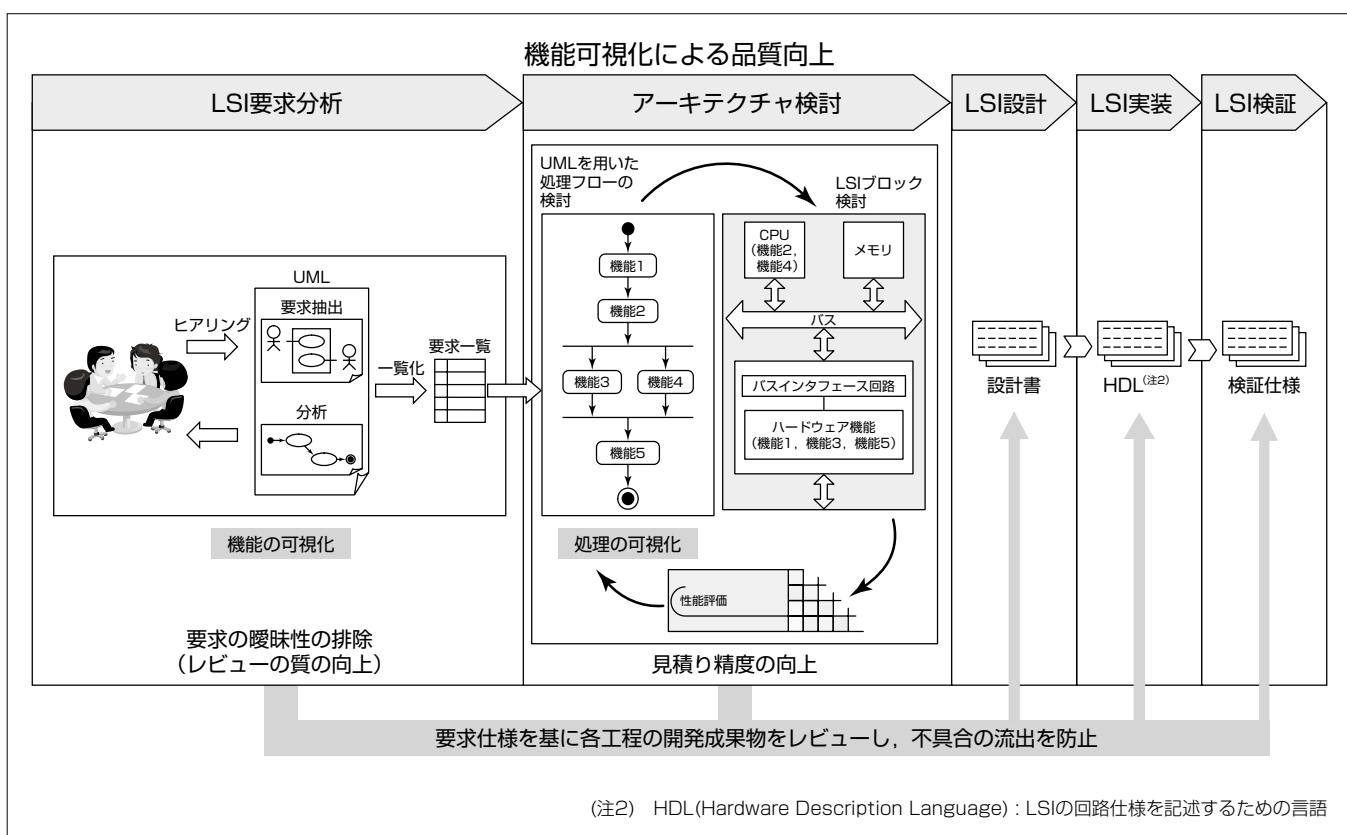

デジタル機器製品の中核機能の多くを支えるLSI(Large Scale Integration)は、半導体の微細加工技術の進歩に伴い、大規模化・高性能化が著しい。これに伴い、多くの機能がLSIに実装されることでLSIの開発難易度は高くなり、仕様や性能などの見積り誤りに起因する問題が顕在化し、後工程に不具合が流出するリスクが増加している。

そこで、仕様や見積り誤りに起因する不具合による設計手戻りや作り直しを防止する活動を行っている。具体的には、ソフトウェア開発で用いられている“仕様を図式表現で定義可能なUML<sup>(注1)</sup> (Unified Modeling Language:統一モデリング言語)”をLSIの要求分析とアーキテクチャ検討に活用し、仕様を可視化する。

### (1) LSI要求分析

UMLを用いて要求分析を実施し、要求を一覧にまとめ

る。図で仕様を明示することで、レビューの質を向上させ、要求の曖昧性をなくし、仕様に起因する不具合を防止する。

### (2) アーキテクチャ検討

アーキテクチャ検討の段階で、回路規模・性能の見積り誤りによって不具合が入る可能性が高い。そこで、UMLを活用して処理フローを可視化し、見積りの精度を高める。

UMLは後工程で作成するLSI設計、実装、検証のドキュメントのレビューにも使用し、各工程のレビューの質を向上させる。

これらの取組みによって、UMLを活用した仕様検討が仕様や見積り誤りに起因する不具合を防止することが可能である。

(注1) UMLは、Object Management Group Inc.の登録商標である。

## UMLを用いた大規模LSIの開発

LSI要求分析で、機能要件の抽出にUMLと要求一覧を活用する。UMLで機能と処理を見る化し、レビューの質を向上させて、仕様不具合を防止する。性能要件の分析で、LSIのアーキテクチャの検討にUMLを活用し、UMLで検討した処理フローを基にアーキテクチャを考案し、見積り精度を上げる。要求仕様を基に、開発後工程の開発成果物を品質確認し、不具合の流出を防止する。

## 1. まえがき

大規模・高性能・高機能のLSIの開発難易度は高くなり、要求仕様の曖昧性による不具合や性能などの見積り誤りに起因する問題が顕在化している。そのため、後工程に不具合が流出するリスクが増加している。

三菱電機設計システム技術センターでは、その根本原因である仕様の品質を向上させるために、ソフトウェア開発で利用されている“仕様を図式表現で定義可能なUML”をLSI設計に活用し、LSI仕様策定フェーズから徹底的な品質の作りこみを行う設計フロントローディングを推進している<sup>(1)</sup>。

本稿では、通信ネットワーク装置のようにLSIとソフトウェアが密に連携するシステムで、UMLを活用して、仕様の品質を向上させる手法について述べる。

## 2. LSI仕様策定フェーズにおける課題

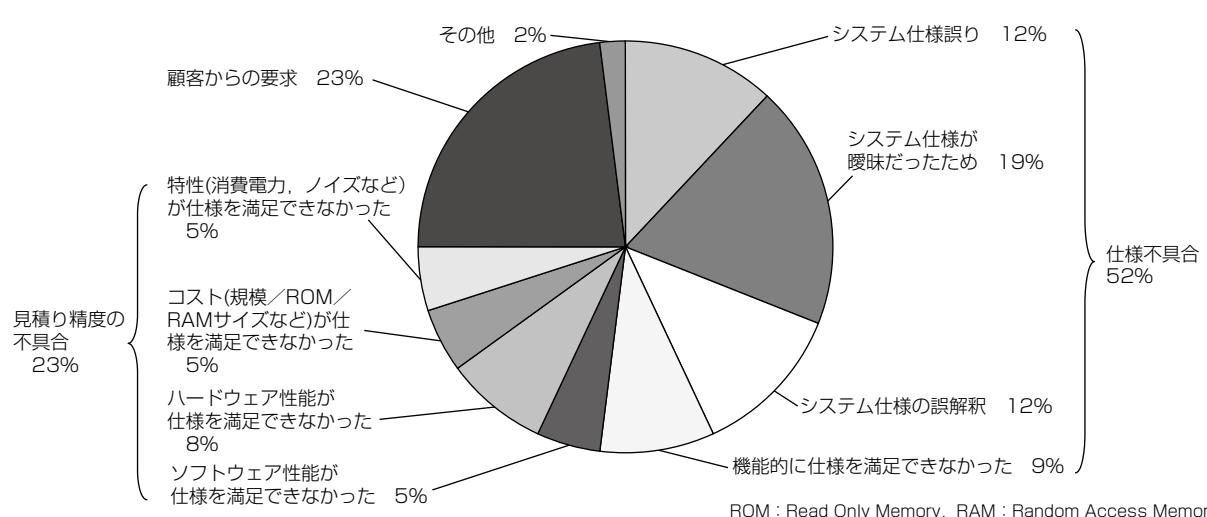

当センターでは、定量的開発プロセスの管理<sup>(2)</sup>によって、開発後工程に設計不具合の流出を防止する活動を行っている。設計不具合流出の原因としては、図1に示すように、仕様や性能に起因する不具合が過半数を占めている。

この主な原因は、2つある。

### (1) 仕様の不具合に起因するケース

LSIの機能や性能を定義する仕様は、自然言語(日本語や英語)ベースの仕様書で記載されるのが一般的である。しかし、自然言語による記述は仕様の曖昧性や、機能の相互関係を厳密に表現できないために機能間の不整合が生じる問題がある。

### (2) 見積り精度に起因するケース

要求仕様を実装設計に落とし込む時の検討が不十分なために、性能などの見積りの精度が悪く、所望の性能を達成できない。

したがって、要求仕様の曖昧性をなくし、仕様見積り誤りに起因する不具合を防止することがLSI開発の課題である。

## 3. LSI設計へのUMLの適用

ソフトウェア開発では、ISO/IEC19501:2005規格とOMG(Object Management Group)で標準化されているUMLで仕様を図式表現することによって仕様を見える化し、レビュー性を向上させている。

LSIの開発でも、LSI仕様策定フェーズで仕様や見積り誤り起因の不具合を防止するために、図2に示すように、UMLを要求分析とアーキテクチャ検討に活用し、要求仕様の完成度と回路規模・性能の見積り精度の向上を図っている。

要求分析にUMLを用い、要件管理のために要求事項を整理した要求一覧を作成し、レビューの質を向上させることによって、要求の抽出漏れを防止する。LSI要求分析における仕様不具合への取組みについては、4章で述べる。

図2. UMLを活用したLSIの開発

図1. システム仕様変更原因<sup>(3)</sup>

また、アーキテクチャの検討に、UML図と性能などの項目を記載した見積表を作成し、見積りに基づいたソフトウェアとハードウェアの構成を検討して、見積り誤りに起因する回路肥大化や性能不足の不具合を防止する。見積り誤りに起因する不具合に対する取組みについては、5章で述べる。

なお、開発後工程の成果物である設計書、HDL(Hardware Description Language)、検証仕様書のレビューで、要求分析の開発成果物である要求仕様(UML図、要求一覧、各種見積り)が期待通りに作成されていることを確認することによって、設計と検証の品質を向上させ、不具合の流出を防止する。

#### 4. LSI要求分析

要求抽出の善し悪(あ)しによって、仕様に起因する不具合が発生するか否かが決まると言っても過言ではない。

要求仕様の品質を向上させるために、要求仕様に次に示す事項を盛り込むことを必須条件とする。

- (1) 要求事項を全て網羅していること

- (2) 何通りにも解釈できる書き方をしないこと

- (3) 簡潔に書かれていること

- (4) 要求事項間で矛盾がないこと

- (5) 制約条件(開発費用、開発期間)のもとで実現性のある要求であること

- (6) 要求を検証可能であること

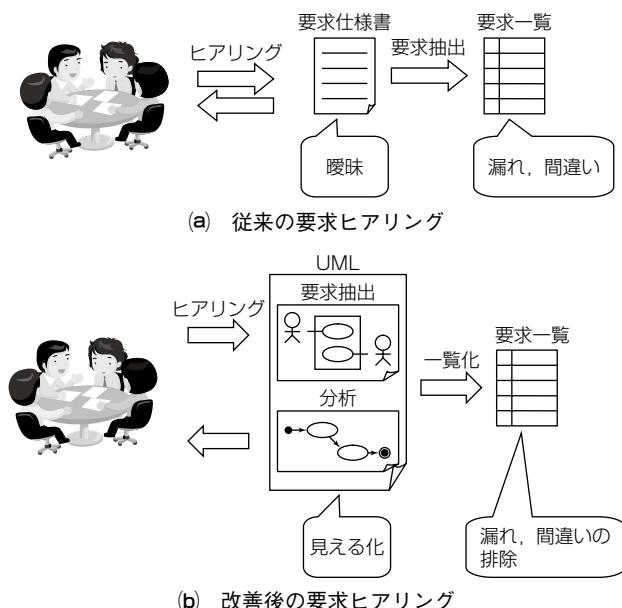

図3に示すように、要求分析で作成する要求仕様書は自然言語の文章などで記述することが一般的である。そのため、要求を何通りにも解釈することができ、要求間の矛盾や過不足に気づきにくく、曖昧性の残った要求仕様となる可能性がある。

図3. 要求ヒアリングと要求分析

それに対し、UMLで規定される表記法で要求を記述することで曖昧性を排除できる。また、図的表現で要求の相互関係を分析・把握することが可能になり、機能要件や性能要件を過不足なく抽出できる。

UMLは、ソフトウェア設計の現場に浸透しており、LSI設計者とソフトウェア設計者とのコミュニケーションが円滑にできるというメリットもある。このため、LSIの要求仕様をソフトウェア設計者でレビューすることが容易でLSI設計者だけで気づかない問題を発見することができる。

UMLで検討した要求は一覧表にまとめ、仕様設計から検証にいたる各工程の成果物が要求に合致しているか確認するために活用する。

#### 5. アーキテクチャ検討

##### 5.1 回路規模と性能

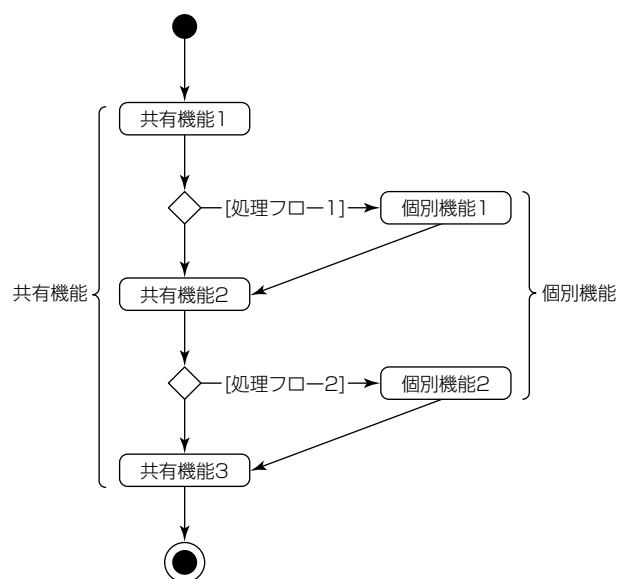

要求分析に基づき、回路規模と性能に対する要求を満たすように、LSIのアーキテクチャ検討を行う。このアーキテクチャ検討の段階では、回路規模や性能の見積り誤りが混入する可能性が高い。そこで、UMLを活用して処理フローを可視化し、見積りの精度を上げる。

##### 5.2 アーキテクチャ検討例

UMLを活用したアーキテクチャ検討例として、機能の共有化による回路規模削減の検討例と、従来LSIのハードウェアだけで制御していた機能をソフトウェアによって代替する検討例を示す。

##### (1) 機能の共有化による回路規模の削減

要求分析に基づき、要求を実現する機能を抽出し、UMLを活用して、処理フローを分析する。図4は、共通の機能を共有する複数の処理フローを1つの処理フローで表記した例である。複数の処理フローで共有する機能から、処理フローごとの個別機能に分岐するポイントを、UML図を

図4. 機能の共有化

図 5. ハードウェア機能のソフトウェアへの代替

を利用して分析することで処理フローごとの個別機能を削減し、回路規模を抑制する。

#### (2) ハードウェア機能のソフトウェアへの代替

CPUの高性能化に伴い、従来ハードウェアで実現していた機能をソフトウェアに置き換えることが可能になってきた。

ハードウェア機能をソフトウェアへ代替する例を図5に示す。この例では、ソフトウェアを処理するCPU、演算処理データや通信データを保持するメモリ、CPUとハードウェアのインターフェースを接続するバス、及びCPUインターフェース回路を持つハードウェアで構成されるアーキテクチャで検討する。

UMLを活用して分析した処理フローの機能に対し、ソフトウェアとハードウェアで実現する機能の複数の組合せを検討し、各組合せの処理性能の見積りを行う。機能をソフトウェアに振り分けることによって、ハードウェアの回路規模は小さくなるため、回路規模の削減目標が決まっている場合には、回路規模も評価の項目として加える。性能低下の一番の要因は、バスインターフェースとメモリインターフェースの遅延であり、バス幅、バスプロトコル、及びメモリアクセス方法による性能の違いを評価項目として挙げ、

図 6. 不具合検出傾向の変化

複数のアーキテクチャを比較検討する。

この性能評価の結果から、性能、回路規模を満たさない場合は、処理フローの再検討やソフトウェアへ代替する機能の再検討を行う。ソフトウェアとハードウェアとを同じ環境でシミュレーションし、性能評価の精度を上げることに加えて、アーキテクチャの検討時点で様々なアーキテクチャで性能を評価することによって、性能品質をより向上させることができる。

## 6. む す び

ソフトウェア開発で利用されているUMLをLSI開発へ適用することで、開発の初期段階で仕様に関する不具合の検出が可能になる。これによって、図6に示すように上流設計での仕様品質や性能品質が向上し、設計下流工程への不具合流出を防止できる。そして、設計手戻り削減と作り直しの抑止につながる。今後は性能見積りの容易化や機能分割方法の指針を整理することが必要である。

## 参 考 文 献

- (1) 竹垣盛一, ほか: フロントローディング型開発設計への取り組み, 三菱電機技報, 80, No.10, 636~638 (2006)

- (2) 吉茂田典夫, ほか: FPGAの定量的開発プロセス管理手法, 三菱電機技報, 87, No. 4, 232~235 (2013)

- (3) JEITA EDA技術専門委員会 SLD研究会: ニーズ/シーズ調査に基づくシステム設計手法の提案とシステム技術言語の適用化検討, 第4回 システムLSI琵琶湖ワークショップ発表資料 (2000)

[http://www.jeita-edatc.com/old/project/sld/public-j2000/bws\\_slides\\_final.pdf](http://www.jeita-edatc.com/old/project/sld/public-j2000/bws_slides_final.pdf)

古茂田典夫\*

城崎雅美\*\*

星直之\*

# FPGAの定量的開発プロセス管理手法

*Quantitative Process Management Method of FPGA Development*

Norio Komoda, Masami Shiroasaki, Naoyuki Hoshi

## 要旨

FPGA(Field Programmable Gate Array)開発における回路設計は、言語ベース設計が主流である。半導体の微細加工技術の進歩とデジタル製品機能の複雑化から、設計回路規模は指数関数的に増大し、言語記述のライン数も数十万行に膨れ上がっている。これに伴い、設計検証品質や開発期間を確保するための開発プロセス管理が不十分で、不具合流出や工程遅延の問題が顕在化しつつある。そこで、言語ベース設計の点で類似しているソフトウェア開発で体系化されている管理手法に着目した。

ソフトウェア開発では定量的開発プロセス管理(以下“定量的開発管理”という。)手法によって品質や工程の測定が行われており<sup>(1)(2)</sup>、その手法を通信機器用FPGA開発へ適用した。その結果、進捗の量化による工程遅延発生時

の早期対策が可能となり、システム試験への流出不具合数は品種あたり半減以下となった。また、実際の工数に対する設計初期段階での見積り誤差も半減した。

こうした成果によって、開発全体の品質を示すフロントローディング率<sup>(注1)</sup>は75%から88%に向上了。このことは、不具合の早期検出率が高まり、手戻りが削減されたことによって、早期の品質改善につながったことを意味する。なお、今回のFPGAの定量的開発管理手法はASIC(Application Specific Integrated Circuits)開発でも同様の効果を得ている。

(注1) フロントローディング率：回路設計完了までの検出不具合数÷総不具合数。この数値が高いほど検証工程以降の流出不具合数が低く、設計品質が高いことを示す。

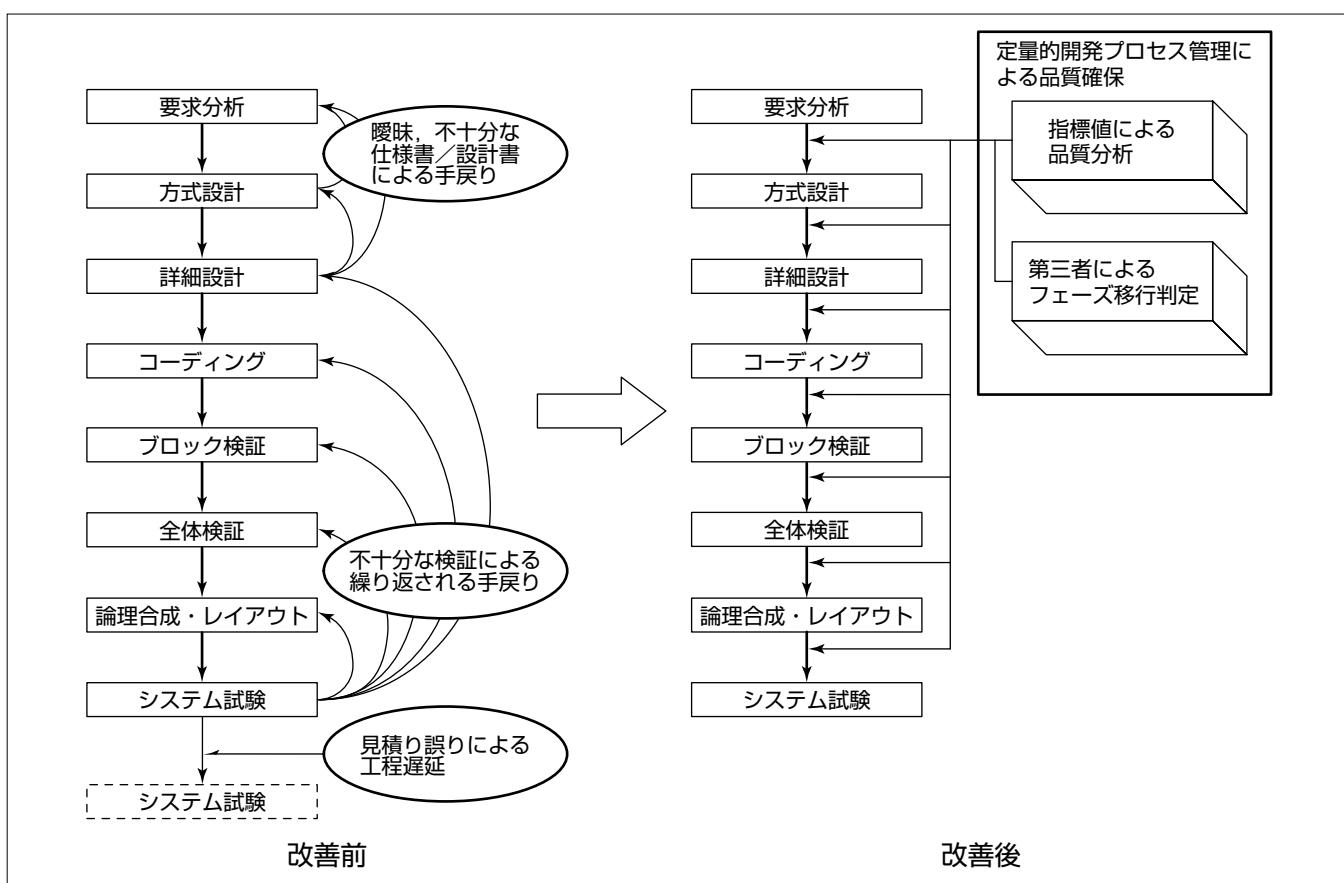

## 定量的開発プロセス管理による品質確保

従来は、品質が不十分なまま次の開発プロセスに移行する場合があったため、品質確保できず手戻りが発生していた。定量的開発プロセス管理を導入することで、指標値から品質を確認し、不十分な場合は現行の開発プロセスで改善してから次の開発プロセスに移行することで、品質確保と工程遵守が可能となった。

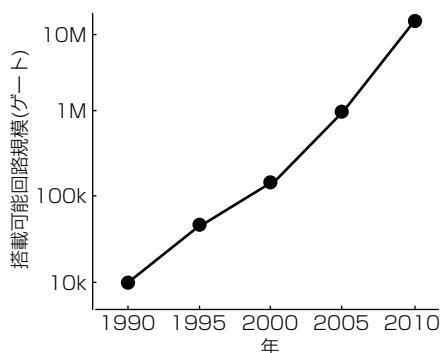

## 1. まえがき

1990年代半ばから、ASICやFPGA開発で、言語ベースの回路設計手法が急速に普及した。この設計手法は、HDL(Hardware Description Language)と呼ばれる言語で記述されるため、設計の容易性、半導体ベンダーに依存しないメリットがあり、設計生産性の向上に大きく寄与した。また、半導体の微細加工技術の進歩とデジタル製品機能の複雑化から、図1に示すように、設計回路規模は指数関数的に増大し、現在では、設計回路規模で数千万ゲート、HDLのライン数で数十万行となる開発も珍しくない。このような設計回路規模の増大に伴い、各開発プロセスで行うべき作業や品質作りこみの実施漏れを見逃したり、分業化された作業分担の割当てや作業間の連携ができないまま作業を進めてしまうことがある。その結果、工程の計画値と実績値との乖離(かいり)や特定回路ブロックの設計品質悪化を見逃し、工程遅延を招くという問題が発生している。同様の問題はソフトウェア開発では既に顕著に現れており、その対策法として定量的開発管理がある。

本稿では、通信機器用FPGA開発に対する定量的開発管理の適用と、その効果について述べる。

## 2. 定量的開発管理の狙いとV字モデル

大規模化したソフトウェア開発では、検証工程で全ての項目を検証し妥当性を確認することは現実的に不可能である。この前提に立ち、検証工程以前の早い工程で品質を管理し作りこんでいくことがソフトウェアの定量的開発管理の目的である。FPGA開発でも言語ベース設計という点で類似しているため、ソフトウェア開発における対策法を応用できると考えられる。

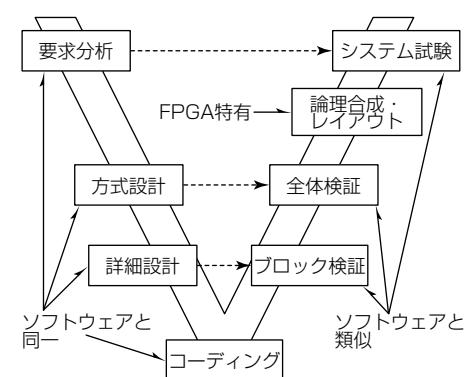

対策を検討するにあたり、V字モデルを活用する。V字モデルとは、開発工程を設計、検証工程に分け、詳細レベルを同じ高さにしてV字型に記載した開発モデルである。V字モデルを見れば、開発工程の各フェーズで何を設計し、その成果物に対して何を検証すれば良いかがわかり、そこ

図1. 半導体プロセス進化に伴う

FPGA搭載可能回路規模

図2. ソフトウェア開発におけるV字モデル

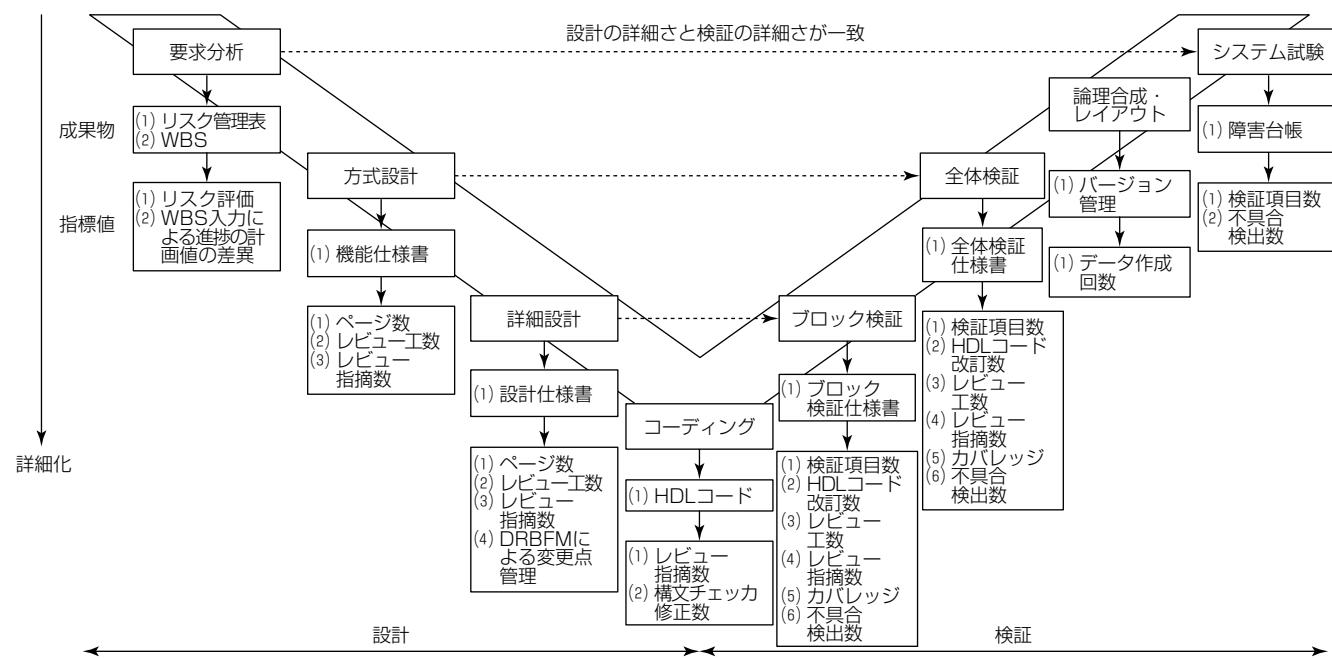

から成果物、管理すべき指標値を抽出できる。図2は、ソフトウェア開発工程を規定したものです、V字の左側がシステムの仕様を詳細化していく工程、右側が詳細な検証からシステム検証に向かってシステムを構築していく工程である。左右の工程は関連付けられており、開発の詳細さのレベルを合わせている。このモデルと同様の考え方で、FPGA開発の差異を考慮しながら作成したV字モデルを図3に示す。設計プロセスについては、ソフトウェアと同じ開発プロセスとなった。検証プロセスについては、FPGA開発の場合、ブロック検証→全体検証の順となる。これは、ソフトウェア開発の単体テスト→結合テストに類似しているため、そのまま置き換えた。FPGA開発特有の開発プロセスである論理合成・レイアウトについては、対応するプロセスがないため、独立した開発プロセスとして追加した。完成したV字モデルから各開発プロセスの成果物を定義し、各成果物に対して表1のような指標値を定量管理すべき値として抽出した。

V字モデルと各プロセスにおける成果物、指標値の関係をまとめたものを図4に示す。各開発プロセスでは第三者者が指標値を分析し、その結果を踏まえて次の開発プロセスに移行してよいかの判断材料とした。

## 3. FPGA開発における定量的開発管理手法

### 3.1 要求分析段階での定量的開発管理手法

大規模FPGA開発では、工程計画を精度よく見積もり、遅延が発生した場合でも早期に挽回(ばんかい)する必要がある。そのためには、FPGA開発における作業を細分化し、細分化された各作業に対してリスクを評価し、作業の進捗状況を量化する必要がある。そこで、次の施策を行った。

- (1) 品質計画書によるリスク評価と事前対策

- (2) 最小作業単位のWBS(Work Breakdown Structure)

入力による進捗量化と工程遅れの早期対策

品質計画書とは、開発開始前に、開発対象のFPGAに関して、どのような設計手法、検証手法、指標を用いて品質確保するかを示した文書である。今回、新たに開発に対す

図3. FPGA開発におけるV字モデル

るリスク評価を行う項目を設けた。これによって懸念点を事前に洗い出した上で、そのリスク対策を検討し、開発中にフォローすることでリスクを最小限に抑えることが可能となった。

工程管理は進捗状況をWBSに入力し管理する。この作業単位を一週間以上にすると、進捗遅れの早期把握が困難

になる。そこで、最小作業単位を5日以内とし、週単位の進捗定量化を行った(図5)。これによって、週単位での進捗遅れの把握ができ、遅れが発生した場合の早期対策が可能となった。これらの対策によって、計画値と実績値の誤差が50%削減され、工数見積り誤りによる開発遅延防止が可能となった。

### 3.2 設計段階での定量的開発管理手法

V字モデルの左側に位置する設計の詳細化では、次の2種類の管理手法を用いた。

- (1) 設計レビュー工数密度と指摘密度を用いたゾーン分析による品質管理

- (2) DRBFM(Design Review Based on Failure Modes)による変更影響範囲の管理

設計レビュー工数密度と指摘密度を用いたゾーン分析による品質管理は、設計レビュー工数密度(レビュー工数/ページ)を横軸に、指摘密度(指摘件数/ページ)を縦軸にとり、実績値をグラフ上にプロットして、設計品質を定量化する。

表1. 定量管理すべき指標値

| フェーズ       | 指標値                | ソフトウェアとの類似性 |

|------------|--------------------|-------------|

| 要求分析       | リスク評価              | ×           |

|            | 工程表入力による進捗の計画値との差異 | ×           |

| 方式設計       | ページ数               | ○           |

|            | レビュー工数             | ○           |

|            | レビュー指摘数            | ○           |

| 詳細設計       | ページ数               | ○           |

|            | レビュー工数             | ○           |

|            | レビュー指摘数            | ○           |

|            | DRBFMによる変更点管理      | ×           |

| コーディング     | レビュー指摘数            | ○           |

|            | 構文チェック修正数          | ×           |

| プロック検証     | 検証項目数              | ○           |

|            | HDLコード改訂数          | ×           |

|            | レビュー工数             | ○           |

|            | レビュー指摘数            | ○           |

|            | カバレッジ              | ○           |

| 全体検証       | 不具合検出数             | ○           |

|            | 検証項目数              | ○           |

|            | HDLコード改訂数          | ×           |

|            | レビュー工数             | ○           |

|            | レビュー指摘数            | ○           |

| 論理合成・レイアウト | カバレッジ              | ○           |

|            | 不具合検出数             | ○           |

|            | データ作成回数            | ×           |

| システム試験     | 検証項目数              | ○           |

|            | 不具合検出数             | ○           |

図5. WBS進捗入力例

図4. FPGA開発におけるV字モデルと成果物、指標値の関係

図6に例を示す。この位置があらかじめ設定した指標値内であれば適正な設計レビューが行われ、不具合除去も適正と判断する。指標値の範囲外の場合は次のように判断する。設計レビュー工数に比べて指摘件数が少ないとときは、設計品質が元々高かったか、設計の詳細にまで踏み込んだレビューができていないと判断しレビューが十分かを調査する。逆に設計レビュー工数に比べて指摘件数が多いときは、設計品質が低いと判断する。この場合は、設計品質の低さが今後問題となる可能性があるため、再レビューを行う。これらの対策によって、早期の品質向上が可能となった。

DRBFMは、流用設計変更時や設計途中の仕様変更時に適用する。DRBFMとは、既存の設計を変更する際、変更による心配点を抽出し、それが持つ影響範囲を検討し、変更設計するまでの対策や第三者の視点でのレビューを実施し、未然に不具合を防止する手法である。一覧表化された変更点に対して一つ一つ管理・対策することで、設計者自身が気づかなかつた不具合を検出することができた。

これらの施策によって、設計段階での早期不具合検出が可能となり、フロントローディング率が向上した。

### 3.3 検証段階での定量的開発管理手法

V字モデルの右側に位置する検証では、次の2種類の管理手法を用いる。

- (1) 不具合カウント基準の統一による不具合混入段階の見える化と分析、対策の実施

- (2) 検証レビュー工数と指摘件数を用いたゾーン分析による品質管理

設計データは、HDLバージョン管理ツールに更新データと更新履歴を登録することで管理する。不具合カウントにはHDLバージョン管理ツールが output する更新履歴ログを用いるが、更新履歴の記載レベルが設計者ごとに異なり、不具合と指標値の対応が不明確であったため、十分な分析ができなかった。そこで、HDLバージョン管理ツールに登録すべきバージョン更新履歴情報を定型化し、カウント基準を統一化した。さらに、HDLバージョン管理ツールのログから不具合発生ブロックや混入原因などのデータを自動取得するツールや、プロセス別検出欠陥数を自動集計するツールを作成した。これらによって、検証品質の分析精度向上と効率化が可能となり、真に必要な対策を実施することができた。

検証レビュー工数密度と指摘密度を用いたゾーン分析による品質管理は、設計段階のゾーン分析と同様に行い、必要に応じて追加レビューなどの対策を実施することで、検証漏れを防止することができた。

図6. 設計レビューにおけるゾーン分析

### 3.4 定量的開発管理による効果

この手法を通信機器用FPGA開発に用いることで、システム試験への流出不具合は半減以下となった。設計段階の定量的管理によって、仕様の誤解やインターフェース仕様不備による設計段階での不具合が減少し、検証段階の定量的管理によって検証漏れによる検証段階での不具合が減少した。特に、設計段階での不具合が減少しており、フロントローディング率は75%から88%に向上して、早期の品質改善につながった。

## 4. む す び

FPGA開発に対してソフトウェアの定量的開発管理手法を適用することは、工数見積り誤りの削減、システム試験への流出不具合削減、開発工程遅延防止に効果があることを述べた。流出不具合削減では、フロントローディング率が向上し不具合の早期検出率が高まり、手戻り削減と品質改善につながった。なお、今回のFPGAの定量的開発プロセス管理手法はASIC開発でも同様の効果を得ている。

今後は、総合的な検証終了判断を行うために、検証消化計画と累積欠陥数をグラフ化したX管理図などの手法を新たに適用して最終設計品質を向上させるとともに、FPGA開発工数に対する定量的開発管理工数の占める割合が高い中規模以下の開発を行う際の設計者の負担を抑える工夫を行っていく。

## 参 考 文 献

- (1) (独)情報処理推進機構 ソフトウェア・エンジニアリング・センター編：改訂版 組込みソフトウェア向け開発プロセスガイド、翔泳社（2007）

- (2) (独)情報処理推進機構 ソフトウェア・エンジニアリング・センター編：定量的品質予測のススメ—ITシステム開発における品質予測の実践的アプローチー、オーム社（2008）

# 無線通信向け低消費電力アナログLSIの設計検証技術

上杉美喜夫\*

大野正輝\*

平峰正信\*\*

Analog LSI Design Verification Techniques for Low-power Wireless Communication

Mikio Uesugi, Masaki Ono, Masanobu Hiramine

## 要 旨

無線通信機器で、特に携帯端末に搭載されるアナログLSIは、電池駆動であるため低消費電力化に対する要求が高い。また、製品サイクルは近年短くなっている傾向があり、開発期間を短縮するために効率のよい設計検証技術が求められている。

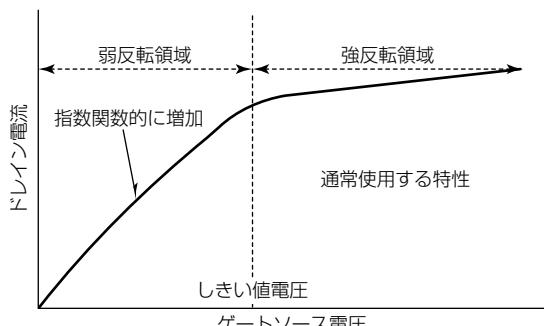

低消費電力化手法の一つとして、MOSFET<sup>(注1)</sup>のゲートソース間電圧をしきい値電圧より低い電圧とする弱反転領域での動作を前提とした設計手法があるが、

- (1) 微少電流のため、動作速度が遅い

- (2) 検証モデルと実デバイスとの性能差が大きい

- (3) 製造プロセスのばらつきに対して特性が敏感に変化する等の理由によって、回路特性の保証が困難なためあまり使

われていなかった。

今回、次に挙げる低消費電力アナログLSIの設計検証技術を適用することで開発の初期段階でこれらへの対策を可能とした。

- (1) 素子サイズ最適化設計技術

- (2) トリミング設計技術

- (3) ばらつき解析検証技術

- (4) 感度解析検証技術

- (5) リーク電流低減設計技術

- (6) 可視化による寄生抽出最適化検証技術

(注1) MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)は、電界効果トランジスタ(FET)の一種で、LSIの中では最も一般的に使用されている構造である。

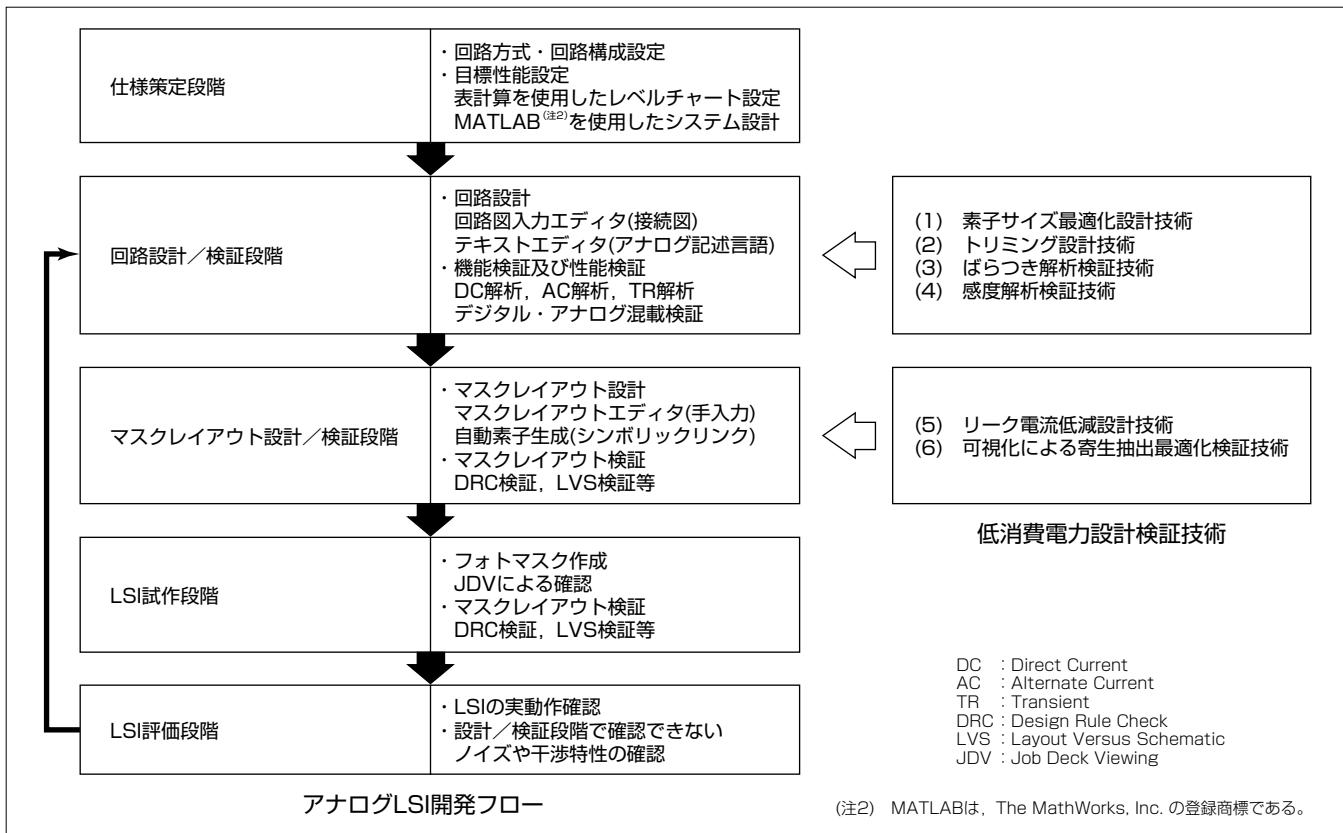

## 低消費電力アナログLSIの開発フローと設計検証技術

アナログLSIの開発フローのうち開発の初期段階で品質を作りこむには、回路設計／検証段階とマスクレイアウト／検証段階が最も効果的である。このため、低消費電力設計検証技術をこれらの段階に追加することで低消費電力アナログLSIの製品品質を高めることができる。

## 1. まえがき

無線通信機器に搭載されるアナログLSIで、特に携帯端末向けのものは、電池駆動が基本となっており、限られた電力消費の中で無線通信に必要な動作を行う必要がある。また、無線携帯機器では、1つのボタン電池で数年間動作することが求められ、低消費電力化に対する要求が高い。一方、製品サイクルは短くなってきており、短期間での効率的な開発が強く求められている。

本稿では、低消費電力アナログLSIの設計で、開発の初期段階で品質を作りこむために用いた設計検証技術について述べる。

## 2. 低消費電力化の手法

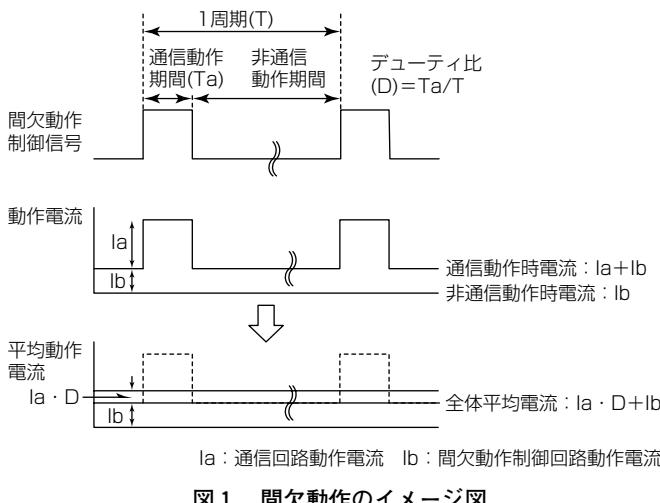

無線携帯機器で、ボタン電池1つで2年間の動作を可能とするためには、アナログLSI全体の消費電力を数十 $\mu\text{W}$ 以下にする必要がある。アナログLSIの低消費電力化を行う手法として、回路を間欠動作させる手法がある。間欠動作の電流イメージを図1を用いて述べる。間欠動作させるには、通信回路と間欠動作のタイミングを生成する間欠動作制御回路が必要である。通信回路の消費電流を $I_a$ 、間欠動作制御回路の電流を $I_b$ とした場合、通信動作時の電流は

図1. 間欠動作のイメージ図

図2. MOSFETの特性

$I_a + I_b$ 、非通信動作時の電流は $I_b$ となる。これをデューティ比 $1/250$ で間欠動作させた場合、アナログLSI全体の消費電流は、 $I_a/250 + I_b$ となり、アナログLSIの消費電流として $I_a$ の消費電流を大幅に低減することができる。このようにデューティ比を調整することで、低消費電力化が可能となるが、デューティ比の調整幅はシステムによって制約がある。また無線携帯機器のようなボタン電池での駆動が必要なシステムについては、間欠動作制御回路の電流 $I_b$ も無視できず、低減する必要がある。

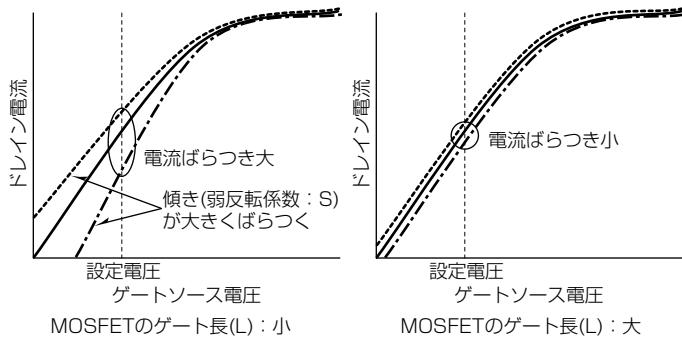

回路を構成する素子であるMOSFETの特性(図2)は、しきい値電圧(MOSFETがオンする電圧)を境に強反転領域と弱反転領域に分かれています。それぞれの特性が異なっています。一般的な回路に使用している領域は、強反転領域といわれるMOSFETがオンした状態での使用を前提としており、数 $\mu\text{A}$ 以上の電流が流れます。しかしこれでは目標である数十 $\mu\text{W}$ 以下にできない。よって弱反転領域での動作を前提とした設計手法を用いることとした。弱反転領域は、MOSFETがオフしている状態であり、数nA以下の微少電流である。この領域におけるドレン電流の特性はゲートソース間電圧に対して指数関数的に増加しており、この特性を用いて電流を制御し、間欠動作制御回路を動作させ、アナログLSI全体を数十 $\mu\text{W}$ 以下の低消費電力に抑えることが可能である。しかしMOSFETを弱反転領域で動作させる場合、次の問題が生じる。

- ①微少電流のため、動作速度が遅い

- ②製造プロセスに対して特性が敏感に変化する

- ③半導体メーカーから提供される回路検証用モデルと実デバイスとの性能差が大きい

- ④については間欠動作制御回路などの動作速度が遅くても問題のない回路用途に限って使用することで対策可能であるが、②、③については回路特性の保証が困難なため、今まであまり使われていなかった。今回、低消費電力アナログLSIの設計検証技術を適用することで②、③への対策を可能とした。

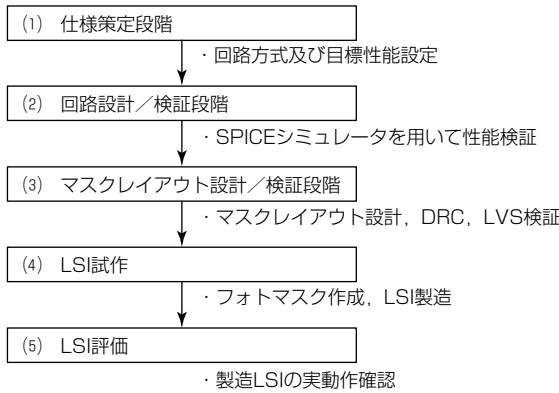

## 3. アナログLSIの開発フロー

まず、一般的なアナログLSIの開発フロー及び各フローの役割について図3を用いて述べる。

- (1) 仕様策定段階

システムとして必要な機能や性能を数式や表レベルで検討し、回路方式及び目標性能を設定する。

- (2) 回路設計／検証段階

策定された仕様に基づき設計を行う。設計した回路はSPICE(Simulation Program with Integrated Circuit Emphasis)シミュレータを用いて検証を行い、機能及び目標性能どおりの動作をするか確認する。

- (3) マスクレイアウト設計／検証段階

図3. アナログLSI開発フロー

(2)で設計した回路に対し、マスクレイアウト設計を行う。アナログ回路ではマスクレイアウトが性能に影響を及ぼすため、大部分が手作業で行われる。また規則どおりの幅や間隔でマスクレイアウト設計が行われているかの検証としてDRCや、回路図と設計したマスクレイアウトが完全に一致していることを確認するため、LVSなどの検証を行う。

#### (4) LSI試作段階

(3)で設計したマスクレイアウトでフォトマスクを作成し、LSIを製造する。

#### (5) LSI評価段階

製造したLSIが回路設計どおりの機能及び性能を達成しているか、実際に動作させて確認する。また回路設計／検証段階で確認できないノイズや回路間の干渉などを確認する。

弱反転領域動作での問題に対して開発の初期段階で対策を行うには、特に(2)回路設計／検証段階、(3)マスクレイアウト設計／検証段階で行うのが最も効果的である。これらの段階で適用した具体的な手法について次章に述べる。

## 4. 低消費電力アナログLSIの設計検証技術

### 4.1 回路設計／検証段階

弱反転領域で動作させた場合の問題点は、製造プロセスに対して特性が敏感に変化することと、検証モデルと実デバイスとの性能差が大きいことを2章で述べた。回路設計／検証段階でこれらの対策を行うのに用いた技術について述べる。

#### 4.1.1 素子サイズ最適化設計技術

製造プロセスの微細化に伴い、チップ面積の低減には大きく貢献しているが、逆に製造ばらつきの影響を受けやすくなっている。このため、製造ばらつきの影響を受けにくい設計を心がける必要がある。弱反転領域の特性で大きな影響を受けるのは、図4の特性の傾きを示す係数である弱反転係数(S)である。この弱反転係数の製造ばらつきを低減する手法として最も効果的なのは、MOSFETのゲート長(L)の最適化である。図4に示すとおり、ゲート長を大

図4. ばらつき特性

きくすれば弱反転係数のばらつきは小さくなり、回路上の設定電圧に対するドレン電流のばらつきを、低減することが可能である。設計時には、チップ面積の低減のため、ゲート長を小さくしがちだが、弱反転領域でのばらつきを検証し、最適なゲート長にする必要がある。

#### 4.1.2 トリミング設計技術

弱反転領域を用いた回路の場合、半導体メーカーから提供される回路検証用モデルと実デバイスとの性能差が大きいため、検証どおりには動作せず、最悪の場合動作しない可能性がある。このため、動作しなかったことを想定した対策が必要である。この対策として有効なのは、トリミング回路を付加することである。トリミング回路は、レジスタなどを用いて外部からソフトウェア的に回路特性を調整したり、レーザを用いて物理的に回路特性を調整する方法がある。特に試作段階では、回路検証用モデルと実デバイスとの性能差を把握するため、トリミング幅は極力大きくしソフトウェア的に調整できるようにしておく。

#### 4.1.3 ばらつき解析検証技術

ばらつきには、使用する電源電圧や温度等の“環境ばらつき”とLSIを製造する際に発生する“製造ばらつき”があり、製造ばらつきはMOSFETの利得や抵抗値などの絶対的なばらつきである“チップ間ばらつき”と素子の位置や向きに起因する相対的なばらつきである“チップ内ばらつき”とがある。またばらつき幅は一般的に“チップ間ばらつき”は $\pm 10 \sim \pm 30\%$ 、“チップ内ばらつき”は $\pm 1 \sim \pm 3\%$ と言われている。一般的な回路を設計する場合、“環境ばらつき”と“チップ間ばらつき”を考慮して、回路の特性がmax条件、min条件で問題ないか確認するコーナー解析を実施すれば、ある程度所望の特性を得ることができていた。しかし弱反転領域での動作は、少しの条件変化でも特性が大きく変動することから“チップ内ばらつき”についても考慮する必要がある。“チップ内ばらつき”的解析にはモンテカルロ解析が有効である。これは回路内の1個ずつの素子を統計分布に基づいてばらつかせ、解析するものである。ばらつき範囲や各素子の最大・最小値及び解析回数を設定でき、検証結果を分析することで、所望の特性を達成している。

#### 4.1.4 感度解析検証技術

また弱反転領域を用いた回路では、論理回路のオン／オフ切り換え時など、回路の状態が遷移する際に発生するノイズ電流が、回路動作に大きな影響を与え、例えば動作停止などの不具合を引き起こす場合がある。

このような不具合を回避するため、回路の構成素子一つずつに対して、素子がばらついた場合に回路特性がどのくらい変動するのかという特性変動に対する素子の寄与度を可視化できる感度解析を実施し、寄与度の高い素子には、不具合を回避する施策を行うことが有効である。

#### 4.2 マスクレイアウト設計／検証段階

回路設計／検証段階では回路自体の特性について述べてきた。マスクレイアウト設計／検証段階では、LSIの物理構造によって発生する現象の把握や影響の低減を主眼としてリーク電流低減設計技術と可視化による寄生抽出最適化検証技術で対策する。

##### 4.2.1 リーク電流低減設計技術

シリコン基板上のPN接合部に光が当たると、起電力が発生しリーク電流が生じる。このリーク電流量は弱反転領域で使用している回路電流と同レベルであり特性劣化や誤動作の懸念が生じる。マスクレイアウト設計時にはPN接合面を確認し、配線層で蔽(おお)い光を遮断する必要がある。これはレイアウト検証ツールであるDRCやLVSでは検出されないため、設計レビュー時に確実に確認することが重要である。

##### 4.2.2 可視化による寄生抽出最適化検証技術

マスクレイアウトの配線による抵抗成分や寄生容量成分による影響も無視できない。特に回路間を接続している配線が長くなると、配線抵抗及び配線と対地間及び配線間の寄生容量が大きくなり、次段の回路を駆動できなくなったり、他信号に対して大きく遅延したりして誤動作する。抵抗、容量及びインダクタンス等の配線寄生素子を抽出するLPE(Layout Parasitic Extraction)を使用し、設計した回路と合わせて検証することも必要である。しかし、実回路でLPEを行う場合、回路規模に応じて抽出時間や、抽出結果を設計した回路と合わせた検証時間が増大するため、回路規模によっては現実的な時間で検証できない問題が発生する。

このため、重要な配線を選択しその部分だけLPE抽出を行い検証時間を短縮する手法が用いられる。重要な配線を検出すためプログラムを作成し、配線長が長い配線や隣接配線との間隔が短い配線をマスクレイアウトツール上でハイライト表示し可視化するなどの手段も有効である。

図5. ブロック図

図6. 出力波形

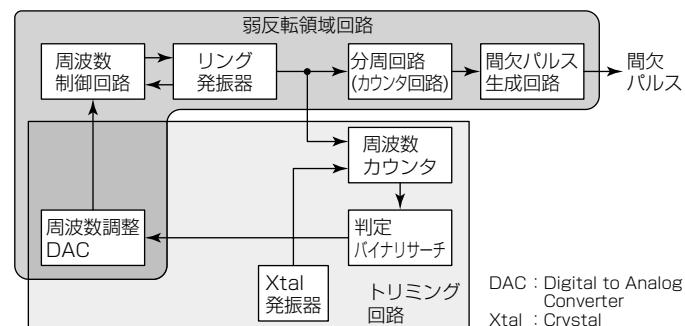

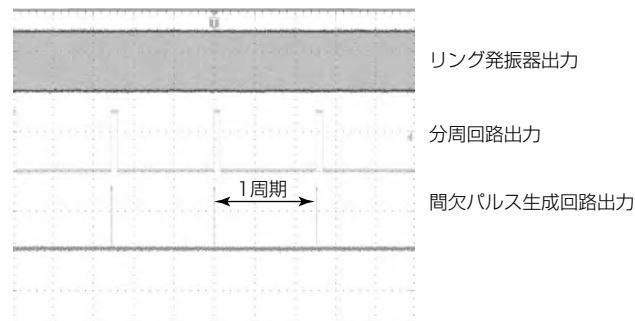

#### 5. 間欠動作制御回路

4章の設計検証技術のすべてを適用し、無線通信向けの間欠動作制御回路を試作した。間欠動作制御回路はアナログLSIを間欠動作させるための制御信号を生成している回路である。試作した回路のブロック図を図5に示す。また、試作品における間欠動作の出力波形を図6に示す。回路内をすべて弱反転領域で動作させた結果、間欠動作制御回路を消費電力  $1\mu\text{W}$  以下で実現することができた。この回路を用いてアナログLSI全体を間欠動作させることで、アナログLSI全体の消費電力を数十 $\mu\text{W}$  以下で実現し、1つのボタン電池で2年間の通信動作を可能とした。

#### 6. むすび

これらの設計検証技術を用いることで、所望の低消費電力アナログLSIを実現できた。本稿では低消費電力化に対する設計検証技術について述べた。この技術は低消費電力化に限らず、様々な用途に展開可能であり、今後もこの技術を活用して開発の初期段階における製品品質の作りこみを行う。

# 冷熱空調家電でのCFD活用による省エネルギー上流設計・検証解析技術

小林 孝\* 濱田慎悟\*\*

中津哲史\*\* 児玉拓也\*\*

衛藤 浩\*\*

*Energy Saving Design and Verification Method for Home Appliances Products using CFD*

Takashi Kobayashi, Satoshi Nakatsu, Hiroshi Eto, Shingo Hamada, Takuya Kodama

## 要 旨

近年の家電製品開発では性能向上、コスト削減、期間短縮における改善ニーズがますます高まっている。一見、三律背反とも思われるQCD (Quality, Cost, Delivery) のバランスを最適に成立させる設計方法論が求められている。特に冷蔵庫やエアコン製品では開発サイクルが短い中で、高い省エネルギー目標に応える必要がある。省エネルギー設計に重要な熱流体现象は目に見えないため、高精度な物理解析モデルを用いた可視化が有効である。

CFD (Computational Fluid Dynamics) を活用した三次元解析技術による現象の定量化・見える化から製品に対する理解度を深め、試作前段階で合理的・創造的に製品仕様を決定することが効果的である。

本稿では、家電製品設計に適した三次元解析手法を開発し、冷蔵庫での省エネルギー構造の構想と、エアコン室外機ファンの空力騒音源を特定した事例について述べる。熱流体・湿度・空力騒音を始めとするエネルギー移動、力学的現象は目に見えず、詳細な計測も困難であるため、高度な解析技術が有効である。その一方で、解析インフラは、数値計算の手段であり、製品開発で効果を創出するには利用技術の更なる向上や技術者育成が不可欠である。今後とも、新価値創造(アイデア考案型の攻めのCAE)から、品質保証(検証型の守りのCAE)までの広範な製品開発にこの手法を適用拡大し、持続可能な省エネルギー社会・地球環境の保全に貢献していく。

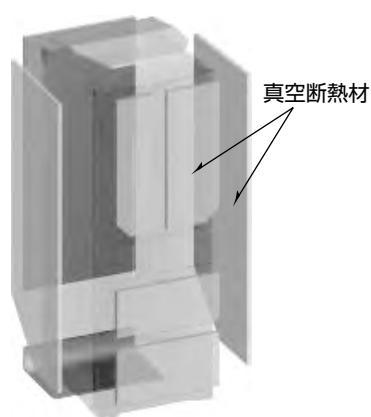

冷蔵庫の省エネルギー設計への適用

ルームエアコンの低騒音化設計への適用

## 冷熱空調家電における三次元熱流体解析手法の適用事例

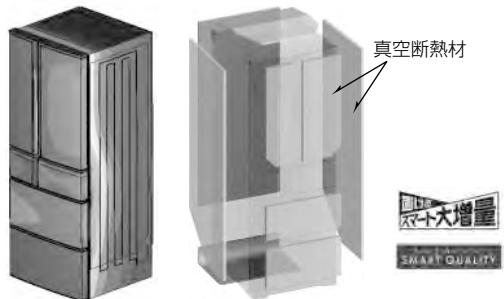

冷蔵庫全体の温度・熱流分布を三次元解析で可視化し、容量アップと省エネルギー性能を両立した“新・薄型断熱構造SMART CUBE”を実現した例(左)。

エアコン室外機プロペラファンの騒音要因となる渦度(流体要素の自転運動の強さ)( $\omega = \text{rot}U$ )の等価面を可視化した解析例(右)。

## 1. まえがき

近年の家電製品開発では性能向上、コスト削減、期間短縮における改善ニーズがますます高まっている。一見、三律背反とも思われるQCDのバランスを最適に成立させる設計方法論が求められている。特に冷蔵庫やエアコン製品では開発サイクルが短い中で、高い省エネルギー要求目標に応える必要がある。省エネルギー設計に重要な熱流体现象は目に見えないため、設計上流段階に高精度な物理モデルを導入することが有効である。近年ではCFDを活用した三次元解析技術が有力な設計支援ツールとなっており、現象の定量化・見える化から製品の理解度を深め、試作前段階に合理的・創造的に製品仕様を決定することが期待できる。

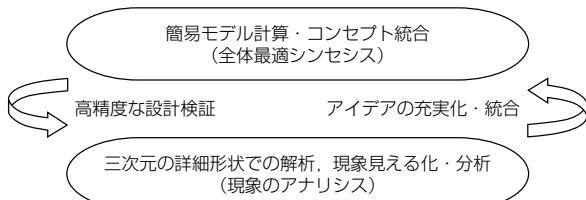

## 2. 熱流体解析による現象見える化・省エネルギー設計法<sup>(1)</sup>

製品設計とは、仮説立案と性能検証を繰り返し、限られた時間内に製品を具現化する創造的プロセスである。設計過程では、自ら設計検討モデルを構想し、設計仕様を満足するまで仮説構築と検証を繰り返して機能・形状を実体化していく。具体的には、図1に示す段階的詳細化(Step-wise refinement)ループを回して、限られた開発期間とりソースの中で製品のQCDを作りこむ。

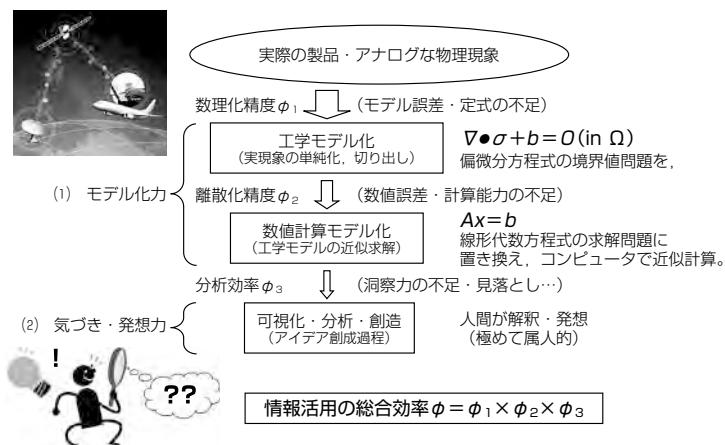

設計上流でのオーダー計算モデルで製品構想の方向性を絞り込み、有望案の三次元解析から高精度な設計検証と発想アイデアの充実化をはかる。大規模解析から得られる現象情報は豊富であり、設計者の発想支援に創造的ブレーカスルーを起こす可能性がある。これらの解析ツールやITの解析結果から得られる解の有効性は設計者が設定するモデル品質次第であり、次の2つの能力が決め手となる(図2)。

### (1) モデル化力(適切な設計モデルを構築する能力)

最新の並列計算環境(High Performance Computing: HPC)上で熱流体解析を行えば、数mm単位の空間解像度、数msオーダーの時間分解能で物理現象が解像できる。つまり、実験データ情報をしのぐ製品丸ごとの物理現象の見える化が実現されつつある。その一方で、例えば空力騒音現象を支配する物理現象スケールは数mPaの圧力変動や数μm程度の渦スケールであり、適切な簡略化や乱流モデルの導入が必要となる(モデルリダクション)。つまり、利用者自身

図1. 段階的詳細化設計ループ

が対象の本質を理解し、適正な支配方程式や計算アルゴリズム、離散化スキーム、乱流モデルを選定し、適切な計算格子や境界条件、時間ステップを決定して、モデルを構築する必要がある。

### (2) 気づき・発想力(膨大な解析結果から読み取る能力)

近年のHPC環境では複数の物理量について、数千万から数億格子点での空間分解能で、μs単位の時間分解能の非定常挙動を計算できる。したがって、よりリアルな“設計モデル”が構築できれば、人間の想像力を超えた製品理解と発想支援が期待できる(Inputの質・量が変われば、Outputの質も変わる)。しかしながら、得られた数値解は単なる数字の羅列である。その解析結果をどこまで信頼し、膨大な三次元情報(一種のビッグデータ)をどんな切り口(物理量、座標軸、時間軸・・・)で分析して発案に結びつけるかは利用者のセンスや経験量に強く依存する。つまり、膨大な解析結果(Information)を効果的に設計知識(Knowledge)，設計革新への英知(Wisdom)へと昇華・価値化させる利用者側での洞察力・創造力(Intelligence)が不可欠である。

## 3. 空調冷熱機器への適用事例

この章では、三次元熱流体解析を省エネルギー冷蔵庫や、エアコン室外機の低騒音化の開発に適用した設計事例について述べる。

### 3.1 冷蔵庫の省エネルギー設計への適用事例<sup>(2)(3)</sup>

#### 3.1.1 薄型断熱箱設計への活用

低消費電力の省エネルギー冷蔵庫を実現するには、ヒートポンプの負荷となる外部からの熱浸入量を減少させる箱の断熱設計が鍵となる。壁を経由した庫内への熱流束 $q_x$ の合計熱量 $Q_{total}$  [W]は式(1)、式(2)でオーダー試算できる。

$$Q_{total} = \iint_A q_x dA = \iint_A K_x \cdot (T_{外気温度} - T_{庫内温度}) dA \quad \dots \dots \dots (1)$$

$$K_x = \frac{1}{\frac{1}{\alpha_o} + \sum \frac{t_{solid}}{\lambda_{solid}} + \frac{1}{\alpha_i}} \quad \dots \dots \dots (2)$$

設計センス=妥当な設計モデルの構築・分析・創造力！

図2. デジタル手法利用における情報欠損・要因過程

$\alpha_0$ ：庫外熱伝達率[W/m<sup>2</sup>K]

$a_i$  : 庫内熱伝達率 [W/m<sup>2</sup>K]

$\lambda$  : 壁の熱伝導率 [W/mK]

$t$  : 固体壁厚さ [m]

$K_x$ ：局所壁熱通過率[W/m<sup>2</sup>K]

ただし、実際の冷蔵庫では断熱が弱い壁部位や板金フランジを経由して壁内を三次元的に熱流が回り込むが、実験的な把握が難しい。そこで図3に示す箱全体での三次元解析モデルを開発し、壁内の熱流経路のビジュアル化・特定を可能とした。この手法を設計上流段階で適用し、断熱の基本となる真空断熱材のレイアウト、扉、外壁の壁厚を最適化して、容量アップと省エネルギー性能を両立させた“新・薄型断熱構造SMART CUBE”を実現した。

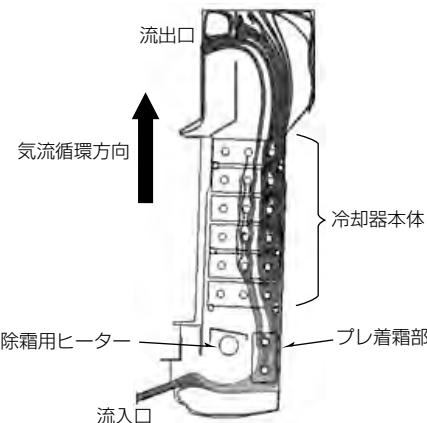

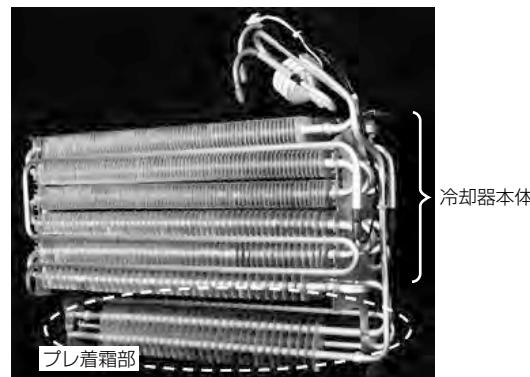

### 3.1.2 プレ着霜冷却器開発への活用

庫内の狭空間の気流や温度、湿度分布は目に見えない現象であり、多点実測が困難である。そこで、冷却器周辺の高温多湿の空気の流動分布を解析的に可視化した。冷蔵室から戻る高湿空気は循環経路内で上向きに曲がる際の遠心力で背面側(図4の右壁側)に集中することがわかった。そこで、高湿空気が冷却器本体に触れる前に効果的に除湿する“プレ着霜冷却器”(図5)を考案した。冷却器の風上に設けたプレ着霜フィン部を通過した空気は除湿状態で冷却器本体に流入するため、冷却器本体への霜付着が軽減できる。その結果、従来品に対して同一の着霜量での冷却能力維持時間を30%延長でき、外気温度が高い季節の除霜運転周期

図3. 冷蔵庫の熱現象可視化例と考案した新薄型断熱箱

図4. 冷蔵室からの多湿空気流動の解析的把握

を24時間から48時間に1回に低減できた。また、集中着霜設計の思想も奏功して除霜のためのヒーター印加時間も従来比で半減し、年間消費電力量を大幅に低減できた。

### 3.2 ルームエアコンへの適用事例<sup>(4)</sup>

### 3.2.1 室外機プロペラファンの低騒音化設計への活用

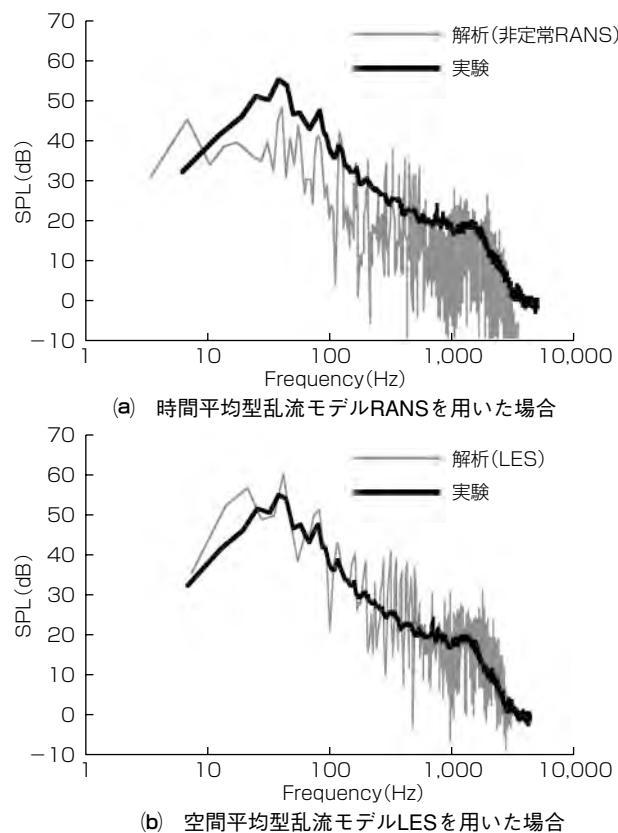

快適居住性を訴求価値とする白物家電では、省エネルギー性能とともに低騒音化も重要な設計テーマである。エアコン室外機で熱交換性能を増大するには、ファン回転数の増加が有効である。しかし、風量はファンの回転数に比例するのに対し、空力騒音は回転数の5～6乗に比例して増大する(図6)。

### 3.2.2 プロペラファンの空力騒音解析技術の開発

回転翼によって空気塊が流動すると、空気の弾性と慣性作用から渦の収縮・拡大に伴う微小な圧力変動が起こる。回転翼は観測者に対して加速度運動する移動音源となり、伝播(でんぱ)した粗密波(騒音)は次式に示すSPL(音圧レベル)値[dB]として評価される。

$$SPL = 10 \times \log \left( \frac{P^2}{P_0^2} \right) = 20 \times \log \left( \frac{P}{P_0} \right) \quad \dots \dots \dots \quad (3)$$

ここで $P_0$  ( $= 2 \times 10^{-5}$  [Pa]) は基準値となる1,000Hzでの人間の標準的最小可聴音圧である。高速な回転体から生じる微小な圧力の伝播現象を実験的に計測して音源部位を特定することは困難である。近年では、表1に示す空力騒音解析手法の適用が有望である。

今回の適用対象では音源へのフィードバック現象は小さいため、計算負荷が軽減できる分離解法を適用した。最初に、非圧縮性流れを仮定して800rpmでファンを回転させ

図5. プレ着霜フィン付き新型冷却器

図6. エアコン室外機(左)とファン周囲の渦度 $\omega$ 等値面(右)

表1. 空力騒音解析手法の分類

| 手法                | 特徴                                                                                                                                     |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| (1) 直接解法<br>(CAA) | Lighthill方程式を直接計算し、圧縮性流体解析での密度変化から粗密波の伝播を直接に求める。伝播する音波の干渉やフィードバックを考慮できるが、波長の1/10程度の格子分解能や、小さな圧力変動を計算可能な高次な精度スキーム、時間分解能が必要で、計算負荷が膨大である。 |

| (2) 分離解法          | 非圧縮性流体解析で音源部位の圧力変動を計算した後に、音響伝播を別途計算する。音源へのフィードバックを考慮できないものの、直接解法に比べて大幅に計算負荷を削減できる利点がある。                                                |

CAA : Computational Aero Acoustics

た非定常乱流解析を行った。解析領域の格子分割数は約3,500万で、空間離散化には2次精度MUSCL(Monotone Upstream-centered Scheme for Conservation Laws)スキームを用い、ファン1回転あたり360タイムステップの時間分解能(4.8kHz)とした(翼枚数と回転数で決まるBPF(Blade Passing Frequency)の1次NZ成分(40Hz)の120倍に相当)。次に、流体解析から得られた圧力変動を音源情報として音響解析の入力条件とした。音響アナロジー解析では、流れ中の移動物体の音圧伝播モデルとして導かれたFfowcs-Williams and Hawkings(FW-H)の波動方程式を解き、ファン回転運動と翼やベルマウス表面の圧力変動に伴う空力騒音を評価した。実験値と解析値は、ファンから風上に0.7m離れた観測点での音圧スペクトルで比較した。流体解析での乱流モデルは、最初に非定常RANS(Reynolds Averaged Navier-Stokes equation)を用いたが、実験値に対して音圧レベルが過小評価された(図7(a))。ここで、非定常RANSで導入されるレイノルズ応力は、非定常流を時間平均的(定常流)に類推するみかけの力である(乱流運動エネルギーkと乱流エネルギー散逸率εの関係から流れの非定常性や局所的な変動を時間平均化したモデルである)。したがって、音源となる微小渦の圧力変動も時間平均化されて過小評価されてしまう。次に用いた空間平均型乱流モデルLES(Large Eddy Simulation)では、非定常性や局所的なはく離は一切モデル化せず、格子サイズ以下のエネルギー伝達だけがモデル化される。モデルの原理的にLESは、RANSが苦手とする大規模はく離や乱流の非定常再現に優れ、解析値は実測値とよく一致した(図7(b))。また渦度等値面による空力騒音源の空間分布の特定・可視化も可能となった。

#### 4. む す び

家電製品を対象とした高精度な熱流体解析モデルを開発し、冷蔵庫での省エネルギー構造の考案や、エアコン室外機ファンの空力騒音源を特定した事例について述べた。熱流体・湿度・空力騒音を始めとするエネルギー移動、力学現象は目に見えず、場の物理量の詳細計測も困難であるため、高精度な解析技術が有効である。この手法を効果的に

図7. ファン空力騒音における実験値と解析値の比較

用いれば、限られた時間制約の中で製品価値を高めつつ、技術合理的なコスト低減(製品ムダ取りVE)も可能となる。その一方で解析インフラは、数値計算の手段であり、製品開発で効果を出すには、創造的な利用技術の開発や技術者育成が不可欠である。今後とも、新価値創造(アイデア考案型の攻めのCAE)から、品質保証(検証型の守りのCAE)までの広範な製品開発にこの手法を適用し、持続可能な省エネルギー社会・地球環境の保全に貢献していく。

#### 参 考 文 献

- (1) 小林 孝: Digital Engineering 2.0の必要性: 日本製造業におけるプロセス革新アーキテクトの必要性, 日本機械学会 設計工学・システム部門講演会講演論文集, 315~318 (2007)

- (2) Kobayashi, T., et al.: An Integrated Design method for Refrigerator using Thermal-Fluid-Refrigeration cycle Coupled Analysis, The Seventh JSME-KSME Thermal and Fluids Engineering Conference 2008 (2008)

- (3) 大和康成, ほか: 節電アシスト機能搭載冷蔵庫“RXシリーズ”的節電・省エネルギー技術, 三菱電機技報, 86, No.10, 564~567 (2012)

- (4) Jeon, W. H., Kobayashi, T., et al.: Study on the CFD method for noise source identification and aeroacoustic analysis of an axial fan, Inter Noise 2011 (2011)

# 制御盤の放熱・耐震設計検証技術

*Thermal and Earthquake Resistant Design and Verification Technologies for Control Console*

Jiro Yoshizawa, Keita Tonoike, Yoshio Okinishi

吉沢二郎\*

外池恵大\*

沖西佳雄\*\*

要旨

箱型筐体(きょうたい)に制御機器を納めた制御盤は、信頼性を確保する上で、放熱設計や耐震設計の重要度が高い。例えばインターネットインフラを支える光通信装置(光通信用の制御盤)は、通信処理量の増加に伴い発熱が増大しており、高い放熱性能が求められている。また、巨大地震の多発によって従来以上に耐震性能の重要性が高まっている。これらの性能確保のためには、設計自由度の高い開発上流で詳細に設計検討する必要がある。

一方で制御盤の放熱設計検証や耐震設計検証は計算機の高速化に伴い三次元データを活用した三次元解析の導入が進んでいる。しかし、無秩序に三次元解析を行うと非効率な作業となり、性能確保の効率的な設計検討を阻害する。

このため、三次元データを有効に活用しながら効率的に設計する設計プロセスの再整備が必要になってきている。

本稿では、光通信装置の放熱性能及び耐震性能を効率的に検討する設計検証技術と設計プロセスを実現する設計環境について述べる。

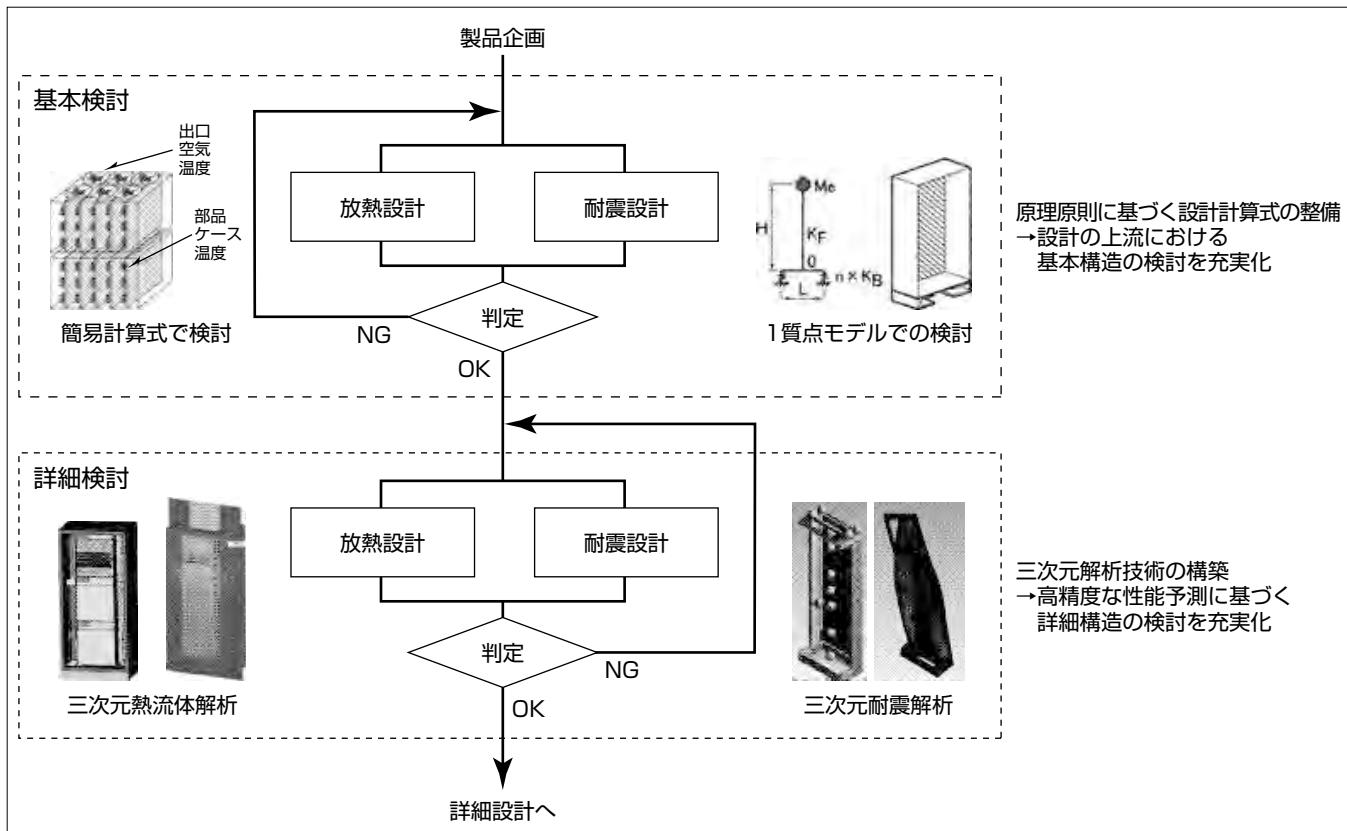

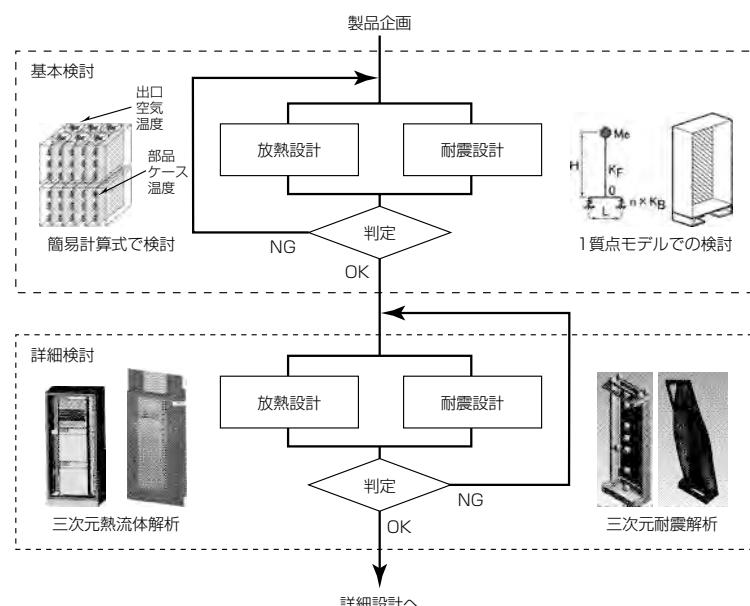

まず、原理原則に基づく設計計算式を集約した設計ツールを整備して、基本構造の幅広い検討を可能とした。次に、実際の詳細構造の現象を予測する三次元解析技術を構築し、高精度な性能予測に基づく詳細構造の検討を可能とした。

設計計算式を用いて基本検討をした上で、三次元解析技術を用いた詳細検討をする設計プロセスの設計環境を整備することで、放熱性能と耐震性能の効率的な設計を実現した。

## 光通信装置の放熱・耐震設計プロセス

光通信装置を対象に、放熱設計と耐震設計の設計検証技術を開発した。設計計算式を用いて基本検討をした上で、三次元解析技術を用いた詳細検討を行う設計プロセスの設計ルールと設計環境を整備することによって、高い放熱性能と耐震性能の効率的な設計を実現した。

## 1. まえがき

箱型筐体に制御用の電気、電子機器を納めた制御盤は、電力システム・情報通信システム・ビル管理システム等を構成する装置として様々な形で利用されている。安定してシステムを稼働させるために、制御盤には高い信頼性が必要とされ、信頼性を確保する上で、制御盤の放熱設計や耐震設計の重要度が高い。

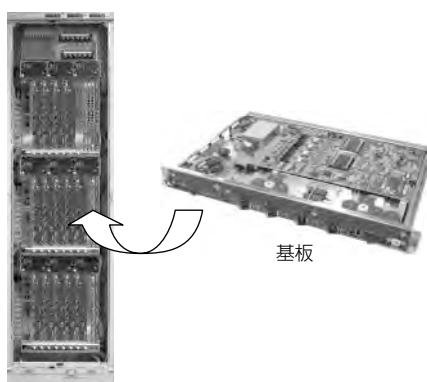

例えば情報通信用の光信号を制御する光通信装置(光通信用の制御盤)は、情報ネットワークインフラを支えるために高い信頼性が要求される。インターネットを中心に情報ネットワークは世界的規模の社会インフラとなって拡大・進化を続けている<sup>(1)</sup>。通信処理量が増加傾向にある光通信装置は、装置の発熱が増大しており、高い放熱性能が求められている。また、巨大地震の多発によって従来以上に耐震性能の重要性が高まっている。これらの性能を確保するためには、設計自由度の高い開発上流段階で詳細に設計検討する必要がある<sup>(2)</sup>。

一方で制御盤の放熱設計や耐震設計検証は計算機の高速化に伴い三次元データを活用した三次元解析の導入が進んでいる。しかし、無秩序に三次元解析を行うと非効率な作業となり、性能確保の効率的な設計検討を阻害する。このため、三次元データを有効に活用しながら効率的に設計する設計プロセスの再整備が必要になってきている。

本稿では、光通信装置の放熱性能及び耐震性能を効率的に検討する設計検証技術と設計プロセスについて述べる。

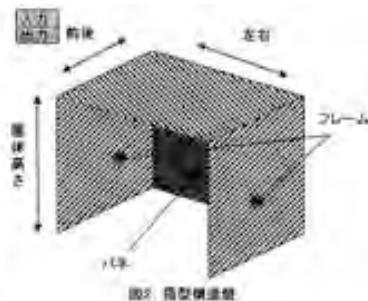

## 2. 放熱・耐震設計プロセスの構築

光通信装置(図1)の放熱設計・耐震設計には、概略性能予測をする設計計算式が従来用いられてきた。原理原則に基づき物理法則から構築された設計計算式は、設計工学の進歩とともに進化し、仮定条件によって異なる多様な計算式が存在する。例えば、放熱設計における仮定条件は、吸排気口の圧力損失を考慮するか否か、放射による放熱を考慮するか否か、冷却用ファンの特性を考慮するか否か等がある。どの計

図1. 光通信装置

算式を用いるかは、設計者の裁量に任されていたため、経験によって設計完成度は大きく異なっていた。また、どちらの計算式でも仮定条件による大きな予測誤差が含まれる。このため、計算式によって設計した試作品の実測結果に基づき再度検討する時間を確保し、製品設計を完了してきた。

一方、市場へのタイムリーな製品投入に向けた短期開発のためには、試作段階の設計手戻りを抑制する必要があり、設計段階の詳細性能予測が重要となる。このため近年では、詳細性能予測が可能なCAE(Computer Aided Engineering)による三次元解析が活用されてきている。しかし三次元解析は、計算モデルの検討に時間がかかり、さらには、計算実行に時間がかかるために多くの設計案の検討は困難である。このために、設計期間内に検討しきれずに、試作段階の設計手戻りが発生するケースが散見されていた。

そこで、設計検討の効率化を図り短期開発を実現するために、設計プロセスの見直しを実施した。まず、設計計算式を棚卸しし、仮定条件を極力排除した上で多くの検討が可能な計算式を選定した。さらに、実測結果との比較によって設計計算式の予測精度を確認し、検討可能な範囲を明確化した。この計算式を用いた設計ツールを整備することで、設計者の経験によらず基本構造の幅広い検討を可能とした。次に、詳細性能予測に必要な精度を製品コストに影響を与える過剰設計とならないように見定めた上で、同精度で予測が可能かつ短時間で計算可能な三次元解析の計算モデルと設計時の判定基準を構築した。これらをルール化することで、高精度な性能予測に基づく詳細構造の検討を可能とした。3章で放熱設計、4章で耐震設計について構築した内容を述べる。

設計計算式を用いて基本検討をした上で、三次元解析技術を用いた詳細検討をする設計プロセス(図2)を実現する

図2. 放熱・耐震設計プロセス

設計環境を整備することで、放熱性能と耐震性能の効率的な設計を実現した。

放熱設計では、従来は設計段階で4週間かけて2,3パターンの検討しかできず、試作段階で2か月程度かけて詳細検討を実施していた。今回の設計環境を製品開発に活用したところ、3週間で約40パターンの検討を実施した上で設計を完了し、試作段階で設計手戻りなく開発を完了した。40パターンの検討は、従来試作段階で実施していた製品の仕様違いやファン故障時などの想定や放熱部品コスト低減に向けた検討などである。

また、耐震設計では、従来は設計段階で2週間かけて検討し、試作段階の耐震試験で問題が発生した場合は、2か月程度の設計手戻りが発生していた。今回の設計環境を製品開発に活用したところ、1週間で設計を完了し、試作段階で設計手戻りなく開発を完了した。

次に、今回整備した放熱設計検証技術と耐震設計検証技術について述べる。

### 3. 放熱設計検証技術

光通信装置は、実装された数十枚の基板から合計4,000W前後の発熱があり、10個以上の強制空冷ファンを搭載して冷却している。複数あるファンの1つが故障しても装置は停止することなく稼働しつづける必要があるため、ファンを交換するまでの間も冷却性能を確保しなければならない。基板に実装される高発熱のLSI(Large Scale Integration)

などのデバイスを冷却するために、強制空冷ファンやヒートシンク、ヒートパイプ等の冷却部品を適切に配置する放熱設計が必要となる。冷却対象のデバイスは100~200個にのぼる。

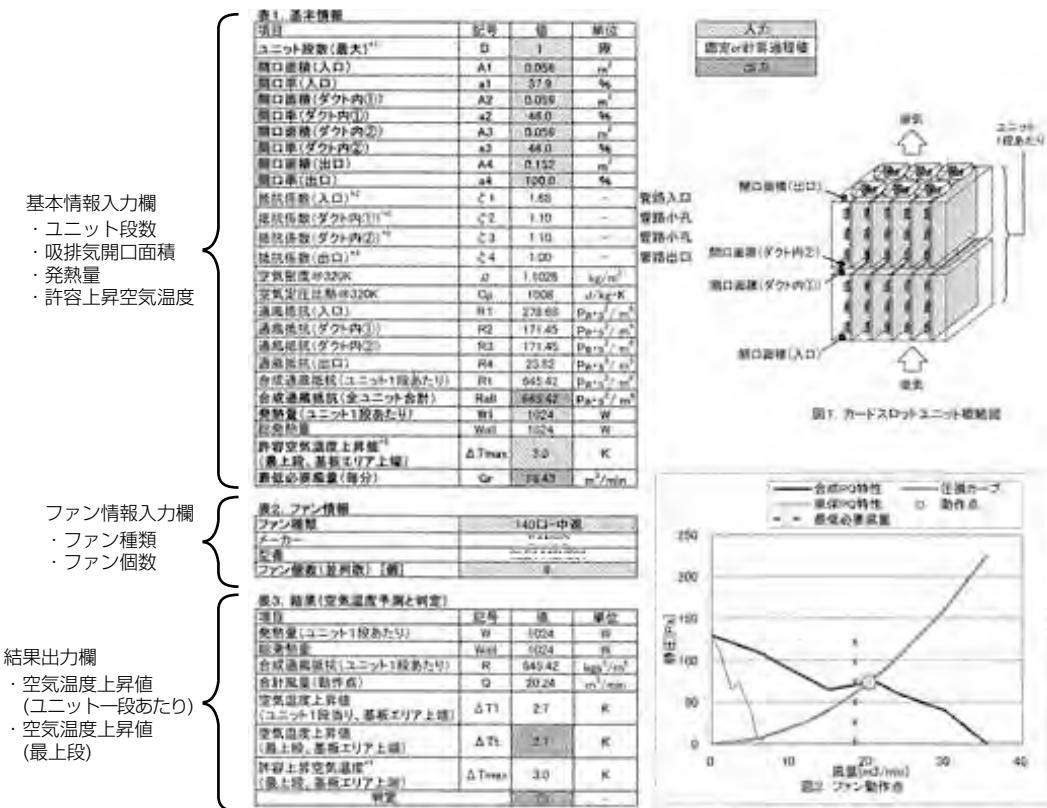

#### 3.1 放熱構造の基本検討

放熱構造の基本検討段階では、まず、盤筐体サイズと総発热量から、強制空冷ファンの必要有無、強制空冷ファンの種類と必要個数等を仮決定する。次に、仮決定した強制空冷ファンの風量から全てのデバイスの温度を計算する。デバイス温度によって、ヒートシンクやヒートパイプによる冷却を必要とするか否かを見極める。全体的に温度が高い場合は、強制空冷ファンの選定まで戻り、繰り返し計算をする必要がある。これらの基本検討は、幅広く検討する必要があるため、瞬時に計算検討が可能な設計計算式を用いるようにした。

設計計算式を集約した表計算シートを用いた放熱設計計算ツール(図3)を整備したこと、効率的な検討が可能になった。また、設計計算式によって計算される温度の誤差は、10°C程度あることを実測結果との比較によって明確にした。誤差を含めて設計許容温度以内になる場合は、以降の詳細検討を省略することが可能である。また、許容温度が誤差範囲内にあり注意が必要なデバイスだけスクリーニングして検討するようにすることで、詳細検討にかかる時間を削減した。

#### 3.2 放熱構造の詳細検討

放熱構造の詳細検討段階では、装置内の冷却風の風速分

図3. 放熱設計計算ツール(基本検討)

布によるデバイス温度への影響を確認し、デバイスの配置やヒートシンク、ヒートパイプの詳細構造を決定する。筐体構造やデバイス配置によって、風速は複雑に分布する。このため、風速分布の影響を含めた放熱構造の検討は三次元熱流体解析によって行う。

詳細検討に必要な精度は $\pm 5^{\circ}\text{C}$ と決定した上で、同精度を確保可能な計算モデルを検討した。その結果、LSIのはんだや内部構成を詳細にモデル化する必要があるとともに、盤筐体内部の冷却風の全体の流れを考慮しなければならないことが判明した。しかし、盤筐全体の計算を実行する

図4. 放熱設計計算モデル(詳細検討)

ためには、計算時間が数十時間かかり、設計期間内の検討に活用できない。そこで、部分計算と全体計算を組み合せた計算モデル(図4)を構築し、計算時間を1/10以下に短縮した。

計算モデルのルールを整備することで、容易に効率的な詳細検討が可能な環境を構築した。

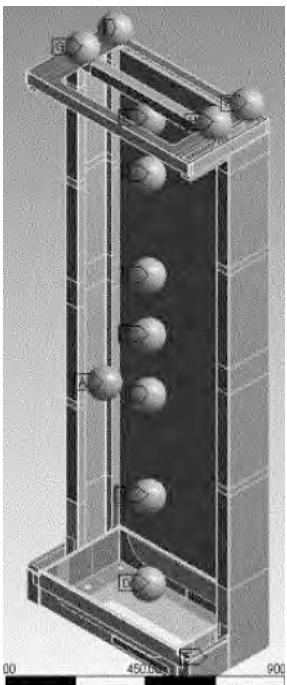

#### 4. 耐震設計検証技術

光通信装置は、質量200~300kg、製品の高さが1.8~2.3m程度ある自立筐体である。床に固定された状態で地震などの振動が加わった際に筐体の固有振動数と振動の周波数が一致して共振を起こし損傷しないように、筐体の固有振動数と強度を高くする必要がある。一方で、通信量増加に対応して設置台数を増加させるために、1台当たりの設置面積の削減が求められている。一般に同一質量、同一高さで設置面積を削減すると筐体の固有振動数が低下するため、耐震設計が重要となる。

##### 4.1 耐震構造の基本検討

耐震構造の基本検討段階では、まず、盤筐体の基本構造と構造部品の板厚等を仮決定する。次に盤筐体サイズと質量から、盤筐体の固有振動数と構造部品の応力を計算し、設計許容値を満足するか判断する。これらの基本検討は、幅広く検討する必要があるため、瞬時に計算検討が可能な設計計算式を用いるようにした。

設計計算式を集約した表計算シートを用いて耐震設計計算ツール(図5)を整備したこと、効率的な検討が可能に

|                                             |                                                                                                                  |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 基本情報入力欄<br>・総質量<br>・筐体高さ                    | 表1. 基本情報                                                                                                         |

| フレーム部情報入力欄<br>・フレーム材料の縦弾性係数<br>・パネル材料の縦弾性係数 | 表2. フレーム部構造<br>・フレーム材料の縦弾性係数<br>・パネル材料の縦弾性係数                                                                     |

| 基礎部情報入力欄<br>・本体材料の縦弾性係数<br>・架台材料の縦弾性係数      | 表3. 基礎部構造<br>・本体材料の縦弾性係数<br>・架台材料の縦弾性係数                                                                          |

| 結果出力欄<br>・固有振動数<br>・頂部変位                    | 表4. 加速度情報<br>・加速度<br>表5. 結果(固有振動数、頂部変位、応力の予測と検定)<br>・固有振動数 (Hz)<br>・頂部変位 (mm)<br>・正規化基準加速度 (g)<br>・引張り基準応力 (MPa) |

図5. 基礎部の変則モデル

(表3中の番号と対応)

図5. 耐震設計計算ツール(基本検討)

図6. 耐震設計計算モデル(詳細検討)

なった。また、設計計算式によって計算される固有値の誤差は、30%程度あることを実測との比較によって明確にした。誤差を含めて設計許容値以上になる場合は、以降の詳細検討を省略することが可能である。

#### 4.2 耐震構造の詳細検討

耐震構造の詳細検討段階では、部品配置やボルト・リベット・溶接等の固定構造による影響を確認し、構造部品や補強部品の詳細形状を決定する。固定構造や部品配置によって、荷重は複雑に分布する。このため、荷重分布の影響を含めた耐震構造の検討は三次元耐震解析によって行う。

詳細検討に必要な固有振動数の精度は±10%と決定した上で、同精度を確保可能な計算モデル(図6)を構築した。

計算モデルのルールを整備することで、容易に効率的な詳細検討が可能な環境を構築した。

#### 5. むすび

光通信装置を対象に、設計計算式を用いて基本検討をした上で、三次元解析技術を用いた詳細検討を行う設計プロセスの設計環境を整備することで、放熱性能と耐震性能の効率的な設計を実現した事例について述べた。

今後、電力や公共施設向け制御盤にも展開していく予定である。

#### 参考文献

- (1) 西村隆司：進化するネットワーク技術特集に寄せて，三菱電機技報，86，No.6，313（2012）

- (2) 小林 孝，ほか：カーナビ開発におけるフロントローディング型実装設計，三菱電機技報，80，No.10，651～654（2006）

# 変更影響分析による 設計課題抽出プロセスの構築

菅ヶ谷貴也\* 山本順司\*\*

長江雅史\*

西島暁生\*

*Frontloading Design Verification Technology by Change Impact Analysis*

Yoshinari Sugegaya, Masashi Nagae, Akio Nishijima, Junji Yamamoto

## 要旨

近年、電子機器の高機能化、高性能化、小型化等が進み他社との競争が激化する中、顧客のニーズに合わせた新製品の市場投入が競争力強化の重要なポイントとなっている。その中で、新製品の市場投入を、計画通りに行うためには、開発遅延の要因となる後工程からの設計手戻り抑制が課題であった。

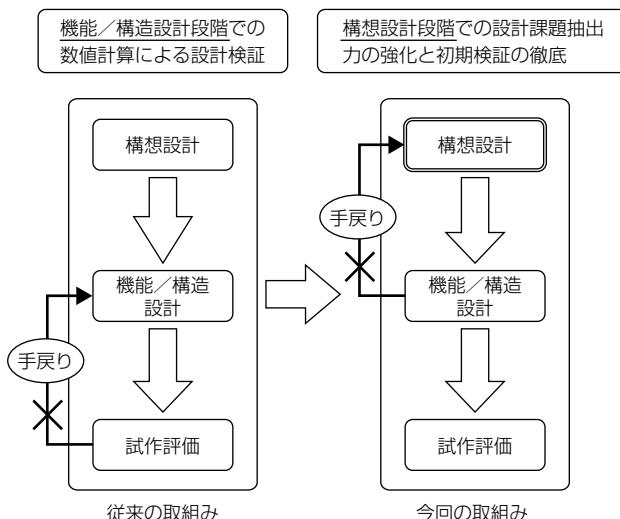

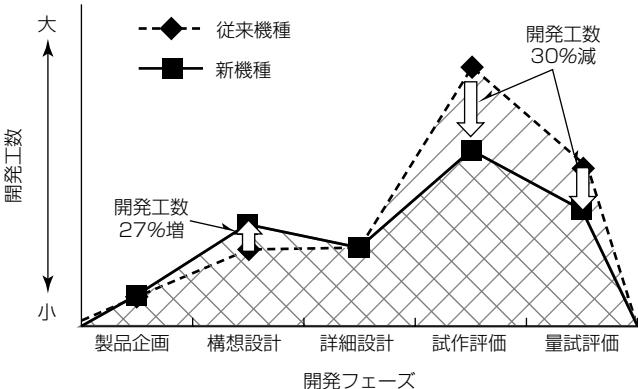

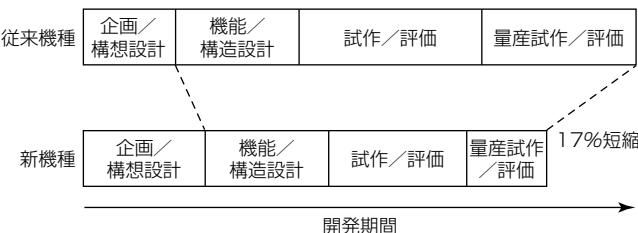

従来の取組みでは、機能／構造設計段階で数値計算を活用した設計検証を強化し、試作／評価時のカットアンドトライ対策などの設計手戻りを抑制した。今回、構想設計段階で、設計課題の抽出とその初期検証の強化に取り組み、

機能／構造設計段階での設計検証漏れや設計変更に伴う設計手戻りを抑制した。

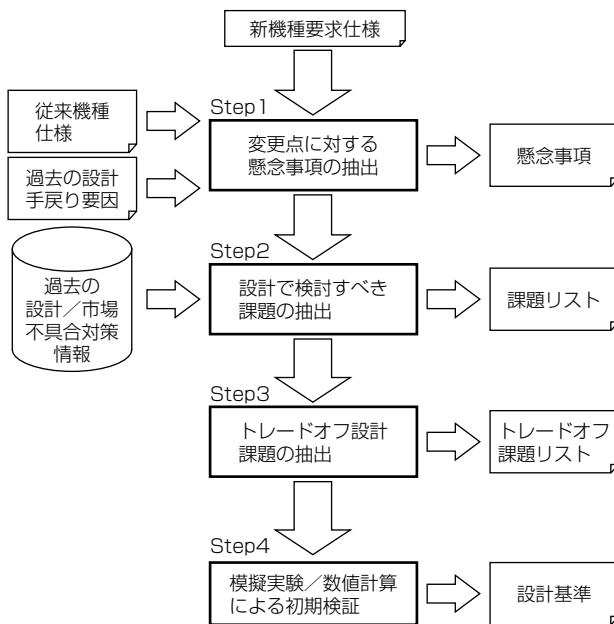

具体的には、構想設計段階で、設計で検討すべき課題を漏れなく抽出するために、従来機種からの変更点に着目し、次の標準的な設計課題抽出プロセスを構築した。

- Step 1：変更点に対する懸念事項の抽出

- Step 2：設計で検討すべき課題の抽出

- Step 3：トレードオフ設計課題の抽出

- Step 4：模擬実験／数値計算による初期検証

## 電子機器の設計フローと構想設計段階における変更点に着目した設計課題抽出プロセス

電子機器の構想設計段階での網羅的に設計課題を抽出するプロセスを示す。従来機種と新しく開発する新機種の要求仕様に対する変更点に着目し、マトリックス表と過去の設計手戻り要因や設計／市場不具合対策情報のデータベースを活用した変更影響分析による網羅的な設計課題の抽出が特徴である。

## 1. まえがき

近年、電子機器の高機能化、高性能化、小型化等が進み他社との競争が激化する中、顧客のニーズに合わせた新製品の市場投入が競争力強化の重要なポイントとなっている。その中で、新製品の市場投入を、計画通りに行うためには、開発遅延の要因となる後工程からの設計手戻り抑制が課題であった。

従来の取組みでは、機能／構造設計段階で数値計算を活用した設計検証を強化し、試作／評価時のカットアンドトライ対策などの設計手戻りを抑制した<sup>(1)</sup>。

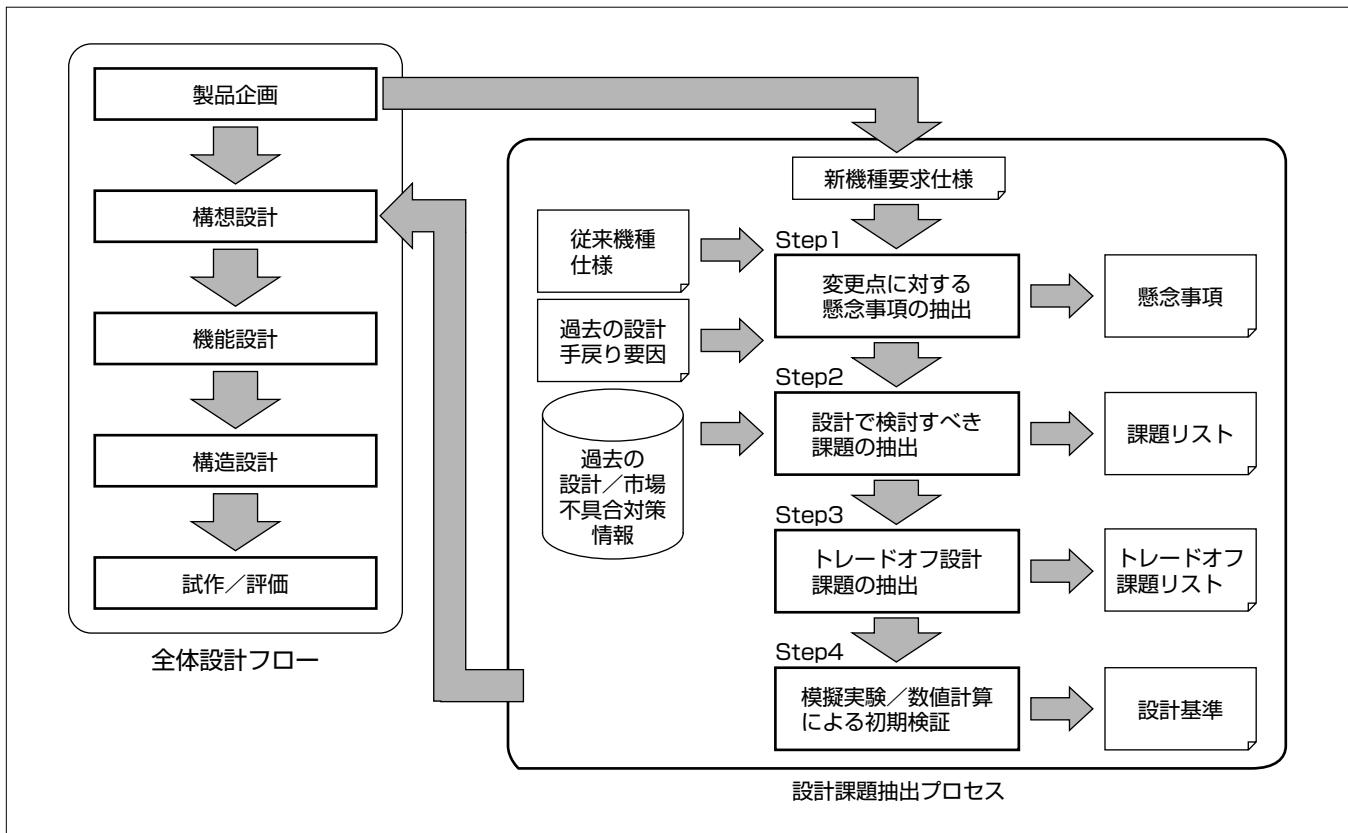

今回、構想設計段階で、設計課題の抽出とその初期検証の強化に取り組み、機能／構造設計段階での設計検証漏れや設計変更に伴う設計手戻りを抑制した(図1)<sup>(2)(3)</sup>。

本稿では、今回実施した構想設計段階における設計課題抽出プロセスと電子機器への適用効果について述べる。

図1. 設計手戻り抑制に向けた取組み

図2. 変更点に着目した設計課題抽出プロセス

## 2. 構想設計段階における課題抽出プロセスの構築

設計手戻りの多くは従来機種からの変更点に対する影響で発生していた。従来では、設計者によるブレーンストーミングで変更点に対する影響範囲を設計課題として抽出していたが、人の知識、経験に依存していたため、全ての設計課題を抽出することは困難であった。そこで、構想設計段階で、設計で検討すべき課題を漏れなく抽出するために、従来機種からの変更点に着目した標準的な設計課題抽出プロセスを構築した(図2)。具体的には次に示す4つのステップを構築した。次章で具体的な事例を述べる。

### Step 1：変更点に対する懸念事項の抽出

- ・従来機種と新しく開発する新機種の要求仕様に対する変更点を定義

- ・変更点と過去の設計手戻り要因を比較検討し懸念事項を抽出

### Step 2：設計で検討すべき課題の抽出

- ・懸念事項に対する優先度の設定

- ・優先度の高い懸念事項をキーワードに、過去の市場不具合対策、設計不具合対策、設計検討事例等を用いて変更に起因する設計課題を抽出

### Step 3：トレードオフ設計課題の抽出

Step 2で抽出した設計課題に対して、複数の設計技術分野で相互の関係を考慮しながら設計解を導出するトレードオフ設計が必要な課題を抽出

### Step 4：模擬実験／数値計算による初期検証

Step 2, Step 3で抽出した設計課題に対して、機能／構造設計前に初期検証

## 3. 変更影響分析技術を活用した課題抽出

機能／構造設計段階の設計手戻りを抑制するために、構想設計段階で、設計手戻り要因となる設計課題を網羅的に抽出し、検証すべき課題を設定する。

### 3.1 変更点に対する懸念事項の抽出

従来機種からの仕様変更点に対する懸念事項を網羅的に抽出するため、表1に示す“変更点－設計手戻り要因のマトリックス表”を構築した。表1では、縦軸に従来機種と新機種の仕様変更点と構成要素、横軸に過去の設計手戻り要因を示しています。

表1. 変更点－設計手戻り要因のマトリックス表

| 変更点に対する懸念事項 | 過去の設計手戻り要因 |      |    |    |     |

|-------------|------------|------|----|----|-----|

|             | 仕様         | 構成要素 | 温度 | 伝送 | ノイズ |

| 変更点         | 筐体         | ○    |    | ○  |     |

|             | 基板         | ○    | ○  | ○  |     |

|             | ：          |      |    |    |     |

| 高速化         | 筐体         |      |    |    |     |

|             | 基板         |      | ○  | ○  |     |

|             | ：          |      |    |    |     |

表2. 変更点に対する優先度評価表

| 変更点 | 手戻り要因 | 問題発生の確率 | 追加工数 | 根拠              | 優先度 <sup>(注)</sup> |

|-----|-------|---------|------|-----------------|--------------------|

| 小型化 | 筐体    | 温度      | 大    | 基板改定, 仕様変更に時間必要 | 高                  |

|     | 基板    | 温度      | 中    | 手戻り対策の検討実績あり    | 中                  |

|     | ⋮     | ⋮       | ⋮    | ⋮               | ⋮                  |

(注) 優先度の判断基準：問題発生の確率と追加工数の組合せで判断

- ・優先度高：過去に検討実績がなく初期検証すべき課題が抽出される可能性あり

- ・優先度中：過去に検討実績があり既に対策方針・基準の明確な課題が抽出される可能性あり

- ・優先度低：詳細設計段階で、数値計算によって設計検証する課題が抽出される可能性あり

り要因のマトリックスを構成している。

この表で変更点と過去の設計手戻り要因の関係を明確化することで、懸念事項の設定漏れを防止することができた。

表1の例では、小型化－筐体(きょうたい)の変更点に対して、温度、ノイズの懸念事項があり、伝送の懸念事項はないと判断している。

### 3.2 設計で検討すべき課題の抽出

懸念事項に対する優先度の設定と、設計で検討すべき課題の抽出を行う。

#### 3.2.1 懸念事項の優先度設定

設計で検討すべき課題を抽出するために、表2に示す“変更点に対する優先度評価表”を用いて、各懸念事項に対する優先度を設定した。この表では、問題発生の確率と設計手戻り発生時の追加工数を評価し、その組合せで優先度を決定する。優先度が高いほど、上流設計で対策が必要と判断し、優先度“中”以上を構想設計段階で検討すべき課題抽出の対象とする。

表2の例では、小型化－筐体－温度の懸念事項に対して、過去に設計手戻りがあったため問題発生の確率“大”，対策として筐体金型の再製作が想定されるため、追加工数“大”とし、優先度“高”とした。また、小型化－基板－温度の懸念事項に対しては、過去の設計検討実績があるため問題発生の確率“中”，追加工数“中”とし、優先度“中”とした。

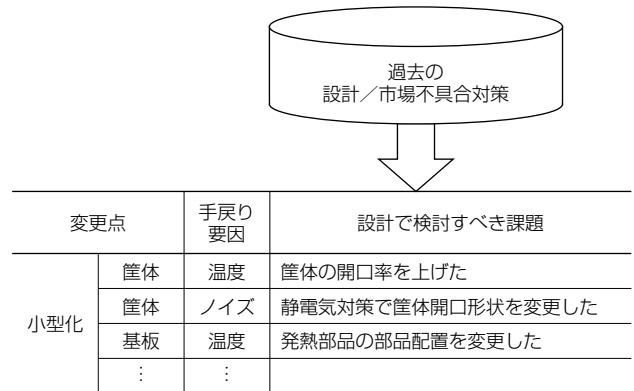

#### 3.2.2 設計で検討すべき課題の抽出

設計で検討すべき課題を漏れなく抽出するため、優先度の高い懸念事項をキーワードとして、過去の設計／市場不具合対策情報等を収集し、抽出された手戻り事例から検証すべき設計課題を設定した。

図3の例では、小型化－筐体－温度のキーワードに対して“筐体の開口率を上げた”，小型化－筐体－ノイズのキーワードに対して“静電気対策で筐体開口形状を変更した”的不具合対策事例があることから、設計で検討すべき課題とした。

図3. 設計で検討すべき課題の抽出

表3. 課題－技術分野マトリックス表

| トレードオフ設計課題 |        | 設計技術分野 |      |      |   |

|------------|--------|--------|------|------|---|

|            |        | 熱設計    | 電気設計 | 構造設計 | … |

| 設計で検討すべき課題 | 筐体の開口率 | ○      | ○    | ○    |   |

|            | 部品配置   | ○      | ○    |      |   |

|            | ⋮      | ⋮      | ⋮    | ⋮    | ⋮ |

### 3.3 トレードオフ設計課題の抽出

それぞれの設計技術分野で独自に設計課題に対する検討を進めた場合、検討結果がほかの設計技術分野に悪影響を及ぼし、後工程の設計手戻りにつながる可能性がある。

そこで、複数の設計技術分野間で影響範囲を確認しながら設計するトレードオフ設計が必要である。このトレードオフ設計の対象課題を事前に抽出するために、表3に示す“課題－技術分野マトリックス表”を構築した。この表では、縦軸を設計で検討すべき課題、横軸を設計技術分野のマトリックス構成として、関係技術分野のマッピングを行った。

表3の例では、図3で示した熱設計で“筐体の開口率を上げた”，ノイズ設計で“静電気対策で筐体開口形状を変更した”という“筐体開口率”に対する相反する不具合事例があったため、トレードオフ課題として構想設計段階で検証を実施し、設計条件を決定した。

## 4. 初期検証と効果

### 4.1 初期検証事例

3章で抽出した設計課題に対して、設計技術分野ごとに設計検証を実施した。また、設計技術分野間で調整が必要な設計課題については、トレードオフ設計検証を実施した。

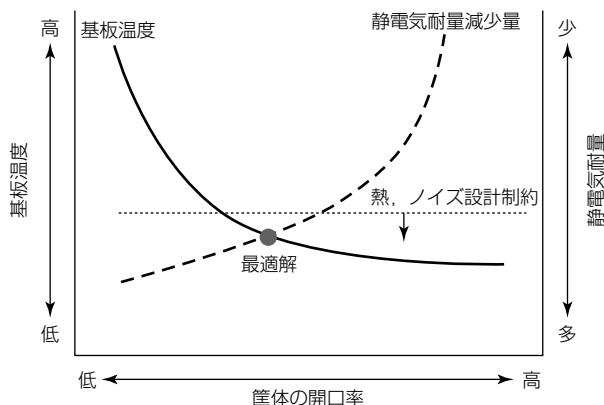

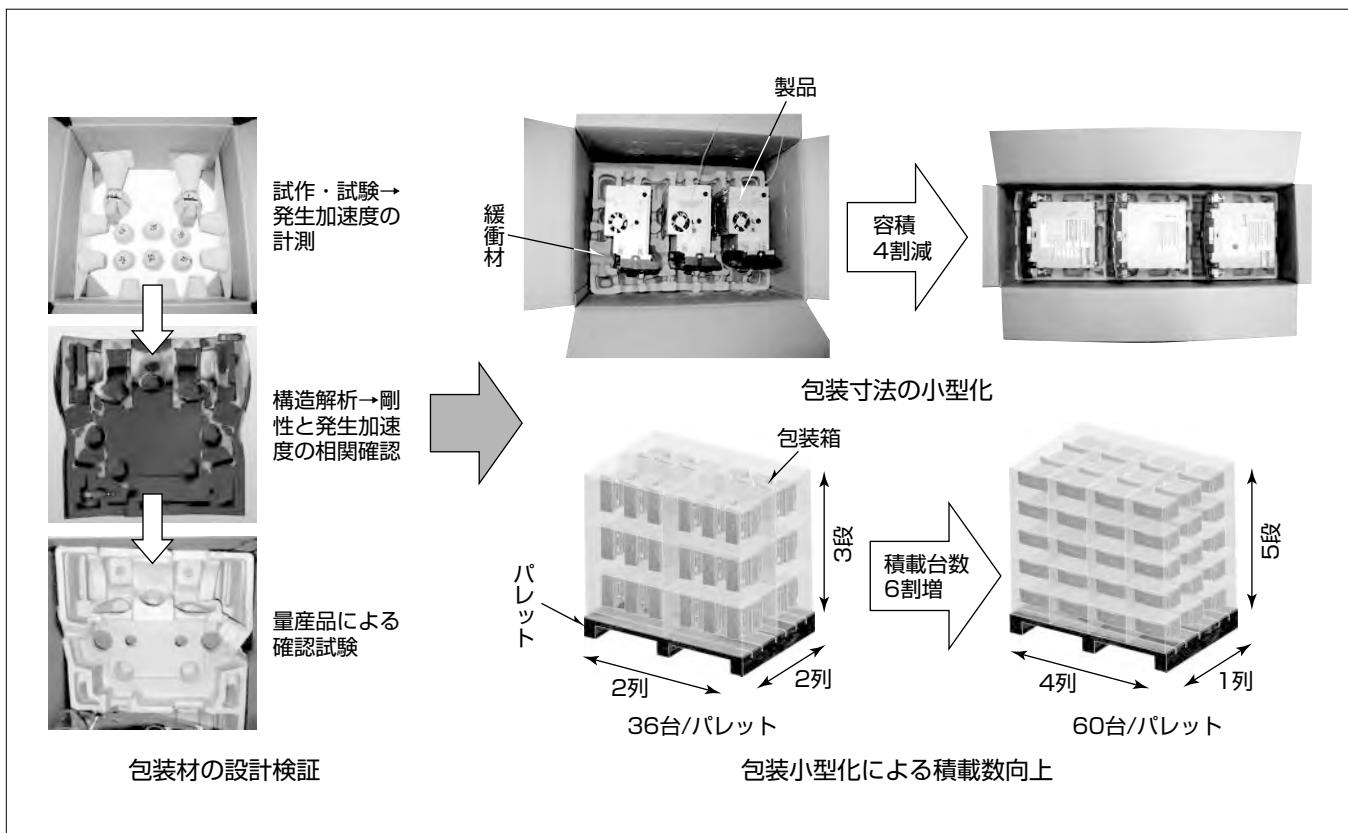

図4で示した“熱設計とノイズ設計のトレードオフ課題”では、熱設計制約から基板温度を下げる対策と、ノイズ設計制約から静電気耐量を上げる対策が、ともに筐体の開口率の調整であり、対策効果が相反するものであった。このトレードオフ設計課題を、構想設計段階で抽出することができたため、熱設計、ノイズ設計双方の制約が守れるよう模擬実験／数値計算による初期検証を行い、設計基準化した。