# ユニバーサルモデル高速タイプQCPUユニット

百目木栄悦\* 鈴木孝幸\*

High-speed Universal Model QCPU Unit

Eietsu Domeki, Takayuki Suzuki

## 要旨

製造業では多品種少量生産へのシフト、リードタイム短縮といった要求から、製造設備の高度化、複雑化が進んでいる。これらに柔軟に対応するため、2007年にシーケンサ"MELSEC-Qシリーズ"のCPUユニット"ユニバーサルモデルQCPU<sup>(1)</sup>"を市場へ投入し、その後もシーケンサのラインアップを拡充している。

更なる基本性能の向上、システム性能向上に対応するため、FA統合コンセプト"iQ Platform"対応製品の核となるシーケンサとして"ユニバーサルモデル高速タイプQCPU"を開発した。主な特長を次に示す。

### (1) 命令処理性能の向上

新規開発のシステムASIC (Application Specific Integrated Circuit) によって、従来のユニバーサルモデル QCPUから基本命令実行時間をおよそ 5 倍向上させ、データ処理能力を向上させた。

## (2) デバイス容量の拡大

内部デバイスを従来のユニバーサルモデルQCPUから最大 2 倍(60Kワード)に拡大した。また、拡張SRAMカセットを装着することで、最大4,736Kワードのファイルレジス

タを使用可能とした。これらによって、レシピデータや品 質管理データ等の増大に対応した。

# (3) 標準的なインタフェースの採用

標準でUSBインタフェース及びEthernet (注1)ポートを備えることで、パソコンや上位機器と連携するネットワークをより簡単に構築可能とした。また、MELSEC-QシリーズCPUユニットとしては初めてSDメモリカードスロットを備え、大容量のSDメモリカードを活用したデータロギング機能を搭載した。

- (4) セキュリティキーによるファイルアクセス制御機能 顧客のプログラムやパラメータを保護するため、セキュ リティキーによるファイルアクセス制御機能を搭載した。

- (5) 従来のユニバーサルモデルQCPUとの高い互換性

装置で使用しているMELSEC-Qシリーズのユニットは そのままで、CPUユニットだけをユニバーサルモデル高 速タイプQCPUに置き換え可能とした。また、既存のプロ ジェクトはPCタイプ変更を行うだけで流用可能である。

(注1) Ethernetは、富士ゼロックス㈱の登録商標である。

## ユニバーサルモデル高速タイプQCPUユニット

基本命令処理の性能向上やデバイス容量の拡大、SDメモリカードスロットの搭載、セキュリティ機能の強化を行った。

\*名古屋製作所 39(185)

# 1. まえがき

製造業では多品種少量生産へのシフト、リードタイム短縮といった要求から、より高速にデータを処理することでタクトタイムを短縮したい、よりきめ細かいデータ処理によって高精度の制御を行いたいといった要望が顧客からあがっている。シーケンサCPUユニットでは、高速演算、大容量データの処理能力向上といった、更なる基本性能の向上、システム性能向上によってこれらの要求に応える必要がある。

このような状況に対し、三菱電機ではMELSEC-QシリーズのCPUユニットであるユニバーサルモデルQCPUの更なる処理能力向上を目指し、ユニバーサルモデル高速タイプQCPUを開発した。

ユニバーサルモデル高速タイプQCPUでは、新規に開発したシステムASICを搭載することでLD命令1.9ns(従来比で基本命令処理性能 5 倍)、FOR/NEXT命令45ns(同19倍)を実現している。また、SDメモリカードスロットを搭載し、大容量のSDメモリカードを活用できるデータロギング機能を搭載した。さらに、顧客が開発した装置のプログラムやパラメータ等の設計資産を保護するため、セキュリティキーによるファイルアクセス制御機能を搭載した。

本稿では、これらユニバーサルモデル高速タイプQCPU の特長及び適用した技術について述べる。

## 2. 製品の特長

ユニバーサルモデル高速タイプQCPUの主な特長を次に 示す。

- (1) 命令処理性能の向上

- (2) デバイス容量の拡大

- (3) 標準的なインタフェースの採用

- (4) セキュリティキーによるファイルアクセス制御機能

- (5) 従来のユニバーサルモデルQCPUとの高い互換性

ユニバーサルモデル高速タイプQCPUは命令処理性能向上とデバイス容量拡大を行った。また、SDメモリカード/USB/Ethernetに対応したほか、セキュリティ機能の強化も行っている。さらに、従来のユニバーサルモデルQCPUと高い互換性を保ち、MELSEC-Qシリーズで構築した既設システムで、CPUユニットだけの置き換えを可能としている。

# 2.1 命令処理性能の向上

ユニバーサルモデル高速タイプQCPUでは、装置のタクトタイム短縮や加工精度向上のため、命令実行時間の短縮と、定周期割り込みプログラム最小実行間隔の短縮を行った。

# (1) 命令実行時間の短縮

主な基本命令について、ユニバーサルモデル高速タイプ QCPUの命令実行時間を**表1**に示す。 基本命令の実行時間短縮によって、PC MIX値で約220 (命令数/µs)を達成し、従来のユニバーサルモデルQCPU からは約3.7倍高速化している。また、FB(Function Block) やST(Structured Text)によるプログラムの構造化及び再利用の促進に向けて、繰り返し命令やサブルーチンコールといった命令を高速化した。

### (2) 定周期割り込みプログラム最小実行間隔の短縮

定周期割り込みプログラムの最小実行間隔を、従来のユニバーサルモデルQCPUの $500\mu s$ から、ユニバーサルモデル高速タイプQCPUでは $100\mu s$ に短縮した。これによって、従来よりもきめ細かい制御が可能となり、装置の加工精度向上が行える。

## 2.2 デバイス容量の拡大

ユニバーサルモデル高速タイプQCPUでは、デバイス容量を拡大することで、レシピデータや品質管理データ等の増大に対応している。

従来のユニバーサルモデルQCPUで29Kワードであった内部デバイスを、ユニバーサルモデル高速タイプQCPUでは最大60Kワードに拡大した。また、拡張SRAMカセット(1 Mバイト、2 Mバイト、4 Mバイト、8 Mバイトから選択可能)を装着することで本体の標準RAMを拡張して、最大4,736Kワードのファイルレジスタを確保することができる。

従来のユニバーサルモデルQCPUでは標準RAMとSRAMカードが別のドライブであり、容量拡大のためファイルレジスタの格納先を標準RAMからSRAMカードに変更する場合には、プログラムやパラメータで指定しているドライブを変更する必要があった。また、標準RAMとSRAMカードを同時に使用するためにはプログラム中でドライブを切り換える必要があった。ユニバーサルモデル高速タイプQCPUでは拡張SRAMカセットによって標準RAMを拡張する形としたことで、ファイルレジスタの容量拡大に伴うドライブの変更が不要となった。また、ファイルレジスタは32ビットインデックス修飾を使用することで、連続領域としてアクセスできる。そのため、プログラム中でのドライブ切り換えが不要となった。

# 2.3 標準的なインタフェースの採用

ユニバーサルモデル高速タイプQCPUでは、SDメモリカードスロットを搭載することで、より大容量のデータの

表1. 主な基本命令の実行時間

| 命令種別         | 対象命令         | 高速タイプ  | ユニバーサルモデル |

|--------------|--------------|--------|-----------|

| 接点命令         | LD X0        | 1.9ns  | 9.5ns     |

| ビット出力命令      | OUT Y0       | 3.9ns  | 9.5ns     |

| データ転送命令      | MOV D0 D1    | 3.9ns  | 19.0ns    |

| 浮動小数点演算      | E+ D0 D2     | 13.0ns | 57.0ns    |

| 繰返し命令(10ループ) | FOR K10~NEXT | 0.45µs | 8.9µs     |

| サブルーチンコール    | CALL~RET     | 1.10µs | 3.9µs     |

取扱いを可能とした。また、Ethernetポート内蔵QCPUと同様にUSB、Ethernetポートを搭載した。

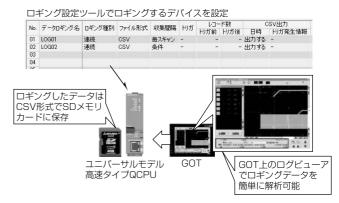

SDメモリカードは、プログラム・デバイスデータのバックアップ/リストア、ブート運転、データロギング機能に使用できる。このうち、データロギング機能については、"MELSEC-Lシリーズ"CPUユニットのデータロギング機能と同等の機能を実現しており、収集したロギングデータを専用のビューアやGOT(Graphic Operation Terminal)を用いることで簡単に解析できるうえ、保存フォーマットもCSV(Comma Separated Values)形式のテキストデータであることから市販の表計算ソフトウェアなどでの活用も容易である(図1)。これによって、メンテナンス工数の削減や品質管理データの収集、迅速なトラブルシューティングが可能である。

また、EthernetポートはプログラミングツールやGOTとの接続で使用する"MELSOFT接続"に加え、"MC(MELSEC Communication) プロトコル"によるデバイスデータの読み書きや、TCP/IP(Transmission Control Protocol/Internet Protocol)とUDP/IP(User Datagram Protocol/Internet Protocol)の通信プログラムに対応しており、Ethernetによる上位通信やメンテナンス用途の通信に活用できる。

## 2.4 セキュリティキーによるファイルアクセス制御機能

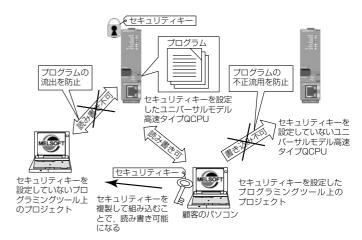

ユニバーサルモデル高速タイプQCPUでは、プログラムやパラメータ、デバイスコメントといった顧客の設計資産からのノウハウ流出やプログラムの不正流用を防止するため、セキュリティキーによるファイルアクセス制御機能を搭載した。

この機能は、プログラミングツールで生成したセキュリティキーをCPUユニットとプロジェクトに設定しておきアクセス時に照合することで、一致しない場合はCPUユニット内のファイル読み書きを制限する機能である。図2に示すように、セキュリティキーを設定していないプログラミングツール上のプロジェクトから、セキュリティキーを設定したCPUユニットに対するファイルの読み書きができない。また、プログラミングツール上のプロジェクトにセキュリティキーを設定している場合でもCPUユニットにセキュリティキーが設定されていなければファイルの書き込みはできない。

また、複数のプログラミングツール上からセキュリティキーを設定したCPUユニットに対するアクセスができるようセキュリティキーの複製を可能とした。セキュリティキーの複製管理については**3.3節**で詳細を述べる。

## 2.5 従来のユニバーサルモデルQCPUとの高い互換性

ユニバーサルモデル高速タイプQCPUは、MELSEC-QシリーズCPUユニットの最上位機種として、従来のユニバーサルモデルQCPUと高い互換性を確保している。

図1. データロギング機能の活用

図2. セキュリティキーによるファイルアクセス制御

MELSEC-Qシリーズのユニットはそのまま使用可能(一部バージョンアップが必要)であり、iQ Platform対応ユニットとのマルチCPU構成でも既設のユニバーサルモデルQCPUを置き換え可能とした。

また、既にあるユニバーサルモデルQCPU用プロジェクトデータのPCタイプを変更することで、ユニバーサルモデル高速タイプQCPU用プロジェクトデータを作成することができる。

そのため、CPUユニットだけを既存のユニバーサルモデルQCPUからユニバーサルモデル高速タイプQCPUに置き換えることによる装置・設備の高速化が可能である。

# 3. 実現のための技術

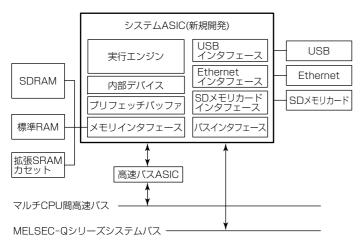

ユニバーサルモデル高速タイプQCPUで、特長の実現にあたり開発した技術について述べる。ユニバーサルモデル高速タイプQCPUでは新規にシステムASICを開発した。システムASIC及びハードウェアのブロック図を図3に示す。

システムASICでは更なる命令実行の高速化に向けて実行エンジンを高速化し、メモリアクセスを効率化した。また、ユニバーサルモデル高速タイプQCPUで搭載する標準インタフェースやバスインタフェースをIP(Intellectual

図3.システムASIC及びハードウェアのブロック図

Property) 部品として組み込むことで製品の部品点数を削減した。

また,安全性を確保しつつ利便性を備えたセキュリティ キーの管理方法を開発している。

特長の実現にあたり開発した技術を次にあげる。

- (1) 実行エンジンの高速化

- (2) メモリアクセスの効率化

- (3) セキュリティキー管理

- (4) 従来のユニバーサルモデルQCPUとの互換性確保

## 3.1 実行エンジンの高速化

新規開発のシステムASICでは、シーケンス命令を実行する実行エンジンのパイプライン構成の見直しや動作周波数の向上を行った。また、使用頻度の高いシーケンス命令については基本命令を組み合わせて直接実行エンジン上で処理することで高速化を図った。

さらに、サブルーチンコール命令など個別の命令についても処理内容を最適化して性能向上を図った。

### 3.2 メモリアクセスの効率化

命令実行時間の短縮にあたり、ASIC外部のSDRAMに 配置したプログラムを実行する場合に、プリフェッチによ るアクセス手法を採用した。これは、あらかじめまとまっ たサイズのプログラムをSDRAMからASIC内部のプリ フェッチバッファに読み込み、プリフェッチバッファ上で 実行する手法である。この手法によってSDRAMアクセス を効率化することで、プログラム実行性能向上を達成して いる。

また、システムASICの外部にある標準RAMや拡張 SRAMカセットに対するアクセスでは、実行エンジンか らキャッシュを介してアクセスする設計とした。これに よって、実行エンジンからのアクセス時の遅延を最小限と し、デバイスアクセスを効率化することで性能向上を実現 した。

## 3.3 セキュリティキー管理

**2.4節**で述べたように、ファイルアクセス制御機能の実現でセキュリティキーを用いた。

セキュリティキーの実現にあたり、安全性確保のために セキュリティキーをグローバルに一意とする一方で、利便 性確保のためセキュリティキーの複製を可能とした。これ によってプログラミングツールで生成したセキュリティキ ーを複製し、他のパソコンへ配布することで、そのパソコ ンからセキュリティキーを設定したCPUユニットに対す るアクセスが可能となる。

セキュリティキーの複製では、無制限にセキュリティキーが複製されることを避けるため、一度複製したセキュリティキーからの複製は不可能な設計を行った。また、複製されたセキュリティキーの盗難や紛失に対する対策として、複製されたセキュリティキーが他のパソコンに配布されるまでの有効期限を設定必須とした。同様に盗難や紛失に備え複製されたセキュリティキーに対するパスワードも設定必須とした。

このように、安全性を確保しつつ、利便性を備えたセ キュリティキーを実現している。

# 3.4 従来のユニバーサルモデルQCPUとの互換性確保

新規開発のシステムASICでは実行エンジンアーキテクチャを一新しているが、実際に実行する命令及びパラメータは従来のユニバーサルモデルQCPUと互換を保っている。さらに、既存の開発プロジェクトを流用する際、パラメータやプログラム変換をPCタイプ変更で実施することで、従来のユニバーサルモデルQCPUのプロジェクトから、ユニバーサルモデル高速タイプQCPUのプロジェクトを作成することを可能とした。

# 4. む す び

MELSEC-Qシリーズのユニバーサルモデル高速タイプ QCPUの特長とそれらを実現するために用いた技術について述べた。ユニバーサルモデル高速タイプ QCPUの開発によって、より高速で高精度の装置開発を可能とした。今後も、シーケンサ CPUの高速化、高機能化、及び利便性の向上を追求していく。

### 参考文献

(1) 石田 浩, ほか:高速シーケンサ"QnUシリーズ", 三菱電機技報, **81**, No.4, 249~252 (2007)