# インバータシステム用1,200V HVIC技術

吉野 清水和宏\*

1,200V HVIC Technology for Power Inverter System

Manabu Yoshino, Kazuhiro Shimizu

#### 要旨

産業、民生機器のインバータ駆動に普及しているIPM (Intelligent Power Module)で、HVIC(High Voltage Integrated Circuit)はパワーチップのゲート駆動や保護の 機能を果たすキーデバイスである。特にAC400V系電源を 使用する市場では1,200V HVICに対する需要がある。しか し1.000V以上のHVICを実現するためには、ハイサイド領 域の高電圧引き出し配線とローサイド領域のオーバーラッ プを回避する必要がある。そのため1,200V HVICは構造や プロセスが600V HVICと比べて複雑, 高コストとなり, 製品化が困難であった。

三菱電機では1997年に独自技術である"分割リサーフ構 造"の開発によって、この課題を克服し1,200V HVICを製 品化した。さらに2008年には第1世代の分割リサーフ構造 に微細加工技術を導入した第2世代型分割リサーフ構造を 600Vクラスにおいて開発し、600V HVICを製品化している。

今回当社は,独自のフィールドプレート技術を改善して この第2世代型分割リサーフ構造を1,200Vへ高耐圧化し、 1,200V HVICへの展開を可能にした。開発した1,200V HVICは第2世代型分割リサーフ構造を適用することで容 易に高耐圧化を実現し,次の特長を持っている。

- (1) 600V HVICと同一のプロセスステップでの高耐圧化 によるプロセスの低コスト化

- (2) 8V/24V系素子を600V HVICと同等の電気的特性に 維持することによる設計効率の向上

これらの特長によって、今後600V HVIC品種の回路流 用による1.200V HVICの効率的な品種展開が期待できる。

NchMOS: Negative channel Metal Oxide Semiconductor

第2世代型分割リサーフ構造を高耐圧化した1,200V HVIC

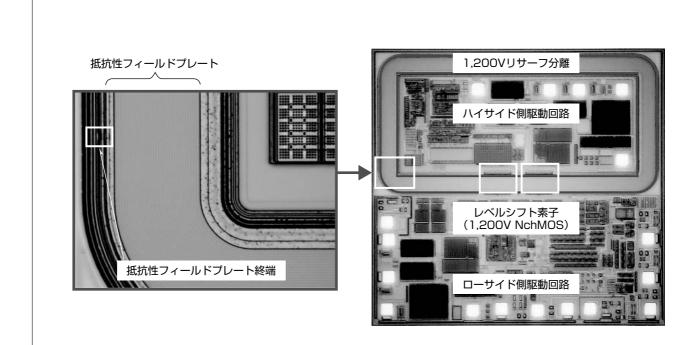

第2世代型分割リサーフ構造を適用することで600V HVICと同一のプロセスステップで1,200V HVICを実現した。高耐圧化は主にレイア ウトによって実施しており,今回フィールドプレート構造として従来の多重フィールドプレートから抵抗性フィールドプレートを新たに採用し

\*パワーデバイス製作所 11(271)

## 1. まえがき

ゲートドライバHVICはハイサイド側のパワーチップを 駆動するために高耐圧のフローティング回路とそのフロー ティング回路へ制御信号を伝達するためレベルシフト機能 を備えている。AC200V系電源を使用する市場では600V HVICが、AC400V系電源を使用する市場では1,200V HVICが必要とされる。600V HVICは既に広く製品化され ている。一方、1,200V HVICについてはIC内部の配線で層 間絶縁膜による1,000V以上の絶縁が困難なため、レベルシ フトされた高電圧の引き出し配線がローサイド領域上を横 断することを避ける必要があり、そのことが製品化の障壁 となっていた。当社は独自技術である"分割リサーフ構造" の開発によってこの課題を解決し1,200V HVICを実現した (第1世代型分割リサーフ構造)。しかしながらこの第1世 代型分割リサーフ構造は深いN型拡散層を基本構造として おり、縦方向の寄生PNP動作を起こしやすく、それを抑 えるためにレイアウト設計の自由度に制約があった。また, 基本構造が600V HVICと異なるため回路設計で600V HVICの回路流用ができないという課題もあった。

近年,第1世代型分割リサーフ構造の寄生PNPトランジスタの動作を解決する構造として,第2世代型分割リサーフ構造が600Vクラスで開発され,品種展開されている。今回,この第2世代型分割リサーフ構造の耐圧クラスを600Vから1,200Vまで高耐圧化し,第1世代の課題を克服した1,200V HVICを開発した。本稿では1,200V高耐圧化の技術について述べる。

## 2. 1,200V高耐圧化技術

### 2.1 第2世代型分割リサーフ構造高耐圧化

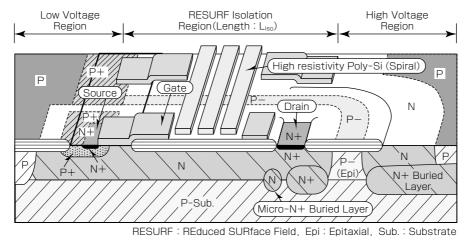

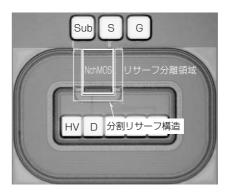

図1に1,200Vに高耐圧化した第2世代型分割リサーフ構造の断面図を示す。ハイサイド側でPエピタキシャル層がN型拡散層を分離している分割部領域は600V HVICと同一

構造のままリサーフ分離領域を高耐圧化している。リサーフ分離領域の高耐圧化は①P型基板/Pエピタキシャル層の高抵抗化、②リサーフ分離距離(Liso)の拡張、③フィールドプレート構造の最適化によって行っており、600VHVICに対して基本構造は同じである。また、P型基板/Pエピタキシャル層の高抵抗化はウェーハ仕様の変更、リサーフ分離距離の拡張及びフィールドプレート構造の最適化はパターンレイアウトの変更であるため、プロセスステップについても600VHVICと同一である。

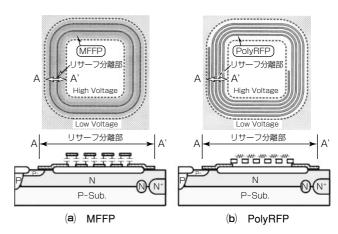

フィールドプレート構造はリサーフ分離領域の表面電位をより安定化させるため、従来の多重フィールドプレート (Multiple Floating Field Plate: MFFP)から抵抗性フィールドプレート (Polycrystalline silicon Resistor Field Plate: PolyRFP)を新規に採用しその構造最適化を行った。

図2にMFFPとPolyRFPの模式図を示す。従来のMFFPは容量の直列結合によって表面電位を安定化させているが、直列結合途中の電極が浮遊状態であるため電位に不均一性が生じてしまう。一方、PolyRFPは高抵抗のポリシリコンを高圧側から低圧側までリサーフ分離表面を渦巻状に配置し、抵抗分割によって表面電位を固定しているためMFFPと比べ安定した表面電位が得られる。特に高耐圧化ではフィールドプレートで覆われるリサーフ分離領域が広くなる

図2. フィールドプレート構造

図1.1,200V高耐圧化第2世代型分割リサーフ構造

ため, その表面電位の安定化効果がより期待できる。

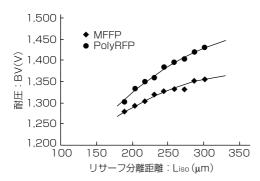

図3にMFFPとPolyRFPにおけるダイオード構造の耐圧-リサーフ分離距離依存性を示す。フィールドプレート構造をPolyRFPにすることでMFFPよりも高耐圧が得られることが分かる。

## 2.2 抵抗性フィールドプレート構造検証

PolyRFPは図2(b)のようにリサーフ分離領域と並列に高抵抗が接続される構造となっている。そのため高電圧が印加された際に従来のMFFPと異なり抵抗成分リークが発生する。また、高抵抗の引き回しによる過渡的特性への影響が懸念される。ここではPolyRFPにおける懸念点の検証について述べる。

#### 2.2.1 フィールドプレート形状最適化

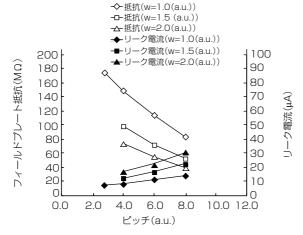

抵抗成分リークは抵抗幅,渦巻のピッチ,ハイサイド領域のサイズによって決まる。図4に1,200V印加時抵抗成分リークの抵抗幅,ピッチ依存性を示す。ハイサイド領域のサイズはその中の回路規模によって変わるため,最も条件として厳しい最小サイズのハイサイド領域で評価した。抵抗幅,ピッチは誤動作防止のため回路に求められるリーク電流10μΑ以下を目標値として設定している。

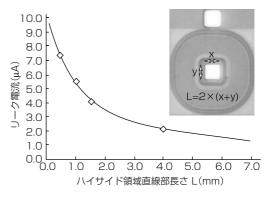

図5に上記で設定した抵抗幅,ピッチにおける抵抗成分 リークのハイサイド領域サイズ依存性を示す。抵抗成分リ ークはハイサイド領域の外周Lに反比例して低下する。製

図3. 耐圧のリサーフ分離距離依存性

図 4. 抵抗成分リークの抵抗幅,ピッチ依存性(V=1,200V印加時)

品ではハイサイド領域内に制御回路や複数のパッドが配置 されるため、抵抗成分リークは2µA以下まで抑えられる。

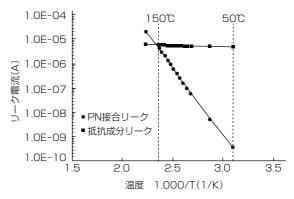

#### 2.2.2 リーク電流温度依存性

リーク電流はPolyRFPの抵抗成分リークとリサーフ分離 領域のPN接合リークからなる。図6に最小のハイサイド領 域サイズのときの抵抗成分リークとPN接合リークの温度依 存性を示す。温度T,活性化エネルギーE,ボルツマン定数 kとするとキャリア数はexp(-E/kT)に比例するため、リー ク電流は温度上昇に伴い指数関数的に増加し、その係数は 活性化エネルギーに依存する。図6から温度依存性は抵抗 成分リークよりPN接合リークの方が高く、リーク電流の増 加する高温ではPN接合リークが支配的となることが分かる。

また、ハイサイド領域面積が大きくなるとPN接合面積に比例してPN接合リークは増加するため、高温におけるリーク電流は回路規模ごとに異なるハイサイド領域サイズに依存してPN接合リークによって決まる。そのため低温では支配的な抵抗成分リークの温度依存性が問題となることはない。

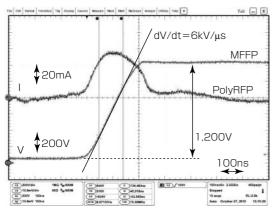

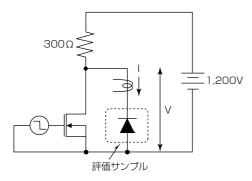

#### 2.2.3 過渡的特性検証

図7にPolyRFPのスイッチング特性を示す。ゲートドライバとして通常使用されるdV/dt=6kV/μsのスイッチングで従来のMFFPと同等のスイッチング特性が得られており、高抵抗の引き回しによる過渡的特性に問題ないことを確認した。

図 5. 抵抗成分リークのハイサイド領域サイズ依存性(V=1,200V印加時)

図 6. リーク電流の温度依存性(V=1,200V印加時)

1: 電流 V: 電圧

図7. PolyRFPのスイッチング特性と測定回路

## 3. 1,200V NchMOS特性

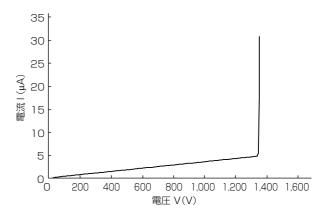

図8に第2世代型分割リサーフ構造を適用し試作した1,200V NchMOSを、図9に試作した1,200V NchMOSの耐圧測定結果を示す。高耐圧化したリサーフ分離を分割リサーフ構造に適用しても耐圧の低下は起こらず、1,200V NchMOSを実現している。ここで、ブレークダウン前のリーク電流がPolyRFPによる抵抗成分リークである。

#### 4. む す び

第2世代型分割リサーフ構造を適用しリサーフ分離領域を高耐圧化することによって、600V HVICと同一のプロセスステップで1,200V HVICを実現した。基本構造及びプロセスステップを600V HVICと同一のまま高耐圧化することで、第1世代型分割リサーフ構造で課題となっていた600V HVICとの回路流用が可能となり、今後1,200V HVICの品種展開が期待される。

図 8. 1,200V NchMOS

図 9. 1,200V NchMOSの耐圧波形

## 参考文献

- (1) Terashima, T., et al.: A new Level-shifting Technique by divided RESURF structure, Proc. ISPSD, 57~60 (1997)

- (2) Shimizu, K., et al.: The 2nd Generation divided RESURF structure for High Voltage ICs, Proc. ISPSD, 311~314 (2008)

- (3) Terashima, T., et al.: Structure of 600V IC and A New Voltage Sensing Device, Proc. ISPSD, 224~ 229 (1993)

- (4) Endo, K., et al.: A 500V 1A 1-Chip Inverter IC with a New Electric Field Reduction Structure, Proc. ISPSD, 379~383 (1994)