# 巻頭論文

山下昭裕\*

前川隆昭\*\*

# 設計プロセス革新による開発効率化

Promotion of Development Efficiency by Design Process Innovation

Akihiro Yamashita, Takaaki Maekawa

# 要旨

製造業では、グローバル市場での性能/価格両面での製品力強化のため、開発プロセス革新によるQCD(Quality Cost Delivery)向上が喫緊の課題となっている。特に、製品企画から製造、販売にわたるものづくりプロセスで最上流にある設計工程の効率化、品質作り込みが重要である。

これまで三菱電機では、設計プロセス革新による開発効率化のための取組みとして、ソフトウェア開発、ASIC (Application Specific Integrated Circuit) 開発、ハードウェア開発で、開発上流段階での設計品質を作り込む"設計フロントローディング"を推進してきた。

本稿では、当社の"設計フロントローディング"推進活動 で活用してきた次の手法と、その適用事例について述べる。 (1) ソフトウェア開発:ゾーン分析によるプロジェクト計 画改善手法、フレームワークによる再利用手法、仕様書 テンプレート活用によるデザインレビュー強化手法

- (2) ASIC開発:UML<sup>(注1)</sup>活用による仕様見える化手法, デジタル/アナログHDL<sup>(注2)</sup>活用による機能検証手法, 検証環境の再利用手法

- (3) ハードウェア開発:インタフェース共通化,変更影響 度分析による課題抽出手法,可視化実験と解析シミュレ ーションを活用した熱設計検証手法,品質工学を活用し た強度・振動試験条件の適正化手法,三次元モデルを活 用した組立性検証手法

- (注1) UML(Unified Modeling Language)は, Object Management Group Inc.の登録商標である。

- 注2) HDL(Hardware Description Language)は、デジタル回路 の振る舞いを記述するためのプログラム言語で、アナログ HDLはアナログ・デジタル混在回路に拡張したものである。

### 設計プロセス革新のねらいと手法

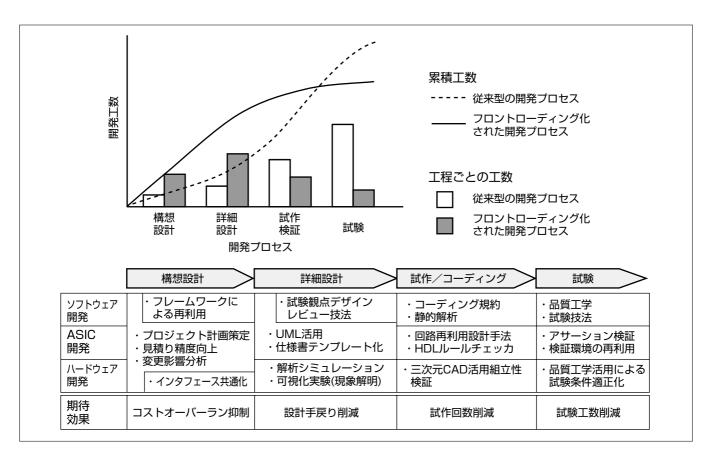

設計フロントローディングによる開発プロセス革新のねらいと、各工程におけるプロセス改善手法と期待効果を示す。各工程でこれらの手法を適用することで、開発上流段階での工数は増加するが、後工程での試作検証工数と試験工数を大幅に削減できるため、開発プロセス全体での累積工数は減少する。

する。

# 1. まえがき

製造業としてグローバル市場への事業拡大戦略に対応する性能,価格両面での製品力強化のため,設計プロセス革新によるQCD向上が喫緊の課題となっている。特に,製品企画から製造,販売にわたるものづくりプロセスで最上流にある設計工程は,開発プロセス全体の効率,品質,コストに多大な影響を与える。

当社では、開発プロセスの各工程における業務改善施策として、開発初期段階での設計品質の作り込みを実現する "設計フロントローディング"を推進してきた(1)。 さらに、これまで培ってきた設計フロントローディング手法を体系的に整備し、開発プロセス改善手法として深掘り、進化させることによって、多岐にわたる当社製品への適用加速、展開を図ってきた。その結果、多くの製品で開発手戻り削減、試作回数/試験工数削減、コストオーバーラン抑制などの効果を実現し、製品開発全体での累積開発工数削減によって、製品開発コスト削減と早期市場投入が可能となった。

本稿では、当社における設計プロセス革新の取組みについて、ソフトウェア/ASIC/ハードウェア設計分野における開発プロセス改善のための手法とその実践例について述べる。

# 2. 設計フロントローディングによる開発プロセス改善

### 2.1 概 要

図1に,設計フロントローディングによる開発プロセス 改善の主要効果である開発工数削減効果を示す。工程ごと の工数は開発上流段階では増加するが,後工程での手戻り による試作検証工数,試験工数が大幅に削減できるため, 開発全体での累積工数は減少する。

図2は、設計フロントローディングを実現するため当社 で活用している代表的手法と期待効果を、開発対象(ソフトウェア、ASIC、ハードウェア)と、適用する工程に分類 して示したものである。

図1. 設計フロントローディングによる開発効率化

#### 2.2 ソフトウェア開発プロセスの改善手法

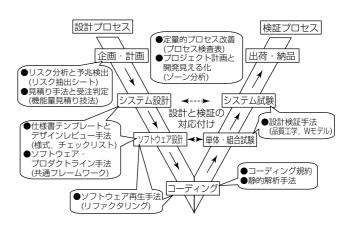

図3は、ソフトウェア開発プロセスの各工程と試験工程の関係を表すV字モデルと、工程ごとの代表的な改善手法を示したものである。

特にソフトウェア開発では、開発各工程での不具合検出数によって、"設計フロントローディング率(設計FL率)"(注3)を算出し、プロセス改善の度合いを評価する指標としている。当社の製品の特性に応じた設計FL率の目標値を設定し、ソフトウェア開発プロセス改善活動を展開中である。

次にソフトウェア設計分野でのプロセス改善の主な手法 について述べる。

(1) ゾーン分析によるプロジェクト計画改善手法

過去の同種の開発プロジェクトを、開発コスト・開発規模などの観点で分類し、計画と実績の乖離(かいり)度を分析する(ゾーン分析)ことで、対象システムの特性に合ったプロジェクト管理を実施する。

(2) ソフトウェアフレームワーク化による再利用手法 シリーズ機種など類似製品に搭載するソフトウェア開発 で、ソフトウェア構造を分析し、共通部と機種依存部に分 類して部品化、機能単位で階層化するなど、全体構造を再 構築(フレームワーク化)することによって、再利用を促進

(3) 仕様書テンプレート,チェックリスト活用によるデザインレビュー強化手法

(注3) 設計フロントローディング率=設計上流での不具合検出数 ÷ 開発全体での不具合検出数

|              | 構想設計                                          | 詳細設計                                         | 試作/コーディング                                 | 試験                                          |

|--------------|-----------------------------------------------|----------------------------------------------|-------------------------------------------|---------------------------------------------|

| ソフトウェア<br>開発 | ・フレームワークに<br>よる再利用                            | ・試験観点デザイン<br>レビュー技法                          | <ul><li>・コーディング規約</li><li>・静的解析</li></ul> | · 品質工学<br>· 試験技法                            |

| ASIC<br>開発   | ・プロジェクト計画策定<br>・見積り精度向上                       | <ul><li>・UML活用</li><li>・仕様書テンプレート化</li></ul> | ・回路再利用設計手法<br>・HDLルールチェッカ                 | <ul><li>アサーション検証</li><li>検証環境の再利用</li></ul> |

| ハードウェア<br>開発 | <ul><li>・変更影響分析</li><li>・インタフェース共通化</li></ul> | ・解析シミュレーション<br>・可視化実験(現象解明)                  | ・三次元CAD活用<br>組立性検証                        | ・ 品質工学活用による<br>試験条件適正化                      |

| 期待<br>効果     | コストオーバーラン抑制                                   | 設計手戻り削減                                      | 試作回数削減                                    | 試験工数削減                                      |

図2. 設計フロントローディング手法

図3. ソフトウェア開発プロセスの改善手法

作成者に依存しがちな仕様書の記載内容をテンプレート 化することで、仕様書の均質化、質的向上を図るとともに、 仕様書記載内容にリンクしたチェックリストを作成、デザ インレビューに活用することで、設計品質を向上させる。

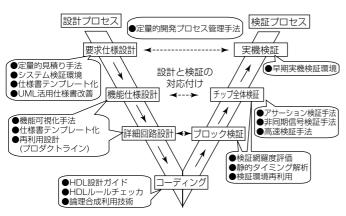

### 2.3 ASIC開発プロセスの改善手法

図4にソフトウェアと同様のV字モデルで、代表的なASIC開発プロセス改善手法を示す。ソフトウェア設計分野での開発プロセス改善手法はデジタル回路設計にも適用され、大規模デジタルASIC開発で初回サンプルでの品質確保に効果を上げている。さらに当社では、電子機器製品差別化のキーパーツとなっているアナログASICの開発プロセス改善に取り組んでいる。

次にデジタル/アナログASIC設計分野でのプロセス改善の主な手法について述べる。

# (1) UMLによる機能可視化とアサーション検証手法(注4)

ソフトウェア開発で活用されているUMLを仕様設計に活用(ユースケース図による機能範囲の明確化,クラス図による機能実現手段の明確化など)することで検証すべき機能を抽出する。さらに、抽出された機能に対して、アサーション検証手法を適用して、機能検証漏れを防止する。

#### (2) アナログHDL活用による機能検証手法

アナログASIC開発で、アナログHDLを活用した機能ブロック単位での検証、アナログHDLとSPICE(注5)シミュレータの併用による大規模全体回路の高速検証などを実施し、初期段階での機能検証を徹底する。

# (3) 検証環境の再利用手法

大規模デジタルASICの検証環境構築において、検証機能を、テストプログラム(試験の手続を記述)、トランザクタ(手続が意図する機能動作を信号動作へ変換)、ドライバ(試験対象に信号値を出力)として部品化、再利用を容易にすることで、検証工数を削減するとともに検証の精度向上を図る。

- (注4) 仕様を検証用言語で記述して,回路記述との等価性を論理 的・数理的に検証する手法

- (注5) 電子回路のアナログ動作をシミュレーションするソフトウェア

図4. ASIC開発プロセスの改善手法

#### 2.4 ハードウェア開発プロセスの改善手法

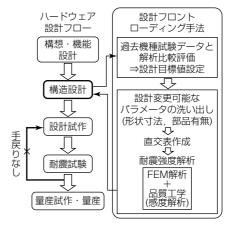

図5は、ハードウェア設計における開発プロセス改善手法(品質工学を活用した耐震強度設計の例)を示したものである。対象製品の重要課題に対応したモデル実験手法とシミュレーション解析技術を構築・強化することで、設計試作前段階における設計品質の作り込みが可能となり、開発後工程での手戻り削減が図れる。

次にハードウェア設計分野でのプロセス改善の主な手法 について述べる。

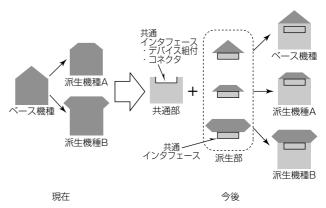

#### (1) インタフェース共通化による派生機種開発

図6はシリーズ開発型製品(能力,容量,サイズなどによる機種系列を持つ製品)の派生機種開発の考え方を示したものである。開発構想段階で,共通部と機種依存部とそのインタフェースを共通化することで,ベース機種開発から派生機種展開発を効率的に進めることが可能となる。

#### (2) 変更影響度分析による課題抽出手法

開発初期段階で、過去機種からの仕様の変更点を明確化し、設計基準・試験規格・過去不具合情報などからその影響範囲を特定することで、開発全般にわたっての課題を抽出する。抽出された課題に対して評価計画を立案、開発各工程で未完了課題項目を一元管理することで早期課題解決を図る。

FEM : Finite Element Method

図5. ハードウェア開発プロセスの改善手法 (品質工学を活用した耐震強度設計の例)

図6. ハードウェア開発における派生機種展開の効率化

(3) オーダーレベル計算/解析シミュレーションを活用した熱設計検証手法

製品の基本性能を決定する機能設計で、表計算ワークシートを活用したオーダーレベル検討(First Order Analysis:FOA)によって、適切な設計の見極めを実施する。さらに、部品配置、冷却風路などを決定する基本設計段階で、三次元形状による熱流体シミュレーションによって温度・流れを精度よく予測・検討することで、早期に熱対策を実施する。

(4) 品質工学を活用した強度・振動解析検証,試験条件適 正化手法

構造設計で、構造強度解析に品質工学を組み合わせて、 直交表による効率的な解析パターンの絞り込みと、感度解 析による各設計パラメータの影響度を評価、適正な強度・ 振動試験条件を設定することで、設計手戻りや過剰設計に よるコスト増を抑制する。

(5) 三次元モデルを活用した組立性検証手法

組立性の検証,デザインレビューに三次元CADデータを活用することで,構造設計段階で組立性課題の抽出,改善検討を実施し,製造準備段階での設計手戻り削減と組立性改善を図る。

# 3. 適用事例

前章で説明したソフトウェア、デジタル/アナログ ASIC、ハードウェア設計の各分野における開発プロセス 改善手法の適用事例は次のとおりである。これらの事例の 内、(1)、(3)、(4)、(5)、(6)については、この特集号の論文で詳細に述べる。

- (1) 社会インフラシステムのソフトウェア開発プロセス改善<sup>②</sup> 社会インフラシステム(広域監視システム)開発プロジェクトに,ゾーン分析に基づくコスト計画/リスク管理手法を適用し,見積り精度向上と目標QCD達成を可能とした。(本号11ページ)

- (2) 空調機器制御ソフトウェアの再利用開発(3)

空調機器制御ソフトウェアを対象とする,再利用型開発環境の構築に取組み,機能部品化による仕様記述の標準化,ソフトウェア試験資産の再利用を可能とし,生産性の向上,試験網羅度の向上を実現した。

(3) 自動車電子キー用アナログASICの開発効率化 $^{(4)}$

自動車電子キー用ASICの開発に、アナログHDL活用による機能ブロック検証手法、大規模回路検証手法を適用し、サンプル試作前の問題点洗い出しによって開発期間短縮を実現した。(本号15ページ)

(4) 映像情報機器, 薄型液晶テレビの熱設計(5) リアプロジェクタシステム, 薄型液晶テレビの開発に,

- FOA, 三次元熱流会解析手法を適用し, 製品の構想設計, 詳細構造設計の各段階に対応した熱対策を検討することで, 設計品質の早期作り込みによるQCD向上を実現した。(本 号19ページ)

- (5) 空調機器筐体(きょうたい)の輸送時落下衝撃強度設計<sup>6)</sup> 設備用パッケージエアコンの開発で、輸送時の衝撃を想定した強度設計手法を構築し、部材削減による原価低減、落下衝撃試験後の設計手戻り削減を可能とした。(本号23ページ)

- (6) 鉄道車両用制御機器の組立性改善(7)

鉄道車両用推進制御装置の開発で、三次元CADを活用した組立性検証手法を適用し、組立性品質の向上を可能とした。さらに、組立作業要領書/部品リスト作成の自動化、組立作業での三次元アニメーション利用による設計手戻り抑制と初品組立時間短縮を実現した。(本号27ページ)

# 4. む す び

当社における開発プロセス改善の取組みを、ソフトウェア設計、ASIC設計、ハードウェア設計の各分野の代表的手法とその適用事例によって述べた。あらゆる製品分野で、品質向上、コスト削減、開発期間短縮に対する市場要求はますます厳しくなっており、引き続き製品ライフサイクル全般にわたるものづくりプロセスの強化と、中長期的な製品戦略まで見据えた開発の効率化に取り組んでゆく。

## 参考文献

- (1) 竹垣盛一, ほか:フロントローディング型開発設計へ の取組み, 三菱電機技報, **80**, No.10, 636~638 (2006)

- (2) 米澤寛泰, ほか:プロジェクトの特性に応じたソフトウェア・プロセス改善手法, 三菱電機技報, **84**, No.12, 669~672 (2010)

- (3) 大河原 繁, ほか:空調機器制御ソフトウェアの再利 用開発, 三菱電機技報, **84**, No.6, 311~314 (2010)

- (4) 武内良祐, ほか:アナログASIC設計フロントローディング手法, 三菱電機技報, 84, No.12, 673~676(2010)

- (5) 児玉拓也, ほか:電子機器におけるフロントローディング型熱設計, 三菱電機技報, **84**, No.12, 677~680 (2010)

- (6) 谷 則行,ほか:大型板金筐体の落下衝撃強度検証技術,三菱電機技報,84,No.12,681~684 (2010)

- (7) 有田直喜, ほか:三次元モデルを活用した組立性改善, 三菱電機技報, **84**, No.12, 685~688 (2010)