# IMITSUBISHI

## 三菱電機技報

Vol.84 No.4

2010

4

特集「パワーデバイス」

## 目 次

### 特集「パワーデバイス」

|                                    |    |

|------------------------------------|----|

| SiCパワーデバイスへの期待                     | 1  |

| 赤木泰文                               |    |

| 環境対策に不可欠なパワーデバイスの技術動向              | 2  |

| マジュムダール ゴーラブ・西村隆司                  |    |

| SiCパワーデバイス技術とその応用                  | 7  |

| 中田修平・中木義幸・三浦成久                     |    |

| 高性能トランスマーケット型パワーモジュール              | 11 |

| 西村 隆・三村研史・平松星紀・塙田裕基・上田哲也           |    |

| 新型パワーモジュール用第6世代IGBTと<br>薄ウェーハダイオード | 16 |

| 高橋徹雄・吉浦康博・本田成人・藤井亮一                |    |

| 第2世代分割RESURF構造を適用したHVIC技術          | 20 |

| 清水和宏・衣笠彰則・寺島知秀                     |    |

| ダイレクトリード接合型大容量パワーモジュール             | 24 |

| 菊池正雄・上田哲也・新飼雅芳・中島 泰・平岡功治           |    |

| "Rシリーズ" HVIPM                      | 28 |

| 上村 仁・梅澤 熟・森下和博・中川良介                |    |

| 6世代IGBTモジュール"NXシリーズ"               | 32 |

| 西山建人・宮崎裕二・中西英俊                     |    |

| 次世代大容量IGBTモジュール"New-MPDシリーズ"       | 36 |

| 田畠光晴                               |    |

| 新大容量2 in 1 IPM "V1シリーズ"            | 40 |

| 魚田紫織・西田信也・為谷典孝・後藤 章                |    |

| 1,200V大型DIPIPM "Ver.4シリーズ"         | 43 |

| 白石卓也・商 明・栗秋和広                      |    |

| 超小型DIPIPM "Ver.4 新シリーズ"            | 47 |

| 白水政孝・田中智典・坂居正喜                     |    |

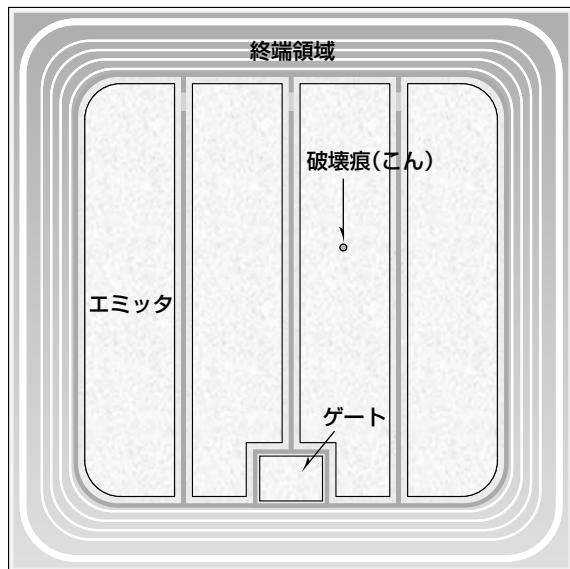

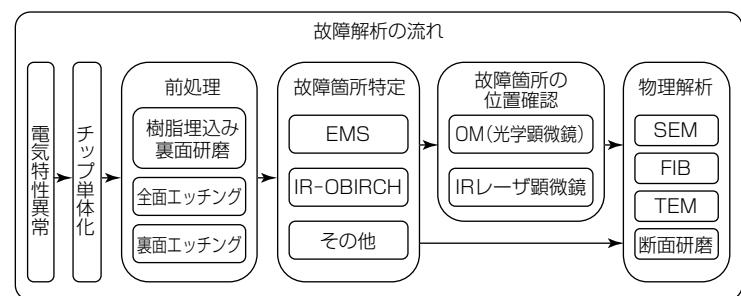

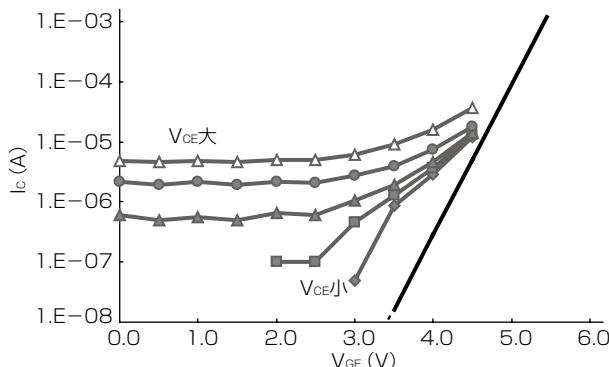

| 素子の品質管理と解析技術                       | 51 |

| 山下文昭・楠 茂・金 敏鎬                      |    |

### 特許と新案

|                |    |

|----------------|----|

| 「半導体装置」「半導体装置」 | 55 |

| 「電力用半導体装置」     | 56 |

### Power Device

|                                                                                             |                                                                               |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Expectations of SiC Power Devices                                                           | Hirofumi Akagi                                                                |

| Indispensable to Counter Climate Change—Progresses in Power Device Technology               | Gourab Majumdar, Takashi Nishimura                                            |

| SiC Power Device Technology and Application                                                 | Shuhei Nakata, Yoshiyuki Nakaki, Naruhisa Miura                               |

| High Performance Transfer-molded Power Module                                               | Takashi Nishimura, Kenji Mimura, Seiki Hiramatsu, Hiroki Shiota, Tetsuya Ueda |

| The 6th Generation IGBT & Thin Wafer Diode for New Power Module                             | Tetsuo Takahashi, Yasuhiro Yoshiura, Shigeto Honda, Ryoichi Fujii             |

| High Voltage IC Technology with 2nd Generation Divided RESURF Structure                     | Kazuhiro Shimizu, Akinori Kinugasa, Tomohide Terashima                        |

| Direct Lead Bonded High Performance Power Module                                            | Masao Kikuchi, Tetsuya Ueda, Masayoshi Shinkai, Dai Nakajima, Koji Hiraoka    |

| "R series" HVIPM                                                                            | Hitoshi Uemura, Isao Umezaki, Kazuhiro Morishita, Ryosuke Nakagawa            |

| 6th Generation IGBT Module "NX series"                                                      | Takeo Nishiyama, Yuji Miyazaki, Hideotsu Nakanishi                            |

| Next Generation Large Current IGBT Module "New-MPD Series"                                  | Mitsuharu Tabata                                                              |

| High Power Dual IPM "V1-Series"                                                             | Shiori Ueda, Nobuya Nishida, Fumitaka Tametani, Akira Goto                    |

| 1,200V Large DIPIPM "Ver.4 Series"                                                          | Takuya Shiraiishi, Ming Shang, Kazuhiro Kuriaki                               |

| Super Mini DIPIPM "Ver.4 New Series"                                                        | Masataka Shiramizu, Tomofumi Tanaka, Masaki Sakai                             |

| Quality Control of Power Devices and Development of an Analysis Technique for Power Devices | Fumiaki Yamashita, Shigeru Kusunoki, Minko Kim                                |

### スポットライト

#### 次世代大容量 "New-MPD" モジュール

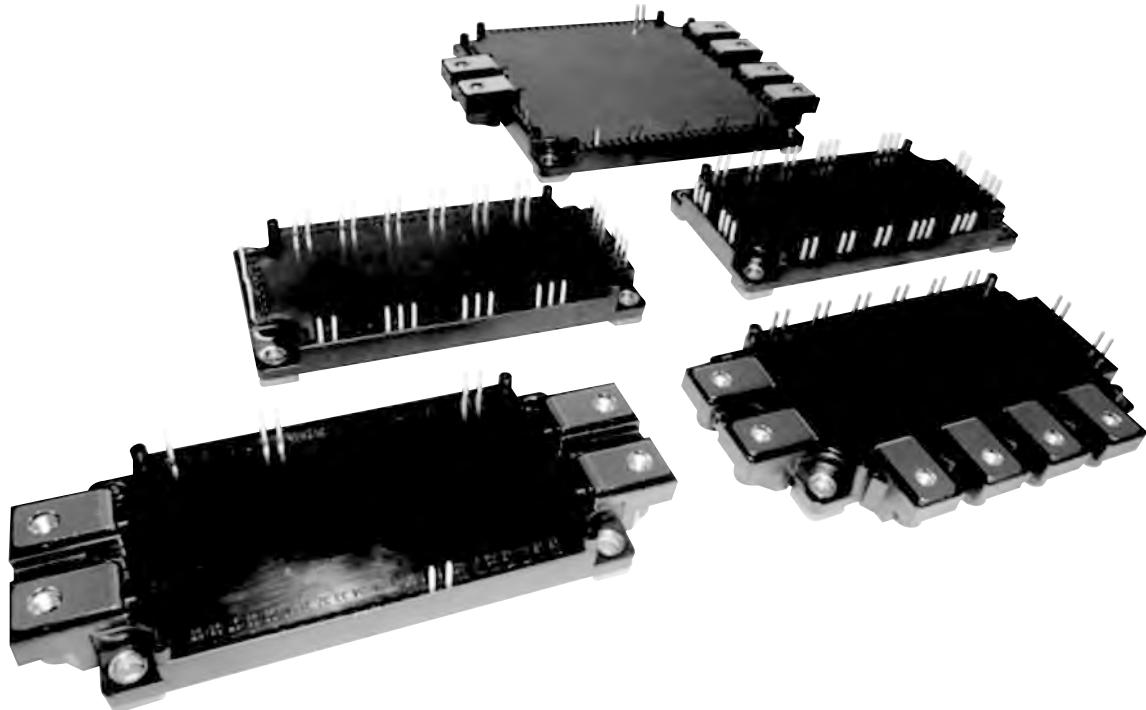

### 表紙：パワーデバイス

最近の省エネルギー・環境意識の高まりに伴い、電力変換装置に使用されているパワーデバイスへの注目が集まっている。三菱電機のパワーデバイスは、民生用から一般産業・鉄道車両用までの幅広いアプリケーションに対応している。

今後、高性能パワーデバイスの出現によって装置の小型化を実現できるとともに、損失低減による省エネルギーが期待されている。

写真は、①大型DIPIPM、②超小型DIP、③次世代大容量IGBTモジュール"New-MPD"、④108RシリーズHVIPM 6.5kV RシリーズIPM、⑤新大容量2 in 1 IPMである。

## 巻/頭/言

## SiCパワーデバイスへの期待

### Expectations of SiC Power Devices

赤木泰文

Hirofumi Akagi

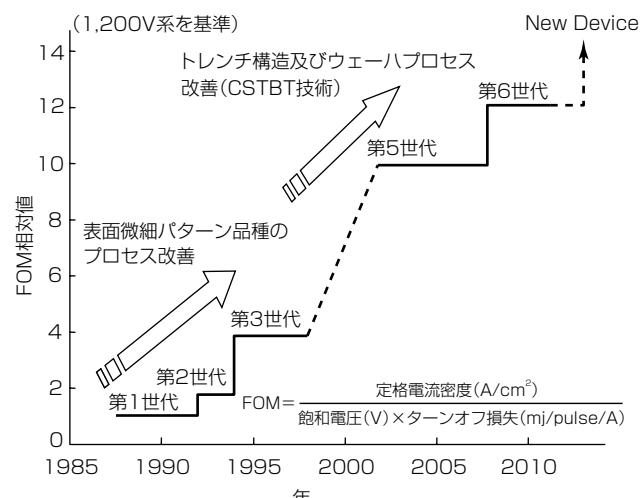

近年のパワーデバイスの発展には目を見張るものがある。1980年代後半に実用化が始まったIGBT(Insulated-Gate Bipolar Transistor)は、世代が進むにつれて性能がステップ的に向上し、最新の第6世代の電力損失は第1世代と比較して1/4に減少した。技術革新が急速に進む電気電子工学の分野において、25年以上にわたってIGBTがパワーデバイスの主役をほかに譲らなかったことも素晴らしいことである。これは、単にIGBTの素性が優れていただけではなく、パワーデバイスの研究者・技術者の性能向上に対する努力と情熱の賜物である。

筆者は学生時代の研究室ゼミで、故宮入庄太教授のさりげない一言が忘れられない。宮入先生は米国GE(General Electric)社が開発したサイリスタ(当時はSCR(Silicon-Controlled Rectifier)と呼ばれた)の将来性にいち早く注目し、アメリカからサイリスタ入手して回路・応用研究に着手したパワーエレクトロニクス研究の先駆者である。サイリスタの基本動作は水銀整流器と同一であるが、サイリスタの飽和電圧(オン時の順電圧降下)は水銀整流器の約1/10、しかも小型・軽量で取り扱いが容易な半導体デバイスである。宮入先生の一言とは“工学の分野では基本動作が同一であっても性能が10倍も異なると技術は同一とは言えない。市場が確立した既存技術を新技術が駆逐するには10倍以上の性能向上が必要不可欠である”であった。

ワイドバンドギャップ半導体のシリコンカーバイド(SiC)を使用したパワーデバイス(SiCパワーデバイス)は、研究開発段階から実用化段階を迎えるようとしている。小容量SiC-SBD(Schottky Barrier Diode)はすでに購入できるが、1,200V/200AクラスのSiC-SBDも早晚製品化されるであろう。SiC-MOSFET(Metal Oxide Semiconductor Field Effect Transistor)モジュールについても同クラスの製品化が産業界から切望されており、より高耐圧のSiCデバイスの研究も進められている。2009年9月にバルセロナ

で開催された世界最大のパワーエレクトロニクス国際会議“EPE2009”では、1,200V/20A SiC-MOSFETモジュール(チップサイズ: 4.09mm角、オン抵抗: 70mΩ at 25°C, 88mΩ at 150°C)の市場投入が近いという興味深い報告があった。国内でも実用化を目指した研究開発が活発に進められている。SiC-MOSFETはIGBTよりも高温動作が可能で、電力損失(オン損失とスイッチング損失の和)も小さく、IGBTの1/10という大幅な電力損失低減を達成しつつある。SiC-MOSFETはオン損失よりもスイッチング損失の低減効果が著しいので、高周波インバータへの応用やPWM(Pulse Width Modulation)インバータのキャリア周波数の高周波化などに適しており、節電だけでなく放熱フィンやインダクタ・コンデンサなどの受動部品の小型化も期待できる。

しかし、SiC-MOSFETを第6世代IGBTに置き換えると、性能が10倍優れているとしてもコスト競争は厳しいものになる。このような“死の谷”を克服するための最も重要なことは、SiCパワーデバイスの研究者・技術者とパワーエレクトロニクス回路・応用の研究者・技術者が協力しながら、IGBTでは参入が困難な新しい市場(回路・応用)を創出することである。たとえば、古くから使用されている商用周波(50/60Hz)変圧器は、電気的絶縁あるいは電圧整合を行うための電気機器である。可聴周波数を超えた20kHz以上の高周波で変圧器を動作させることができれば、変圧器を大幅に小型・軽量化することができ、電力損失も低減できる。このためには、直流から高周波さらに高周波から直流へ双方向かつ超高効率で電力を変換するパワーエレクトロニクス技術が必要不可欠である。超低損失のSiC-MOSFETを使用することができれば100kVAクラスの小型・軽量・高効率のDC/DC変圧器の実現も夢ではない。デバイス技術者と回路技術者が連携を強め、一刻も早くDC/DC変圧器を開発したいものである。

## 巻頭論文

# 環境対策に不可欠な パワーデバイスの技術動向

*Indispensable to Counter Climate Change—Progresses in Power Device Technology*

Gourab Majumdar, Takashi Nishimura

## 要 旨

地球温暖化・環境汚染・エネルギー問題は、人類にとって最も重要な課題となっている。環境保護のため資源とエネルギーを高度利用することが重要な課題であり、その解決のためには、電力分野で、高効率で低消費電力の家電機器及び産業装置の開発、風力発電・太陽電池・燃料電池などクリーンエネルギーを電力源とする発電システムの開発、ハイブリッド電気自動車(HEV)やピュア電気自動車(EV)など超低燃費の新しい自動車の開発などが必要不可欠であり、パワーエレクトロニクス技術の展開とそのキー パーツであるパワーデバイスの果たすべき役割は重要である。これらシステムに適用されているパワーデバイスは、数アンペアの低電流領域から数千アンペアの大電流領域まで及んでいる。また、太陽光発電や風力発電などのクリーンエネルギーへの応用も拡大している。このような適用分野の広がりに対応して三菱電機のパワーデバイスも大きな

発展を遂げており、今後も継続的な進化が期待されている。

特にIGBT(Insulated Gate Bipolar Transistor)モジュールやIGBTと駆動回路と保護・制御の周辺回路を最適な構成で一つのパッケージに組み込んだ高機能・小型のインテリジェントパワーモジュール(IPM)の技術革新は目覚ましく、今日では数十ワットから数十メガワット領域のパワーエレクトロニクス装置で、電力損失を大幅に低減し、省エネルギーの電力変換効率向上に大きく寄与している。

またパワーモジュールは、IGBTやダイオードなどパワーチップの高性能化だけではなく、新パッケージ技術や周辺回路機能の集積化に最適なHVIC(高電圧集積回路)などの技術ポテンシャルを駆使し、パワーエレクトロニクス機器の応用分野の拡大につれて、様々な応用ニーズに対応しつつ、進化し続けている。

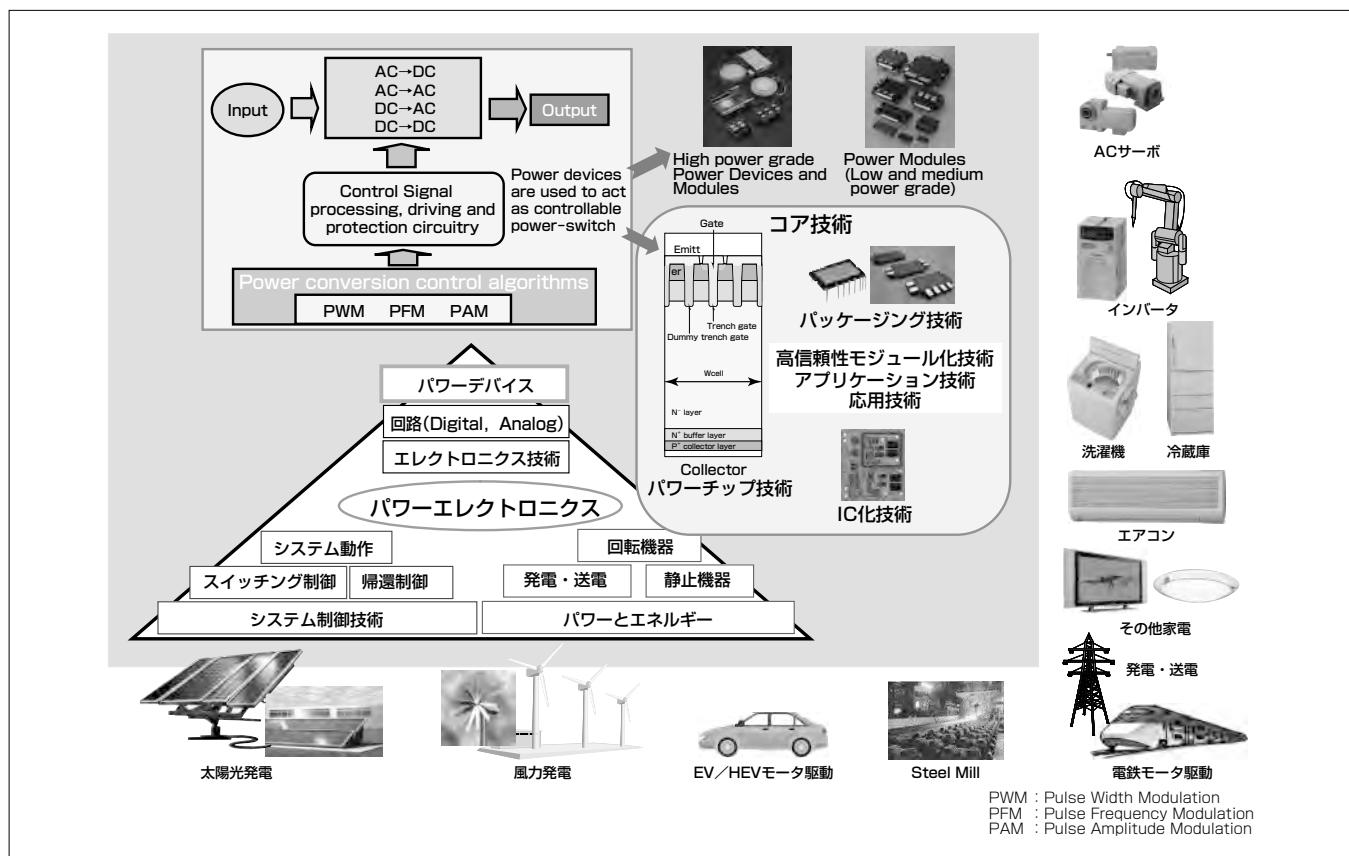

## パワーエレクトロニクス技術の概念とパワーデバイスの重要性

IGBTモジュールやIPMは、産業用のモータ制御や電源、インバータ家電、太陽光発電、電車や自動車など幅広い分野のパワーエレクトロニクス領域で使われている。パワーエレクトロニクス装置の省エネルギー化や小型化、高性能化の実現のためパワーデバイスに対する期待は大きい。

## 1. まえがき

現在、人類の存続に大きな危機感を与えていた最も重要なグローバル的な課題は地球温暖化や環境汚染であり、消えていく化石リソースなどの問題も加え、エネルギーの有効利用が日常生活まで直結する時代になってきた。それに伴い、特に電気エネルギー分野の技術開発が世界的な話題となっている。家電の省エネルギー化、ハイブリッド車や電気自動車など新エネルギー自動車の開発、風力発電・太陽光発電など再生可能エネルギーの実用化など、様々な国家レベルの開発研究が行われているが、それライノベーションのカギを握るのが、パワーエレクトロニクス(PE)技術とその発展をコア技術として支えるパワーデバイスの進化である。資源とエネルギーを高度利用し、地球環境保護に、より早く貢献するためには、密接な関係にある両方の技術の継続的な発展が期待され、様々な分野で注目を集めている<sup>(1)</sup>。

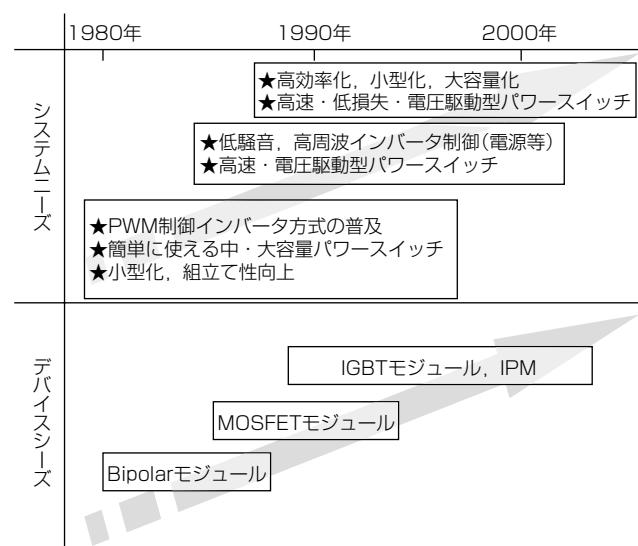

本稿の2ページに示した概念図は、省エネルギー・環境課題の解決に挑戦している応用システムとPE技術の基本的な仕組みに加え、コアテクノロジーとして重要な役割を果たすパワーデバイスとの密接な関係を示すものである。PEシステムの開発を進めるに当たって、最適な電力変換用ハードウェア及びソフトウェアの両面で多くの課題が発生するが、最も重要なのはシステムの心臓部として機能するパワーデバイスの選定である。以前は、パワーデバイスの開発はハードウェアを重視したデバイス単体としての性能改善が中心であったが、今日では、その開発方向は単なるデバイスの性能改善だけではなく、より高度な機能を内蔵したり、自己制御を可能としたりした、インターフェースの向上を図ったものになっている。このため、パワーモジュールの更なる技術発展が期待されている。図1に、密接に進んできたシステムニーズ対デバイスシーズの過去20数年間の主な動きを示す。この期間に、PE機器の発展として高効率・高性能化の追求とともに重要とされてきたのはパワー変換機のパワー密度向上である。これに対してIGBTモジュールやIPM製品群の世代交代が激しく進み、PE装置のパワー密度向上に大きく寄与した。今後、Si系IGBTやダイオードなど主力パワーデバイスの更なる高性能化、半導体ソリューションを追求するIPMの高機能化、又は新材料(SiCなど)適用のチップ技術などへの展開が期待されている。当社は、IGBTモジュールやIPMを含め、業界トップレベルのパワーデバイス技術の開発・実用化や、次世代デバイスの研究などを通じて、パワーデバイスの継続的な発展を目指して事業を進めている。

本稿では、パワーデバイス技術の主なトレンドについて述べる。

## 2. 主パワーチップ技術動向

PE機器の発展は、パワーデバイスの物理学やプロセス技術の革新やブレークスルーによって加速され続けていると言っても過言ではない。

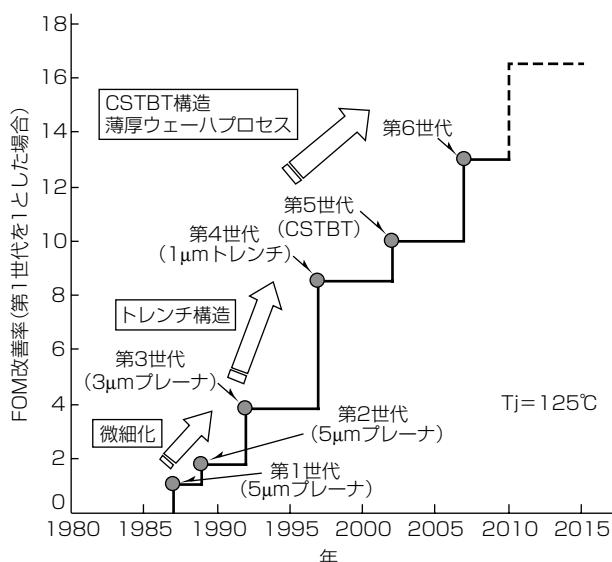

1980年代に製品化されたIGBTが、現在パワーデバイスの主役の座を占めている。このポジションをとることに当たって重要なポイントは、IGBTの技術発展である。図2に、当社IGBTチップの性能改善の経緯をFOM(Figure Of Merit)の相対値で示す。セル構造の微細化、プレナーゲート構造からトレンチゲート構造への移行、キャリア蓄積層を加えた新トレンチゲート構造デバイス(CSTBT)の適用及びリファイン化、ウェーハの薄厚化などの技術進歩によって、2009年に製品化した第6世代IGBTは第1世代品に対し、FOMが約12倍レベルまで改良している。

図1. システムニーズ対デバイスシーズの推移

図2. IGBTのFOM改善

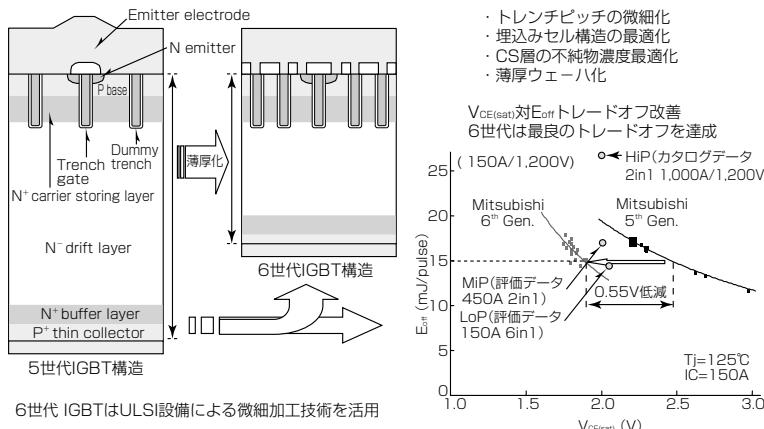

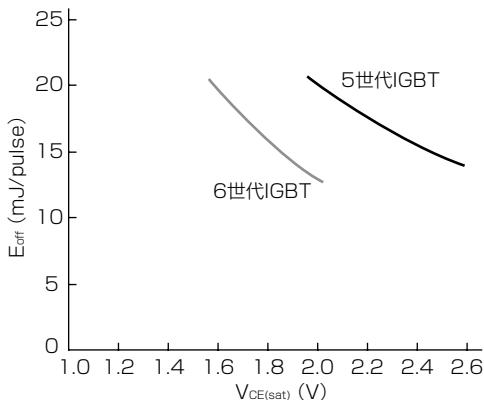

図3に、1,200V耐圧クラスの6世代IGBTのセル構造の特徴及び特性改善について第5世代との比較を示す。6世代IGBTはULSI(Ultra LSI)設備適用のプロセスによってウェーハ厚みの最適化に加え、セル構造の微細化やキャリア蓄積層の最適な形成などが特徴の新CSTBT構造の技術であり、飽和電圧 $V_{ce(sat)}$ 及びターンオフスイッチング損失(ターンオフ・スイッチング・エネルギー) $E_{off}$ のトレードオフを大幅に改善したものである。また、第6世代IGBTの場合、電流密度の許容範囲も広くなつたことによって、従来の5世代IGBTに比べて、20%以上のFOM向上(図2)が実現できた。

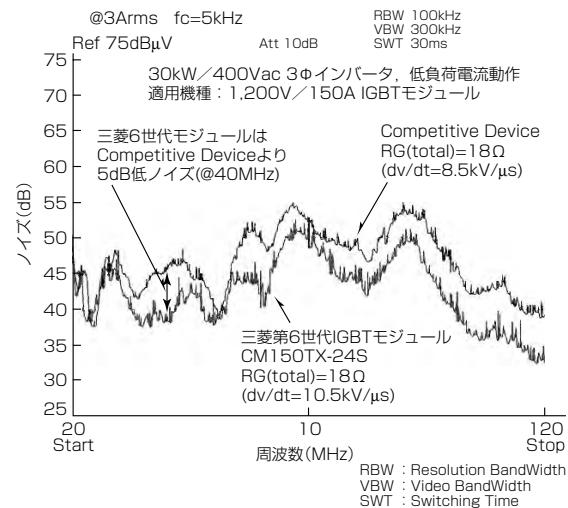

また、インバータなど誘導負荷スイッチング用途で重要な回生機能の役割を果たすフリーホイル・ダイオードFWD(Free Wheeling Diode)についても、6世代IGBTチップ技術の発展に匹敵する新プロセスや構造を適用し、大幅な性能の改善を図った。図4に1,200V耐圧クラスの新しいダイオード(第6世代FWD)技術の特徴を示す。

この場合も、チップ断面図で示すように薄ウェーハ化がキーであり、FZタイプを用いて最適な縦構造を実現したことでのオノ電圧 $V_F$ 及び逆回復動作損失(エネルギー) $E_{sw(rec)}$ のトレードオフを大きく改善することが可能となった。ま

図3. 第6世代IGBTのチップ構造及び特性改善

図4. 第6世代FWDのチップ構造及び特性改善

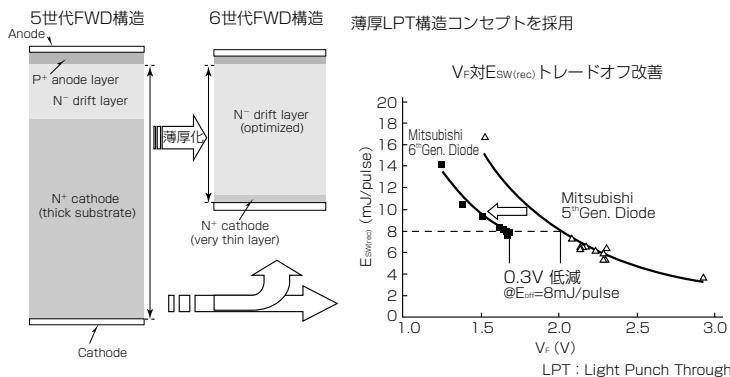

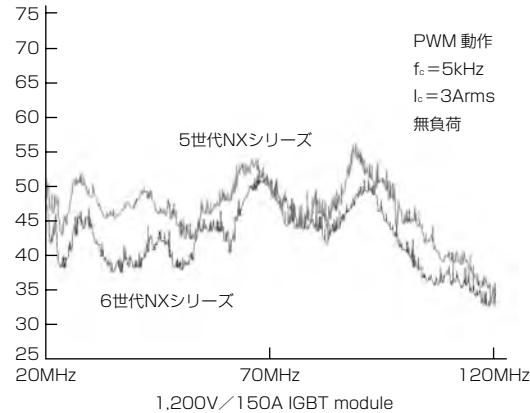

た、第6世代ダイオードのもう一つ大きな特長は、低負荷電流条件でも電流リングが抑制されたソフトな逆回復動作をすることであり、インバータなど応用装置のEMI(Electro Magnetic Interference)ノイズの低減に大きく貢献している。図5に最新IGBTモジュールのEMI評価結果の一例を示す。

低負荷電流インバータ動作条件でも、第6世代IGBT/FWDチップを適用した150A/1,200V定格の第6世代IGBTモジュールが従来品に比べて、EMIレベルは5dB以上(@40MHz)低減されていることが分かる。

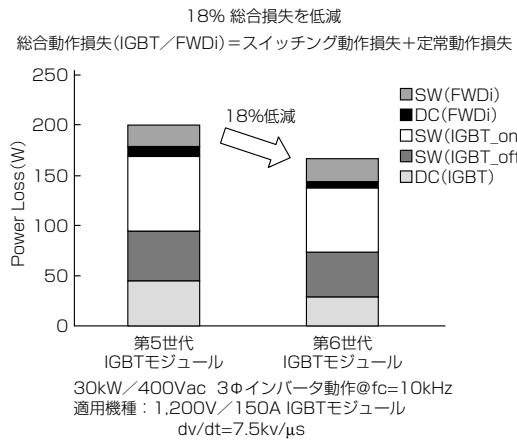

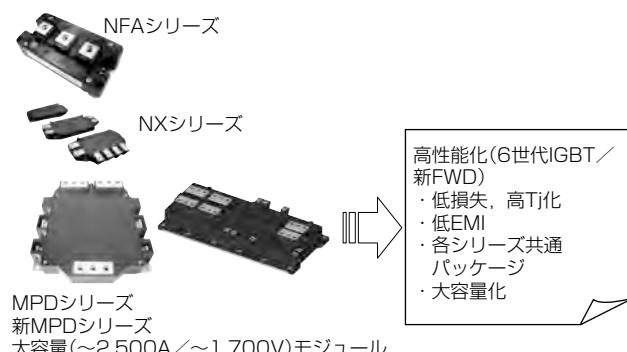

また図6に示すように、インバータ実動作シミュレーション結果から150A/1,200V第6世代IGBTモジュールの総合動作損失(@10kHz)は、同第5世代タイプに比べて18%低減されていることが分かる。これら新世代の主要パワーチップ技術を適用することによって、IGBTモジュールの高性能化が進んでいる。図7にその概念を示す。第6世代IGBTモジュールシリーズのほとんどが、従来製品との互換性を重視して5世代と同一パッケージ構造を適用している。

図5. 最新IGBTモジュールのEMIノイズ比較

図6. 最新IGBTモジュールの損失比較

### 3. パワーモジュール高機能化動向

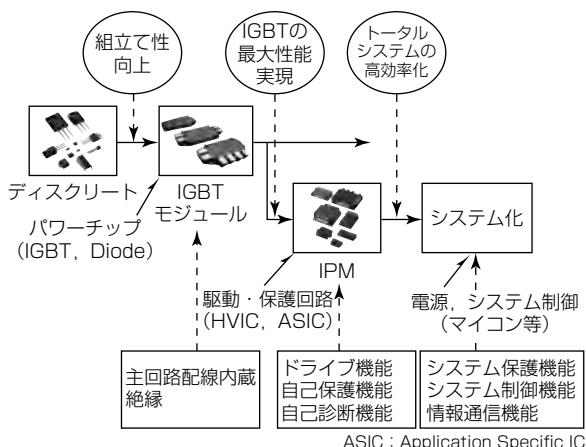

IGBTチップ及びその最適な駆動・保護機能をマルチチップ構成でコンパクトなモジュールパッケージに集積化した、当社独自コンセプトのIPMが、IGBTの発展に大きな役割を果たした。IPMはこれまで多くの応用分野で顧客の要求、悩みのソリューションとして発展してきたとともに、図8に示すようにパワーモジュールの二極化の流れを導いてIGBTモジュールとともに技術進歩を遂げてきた。

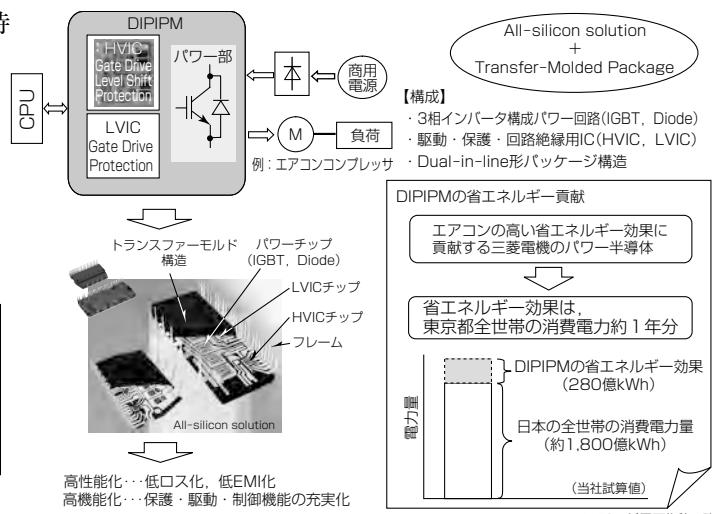

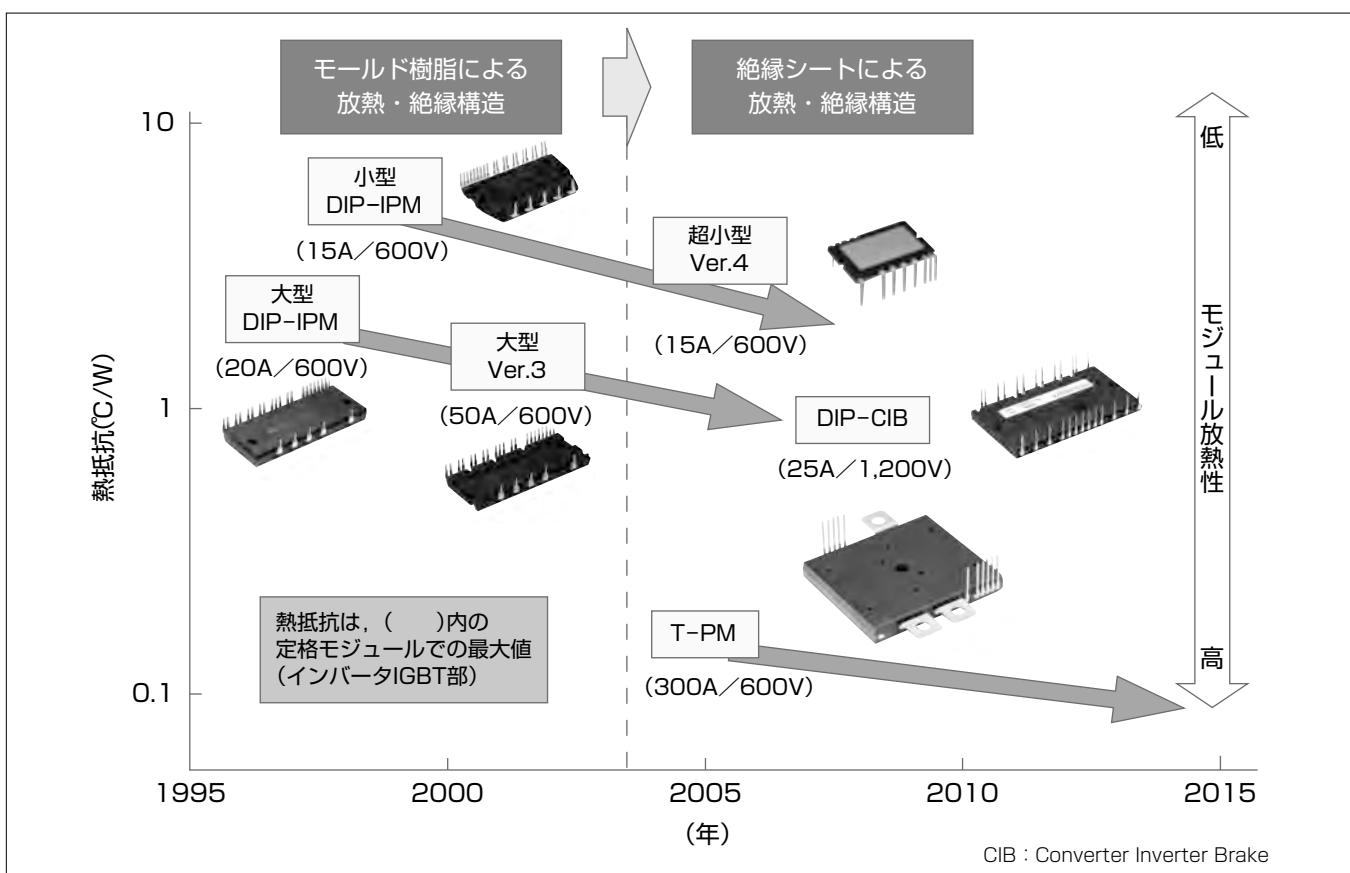

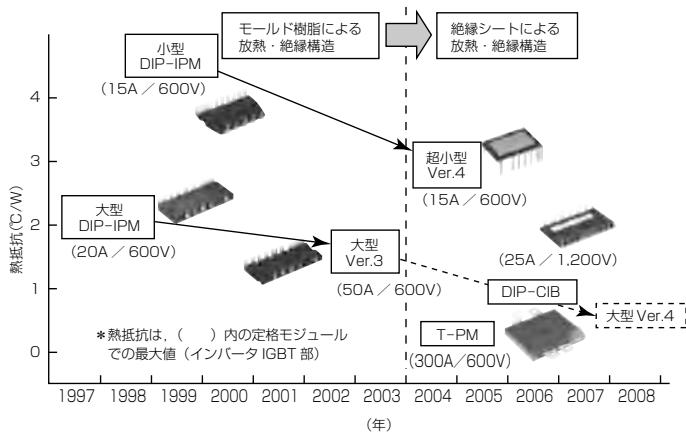

これらIPMは、パワーデバイスとして使用が簡便であるほか、市場での故障が改善されるなどを特長に、産業用インバータ、インバータ家電、電気自動車、電気鉄道など駆動システム用途に幅広く普及した。今後は周辺システム機能を最適な半導体集積技術を駆使してシステム化へ進もうとしている。IPMソリューションとして最も注目を集めてきたのは、インバータ家電や小容量モータドライブ応用に的確なソリューションと1990年代に生まれたDIPIPM(Dual In-line Package IPM)製品群である。DIPIPM製品群は市場投入後、インバータ家電用途でデファクト品として成長し、省エネルギー化に大きく貢献した(図9)。今後、更なる高性能・高機能化に向けて成長し続けることが期待されている。

IGBTモジュールの展開

図7. 製品シリーズの展開

図8. パワーモジュールの高機能化のトレンド

### 4. 新材料パワーデバイス

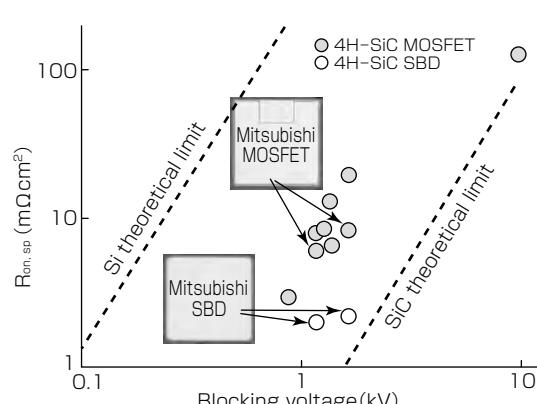

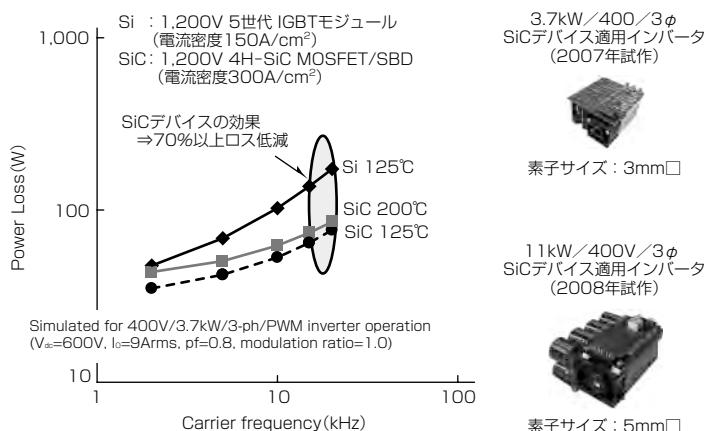

パワーデバイス材料として重要な物性で見れば、SiCはシリコン(Si)と比較し約10倍の絶縁破壊電界強度や約3倍のバンドギャップなどの特長を持つため、低オン損失で高温動作かつ、高速動作が可能な新世代の電力変換用スイッチング素子の実現に向けて希望を与えている。SiデバイスのPiNダイオードやIGBTなどバイポーラデバイスが使われている数kV級以上の応用領域では、SiCを用いたパワーデバイスとそれを応用したインバータの実現が切望されている。特にスイッチングデバイスであるSiC-MOSFET(Metal Oxide Semiconductor Field Effect Transistor)は、低損失性とスイッチング駆動の容易性から、その開発には大きな期待が寄せられている。

図10に発表したいいくつかのSiCデバイス(nチャネル形MOSFET及びSBD(Schottky-Barrier Diode))のオン抵抗率と降伏電圧の関係を、次の関係式から求めた理論限界との比較で示す。

図9. DIP-IPMの特長と省エネルギー化への貢献

図10. SiCデバイスのオン抵抗の低減

図11. SiCインバータ試作と実動作評価

$$R_{on, sp} = W/q\mu_n N_D = 4V_B^2/\varepsilon_r E_C^3 \dots\dots\dots(1)$$

(for unipolar one-sided step junction devices)

$R_{on, sp}$  : Specific ON-resistance(オン抵抗)

W : Depletion Width(空乏層幅)

q : Elementary Charge Value(電子の電荷量)

$\mu_n$  : Electron Mobility(電子の移動度)N<sub>D</sub> : Drift Layer Doping(ドリフト層ドーピング濃度)V<sub>B</sub> : Breakdown Voltage(絶縁破壊電圧) $\varepsilon_r$  : Dielectric Constant(誘電率)E<sub>C</sub> : Critical Electric Breakdown Field(絶縁破壊電界)

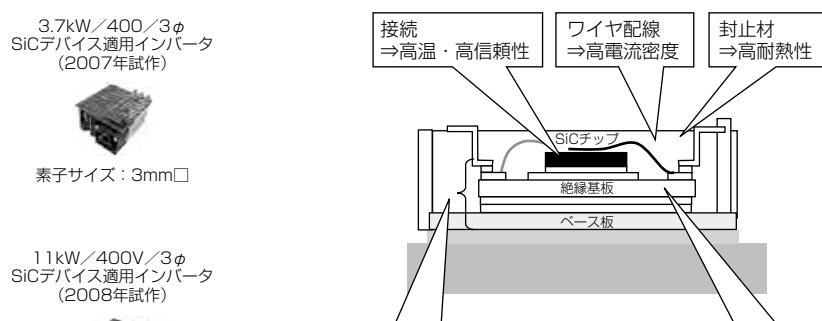

さらに図10に当社が研究を進めている4H-SiC材料適用した1,200V及び1,700V耐圧クラスの大電流容量型MOSFET及びSBD試作チップの最新特性も示す。また、図11にこれら試作チップを採用して試作した高パワー密度の高周波SiCインバータを示す<sup>(2)(3)</sup>。図に示すグラフは、実動作における動作周波数対損失特性の比較であるが、従来のSiモジュール(IGBTとPiNダイオードの構成)に比べ、SiCモジュール(MOSFET及びSBDの構成)の損失が大幅に低減していることが分かる。また、SiCデバイスはその材料の特徴から高温動作に優れていることが知られているが、実装の形態ではデバイスのみならず、周辺材料・組立てに関する高度な技術開発も重要な課題である。図12に高温動作対応のSiCモジュール構造のイメージと、高温動作を実現するに当たっての技術課題解決のポイントを示す。

SiCデバイスを使用することによって、インバータなど様々なPE装置の高効率化を実現できる。また、パワー密度の大幅な向上や動作周波数の高周波化による周辺回路部品の小型化や、冷却システムの大幅な簡素化などのメリットを生かして応用装置の革新的な技術進歩が得られるため、様々な応用分野で大きな省エネルギー効果を得ることが可能となり、地球環境問題への対応として大きく貢献できると考えられる。

## 5. む す び

環境保護対策が重要になるにつれ、省エネルギー化やクリーンエネルギーをリードするパワーエレクトロニクスと

図12. 高温動作対応SiCモジュールの構造と技術課題

図13. 当社パワーデバイス技術の主なトレンド

そのキーパーツであるパワーデバイスはますます必要不可欠な技術になっている。パワーデバイス技術の発展は目覚ましいものがあり、パワーエレクトロニクス市場の拡大に伴う多彩な要求に対応した性能・機能・品質・信頼性及び使いやすさを追求した新デバイスが開発されている。

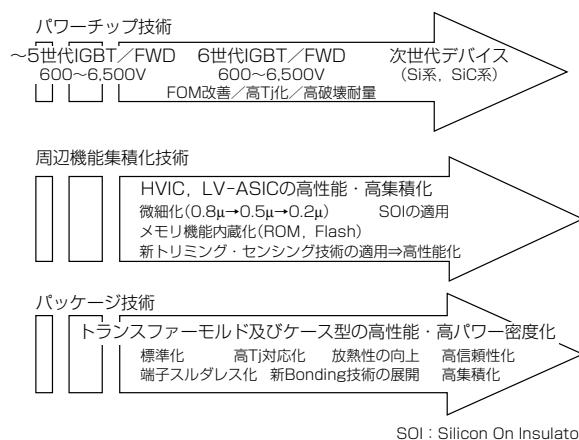

図13に当社が進めているパワーチップ技術、周辺機能集積化技術及び、パッケージ技術の三つのカテゴリーの主要な技術トレンドを示す。パワーチップ技術に関して、シリコン系IGBTが主役の座を継続的に獲得しているが、将来的には、SiC(Silicon Carbide)を適用したMOSFETやSBDなど超低損失パワーデバイスの市場登場も予想されている。環境保護のために、これら技術を駆使した当社パワーエレクトロニクスの更なる発展がますます注目を集めていく。

## 参 考 文 献

- (1) Majumdar, G. : Power Modules as Key Component Group for Power Electronics', PCC Nagoya (2007)

- (2) Kinouchi, S., et al. : High Power-Density SiC Converter, ICSCRM Ootsu (2007)

- (3) 大森達夫 : SiCパワーデバイス技術開発の現状, Nikkei Micro-devicesセミナー, 東京 (2007)

中田修平\*

中木義幸\*

三浦成久\*

# SiCパワーデバイス技術とその応用

*SiC Power Device Technology and Application*

Shuhei Nakata, Yoshiyuki Nakaki, Naruhisa Miura

## 要 旨

半導体パワーデバイスは電力を効率よく制御する重要な役割を果たしており、家電製品から産業、宇宙製品に至る広い分野で使用されている。

SiC(Silicon Carbide)を用いたSiCデバイスは、電力変換器の更なる省エネルギー・小型化を実現する次世代デバイスとして期待されている。

三菱電機はSiC-MOSFET(Metal Oxide Semiconductor Field Effect Transistor)とSiC-SBD(Schottky Barrier Diode)のSiCデバイスの開発を進めるとともに、インバータへの応用技術開発を行うなど実用化を目指した開発を進めている。

2006年1月には、開発した耐圧1,200V、電流10A級の

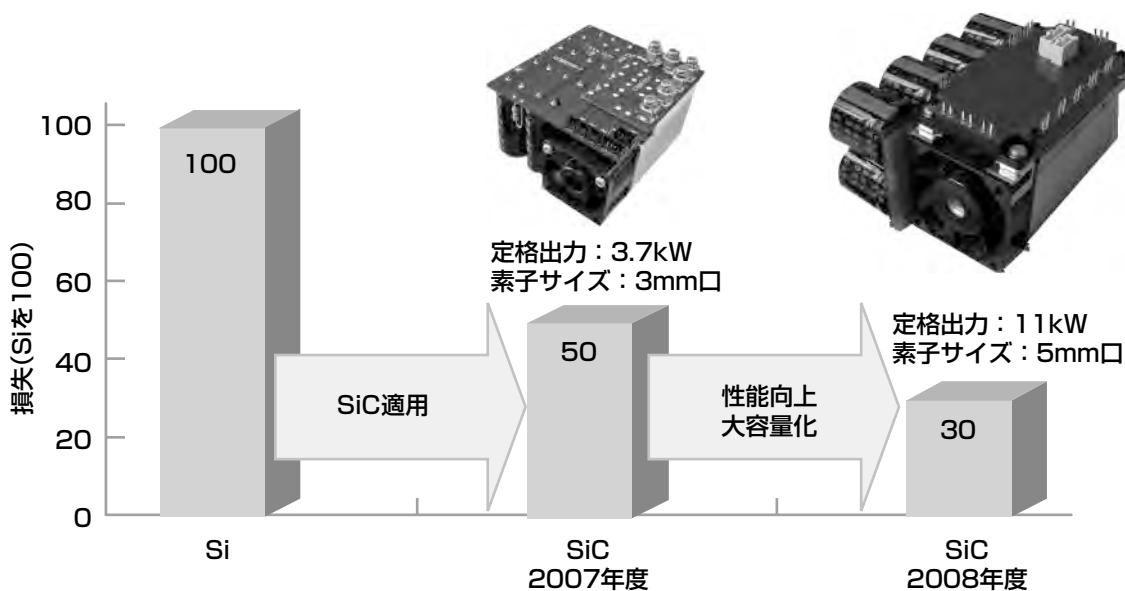

SiCデバイスを用いたインバータで、世界で初めて3.7kW定格の三相モータの駆動に成功した。2007年10月には、低損失特性を生かしたパワー密度9W/cm<sup>3</sup>のSiCインバータを実現し、従来のSi-IGBT(Silicon-Insulated Gate Bipolar Transistor)を用いたインバータに対して50%の電力損失低減を実証した。

2009年2月には、デバイスの性能向上と大容量化によってパワー密度10W/cm<sup>3</sup>の11kW SiCインバータを試作して、電力損失を70%低減できることを示した。

今後SiCデバイスを応用する上での信頼性技術を更に高め、SiCデバイスの早期実用化を目指した開発を行っていく。

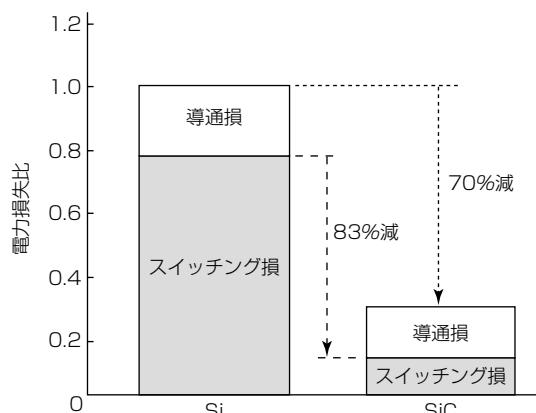

## SiCインバータの低損失化

当社では、2007年10月に3mm□のSiCデバイスを用いて3.7kWのSiC-インバータを開発し、従来のインバータに対して50%の電力損失低減を実証した。2009年2月には、性能と容量を向上した5mm□のSiCデバイスを用いパワー密度10W/cm<sup>3</sup>の11kW SiCインバータを試作し、70%の電力損失低減を示した。

## 1. まえがき

半導体材料であるシリコンカーバイト(Silicon Carbide: SiC)は、従来Siに比べて絶縁破壊電界強度が約一けた高いなどの特長を持つ。

この高い絶縁破壊電界強度特性によって、SiCデバイスはSiデバイスで不可能であった高電圧ユニポーラデバイスが実現でき、通電時の損失を低減できるとともに、スイッチング時(オン／オフ時)に発生する損失を大きく減らすことができる。このため、電力変換器であるインバータにSiCデバイスを使用することによって、電力損失の大幅な低減及び機器の小型化が可能になる。

当社はSiC-MOSFETとSiC-SBDの開発を同時に進めてその基本特性の向上を目指すとともに、インバータなどの応用技術開発を行うなど、SiCデバイスの実用化を目指した開発を進めている。

2006年1月に耐圧1,200V、電流10A級のSiCデバイス(SiC-MOSFET, SiC-SBD)を開発し、それを用いたSiCインバータで、世界で初めて3.7kW定格の三相モータの駆動に成功した。2007年10月には、低損失特性を生かした3.7kW定格出力インバータを試作し<sup>(1)</sup>体積を1/4に小型化(パワー密度10W/cm<sup>3</sup>)できることを実証した。

2009年2月には、10A級のSiCデバイスを並列接続したモジュールを組み合わせ10kWの出力を実現し、電力損失が従来のSiインバータに対し70%低減できることを示した<sup>(2)</sup>。

本稿では大容量のSiCデバイスの開発及び、11kW出力のインバータに適用したときの効果について述べる。

## 2. SiCデバイスの開発

### 2.1 SiCデバイスの現状

パワーエレクトロニクスへの適用を考える場合には、大容量のデバイスの実現が不可欠である。次に当社の大容量SiCデバイスの開発状況について述べる。

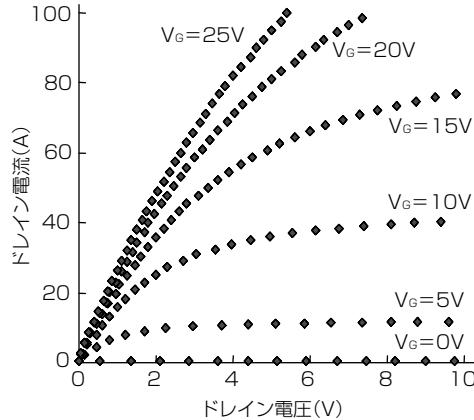

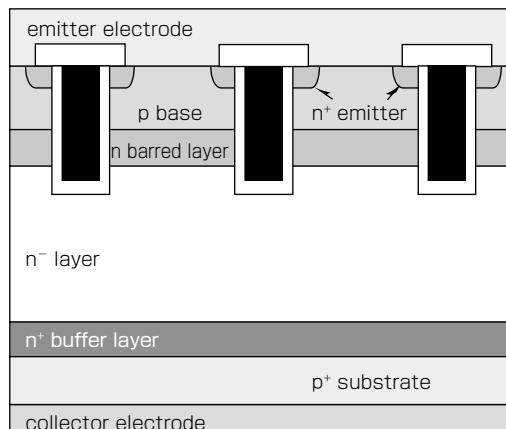

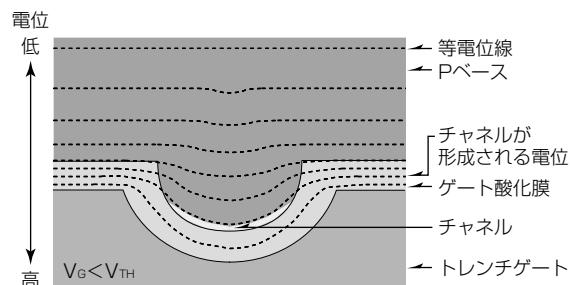

### 2.2 SiC-MOSFET

開発しているSiC-MOSFETは、いわゆる縦型構造のMOSFETであり、図1の上図に示す構造をしている。次に構造について述べる。n型SiCウェーハを基板に用い、エピタキシャル成長<sup>(注1)</sup>によってウェーハ表面にドリフト層を形成している。その厚さ及び実効的な不純物濃度は、ドレイン電極への定格電圧印加時のリーク電流が十分に抑えられるよう設定している。MOSFETを構成しているPウェル領域及びN<sup>+</sup>領域は、それぞれAlとNイオンを多段注入することで形成している。注入元素の活性化は、シャトル型の高温熱処理炉を用い<sup>(3)</sup>、Ar雰囲気での高温アニール処理<sup>(注2)</sup>によって行っている。

(注1) 薄膜結晶成長技術であり、基板となる結晶の上に結晶成長を行う手法

(注2) 内部のひずみを取り除く熱処理のこと

ゲート酸化膜はパイロジェニックウェット酸化と窒化ガス中でのポストアニールによって形成し、界面準位密度の低いMOS界面を実現している。層間絶縁膜を堆積(たいせき)してコンタクトホールを開口後、Niシリサイド層を形成してウェル領域とソース領域に低コンタクト抵抗率のオームикンタクトを実現している。

フロント面には、ワイヤボンディングが可能な厚膜Al層をソース電極としており、裏面のドレイン電極にはシリサイド層形成後にダイボンド用の金属積層膜をスパッタで形成している。

このようにして作製したSiC-MOSFETの室温におけるドレイン電流-ドレイン電圧特性を、図1の下図に示す。素子の有効面積は約0.2cm<sup>2</sup>である。このMOSFETは、図に示されるようにゲート電圧(V<sub>G</sub>)を20Vとすることで、100Aのドレイン電流を制御することが可能である。また、図示はしていないがゲートをオフしたときの耐圧として1,200V以上を確保している。

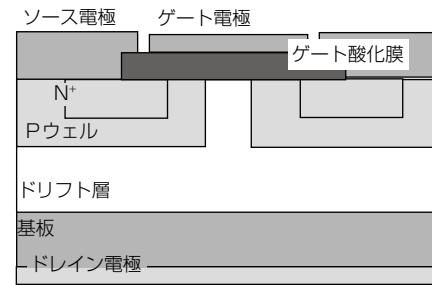

### 2.3 SiC-SBD

SiC-SBDも、MOSFET同様のn型SiCウェーハを用いて作製している。ドリフト層の厚み及び不純物濃度は、SiC-MOSFETと同様に定格電圧印加時のリーク電流が十分に抑えられるよう設定されている。オーム電極は裏面のカソード側のNiシリサイド層によって形成している。その後、ショットキー電極を形成し、シリサイド層形成温度以下でのアニール処理によってショットキー障壁高さを安定化している。フロント面及び裏面は、MOSFETと同様にそれぞれ厚膜Al層とカソード電極側に金属層を

図1. SiC-MOSFETの構造と電気特性

形成している。素子終端部はAl注入によって形成されたガードリング構造、さらにその周辺にJTE(Junction Termination Extension)構造<sup>(注3)</sup>を持つ2段終端構造とし、安定した耐圧を実現している。

図2に、試作したSiC-SBDの室温における電流-電圧特性を示す。チップ面積はおよそ5mm<sup>2</sup>で、素子の有効面積はおよそ0.25cm<sup>2</sup>である。図に示すように順方向電圧が0.96V(V<sub>th</sub>)から電流が流れ始め、その後SBDの特徴である電流-電圧特性を示している。また、1,200V以上の耐圧を確保している。

(注3) 端部の電界強度を低減し耐圧を向上させる構造

### 3. 11kW SiCインバータの試作と評価

#### 3.1 11kW SiCインバータ

2章で述べたSiCデバイスを用いて大出力のインバータを試作した結果について述べる。

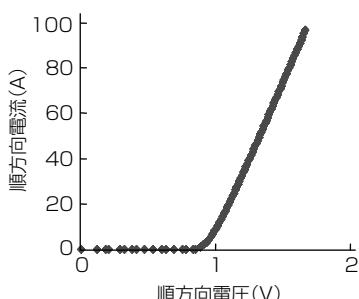

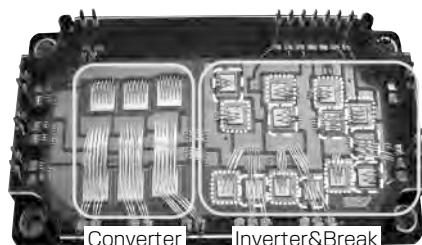

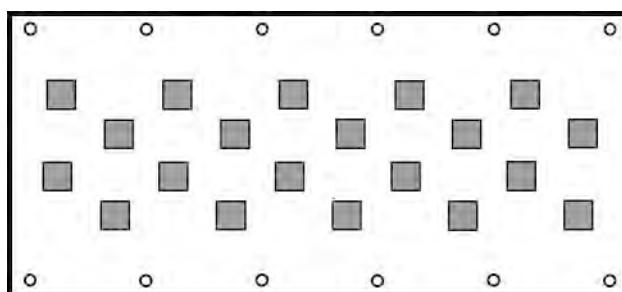

図3に、試作インバータを構成するモジュール部の素子配置を示す。モジュールは、コンバータ回路・インバータ回路・ブレーキ回路から構成されており、図の左側部分がコンバータ回路、右側部分がインバータ回路とブレーキ回路である。コンバータ一部はSiのダイオードを用いており、インバータ&ブレーキ部はSiC-MOSFETとSiC-SBDを用いて構成している。モジュールは市販品のパッケージを用いて試作している。図の破線で囲まれている素子がSBDを示しており、点線で囲まれた素子がMOSFETを示している。

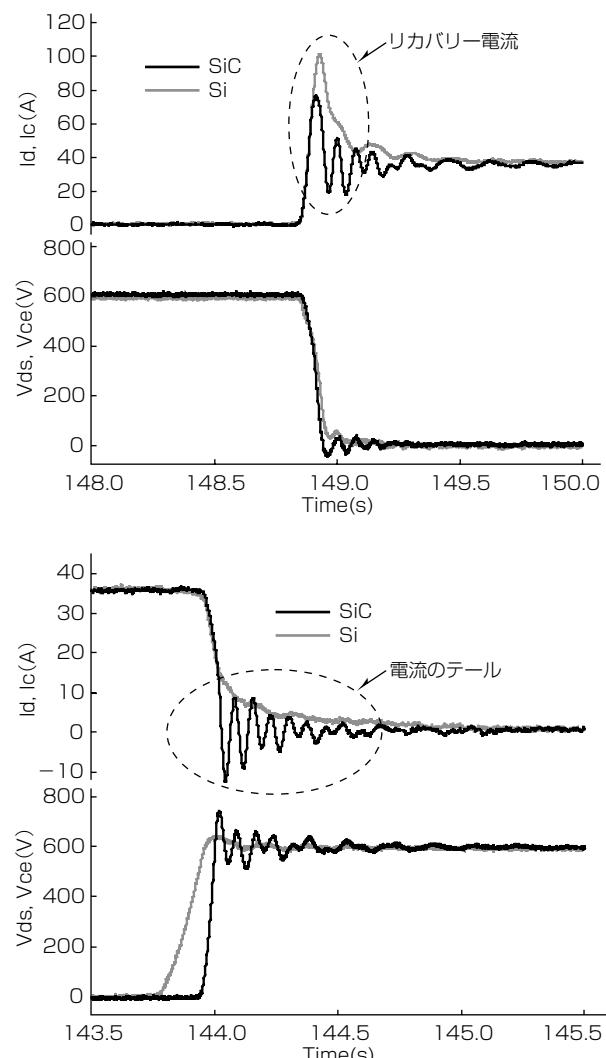

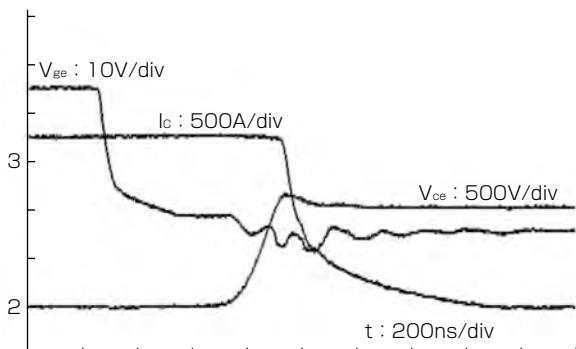

図4に、SiCインバータの動特性評価結果(スイッチング波形例)を示す。測定はモジュールの上下アームを用い、誘導性負荷を用いることで行っている。図の波形は125°Cの条件下での結果である。

図2. SiC-SBDの電気特性

図3. 試作SiCインバータの素子配置

図において上図がターンオン時の電流電圧波形を示しており、下図がターンオフ時の電流電圧波形を示している。波形の濃淡はそれぞれSiCデバイスを用いた場合と従来のSiを用いた場合の波形を示している。

ゲート抵抗は、ターンオン時のスイッチング速度(dI/dt, dV/dt)がSiデバイスを用いたモジュール(ゲート抵抗は、データシートで許容されている最小値)と同程度になるよう設定している。

図に示されるようにSiCデバイスの場合、SBDの効果によってターンオン時のスパイク状の電流(リカバリー電流)がSiデバイスに対して低減される。波形に表れる振動は回路の寄生容量と寄生インダクタンスに起因する。

また、ターンオフ時には、Siデバイスでは電流波形にテールがあるのに対し、SiCデバイスではすみやかに遮断されている。

先に述べたスイッチング試験から得られるスイッチング損失と電流値の関係と静特性の測定結果(IV特性)を用いることで、インバータ動作時(キャリア周波数15kHz、力

上図：ターンオン時、下図：ターンオフ時。

各図の上部が電流波形、下部が電圧波形。

波形の濃淡は、SiCデバイスとSiデバイスを示している。

図4. SiCインバータのスイッチング波形

図5. SiインバータとSiCインバータの損失比較

率0.8、実効電流23A、出力11kW)の電力損失が求められる。

図5に、Siデバイスを用いた場合とSiCデバイスを用いた場合の損失計算結果を示す。図に示されるように電力損失が大幅に低減され、従来のSiインバータと比較して70%低減となる。また、図には導通損とスイッチング損の分析結果も合わせて示しているが、SiCデバイスではスイッチング損失(SW損)の低減効果が大きく、Siデバイスに対して83%の低減効果がある。

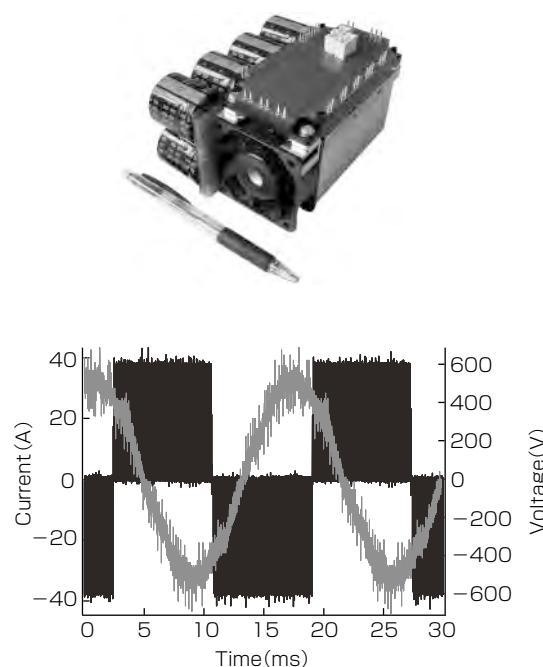

### 3.2 SiCインバータの特性

インバータ損失の低減は機器の小型化に寄与する。図6にこのモジュールを用いて試作したSiCインバータ及びモータ制御時(11kW出力)の電流電圧波形を示す<sup>(4)</sup>。低損失化によって冷却系が小型化できるために、SiCインバータは容積1.1L(従来インバータ比1/4)まで小型化されている。この結果、パワー密度10W/cm<sup>3</sup>を実現している。この値は同容量のSiインバータに対し約4倍のパワー密度である。

図6下にモータ制御時の電流電圧波形を示す。このときの出力は11kWであり、図に示されるように安定にモータを制御できていることが示されている。

### 4. む す び

SiCデバイスの開発及び応用技術開発の一環として、有効面積0.2cm<sup>2</sup>と世界最大級の大容量SiCデバイスを用いた11kWのSiCインバータを試作し効果を評価した。SiCデバイスを用いることで、インバータのスイッチング時の特性がSiデバイスに対して優れており、11kW出力時の電力損失を従来のインバータに対して70%低減できることを示した。また、低損失効果によってインバータの体積を1/4に

図6. 試作インバータとモータ制御時の電流電圧波形

小型化でき、パワー密度を10W/cm<sup>3</sup>に向上できることを実証した。今後もSiCデバイスを応用する上での信頼性技術を更に高め、早期実用化に向けて開発を進めていく。

この研究は、経済産業省/NEDO((独)新エネルギー・産業技術総合開発機構)から委託された“パワーエレクトロニクスインバータ基盤技術開発”的成果を含んでいる。

### 参 考 文 献

- (1) Watanabe, T., et al.: Shuttle Activation Annealing of Implanted Al in 4H-SiC , Jpn. J. Appl. Phys. **47**, No.4, 2841~2844 (2008)

- (2) Kinouchi, S., et al.: High Power Density SiC Converter, Material Science Forum Vols. 600-603, 1223~1226 (2009)

- (3) Nakata, S., et al.: Substantial Reduction of Power Loss in a 14kVA Inverter Using Paralleled SiC-MOSFETs and SiC-SBDs, Silicon Carbide and Related Materials 2008, 903~906 (2009)

- (4) 木ノ内伸一, ほか:SiCインバータによる省エネルギー・省資源, 三菱電機技報, **83**, No.10, 615~618 (2009)

# 高性能トランスファーモールド型 パワーモジュール

西村 隆\* 塩田裕基\*

三村研史\*\* 上田哲也\*\*\*

平松星紀\*\*

*High Performance Transfer-molded Power Module*

Takashi Nishimura, Kenji Mimura, Seiki Hiramatsu, Hiroki Shiota, Tetsuya Ueda

## 要旨

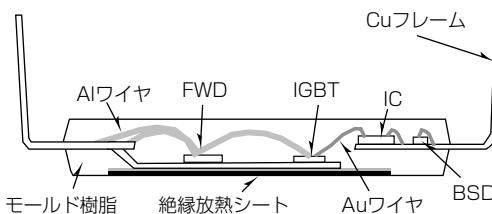

生産性に優れるトランスファーモールド型のパワーモジュールは、従来小型軽量化を特長に、主に白物家電用途のモジュール(Dual In-line Package-Intelligent Power Module : DIP-IPM)として市場を伸ばしてきた。近年、それらの用途にもモジュールの大容量化・小型化の要望が高まり、更なる放熱性の向上が必要となった。この解決策として、従来パッケージの放熱・絶縁構造を見直すとともに、絶縁シートの放熱性を改善した。新規開発したパワーモジュールは、従来モールド樹脂が担っていた放熱・絶縁の役割を、高熱伝導かつ高絶縁耐圧の絶縁シートが担うことで、高絶縁耐圧と低熱抵抗化を実現した。

さらに三菱電機は、絶縁シートの優れた放熱性を生かし、ヒートスプレッダ<sup>(注1)</sup>を内蔵した高放熱モジュール構造の適用によって、大容量に対応可能なトランスファーモールド型パワーモジュール(Transfer-molded Power Module : T-PM)を開発し、産業用及び車載用に展開している。T-PMは、①セラミックス基板搭載モジュールに匹敵する放熱性を持つ、②従来のケース型モジュールに比べ、高い信頼性を持つなどを特長に、今後更に大きな需要が見込まれる。

本稿では、T-PMに適用される絶縁シート技術の紹介と、最近の技術動向を述べるとともに、T-PMの高性能化技術について述べる。

(注1) チップからの発熱を効果的に放散させるために設けられた金属などの構造部材

## トランスファーモールド型パワーモジュールの放熱性の向上

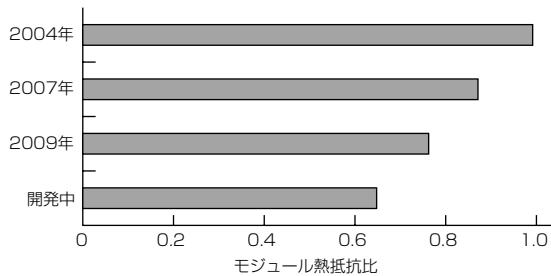

1997年に大型DIP-IPMを商品化して以来、モールド樹脂で放熱・絶縁するモジュールの市場が拡大したが、放熱性に限界が生じたため、2004年から絶縁シートを適用することによって、モジュールの熱抵抗低減を実現した。さらに高放熱が可能なT-PMは、産業用、車載用の大容量モジュールに展開され、絶縁シートの高熱伝導化とともに、熱抵抗の低減が図られている。

## 1. まえがき

半導体の樹脂モールドは、1960年代前半、代表的な熱硬化樹脂であるエポキシ樹脂材によるキャスティング封止で始まった。1960年代後半には、より生産性が優れた固形封止材を用いた低圧トランジスター成形法が開発され、これが現在の半導体樹脂モールド技術の主流になっている。

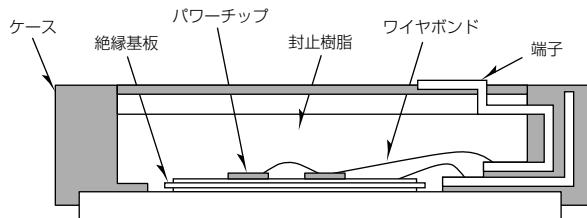

一方、パワーモジュールのパッケージ基本構造は、従来は図1に示すようなケース型モジュールが主流であったが、当社では1997年から半導体樹脂モールド技術で養われたトランジスターモールド型パワーモジュールを実用化し、この10年でパッケージ種、生産数ともに増加している。トランジスターモールド型パッケージは生産性に優れる上、小型化・軽量化を実現しており、主に白物家電用途の小容量の領域で急速に拡大している。このパッケージ構造では、絶縁耐圧を確保しつつ、熱抵抗を低減することが重要であり、最新世代では高熱伝導の“絶縁シート”を採用することで放熱性能を大幅に改善し、パッケージの小型化を実現した<sup>(1)</sup>。

本稿では絶縁シートの進歩によって、大電流化、高電圧化が大いに期待されるトランジスターモールド型パワーモジュールの高放熱化技術の開発状況について述べる。

## 2. モールド型パッケージ構造の歴史

図2に当社の代表的なモールド型パワーモジュール製品の変遷を示す。1997年に初めてトランジスターモールド型の大型DIP-IPM(～20A/600V)を製品化し、1999年には

図1. ケース型モジュールの構造

図2. モールド型パワーモジュール製品の変遷

ヒートスプレッダを持たない小型DIP-IPM(～15A/600V)を上市した。その後、2002年に大型DIP-IPMをベースに、銅材のヒートスプレッダを内蔵して低熱抵抗化を図り、電流容量50Aまで対応した大型DIP-IPM Ver.3を開発した。

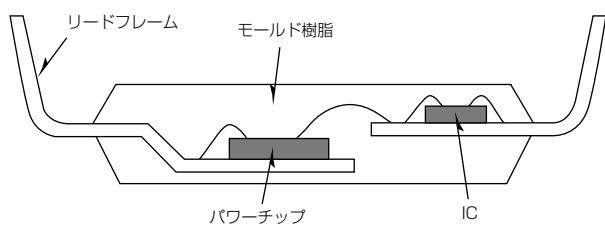

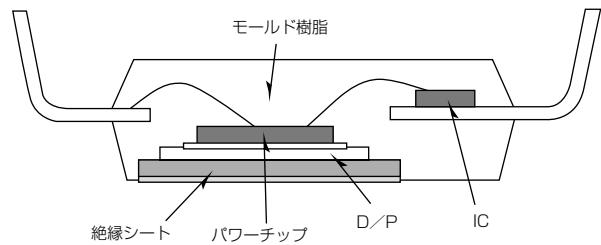

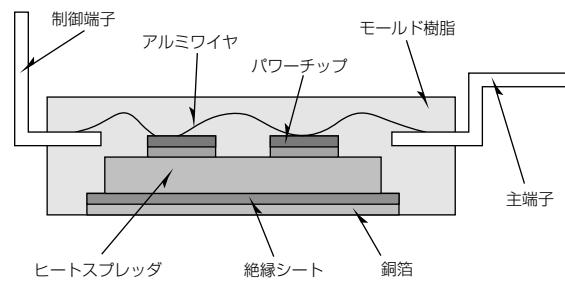

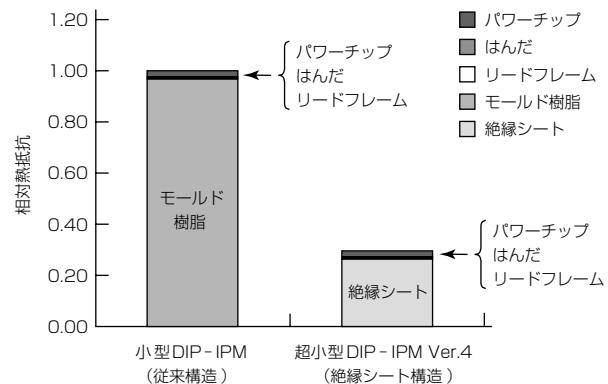

2004年にはパッケージコンセプトを見直して、“絶縁シート”を採用したDIP-IPM(超小型Ver.4)を開発・量産化した。従来のDIP-IPMでは、モールド樹脂が放熱と絶縁を担ってきたが、超小型DIP-IPM Ver.4では、新たに開発した高熱伝導絶縁シートに放熱及び絶縁機能を持たせた構造としている。図3にモールド樹脂によって絶縁された従来構造及び図4に絶縁シート構造のDIP-IPMの断面構造模式図を示す。

絶縁シート搭載のパワーモジュールは、DIP-IPM以外にも展開しており、2004年以降には主に産業機器、又は車載用途向けに、定格300A/600Vの大容量モールド型IGBT(Insulated Gate Bipolar Transistor)モジュールとなるT-PM(図5)を開発した<sup>(2)</sup>。これは、絶縁シートと銅ヒートスプレッダの組合せによって極めて高い放熱性を実現している。また、2006年には、汎用(はんよう)インバータ用途向けに、絶縁シートとアルミヒートスプレッダを放熱経路としたDIP-CIB(DIP-Converter Inverter Brake)を製品化した。

図3. モールド樹脂絶縁型モジュールの構造

(従来型：小型DIP-IPM)

図4. 絶縁シート型モジュールの構造(超小型DIP-IPM Ver.4)

図5. トランジスターモールド型大容量パワーモジュール

(T-PM)構造図

### 3. 絶縁シート適用トランスファーパワーモジュール

### 3.1 絶縁シート適用のメリット

従来のDIP-IPMは、図3のようにパワーチップ、制御チップを同一リードフレーム上に搭載し、全体をモールド樹脂で封止する構造となっている。パワーチップからの放熱は、チップ→はんだ→リードフレーム→モールド樹脂を経由し、外部に放出される。

一方、絶縁シート構造DIP-IPMは、図4のようにフレームと絶縁シートを接合し、フレームから直接絶縁シートを経由して放熱する構造としている。

絶縁シートは、モジュールの高放熱化と高絶縁耐圧化を実現することを目的としている。放熱性は、式(1)で表される熱抵抗の逆数であり、各構成層の熱伝導率が高く、絶縁層の厚さが薄いほど良くなる。

R<sub>th</sub> : 熱抵抗 λ : 構成材料の熱伝導率

t: 厚さ S: 伝熱面積

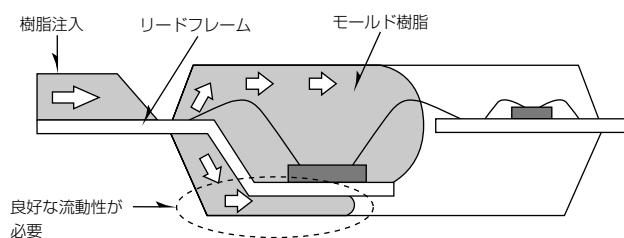

モールド樹脂の熱伝導率は、表1に示すように比較的高い熱伝導率のフィラーを用いても数W/mKレベルが限界となっている。また、図6には、モールド成形時の樹脂の流動イメージを示しており、リードフレーム下の間隔が狭く、樹脂の流動抵抗が大きくなっている。したがって成形性を確保するためには、リードフレーム下の樹脂層の薄膜化には限界が生じる。このように従来構造のDIP-IPMでは、モールド注入の制約から樹脂の高熱伝導化と絶縁層の薄膜化に限界が生じ、放熱性向上が困難であった。

対してモールド封止型モジュールの高放熱化を目的として絶縁シートを適用したDIP-IPMでは、熱抵抗の大幅な低減が可能となる。図7に、シミュレーションで求められたDIP-IPMの熱抵抗の成分比率を示す。モールド樹脂の熱伝導率は金属、セラミックスに比べて1~2けた小さく、

表1. モールド樹脂に用いられる熱伝導フィラーと熱伝導率

| 熱伝導 フィラー                             | 熱膨脹係数<br>×10 <sup>-6</sup> (/K) | 熱伝導率<br>(W/mK) | モールド樹脂としての<br>熱伝導率(W/mK) |

|--------------------------------------|---------------------------------|----------------|--------------------------|

| 溶融シリカ SiO <sub>2</sub>               | 0.5                             | 1              | 0.7~0.8                  |

| 結晶シリカ SiO <sub>2</sub>               | 1.5                             | 12             | 2.0~2.5                  |

| アルミナ Al <sub>2</sub> O <sub>3</sub>  | 6                               | 36             | 3.0~4.0                  |

| 窒化ケイ素 Si <sub>3</sub> N <sub>4</sub> | 3.2~3.7                         | 45             | 3.0~3.5                  |

図6. モールド成形時の樹脂流動イメージ

モールド型パッケージでは封止樹脂層(モールド樹脂)の熱抵抗が支配的になる。絶縁シート構造でも、絶縁シート部の熱抵抗が最も大きな比率を示すことに変わりはないが、従来型のモールド樹脂に比較すると1/3以下となっている。これは、絶縁シートの熱伝導率を高く、かつ薄く設計できるためである。この絶縁シートを適用することによって、モジュールの放熱性が飛躍的に向上し、従来型に比較し大幅にパッケージを小型化することに成功した。

### 3.2 絶縁シートの高熱伝導化技術

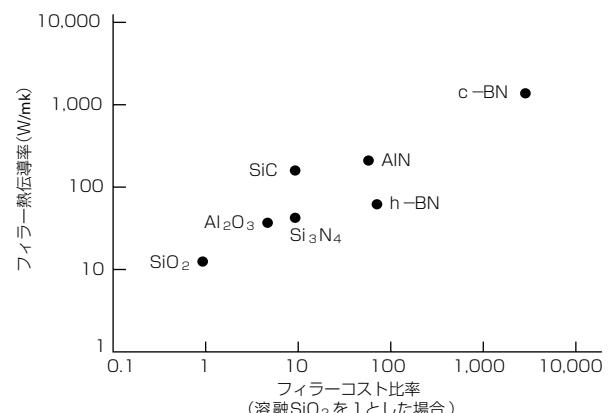

樹脂モールドによる絶縁と異なり、絶縁シートを用いたパワーモジュールでは放熱性と封止を機能分担しているため、絶縁シートは放熱性重視の設計が可能となる。すなわち、放熱性と電気絶縁性が求められる絶縁シートは、封止材料に必要な流動性や離型性などが不要となるため、熱伝導フィラー<sup>(注2)</sup>(以下“フィラー”という。)の充填(じゅうてん)率を高めることができ、フィラー形状、粒径、界面処理などの材料設計の自由度も高くなった。また、材料使用量が少ないため、比較的高コストの材料設計が可能となるというメリットも生じる。図8に、絶縁シートに使用可能な代表的なフィラーのコストと熱伝導率を示す。従来の封止材料には、コストの制約から酸化物フィラーが主に使用されていた。一方、絶縁シート型パワーモジュールに適用

(注2) 熱伝導率向上のために添加される充填材

図7. 従来構造及び絶縁シート構造のDIP-IPMの熱抵抗

図8. 熱伝導フィラーのコストと熱伝導率

される絶縁シートは、使用量が少ないため、比較的高価な材料、特に最近の高放熱性が要求される大容量パワーモジュールには、窒化物系フィラーの適用が盛んに検討されている。

最近の有機材料の高熱伝導化技術動向として、以下のような様々な検討が進められている。

- ①フィラーの高充填化：フィラー形状、粒径設計による充填率極限化技術<sup>(3)</sup>

- ②フィラー間の熱抵抗低減：ブリッジ材によるフィラー間熱抵抗の低減技術<sup>(4)</sup>

- ③樹脂成分の高熱伝導化：液晶骨格導入等による樹脂ナノ構造制御技術<sup>(5)</sup>

- ④異方性フィラーの配向制御：c, h-BN等異方性の強いフィラーの充填配向制御技術<sup>(6)(7)</sup>

このように、有機材料の高熱伝導化技術の進歩とともに、絶縁シートの性能も向上している。図9に、当社の大容量トランスファーパワーモジュールT-PMのモジュール放熱性の進化を示す。2004年に初めて絶縁シートを適用したモジュールの熱抵抗に対し、絶縁シートの熱伝導率の向上とともにモジュールの熱抵抗は低下し、2009年では20%以上低減している。また、開発中のモジュールでは、2004年品に比べて35%程度の熱抵抗低減を目指している。このように絶縁シートの高熱伝導化に伴い、モジュール放熱性は向上し、小型化又は大容量化設計が可能となってきている。

### 3.3 絶縁設計技術

T-PMでは図5に示したように、リードフレーム(ヒートスプレッダ)と銅箔(はく)間に高電圧が印加されるため、その間に挟まれた絶縁シートや封止樹脂で絶縁を確保する構造になっている。電界が集中する絶縁シート及びリードフレーム近傍の封止樹脂では、高耐圧絶縁設計が重要である。特に絶縁シートは薄肉であり高電界が印加されるため、高度な絶縁設計技術が必要となる。

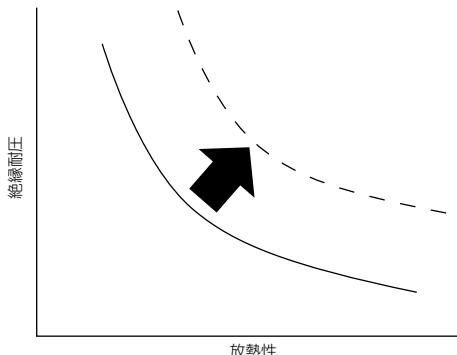

図10に絶縁シートを適用したモジュールの放熱性能と絶縁性能の関係を示す。放熱性能と絶縁性能は、しばしばトレードオフの関係にあり、例えば熱伝導シートで考えると、フィラー粒径を大きくすることで熱伝導率は向上するが、フィラー端部の局所電界が高くなり耐電圧は低下する。

図9. T-PMの放熱性の向上

よって、高耐圧高熱伝導シートを構築するには両者のバランス設計が必要であり、次のような絶縁設計要素を最適化する必要がある。

- ①絶縁シートの厚さ

- ②フィラーの粒径、形状

- ③フィラーの種類(誘電率)

- ④フィラーの充填率

- ⑤シート内ボイドサイズ

- ⑥リードフレーム(ヒートスプレッダ)端部形状

表2に、絶縁シートに適用される主な熱伝導フィラーの物性を示す。絶縁設計には、フィラー自体の絶縁抵抗値だけでなく、誘電率や耐湿性への配慮も重要である。窒化物フィラーは、酸化物系フィラーに比較し、高い放熱設計が可能となるが、例えは窒化アルミニウムでは、高誘電率であることに加え、耐湿性の配慮が必要となる。フィラーと樹脂の誘電率の差が大きいと、通電時の電界集中が生じやすく、絶縁性能の低下につながる場合がある。また耐湿性が低い材料では、分解したイオン成分によってリーク電流の増大を引き起こし、絶縁性能が低下する場合がある。このため、例えは窒化アルミニウムを絶縁材料に用いるには、耐湿性向上策として様々な表面処理法が施されている<sup>(8)</sup>。

このように、絶縁シートの絶縁性能はフィラーの影響を大きく受けており、フィラーの特性を生かした絶縁設計技術が不可欠である。

### 3.4 信頼性向上技術

絶縁シート適用のパワーモジュールでも、セラミック基板を用いたパワーモジュールと同様の信頼性が求められる。特に最近は、モジュールの大容量化、コンパクト化に伴うモジュール作動温度の上昇や、高温高湿環境下耐性への要

図10. モジュールの放熱性と絶縁耐圧の関係

表2. 絶縁シートに適用される主な熱伝導フィラーの物性

| 熱伝導フィラー   | 熱伝導率<br>W/mK                   | 体積固有抵抗<br>$\Omega \cdot \text{cm}$ | 比誘電率                 | 耐湿性 |     |

|-----------|--------------------------------|------------------------------------|----------------------|-----|-----|

| 結晶シリカ     | SiO <sub>2</sub>               | 12                                 | $1 \times 10^{15}$   | 4.6 | 良好  |

| アルミナ      | Al <sub>2</sub> O <sub>3</sub> | 36                                 | $1 \times 10^{15}$   | 10  | 良好  |

| 窒化硼素(六方晶) | h-BN                           | 60                                 | $1 \times 10^{14}$   | 4.2 | 良好  |

| 窒化アルミニウム  | AlN                            | 200                                | $> 1 \times 10^{14}$ | 8.5 | 対策要 |

図11. トランスファーモールドのO<sub>2</sub>とH<sub>2</sub>Oの拡散を示す模式図

図12. 霧囲気の絶縁シート耐熱寿命に与える影響

求が高まっており、過酷な作動環境での信頼性確保が不可欠となっている。

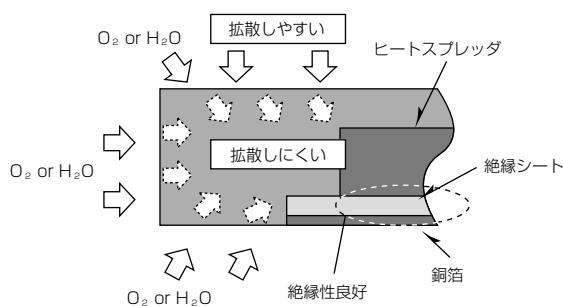

絶縁シートは、熱伝導性のセラミックフィラーを樹脂で固めたものであり、樹脂の耐熱性及び耐湿性等が信頼性を左右する重要な要素となる。このため、絶縁シートに適用される樹脂は、比較的、耐熱性と耐湿性に優れる高架橋樹脂が用いられている。またトランスファーモールド型パワーモジュールの特長は、図11に示すとおりモールド樹脂で覆われた構造になっており、絶縁シートは外気と直接触れない構造、すなわち、直接酸素や水分に触れない構造になっている。一般に樹脂劣化は、熱・光・酸素等のアタックによってラジカル<sup>(注3)</sup>を発生する分解サイクルが進行することが知られている。絶縁シートが直接アタックされにくいモールド構造では、樹脂の耐久性が更に向上することが期待できる。

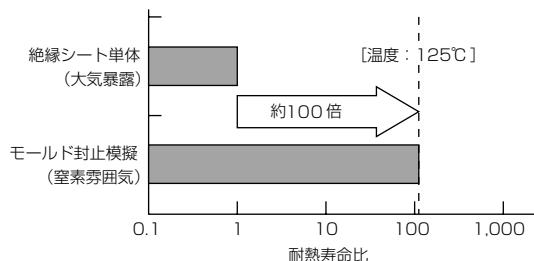

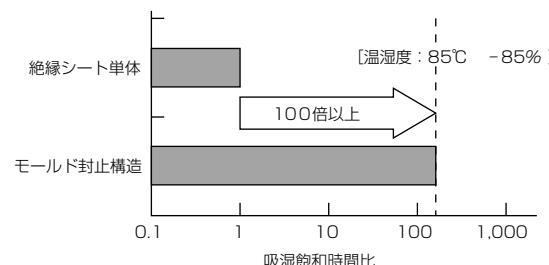

図12に、絶縁シート単体とモールド封止された構造を模擬した窒素雰囲気下での耐熱寿命比を示す。また絶縁シート単体と実際にモールド封止された絶縁シートが吸湿飽和するまでの時間比を図13に示す。これらの評価結果から、熱分解速度や吸湿速度が2けた以上遅くなっていること、絶縁シートの耐熱性、耐湿性はモールド封止されることによって、大きく向上するものと思われる。

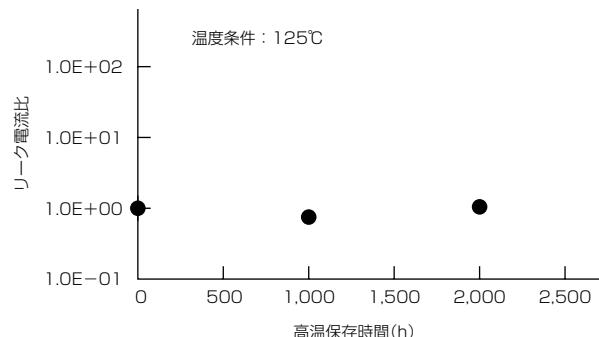

図14には、T-PMを125℃で長期保管してモジュールリーケ電流を測定した結果、2,000時間後も安定した絶縁性を維持できることが示されている。

(注3) 不対電子を持つ化学種のこと

#### 4. む す び

当社のトランスファーパワーモジュールは、絶縁シートの性能向上とモジュール部品を強固に封止するモールド技

図13. 封止有無の絶縁シート吸湿速度に与える影響

図14. T-PMの高温保存時間とリーケ電流の関係

術の融合技術によって、優れた放熱性と信頼性を実現している。今後、更に大容量化と高性能化を実現するパワーモジュールの開発を目指すためには、絶縁シートをはじめとする材料技術の更なる進化が重要となる。

#### 参 考 文 献

- (1) 菊池 巧, ほか: モールド型パワーモジュール用絶縁シート, 三菱電機技報, 81, No.5, 365~368 (2007)

- (2) 篠原利彰, ほか: トランスファーモールド型大容量パワーモジュール, 三菱電機技報, 81, No.5, 325~328 (2007)

- (3) 福家直仁: 高放熱性シート状封止材の開発内容について, 第10回プリント配線板EXPO, PWB-9, 25~32 (2008)

- (4) 出光ホームページ

<http://www.idemitsu.co.jp/ipc/resin/challenge/metal.html>

- (5) 日立化成ホームページ

[http://www.hitachi-chem.co.jp/japanese/information/2009/n\\_090714.html](http://www.hitachi-chem.co.jp/japanese/information/2009/n_090714.html)

- (6) 日立化成ホームページ

[http://www.hitachi-chem.co.jp/japanese/information/2009/n\\_090623.html](http://www.hitachi-chem.co.jp/japanese/information/2009/n_090623.html)

- (7) 宮田健治, ほか: 複合材料の熱伝導における粒子配向の影響, 第30回日本熱物性シンポジウム講演論文集, 136~138 (2009)

- (8) 川崎 卓: 热伝導性フィラーの特性・設計及び热伝導率の向上, 技術情報協会セミナーテキスト, 1~45 (2007)

# 新型パワーモジュール用第6世代IGBTと薄ウェーハダイオード

高橋徹雄\* 藤井亮一\*\*

吉浦康博\*

本田成人\*

The 6th Generation IGBT & Thin Wafer Diode for New Power Module

Tetsuo Takahashi, Yasuhiro Yoshiura, Shigeto Honda, Ryoichi Fujii

## 要旨

近年、パワーデバイスの用途は、産業、民生、電鉄、電力などに加え、昨今の環境問題への取組みなどによって、自動車用、新エネルギー用など様々な分野に広がり、その規模も拡大している。同時に、環境や電子機器の動作への悪影響を防止する法規制に対応するため、低損失化、低ノイズ化、高耐量化、高信頼性化など、IGBT(Insulated Gate Bipolar Transistor)やダイオードに求められる性能は年々厳しくなっている。

三菱電機は、これらの要求にこたえるため、プレーナ型IGBT(第3世代)、トレンチ型IGBT(第4世代)、電荷蓄積型IGBT(CSTBT)(第5世代)などを開発してきた。

今回、更なる特性向上とコストダウンを目指し、新型パ

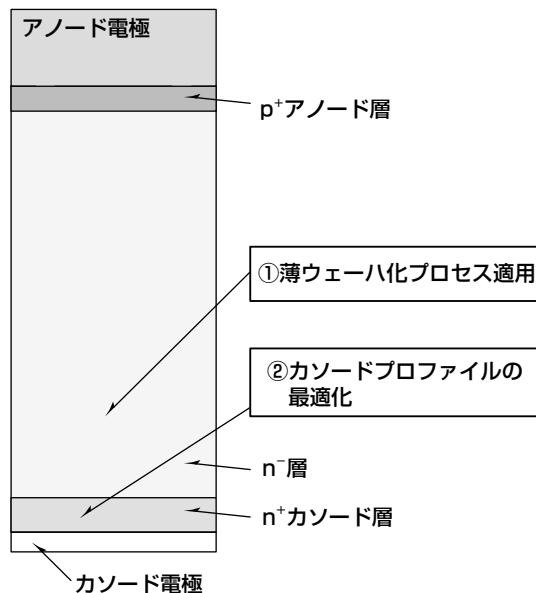

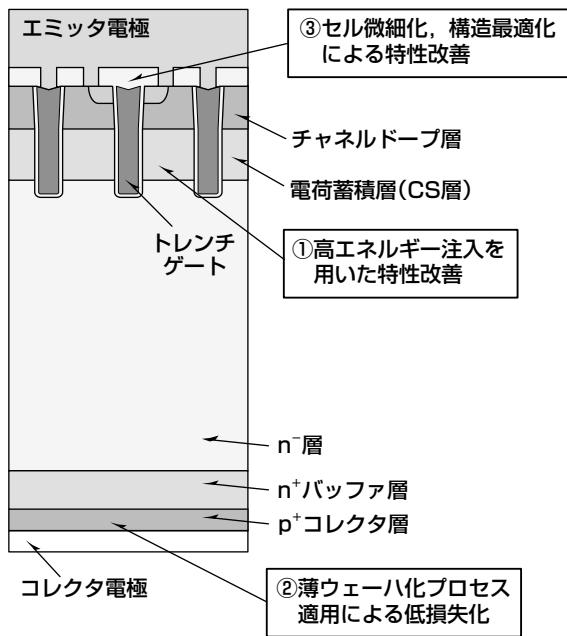

ワーモジュール用として第6世代IGBTと薄ウェーハダイオードを開発した。第6世代のIGBTは、①高エネルギー注入技術を用いた特性の安定化、②薄ウェーハ化プロセスを適用した特性改善、③微細化プロセスを用いた特性改善と最適化によって性能指数FOM(Figure Of Merit)で31%の改善を実現した。薄ウェーハダイオードは、①薄ウェーハ化プロセスを適用した特性改善、②カソードのプロファイルの最適化によって順方向電圧降下 $V_F$ を改善し、FOMで38%の改善を実現した。

この新型パワーモジュール用第6世代IGBTと薄ウェーハダイオードの開発をベースにして、様々な製品向けの新チップを順次開発していく。

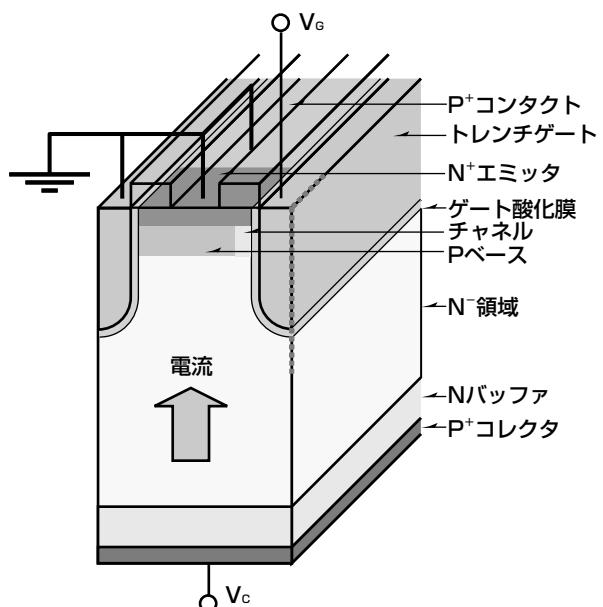

## 6世代IGBTと薄ウェーハダイオードの構造と特徴

6世代IGBTは、①高エネルギー(MeV)注入によるCS層形成技術、②薄ウェーハ化プロセスを用いたLPT(Light Punch-Through)構造の適用、③微細化プロセスとセル構造最適化を用いていることが特徴である。また、薄ウェーハダイオードは従来の拡散ウェーハの問題であった基板厚みとカソードプロファイルの問題を、①薄ウェーハ化プロセス適用、②n<sup>+</sup>カソードプロファイルの最適化によって $V_F$ を低減させている。

## 1. まえがき

パワーデバイスは、地球環境保護をキーワードに従来のインバータ、サーボをはじめとする産業用機器、エアコン、冷蔵庫などの民生用機器に加え、ハイブリット自動車、電気自動車、風力発電及び太陽光発電などの分野にも使われており、ますます重要性が高まっている。

現在の主力パワーデバイスはIGBTとFWD(Free Wheeling Diode)であり、これらの性能改善がパワーエレクトロニクス発展の鍵(かぎ)を握っていると言っても過言ではない。当社は、これらのデバイスの性能を継続して改善してきた。1980年代後半からプロセスの微細化の推進やCSTBTなどの低損失IGBT導入などの改善を続け、2007年までに、性能指数FOMで10倍の改善を図っている。

本稿では、更なる性能改善を進めた第6世代IGBTと薄ウェーハダイオードの開発について述べる。

## 2. 第6世代IGBT

### 2.1 IGBTの性能向上

1987年に第1世代IGBTが発表されて以来、IGBTは常にその特性の改善を続けている。図1にIGBTのFOMの伸展を示す。

性能指数FOMは、チップサイズを決める主要素のコレクタ電流密度 $J_c$ (A/cm<sup>2</sup>)、定常損失を決めるコレクタ-エミッタ間飽和電圧 $V_{CE(sat)}$ (V)、ターンオフ損失 $E_{off}$ (mJ/p/A)の値を用いて式(1)で示されるもので、素子の特性を定量的に示す値である。

$$FOM = \frac{J_c}{V_{CE(sat)} \times E_{off}} \quad \dots \dots \dots (1)$$

第1世代IGBTはプレーナ型IGBTであり、世代が進むにつれて微細化することで特性の向上を図ってきた。第4世代

図1. IGBTの性能指数FOMの推移

になるとプレーナ型からトレーナ型へと構造が変わり、特性が大幅に向上了。第5世代になると電荷蓄積型IGBT(CSTBT)という新型IGBT構造と、薄ウェーハ化のプロセス適用によって特性を改善した。

### 2.2 第6世代IGBTの構造の特徴

第6世代IGBTでは、①高エネルギー注入技術を用いた不純物プロファイル形成による特性安定化、②薄ウェーハ化プロセスを適用した特性改善、③微細化プロセスとセル構造最適化による特性改善などの技術を適用している。

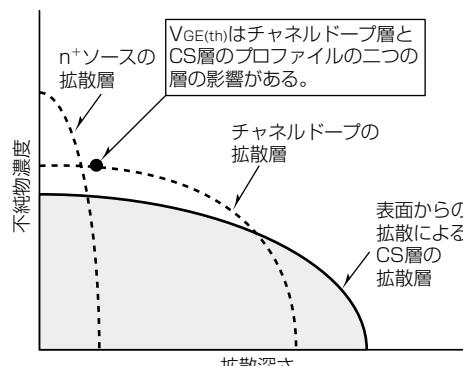

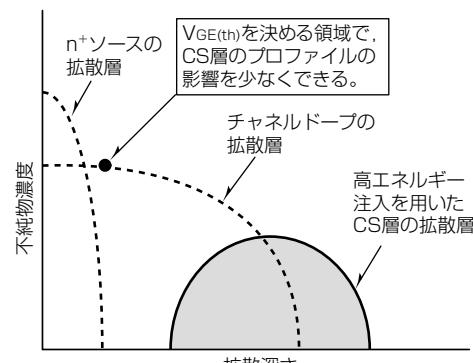

表1に、1,200Vクラスの第5世代IGBTと第6世代IGBTの構造比較を示す。

第6世代IGBTでは、IGBT特性の重要なパラメータであるゲート-エミッタ間しきい値電圧 $V_{GE(th)}$ のばらつき低減のため、電荷蓄積層(CS層)と呼ばれる領域を、不純物を高電界で加速して注入する高エネルギー注入技術を用いて形成している。

図2に高エネルギー注入技術による不純物プロファイル形成の概要を示す。IGBTは表面にMOS(Metal Oxide Semiconductor)を形成し、オン／オフを実現しており、

表1. 5世代IGBTと6世代IGBTの構造比較

| 項目        | 構造     | 5世代      | 6世代 |

|-----------|--------|----------|-----|

| 不純物プロファイル | 標準     | レトログレード  |     |

| 薄ウェーハプロセス | 適用     | 適用       |     |

| トレーナピッチ   | ワイドピッチ | 狭ピッチ     |     |

| セル構造      | 標準     | セル構造を最適化 |     |

(a) 5世代IGBTの不純物プロファイル

(b) 6世代IGBTの不純物プロファイル

図2. 高エネルギー注入技術による不純物プロファイル形成

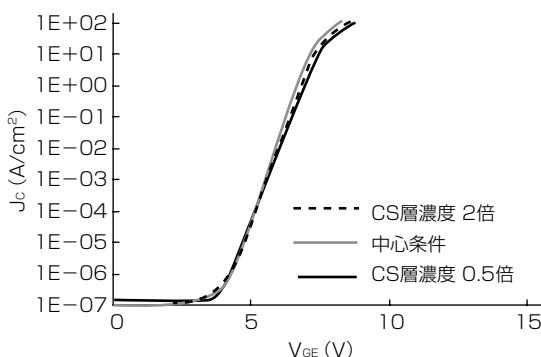

$V_{GE(th)}$ は主にMOSのゲート酸化膜厚とチャネルドープ層濃度で決まっている。第5世代以降のIGBTはn-ドリフト層の導電率変調時のキャリア分布を最適化するためにCS層を追加形成している。第5世代IGBTはCS層を表面から熱拡散しており、 $V_{GE(th)}$ を決めるポイントの不純物濃度がチャネルドープ層の拡散と、CS層の拡散の二つの拡散で決まっていた。第6世代IGBTでは、この $V_{GE(th)}$ のばらつきにつながる問題を極限まで下げる目的として、CS層を形成する不純物を高エネルギーで打ち込む注入技術を採用した。これによって、CS層の効果を保持しつつ、 $V_{GE(th)}$ の安定化を実現している。

また、第5世代IGBTに適用した薄ウェーハ化プロセスを更に進めて、 $V_{CE(sat)} - E_{off}$ のトレードオフを改善している。セル構造については、トレンチピッチを含むセル構造自体を見直してEMI(Electro Magnetic Interference)ノイズ低減対策、ゲート容量の最適化等を行っている。

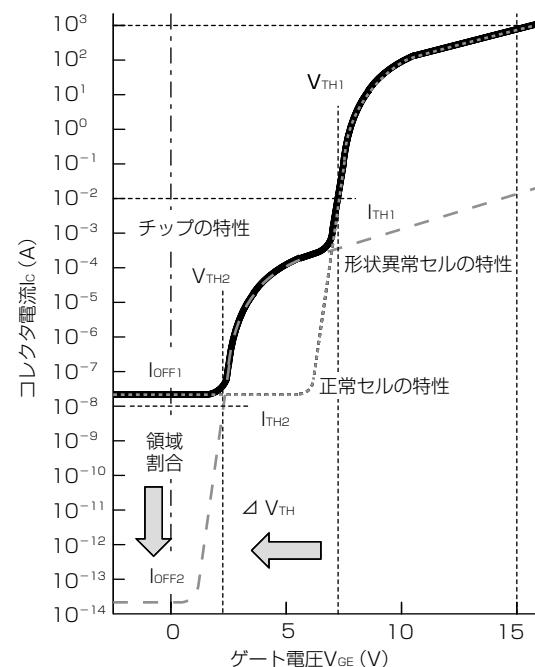

### 2.3 第6世代IGBTの電気特性

図3に、1,200Vクラス第6世代IGBTのコレクタ電流密度 $J_c$ と、ゲートエミッタ間電圧 $V_{GE}$ 特性を示す。先に述べた高エネルギー注入技術適用によって、 $V_{GE(th)}$ がCS層注入量の影響をほとんど受けないことがわかる。

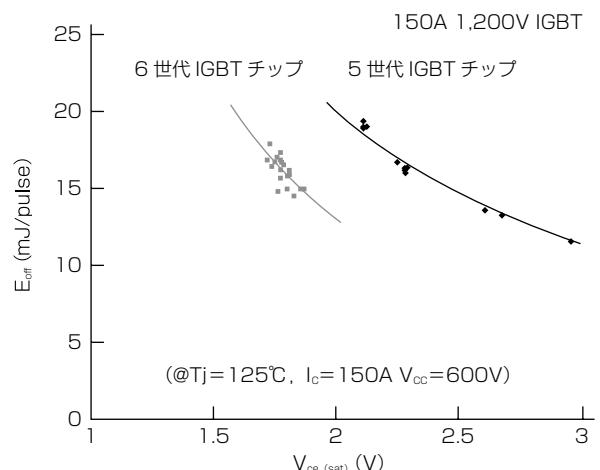

図4に、150A 1,200V定格の第6世代IGBTと第5世代IGBTの $E_{off}$ と $V_{CE(sat)}$ のトレードオフ相関を示す。一般的にIGBTでは $V_{CE(sat)}$ と $E_{off}$ とはトレードオフの関係にあり、こ

図3. 第6世代IGBTの $J_c$ - $V_{GE}$ 特性( $T_j=25^\circ\text{C}$ )

図4.  $E_{off}$ - $V_{CE(sat)}$ のトレードオフ相関

( $T_j=125^\circ\text{C}$ ,  $V_{cc}=600\text{V}$ ,  $I_c=150\text{A}$ )

のトレードオフ自体を改善する構造を作り出すことが求められる。今回の第6世代IGBTでは、第5世代IGBTに比べて $V_{CE(sat)}$ 比で約23%の低減を実現している。

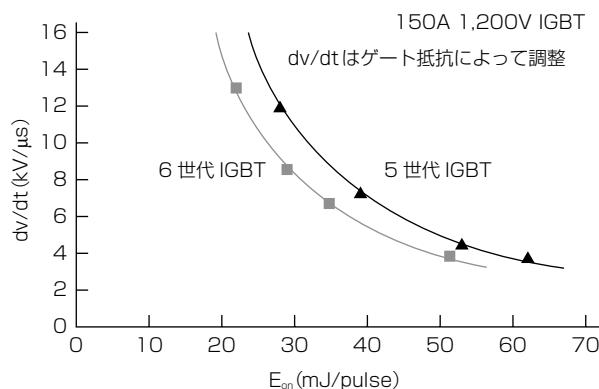

図5に、同一チップのターンオン損失 $E_{on}$ -電圧上昇率 $dV/dt$ の依存性を示す。IGBT開発では $E_{on}$ の低減も求められるが、 $E_{on}$ を低減するためにはスイッチング速度を早くすると $dV/dt$ が大きくなる。この $dV/dt$ はEMIノイズと密接な関係があり、 $dV/dt$ が大きくなるとノイズレベルも大きくなる。このため、 $dV/dt$ と $E_{on}$ のトレードオフ関係の改善が重要となる。第6世代IGBTでは、セル構造の見直しによって、第5世代IGBTに比べて同一 $dV/dt$ で $E_{on}$ が約20%の低減を実現している。

最終的に、性能指標FOM比較で、第5世代のIGBTに比べると第6世代IGBTは31%向上している(図1)。

### 3. 薄ウェーハダイオード

#### 3.1 薄ウェーハダイオードの構造の特徴

従来型ダイオードは、裏面からのn形不純物の拡散によってカソードを形成していた。このため裏面に形成されたカソード厚みが非常に厚く、順方向電圧降下 $V_F$ 低減の妨げとなっていた。薄ウェーハダイオードでは、IGBTで適用した薄ウェーハ化プロセスの適用、及びカソードプロファイルを見直すことで、 $V_F$ の大幅な改善を実現している。

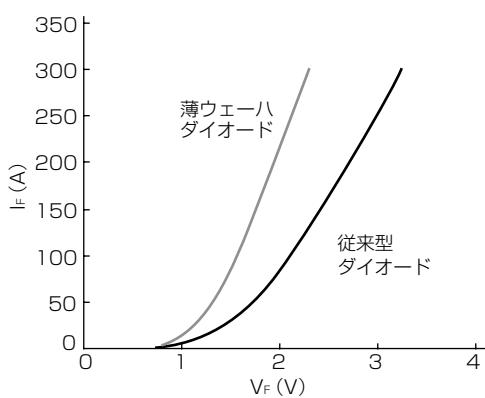

#### 3.2 薄ウェーハダイオードの電気特性

図6に150A 1,200V定格の従来型ダイオードと薄ウェーハダイオードの順方向電流 $I_F$ と $V_F$ の関係を示す。基板厚みが大幅に薄くなったことによって、同じ $I_F$ を流すのに必要な電圧 $V_F$ が低減され、 $I_F$ - $V_F$ 特性が大幅に改善されている。

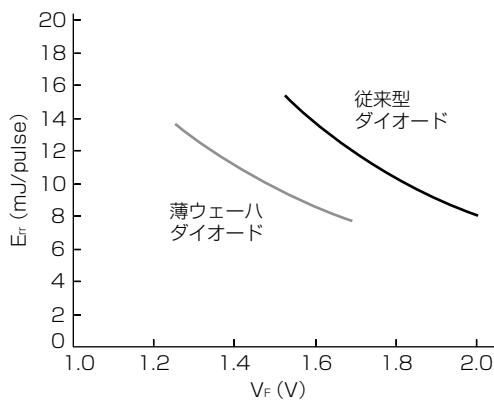

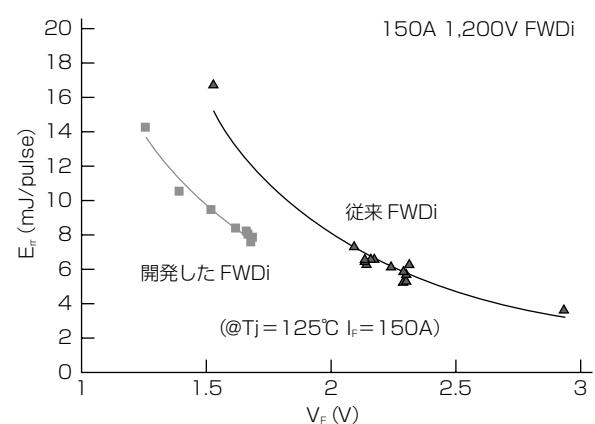

図7には従来型ダイオードと薄ウェーハダイオードの $V_F$ とリカバリー損失 $E_{rr}$ のトレードオフ相関を示す。一般に $V_F$ と $E_{rr}$ にはトレードオフ相関があり、このトレードオフ相関自体を改善するのがダイオード開発のポイントの一つ

図5.  $E_{on}$ - $dV/dt$ のトレードオフ相関

( $T_j=125^\circ\text{C}$ ,  $V_{cc}=600\text{V}$ ,  $I_c=150\text{A}$ )

図 6. 順方向の電流-電圧特性( $T_j=25^\circ\text{C}$ )

図7.  $V_F$ - $E_r$ のトレードオフ特性( $T_j=125^\circ\text{C}$ ,  $V_{CC}=600\text{V}$ ,  $I_F=150\text{A}$ )

である。薄ウェーハダイオードではこの $V_F$ - $E_{rr}$ トレードオフ相関で、同一 $V_F$ で $E_{rr}$ が33%と大幅な改善を実現している。

ダイオードに関する性能指標FOMを式(2)で定義して、従来型ダイオードに対する薄ウェーハダイオードの性能を比較すると38%向上している。

ここで、 $J_A$ はアノード電流密度( $A/cm^2$ )、 $V_F$ は125°Cでの順方向電圧降下(V)、 $E_{rr}$ は125°Cのリカバリー損失(mJ/pulse)を示す。

## 4. む す び

低損失、低ノイズを目指す新型パワーモジュールに向け

1,200Vクラスの第6世代IGBT、及び薄ウェーハダイオード

を開発し、性能指数FOMでIGBT、FWDそれぞれ31%、

38%の改善を実現した。これは次世代デバイスとしての期

待にこたえるものである。

この技術は1,700Vクラスへの応用も行っており、第5世代から大幅な性能改善を確認しており、様々な製品に順次展開することを検討している。今後もSiデバイスの性能改善を継続し、パワーエレクトロニクスの発展と省エネルギー社会の実現に貢献していく。

参 考 文 献

- (1) Takahashi, T., et al.: CSTBT™ (III) as the next generation IGBT, Proceedings of ISPSD 2008, 72~75 (2008)

- (2) Sato, K., et al.: New chip design technology for next generation power module, Proceedings of PCIM 2008, 673~678 (2008)

- (3) Takahashi, H., et al.: Carrier Stored Trench-Gate Bipolar Transistor(CSTBT) -A Novel Power Device for High Voltage Application, ISPSD'96, 349~352 (1996)

- (4) Nakamura, K., et al.: Advanced Wide Cell Pitch CSTBTs Having Light Punch-Through (LPT) Structures, ISPSD'02, 277~280 (2002)

清水和宏\*

衣笠彰則\*

寺島知秀\*

# 第2世代分割RESURF構造を適用したHVIC技術

*High Voltage IC Technology with 2nd Generation Divided RESURF Structure*

Kazuhiro Shimizu, Akinori Kinugasa, Tomohide Terashima

## 要旨

近年の環境問題に対する意識の高まりから、省エネルギー技術への関心は年々増加している。この省エネルギー技術の一つとして注目されるパワーエレクトロニクスで重要な役割を果たしているのが、IGBT(Insulated Gate Bipolar Transistor)やMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)等のパワー半導体素子とそれらを制御する回路技術である。

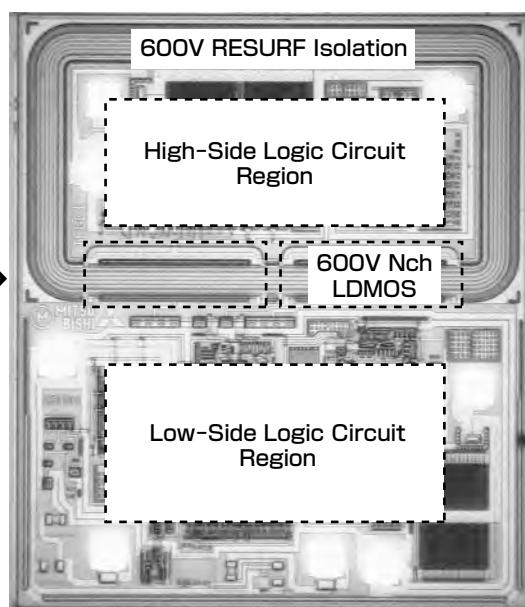

三菱電機では、このパワー半導体素子の制御回路を1チップに搭載したHVIC(High Voltage Integrated Circuit：高電圧集積回路)を開発し、IPM(Intelligent Power Module)の高機能化、差別化のキーデバイスとして継続的な性能改善を行っており、パワー半導体素子の駆動機能に加え、保護機能の強化やROM内蔵、ブートストラップ機能内蔵などを進めている。また、この進化に対応するため、HVICは微細加工技術を適用することで、より大規模な回路の搭載を実現してきた。本稿では第2世代分割RESURF(REDuced SURface Field)構造と、8インチ製造ラ

イン／0.5μm相当のデザインルールを適用した第4世代600V HVICプロセス技術、搭載デバイス特性の概要について述べる。

この最新世代HVICの特徴は次のとおりである。

- (1) N<sup>+</sup>埋め込み拡散層とP<sup>-</sup>エビ基板をベースにした、第2世代分割RESURF構造の適用

- (2) 微細埋め込みマスクパターンで形成した電界緩和構造による高耐圧(800V)の実現

- (3) 8V／24V系素子(CMOS(Complementary Metal Oxide Semiconductor)／Bip.Tr／容量・抵抗類)と600V系Nch／PchMOSを同一チップ上に形成

- (4) N<sup>+</sup>埋め込み拡散層の導入による、高サージ耐量の実現

- (5) レーザトリミング機能の内蔵によって、回路特性の微調整が可能

今後、第4世代HVICの製品展開を行うとともに、1,200Vクラスへの適用を目的とした構造開発を継続する。

600V Nch-LDMOSFET applied

the 2nd generation divided RESURF structure

The 4th Generation 600V HVIC

for Power Device Gate drive

LDMOSFET : Lateral Double-diffused MOSFET

## 第2世代分割RESURF構造を適用した第4世代600V HVICチップ

高電位島分離領域内に高耐圧デバイスを形成可能にする“分割RESURF構造”を第2世代に進化させ、この構造と0.5μm級加工技術と8インチ製造ラインを適用した第4世代の600V HVICプロセスを開発した。

## 1. まえがき

ゲートドライバ用HVICは、パワー半導体素子の駆動に関する、短絡等による素子破壊を防止する保護機能なども含め、統合した機能を持つキーデバイスとしてIPMに広く採用されている。このHVICの構造的な特徴は、低電位領域の制御信号を高電位側回路へ伝達するレベルシフト機能を実現するため、高電位が印加される内部配線を形成可能としたことであるが<sup>(1)</sup>、この配線に対する層間絶縁酸化膜の耐量などを考慮すると、HVICの高耐圧化は600Vクラスが限界であった。当社では独自の“分割RESURF構造”を開発することでこの限界を克服し、1,200V耐圧のHVICを実現した<sup>(2)(3)</sup>。この第1世代分割RESURF構造は高耐圧化に適していたが、深いN拡散層を基本構造としてデバイスを構築しているため、縦方向の寄生PNPが容易に動作し、それを抑制するために素子レイアウト設計の自由度を制限していた。この問題点を解決する目的で、P<sup>-</sup>基板/P<sup>-</sup>エピ層とN<sup>+</sup>埋め込み層(NB)，微細マスクパターンから形成されるマイクロN<sup>+</sup>埋め込み層(μ-NB)を適用した第2世代分割RESURF構造を開発した。

本稿では第2世代分割RESURF構造と、この構造を適用した最新のHVIC技術について述べる。

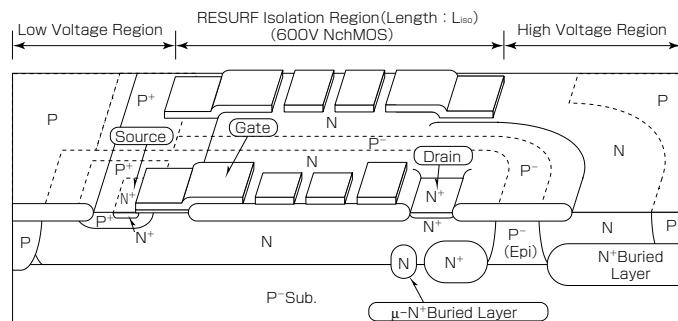

## 2. デバイス構造及びプロセス

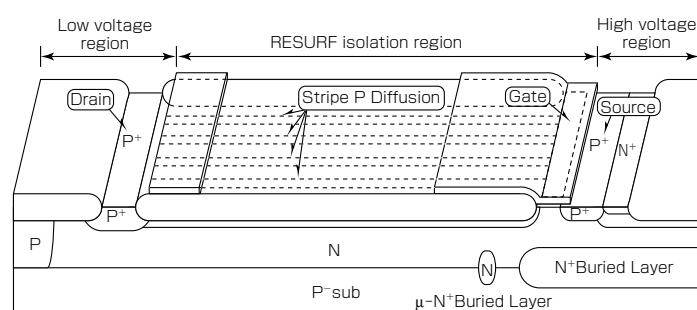

図1に、第2世代分割RESURF構造を適用した高耐圧Nch-LDMOSFETの断面図を示す。P<sup>-</sup>基板上にP<sup>-</sup>エピ層を形成しているため、RESURF領域となるN拡散層は、リンの高エネルギー注入と高温拡散プロセスによって形成している。デバイス構造でNBを導入することで、第1世代型の問題点であったロジック領域下部に存在する寄生PNP動作を抑制できる。また、P<sup>-</sup>エピ層をP<sup>-</sup>基板と同一濃度として、分割部が高電圧印加時に完全に空乏化し、電界集中による降伏が発生しない構造にできる。

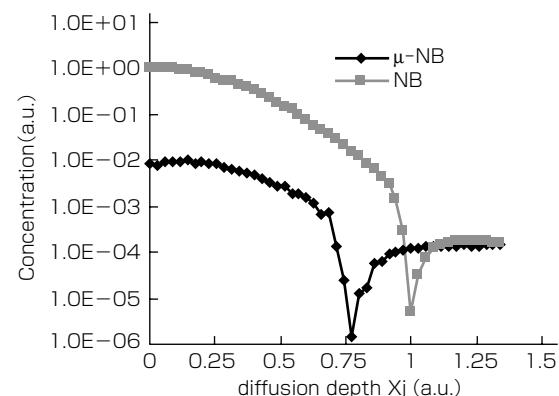

一般にNBは、浅くかつ高濃度にすると、面積が小さく寄生動作に対し効果的な分離構造が形成できる。一方、深くかつ低濃度の場合、拡散終端コーナー部での電界集中を緩和できるので、高耐圧分離に適している。この背反する

図1. 第2世代分割RESURF構造を適用した高耐圧Nch-LDMOSFETの断面構造

要求項目にこたえるために、μ-NB構造を新たに導入した。この構造では微小領域からの不純物拡散によって、同一の製造工程で広い面積部(NB部)より低濃度の拡散層が形成できる効果を利用していている。図2に、テストパターンにおけるNB部とμ-NB部の不純物プロファイルを示す。μ-NB部のパターンは等間隔の点(微小領域)で形成されており、各拡散層はSR(Spreading Resistance)法で測定した。微小な不純物導入部からの三次元的な拡散によって、μ-NB部ではNB部と比較して表面濃度は1%程度と低いにもかかわらず、拡散深さは75%程度を確保できている。したがって、NBパターンの終端部にμ-NBパターンを配置することで、電界を緩和することが期待できる。今回開発した第2世代分割RESURF構造は、8インチ製造ライン/0.5μmルール相当のウェーハプロセス技術を適用しており、8V/24V系素子(CMOS/Bip.Tr/容量・抵抗類)と回路特性の高精度化を目的としたレーザトリミング機能が搭載されている。

## 3. デバイス特性

### 3.1 RESURFダイオードの耐圧特性

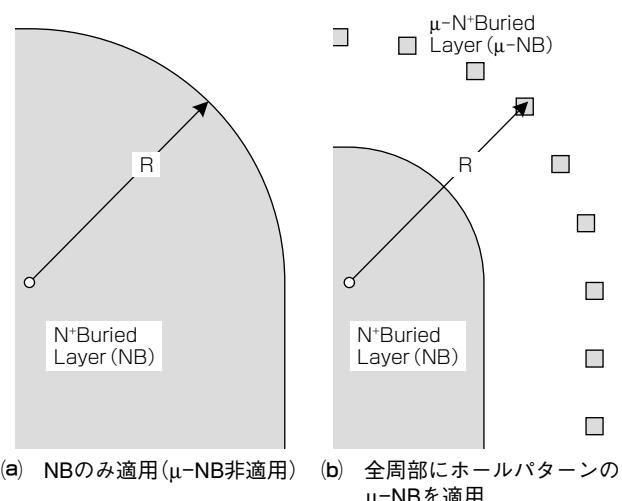

図3に、デバイス耐圧実験に使用したμ-NBのパターンレイアウトを示す。

図2. NB部及びμ-NB部の不純物拡散プロファイル

図3. NB及びμ-NBのパターンレイアウト

なお、このパターン端はすべて同一の半径  $R$  となるよう設計されている。

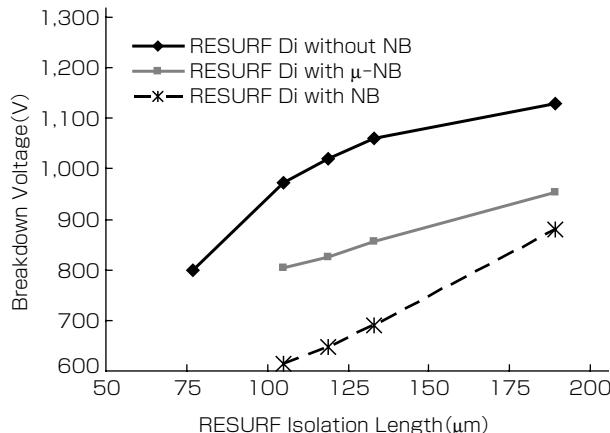

図4に、図3(a)(b)の2種類のN<sup>+</sup>埋め込み拡散層パターンを適用した場合と、NBを全く適用しない場合のRESURFダイオード耐圧の分離距離Liso(図1)依存性を示している。Liso=119μmの場合、NBなし構造の耐圧は1,020Vである。この基本構造にNB構造を付加すると耐圧は640Vにまで大きく低下するが、μ-NB構造を適用することで815Vに改善される。この値は、NB構造のLiso=170μmにおける耐圧と同等である。これはμ-NB構造を採用することでRESURF分離距離が50μmも縮小できることを示しており、μ-NB構造はチップ面積縮小にも効果的であるといえる。

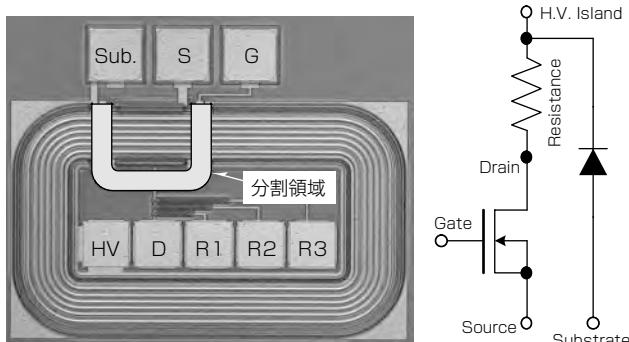

### 3.2 高耐圧Nch-LDMOSFET/Pch-MOSFETの特性

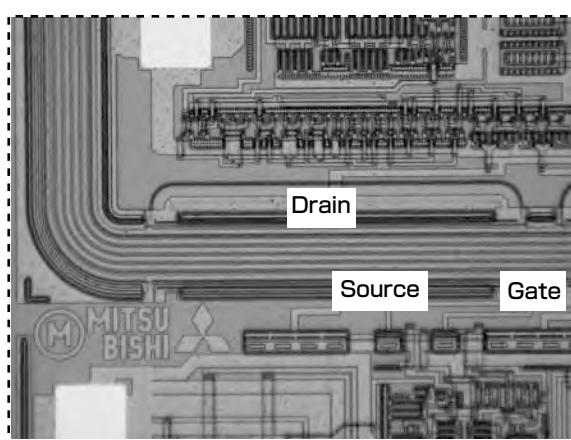

図5に、第2世代分割RESURF構造を適用したNch-LDMOSFETのチップ写真とその等価回路を示す。分割領域はP<sup>-</sup>エピ層で形成されており、その上部はNch-LDMOSFETのドレイン電極に接続されたポリシリコンのフィールドプレートでカバーされている。またドレイン電極はポリシリコンフィールドプレート上に形成したアルミ配線によって、高電位島内の電極パッドに接続されている。

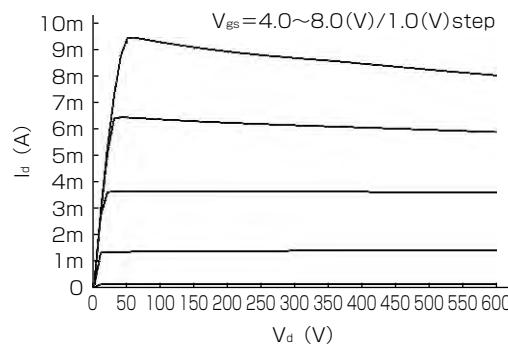

図6に、Nch-LDMOSFET(Liso/Wgate=119μm/140μm)のI-V特性を示す。オン抵抗は、 $V_d=5V/V_g=$

図4. RESURFダイオード耐圧のLiso依存性評価結果

図5. Nch-LDMOSFET(分割RESURF構造)のチップ写真と等価回路

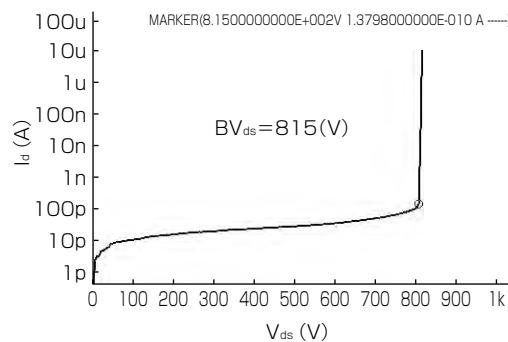

15V印加時で2.5kΩが得られている。またオン耐圧は、 $V_g=\sim 8V/I_{ds}=8mA$ の範囲でレベルシフト動作に要求される600V以上を確保している。図7に示すように、オフ耐圧は815Vであり、この値は先に述べたRESURFダイオード構造で同じ分離距離(Liso=119μm)の場合と同じ耐圧である。これは分割領域を形成するP<sup>-</sup>エピ層が完全に空乏化して、この不連続部で耐圧劣化を引き起こさないことを示している。分割領域で、高電位島部とNch-LDMOSFETのドレイン部間のパンチスルーフ耐圧は35Vであり、レベルシフト回路の動作上十分な値が確保できている。

図8に、高耐圧Pch-MOSFETの断面構造を示す。Pch-MOSFETは、RESURF分離領域にP<sup>-</sup>オフセットドレイン層を付加した自己分離構造として形成できる。今回P<sup>-</sup>オフセットドレイン層パターンを、従来の全面パターンからスリットパターンに変更することで、耐圧と出力電

図6. Nch-LDMOSFETのI-V特性

図7. Nch-LDMOSFETのオフ耐圧波形

図8. 高耐圧Pch-MOSFETの断面構造

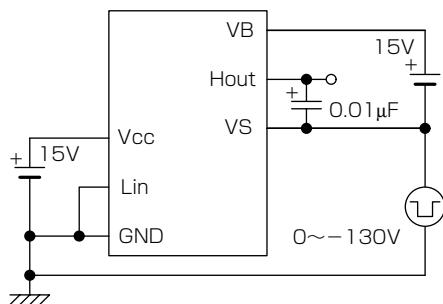

図9. ラッチアップ破壊耐量評価回路

流のトレードオフを改善した。スリット構造を適用すると、ドレイン層の総断面積が減少し抵抗値が増加するというデメリットがあるが、N領域に対する表面積が増加するため空乏層形成が促進されるというメリットがある。このため従来構造では高耐圧を保持できない、比較的濃度の高いオフセットドレイン層を導入しても高耐圧保持が可能になり、抵抗値が低くなることで出力電流が増加し特性を改善できた。今回の試作デバイス( $L_{iso}/W_{gate} = 119\mu m/140\mu m$ )は、オフ耐圧800V／オン抵抗 $20k\Omega @ V_d = 5V / V_g = 15V$ であり、従来構造の同耐圧品より約2倍の出力電流が得られた。また、オン耐圧もゲート印加電圧が-15V以上で-600Vを保持できており、レベルシフト素子として十分な特性を持っている。

### 3.3 ラッチアップ破壊耐量

ゲートドライバ用HVICが使用されるインバータ回路は、モータ等のL負荷に大電流を供給するため、スイッチング動作時に大きなサージ電圧が発生する。この影響で、HVICの高電位側回路基準電位となるVS端子には、負バイアスが印加される。PN接合分離が順バイアスされることでHVIC内部に過大な電流が発生し、CMOS構造の寄生サイリスタが動作してラッチアップ破壊が起こる。このためHVICは、この負サージ電圧に対する破壊耐量の大きさも重要な特性となる。

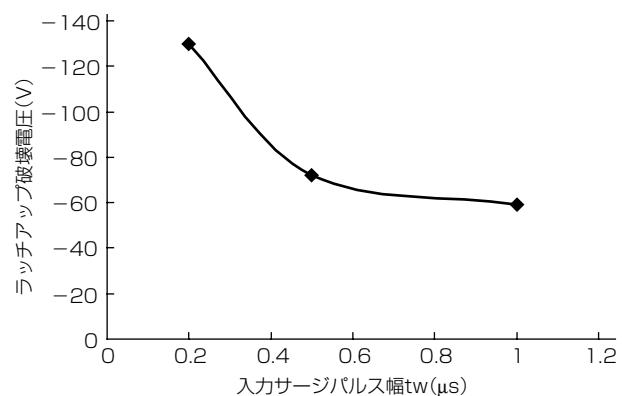

図9に、VS端子における負サージ電圧のラッチアップ破壊耐量への影響を評価する回路を示す。HVIC内部回路がラッチアップ破壊するまで、負電圧を矩形(くけい)パルス幅0.2~1.0μsの範囲で印加している。図10に、室温におけるラッチアップ破壊耐量評価結果を示す。今回の試作デバイスでは、入力サージパルス幅1.0μs以下でサージ破壊電圧を-60V以上確保している。

図10. ラッチアップ破壊耐量評価結果

### 4. むすび

P-基板/P-エピ層とμ-NB構造を適用した、第2世代分割RESURF構造を開発した。μ-NB構造はこれを適用しない通常のNB構造と比較して、小さいRESURF分離距離で同一耐圧を得ることができた。また第2世代分割RESURF構造は、分割部のP-エピ層が完全に空乏化することで、これを形成しない基本のRESURFダイオード構造と同一の耐圧値が得られることを確認した。このことは更に高耐圧の1,200VクラスのHVICにも適用可能であることを示唆しており、現在この耐圧クラスのHVIC開発を進めている。

### 参考文献

- (1) Terashima, T., et al.: Structure of 600V IC and a new voltage sensing device, Proc. ISPSD, 224~229 (1993)

- (2) Terashima, T., et al.: A New Level-shifting Technique by divided RESURF Structure, Proc. ISPSD, 57~60 (1997)

- (3) Donlon, J., et al.: A New 1200V Converter-Inverter-Brake(CIB) Module Family Featuring CSTBT Chips and a New 1200V High Voltage Integrated Circuit(HVIC), Industry Applications Conference, 2006. 41st IAS Annual Meeting. Conference Record of the 2006 IEEE Volume 2, Issue, 763~769 (2006)

# ダイレクトリード接合型 大容量パワーモジュール

菊池正雄\* 中島 泰\*\*

上田哲也\* 平岡功治\*\*

新飼雅芳\*

*Direct Lead Bonded High Performance Power Module*

Masao Kikuchi, Tetsuya Ueda, Masayoshi Shinkai, Dai Nakajima, Koji Hiraoka

## 要 旨

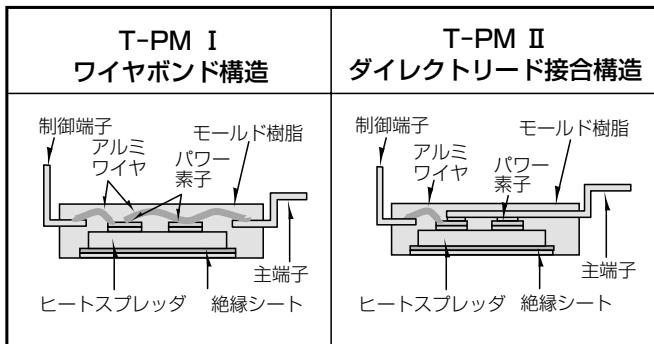

三菱電機では、パワーデバイスを搭載した絶縁基板をケースに収納してゲル充填(じゅうてん)したゲル封止型モジュールの構造・製造合理化を目的に、半導体パッケージング技術を応用したトランスマーキード型パワーモジュール(Transfer molded-Power Module : T-PM)を1997年に上市した。生産規模が大きい家電向け等の小容量機種から容量増加を進め、現在では産業用途に使用可能な300Aクラスのパワーモジュールまで適用範囲を拡大してきた。

T-PMでは、従来のゲル封止構造と異なって、硬質のモールド樹脂で封止する構造となっているため、デバイスと被接合材との熱応力を分散する効果が、信頼性向上に大きく貢献した。このことは、産業用途等の分野におけるT-PMの大きな強みとなっている。

さらに、当社独自のT-PMのパッケージ構造を進化さ

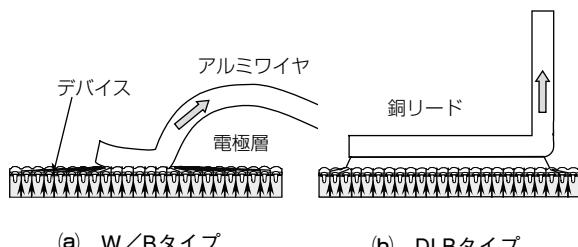

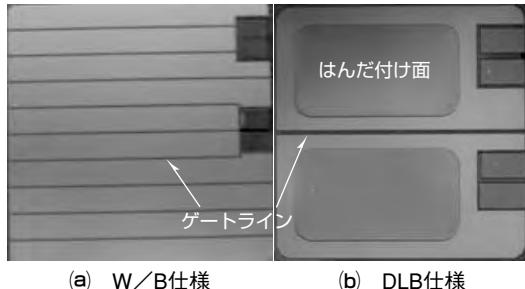

せるため、新しい配線構造を提案した。すなわち、元来リードフレームによって配線を形成するため、リードフレームに設けたインナーリードをデバイス上部まで延長し、直接デバイス表面の電極に接合することで、ワイヤボンドを必要としないパワーモジュールが製造可能となった。当社では、このT-PMを“ダイレクトリード接合型パワーモジュール(DLB T-PM)”と呼び、新しいパワーモジュールとして提供している。

DLB T-PMは、これまでのワイヤバンド構造に対して大面积接合構造となるため、パッケージの特性面や、特に熱応力に起因する信頼性の点で、より大きな電流容量に適したパワーモジュールとなっている。

本稿では、DLB T-PMの特長及び製造上の工夫について述べる。

T-PMの外観と内部構造

## DLB T-PMの特長

- ①内部配線の省スペース化

- ②接合強度の向上

- ③内部配線抵抗の低減

- ④自己インダクタンスの低減

- ⑤接合部信頼性の向上

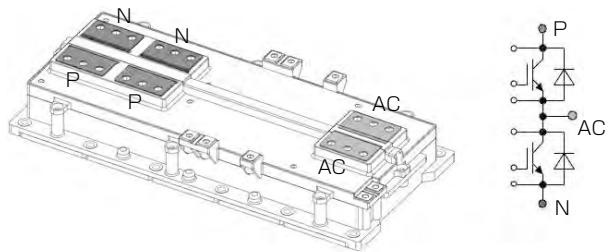

## DLB T-PMの構造と特長

上下アームで回路構成されたT-PMの外観と内部構造を模式的に示す。DLB T-PMでは、多数のワイヤボンドからリードフレームを延長した1枚のリードに、デバイス上の配線材を置き換えた。DLB構造では、T-PM本来のメリットに加え要旨で述べた特長を備えた、大容量化に非常に適したパワーモジュールである。

## 1. まえがき

当社は、半導体パッケージング技術を応用した“トランスマーモールド型パワーモジュール(Transfer molded-Power Module : T-PM)”を、製造合理化の効果が大きい家電向け等の小容量機種から供給を開始して以来徐々に容量増加を図り、現在では産業用途に使用可能な300Aクラスまで適用範囲を拡大してきた<sup>(1)</sup>。

さらに近年では、これまでデバイスからの配線方法として主流であったワイヤボンド方式にとって代わり、インナーリードを直接デバイス表面に接合する“ダイレクトリード接合型パワーモジュール(Direct Lead Bond T-PM : DLB T-PM)”を開発し、より高い信頼性、生産性を備えたパワーモジュールの提供を続けている。

本稿では、当社独自のDLB T-PMの特長並びに工夫点について述べる。

## 2. ダイレクトリード接合型パワーモジュールの構造的特徴

### 2.1 従来構造との比較

表1に、当社パワーモジュールの構造を比較した。従来構造であるゲル封止構造では、パワーデバイスを搭載した絶縁基板をベース板にはんだ付けする。パワーデバイスの電極面と基板、ケースに取り付けられた金属ターミナルはアルミワイヤをワイヤボンディングして配線する。その後、シリコンゲルを充填してケース内部を保護する。

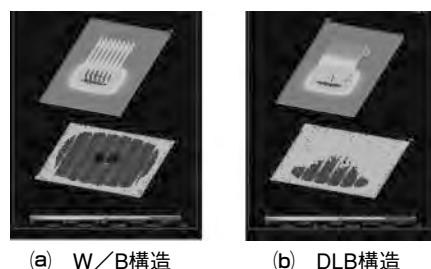

一方、第1世代T-PMの場合、熱拡散を目的としたヒートスプレッダにパワーデバイスを直接はんだ付けし、主端子及び制御端子とデバイスをワイヤボンドで配線する。その後、これらの部材をトランスマーモールドによって封止し、部材を保護、保持する。T-PMでは、ケースとゲルといった複数の保護材を必要とせず、また、あらかじめ端子をケースに保持する工程も不要となるため、生産性が高い構造となっている。

しかしながら、ワイヤボンド(W/B)構造の場合、大容量化に伴って多数のワイヤを接合する必要がある。それに対して、DLB構造では、主端子となるインナーリードがデバイスの直上まで延ばされ、直接デバイス表面にはんだ付けすることによって、従来のゲル封止構造では困難であった多数のワイヤの1本の金属リードへの置き換えを実現

した。なお、デバイス表面電極には、はんだ付け可能なメタライズ層を形成している。

### 2.2 DLB構造の性能上のメリット

これまで述べてきたDLB構造、その構造的特徴によって、次のような大容量化に適した利点を持つ。

#### (1) パッケージ内部配線の省スペース化

ボンディング作業に必要なスペースを削減できる。

#### (2) 接合強度が向上

W/B構造に比べて大きな接合部を形成することができる。

#### (3) 内部配線抵抗を低減

図1(a)のように、W/B構造では、ワイヤボンド部へとデバイス表面の薄い電極層の通電抵抗が大きくなる。一方、DLB構造では、図1(b)のようにデバイス表面に面積が大きい銅リードを接合するため、電流経路はデバイス厚さ方向のみに短縮される。このため、後者の方が配線抵抗が小さくなり、当社実績では配線抵抗が半減している。

#### (4) 自己インダクタンスの低減

配線が平面構造となることや、リードとヒートスプレッダを近接配置できるため、図2に示すように、DLB構造はW/B構造に対して、約40%低減できる。

さらに、DLB構造は、W/B構造に対して、デバイスの配線接合部に対する長期信頼性の飛躍的な向上を実現できるが、これに関しては3章で述べる。

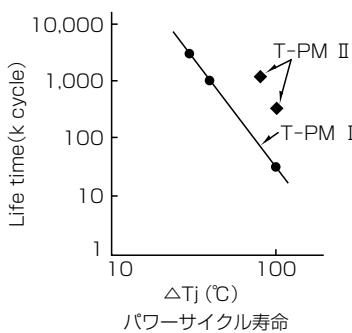

## 3. ダイレクトリード接合部の信頼性

元来、T-PMは、デバイスの配線接合部の温度サイクルに対して高い信頼性が得られる構造となっている<sup>(2)</sup>。これは、図3に示すように、ゲルに比べて硬いモールド樹脂が、線膨張係数差が大きいシリコンからなるデバイスとアルミワイヤ、又はヒートスプレッダ間に発生する熱応力を分散することによる。DLB構造の場合も同様に、モールド樹脂による応力分散効果で、信頼性の向上が実現できる。

図1. パワーモジュールの接合構造の比較

表1. パワーモジュール構造の比較

| ゲル封止構造                              | 第1世代 T-PM<br>W/Bタイプ                                              | 第2世代-T-PM<br>DLBタイプ                                              |

|-------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|

| アルミワイヤ<br>絶縁基板<br>ゲル<br>ケース<br>ベース板 | 制御端子<br>アルミワイヤ<br>モールド樹脂<br>パワーモジュール<br>ヒートスプレッダ<br>絶縁シート<br>主端子 | 制御端子<br>アルミワイヤ<br>モールド樹脂<br>パワーモジュール<br>ヒートスプレッダ<br>絶縁シート<br>主端子 |

図2. インダクタンスの比較

図3. 接合部の歪(ひずみ)量

図4. パワーサイクル寿命

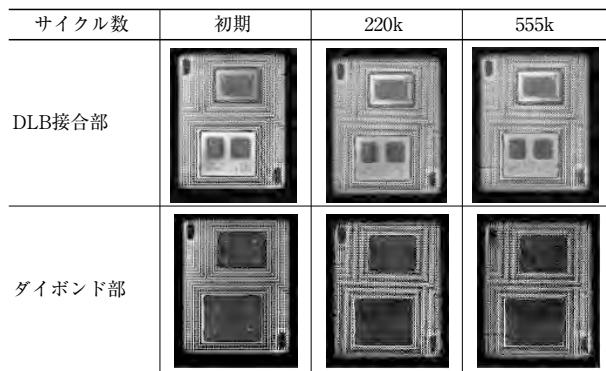

表2. パワーサイクル試験における接合部の超音波画像( $\Delta T=70K$ )

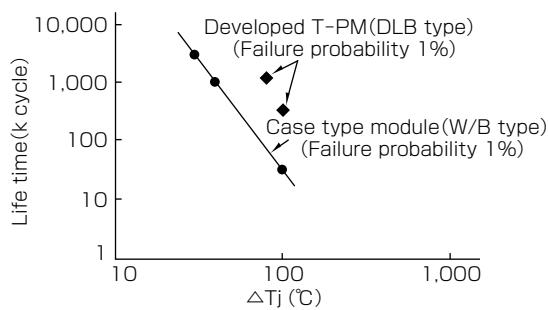

図4に、表1で比較した各々のモジュール構造におけるパワーサイクル試験結果を示す。モールド封止型構造では、ゲル封止型構造に比べて長寿命化されており、さらに、DLB構造のパワーサイクル寿命は、W/B構造よりも5倍超に延びる。表2は、デバイス裏面の接合部の超音波画像であるが、DLB接合部、ダイボンド部いずれも初期に比べて、接合部の亀裂(きれつ)の進行がほとんど認められない。

先に述べたように、T-PMはモールド封止によって温度サイクル寿命が向上するが、DLB構造固有の構造的特徴によって一層の長寿命化が図れる。

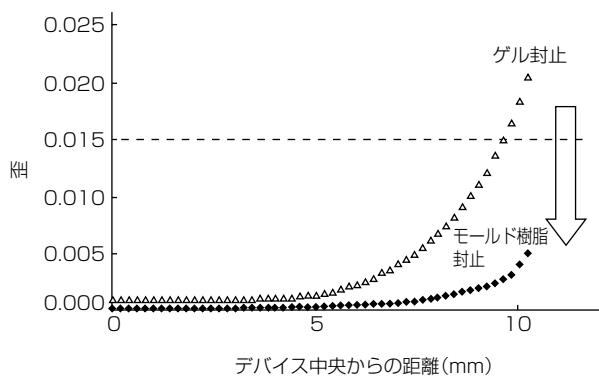

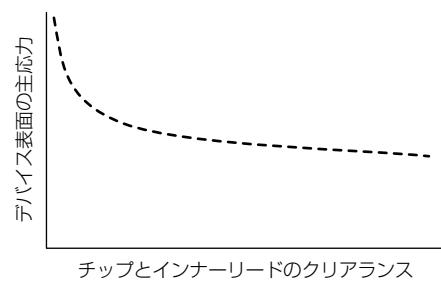

ここでは、図1で示した電流経路の違いに着目し、通電発熱時の温度分布を解析した。その結果、図5のように、W/B構造が比較的デバイス中央部に高い温度領域が存在する一方、DLB構造では、接合部下方に温度分布が広が

図5. 通電時の発熱状態(電気-熱連成解析)

りかつ平坦(へいたん)化していることがわかった。W/B構造では、最も熱応力を受ける中央部のワイヤから順次加速的にワイヤの破壊が進行するが、DLB構造では、亀裂導入部となるはんだ付け端部は、比較的低い温度に抑制されるため、亀裂が進行しづらいものと考えられる。すなわち、電流経路による温度分布の違いが寿命の違いとなって現れたものと考えている。

もちろん、亀裂進展に対する寿命は、デバイスとリード間の線膨張ミスマッチを受け持つはんだ層の緩衝作用、すなわち層厚さに依存するため、厚さの適正化並びに制御が必要となる。

パワーモジュールにとって、接合部の信頼性の向上は次の付加価値を生み出す。

#### (1) システムの高信頼化

近年、環境負荷軽減を背景に自動車分野をはじめ産業、エネルギーなど様々な分野でパワーエレクトロニクスシステムの応用が進んでおり、パワーモジュールの高信頼要求にこたえることができる。

#### (2) より厳しい動作条件への適用

高い信頼性が確保できれば、パワーデバイスを高温で動作させることができると、高性能化やコストメリットを訴求できる。

今後は、これらのシステム全体の付加価値向上に貢献していきたいと考えている。

## 4. DLB T-PMの生産設計

### 4.1 DLB T-PM製造プロセス

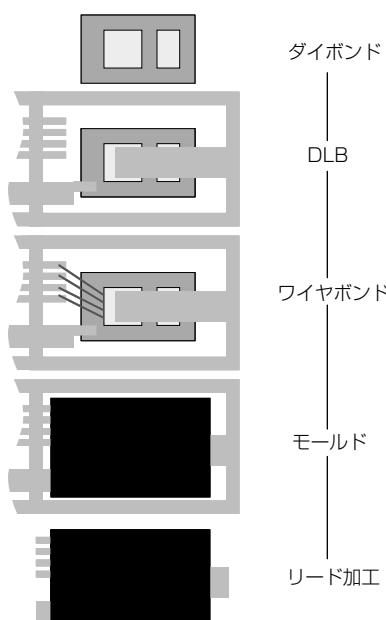

DLB T-PMは、広く普及した半導体パッケージのアセンブリ技術をベースとしたフローで製造される。すなわち、図6のようにリードフレームでベアチップのアセンブリ工程を流し、トランシスターモールド、リード加工を経てT-PMの形状に仕上げる。当然のことながら、従来のW/B構造とは、デバイス上面の配線接合工程が異なるが、その他の工程はほぼ従来工程をベースに設計されており、十分に実績のあるプロセスで製造されている。

### 4.2 DLB接合プロセスについて

DLB構造では、はんだ接合が品質を支配するため、できるだけ簡便なプロセスを作りこむことによって品質を安定化させることが肝要である。

図 6. DLB T-PM 製造フロー

図 7. デバイス表面構造

#### 4.2.1 表面電極構造の検討

デバイス表面は、各セル上に金属電極層が形成されているが、当社のこれまでのデバイスは、図 7(a)のように、これらのセルを駆動するゲート電極への複数の配線(ゲートライン)が表面に形成されており、面積が大きいリードを接合すると、ゲートライン上に接合することとなる。したがって、DLB構造では、図 7(b)のようにはんだ付け面にゲートラインが重ならないように設計している。

#### 4.2.2 必要なはんだ厚さの確保

DLB構造の寿命設計には、はんだ付け厚さを制御することが重要である。すでに当社では、ゲル封止型モジュールの絶縁基板とベース板とのはんだ付けで、ワイヤバンプによってはんだを所望の厚さ以上にすることで寿命向上を図っており<sup>(3)</sup>、ダイレクトリード接合部でも、図 8 のように所定の厚さ以上で応力は飽和して寿命を確保できる。

図 8. DLB部はんだ厚さと応力

図 9. DLB部断面

DLB T-PMでは、インナーリードとデバイスとの間隔をパッケージ設計と治具設計によって制御し、はんだを供給することで極めて簡便にはんだ厚さを制御している。図 9 は、DLB接合部断面であるが、リードに穴が形成されており、デバイス上をぬれ広がってなお余剰のはんだはリード上部にぬれ広がることで、十分なはんだ量を供給しつつ、はんだのはみ出しも防止している。

### 5. むすび

T-PMの新たな取組みであるDLB T-PMでは、①パッケージ本体のパワー密度を増加できる、②ダイレクトリード接合部のヒートサイクル信頼性が高いといったメリットがパワーモジュールの大容量域への適用拡大に極めて有用であり、環境負荷軽減にますます普及の加速が見込まれるパワーエレクトロニクスシステムのダウンサイジングに対して、当社ではDLB T-PMの展開を図るとともに、より進化したパワーモジュールの提供を続けていく所存である。

### 参考文献

- (1) 菊池 巧, ほか: モールド型パワモジュール用絶縁シート, 三菱電機技報, 81, No.5, 365~368 (2007)

- (2) 杉木昭雄, ほか: 樹脂封止型パワモジュールのAlワイヤボンド部の信頼性に関する研究, Mate2007論文集 (2007)

- (3) Hayashi, K., et al.: Improvement of Fatigue Life of Solder Joints by Thickness Control of Solder with Wire Bump Technique, ECTC2002

# “Rシリーズ” HVIPM

*"R series" HVIPM*

Hitoshi Uemura, Isao Umezaki, Kazuhiro Morishita, Ryosuke Nakagawa

上村 仁\* 中川良介\*\*

梅寄 勲\*

森下和博\*

## 要 旨

世界的な環境意識の高まりに対し、電気鉄道による旅客・貨物輸送は環境負荷の低い輸送手段としてその重要性が高まっている。大型電力変換装置に使用されるパワー半導体デバイスの主流は、十数年前まで広く採用されていたGTO(Gate Turn Off)サイリスタから、IGBT(Insulated Gate Bipolar Transistor)モジュールなどの新しいデバイスへと大きく変遷している。

三菱電機では、鉄道車両用パワーデバイスに対する要求事項にこだえるため、これまでにも高耐圧化、大電流化、低損失化、高機能化としてHVIPM(High Voltage Intelligent Power Module)の開発を行ってきた。そしてこのたび、これらの要求事項及び高温動作化を実現した“Rシリーズ”HVIPMを開発した。

RシリーズHVIPMの主な特長を次に示す。

### (1) 動作温度

新構造のIGBT・Diodeチップと、温度特性を改善したパッケージ材の採用によって、3.3kV耐圧RシリーズHVIPMの最大動作温度を150°Cに拡大し、高温動作を可能とした。

### (2) 定格電流

低損失IGBTとDiode及び低抵抗電極の採用によって、定格電流を従来比25%向上した。

### (3) 保護動作

過熱保護のためにIGBTチップに温度検出用のセンサを内蔵し、HVIPMの制御回路に搭載している専用ICとの組合せによって、高精度で応答性の良い保護動作を実現した。

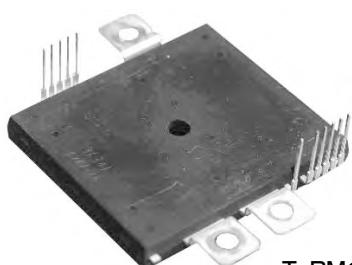

3.3kV耐压 Rシリーズ HVIPM

6.5kV耐压 Rシリーズ HVIPM

## “Rシリーズ” HVIPMの外観

RシリーズHVIPMでは3.3kV耐圧と6.5kV耐圧をラインアップしており、3.3kV耐圧のHVIPMは絶縁耐圧6kV、6.5kV耐圧のHVIPMは10.2kVの絶縁耐圧を持つパッケージを採用した。さらに、RシリーズHVIPMは従来のHVIPMの外形や電極端子配置などを変更せずに互換性を持たせており、素子の置き換えを容易に行うことを可能とした。

## 1. まえがき

近年、世界的に環境問題が大きくクローズアップされる中、CO<sub>2</sub>排出量の少ない電気鉄道(以下“電鉄”といふ。)の役割が非常に重要となってきている。

電鉄市場から高耐圧IGBTモジュール(以下“HVIGBT”といふ。)に対する要求は、高信頼性であることはもちろんのこと、低電力損失、大電流定格及び高温動作への対応が期待されている。

当社はHVIGBTに駆動回路、保護機能を内蔵した鉄道車両用電力変換装置に適用可能な大電力容量のHVIPMを他社に先駆けて開発し、1997年に新幹線の推進制御用として採用されて以来、多数の採用実績を誇っている。今回、先に述べた要求性能を満足させるために、3.3／6.5kV耐圧のRシリーズHVIPMを開発した。

本稿では、3.3kV耐圧のRシリーズHVIPMの電気的特性を中心として、要求性能に対するRシリーズHVIPMの特長と評価結果について述べる。

## 2. RシリーズHVIPMの特長

RシリーズHVIPMは、次に示す設計コンセプトを基本として開発を行った。

- (1) 損失の低減：IGBTとDiodeを新規に開発し、低損失化を図った。

- (2) 動作温度範囲の拡大：新構造のIGBT、Diodeの採用とパッケージ材料の見直しによって最大動作温度150°Cを実現し、低温側も-50°Cの動作を可能とした。

- (3) 定格電流アップ：従来のHVIPMに対して、25%の電流定格アップを実現した。

- (4) 保護性能アップ：電流検出、温度検出をIGBTチップに内蔵し、さらに制御基板に搭載している専用ICと組み合わせて使用することによって高精度な保護を実現した。

- (5) 高信頼性：電鉄用途は高信頼性が要求されるため、安全動作領域に対しても十分な破壊耐量を確保した。また、パッケージ構造の最適化によって信頼性も向上させた。

### 2.1 RシリーズIGBTチップ

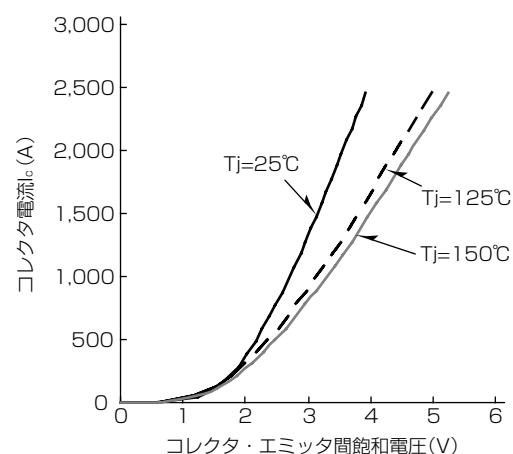

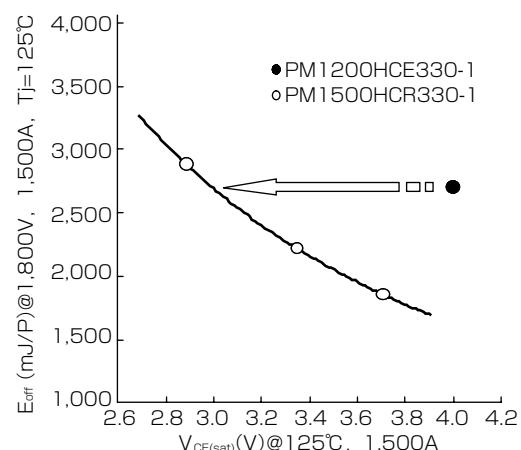

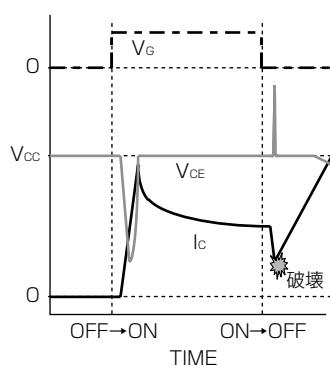

IGBTチップは従来のPT(Punch Through)からLPT(Light Punch Through)構造に変更し、セル構造を最適化することによってオン電圧( $V_{CE(sat)}$ )の低減を実現した。また、図1に示す出力特性が“温度が上昇するほどに電流が減少する”負帰還特性になっており、並列接続時のHVIGBT間の電流バランスは安定的に保たれ、複数のモジュールを並列接続して用いることも容易となる。図2は $V_{CE(sat)}$ と $E_{off}$ のトレードオフカーブを示しており、従来のHVIPMに対して同一の $E_{off}$ で比較した場合に、 $V_{CE(sat)}$ が25%低減された。

## 2.2 動作温度拡大

従来のHVIPMの動作温度範囲は、IGBTとDiodeの電力損失の増加による熱破壊や構成される材料の制約などから、-40°Cから+125°Cに制限されている。今回、新構造のIGBTとDiodeの採用によって、電力損失を低減することで高温動作を可能にした。また、温度範囲を制約する構成材料として、絶縁性能を確保するために封入されている充填(じゅうてん)材(シリコーンゲル)がその一つに挙げられる。当社は材料メーカーと協力し、温度特性を大幅に改善した新充填材を開発することによって、使用可能な動作温度範囲を-50°Cから+150°Cまで拡大した。今回、動作温度範囲の拡大を実現したことによって、システムの高出力化や冷却器設計の自由度を高めることができた。

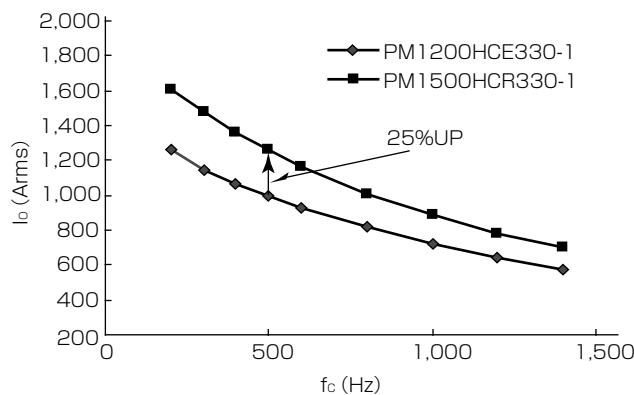

## 2.3 定格電流アップ

3.3kV耐圧のRシリーズHVIPMの最大定格電流は、従来の1,200Aに比べ25%増の1,500Aとすることができた。その一例に、スイッチングキャリア周波数を係数としてインバータ出力電流を計算した結果を図3に示す。T<sub>jmax</sub>=125°C条件下で比較した場合、インバータ出力電流はスイッチングキャリア周波数500Hzで、現行比250A(約25%)

図1. コレクタ・エミッタ間飽和電圧特性

図2. RシリーズHVIPMと従来HVIPMのトレードオフ比較

増加でき、さらに $T_j = 150^\circ\text{C}$ とした場合は、約550A(約55%)出力電流を増加させることが可能である。また、電流增加に伴い、主電極発熱の影響が懸念されるため、内部配線構造の最適設計によって配線抵抗を従来比50%低減させることで、定格電流アップを可能とした。

## 2.4 保護機能の精度アップ

当社のHVIPMに備えられた制御電源低下保護(UV)、過電流保護(OC)、過熱保護(OT)を精度良く、かつ、個体差などのばらつきを小さくすることによって、電力変換装置の余分な設計マージンが不要となり、経済的で高性能な装置設計が可能になる。

また、電鉄の場合、加速・減速などの動作頻度が高く、積載量や乗車率、傾斜勾配(こうぱい)の変化も多いことから、瞬間的な過電流や急激な温度変化なども想定されるため、異常時の迅速な保護動作が必要不可欠となる。

RシリーズHVIPMではIGBTチップに電流センサを内蔵しており、専用ICと組み合わせることで、より高精度な過電流保護を実現している。

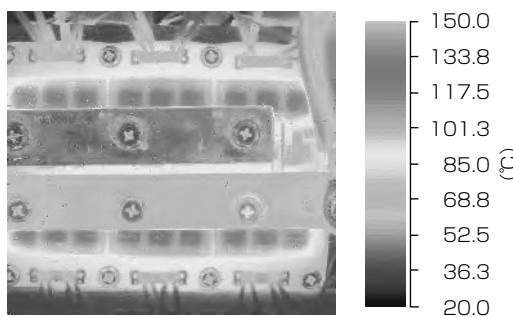

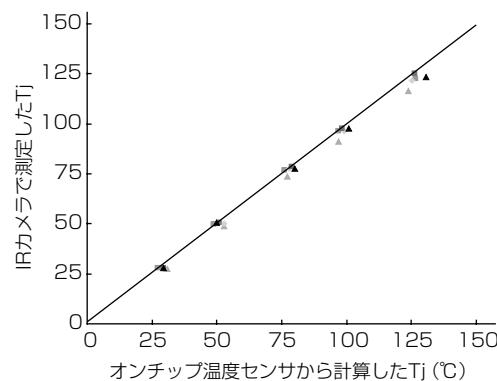

図4にRシリーズHVIPMの面内温度分布、図5にオンチップ温度センサの測定精度を示す。電流センサと同様に温度センサもIGBTチップに内蔵しており、IR(赤外線放射)カメラで表面温度を測定した結果とオンチップ温度センサで測定した結果を比較すると、どの温度領域に対しても高精度でチップの温度を検出できていることがわかる。

図3. インバータ出力電流

( $V_{cc}=1,800\text{V}$ ,  $T_i=60^\circ\text{C}$ ,  $f_o=50\text{Hz}$ , P.F=1,  $T_{jmax}=125^\circ\text{C}$ )

図4. 面内温度分布( $T_i=25^\circ\text{C}$ ,  $I_c=900\text{A}$ )

また、制御基板に搭載している専用ICと組み合わせることで、応答性を向上した精度の高い過熱保護を実現した。

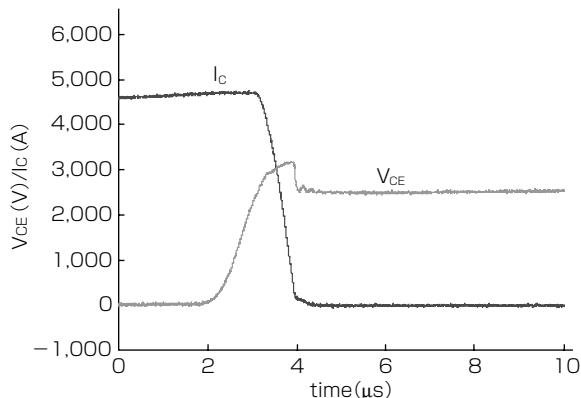

## 2.5 高破壊耐量

適用される市場の特殊性から、HVIPMには高い信頼性が求められ、安全動作領域に対して十分な破壊耐量を持つこともその一つに挙げられる。図6に、RシリーズHVIPMの最大接合温度150°C時の定格電流の3倍遮断(2,500V / 4,500A)波形を示す。動作波形で異常な挙動などなく安定した動作が確認できた。

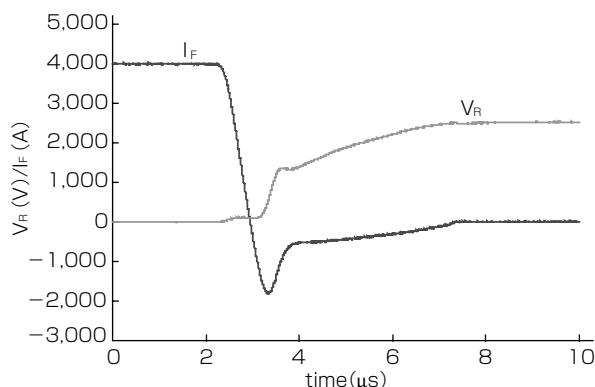

図7にDiodeの逆回復波形を示す。IGBTと同様に接合温度150°Cで実施し、定格の2.5倍の順方向電流(2,500V / 4,000A)を通電している。新構造のDiodeはソフトリカバ

図5. オンチップ温度センサ(6点測定)の温度測定精度

図6. 遮断試験波形

( $V_{cc}=2,500\text{V}$ ,  $I_o=4,500\text{A}$ ,  $T_j=150^\circ\text{C}$ )

図7. 逆回復試験波形

( $V_{cc}=2,500\text{V}$ ,  $I_f=4,000\text{A}$ ,  $T_j=150^\circ\text{C}$ )

リーとなる設計にしており、リカバリー時の振動などを抑制し破壊耐量を向上させている。耐量試験では破壊耐量の指標となるピーク損失が、スペック比の約3倍の余裕度があることを確認した。

## 2.6 パッケージの互換性

図8に3.3kV耐圧RシリーズHVIPMの外観を示す。RシリーズHVIPMは従来のHVIPMの外形や電極端子配置、信号のインターフェースを変更せず、パッケージの内部構造について改良を行っている。これによって、既存システムからの置き換えなども容易に行うことができる。

## 3. む す び

RシリーズHVIPMの適用によって、高温動作利用やインバータ損失の低減、出力電流の拡大が可能となり、主変換装置の小型化や高出力なシステムの構築が可能となった。

今後も多様化するユーザーからのニーズを反映した製品開発を行い、更なる高性能かつ高信頼性の製品を提供していく所存である。

図8. 3.3kV耐圧RシリーズHVIPMの外観

## 参考文献

- (1) Iura, S., et al.: Development of New Generation 3.3kV IGBT module, PCIM Europe (2006)

- (2) 小林知宏, ほか: 鉄道車両用パワーデバイスの動向, 三菱電機技報, 83, No.11, 657~659 (2009)

- (3) 小林知宏, ほか: 鉄道車両用パワーデバイスの動向, 第46回鉄道サイバネ・シンポジウム論文集, 513 (2009)

# 6世代IGBTモジュール“NXシリーズ”

西山建人\*

宮崎裕二\*

中西英俊\*

6th Generation IGBT Module "NX series"

Taketo Nishiyama, Yuji Miyazaki, Hidetoshi Nakanishi

## 要 旨

IGBT (Insulated Gate Bipolar Transistor) モジュールは、産業分野でインバータ、モータ制御などに広く使用されている。また、医療機器や溶接機、瞬時停電対策用バックアップ電源であるUPS(Uninterruptible Power Supply)で使用されるなど、応用機器の分野はますます拡大している。さらに近年では、太陽光や風力をはじめとする自然エネルギーを利用した発電の電力変換用インバータとしてIGBTモジュールの需要が増加しており、今後ますますIGBTモジュールの果たす役割は大きくなると予想される。

三菱電機では、低損失を特徴とする5世代IGBTであるCSTBT(キャリア蓄積効果を利用した当社オリジナルIGBT)を搭載したIGBTモジュールを市場へ供給し、様々

な分野で高いシェアを獲得してきた。しかし、用途の多様化に伴い、単に低損失というだけでなく、低ノイズ、高温での動作保証など、更なる性能向上の要求が増してきている。このような背景から、今回5世代IGBTより更に次の点で性能を向上させた6世代IGBT及びFWDi(Free Wheeling Diode)を搭載した“6世代NXシリーズ”を開発した。

- (1) 損失の低減(当社5世代IGBT比)

- (2) 使いやすさの追及

- ①放射ノイズの低減

- ②ゲート容量の低減

- ③発振抑制ゲート抵抗の温度依存性の低減

- (3) 高温での動作保証

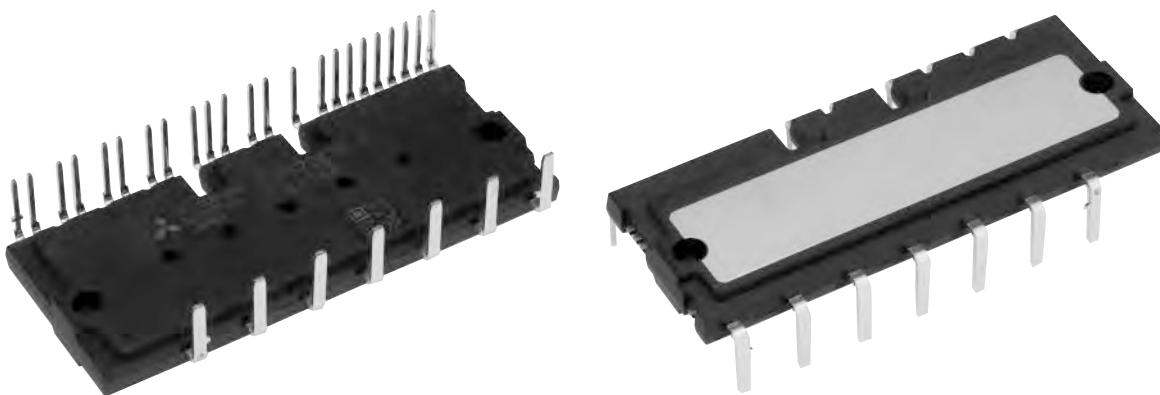

## 6世代NXシリーズの外観(2in1, 6in1, 7in1, CIB)

写真はCSTBTをベースにした6世代IGBT及びFWDiを搭載したIGBTモジュールである。

2in1タイプ(1,200V/150~450A)：手前左, 7in1タイプ(1,200V/75~150A)：手前右, 6in1タイプ(1,200V/75~150A)：中央左, CIB(Converter Inverter Brake)タイプ(1,200V/35~100A)：中央右, 2in1タイプ(1,200V/600~1,000A)：奥

## 1. まえがき

IGBTモジュールは、応用機器に合わせて最適な回路構成・電力容量、外形を提供することが必要である。5世代NXシリーズでは、ケース、ピン端子など共通の部品と5世代IGBTとを用いて、様々な回路構成を実現してきた。今回、5世代IGBTより更に性能を向上した6世代IGBTとFWDiを搭載した“6世代NXシリーズ”を開発した。回路構成は2in1、6in1、7in1、CIBとし、定格電圧は1,200V、定格電流は35～1,000Aとし、幅広い市場の要求にこたえられるラインアップとした(2010年4月時点の予定ラインアップ)。本稿では、開発した製品の特長について述べる。

## 2. 開発製品の特長

この開発製品は、市場からの要望を反映し、損失の低減だけでなく、ノイズ低減など使いやすさの向上と高温での動作保証を実現した。

### 2.1 損失の低減

IGBTモジュールで発生する損失は、一般的にスイッチング損失と定常損失に分類される。さらにスイッチング損失はターンオフ損失( $E_{off}$ )、ターンオン損失( $E_{on}$ )及びFWDiのリカバリー損失( $E_{rr}$ )に分類される。6世代NXシリーズはそれぞれの損失低減を行った。

#### 2.1.1 IGBTチップの改善

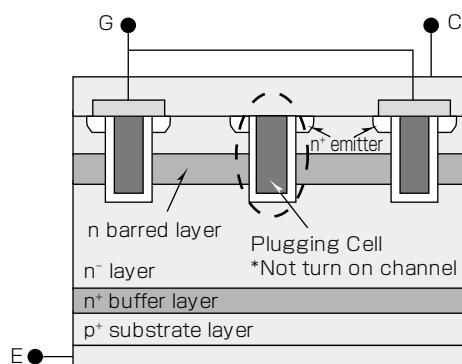

IGBTで発生する $E_{off}$ と定常損失のもととなる $V_{CE(sat)}$ には、トレードオフの関係がある。 $E_{off}$ はターンオフ時にN<sup>-</sup>層に残っているキャリアの量が少ないほど低減できるが、 $V_{CE(sat)}$ はキャリアが少ないほど大きくなり定常損失を増加させる。このトレードオフを改善するため、6世代IGBTはキャリアの注入効率を抑制することで残留キャリア濃度を最適化し、 $E_{off}$ の増加を抑えた。一方、少ないキャリアを有効に利用し $V_{CE(sat)}$ を低減するため、キャリアの存在エリアのN<sup>-</sup>層の厚みを薄くするとともに、微細加工によってセルピッチを縮小しチャネル密度を増加させた。さらにCS(Carrier Stored)層の最適化と、PCM(Plugging Cell Merged)技術を用いてエミッタ近傍のキャリア濃度を上げることで、 $V_{CE(sat)}$ の低減を可能とした。これらの最新技術を導入することで6世代IGBTはトレードオフの改善を達成し、5世代IGBTと比べて、例えば図1の $E_{off}=15\text{mJ}/\text{pulse}$ の条件で $V_{CE(sat)}$ を約23%改善した。

#### 2.1.2 FWDiの改善

FWDiには立ち上がりが急峻(きゅうしゅん)な電圧をダイオードに印加したときに、オフ状態に戻る前にリカバリー損失( $E_{rr}$ )が発生する。キャリアの寿命を制御するライフタイムコントロールによって逆回復時間を短縮でき、 $E_{rr}$ を小さくすることができるが、順方向電圧( $V_F$ )が上がるため、定常損失が大きくなる。FWDiの損失を小さくす

図1.  $E_{off}$ - $V_{CE(sat)}$ トレードオフ特性

図2.  $E_r$ - $V_F$ トレードオフ特性

るには、このトレードオフを改善する必要がある。今回開発したFWDiは、ライフタイムコントロール、チップ厚の最適化、さらにベース濃度の最適化によって、従来品より $E_{rr}$ と $V_F$ のトレードオフを改善した(図2)。従来品と比べて $E_{rr}=8\text{mJ}/\text{pulse}$ の条件で $V_F$ を0.33V改善した。

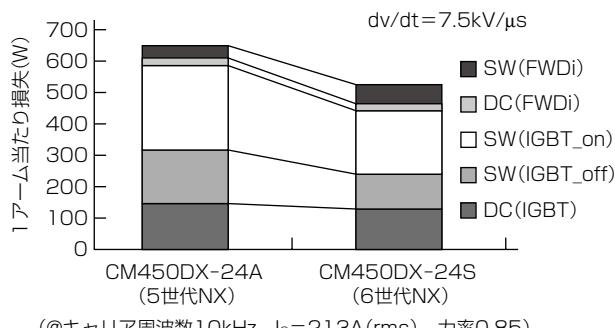

この技術によって6世代IGBTとFWDiの特性改善をすることで、PWM(Pulse Width Modulation)インバータ動作における損失の低減に成功した。ターンオン時にコレクターエミッタ電圧( $V_{CE}$ )のdv/dtが7.5kV/ $\mu\text{s}$ となるようにゲート抵抗をそれぞれ調整した条件で、PWMインバータ動作を想定した損失シミュレーションによって、従来のNXシリーズと6世代NXシリーズの損失を比較した。その結果、6世代NXシリーズは従来のNXシリーズに比べて、トータル発生損失を約24%低減できることを確認した(図3)。

## 2.2 使いやすさ

### 2.2.1 EMIノイズの低減

IGBTモジュールは、高電圧・大電流を高速スイッチングすることから、EMI(Electro Magnetic Interference)ノイズの発生源となることがある。IGBTモジュールを搭載した応用機器の分野が広がるにつれ、事務所向けでは無

線などに影響を与えないこと、工場内の装置ではネットワークで接続された装置に誤動作を起こさせないことなど、他の周辺装置に影響を与えないことが必要となる。そのため低損失に加え低ノイズの要求が高まっている。

応用機器から発生するEMIノイズの一要因に、IGBTモジュールのスイッチング動作時のdv/dtがある。図4に示すように、ターンオン時のdv/dtとE<sub>on</sub>はトレードオフの関係にあるが、6世代IGBTはCS層及びPCMの最適化によってコレクターゲート間の容量を低減することで、このトレードオフを改善した。

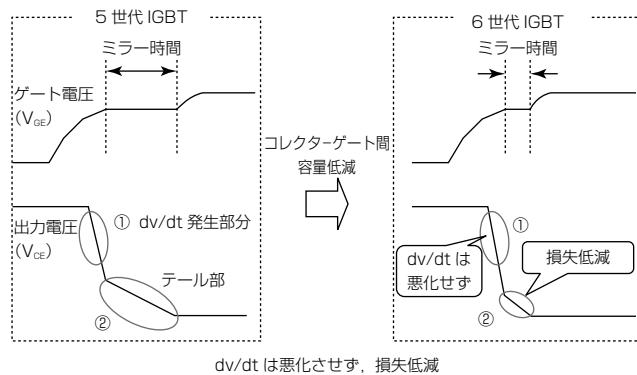

図5にターンオン時のゲート電圧(V<sub>GE</sub>)及びコレクターエミッタ電圧(V<sub>CE</sub>)の波形を示す。EMIノイズはV<sub>CE</sub>波形の立ち上がり始めの部分(図5①)の傾きに影響される。この部分が急峻であればノイズが大きくなると考えられている。一方、E<sub>on</sub>はV<sub>CE</sub>波形のテール部(図5②)に依存していることから、この部分を減らすことによってE<sub>on</sub>を低減することが可能になる。

テール部はゲートのミラー時間と連動しており、テール部を小さくするためには、このミラー時間を短縮する必要がある。ミラー時間はコレクターゲート間容量に比例するため、コレクターゲート間容量を小さくすればテール部が小さくなりE<sub>on</sub>を低減することができる。6世代IGBTでは、PCMの最適化によってコレクターゲート間容量を5世代IGBTと比較して1/2以下に低減した。その結果、dv/dt(図5①)を上げることなく損失を低減することが可能とな

図3. インバータ動作時の損失

図4. dv/dt-E<sub>on</sub>トレードオフ特性

り、dv/dt-E<sub>on</sub>トレードオフの改善ができた。

ノイズ低減効果を実証したデータを図6に示す。5世代IGBTを搭載したNXシリーズと6世代IGBTを搭載したNXシリーズのEMIノイズを比較した結果(E<sub>on</sub>同等)、装置に影響を与えることが多い40MHz付近のノイズレベルが約5dB低下していることが分かる。

## 2.2.2 ゲート電荷の低減

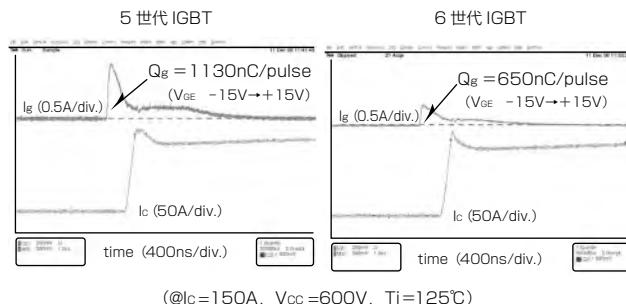

IGBTは電圧駆動素子であり、スイッチングするためにはゲート容量への充放電が必要となる。6世代IGBTでは、PCMの最適化によってゲート容量を小さくしている。このため、ゲートの充放電に必要な電荷量(Q<sub>g</sub>)は、図7に示すとおり5世代IGBTに比べ約40%低い。

図5. ターンオン波形

ターンオンスイッチング損失を同等とした場合 (R<sub>g</sub>調整)

Ref 75dBμV ATT 10dB SWT 30ms

図6. EMIノイズ

図7. ターンオン時のゲート電流

図8. 発振抑制抵抗の温度依存性

図9. 短絡耐量SCSOA

したがって、ゲート駆動回路の設計で、駆動電力が小さくなることでコストの低減が可能になる。

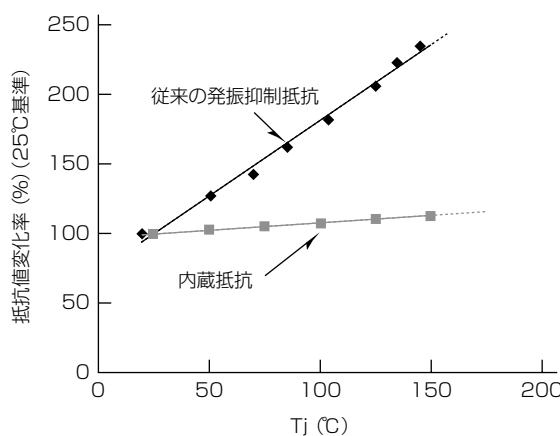

### 2.2.3 発振抑制ゲート抵抗の内蔵

IGBTモジュールはチップを並列に接続し、電流容量を増加させる場合がある。このときには、各チップ間で発振しないようにするために、チップごとのゲートに発振抑制抵抗を接続する。6世代IGBTは従来の5世代IGBTに対して温度依存性の小さい発振抑制抵抗をチップに内蔵することによって、温度変化に対するスイッチングスピードなどの特性変動をより小さくすることができた。図8に、従来の抵抗と内蔵抵抗の温度依存性について示す。

### 2.3 高温での動作保証

近年、IGBTモジュールを搭載する機器も多様化しており、使用条件拡大を目的としてIGBTモジュール動作保証温度の高温化要求が増加する傾向にある。

6世代IGBTは、構造の最適化を行うことで高温時のリーケ電流を抑制し、熱暴走しにくい設計とした。これによって、動作時のジャンクション温度(Tj)の最大許容値を、従来よりも25°C高くした温度条件でも安定した動作と破壊耐量が確保できた。まず、短絡耐量(Short Circuit Safe

図10. 逆バイアス安全動作領域：RBSOA

表1. 6世代NXシリーズ ラインアップ

| 型名            | 電圧定格(V) | 定格電流(A) | 回路   |

|---------------|---------|---------|------|

| CM35MXA-24S   | 1,200   | 35      | CIB  |

| CM50MXA-24S   |         | 50      |      |

| CM75MXA-24S   |         | 75      |      |

| CM100MXA-24S  |         | 100     |      |

| CM75RX-24S    |         | 75      |      |

| CM100RX-24S   | 7in1    | 100     | 7in1 |

| CM150RX-24S   |         | 150     |      |

| CM75TX-24S    |         | 75      |      |

| CM100TX-24S   | 6in1    | 100     | 6in1 |

| CM150TX-24S   |         | 150     |      |

| CM150DX-24S   |         | 150     |      |

| CM200DX-24S   | 2in1    | 200     | 2in1 |

| CM300DX-24S   |         | 300     |      |

| CM450DX-24S   |         | 450     |      |

| CM600DXL-24S  |         | 600     |      |

| CM1000DXL-24S |         | 1,000   |      |

Operating Area : SCSOA)は、 $T_j = 150^\circ\text{C}$ で $10\mu\text{s}$ 以上非破壊遮断可能である(図9)。また逆バイアス安全動作領域(Reverse Bias Safe Operation Area : RBSOA)は、 $T_j = 150^\circ\text{C}$ でコレクターエミッタ間の跳ね上がり電圧を1,200V(最大定格)発生させた状態で、定格の2倍以上の電流が遮断可能であり、遮断後の発振等も見られない良好な短絡波形(図10)が確認できた。

6世代NXシリーズ(表1)は温度マージンも確保できることから、更に使いやすいモジュールになり得ると考える。

### 3. む す び

今回開発した6世代NXシリーズは、低損失、低ノイズ、高温時での動作保証を可能とする製品化を実現し、市場の期待にこたえる製品となっている。

### 参 考 文 献

- (1) 松本 学：新世代IGBTモジュール“NXシリーズ”，三菱電機技報，81, No.5, 337～342 (2007)

# 次世代大容量IGBTモジュール “New-MPDシリーズ”

田畠光晴\*

*Next Generation Large Current IGBT Module "New-MPD Series"*

Mitsuharu Tabata

## 要旨

近年、風力発電の急速な設置拡大によって、1,000A級のIGBT(Insulated Gate Bipolar Transistor)モジュールの需要が増加している。市場での並列接続数の低減に対応するため、産業用IGBTモジュールの電流容量拡大版として、2素子入りの1,800A／1,700V, 2,500A／1,200Vを開発した。直流・交流変換回路として通常使用される電圧型インバータブリッジ回路を採用する製品群に広く適用可能である。

モジュール内外の直流母線の低インダクタンス化を追求し、内部インダクタンスは約5nHと小さく設計し、主端子配置は外部配線のインダクタンスを低減しやすいよう配慮した。これらによって、大電流回路の配線構成が容易となる。大電流装置で用いられるアクティブクランプ回路からの要請によって、各素子に専用のコレクタセンス端子を準備した。

対象となる大電力装置では水冷(液冷)が一般的であり、このモジュールでは水冷にも適するように配慮した。チップ

の間隔を広く取り水冷冷却器の高い放熱能力を生かせるようにするとともに、直線的な水冷パイプが干渉なくチップ直下に配置できるように工夫した。

また、ベース板を銅からアルミに変更し、軽量化、サーマルサイクル耐量向上を実現した。熱伝導阻害要因のはんだ層を1層減らすことによって、銅からアルミへの変更による熱伝導率低下を相殺し、全体としての熱抵抗を同等とした。

大容量化に伴うベース板面積の増加に対し、フィン、モジュール双方への平坦(へいたん)度要求を軽減するため、従来のIPM(Intelligent Power Module)製品で実績のある分割ベース板構造を採用した。

今後、共通部材を使用した小筐体(きょうたい)の1,500A／1,200V, 1,100A／1,700V製品をシリーズ展開予定である。

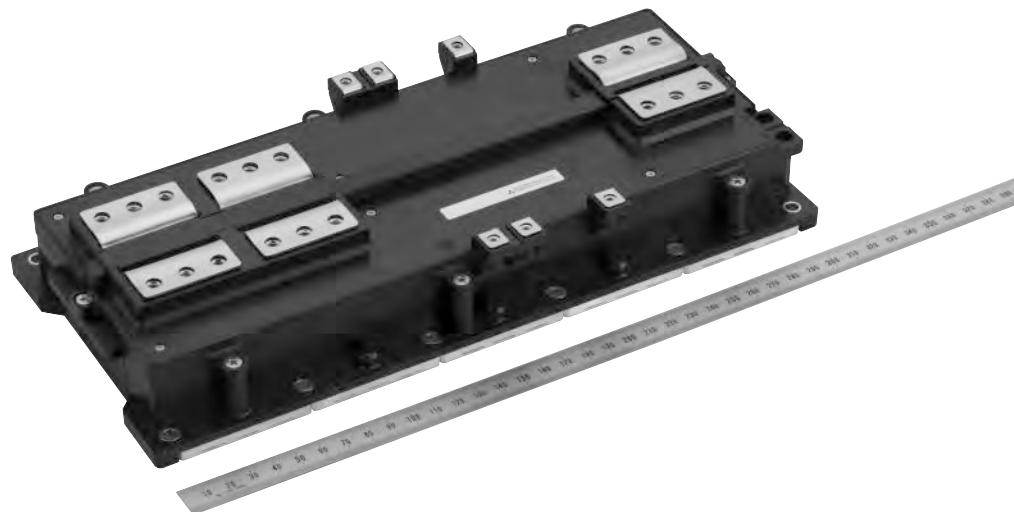

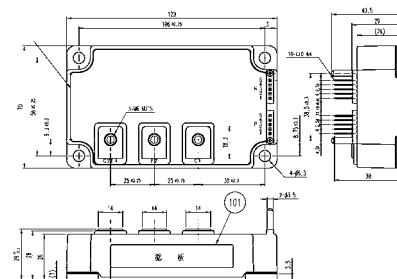

## “CM1800DY-34S(1,800A／1,700V)”, “CM2500DY-24S(2,500A／1,200V)”の外観

最大サイズは310×142×51 (mm)。内蔵回路はIGBT : 2, ダイオード : 2によって、2素子入りハーブリッジ回路を構成している。

## 1. まえがき

従来風力発電は、発電設備としての能力よりもむしろシンボル的理由によって設置されることが多かったが、発電効率向上などによって発電設備としての魅力が増加するに従い、急速に設置量が増大し、その新規設置量は30GW/年近くに至っており、欧、米、中国などで主力発電形態の一つへ成長しようとしている。風力発電には風車の大型化によって発電コストが低下する性質があり、普及と大型化が同時に行われてきたが、基本的には分散発電であり、水力発電や原子力発電のように一点集中の大型設備とはなり難い。このメガワット級の発電装置を多数使用するという形態が牽引(けんいん)力となり、発電電力を系統電力波形に整形変換するインバータ回路に使用される1,000A級の電力半導体の需要が伸びてきた。この市場に対し、量産性の優れる、より低電流の電力半導体製品からのステップアップ展開として、1,800A/1,700V(2素子入り)をはじめとする“New-MPD(Mega Power Dual)シリーズ”を商品化した。

## 2. 製品展開

大小二つのパッケージについて、1,700V耐圧と1,200V耐圧の計4機種(表1)を展開する計画であり、開発の中心として1,800A/1,700V定格を先行開発した。現行製品であるMPDシリーズは、定格1,000A/1,700V又は1,400A/1,200Vが最大であり、風力発電にはこれらの製品が並列接続して使用されていたが、風車の主力需要が2~4MWとなり需要数も増加し、並列接続の煩雑さ軽減のため、より大容量の素子を求める声が強くなった。この要求に対応するため、今回電流容量を拡大した製品を開発した。この製品は2素子入り製品として三菱電機では最大となる。同じ筐体で2,500A/1,200Vも開発する。

また、今後共通部材を使用した展開製品として、1,500A/1,200V、1,100A/1,700Vを開発予定である。

## 3. 製品の特徴

### 3.1 端子配置は現行MPDシリーズのコンセプトを継承

この製品が対象として想定する応用製品は、直流・交流変換回路として通常使用される電圧型インバータブリッジ回路を採用する製品群である。このインバータブリッジ回路では、大電流応用では、還流経路である直流母線で特に低いインダクタンスが要求されるが、この部分を構成する

外部配線のインダクタンスを低減しやすい端子配列として、P, N端子<sup>(注1)</sup>を筐体の1辺付近に集中させている(図1のP, N端子)。また、交流出力端子(図1のAC端子)を対辺に配置し、中央に駆動回路基板を設置するスペースを持っている。この配置は従来機種であるMPDシリーズで好評を得たため、今回の製品群でもこのコンセプトを踏襲した。

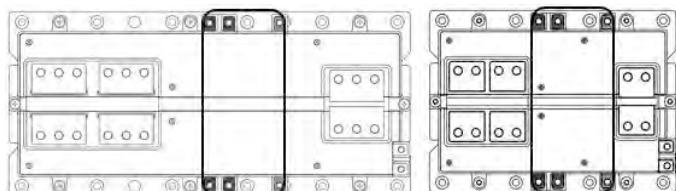

### 3.2 大小筐体の信号端子の位置関係を共通化

今後開発予定の小パッケージの信号端子の位置関係を、図2のように共通とする予定であり、大小の駆動回路を共通基板で設計できる。共通基板としない場合にも、駆動基板のレイアウト設計の思想がある程度共通化できることによって、基板設計の省力化に貢献すると考えている。

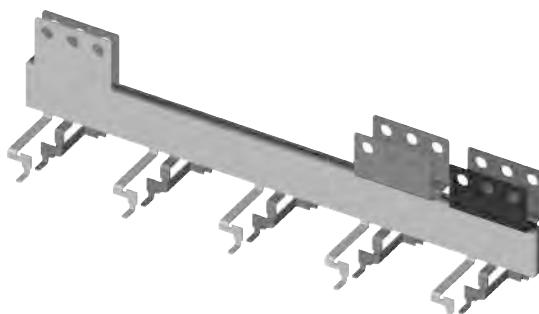

### 3.3 多層ラミネート電極による低インダクタンス

大電流を高速スイッチングするには、直流母線のインダクタンスの低減が重要となる。モジュール内部についても、直流母線インダクタンスに影響するP, N間のインダクタンスを低減するため、モジュール内部配線の直流母線部分(P, N電極)4層を含む6層ラミネート電極とした(図3)。

(注1) 外部の直流母線と接続される端子で、モジュールの端子名でのC1, E2に相当する。

図1. 端子配置

図2. 信号端子配置

図3. ラミネート電極

表1. 製品展開

|        | 900A | 1,000A | 1,100A | 1,400A | 1,500A | 1,800A | 2,500A |

|--------|------|--------|--------|--------|--------|--------|--------|

| 1,700V |      | ○      | ◎      |        |        | ◎      |        |

| 1,200V | ○    |        |        | ○      | ○      |        | ○      |

○: MPD ◎: New-MPD

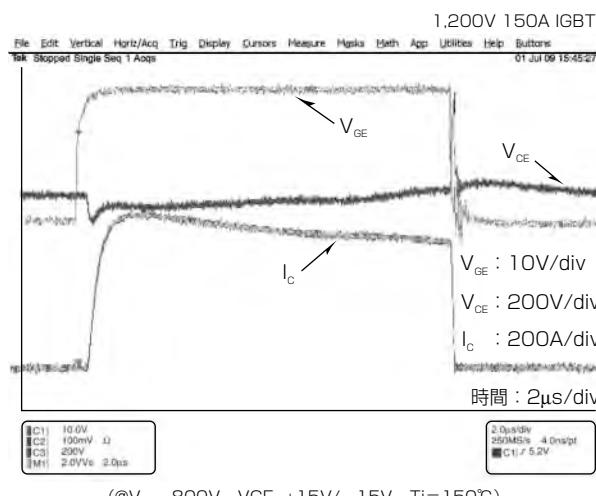

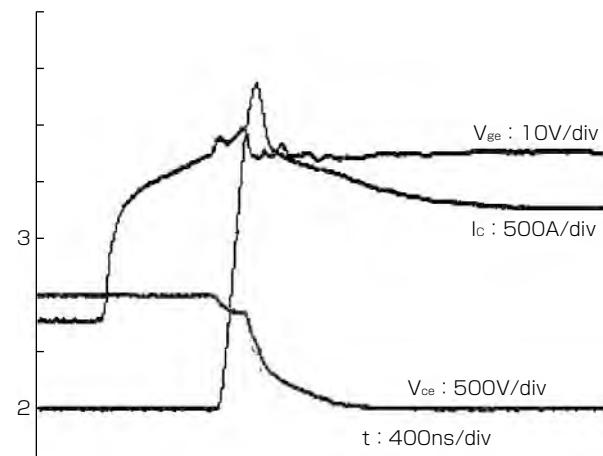

これによって“CM1800DY-34S”では同電流定格で実用上要求のある10nHを大幅に下回る5.25nHを達成した。実験レベルでは、外部回路を含めた直流母線インダクタンス全体として10nH以下を得ており、この状態では例えば図4の波形に見られるように、1,800Aの高速遮断でのサージ電圧を200V程度に抑制できる。

一方、スイッチング損失については、直流母線インダクタンスの最小化が最適とは限らないことが知られている。効率(低損失)を優先する場合には、直流母線インダクタンスが少し大きい方がソフトスイッチング気味となりスイッチング損失が低下するので好ましく、実際の装置設計で直流母線インダクタンスは調整対象である。しかし、インダクタンスの増加は外部回路で実現できるが、減少は外部回路では実現できないため、内部インダクタンスが小さい方が全体としての直流母線インダクタンスの調整範囲を広く取れる。この製品はモジュール内部の直流母線インダクタンスを小さく設計したため、高速性優先にも、効率優先にも対応できる適用自由度の高いパッケージとなっている。

### 3.4 水冷への対応

扱う電流が大きくなるに従い素子の総熱損失量も増加するため、より効率の良い冷却手段が必要となる。冷却能力の高い冷却器として一般に水冷(液冷)やヒートパイプが用いられており、今回開発した製品でもこれらの冷却手段が用いられることを想定している。これらの冷却器では内部にパイプが設置されており、パイプ近傍の放熱効率が他の部分よりも高いため、発熱源であるチップの直下にパイプが配置されることが望ましい。このような配置関係をモジュール外部で実現するためには、モジュール内部の各チップの配列をつなぐ直線と、モジュールの取付けねじ位置とが干渉しないようにモジュールを設計しておく方が良い。このモジュールではこの点を考慮してチップ配置と取付けねじ位置を設計した。図5でパイプが上下方向に配置される場合に、上下2チップを結ぶ垂直線上に取付け穴がないように配置した。

一方、水冷(液冷)やヒートパイプを使用した放熱フィンでは、冷却器の冷却面の単位面積当たりの放熱能力が空冷

図4. ターンオフ波形例

の場合の数十倍に増加するため、ベース板による面方向の熱拡散が減少し、モジュール内部の放熱構造が同一であってもモジュールの熱抵抗が増加する。このような冷却状況では、熱源近傍の冷却経路が支配的となり、複数の熱源が近接したときの干渉の影響が顕著となる。大電流定格のIGBTモジュールは、モジュール内部で多数のチップを並列接続して大きな電流定格を実現しているが、水冷の高い冷却能力を放熱システム全体として生かすには、モジュール内部の並列チップが分散され、間隔が広い方が都合が良い。この製品群ではチップ同士の中央間距離を30mm程度と広く取ることによって、外部の水冷放熱器の放熱能力をより良く生かせるようにした。

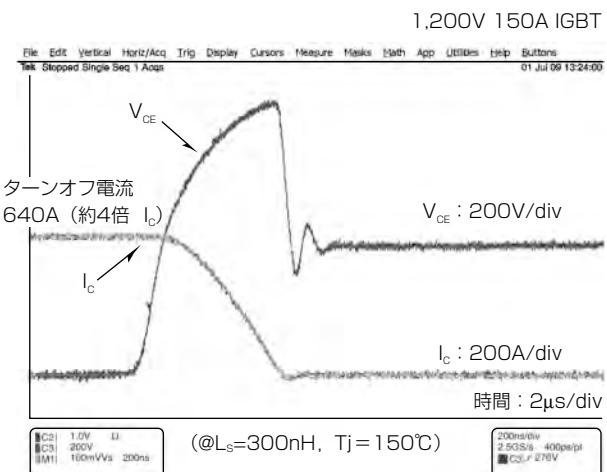

### 3.5 6世代チップ採用による低損失

6世代チップでは、トレードオフを最大で20%改善し、インバータブリッジ回路全体として5~10%の損失低減が可能となる(当社比、一般的なインバータ動作にて)。また、新しいダイオードはソフトリカバリー特性とし、特に従来の1,700V耐圧製品で問題となっていたリカバリー時のリングギングを抑制する設計としている(図6)。

これらのチップ特性によって、特にスイッチング周波数が2~4kHzの応用で、低ノイズ、低損失を享受可能である。また、パッケージ、チップともにより高速なスイッチングにも対応できるように設計しており、従来のこのクラスの電流定格のIGBTモジュールでは困難であった10kHz以上のスイッチングも可能である。

図5. チップ配置

図6. ターンオン波形例

### 3.6 アルミベース板採用による軽量化

電力半導体モジュールは、内部にセラミックを使用しているため衝撃に弱く、組み付け時に壊れもの扱いが必要となるが、モジュールが大型化すると質量の増加によって扱いが困難となる。大型化による質量増を抑制するため、従来の銅ベース板をアルミに変更することによって、総質量を約2/3(従来と同様に銅ベース板を使用した場合の予測質量との比較)とした。合わせて持ち運び用に短辺に側面突起を設けており、取付け作業などを容易にしている。

一方、水冷ではフィンの熱容量に対し冷却能力が上がるため、冷却時定数が小さくなり、冷却速度が上がり電力変化に対するケース温度(チップ直下のベース板温度、 $T_c$ )の追従性が良くなる。結果として $T_c$ の振れが頻繁となり、モジュール部材の金属疲労を促進させる。従来のモジュール構造で $T_c$ 変化に対する金属疲労寿命のボトルネックは基板(セラミック)下のはんだであった。基板下のはんだは線膨張係数の大きく異なる層の接合部に使用されるため、温度変化の繰り返しによって金属疲労を起こしてクラックを生じ、このクラックの成長によって最終的に熱伝導を妨げるようになり、製品の寿命が短くなる。また、はんだは他の熱伝導部構造素材である、銅、アルミ、AIN(基板の素材)などと比較して、熱を通し難い素材であるため、放熱の阻害要因もある。これに対し、今回採用したアルミベース板は基板とアルミを直接接合しており、はんだより金属疲労寿命の長いアルミによって、サーマルサイクル寿命が向上する。また、はんだ層をなくすことによって、ベース板を銅からアルミへ変更したことによる熱伝導率低下を相殺し、総合的な熱抵抗を従来の銅ベースと同等にできた。

### 3.7 主端子の接触抵抗を低減

直流母線は外部配線も含めて低いインダクタンスとすることが要求されるため、大電流の装置の外部配線では比較的薄い銅板によるラミネートバスバーが利用されることが一般的であるが、モジュールの端子との接触面積が小さいと電流が集中し発熱が増加する。これを軽減するため、従来機種MPDでは各端子板のねじ穴数を複数としたが、この製品でもこの方式を踏襲し、従来どおりの十分な接触面積を確保した。

### 3.8 素子ごとにコレクタセンス端子を持つ

この製品を搭載する装置には定格電流を超える大電流が流れるような異常動作が不可避に想定されるものがあり、このような場合、異常電流を検出し電流を遮断しシステムを停止する機能を備えるが、定常時と同じ速度で電流を遮断すると他の破壊を引き起こす可能性がある。しかし特に大電流装置では安全に電流を遮断する条件が狭く、精度良く制御するため、コレクタ電圧をリアルタイムで測定し適度な遮断速度に調整する“アクティブクランプ”<sup>(注2)</sup>という

図7. ベース板面側の外観

機能を持ったドライバが採用されることが多い。このような方式のドライバ基板が構成しやすいよう、コレクタ電圧センス専用端子をP, N各々に設置した。

(注2) 同名のスイッチング電源におけるトランスクアをリセットする手法(部分共振の一種)とは無関係。

### 3.9 分割ベース板

電力容量の増加に伴い、放熱面であるベース板面積も広くする必要があるが、一般的にベース板面積が広くなるとモジュール側、フィン側とともに平坦度を確保することが困難になる。この問題への対策として、この製品では従来のIPM製品で実績のある分割ベース板構造を採用した(図7)。なお、分割ベース板構造ではモジュール取付け時に分割部が柔軟に動くため、応力が樹脂ケースに掛かりケース高さに制約が生じるが、この製品ではケースを上下に2分割して制約を回避した。

一方、パワー半導体チップのスクリーニングには大電流の通電が要求される内容があるが、ワイヤボンドなどによる配線を行う前のウェーハやチップ状態では通電電流に限界があり、大電流のモジュールでは、これまでモジュール完成後に試験をする必要があった。しかし電流定格が大きくなるに従い、この試験には大掛かりな試験装置が必要となり、また一つのチップの不良によってモジュール全体が不良となるので使用チップ数が増えると不良率が増加するなど、量産性に障害が発生する。今回、分割ベース板構造を採用したことでワイヤボンド後の状態が個片化したため、ベース板1枚の状態でスクリーニング試験することによって、これらの問題を解決した。

## 4. む す び

この製品は風力発電拡大による需要増によって商品化が可能となったもので、ターゲットとした風力発電に適した選択であることはもちろんあるが、この製品の商品化が新たな大電流スイッチング応用機器需要発生の契機となることを期待している。

なおこの製品は執筆時点で開発中であり、試作品を基にしている。量産製品とは内容が異なる場合がある。

# 新大容量 2 in 1 IPM “V1シリーズ”

魚田紫織\* 後藤 章\*\*

西田信也\*

為谷典孝\*

*High Power Dual IPM "V1-Series"*

*Shiori Uota, Nobuya Nishida, Fumitaka Tametani, Akira Goto*

## 要 旨

京都議定書の締結から13年、地球環境保全のための省エネルギー化は世界共通の課題であり、これを実現するためのキーパーツとして、IPM(Intelligent Power Module)が注目されている。

また、アプリケーションは、従来需要のあったサーボ・インバータ分野のみならず、クリーンエネルギー、建設機器など多岐にわたって拡大しており、これに伴い、低損失化要求に加え、大容量化、高寿命化の要求も高まっている。

このような市場ニーズにこたえるために、今回次の特長を持つ大容量 2 in 1 IPM“V1シリーズ”をリリースした。

- (1) 多岐アプリケーションへ対応しやすい 2 in 1 の回路構成とし、大容量帯のラインアップを充実化した。

- (2) 旧世代 2 in 1 “Vシリーズ”から簡便な置き換えを可能とするため、外形及び端子配列を Vシリーズと共通化した。

- (3) 热設計技術を適用したIPM内部デザインによって、放熱性を向上させ、Vシリーズと同一外形で大容量化(大電流)を実現した。

- (4) 回路最適化によって、負荷短絡時の過大な電流を抑制することで、旧世代製品よりも短絡破壊耐量を改善した。

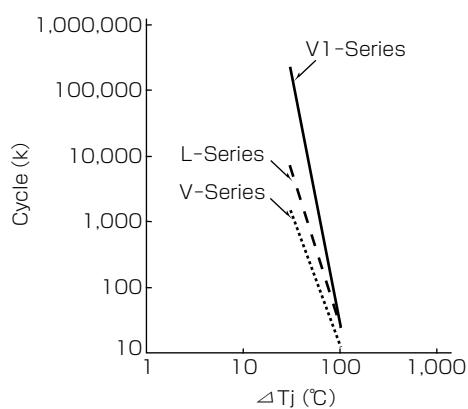

- (5) ワイヤボンディング(IPM内部の電気的接続)条件最適化によって、パワーサイクル1,000cycle時の $\Delta T_{j\text{c}}$ は、旧世代Vシリーズ $\Delta 32^\circ\text{C}$ 、Lシリーズ $\Delta 45^\circ\text{C}$ に対し、V1シリーズでは、 $\Delta 60^\circ\text{C}$ に改善した。

- (6) 先行リリースしたLシリーズ(6 in 1, 7 in 1)と同様の0.8μmフルゲートCSTBT(Carrier Stored Trench-gate Bipolar Transistor)を並列駆動することで大容量化を実現し、旧世代Vシリーズから21%, Lシリーズから23%の低損失化を達成した。

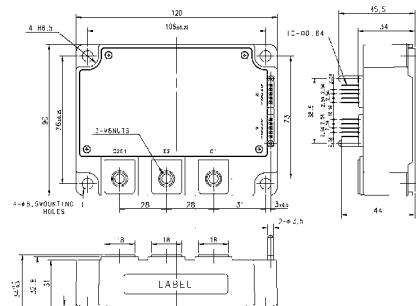

V1シリーズ小型パッケージ

V1シリーズ大型パッケージ

## 新大容量 2 in 1 IPM V1シリーズの外観

V1シリーズ小型パッケージ 定格：600V/400A, 600A, 1,200V/200A, 300A, 450A

V1シリーズ大型パッケージ 定格：600V/800A, 900A, 1,200V/600A

## 1. まえがき

各国が国策として省エネルギー化対策に取り組む中、IPMは多岐にわたって応用分野を拡大しており、更なる低損失化に加え、大容量化、高寿命化のニーズが高まっている。

今回、このような市場ニーズにこたえるため、新大容量2 in 1 IPM“V1シリーズ”を開発した。V1シリーズIPM製品ラインアップを表1に示す。

V1シリーズは、大容量帯ラインアップの充実化とともに、旧世代“Vシリーズ”からの置き換えによる応用機器側の負荷軽減のため、外形及びピン配置をVシリーズと共通化した。

また、旧世代製品からのパワーサイクル寿命向上に加え、先行リリースしたL1シリーズと同様の、5世代フルゲートCSTBTチップ搭載による低損失化によって、市場ニーズにこたえる製品である。

本稿では、V1シリーズの特長と要素技術について述べる。

## 2. V1シリーズIPMの特長

### 2.1 パワーデバイス(低損失化)

旧世代Vシリーズではプレーナ型IGBT(Insulated Gate Bipolar Transistor)を、Lシリーズではチャネル密度を制御するPCM(Plugging Cell Merged)技術を採用したCSTBTを搭載していた(図1)。

PCM CSTBTは、プレーナ型IGBTと類似したゲート電荷量、短絡耐量を持ち<sup>(1)</sup>、かつプレーナ型よりも低損失であるため、旧世代Lシリーズでは、この構造を採用していた。

V1シリーズでは、更なる低損失化の要求にこたえるため、このPCM構造の低損失版として、先にリリースしたL1シリーズと同様のフルゲートCSTBTを採用している(図2)。

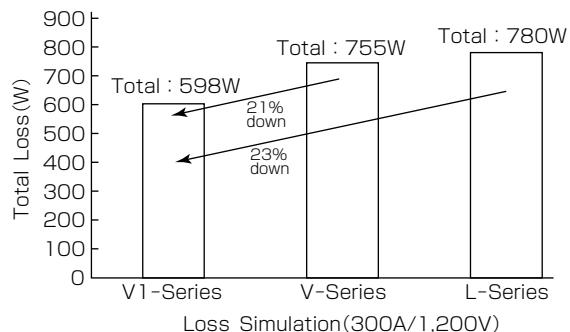

V1シリーズと旧世代Vシリーズ、Lシリーズの損失シミ

ュレーション比較結果を図3に示す。フルゲートCSTBT採用によって、V1シリーズのトータル損失は、旧世代Vシリーズから21%、Lシリーズから23%低減した。

### 2.2 制御(短絡破壊耐量向上)

V1シリーズでは、低損失化に加え、フルゲートCSTBTチップを並列駆動することで大容量化を実現している。

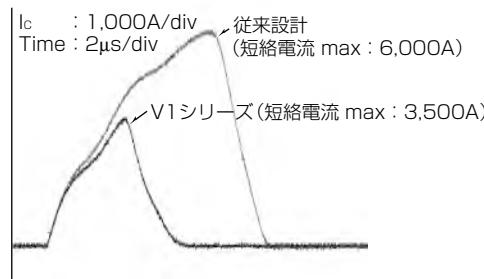

チップの並列駆動では、ゲート発振、チップ間電流アンバランス、これらに伴う負荷短絡時の過大電流の発生が懸念され、旧世代製品よりも短絡破壊耐量が劣化するおそれがある。

この問題を解決するため、V1シリーズでは、パターン及び回路の最適化設計を行い、フルゲートCSTBTの並列駆動を実現した。これによって、旧世代製品からの低損失化と大容量化を達成可能となった。

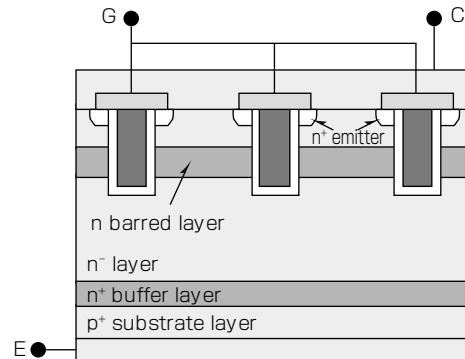

図1. PCM CSTBTの構造

図2. フルゲート CSTBTの構造

図3. 損失シミュレーション比較結果

(条件:  $V_{cc}=600V$ ,  $f_0=15kHz$ ,  $I_0=180Apeak$ ,  $PF=0.8$ , 変調率1,  $T_j=125^\circ C$ )

\*Lシリーズは1/3モジュールで算出

図4. 回路、パターン適正化設計による短絡電流抑制結果

(条件:  $V_{cc}=200V$ ,  $T_a=125^{\circ}C$ ,  $V_D=15V$ ,  $L$ 負荷 = 0.1m, 600A/1,200V)

(a) V1シリーズ(小型パッケージ) (b) Vシリーズ(大型パッケージ)

**図5. 熱シミュレーション比較結果**

(V1シリーズ vs 旧世代Vシリーズ)

(パワー印加条件: IGBT 100W, FwDi 38W)

負荷短絡時のV1シリーズの電流波形を図4に示す。従来設計では約6,000A発生する過大な負荷短絡時ピーク電流をV1シリーズでは42%抑制しており、IGBTの保護性能を向上させた。

## 2.3 構造

### 2.3.1 热设计(大容量化)

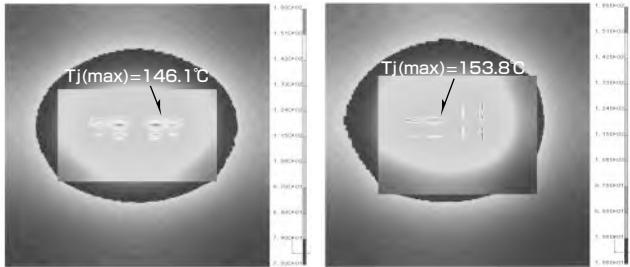

V1シリーズIPMでは、パワー部の熱干渉及びワイヤボンド配線による熱シミュレーションを適用した構造設計によって、旧世代Vシリーズよりも放熱性を向上させた。

V1シリーズと旧世代Vシリーズ(大型パッケージ)の熱シミュレーション比較結果を、図5に示す。

V1シリーズでは、チップサイズがVシリーズよりも小さいため、チップの熱抵抗は大きくなるが、同一パワー印加時のチップ温度最大値 $T_j(\max)$ は、Vシリーズ(大型パッケージ)153.8°Cに対し、パッケージが小型化しているにも関わらず、146.1°Cと抑制されている。また、V1シリーズでは、チップの熱干渉性を見直すことで、チップ温度が上昇しにくい設計としている。

このような放熱設計によって、V1シリーズではチップの小型化を実現し、旧世代Vシリーズでは大型パッケージの製品を小型パッケージに集約可能となった。また、V1シリーズでは、Vシリーズからスムーズに置き換えられるよう、外形及び端子配列を共通化した(図6)。

### 2.3.2 ワイヤボンディング(高寿命化)

V1シリーズでは、ワイヤボンディング条件の最適化によって、パワーサイクル寿命を改善することで、高寿命化

小型パッケージ(120×70×29(mm))

大型パッケージ(120×90×34(mm))

図6. V1シリーズの外形

図7. パワーサイクルカーブ

のニーズにこたえている。

パワーサイクルカーブを図7に示す。1,000cycle時の $\Delta T_j$ は、旧世代Vシリーズ $\Delta 32^\circ\text{C}$ 、Lシリーズ $\Delta 45^\circ\text{C}$ に対し、V1シリーズでは $\Delta 60^\circ\text{C}$ に改善した。

### 3. む す び

新大容量 2 in 1 IPM V1シリーズについて述べた。この製品は、低損失化に加え、多様化するIPM応用製品市場からの大容量化、高寿命化のニーズを受けて実現した製品であり、市場の期待に添うものであると考える。

今後は、更に大容量帯のラインアップを充実させるとともに、各応用製品に適した機能、性能を持つIPMを開発・提供し、地球環境保全に貢献していく所存である。

参 考 文 献

- (1) 井上貴公, ほか:新チップ内蔵IPM “L1/S1シリーズ”, 三菱電機技報, 81, No.5, 345~348 (2007)

白石卓也\*

商 明\*

栗秋和広\*

# 1,200V大型DIPIPM “Ver.4シリーズ”

1,200V Large DIPIPM "Ver.4 Series"

Takuya Shiraishi, Ming Shang, Kazuhiro Kuriaki

## 要 旨

近年、地球温暖化問題の意識が高まる中、省エネルギー化・高性能化を目的としたモータ駆動システムのインバータ化が、民生機器から産業機器まで幅広く進展している。三菱電機のDIPIPM (Dual In-line Package Intelligent Power Module)は、省エネルギー化・高性能化を実現できるキーデバイスとしてインバータ駆動用に多数採用されている。

今回海外市場向けのAC400V電源に対応可能な、1,200V系DIPIPMシリーズの新製品開発を行った。新製品開発を進めていく上で、従来品よりも外形サイズの小型化及び大容量化を達成するには、発生損失の低減、放熱性の改善が

課題であった。

新製品である1,200V大型DIPIPM “Ver.4シリーズ”は、それらの課題を解決するために搭載IGBT (Insulated Gate Bipolar Transistor)に当社独自開発の“LPT-CSTBT (Light-Punch Through Carrier Stored Trench-Gate Bipolar Transistor)”を採用し、従来品より発生損失を低減した。また高放熱特性を持つ絶縁シートによる絶縁方式で、従来品より放熱性を改善した。これによって小型化・定格電流のシリーズ拡大を実現し、また最適な短絡電流検出方式、モジュール温度検知機能の内蔵によって高機能化を図った。

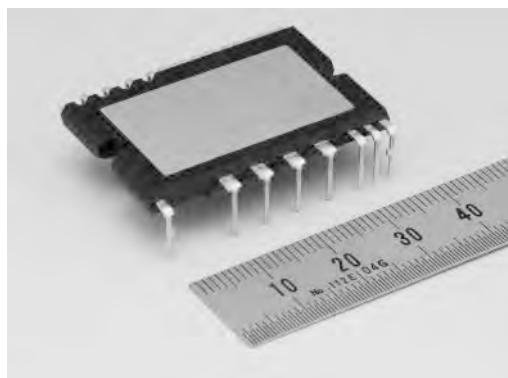

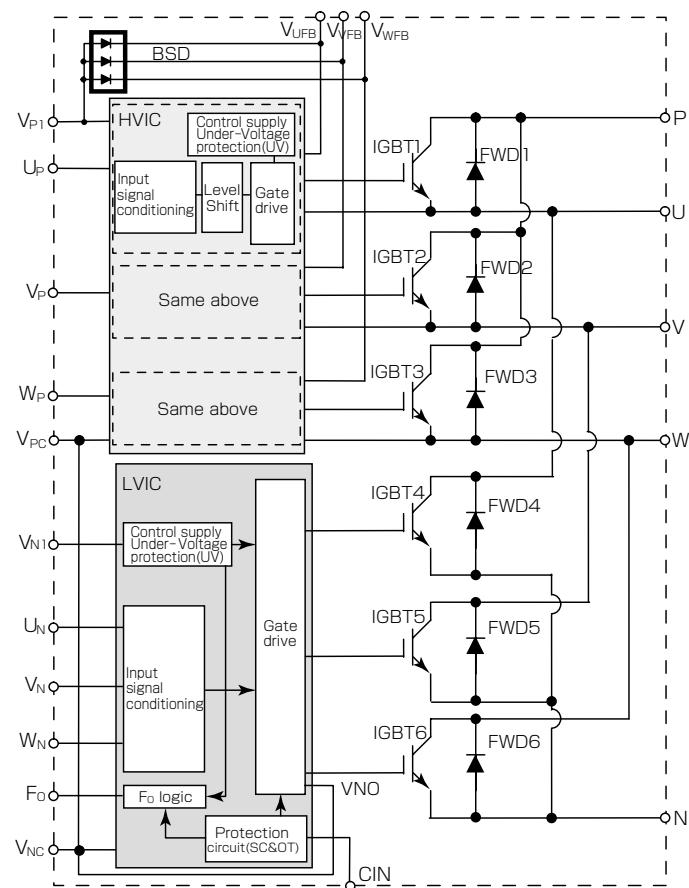

## 1,200V大型DIPIPM “Ver.4シリーズ”の外観

1,200V大型DIPIPM Ver.4シリーズは、LPT-CSTBT×6素子、FWD×6素子によるインバータ回路と、それらを駆動するHVIC (High Voltage Integrated Circuit), LVIC (Low Voltage Integrated Circuit)によって構成される。低損失のLPT-CSTBTと高放熱絶縁シート構造方式の採用によって、従来の1,200V DIPIPMシリーズに比べて低損失化及び低熱抵抗化を実現した。

## 1. まえがき

当社のDIPIPMは、パワーチップと制御ICチップを同一パッケージに内蔵したトランスマーキット構造のIPMであり、エアコン、冷蔵庫、洗濯機等の白物家電用途から小容量モータ駆動用としての産業機器用途と幅広く普及している。

近年の省エネルギー化・高性能化の需要が高まる中、当社ではトランスマーキット構造のIPMとしては業界初の1,200V DIPIPMシリーズ(5~25A)を2005年に製品化し、パッケージエアコンや産業用モータへのインバータ基板の小型化に貢献してきた。今回パッケージエアコンや産業市場向けに、従来の1,200V DIPIPMシリーズより小型・高機能が特長の1,200V大型DIPIPM Ver.4シリーズ(5~35A)を開発し、量産を開始した。

本稿ではこの1,200V大型DIPIPM Ver.4シリーズの概要、特長、内部構造及び内蔵機能について述べる。

## 2. 1,200V大型DIPIPM Ver.4シリーズの概要

1,200V大型DIPIPM Ver.4シリーズは、従来の1,200V DIPIPMシリーズに比べて、パッケージサイズを小型化し電流定格を拡大したシリーズ展開を行っている。次に1,200V大型DIPIPM Ver.4シリーズの特長について述べる。

### (1) 低熱抵抗

従来のモールド樹脂絶縁方式から、高放熱絶縁シート構造方式を採用することによって低熱抵抗化を実現(従来品の1,200V DIPIPM比で約30%低減)した。

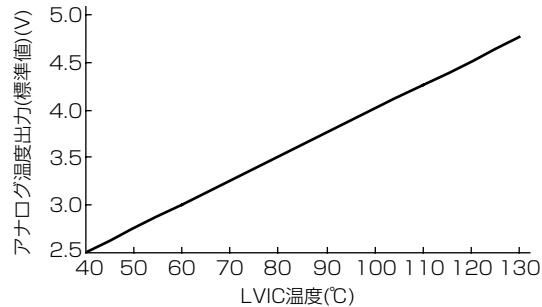

### (2) 温度検知機能

モジュール温度情報をアナログ電圧信号として外部へ出力する機能をLVICに内蔵することによって、モジュール温度検出を目的に取り付けていた外付けのサーミスタを不要とした。

### (3) 短絡保護回路の簡略化

パワー素子のエミッタ電流の数千分の1程度の電流を取り出し、この電流による短絡電流検出方式を採用した。大電力用シャント抵抗を使用しなくても短絡保護が可能となり、シャント抵抗による発生損失を大幅に低減した。

### (4) パッケージサイズの小型化と定格電流アップ

当社独自に開発した第5世代LPT-CSTBT搭載による低損失化と、絶縁シート構造方式の採用による低熱抵抗化によって、同定格電流の従来品に比べて約30%小型化し、さらに定格電流をアップしたシリーズ展開を実現した。

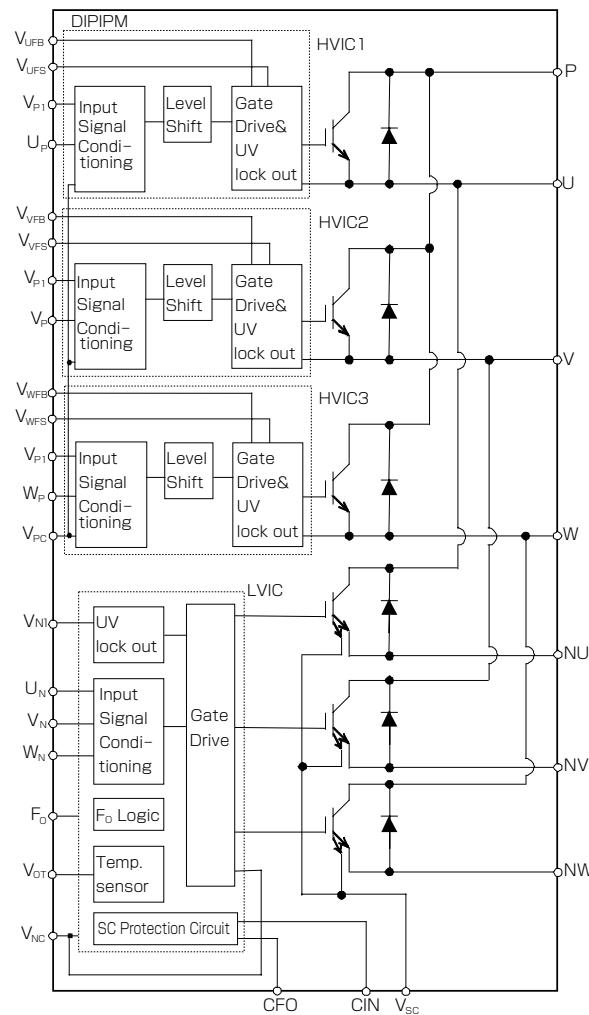

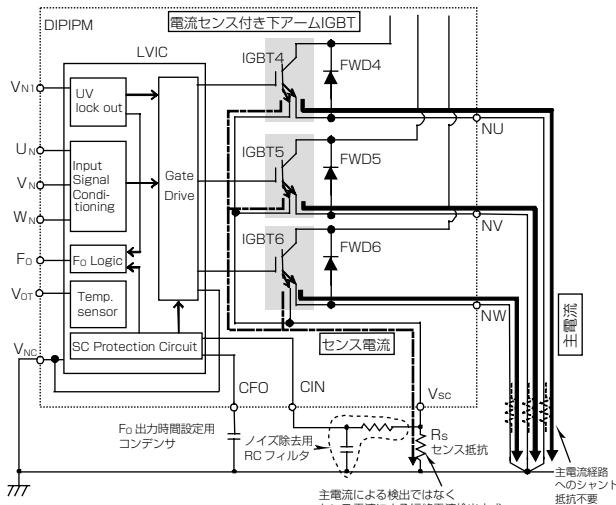

## 3. 1,200V大型DIPIPM Ver.4の回路構成と機能

DIPIPMの内部回路は、従来の構成と同様、IGBTとFWD(Free Wheeling Diode)を各6素子搭載し、三相AC出力インバータのパワー回路部とパワーチップを制御する

制御IC(HVIC, LVIC)で構成している。図1に1,200V大型DIPIPM Ver.4シリーズの内部回路図を示す。

### (1) パワー回路部

IGBT(6素子), FWD(6素子)による三相AC出力インバータ回路構成

### (2) 制御IC部

HVIC：上アームIGBT駆動回路、高圧レベルシフト回路、制御電源電圧低下(Under Voltage)保護回路(エラー出力なし)

LVIC：下アームIGBT駆動回路、制御電源電圧低下(Under Voltage)保護回路、LVIC部アナログ温度出力回路、短絡電流(Short Circuit)保護回路(短絡保護は、下アームIGBTのエミッタセンス( $V_{SC}$ )端子に外付けの電流検出抵抗を接続し、所定のしきい値電圧に達すると下アームIGBTを遮断する)

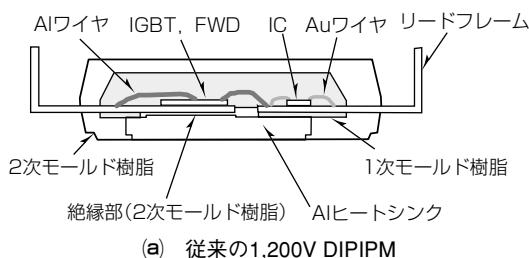

## 4. 1,200V大型DIPIPM Ver.4の内部構造

図2に、1,200V大型DIPIPM Ver.4と従来の1,200V DIPIPMの断面構造図を示す。1,200V大型DIPIPM Ver.4のパッケージ内部構造は、リードフレーム上にパワーチップで

図1. 1,200V大型DIPIPM Ver.4の内部回路

表1. PS22A78-Eの電気的特性

| 項目                 | 記号            | 条件                                          | 最小値 | 標準値 | 最大値 | 単位      |

|--------------------|---------------|---------------------------------------------|-----|-----|-----|---------|

| コレクタ・エミッタ間<br>飽和電圧 | $V_{CE(sat)}$ | $V_D = V_{DB} = 15V, T_j = 25^\circ C$      | —   | 1.9 | 2.6 | V       |

|                    |               | $V_{IN} = 5V, I_c = 35A, T_j = 125^\circ C$ | —   | 2.0 | 2.7 |         |

| FWD順電圧降下           | $V_{EC}$      | $T_j = 25^\circ C, -I_c = 35A, V_{IN} = 0V$ | —   | 2.2 | 2.8 | V       |

|                    |               | $t_{on}, V_{CC} = 600V, V_D = V_{DB} = 15V$ | 0.5 | 1.2 | 1.9 |         |

| スイッチング時間           | $t_{rr}$      | $I_c = 35A, T_j = 125^\circ C$              | —   | 0.5 | —   | $\mu s$ |

|                    |               | 誘導負荷(上-下アーム)                                | —   | 0.6 | 0.9 |         |

|                    | $t_c(on)$     | $V_{IN} = 0 \leftrightarrow 5V$             | —   | 2.4 | 3.5 |         |

|                    |               | —                                           | —   | 0.6 | 0.9 |         |

|                    | $t_{ce(off)}$ | —                                           | —   | —   | —   | —       |

(a) 従来の1,200V DIPIPM

(b) 1,200V大型 DIPIPM Ver.4

図2. DIPIPM断面構造

あるIGBT及びFWD、制御ICチップであるHVIC及びLVICを搭載し、各チップ間をAIワイヤー及びAuワイヤーで接続する。その後アルミヒートシンクと絶縁放熱シートを合わせてトランスマルチモールド化した構造である。

従来品のモールド樹脂による絶縁方式に対して、高放熱絶縁シートによる絶縁方式を導入したことが1,200V大型DIPIPM Ver.4シリーズの最大の特長である。またフレームとAIヒートシンクを絶縁するための2次モールド工程が、絶縁シート構造技術の導入によって削除可能となる。この新構造によって、1,200V大型DIPIPM Ver.4は従来の1,200V DIPIPMシリーズと比較して、約30%の熱抵抗低減と約30%の小型化を実現した。

## 5. 1,200V大型DIPIPM Ver.4の大容量化・高機能化

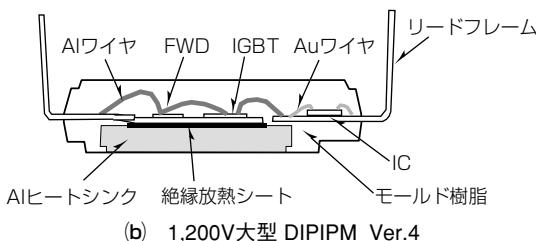

### 5.1 大容量化

1,200V大型DIPIPM Ver.4シリーズでは、当社独自に開発したパワーチップ“LPT-CSTBT”を搭載し損失低減を実現した。従来品搭載のプレーナ型IGBTとのトレードオフ特性(飽和電圧 $V_{CE(sat)}$ に対するターンオフスイッチング損失 $E_{off}$ )比較を図3に示す。

4章で述べた絶縁シート構造による低熱抵抗化との相乗効果によって、従来の1,200V DIPIPMシリーズは定格電流25Aまでのラインアップであるのに対し、1,200V大型DIP-

図3. トレードオフ特性

IPM Ver.4シリーズでは、35Aまで定格電流をアップしシリーズの充実化を実現した。表1に代表特性として“PS22A78-E(35A/1,200V)”の主な電気的特性を示す。さらにパッケージサイズを小型化し実装面積を従来品比で約30%削減し、すでに量産中である600V系大型DIPIPM Ver.3及びVer.4シリーズと同じ外形サイズとした。これによって、定格電圧が異なる場合でも実装基板の共用化ができる、基板の設計効率向上に貢献できる。従来シリーズとの比較を表2に示す。

### 5.2 高機能化

#### (1) 短絡保護回路の最適化

従来の短絡保護は、外部接続したシャント抵抗でIGBTのエミッタ電流に応じた発生電圧を検出し保護する方式を採用していた。1,200V大型DIPIPM Ver.4シリーズでは、アンペアレベルの大電流でなくエミッタ電流から分流したミリアンペアレベルのセンス電流に応じた電圧を検出し保護する方式に変更した(図4)。センス電流を取り出す目的として、下アームのパワーチップには電流センス付きIGBTを搭載している。エミッタ電流経路へのシャント抵抗接続が不要となるため、NU/NV/NW端子-VNC端子間インダクタンス起因のサージ電圧の発生を抑制でき、基板設計における設計自由度を向上できる。またシャント抵抗選定の際、従来の短絡保護方式では大電力用に限定されるが、センス電流での検出では損失を低減でき、基板実装面積の小型化・低コスト化に貢献できる。

表2. DIPIPMシリーズ比較

| 定格電圧   | シリーズ        | 型名      | 外形<br>(パッケージサイズ) | 電流定格 |     |     |     |     |     |     |     |

|--------|-------------|---------|------------------|------|-----|-----|-----|-----|-----|-----|-----|

|        |             |         |                  | 5A   | 10A | 15A | 20A | 25A | 30A | 35A | 50A |

| 600V   | DIP Ver.3   | PS218×× | 大型(79×31mm)      |      |     |     | ○   | ○   | ○   | ○   |     |

|        | DIP Ver.3.5 | PS212×× | 大型(79×31mm)      |      |     |     | ○   | ○   | ○   |     |     |

|        | DIP Ver.4   | PS21A×× | 大型(79×31mm)      |      |     |     |     |     |     | ○   | ○   |

| 1,200V | -           | PS2205× | 超大型(79×44mm)     | ○    | ○   | ○   |     | ○   |     |     |     |

|        | DIP Ver.4   | PS22A×× | 大型(79×31mm)      | ○    | ○   | ○   |     | ○   | ○   | ●   |     |

○：量産中 ●：開発検討中

図4. センス電流による短絡電流検出方式

図5. アナログ温度出力-LVIC温度特性

## 6. むすび

今回開発し製品化した1,200V大型DIPIPM Ver.4シリーズの構造、機能及び特長について述べた。今後は開発した技術の水平展開を進め、また地球環境保護を考慮した高附加值の製品開発によってインバータ市場への継続的な貢献を目指す。さらに民生市場のみならず、太陽光発電用途やIH(Induction Heating)用途への新市場要求に適した製品展開を行うことによって、DIPIPMの更なる需要拡大が期待される。

## 参考文献

- (1) 長原輝明, ほか: DIP-IPM Ver.4シリーズ展開, 三菱電機技報, 81, No.5, 349~352 (2007)

- (2) Kawafuji, H., et al.: New 5-35A/1200V Transfer Mold IPM with heat dissipating insulation sheet, PCIM (2008)

## (2) 温度検知機能の内蔵

モジュールの温度保護は、温度を検出するサーミスタをモジュールの放熱用ヒートシンクなどの周辺部に外部接続する方式が主流である。サーミスタをヒートシンクへ取り付けた場合、ヒートシンクとモジュールとの固定がゆるくなり、使用中に外れてしまうとモジュール温度が正確に検知できない可能性がある。今回の温度検知機能は、制御IC (LVIC) 内部に温度検出素子を内蔵してアナログ電圧信号を出力する方式である(図5)。この機能を利用すれば、外付けのサーミスタが不要となり、システムコストの低減が実現できる。さらにモジュールから直接信号を出力するため、温度情報の信頼性が確保される。

白水政孝\*

田中智典\*

坂居正喜\*

# 超小型DIPIPM “Ver.4 新シリーズ”

*Super Mini DIPIPM "Ver.4 New Series"*

Masataka Shiramizu, Tomofumi Tanaka, Masaki Sakai

## 要 旨

三菱電機のDIPIPM (Dual In-line Package Intelligent Power Module)は、パワーチップとそれを駆動し、かつ保護機能を持つ制御用ICチップを内蔵したトランスマルチモード構造のIPMである。

2004年から、DIPIPMシリーズの中で最小のパッケージとして超小型DIPIPM Ver.4シリーズを製品化し、エアコン、洗濯機、冷蔵庫などの白物家電機器のインバータユニットの小型化に貢献してきた。

近年、世界的な地球環境保護の高まりの中で、省エネルギー化がより一層重要視されはじめ、海外市場でもインバータ化が進んできている。それと同時に、白物家電市場ではインバータユニットの更なる低コスト化を進めており、基板搭載面積がより小さくてすむ小型外形品や周辺部品の

削減などの強い要望がある。

このような市場要求に対応するため、当社では超小型DIPIPM Ver.4から置き換わる製品として、“超小型DIPIPM Ver.4 新シリーズ”を2009年10月から量産し、白物家電市場に加え産業用途向けにも製品展開している。

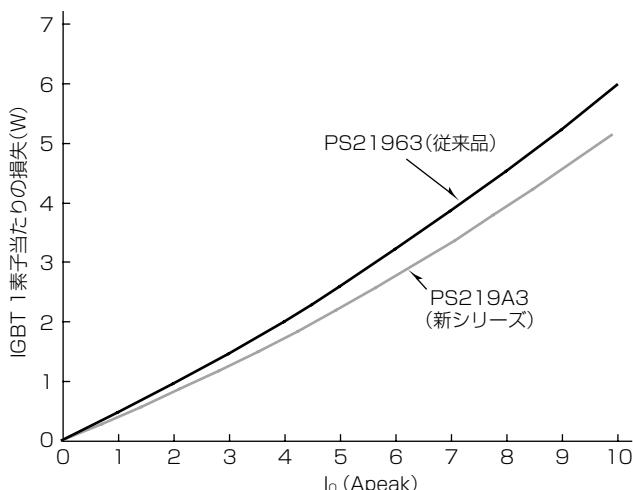

この超小型DIPIPM Ver.4 新シリーズは、外付けしていたBSD(Bootstrap Diode)を、超小型DIPIPM Ver.4と同じパッケージサイズに内蔵し、基板の搭載部品削減と基板面積縮小に貢献している。また、独自開発のフルゲートCSTBT(Carrier Stored Trench-Gate Bipolar Transistor)を搭載し、低損失(超小型DIPIPM Ver.4比約15%減)を実現している。

超小型DIPIPM Ver.4新シリーズの外観

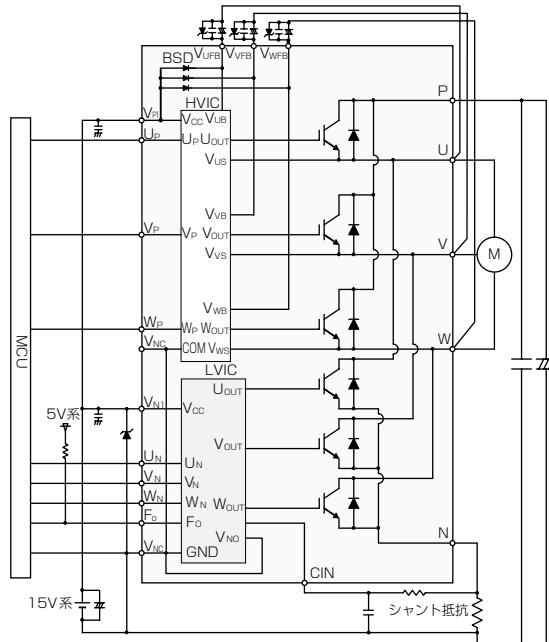

超小型DIPIPM Ver.4新シリーズの応用回路例

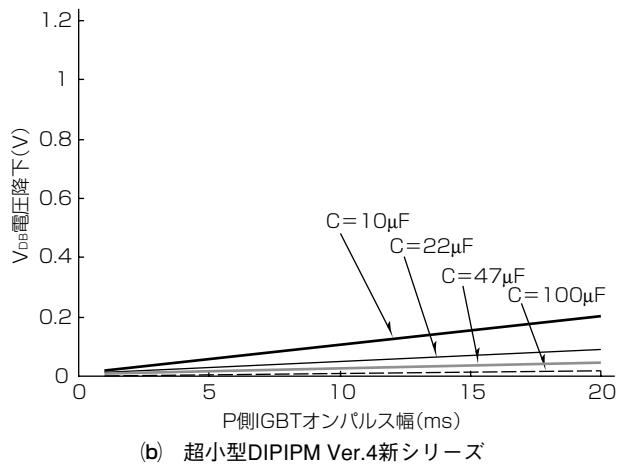

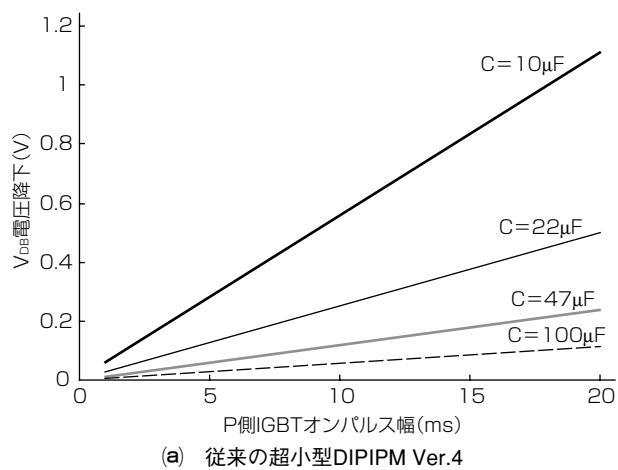

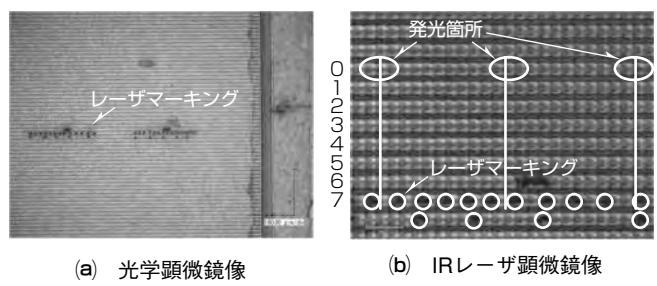

## 超小型DIPIPM Ver.4新シリーズの外観及び応用回路例