# シーケンサ"QnUモデル"のフルラインアップ化

中南和宏\* 青木康一\*

Complete Product Lineup of Programmable Controllers "QnU Models"

Kazuhiro Nakaminami, Koichi Aoki

## 要旨

製造現場では、生産性向上やタクトタイム短縮といった要求が日々高まっている。こうした声にこたえるため、2007年に高速シーケンサ"QnUモデル"を市場に投入した。その後、生産システムの多様化に対応するため、ラインアップの拡充を図った。本稿では、製品の特長とフルラインアップ化のための技術について述べる。

## (1) 製品の特長

超大容量モデルに、1,000Kステップのプログラムメモリや、最大925Kワードまで使用可能なデバイスメモリを搭載し、従来は不可能であった大規模制御を可能とした。また、プログラムの共通化を可能とし、メンテナンス性の向上を実現した。Ethernet<sup>(注1)</sup>内蔵モデルは、追加ユニットなしでEthernet通信を実現可能とした。また、IP (注1) Ethernetは、富士ゼロックス㈱の登録商標である。 (Internet Protocol)アドレスの設定なしで接続を実現する, 簡単接続機能を搭載した。小容量モデルは、従来品と比較 して演算処理速度を大幅に向上した。また、USB(Universal Serial Bus)ポートを標準搭載し、利便性の向上を 図った。

# (2) フルラインアップ化のための技術

超大容量モデルでは、増大したプログラムメモリに対し プリフェッチ・キュー方式を採用し、プログラムメモリの 大容量化と命令の高速実行の両立を可能とした。Ethernet内蔵モデルでは、簡単接続機能や同じハブに接続され たシーケンサCPU(Central Processing Unit)の自動検索機 能を実現するための技術を搭載した。小容量モデルでは、 通信技術を活用し、標準搭載したポートと外部機器との接 続性を強化した。

# フルラインアップ化を実現したシーケンサ"QnUモデル"

1,000Kステップのプログラムが実行可能なプログラムメモリを搭載し、デバイスメモリを最大925Kワードまで使用可能とした。また、Ethernetポートを標準搭載したことによって、上位情報系ネットワークや装置間の連携を強化した。 ※写真中のQ50UDEHCPU、Q100UDEHCPUは開発中のものであるため、シリアル番号を印字していない。

\*名古屋製作所 31(187)

## 1. まえがき

近年製造現場では、生産性向上やタクトタイム短縮といった要求の高まりを見せている。こうした声にこたえるため、2007年に高速シーケンサ"QnUモデル"を開発し、大幅な性能向上を達成した。今回、生産システムの多様化に対応するため、小規模システム制御用から超大規模システム制御用までに至るQnUモデルのフルラインアップ化を実現した(図1)。これによって、装置を制御するのに最適なシーケンサCPUを柔軟に選択可能となった。ラインアップ拡充とともに、デバッグ時の利便性向上や、トラブル発生時のダウンタイム短縮を目的として、QnUモデルの機能拡充を図った。さらに、発熱や振動に対する解析手法を導入し、製品の最適設計を行った。本稿では、製品の特長とフルラインアップ化のための技術について述べる。

## 2. 製品の特長

## 2.1 QnUモデルのフルラインアップ化

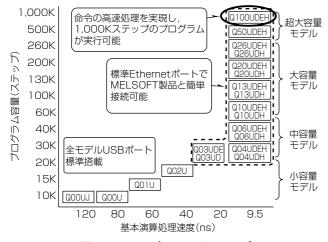

図1にQnUモデルのラインアップ,表1にQnUモデル "Q100UDEHCPU"の仕様を示す。プログラム容量は10K ステップから1,000Kステップまでの広範囲にわたりラインアップした。また、QnUモデルでは、新規にシステムASIC (Application Specific Integrated Circuit)を開発し、命令の高速処理(基本演算処理速度9.5ns)を実現した。とりわけ超大容量モデルは、命令の高速処理とプログラムメモリ大容量化の両立に成功した。

図1. QnUモデルのラインアップ

表 1. QnUモデル"Q100UDEHCPU"の仕様

| 項目      |                 |         | 仕様   |  |

|---------|-----------------|---------|------|--|

| メモリ容量   | プログラム(ステップ)     | 1,000K  |      |  |

|         | プログラムメモリ(byte)  | 4,000K  |      |  |

|         | 標準RAM(byte)     | 1,792K  |      |  |

|         | 標準ROM(byte)     | 16,384K |      |  |

| デバイス    | 内部デバイス(ワード)     | 29K     | 合計   |  |

| メモリ容量   | 標準RAM領域(ワード)    | 896K    | 925K |  |

| プログラム実行 | ログラム実行本数(本) 252 |         | 52   |  |

RAM: Random Access Memory ROM: Read Only Memory

## 2.2 プログラムの超大容量化

大規模化する生産システムの要求にこたえるために、プログラム容量1,000Kステップを搭載した超大容量モデルを開発した。従来、設備・装置ごとに別々に作成していたプログラムを共通化し、1台のシーケンサCPUで実行できれば、共通化したプログラムのみを管理すればよいため、メンテナンス性を大幅に向上させることができる。すなわち、シーケンサシステム全体のTCO(Total Cost of Ownership)削減につなげられる。また、シーケンサCPUは252本のプログラムが実行可能であり、構造化プログラミングによる設計・保守コスト削減につなげられる。さらに、デバイスメモリ容量についても、標準で最大925Kワードのデバイスメモリを使用可能としているため、従来デバイスメモリ容量拡張のためにメモリカードが必要であったシステムでは、コストの削減が可能となる。

#### 2.3 Ethernetポート標準搭載

中~超大容量モデルでは、Ethernetポートを標準搭載 したモデルをラインアップに追加した。従来Ethernetユニットが必要なシステムでは、ユニットが不要となるため、 装置全体のコスト削減につなげることができる。また、新 機能の追加によって、"MELSOFT"製品とシーケンサ CPUが簡単に接続可能となり、利便性が向上した。

## 2.4 小容量モデルの基本機能充実

小容量モデルでもQnUモデルのアーキテクチャを採用し、従来の"Qシリーズ"と比較して、演算処理速度で大幅な性能アップを実現した。さらに、ハイエンドな超大容量モデルからコストパフォーマンスに優れた小容量モデルに至る全モデルについてUSBポートを標準搭載し、利便性の向上を図った。

## 3. フルラインアップ化のための技術

## 3.1 QnUモデルのハードウェア構成

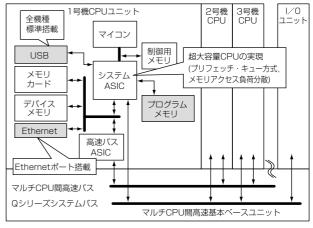

QnUモデルでは、各種モデルに最適なハードウェア構成を採用している。図2に超大容量モデルのハードウェア

I/O: Input/Output

図2. 超大容量モデルのハードウェア概略ブロック図

概略ブロック図を示す。QnUモデルでは、マルチCPU間高速バスシステムを構築し、マルチCPU間はもちろん、モーションコントローラとも高速な通信が可能である。また、システムASIC内部にあったプログラムメモリをシステムASIC高速データバス上に移すことで、命令の高速化とメモリの大容量化の両立を実現した。さらに、Ethernetポートを標準搭載し、上位情報系ネットワークや装置間の連携を強化した。

#### 3.2 メモリサイズ増大に伴う技術

システム全体のTCO削減を目的として、QnUモデルではプログラムメモリ容量1,000Kステップを搭載したモデル(超大容量モデル)を開発した。メモリ増大に伴い、新規ハードウェアアーキテクチャを搭載したシステムASICを開発し、シーケンサCPUの機能追加を実施した。

#### 3.2.1 命令の高速実行

プログラムメモリの大容量化を実現するに当たり、従来のシステムASIC内部メモリでは容量が不足するため、外部メモリを用いる必要がある。外部メモリにプログラムを格納した場合、プログラムの読み出し時に遅延が発生し性能低下を招く。超大容量モデルでは、遅延を回避するために命令プリフェッチ・キュー方式を採用した。命令プリフェッチ・キュー方式とは、あらかじめ大量の命令をシステムASIC内部のメモリに読み出しておき、システムASIC内部に保存した命令を実行する方式である。これによって、命令読み出しの遅延による性能低下を回避することに成功した。

#### 3.2.2 メモリアクセスの高速化

メモリ容量拡張に伴い、システムASICとつながるデータバスの負荷容量が増大し、メモリアクセスが遅くなる。 負荷容量を分散・軽減するため、最適な回路構成へ見直し を図ることによって、高速なメモリアクセス性能とメモリ の大容量化の両立を可能とした。

# 3.2.3 デバッグにおける利便性の向上

シーケンサCPUが稼働中に、シーケンサCPUを停止することなくプログラムを修正する(RUN中書き込み)機能が広く利用されている。大容量モデルや超大容量モデルは、プログラムメモリのサイズが増大したことに伴い、プログラムメモリへの書き込み開始から完了までの時間が小容量モデルと比較して長くかかる。書き込み実行後すぐに間違いに気づいてプログラムの転送をやり直す場合の手間を軽減させるため、RUN中書き込み中に書き込みを中止し、新たなプログラムが書き込み可能となる機能を実装した。これによって、装置設計のデバッグにおける利便性を向上させることができる。

# 3.3 Ethernetを活用した機器間,装置間の連携強化

装置の設計時や実稼働時には、Ethernet環境が整備されていることが多い。次に述べる機能の実現によって、シ

ーケンサCPUとEthernetの連携を強化し、設計・保守における利便性を向上させた。また、シーケンサCPU間、及び機器間のデータ連携を容易にした。

#### 3.3.1 通信設定の煩雑さ解消

Ethernet内蔵モデルは、Ethernet通信をする上で不可欠であるIPアドレスやサブネットマスクの設定を不要とし、USBやRS232接続と同様に、簡単に直結接続できる機能を実現した。これは、Ethernetケーブルを介して1:1でシーケンサCPUとMELSOFT製品を直結接続する機能である。また、シーケンサCPUに設定されているIPアドレスの値がわからなくなった場合にも有効な機能である。

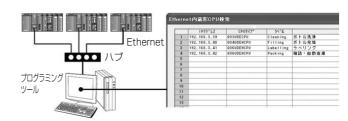

# 3.3.2 システム全体の把握における手間軽減

プログラミングツールを使用しているパソコンと同じハブに接続されているシーケンサCPUの検索結果を表示し、そこからアクセス対象のシーケンサCPUを選択することができる機能を実現した(図3)。これは、盤内に複数のシーケンサCPUが収納されており、各シーケンサCPUのIPアドレスが不明な場合や、直接シーケンサCPUを視認できない場合に有効な機能である。この機能は、プログラミングツールがシーケンサCPUに向けて要求パケットをブロードキャスト送信し、応答パケットからCPU種別等をリスト表示することによって実現している。

## 3.3.3 データ共有による装置間の連携強化

シーケンサCPUとEthernetで接続された機器が、任意のデータを無手順で送受信する機能(ソケット通信機能)を実現した。これによって、シーケンサCPU間やシーケンサCPUと上位パソコン間に加え、装置間、機器間のデータ連携が可能となる。ソケット通信機能では、TCP(Transmission Control Protocol)とUDP(User Datagram Protocol)の通信プロトコルをサポートし、複数の機器と同時に通信可能(ポート番号で識別)とした。ソケット通信機能で使用する主な命令を表2に示す。

図3.接続されているシーケンサCPUの検索結果表2.ソケット通信機能で使用する主な命令

| 命令          | 機能             | 通信プロトコル |     |

|-------------|----------------|---------|-----|

| th. th      | 1)交用と          | TCP     | UDP |

| SP.SOCCSET  | コネクションの設定      | 0       | 0   |

| SP.SUCCSE I | (IPアドレス,ポート番号) |         |     |

| SP.SOCOPEN  | コネクションのオープン    | 0       | ×   |

| SP.SOCSND   | データ送信          | 0       | 0   |

| SP.SOCRCV   | データ受信          | 0       | 0   |

| SP.SOCCLOSE | コネクションのクローズ    | 0       | ×   |

○:命令を使用する ×:命令を使用しない

#### 3.4 接続性強化によるコストパフォーマンス向上

ユーザー要望の高いUSBポートを小容量モデルに標準搭載することで、RS232ポートでGOT (Graphic Operation Terminal) などの機器を接続している場合でも、USBポートからプログラミングツールを使用しているパソコンへの同時接続を実現した。また、小容量モデル標準搭載のRS232ポートによる"MELSECコミュニケーションプロトコル(MCプロトコル)"通信を実現した。これによって、小規模システム制御用から超大規模システム制御用までのシーケンサCPUで、MCプロトコルによる外部機器との直結接続が実現できる。

## 4. ダウンタイム短縮

例えば、ネットワークユニットといったインテリジェント機能ユニットで発生したエラーコードなどの情報は、電源OFF時に保持されないことが多く、起動時やリセット時にそれらの情報がクリアされてしまう。インテリジェント機能ユニットで発生したエラーをシーケンサCPU内部の停電保持可能なメモリに収集することによって、起動時やリセット解除時でも、エラー情報を保持できる機能を追加した。CPUに保存されたエラー情報と組み合わせることで、システムに発生したエラーの原因を早期解明し、システムのダウンタイム短縮につなげることができる。また、今後インテリジェント機能ユニットが新たにラインアップに追加された場合でも、シーケンサCPUをバージョンアップすることなく、新しいユニットのエラー履歴の収集が可能な構造を実現している。

# 5. 耐環境性への取り組み

QnUモデルでは、熱解析や振動モードの分析を実施することによって、発熱、振動などの環境要因に対して最適設計を行い、耐環境性の向上に努めている。

# 5.1 熱解析

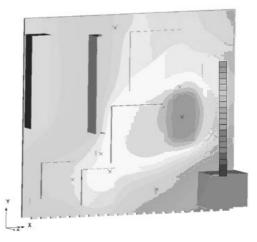

高温環境下では、電子部品の寿命が短くなる。図4は超

図4. 超大容量モデルの内部基板の部品温度分布

大容量モデルの内部基板の部品温度分布の解析結果である。 熱解析ツールの活用によって、部品配置や発熱対策部品実 装の最適設計を行い、温度マージンを確保した。

#### 5.2 振動解析

プレス装置など振動環境下では、高い耐振性が求められる。シーケンサCPUの耐振動性は、プログラマブルコントローラ装置への公的規格"JIS B 3502、IEC 61131-2"に適合している。振動モードの分析結果から、振動を小さくするように部品を配置し、高い耐振動性を備えた製品を開発した。

# 6. む す び

高速シーケンサ"QnUモデル"のフルラインアップ化と、それを実現するための技術について述べた。フルラインアップ化の実現によって、装置を制御するのに最適なシーケンサCPUを柔軟に選択可能とした。今後も、シーケンサCPUの高速化・高機能化、利便性の向上を追求していく。

## 参考文献

(1) 石田 浩, ほか:高速シーケンサ"QnUシリーズ", 三菱電機技報, **81**, No.4, 249~252 (2007)