## CMOSプロセスによる高周波デバイス技術

大森達夫\* 末松憲治\*\* 山川 聡\*

## 要旨

昨今のシリコンCMOSプロセスの急速な微細化により,デバイスの高周波特性が著しく向上し,GHz帯での高周波動作が可能となってきた。このような背景を下に,Bluetoothや無線LAN(IEEE802.11a/b/g)等の近距離無線通信用LSIの製品化が始まっている。また,CMOSで高周波回路の実現により,ロジック回路やメモリ回路との1チップ化が可能になることから,無線携帯機器の部品点数削減や低コスト化の面からも期待されている。

しかし、CMOSで用いるシリコン基板は、半絶縁性である化合物半導体基板とは異なり比抵抗が約10 ・cmと低いため、基板に起因した寄生効果による信号損失が大きいという問題がある。したがって、高周波回路設計には基板起因の寄生効果に対する物理的な理解や高精度モデルが重要

となる。

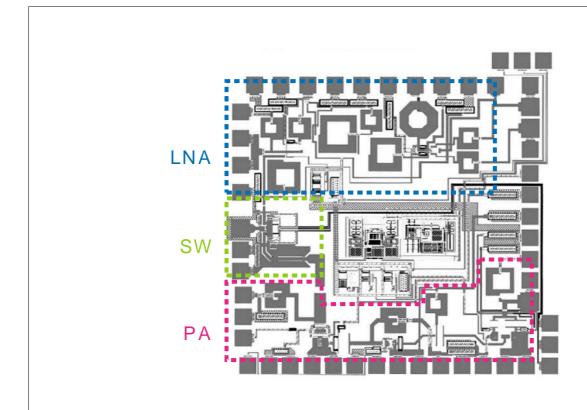

今回,5 GHz帯無線LAN用デバイスを目的として 0.18μmCMOS技術を用いたトランジスタ,インダクタの 等価回路モデルの作成,及び伝送線路間のクロストークの 電磁場シミュレーションを用いた解析を行った。また,これらのモデルや,得られた知見を基に,低雑音アンプ (LNA),送信アンプ(PA),アンテナスイッチ(SW)等からなる送受信回路の試作も行った。特に基板内の不純物分布を新しく最適化したトランジスタ(Depletion-layer-Extended Transistor: DET)を用いたアンテナスイッチにおいて,挿入損失1.4dB,アイソレーション25dBといった良好な特性を得ることができた。

## 5 GHz帯無線LAN用の高周波送受信部試作回路

このレイアウトは, $0.18\mu mCMOS$ プロセスを用いた  $5\,GHz$ 帯無線LAN用の高周波送受信部の試作回路である。低雑音アンプ (LNA),送信アンプ (PA),アンテナスイッチ (SW)を搭載している。トランジスタ,インダクタ,線路等の個々の要素デバイスは  $5\,GHz$ に対して最適にレイアウトされている。