## 0.18µm eDRAM**コアの開発による** 0.18µm DRAM**混載システム**LSI**コア技術の確立**

林 勇\* 辰巳 隆\*\*\* 山崎 彰\* 井上一成\*\*\*

## 要旨

0.18μm HD( Hyper DRAM )技術を使用して32MビットeDRAMコアを開発した。

eDRAMの応用分野は、大きく分けて、グラフィック関連、ネットワーク関連、ディジタルAV、パソコン周辺関連に分類することができ、特にグラフィックやネットワーク関連では大メモリ容量+高速データ転送が必要になる。最も高性能の要求される三次元グラフィックでは120Mビット、30Gバイト/秒以上の性能が要求される。今回開発したeDRAMコアは、これらの要求を十分に満たす性能を実現するものである。

高速データ転送速度を実現するために,リード/ライトデータバス分離,デュアルポートセンスアンプを採用した。これにより,256ビットリード/ライト同時で200MHz動作(=12.8Gバイト/秒)の高スループット動作を実現した。さらに,このコアを四つ搭載すると,最高51.2Gバイト/

秒のデータ転送速度が得られる。また,電源系のモジュール化などにより,バンク数:1,2,4バンク,データバス幅:リード/ライト各64,128,256ビット,の構成への対応を可能にした。

コアサイズは23.3mm²,動作電流はリード/ライト同時動作時に1.2W,スタンバイ電流は0.8mWである。動作仕様上の特長としては、一方のバンクをアクティベートしながら他のバンクをプリチャージしたり、一方のバンクをリード/ライト中に他のバンクをアクティベートすることが可能であり、見掛け上のレイテンシを小さくすることが可能である。

今回0.18µm HD eDRAMコアの開発を行うことで,今後ますます必要とされるDRAM混載LSI市場の要求を十分満たすことができる高速eDRAMコア設計技術の動作を実証することができた。

## 0.18µm eDRAM**のチップ概要**

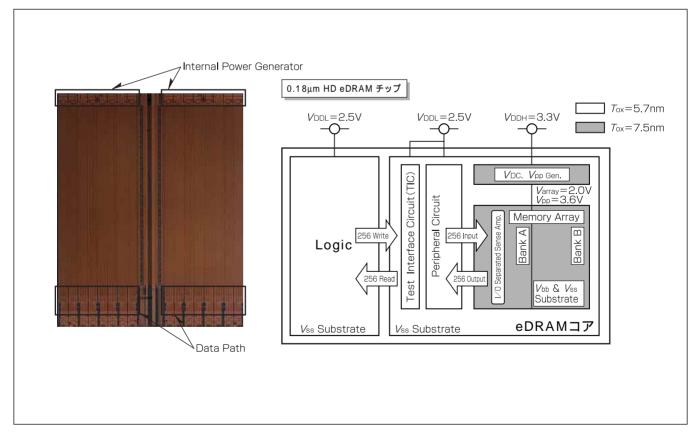

$0.18 \mu m$  eDRAMコアのチップ写真と,eDRAMコアを混載したチップのイメージ図を示す。コアの周辺部はユーザーロジックと同じ2.5 V 電源  $V_{\text{DDL}}$  )で動作し,アレー部は3.3 V電源  $V_{\text{DDH}}$  から降圧回路及び昇圧回路によって得られる電源で動作する。周辺部はゲート酸化膜5.7 nm,アレー部は7.5 nmのトランジスタを使用している。