## 第三世代64MビットDRAM

井上好永\* 蜂須賀敦司\*\* 羽倉 司\* 白竹 茂\*\*\* 早川吾郎\*

## 要旨

DRAM( Dynamic Random Access Memory )は,ファーストページ(FP)モードからEDO(Extended Data Out )モードに移行し,今やシンクロナスDRAMの全盛期となりつつある。今後はRambus DRAM\*等の超高速性能が要求されており,DRAMには従来に増して多機能・高性能化が求められる。

こうした要求に対応するため, 0.25μmCMOSプロセス

を使用した高速で低消費電力な第三世代64MビットDRA M EDOモード品の開発を行った。さらに、将来の低電圧化に対応させるため2.5V動作を想定して回路を開発した。

今後,第三世代64MビットDRAMをコアとして,更なる高性能な製品を開発していく。

\* "Rambus DRAM"は,米国Rambus Inc.の商標である。

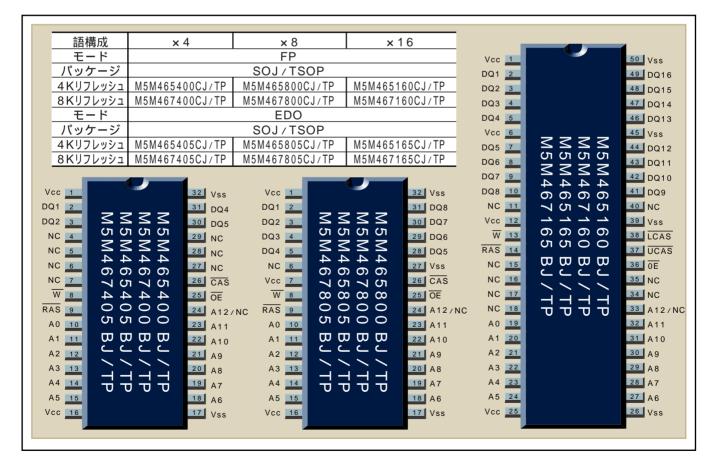

## 第三世代64MビットDRAM FPモード EDOモード ピン配置

左から×4品,×8品,×16品のピン配置図(400mil SOJ,400mil TSOP)を示す。 注:A12-8kリフレッシュ品,NC-4kリフレッシュ品

NC: ノンコネクションピン