# mitsubishi

## 三菱電機技報

Vol.68 No.3

特集“先端半導体”半導体事業35周年記念

'94 3

## 特集 “先端半導体” —— 半導体事業35周年記念 ——

### 目 次

#### 特集論文

|                                      |       |

|--------------------------------------|-------|

| 巻頭言                                  | 1     |

| 平林庄司                                 |       |

| パラダイムシフトの時代を迎えたマイクロエレクトロニクス          | 2     |

| 大見忠弘                                 |       |

| 半導体の技術動向と展望                          | 3     |

| 坂根英生                                 |       |

| 64M ビット DRAM                         | 7     |

| 諸岡毅一・宮本博司・古谷清広・岡本龍郎・須賀原和之            |       |

| ブロック消去可能な16M ビットフラッシュメモリ             | 11    |

| 中山武志・三原雅章・宮勝好和・大井 誠・新井 肇             |       |

| 高速 QuadCAS 付き第三世代 4 MDRAM            | 15    |

| 吹上貴彦・豆谷智治                            |       |

| 高速 1 M ビット CMOS スタティック RAM           | 19    |

| 櫻原洋次・坂口定則・秋山義雄・田原良昭・南 ふゆみ            |       |

| 超薄形パッケージ IC を搭載した大容量 IC メモリカード       | 24    |

| 郷地英伸・越智克則・寺岡康宏                       |       |

| 高性能新16ビット マイクロコントローラ “M16シリーズ”       | 29    |

| 中尾裕一・北上尚一・清水 徹・三輪久晴・水垣重生             |       |

| データリンク層通信プロトコルコントローラ内蔵 MCU           | 34    |

| 長 労樹・山ノ井悟郎・林 良紀・田代 哲・藤沢行雄            |       |

| システム提案型マイコン応用技術                      | 39    |

| 樋口敬三・山田闇裕・杉本正樹                       |       |

| 12ビット100kFLIPS ファジー推論プロセッサ           | 45    |

| 下郷研一・新田泰彦・坂下徳美・中村和夫・徳田 健             |       |

| 0.5μm CMOS セミカスタム IC                 | 49    |

| 真田邦彦・青木一夫・前野秀史・松本 尚・笛田真喜子            |       |

| 国際標準 JPEG 準拠のカラー画像圧縮・伸長 LSI          | 54    |

| 小川文伸・井田静男・今中良史・杉野博之・寺根秀幸             |       |

| VTR 用ワンチップカラオケプロセッサ LSI              | 59    |

| 安達靖史・山田友右                            |       |

| 3 V 動作10ビット50M サンプル／秒 CMOS D／A コンバータ | 63    |

| 中村泰之・三木隆博・西川毅一・岡田圭介                  |       |

| トレンチ MOS ゲート構造の600V 絶縁ゲートバイポーラトランジスタ | 68    |

| 原田真名・湊 忠玄・高橋英樹・西原秀典・井上敬二・高田育紀        |       |

| 溶融再結晶化法を用いた新型高効率薄膜多結晶シリコン太陽電池        | 73    |

| 森川浩昭・有本 智・石原 隆・隈部久雄・室谷利夫             |       |

| 小型・高機能エアバッグ用半導体加速度センサ                | 77    |

| 荒木 達・山本雅裕・瀬々倉 孝                      |       |

| CMOS ゲートアレー用自動レイアウト技術                | 82    |

| 中尾博臣・高橋一浩・定兼利行・奥田亮輔・寺井正幸・佐藤興二        |       |

| VLSI マスクデータ照査システム                    | 86    |

| 菅野 誠・濱本末雄・田中健一・宗像恒任・森泉幸一             |       |

| 高誘電率薄膜技術                             | 90    |

| 佐藤一直・三上 登・川原孝昭・楠見嘉宏・伊藤博巳             |       |

| X 線リソグラフィー技術                         | 94    |

| 幸丸正樹・丸本健二・尾崎禎彦・島野裕樹・中西哲也・吉岡信行        |       |

| ハーフミクロン対応ロジック用 CMOS LSI ウェーハプロセス     | 99    |

| 野崎雅彦・越久和俊・原田 繁・東谷恵市・高田佳史             |       |

| ノンバイアス ECR プラズマによる微細加工技術             | 103   |

| 丸山隆弘・藤原伸夫・米田昌弘・塚本克博・大森達夫・番條敏信        |       |

| 高機能・高信頼性パッケージ                        | 107   |

| 佐々木育夫・樋口徳昌・森賀南木・木村通孝                 |       |

| 特許と新案                                |       |

| 「パターン配置方法」「寸法選別方法」                   | 113   |

| 「短絡移行アーク溶接機」                         | 114   |

| スポットライト                              |       |

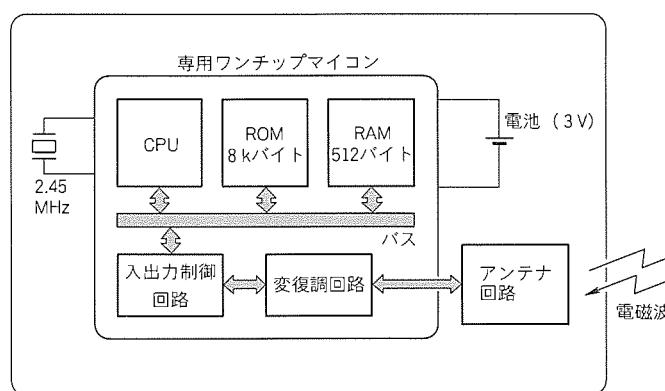

| 非接触 IC カード                           | 112   |

| 電源開発(株)本州-四国連系線鳴島ケーブルヘッド地点用          |       |

| 500kV, 250MVA 分路リアクトル                | (表 3) |

### 表紙

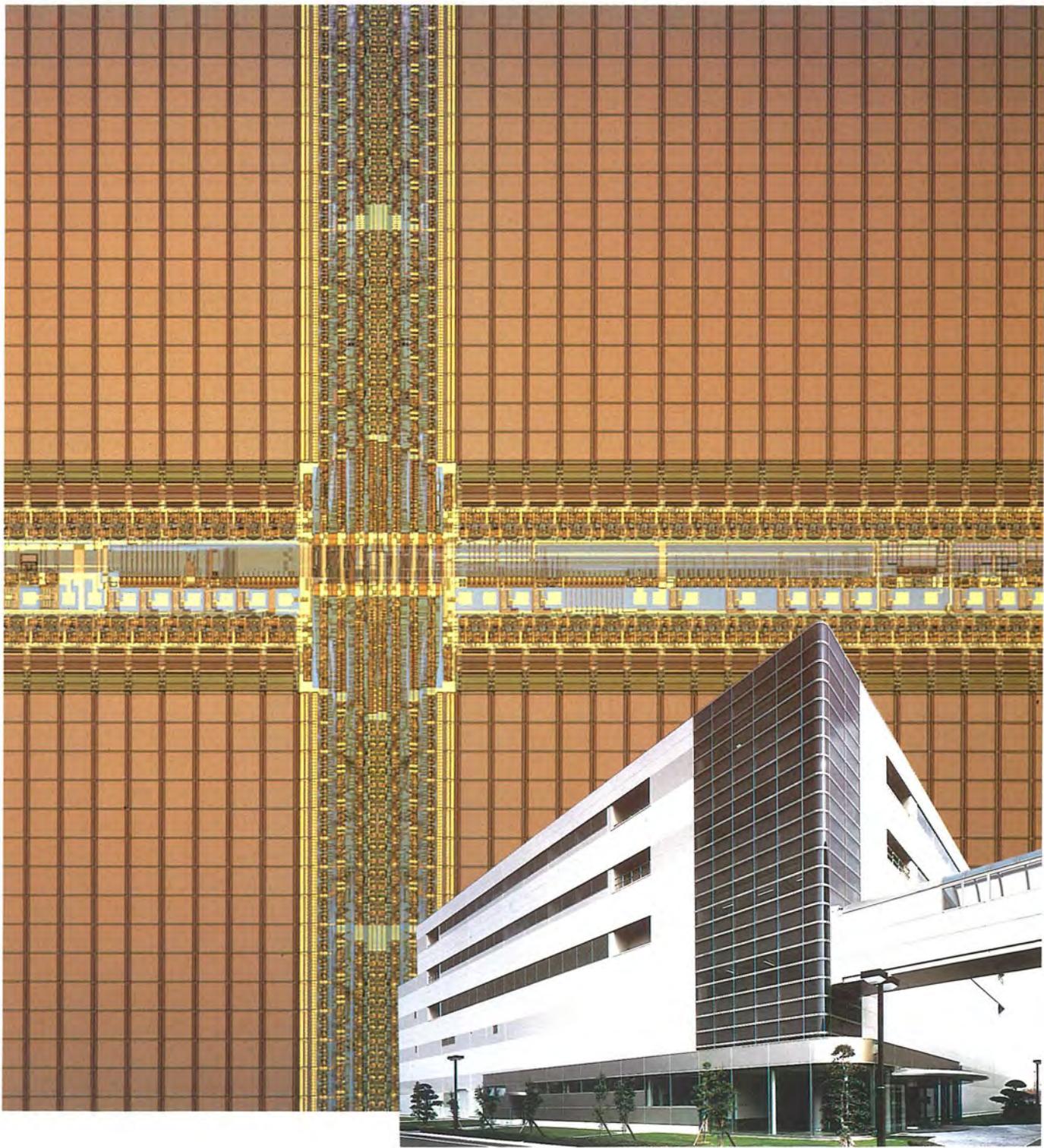

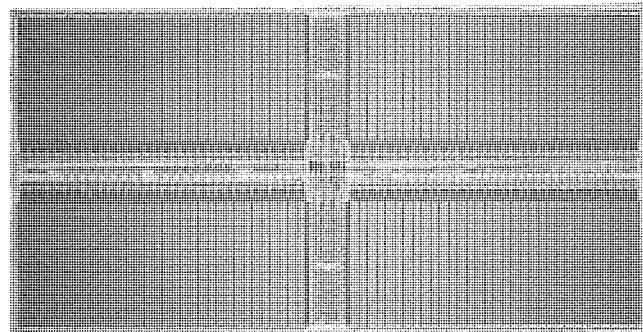

#### 64M ビット DRAM チップと ULSI 開発棟

表紙の写真は、当社における半導体技術開発の拠点である ULSI 開発研究所(伊丹市)に完成した ULSI 開発棟と、そこで開発した 64M ビット DRAM チップである。

ULSI 開発棟は 64M ビット DRAM 以降の先端製造技術開発及び先端デバイスの開発を行うため建設した新開発棟で、最新鋭のクリーンルームと開発設備を備えている。

64M ビット DRAM は、0.35μm CMOS 技術を用い、面積10.59mm×20.6mm のチップに約1億4000万個のトランジスタやコンデンサを集積しており、動作電圧 3.3V で 32ns の高速アクセス時間を実現した。

三菱電機技報に掲載の技術論文では、国際単位“SI”(SI 第2段階(換算値方式)を基本)を使用しています。ただし、保安上、安全上等の理由で、従来単位を使用している場合があります。

## アブストラクト

### 半導体の技術動向と展望

坂根英生

三菱電機技報 Vol.68・No.3・p.3~6 (1994)

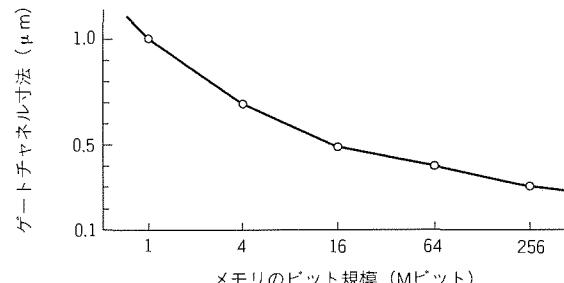

急速な半導体技術の進歩が、応用市場を目覚ましく拡大してきた。その半導体産業も1990年代に入り、量的拡大から、より質的拡大すなわち高性能化・小型化・低消費電力化・ディジタル化等を一層追求する時代に転換してきている。この転換期を乗り越えるためには、応用市場からのニーズと半導体自身のシーズ技術の融合がますます重要になっていく。本稿では、最近の応用市場動向と、それに対する半導体側からのアプローチについて展望する。

### 64M ビット DRAM

諸岡毅一・宮本博司・古谷清広・岡本龍郎・須賀原和之

三菱電機技報 Vol.68・No.3・p.7~10 (1994)

0.35μm デザインルールと 5 層ポリシリコン 2 層アルミ CMOS プロセスを用いた 64M ビット DRAM を開発した。 $\times 1 / \times 4 / \times 8 / \times 16$  の 4 種類の語構成と、高速ページ/ニブル/スタティックコラムの各モードを同一チップ上で選択可能とした。チップサイズは 218mm<sup>2</sup> であり、500mil 幅の SOJ/TSOP パッケージに収容している。電源電圧 3.3 V, LVTTL(Low Voltage TTL) インタフェースを採用した。性能は、RAS アクセス時間 50ns、動作時電源電流 120mA を実現している。

### ブロック消去可能な 16M ビットフラッシュメモリ

中山武志・三原雅章・宮脇好和・大井 誠・新井 肇

三菱電機技報 Vol.68・No.3・p.11~14 (1994)

3.3V と 12V の 2 電源で動作するブロック消去(64K バイト単位)可能な 16M ビットフラッシュメモリを開発した。0.5μm ルールを用いて、セルサイズ 1.7μm × 1.9μm, チップサイズ 9.3mm × 11.5mm を実現した。電源電圧 3.3V で 100ns の高速アクセスタイムや、自動消去中に消去動作を一時中断し、読み出し動作を行い、引き続き消去動作を行うことのできる消去サスPEND/リジューム機能などを実現した。

### 高速 QuadCAS 付き第三世代 4 MDRAM

吹上貴彦・豆谷智治

三菱電機技報 Vol.68・No.3・p.15~18 (1994)

0.65μm の最小設計寸法を採用し、さらに最新回路技術を駆使することにより、アクセスタイムの高速化・低消費電力化を図った 4 MDRAM (4 メガビット DRAM) 第三世代品を開発した。新機能である QuadCAS (コラムアドレスストローブ) 機能は、4 ビットの入出力データを四つの CAS を用いることにより、任意に高速書き込み、読み出しを可能にする。また、バッテリ駆動に適したセルフリフレッシュ機能も備えている。

### 高速 1 M ビット CMOS スタティック RAM

樋原洋次・坂口定則・秋山義雄・田原良昭・南 ふゆみ

三菱電機技報 Vol.68・No.3・p.19~23 (1994)

アクセスタイム 15ns の高速 1 M ビット (128K × 8 / 256K × 4 / 1 M × 1) CMOS スタティック RAM (SRAM) を開発した。この SRAM では高性能を達成するために多層配線を含む 0.6μm 微細化プロセス技術と高信頼性かつ高性能トランジスタを採用している。また、回路面において多層配線を有効に用いる分割ワード線方式、新型の内部同期式回路などを使用し、アクセス時間 15ns という高速性能を達成した。

### 超薄形パッケージ IC を搭載した大容量 IC メモリカード

郷地英伸・越智克則・寺岡康宏

三菱電機技報 Vol.68・No.3・p.24~28 (1994)

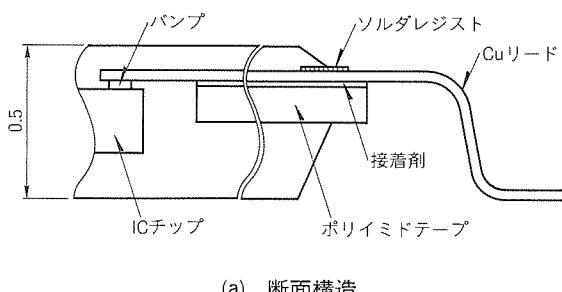

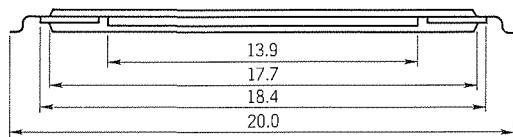

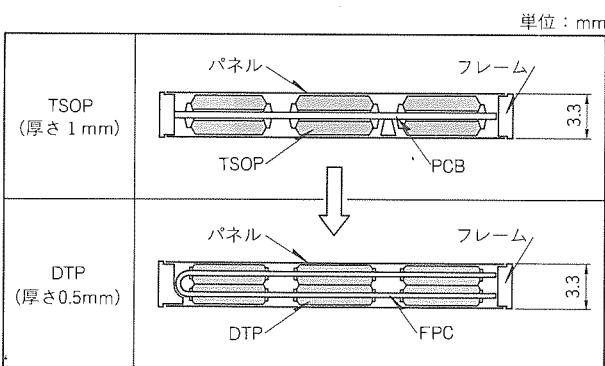

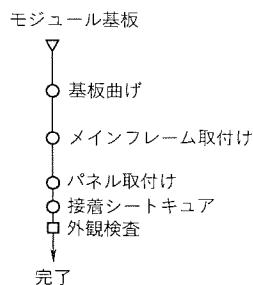

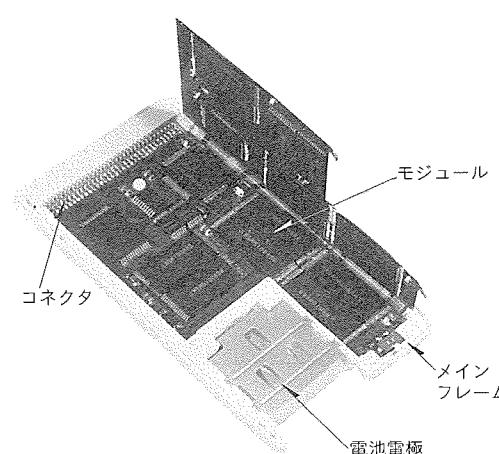

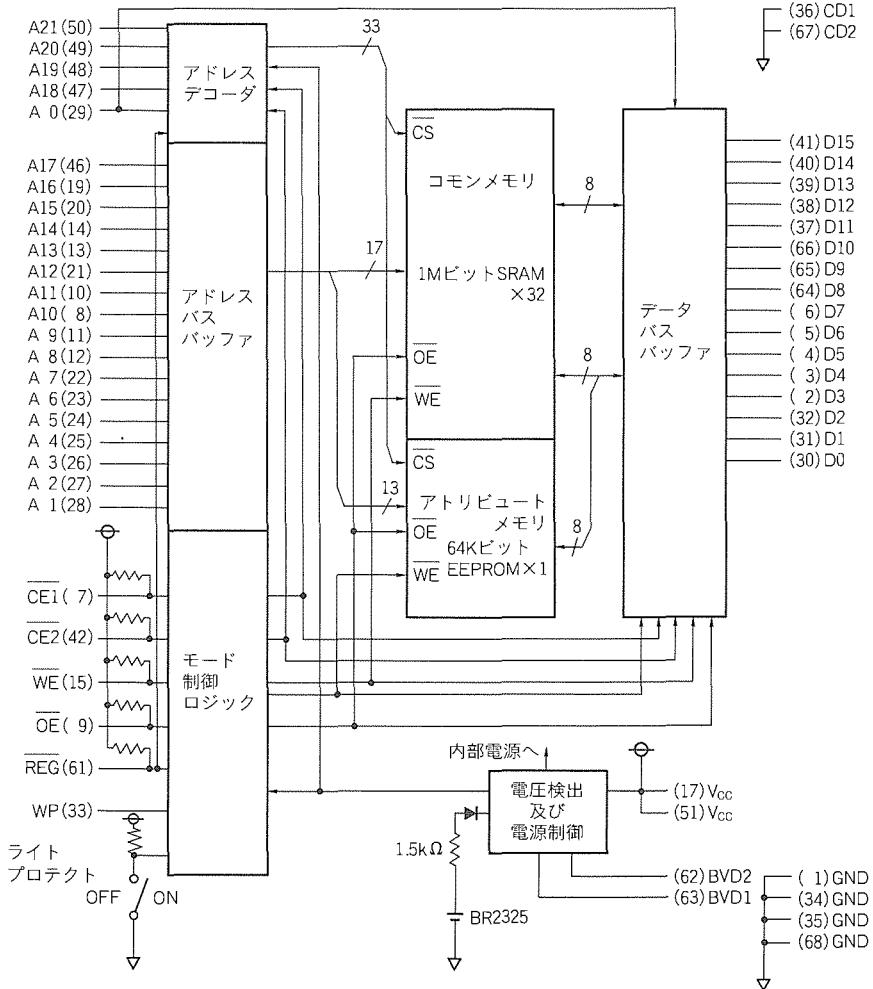

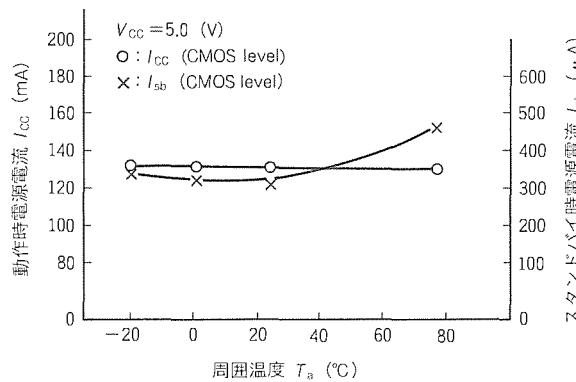

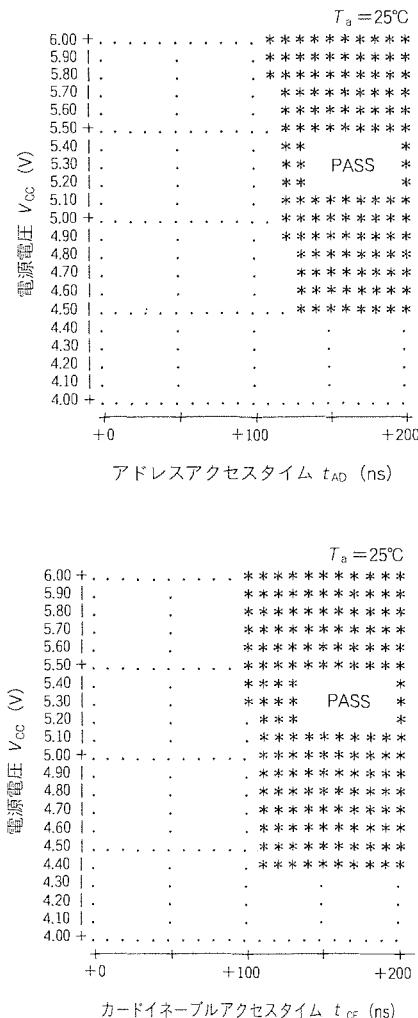

厚さ 0.5mm の超薄形パッケージとして 32pin DTP(Dual Tape carrier Package), 28pin DTP 及び 80pin QTP(Quad Tape carrier Package) を業界で初めて開発した。32pin DTP に 1M ビット SRAM を、80pin QTP にカード周辺回路用 IC を封入し、それぞれ 32 個と 3 個を高密度実装した厚さ 3.3mm の高信頼性の 4 M バイト SRAM カードを開発した。

### 高性能新 16 ビットマイクロコントローラ "M16シリーズ"

中尾裕一・北上尚一・清水 徹・三輪久晴・水垣重生

三菱電機技報 Vol.68・No.3・p.29~33 (1994)

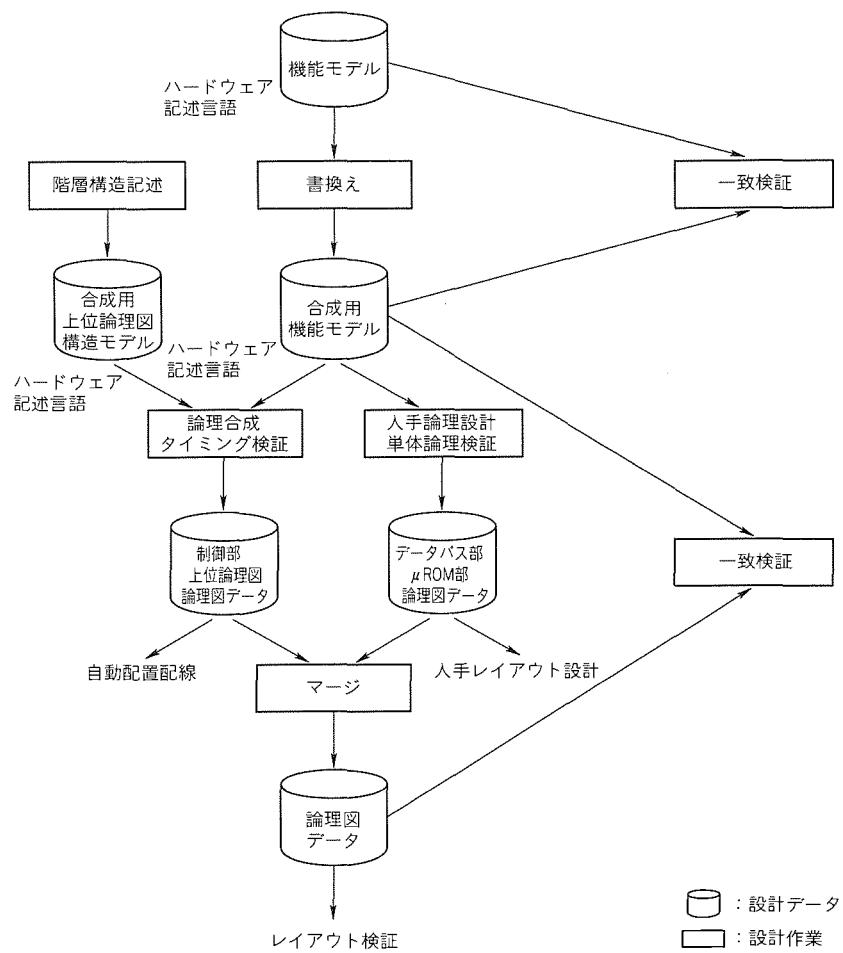

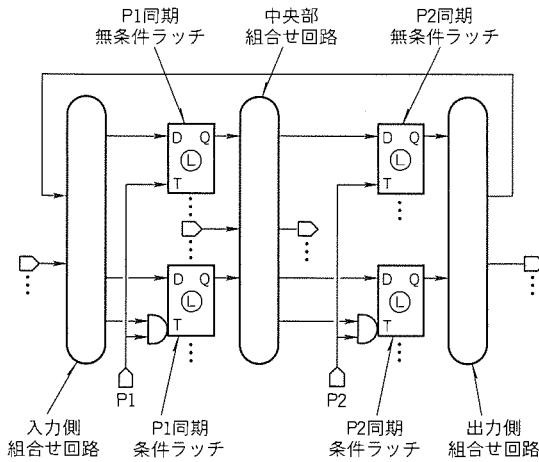

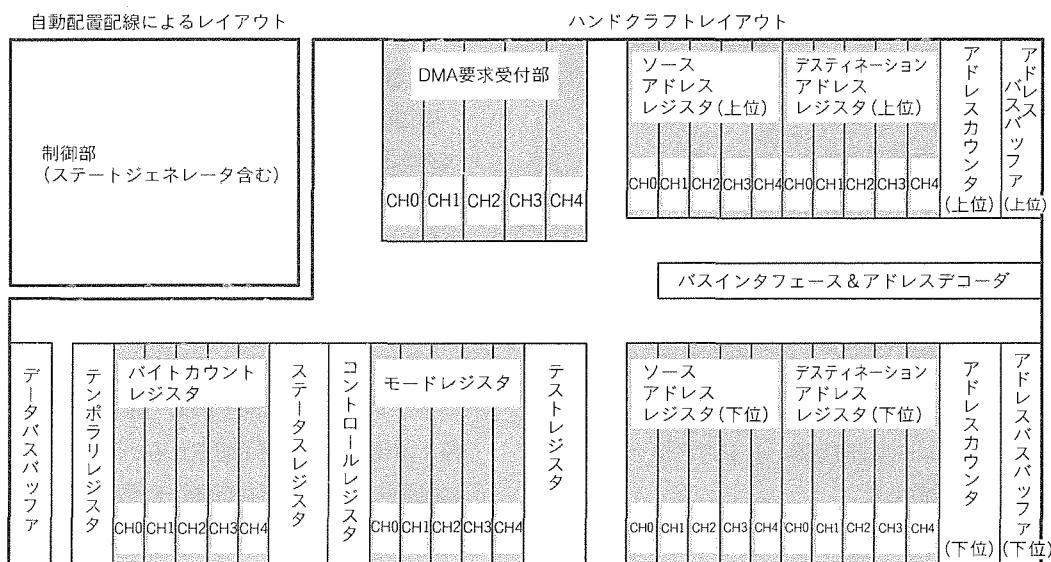

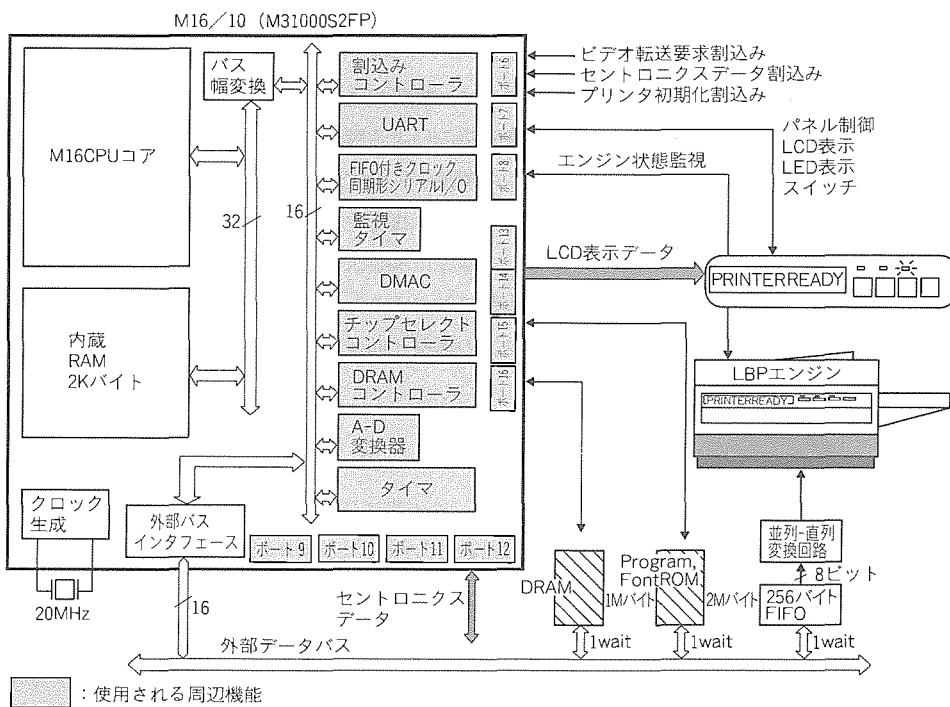

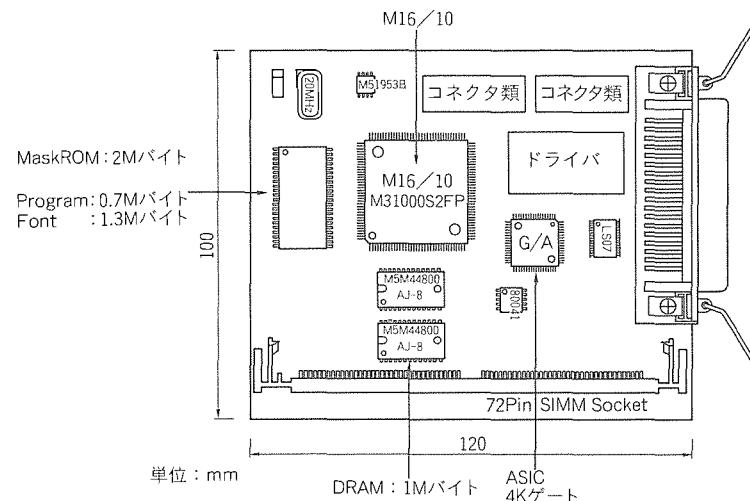

CPU 内部 32 ビット、内蔵周辺及び外部バス 16 ビットを基本構成とする新世代 16 ビットマイクロコントローラ M16 シリーズを開発した。第一世代 M16 は、4~5MIPS を持つ CPU コア及び OA 関連機器制御に適した周辺機能を搭載し、約 37 万トランジスタを集積する。LSI は、いわゆるトップダウン設計の考え方によって開発した。HDL による定義を最上位とし、生成するマクロセルの性格により、セルベース設計とハンドクラフト設計を使い分けて最適なマイコン LSI を実現した。

### データリンク層通信プロトコルコントローラ内蔵 MCU

長 芳樹・山ノ井悟郎・林 良紀・田代 哲・藤沢行雄

三菱電機技報 Vol.68・No.3・p.34~38 (1994)

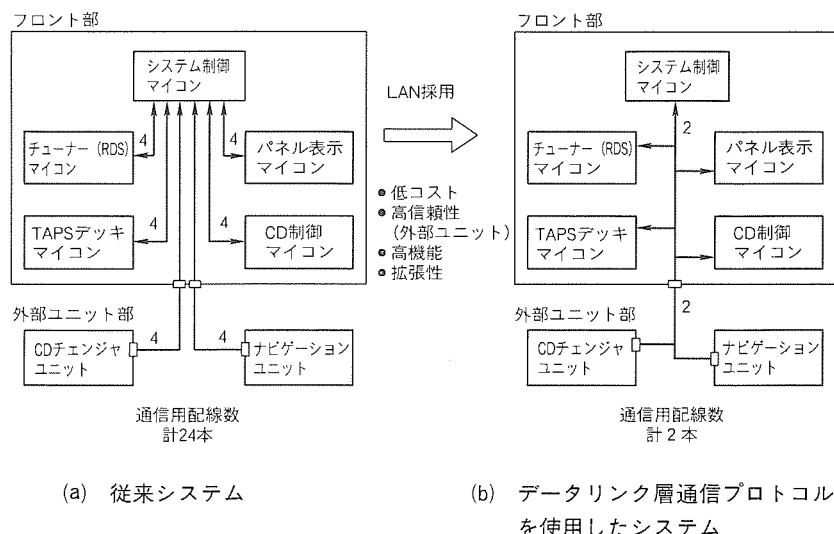

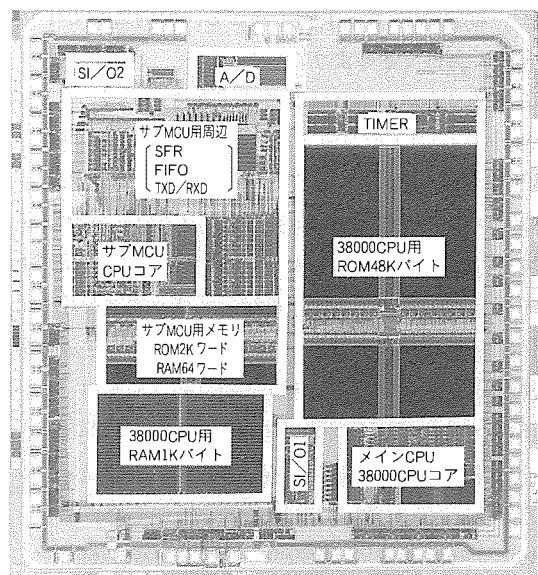

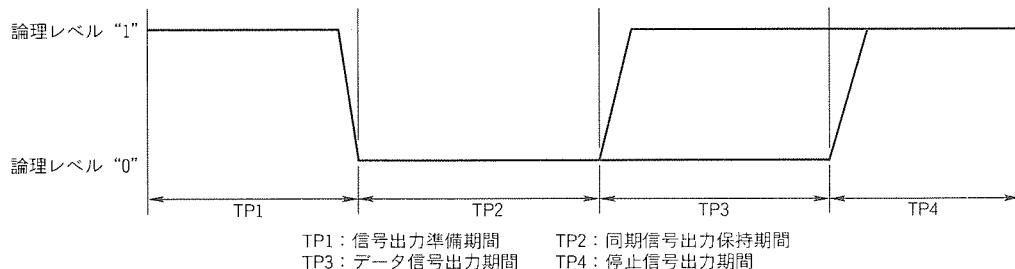

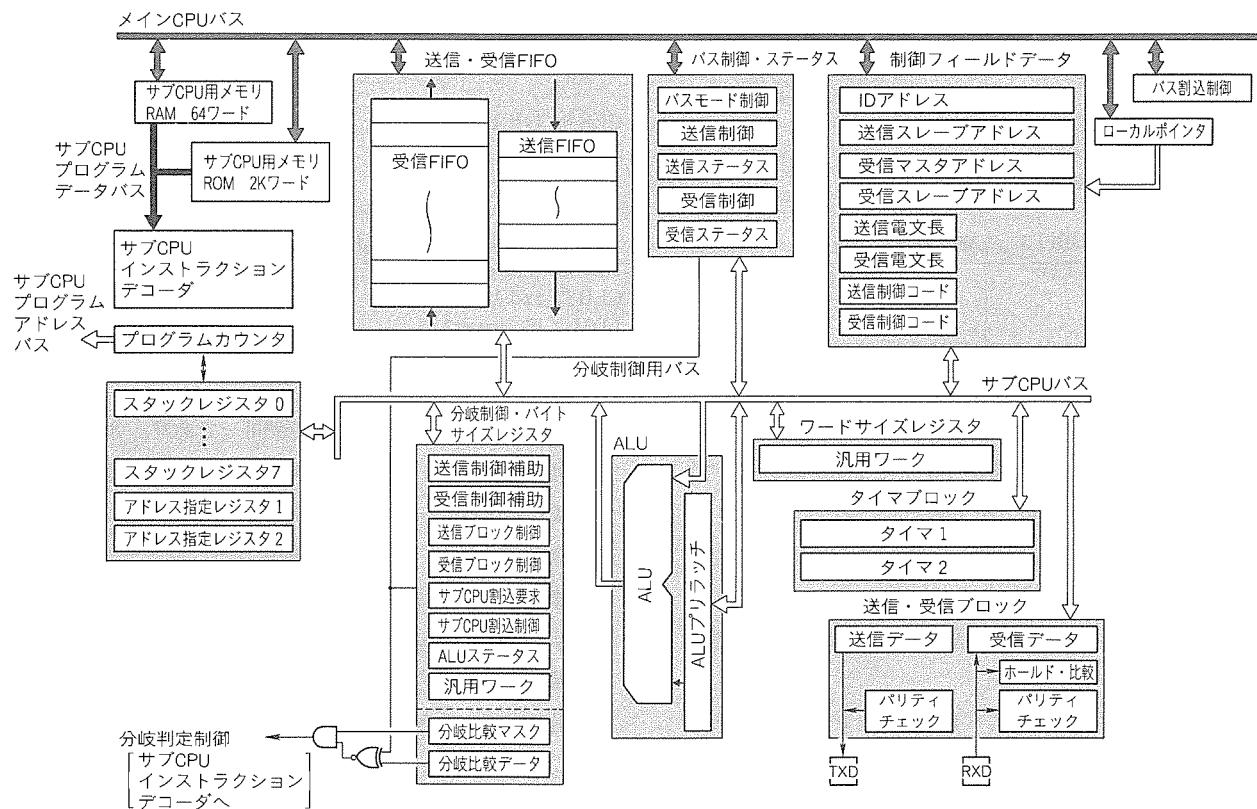

小規模な装置 - 装置間のデータリンク層通信プロトコルコントローラを内蔵したマイクロコントローラを開発した。今回開発したデータリンク層通信プロトコルは、半二重非同期マルチマスター方式、約 4~30 kbps の伝送速度で、優先制御は CSMA/CD 方式である。プロトコルコントローラ部は新たに開発した専用のオンチップサブ MCU を用いて、ファームウェアで実現している。J1850 を始めとする通信プロトコルにファームウェアの変更によって容易に対応できる。

### システム提案型マイコン応用技術

樋口敬三・山田眞裕・杉本正樹

三菱電機技報 Vol.68・No.3・p.39~44 (1994)

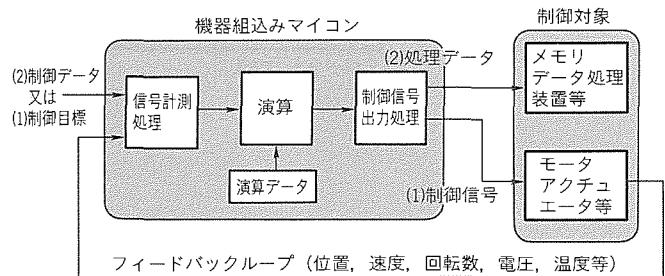

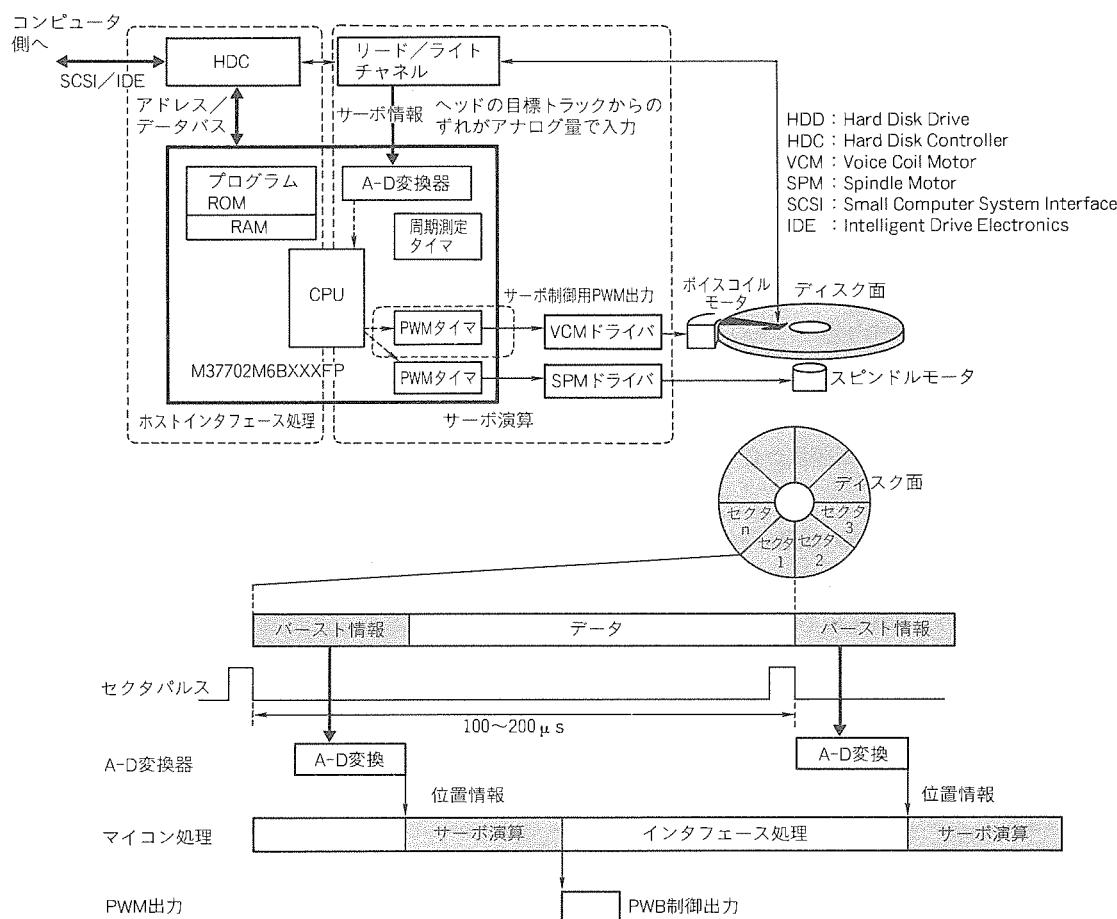

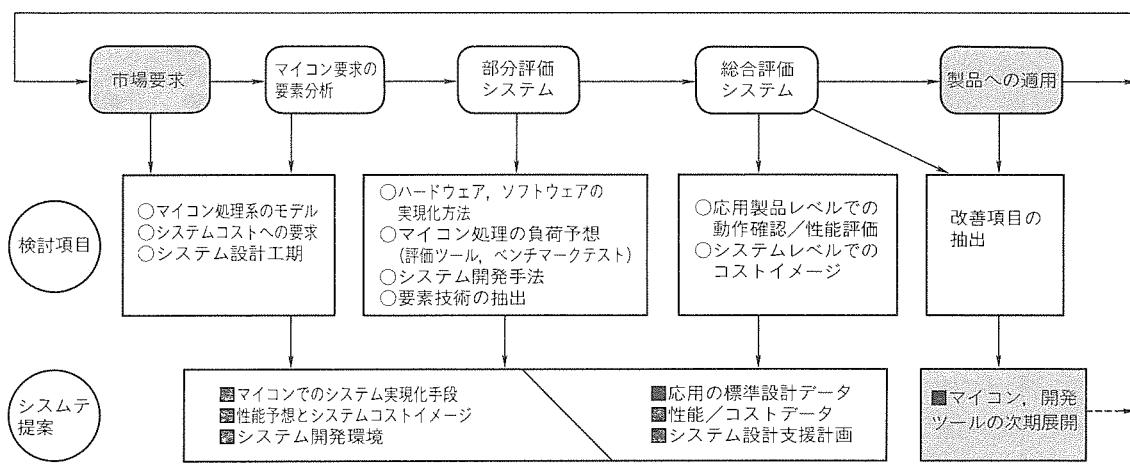

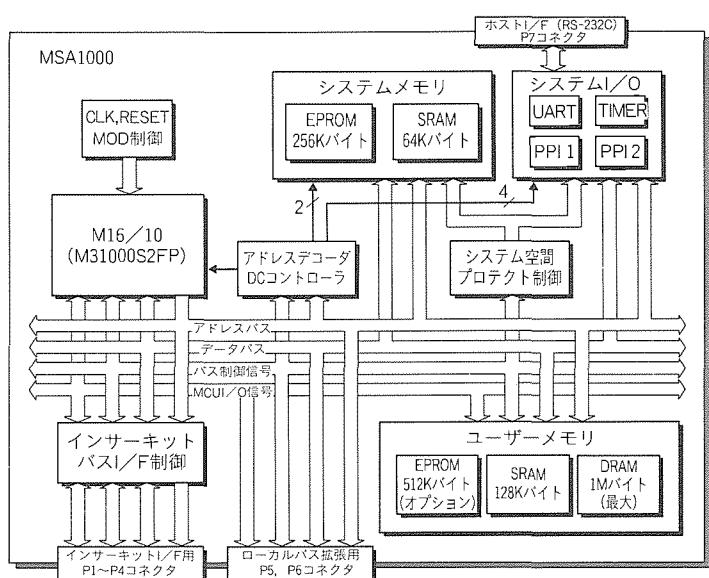

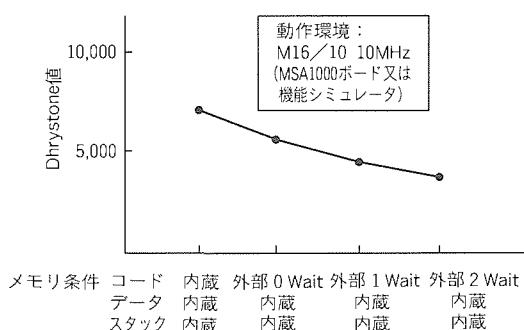

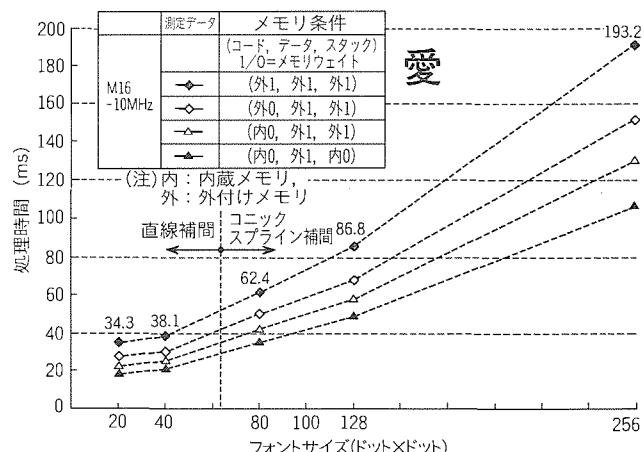

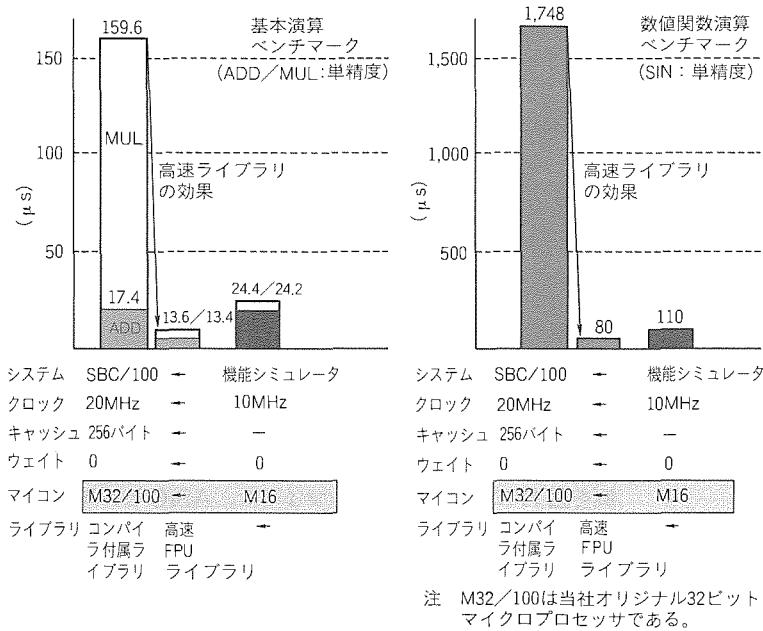

マイクロコンピュータ(マイコン)が用いられる機器組込み応用では、マイコンの特長を最終製品においてコスト、性能、機能面でどのように差別化できるかを事前評価することは難しい。当社ではマイコンを使用した応用製品での適合性評価を提供するとともに、最終応用製品にはほぼ等価な評価用システム(通称デモセット)を開発し、システム提案活動を実施してきた。その応用事例を論じる。

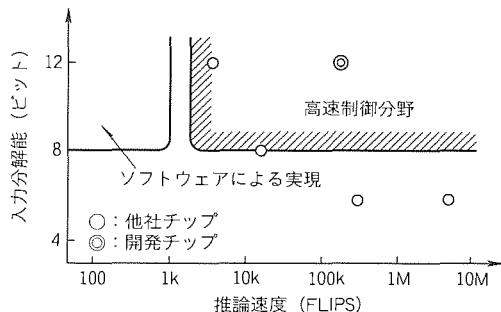

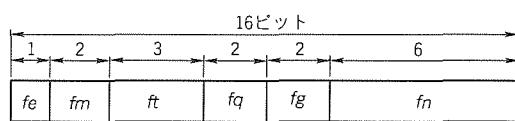

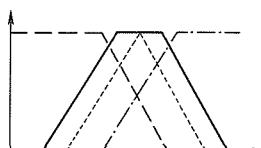

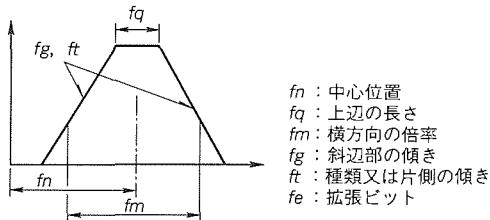

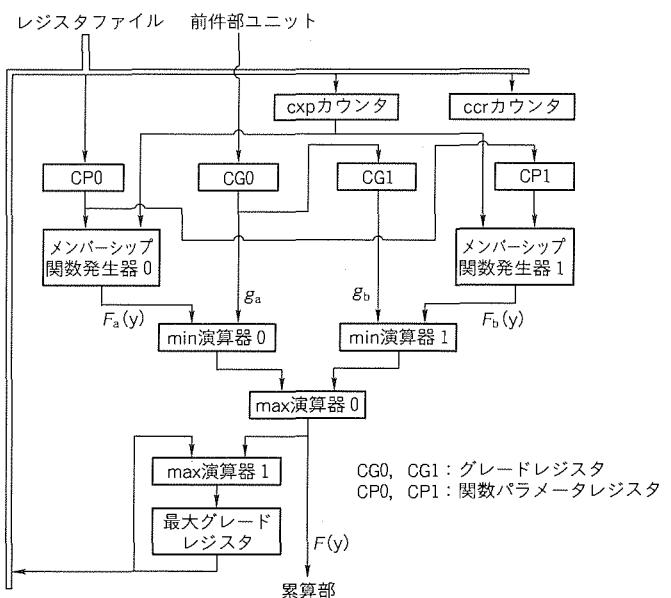

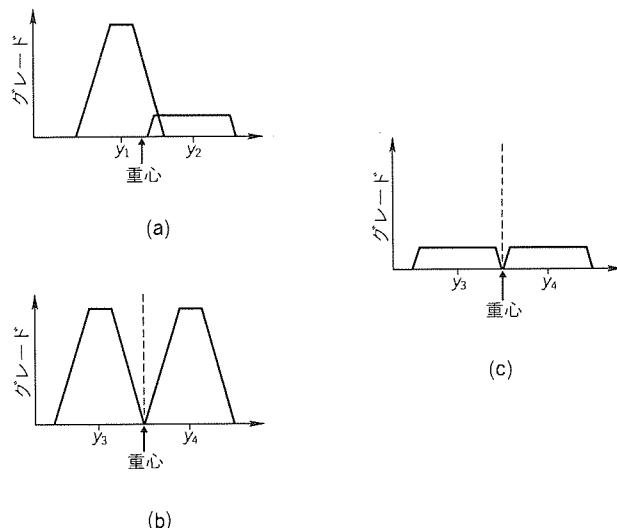

### 12 ビット 100k FLIPS ファジー推論プロセッサ

下邨研一・新田泰彦・坂下徳美・中村和夫・徳田 健

三菱電機技報 Vol.68・No.3・p.45~48 (1994)

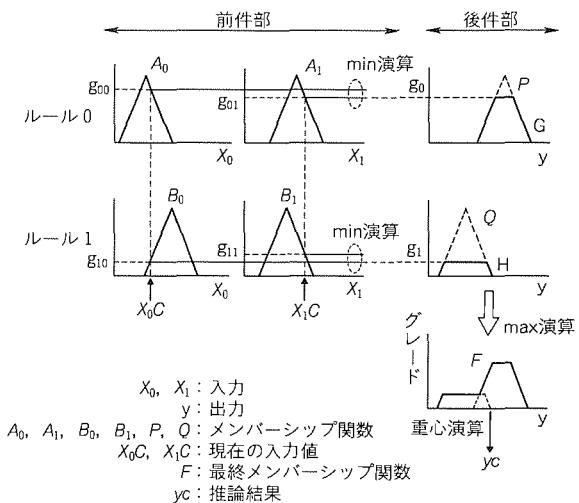

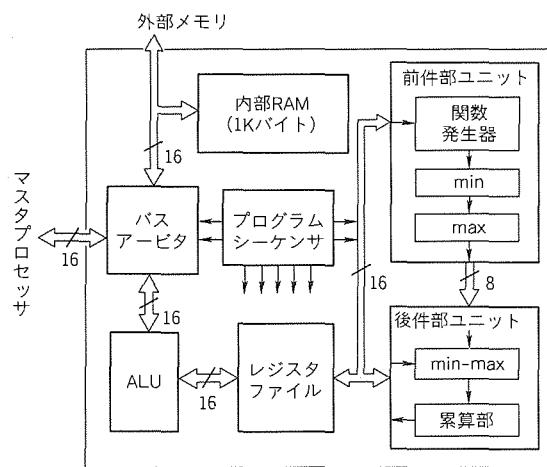

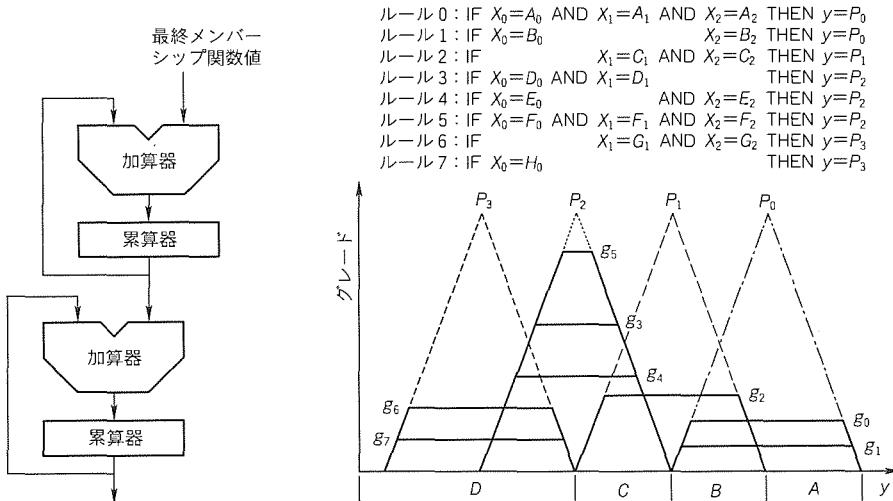

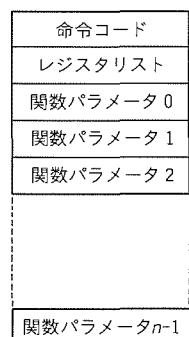

自動車エンジン制御等の高速制御分野への適用が可能な 12 ビット 100k FLIPS (Fuzzy Logical Inference Per Second) のファジー推論プロセッサを開発した。推論速度向上のために、前件部処理と後件部処理のパイプライン化、add/divide アルゴリズムの改良を行った。さらに、ルール命令や専用のメンバーシップ関数発生器を設け処理を高速化した。このプロセッサは、1 μm CMOS 技術によって 86k 素子が 7.5mm × 6.7mm に集積され、最高 100ns の命令サイクルで動作する。

# Abstracts

Mitsubishi Denki Gihō: Vol.68, No.3, pp.24~28 (1994)

## Large-Capacity Memory Card Using Ultra-Thin Package Technology

by Hidenobu Gochi, Katsunori Ochi & Yasuhiro Teraoka

In an industry first, the corporation has developed ultra-thin 0.5mm-thick tape-carrier packages, including 28- and 32-pin dual tape-carrier packages (DTPs) and 80-pin quad tape-carrier packages (QTPs). A 3.3mm-thick high-reliability 4MB SRAM memory card has been developed using 32 1Mbit SRAM devices packaged in 32-pin DTPs, a 64Kbit EEPROM device packaged in a 28-pin DTP, three peripheral ICs packaged in 80-pin QTPs, and high-density mounting technology.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.29~33 (1994)

## M16 Series: A New-Generation High-Performance 16bit Microcontroller

by Yuichi Nakao, Naoichi Kitakami, Toru Shimizu, Hisaharu Miwa & Shigeo Mizugaki

The corporation has developed the M16 Series, a new-generation 16bit microcontroller based on a 32bit microprocessor with a 16bit external bus and 16bit peripheral circuits. The first-generation M16 microcontrollers, which comprise approximately 370,000 transistors, consist of a 4~5 MIPS microprocessor core coupled with peripheral circuits suited for control of electronic office equipment. The devices were developed using a top-down philosophy. Hardware description language (HDL), used to define the device at the highest level, was combined with handcrafted design and cell-based design in consideration of the characteristics of each submodule in order to satisfy flexibility and small die size.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.34~38 (1994)

## A Microcontroller with a Built-In Data-Link-Level Protocol Control Function

by Yoshiaki Cho, Goro Yamanoi, Yoshinori Hayashi, Tetsu Tashiro & Yukio Fujisawa

A microcontroller with a data-link protocol control function has been developed to enable network communications between compact electronic equipment. A separate on-chip microcontroller uses firmware to implement a half-duplex asynchronous multimaster protocol with a speed of 4~30kbps and applies carrier-sense multiple access with collision detection (CSMA/CD) for priority control. The firmware can be easily modified to adapt the device for J1850 and other communications protocols.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.39~44 (1994)

## Systematic Design of Microcomputer-Based Embedded-Control Systems

by Keizo Higuchi, Kunihiko Yamada & Masaki Sugimoto

In microcomputer-based embedded-control applications, it is difficult to determine the effects of a microprocessor choice on the cost, performance and functionality of the end product. The corporation therefore offers design support services which include (1) evaluating microprocessor suitability for specific applications, (2) supplying demonstration systems nearly equivalent to the final application product, and (3) proposing systems. The article introduces these services.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.45~48 (1994)

## A Fuzzy Inference Processor with 12bit Resolution and 100k FLIPS Performance

by Ken'ichi Shimomura, Yasuhiro Nitta, Narumi Sakashita, Kazuo Nakamura & Takeshi Tokuda

The corporation has developed a high-performance fuzzy inference processor with 12bit resolution capable of 100k fuzzy logical inferences per second (FLIPS) for automotive use and other demanding applications. In order to maximize processing speed, the device features a pipeline architecture with pre- and post-processing, and an improved add/divide algorithm. Speed improvements were also achieved by adding rule instructions and including a dedicated circuit for generating membership functions. The device, which consists of 86,000 transistors, is implemented using 1.0  $\mu$ m CMOS technology with a die size of 7.5  $\times$  6.7mm. The minimum instruction cycle time is 100ns.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.3~6 (1994)

## A Review of Trends in Semiconductor Technology

by Hideo Sakane

The rapidly advancing front of semiconductor technology research has expanded into the applications market. Since entering the 1990s, the semiconductor industry has been shifting from a mass-production oriented market to an increasingly quality-oriented one—with special emphasis on high-performance, compact form factor, low-power consumption, and digital functionality. Making this shift requires a synthesis of application needs with semiconductor seed technologies. The article surveys application trends in the market and various approaches toward providing suitable semiconductor devices.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.7~10 (1994)

## A 64Mbit DRAM

by Yoshikazu Morooka, Hiroshi Miyamoto, Kiyohiro Furutani, Tatsuo Okamoto & Kazuyuki Sugawara

A 64Mbit CMOS DRAM has been developed applying a CMOS process with 0.35  $\mu$ m design rule, 2-layer polyimide, 3-layer polysilicon and 2-layer metalization. The same chip can be configured for 1, 4, 8 or 16bit word lengths with addressing by high-speed page, nibble, or static column modes. The 218mm<sup>2</sup> die is housed in 500-mil SOJ or TSOP packages. The power supply is 3.3V, with a low-voltage transistor-transistor logic (LVTTL) interface. The random access strobe (RAS) access time is 50ns, and the device dissipates 432mW when operating at 120mA.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.11~14 (1994)

## A 16Mbit Flash Memory with Block-Erasure Capability

by Takeshi Nakayama, Masaaki Mihara, Yoshikazu Miyawaki, Makoto Ooi & Hajime Arai

A 16Mbit flash-memory device with a 64kB block-erase function has been developed. It is capable of operating on dual 3.3V and 12V power supplies. Implemented using 0.5  $\mu$ m technology, it has a cell size of 1.7  $\times$  1.9  $\mu$ m and chip size of 9.3  $\times$  11.5mm. The access time is 100ns operating on the 3.3V supply voltage. The device also includes an erase suspend/resume function that allows the automatic erase function to be temporarily interrupted, the memory contents read out, and the erasure resumed.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.15~18 (1994)

## A Third-Generation 4Mbit DRAM with High-Speed Quad Column Address Strobes

by Takahiko Fukui & Tomoharu Mamei

A third-generation 4Mbit DRAM has been designed utilizing a minimum transistor length of 0.65  $\mu$ m and a new circuit. This new device has high access speed and low power dissipation. It has a quad column access strobe (CAS) function that enables arbitrary high-speed writing or reading by each CAS. It also has a self-refresh function that is suitable for battery back-up application.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.19~23 (1994)

## A High-Speed 1Mbit CMOS SRAM

by Yoji Kashihara, Sadanori Sakaguchi, Yoshiaki Akiyama, Yoshiaki Tahara & Fuyumi Minami

A high-speed 1Mbit CMOS static RAM has been developed with a 15ns access time and 1, 4 and 8bit word lengths. The device was implemented using a 0.6  $\mu$ m CMOS process, multilayer metalization, and high-performance, high-reliability transistors. The circuit achieves a 15ns access speed through use of a distributed word-line architecture suited for multilayer metalization and a new internal clock-synchronization circuit.

## アブストラクト

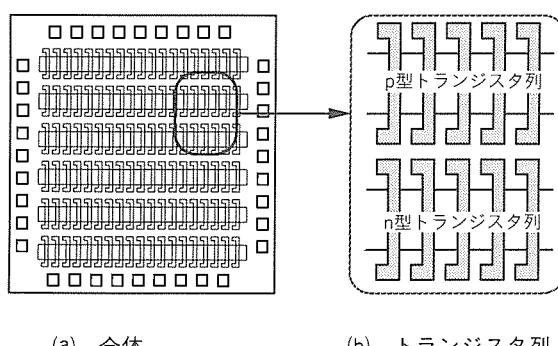

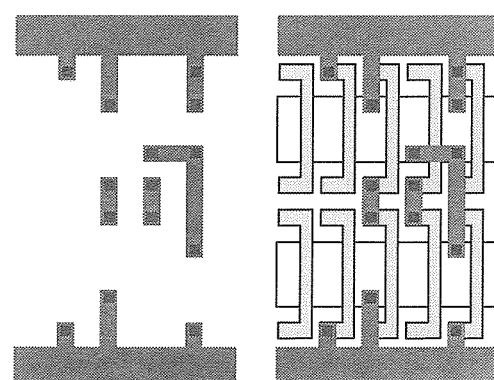

### 0.5μm CMOS セミカスタム IC

真田邦彦・青木一夫・前野秀史・松本 尚・笹田真喜子

三菱電機技報 Vol.68・No.3・p.49～53 (1994)

最先端のシステムオンシリコン設計技術の基盤となる 0.5μm CMOS ゲートアレーに引き続き、今回新しくエンベッデッドタイプの高密度モジュールジェネレータ、PLL、GTL 回路を開発した。その結果、エンベッデッド セルアレー及びセルベースICを含めた 0.5μm セミカスタム IC トータルの開発体制が整い、高機能なシステムを 1 チップで設計することが可能となった。

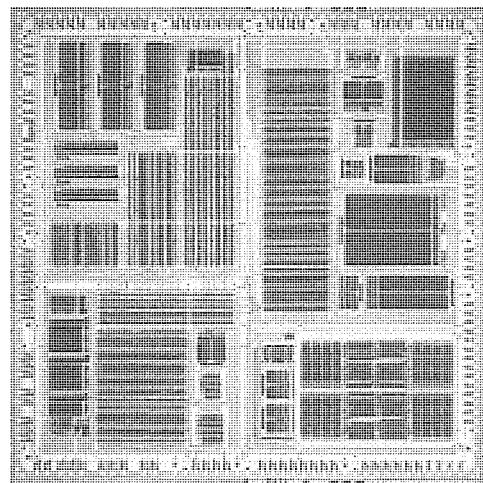

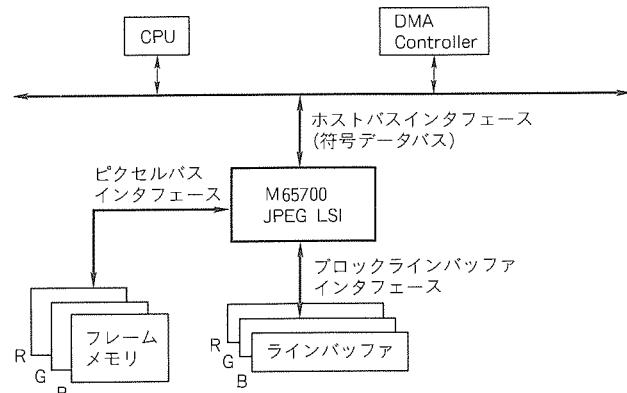

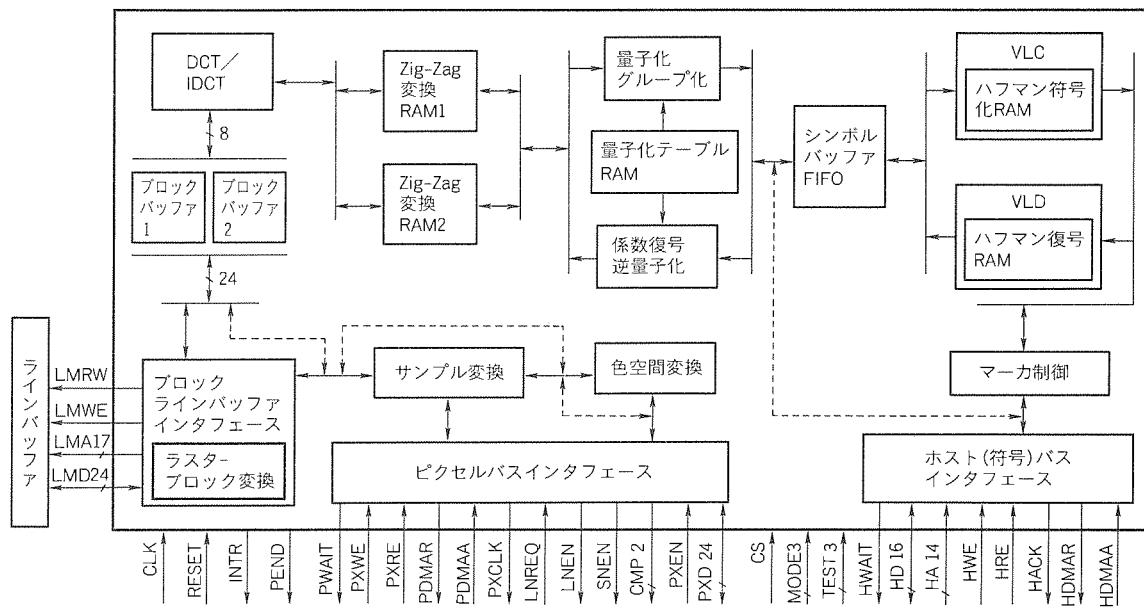

### 国際標準 JPEG 準拠のカラー画像圧縮・伸長 LSI

小川文伸・井田静男・今中良史・杉野博之・寺根秀幸

三菱電機技報 Vol.68・No.3・p.54～58 (1994)

国際標準 JPEG (Joint Photographic Experts Group) の基本システム準拠のカラー画像圧縮・伸長 LSI を開発した。この LSI の最大の特長は、カラー画像 (RGB, 640×480画素) を 30 フレーム/秒で符号化/復号できる高速性である。また、各種フォーマット変換や簡易符号量制御など豊富な周辺機能を 1 チップ内に収めた。この LSI は高速性により、静止画像はもちろんのこと、ディジタルビデオ機器やパソコン上での動画ファイルリングなど動画像への応用も可能となる。

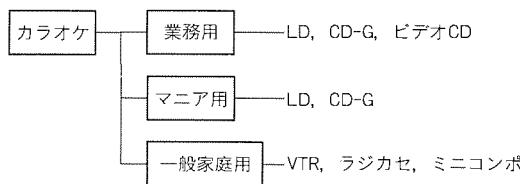

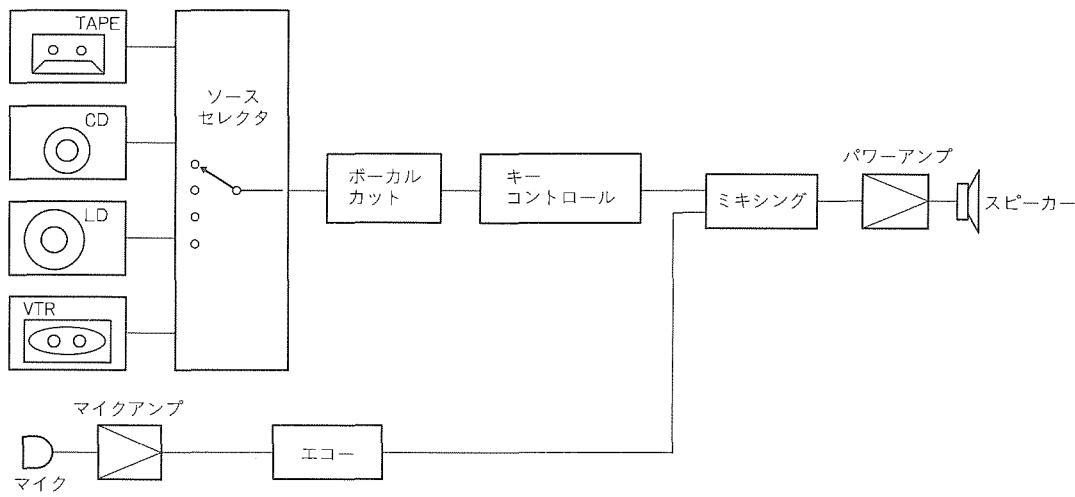

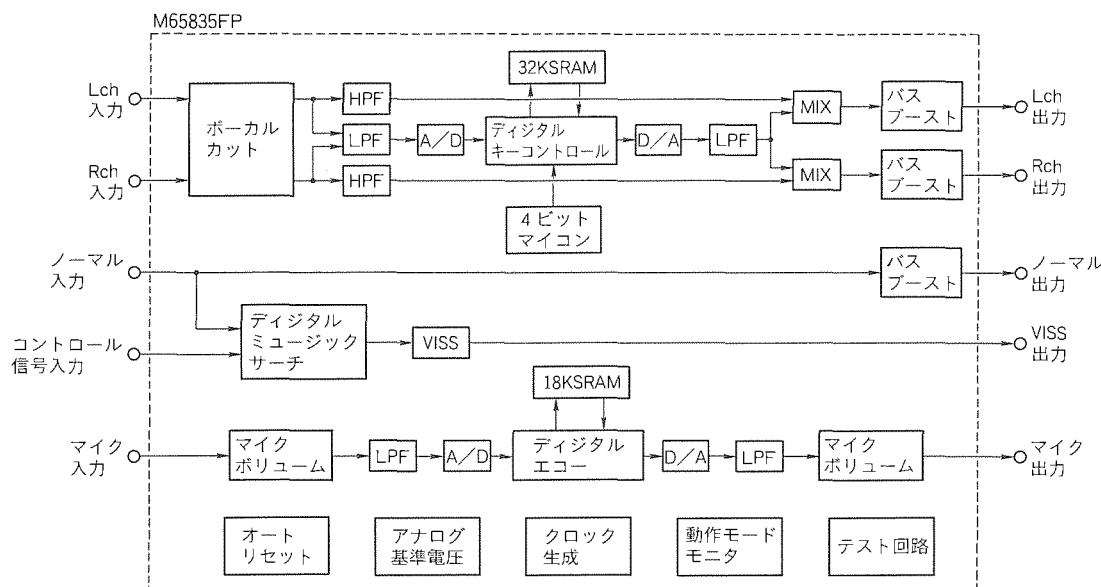

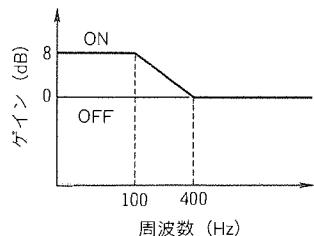

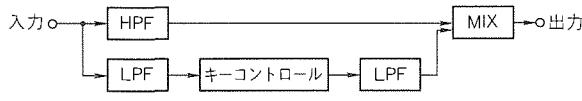

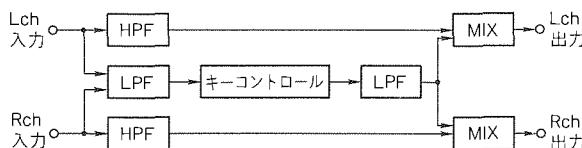

### VTR 用ワンチップカラオケプロセッサ LSI

安達靖史・山田友右

三菱電機技報 Vol.68・No.3・p.59～62 (1994)

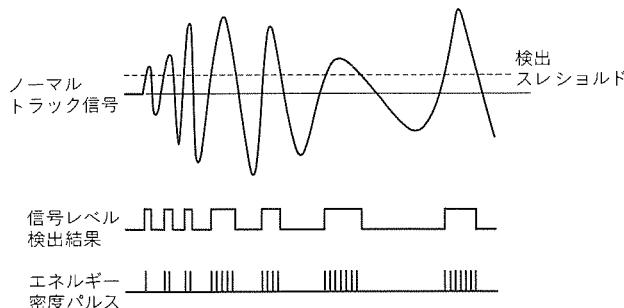

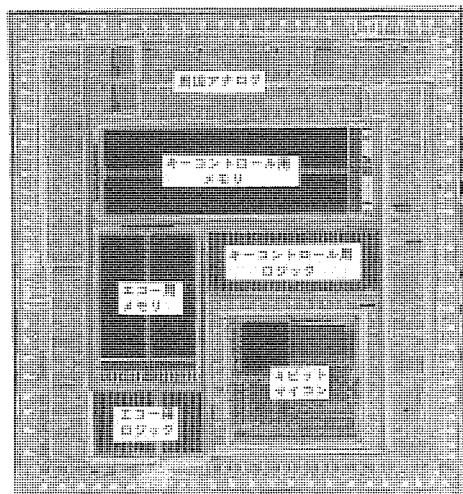

当社では、従来からディジタルエコーやディジタルキコントロール等のカラオケ専用 LSI を多数製品化し、市場に広く親しまれている。今回、シリーズ中最も高機能なワンチップカラオケプロセッサ LSI M65835 FP を開発した。この IC は、主にカラオケ機能付き VTR 用として、ボーカルカット、キーコントロール、エコー等カラオケに必要なすべての機能とテープの頭出しが容易に検出できるディジタルサーチシステムを搭載し、最新の 0.8μm CMOS プロセスで実現した。

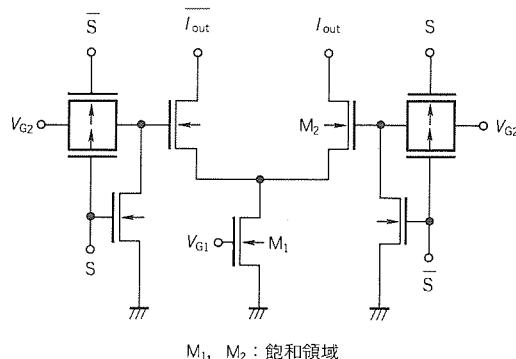

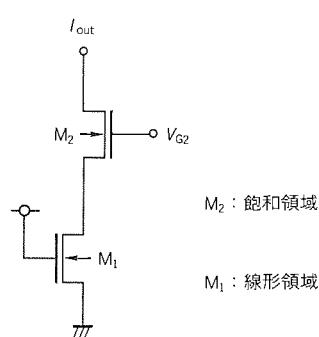

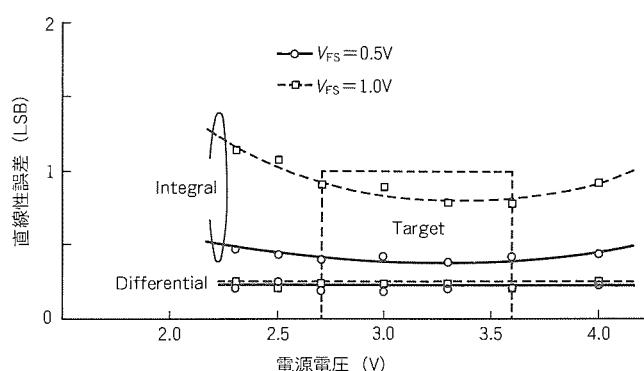

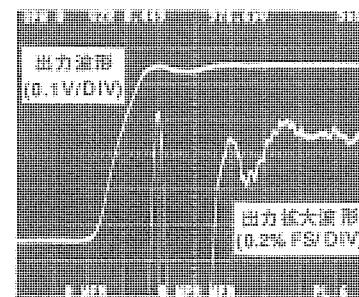

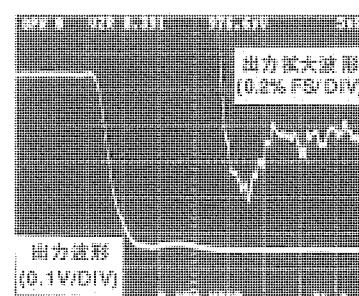

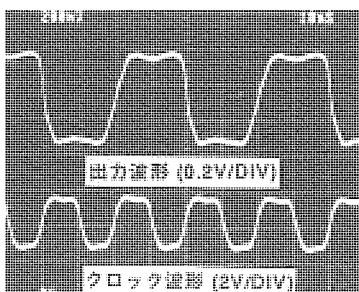

### 3 V 動作10ビット50M サンプル/秒 CMOS D/A コンバータ

中村泰之・三木隆博・西川毅一・岡田圭介

三菱電機技報 Vol.68・No.3・p.63～67 (1994)

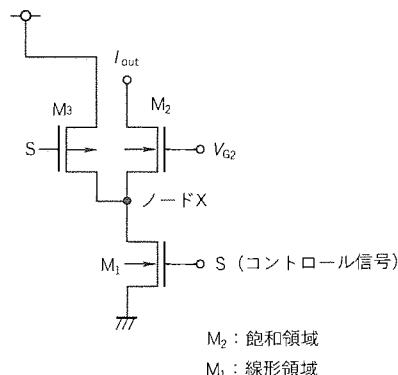

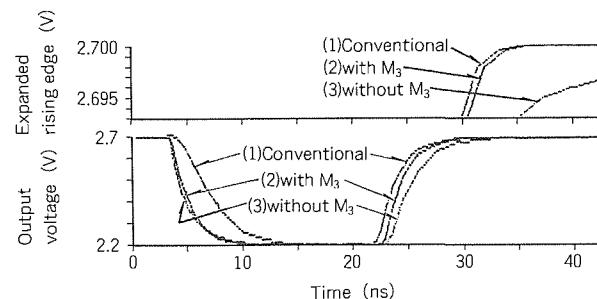

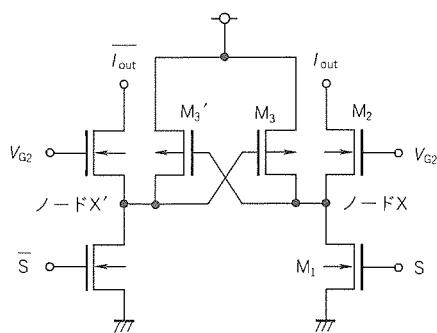

3 V 電源 (2.7V 以上) で動作する分解能 10 ビット、最大変換速度 50M サンプル/秒の CMOS D/A コンバータを世界で初めて試作した。

当社独自のバイアス方法及び駆動方法を用いた電流源回路を新たに開発することで上記性能を達成した。パッドを除いた有効面積は 1.41mm × 1.28mm と小さく、システム VLSI へのオンチップ化に適している。消費電力は、最大 50mW (フルスケール出力電流が 10mA のとき) である。

### トレンチ MOS ゲート構造の

#### 600V 絶縁ゲートバイポーラトランジスタ

原田真名・湊 忠玄・高橋英樹・西原秀典・井上敬二・高田育紀

三菱電機技報 Vol.68・No.3・p.68～72 (1994)

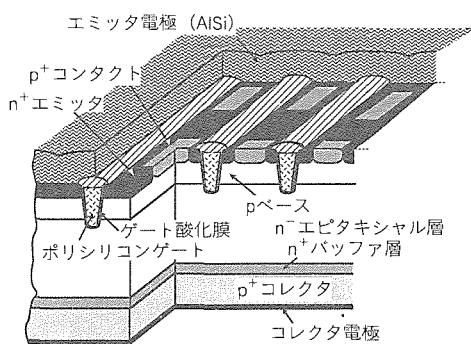

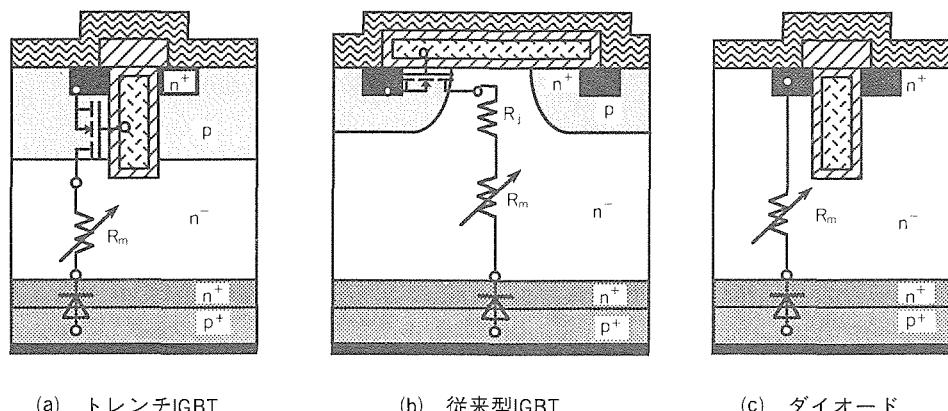

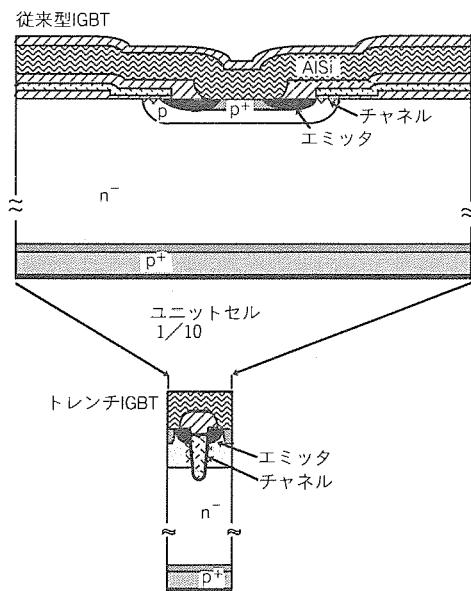

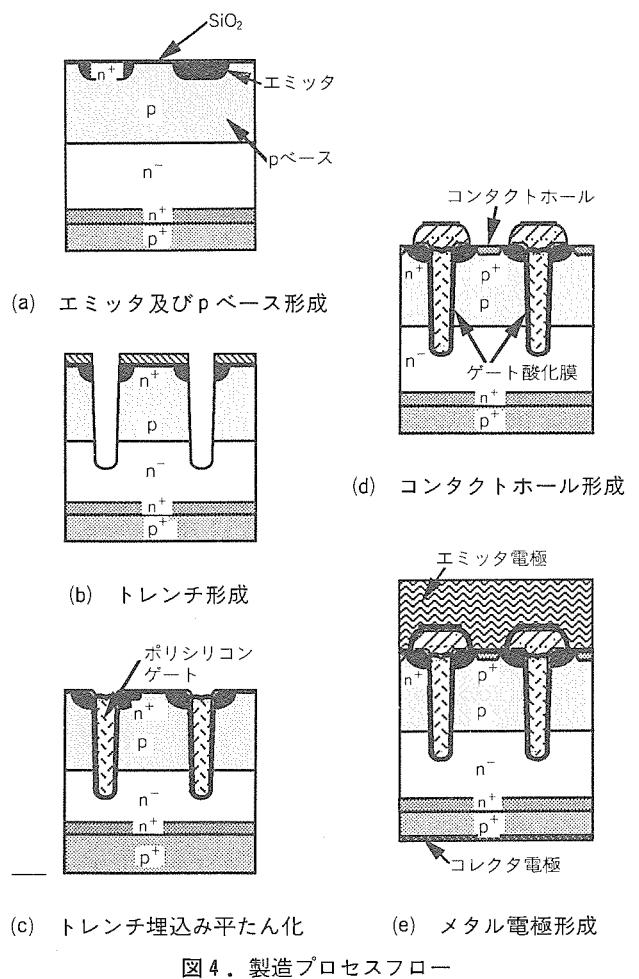

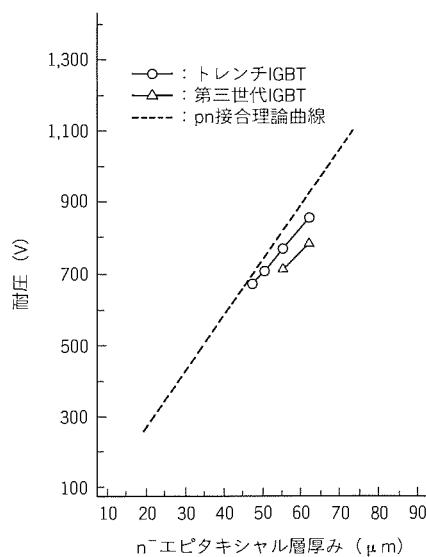

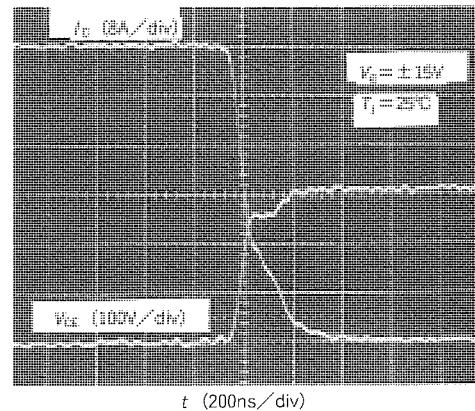

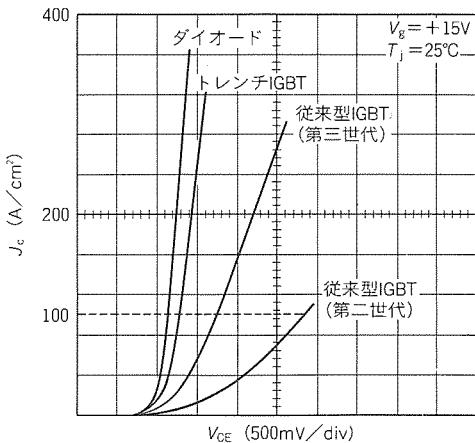

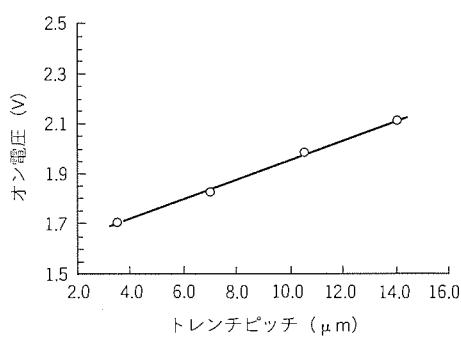

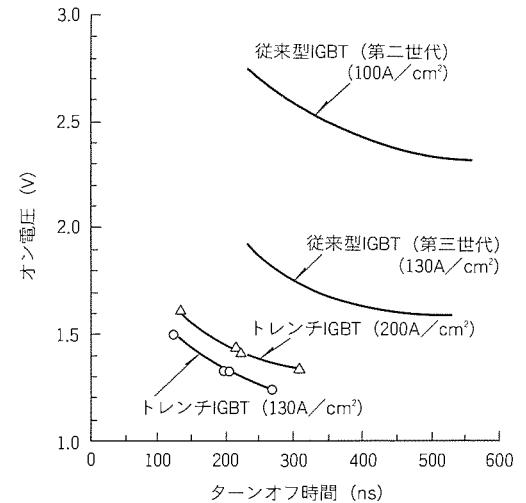

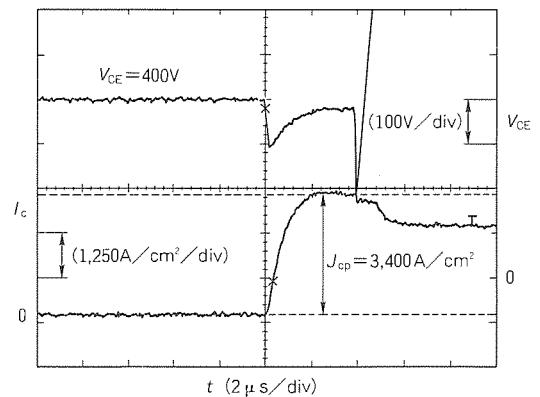

トレンチ MOS ゲート構造の 600V, 50A 絶縁ゲートバイポーラトランジスタ (トレンチ IGBT) を開発した。トレンチ MOS ゲート構造の採用により、ユニットセル寸法を従来構造 IGBT の約 1/10 に縮小することができ、200A/cm<sup>2</sup> の高電流密度で 1.4V ( $t_f = 200$  ns) と極めて低いオン電圧を得た。トレンチ IGBT は、素子耐圧、破壊耐量にも優れており、IGBT の理想形をほぼ実現しているデバイスであることを確認した。

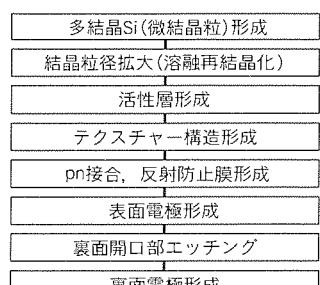

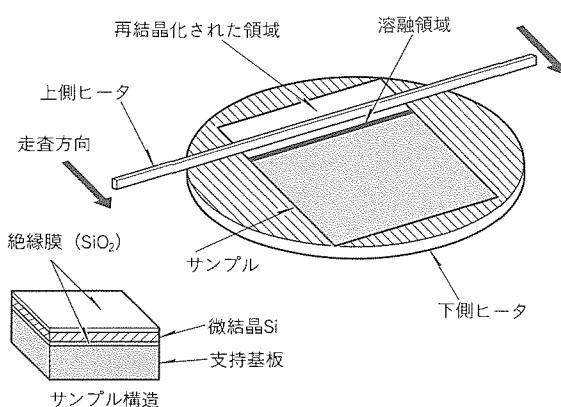

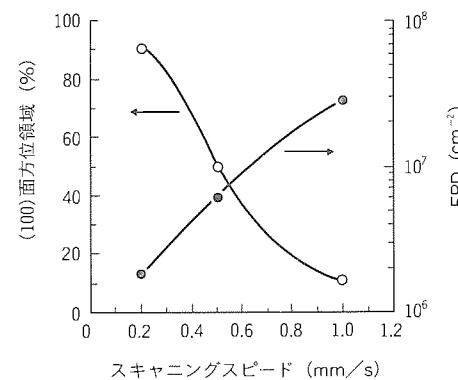

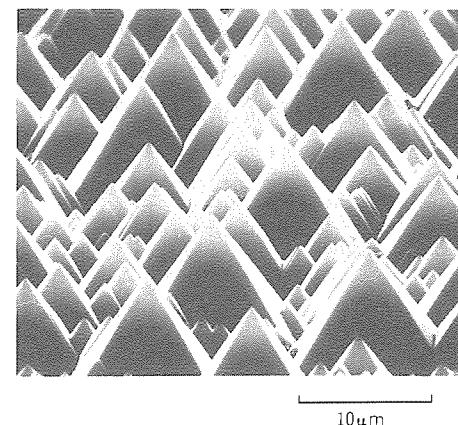

### 溶融再結晶化法を用いた

新型高効率薄膜多結晶シリコン太陽電池

森川浩昭・有本 智・石原 隆・隈部久雄・室谷利夫

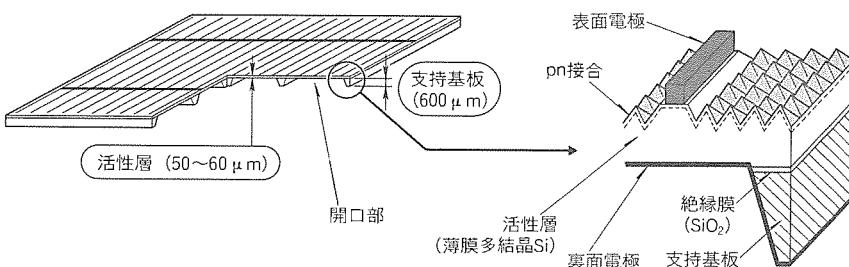

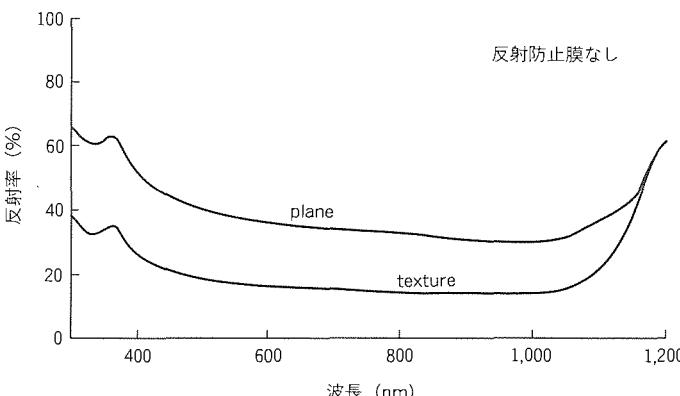

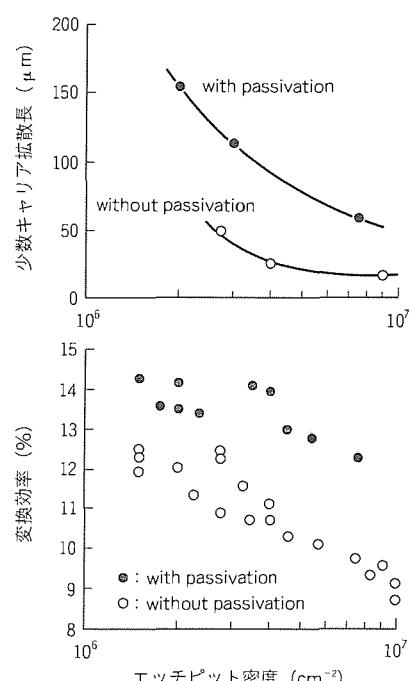

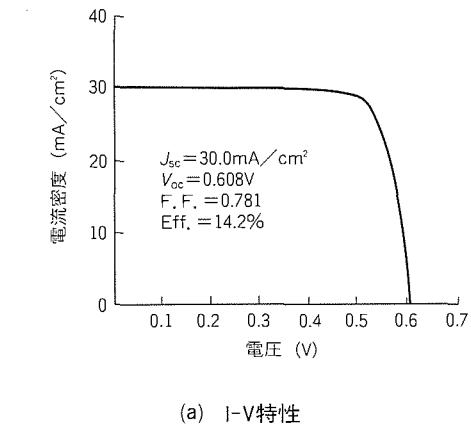

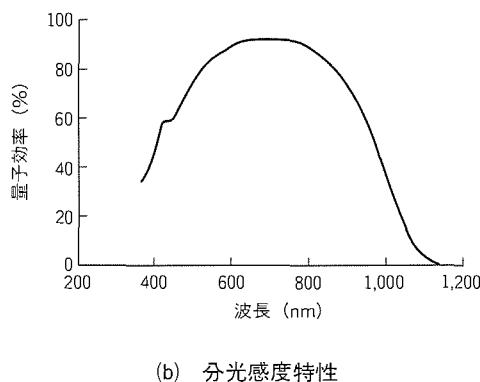

三菱電機技報 Vol.68・No.3・p.73～76 (1994)

溶融再結晶化法による絶縁膜上の薄膜多結晶シリコンの高品質化技術、活性層内に有効に光を閉じ込めるための独自の構造及びプロセスを開発し、薄膜多結晶シリコン太陽電池としては世界最高の変換効率 (14.2 %, 10cm 角) を実現するとともに、電力用太陽電池の実用化上最も重要な材料コストを従来の 1/10 に低減している。

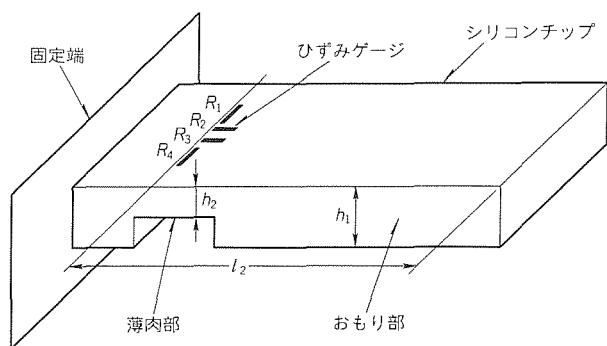

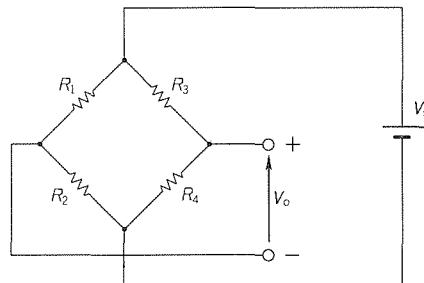

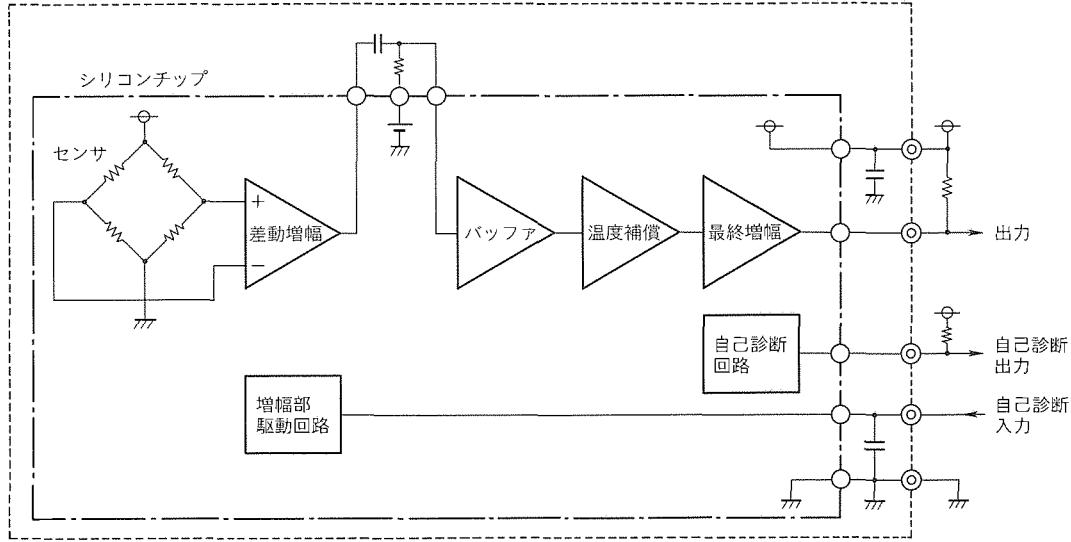

### 小型・高機能エアバッグ用半導体加速度センサ

荒木 達・山本雅裕・瀬々倉 孝

三菱電機技報 Vol.68・No.3・p.77～81 (1994)

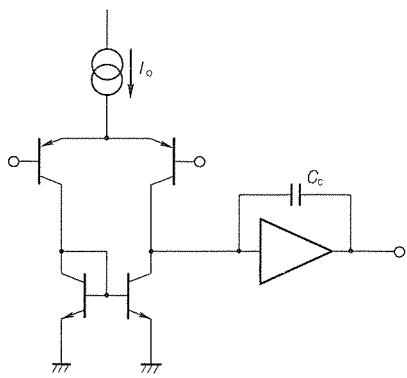

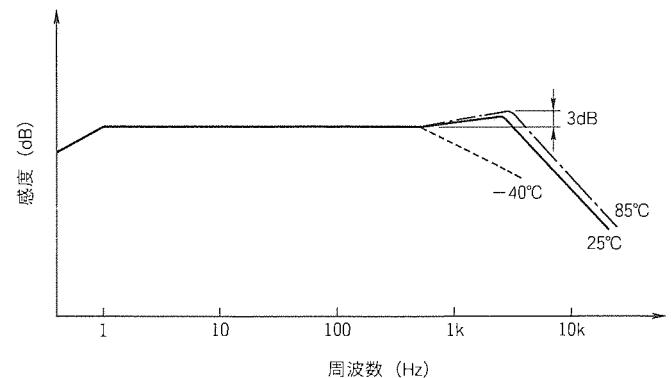

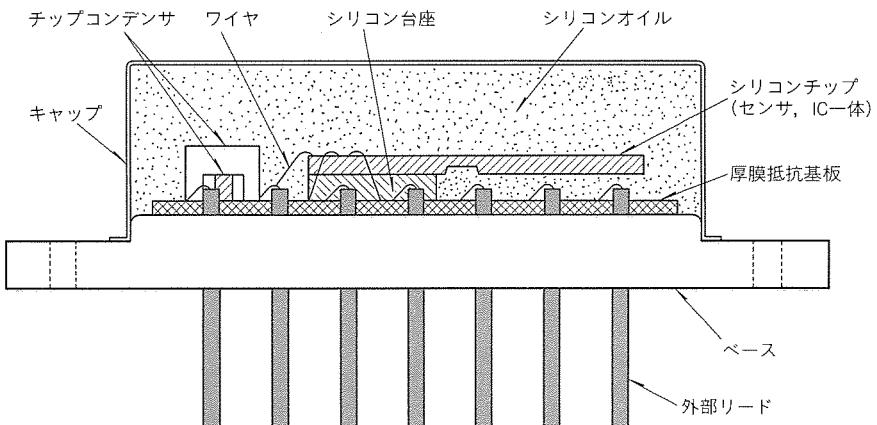

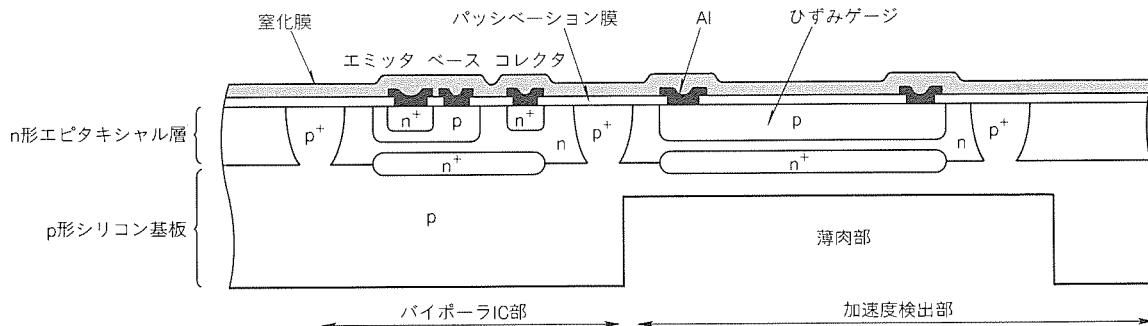

今回、開発したエアバッグ用半導体加速度センサは、加速度によって生じるシリコンチップ上の機械的ひずみをピエゾ抵抗効果 (Piezo-resistive Effect) によって電圧に変換するセンサ部と、增幅回路や自己診断回路 (Diagnosis Circuit) などの信号処理回路を当社独自の IC 化センサ技術によってワンチップに集積化したため、従来の圧電セラミック型の加速度センサに比べ、約 1/2 の価格と 1/3 のサイズとを実現した。

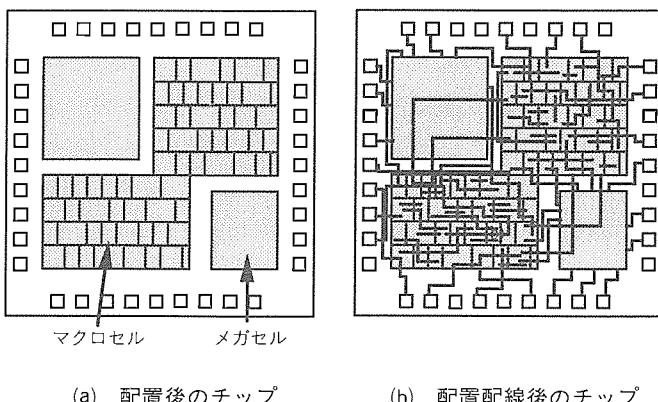

### CMOS ゲートアレー用自動レイアウト技術

中尾博臣・高橋一浩・定兼利行・奥田亮輔・寺井正幸・佐藤興二

三菱電機技報 Vol.68・No.3・p.82～85 (1994)

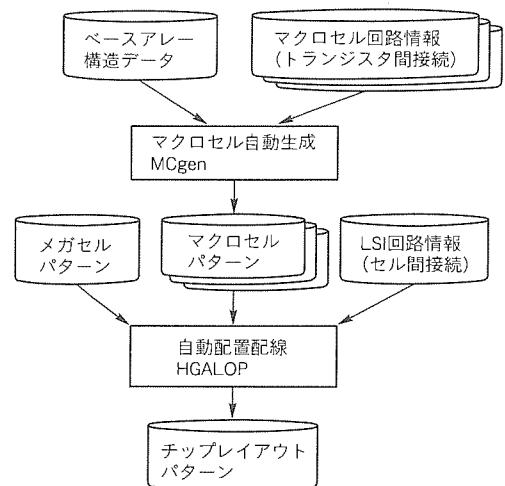

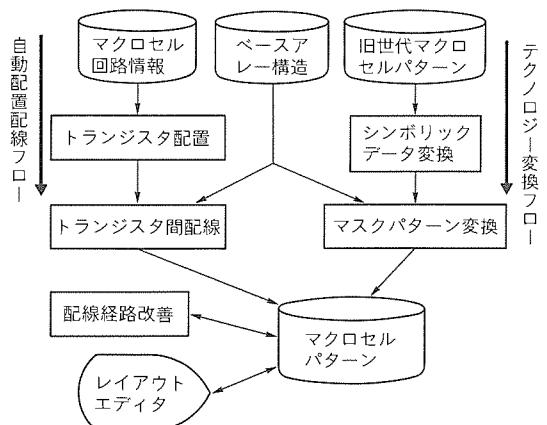

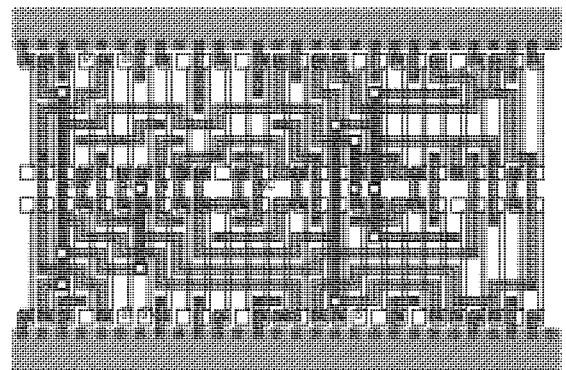

CMOS SOG (Sea of Gate) ゲートアレー自動レイアウトのための CAD ソフトウェア、自動配置配線 HGALOP とマクロセル自動生成 MCgen を開発した。HGALOP は、SOG ゲートアレーのレイアウト構造を有効利用したアルゴリズムにより、汎用的な市販ツールより平均 20 倍高速であり、MCgen は独自の配線手法により、高密度なマクロセルのレイアウトパターンを生成する。共に、0.5μm 以上のデバイスに適用中である。

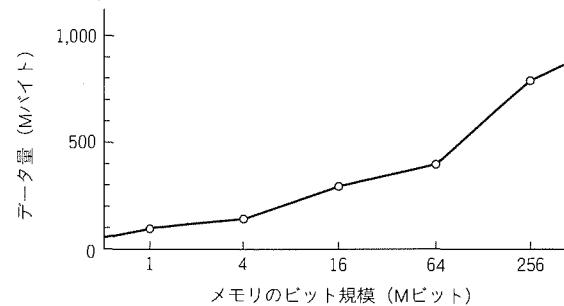

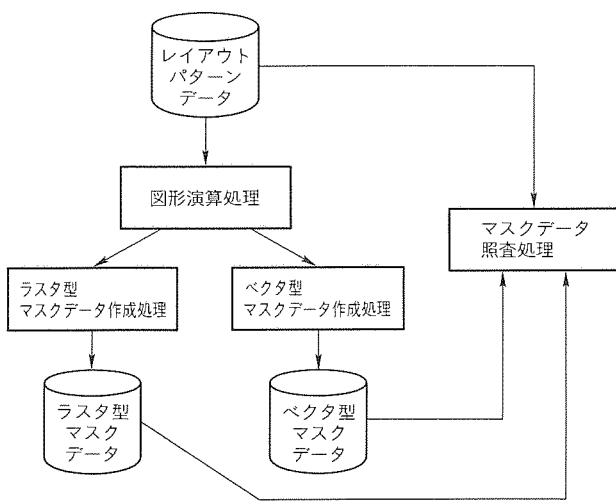

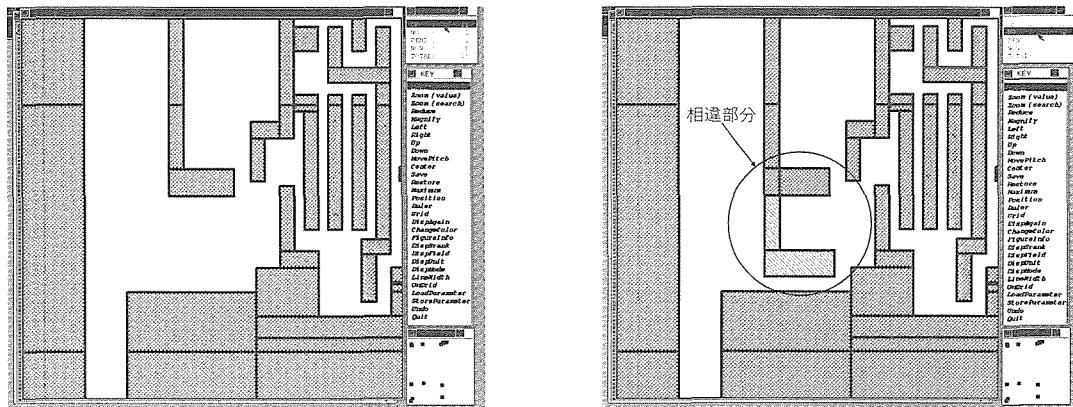

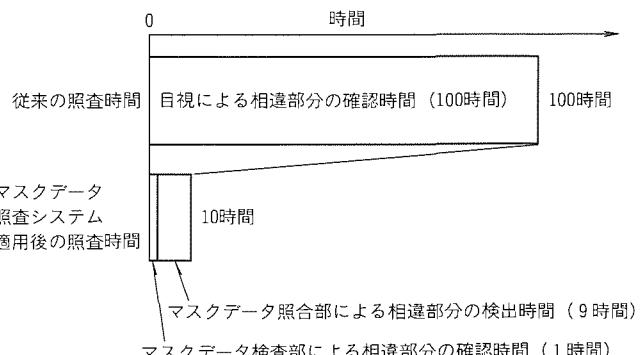

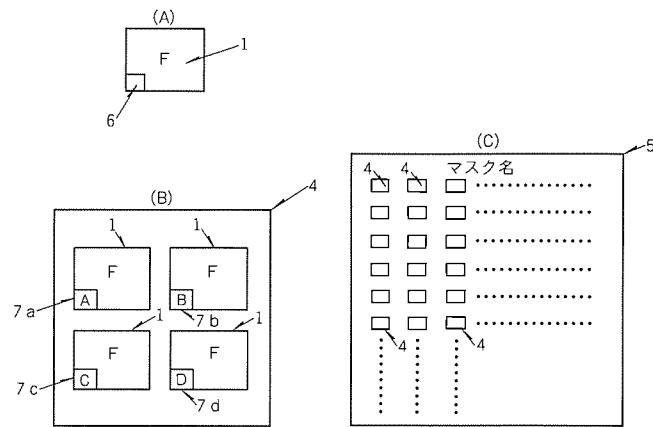

### VLSI マスクデータ照査システム

菅野 誠・濱本末雄・田中健一・宗像恒任・森泉幸一

三菱電機技報 Vol.68・No.3・p.86～89 (1994)

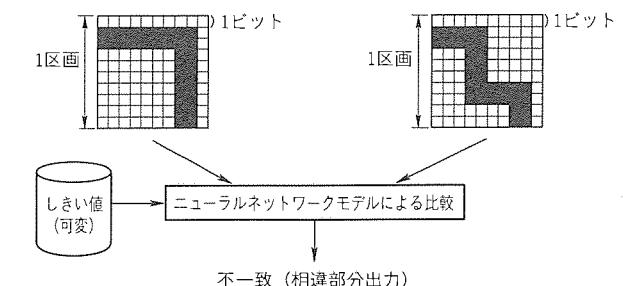

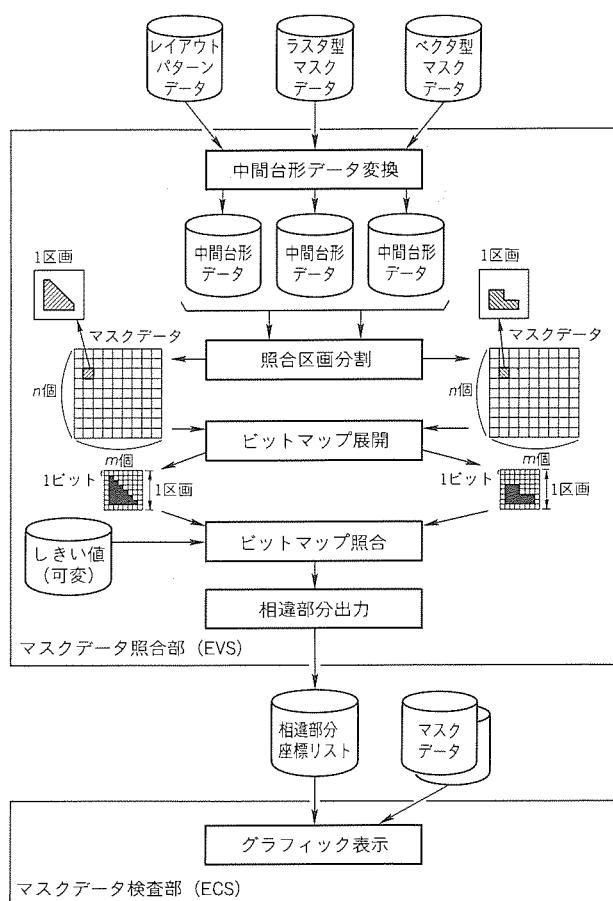

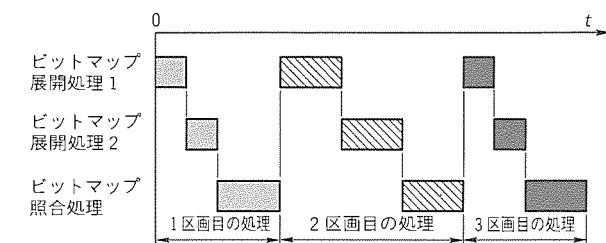

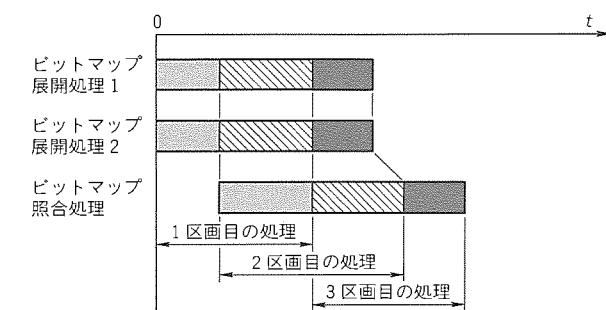

複数の VLSI マスクデータを相互比較し、パターン相違部分を高速に自動検出するマスクデータ照査システムを開発した。このシステムは、ニューラルネットワークモデルを用いて、丸め誤差等パターンの微妙なズレによる相違部分の検出、不検出を自動的に判断できるものであり、従来のグラフィック画面での目視照査に比べて、1/10 以下の時間で照査可能となった。なお、このシステムは、既に 16MDRAM (16 メガビット DRAM) 等、製品へ適用した。

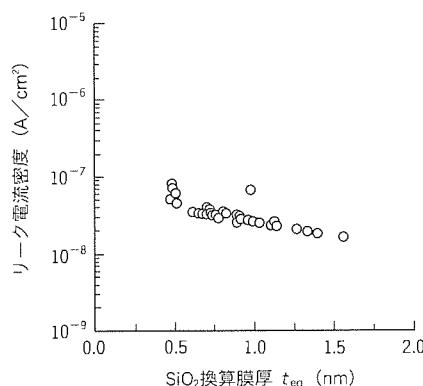

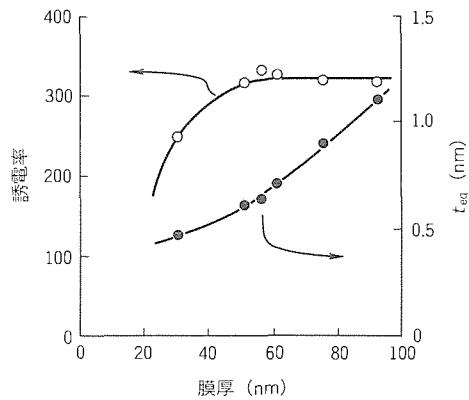

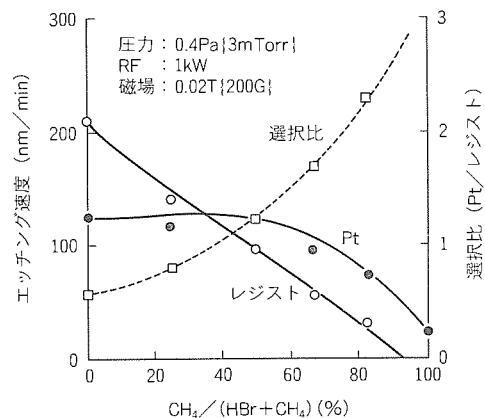

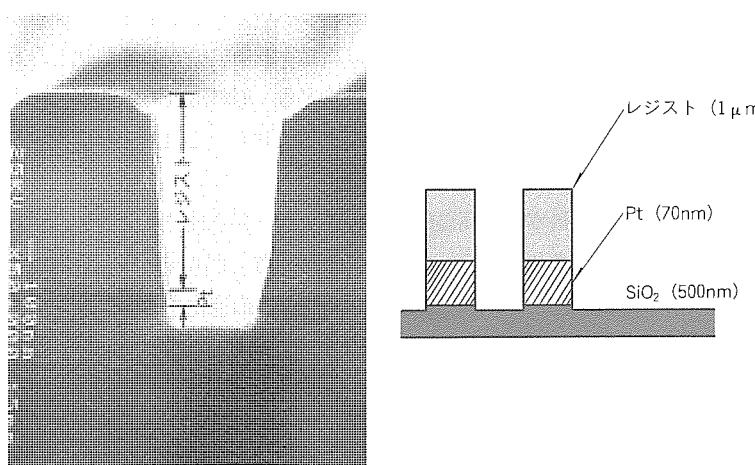

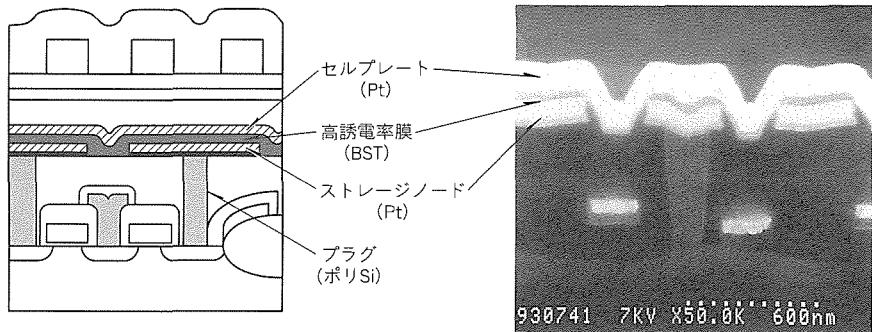

### 高誘電率薄膜技術

佐藤一直・三上 登・川原孝昭・楠見嘉宏・伊藤博巳

三菱電機技報 Vol.68・No.3・p.90～93 (1994)

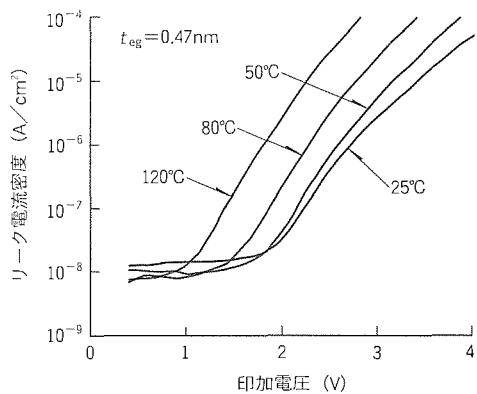

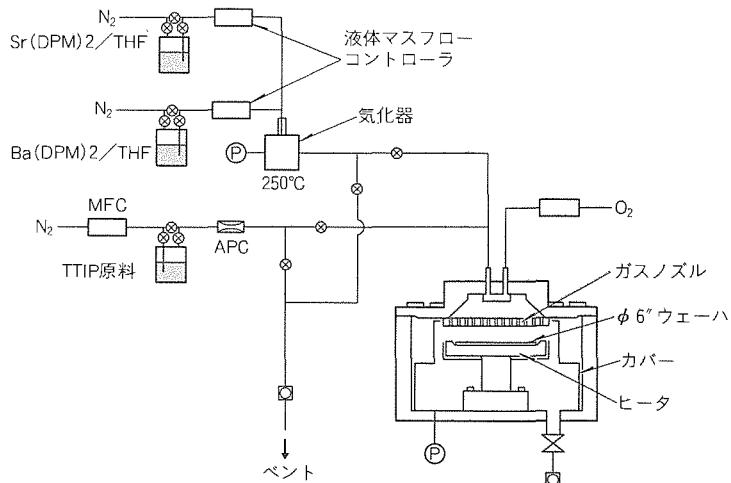

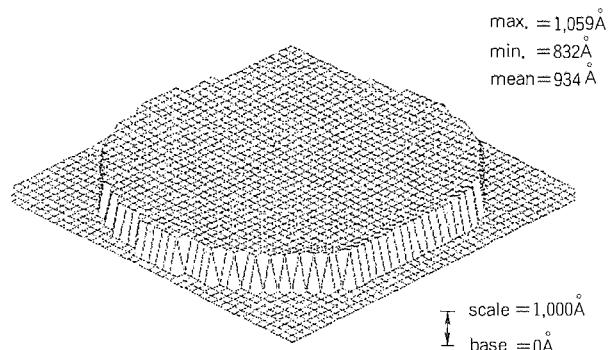

高誘電率を持つ (Ba, Sr) TiO<sub>3</sub> 膜の DRAM への適用性を検討した。スパッタ成膜法、CVD 成膜法及びエッチング加工法を検討し、各プロセスで 256MDRAM に適用可能な基本特性を達成した。実際に、高誘電率薄膜を適用した 256MDRAM 構造を試作し、シンプルなセル構造を持ち、製造コストを低減できる 256MDRAM の実現性を示した。

# Abstracts

Mitsubishi Denki Gihō: Vol.68, No.3, pp.73~76 (1994)

## Zone-Melting Recrystallization Technique Developed for Production of A New Highly Efficient Thin-Film Polycrystalline Silicon Solar Battery

by Hiroaki Morikawa, Satoshi Arimoto, Takashi Ishihara, Hisao Kumabe & Toshio Murotani

The corporation has demonstrated a thin-film polycrystalline silicon solar cell with the world's highest conversion efficiency: 14.2% over a 10 × 10cm square. A zone-melting recrystallization technique for forming thin polycrystalline silicon layer over insulator and a novel structure and process have been developed. The cost of materials for the device is one-tenth that of previous solar cells, providing strong motivation for commercial development.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.77~81 (1994)

## Compact, Highly Functional Semiconductor Acceleration Sensor for Airbag Systems

by Toru Araki, Masahiro Yamamoto & Takashi Ssekura

The corporation has integrated a semiconductor accelerometer for airbag applications on a single chip with comprised of a piezoresistive element that converts strain to voltage, an amplifier and diagnostic circuits. This device costs half that of previous ceramic devices and occupies one-third the volume.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.82~85 (1994)

## Automatic Layout Technology for CMOS Gate Arrays

by Hiroomi Nakao, Kazuhiro Takahashi, Toshiyuki Sadakane, Ryosuke Okuda, Masayuki Terai & Koji Sato

The corporation has developed automatic CAD layout software for CMOS sea-of-gate arrays, HGALOP (automatic placement and routing), and MCgen (automatic macrocell generation). HGALOP employs an algorithm that effectively uses the conformity in the layout structures of sea-of-gate devices and is, on average 20 times faster than commercially available tools. MCgen employs a proprietary automatic routing method that generates dense layout patterns for macrocells. The software is being used for devices of 0.5 μm or larger.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.86~89 (1994)

## A Verification System for VLSI Mask Data

by Makoto Kanno, Sueo Hamamoto, Ken'ichi Tanaka, Tsunesato Munakata & Koichi Morizumi

The corporation has developed a mask-verification system that rapidly compares VLSI mask data and detects pattern errors. The system, which employs a neural network model, can automatically determine whether small rounding and similar errors due to slight mask misalignments will be detected. It tests masks in less than one-tenth of the time required for visual comparison on a graphic display, and has already been applied in the production of 16Mbit DRAM devices.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.90~93 (1994)

## Technology for High-Dielectric-Constant Thin Films

by Kazunao Sato, Noboru Mikami, Takaaki Kawahara, Yoshihiro Kusumi & Hiromi Ito

The authors have investigated the application of the high-dielectric-constant thin films of (Ba, Sr) TiO<sub>3</sub> to DRAM devices. Studies were conducted on etching processes and film formation by sputtering and chemical vapor deposition (CVD). Suitable process characteristics for 256Mbit DRAM devices were achieved, and a high-dielectric film was employed in fabrication of 256Mbit devices. The film allows use of a simple cell structure that will lower the cost of producing these devices.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.49~53 (1994)

## 0.5 μm Semicustom CMOS IC

by Kunihiro Sanada, Kazuo Aoki, Hideshi Maeno, Hisashi Matsumoto & Makiko Sasada

The corporation has recently advanced its system-on-silicon design technology by developing a generator for embedded-type high-density modules and phase-locked loop (PLL) and Gunning transceiver logic (GTL) elements for its 0.5 μm CMOS gate arrays. This advance rounds out the corporation's development capabilities for 0.5 μm semicustom devices including embedded-cell arrays and cell-based ICs, allowing design of high-performance integrated systems.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.54~58 (1994)

## A Still-Color-Image Compression/Expansion LSI that Conforms to JPEG International Standards

by Fuminobu Ogawa, Shizuo Ida, Yoshifumi Imanaka, Hiroyuki Sugino & Hideyuki Terane

The corporation has developed a high-performance still-color-image compression/expansion LSI that complies with the baseline system of standards of the Joint Photographic Experts Group (JPEG). This new LSI is capable of coding or decoding 640 × 480 pixel RGB images at a rate of 30 frames per second. It is therefore useful for storing moving-picture data in digital video equipment and personal computers as well as use for still-image applications. The device also includes a number of peripheral functions including color space conversion and simple coding rate control for a variety of applications.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.59~62 (1994)

## A Single-Chip LSI Karaoke Processor for VCR Applications

by Yasushi Adachi & Yusuke Yamada

The corporation has developed the M65835FP high-performance one-chip karaoke processor for karaoke-capable VCRs. It contains a vocal-track cut function, key control functions, echo processing function, and a digital search system for tape cueing. The device is implemented in a new 0.8 μm CMOS process. The corporation had previously developed an echo processor, digital key control, and other special-purpose ICs for karaoke use.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.63~67 (1994)

## A 10bit 50 Megasample per Second CMOS DA Converter that Operates on 3V

by Yasuyuki Nakamura, Takahiro Miki, Yoshikazu Nishikawa & Keisuke Okada

The corporation has produced a prototype of the world's first CMOS DA converter. It has 10-bit resolution, a maximum conversion rate of 50 megasamples per second, and operates on a 3V power supply (2.7V and above). This high performance was achieved by developing a current-source circuit with proprietary bias and drive methods. The effective device area (minus bonding pads) is 1.28 × 1.41mm, a design that allows integration in larger monolithic devices. Maximum power consumption is 50mW at the rated full output current of 10mA.

Mitsubishi Denki Gihō: Vol.68, No.3, pp.68~72 (1994)

## A 600V Gate-Insulated Bipolar Transistor Using a Trench MOS Gate

by Masana Harada, Tadaharu Minato, Hideki Takahashi, Hidenori Nishihara, Keiji Inoue & Ikuonori Takata

The corporation has developed a 600V/50A insulated-gate bipolar transistor (IGBT) with a trench MOS-gate structure. As a result of this trench MOS-gate structure, the new IGBT has a cell area one-tenth that of previous IGBTs, sustains a maximum current density of 200A/cm<sup>2</sup>, turns on at the unusually low level of 1.4V (t<sub>on</sub>=200ns), and has a high breakdown voltage. Tests on these trench IGBTs showed their characteristics to be nearly ideal.

## アブストラクト

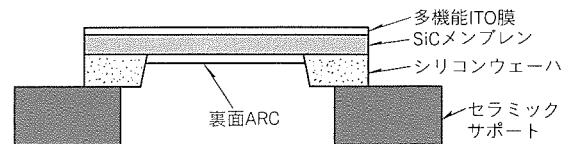

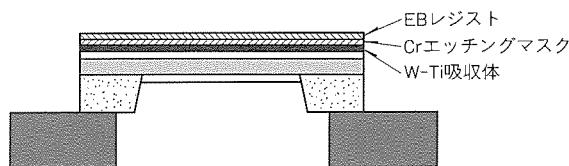

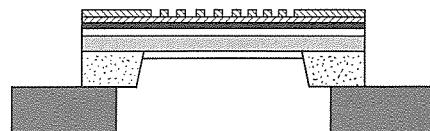

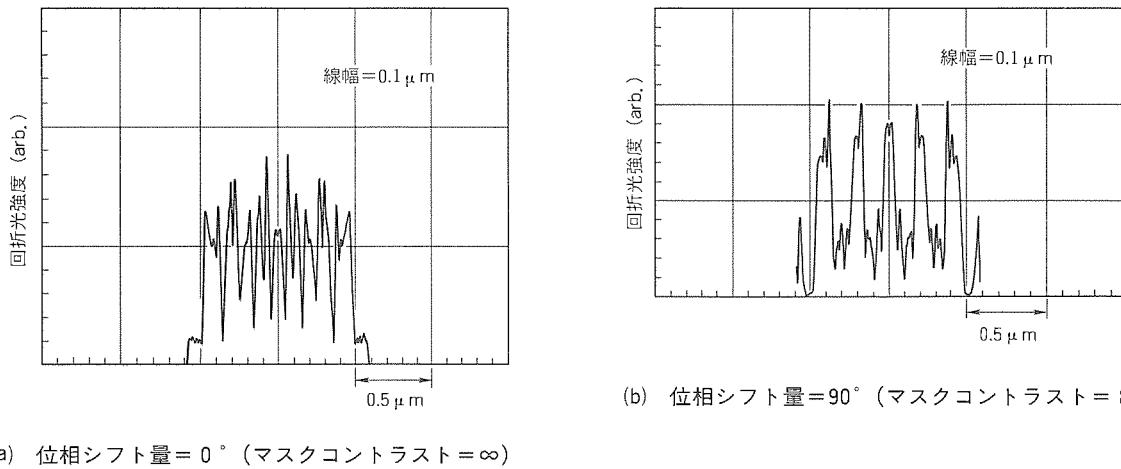

### X線リソグラフィー技術

幸丸正樹・丸本健二・尾崎禎彦・島野裕樹・中西哲也・吉岡信行

三菱電機技報 Vol.68・No.3・p.94～98 (1994)

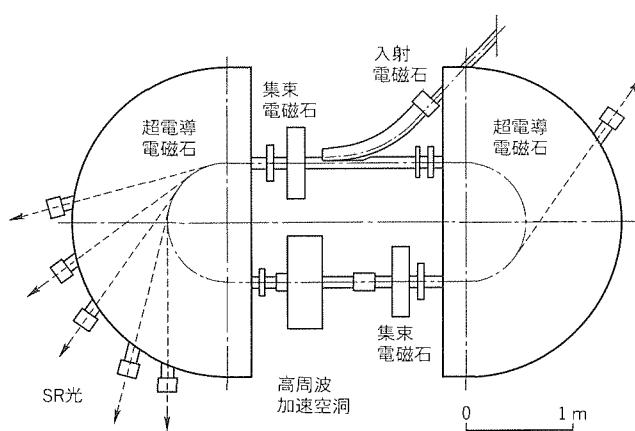

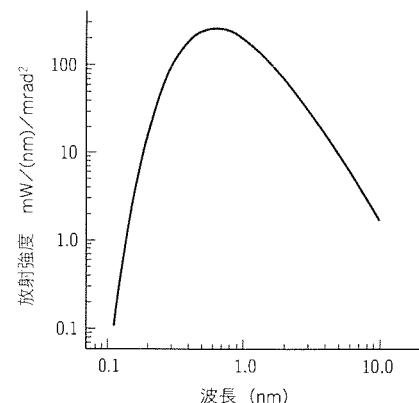

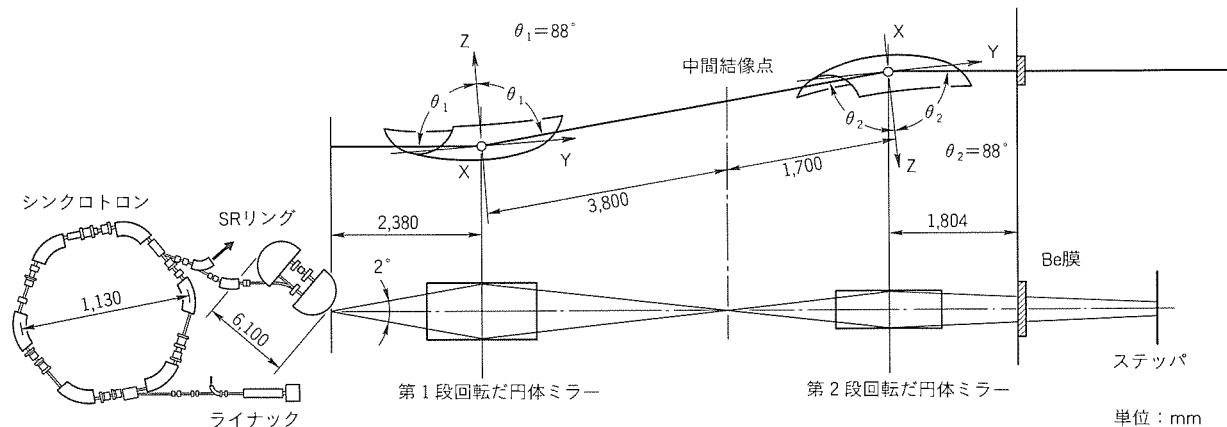

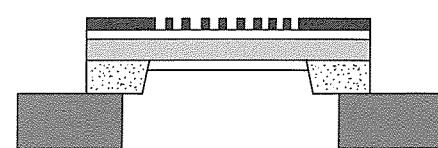

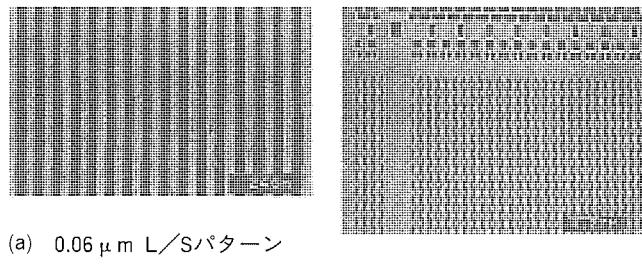

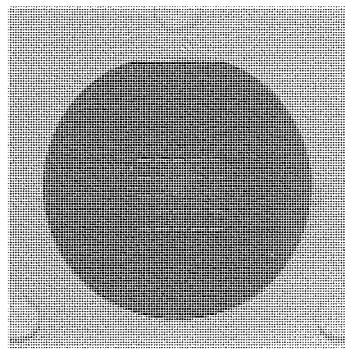

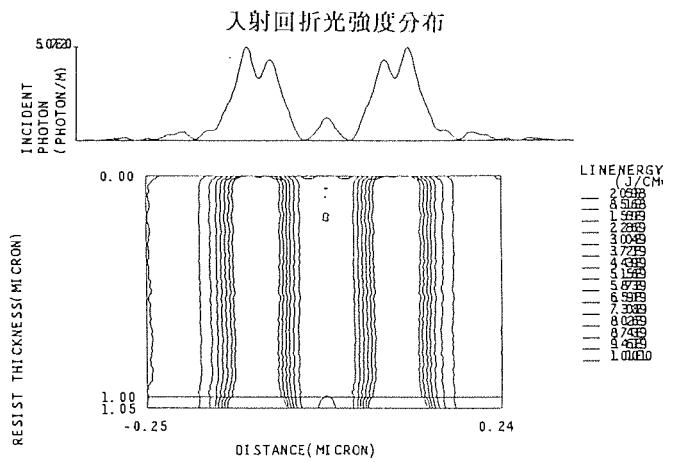

クォーターミクロン以降の半導体デバイス微細加工技術として、シンクロトロン放射(Synchrotron Radiation: SR)光を用いたX線リソグラフィー技術の開発を進めている。

本稿では、光源となるSRリングの小型化、ビームライン照明系の集光光学系によるSR光強度増強や真空保護機能、X線マスクの解像性・位置精度向上、特性評価のための転写シミュレーションに関する当社の取組の概要を紹介する。

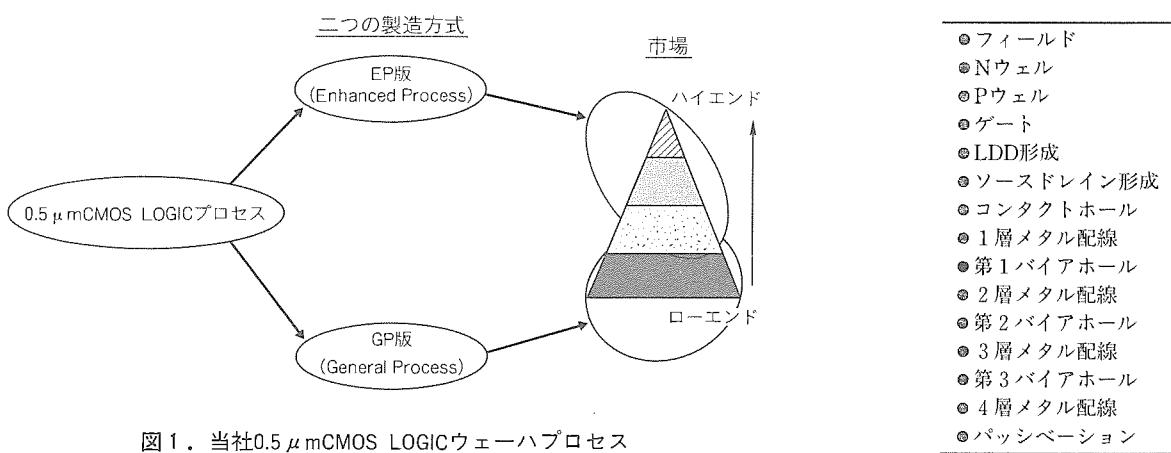

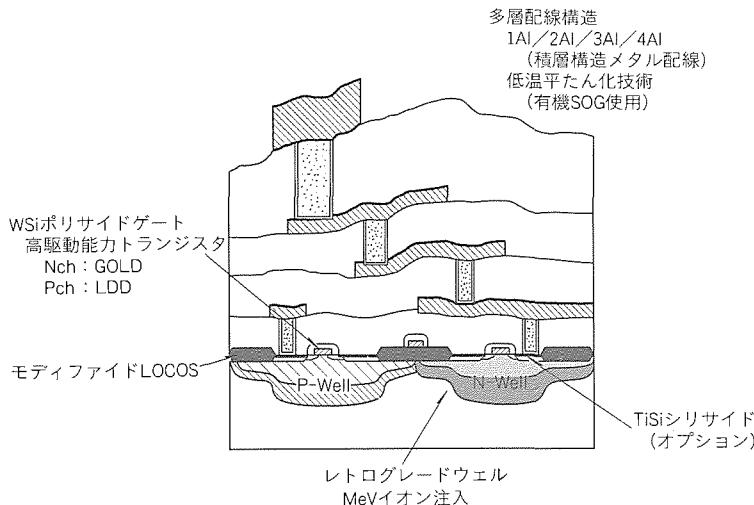

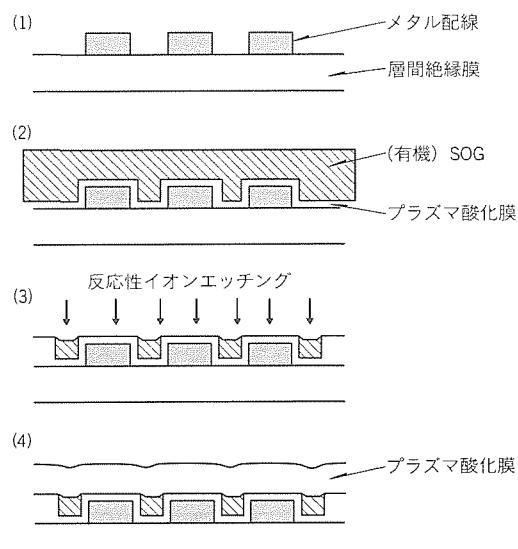

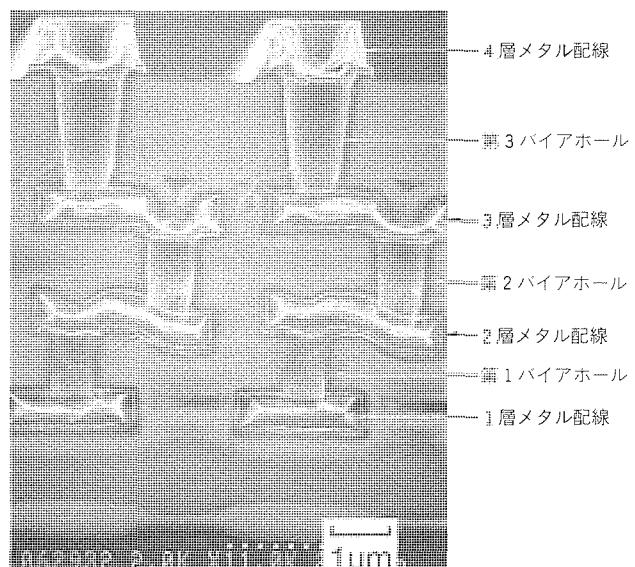

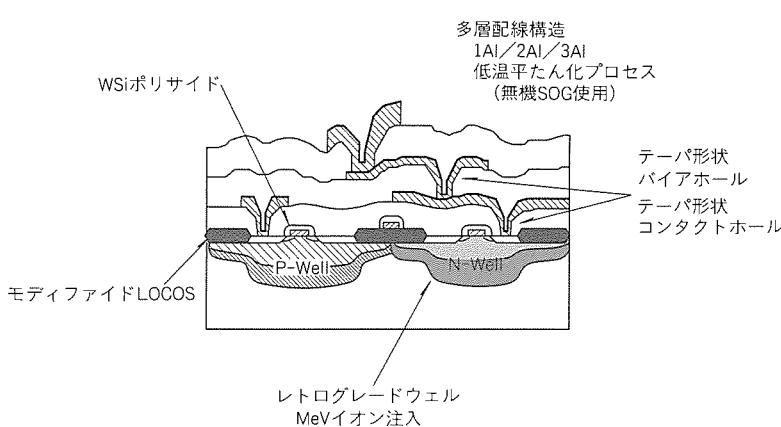

### ハーフミクロン対応ロジック用 CMOS LSI ウェーハプロセス

野崎雅彦・越久和俊・原田 繁・東谷恵市・高田佳史

三菱電機技報 Vol.68・No.3・p.99～102 (1994)

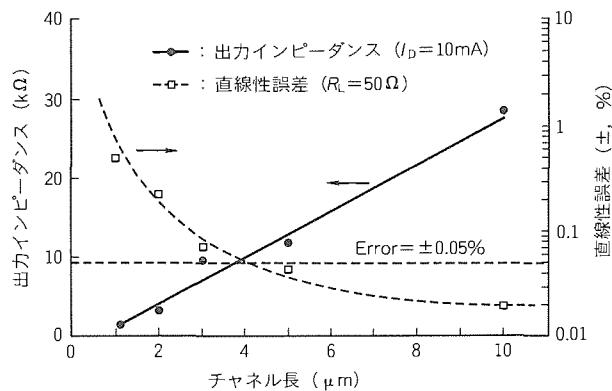

世界最小レベルの微細ピッチで配線可能な多層配線技術と、飽和ソースドレイン電流 NMOS:  $0.44\text{mA}/\mu\text{m}$ 、PMOS:  $0.22\text{mA}/\mu\text{m}$  という高駆動能力トランジスタを持つ  $0.5\mu\text{m}$  ロジック用 CMOS LSI ウェーハプロセスを開発し、高品位ロジックデバイスの世界最高レベルの性能及び低コスト化を達成できた。今回開発した高品位ロジックデバイス技術と、16MDRAM に代表されるメモリデバイス技術とを融合させ、コンパクト化・高機能化に優れたシステム LSI 開発への展開が可能となった。

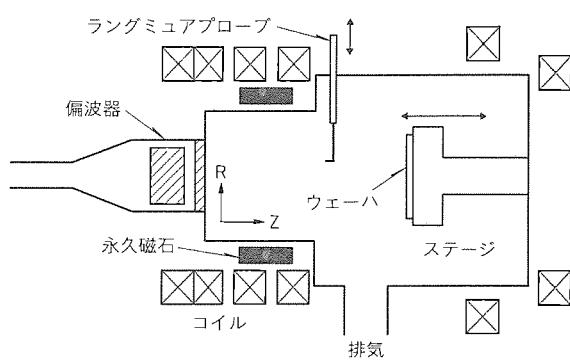

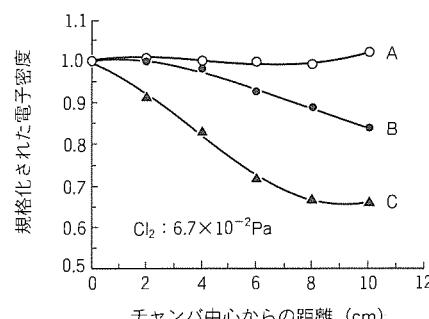

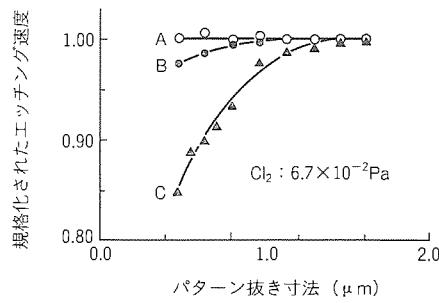

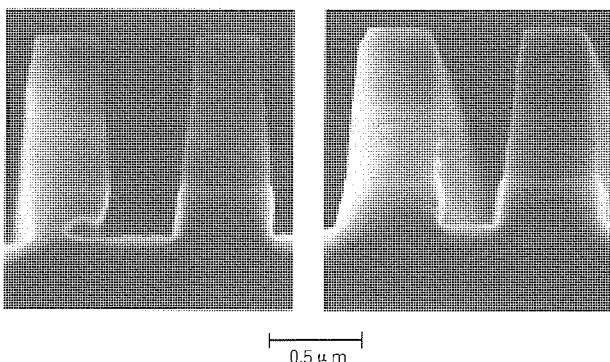

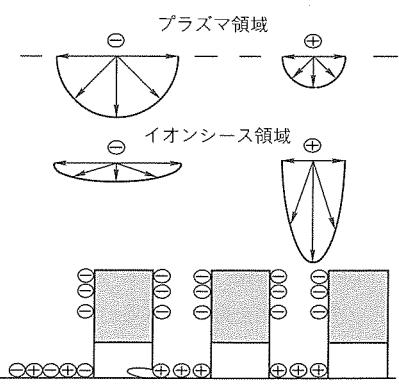

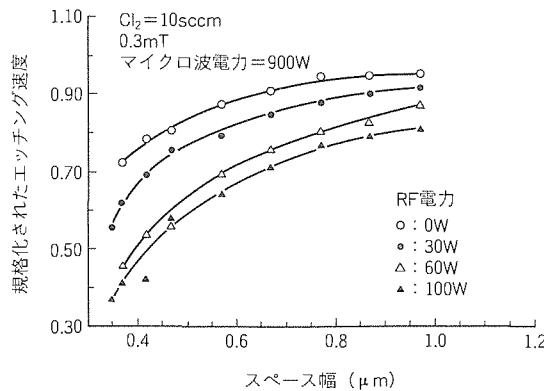

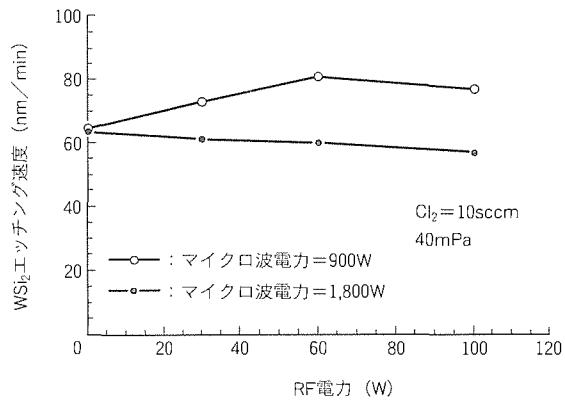

### ノンバイアス ECR プラズマによる微細加工技術

丸山隆弘・藤原伸夫・米田昌弘・塚本克博・大森達夫・番條敏信

三菱電機技報 Vol.68・No.3・p.103～106 (1994)

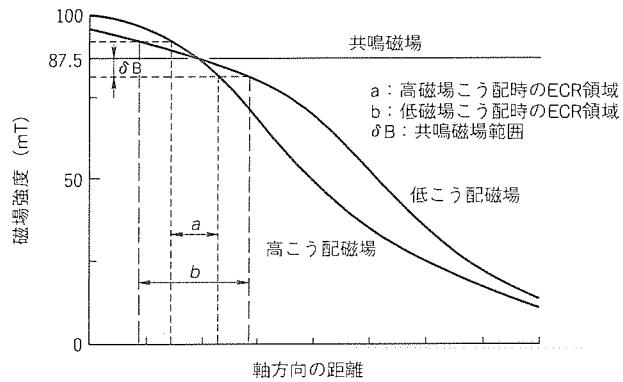

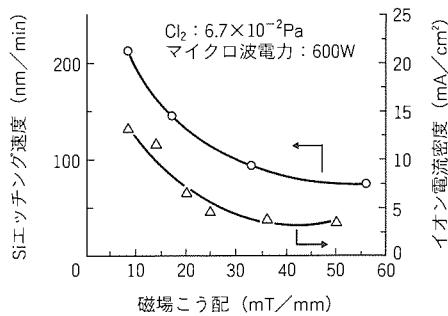

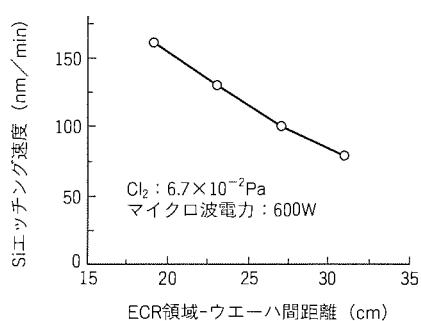

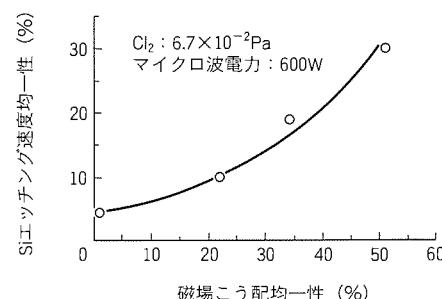

$0.25\sim0.3\mu\text{m}$  レベルの ULSI の製造には、高異方性エッチング技術が必要である。このため、新たに複合磁場を用いた電子サイクロトロン共鳴(ECR)プラズマエッチング技術を開発した。この技術では ECR 領域の磁場こう配の制御により、大口径ウェーハを高速度で均一性良くエッチングできるとともに、パターンのアスペクト比に依存したイオン軌道の乱れの抑制によって高選択性・高異方性エッチングの実現が可能である。

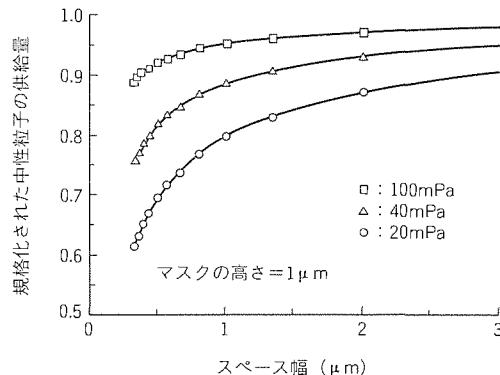

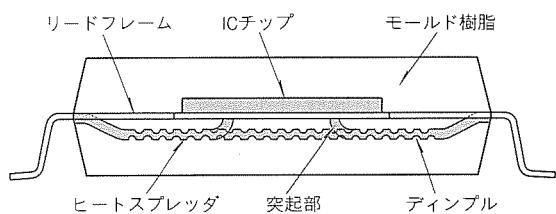

### 高機能・高信頼性パッケージ

佐々木育夫・樋口徳昌・森賀南木・木村通孝

三菱電機技報 Vol.68・No.3・p.107～111 (1994)

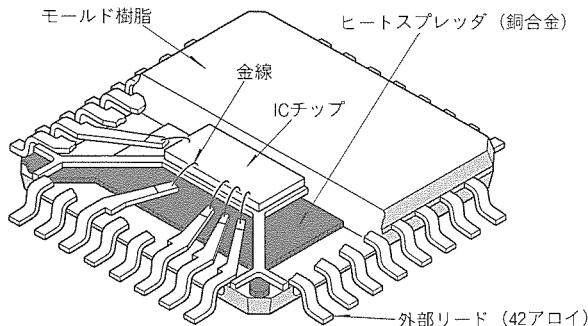

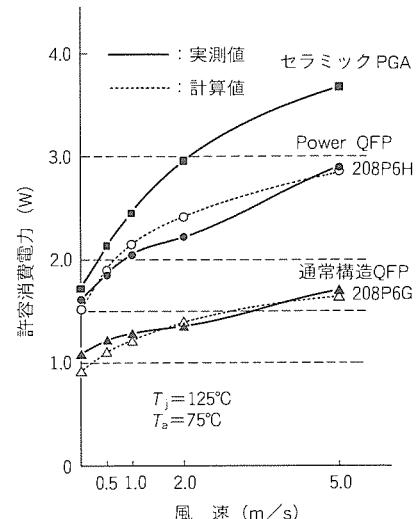

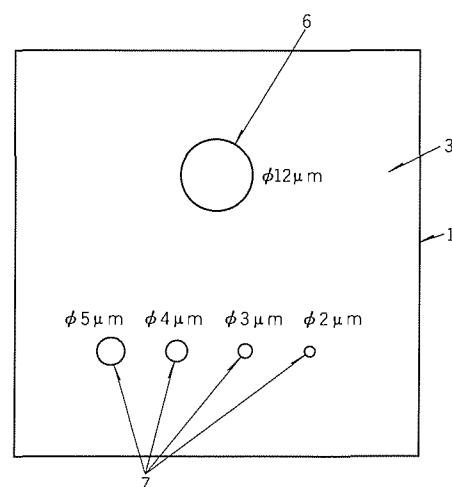

電子機器の高機能化、高速化、小型・軽量化など多様化する要求に対応した4種類の新パッケージの開発状況を紹介する。

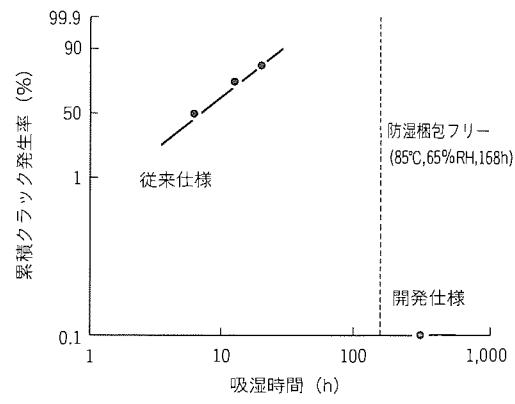

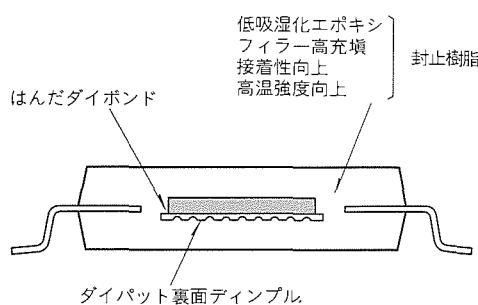

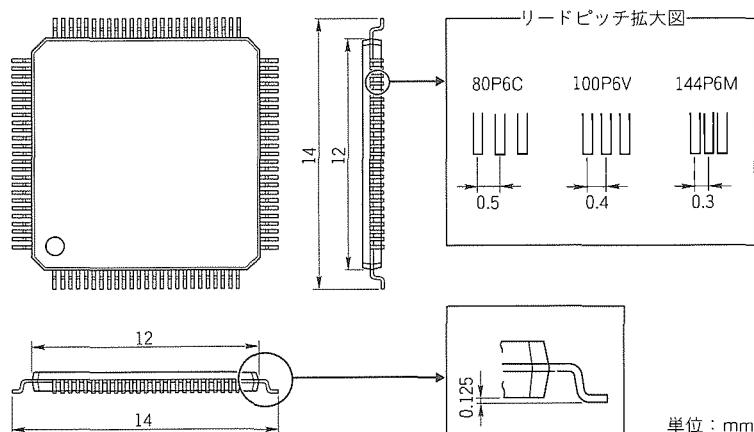

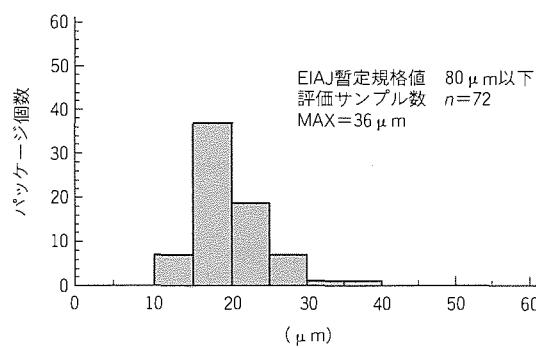

①メモリのチップ収容率向上により、パッケージの小型化を達成した“LOC構造”パッケージ。②メモリの防湿こん(帽)包開封後、実装までの制約条件をなくした高信頼性パッケージ。③マイコン、ゲートアレーなど非メモリの小型化を目的としたファインピッチ QFP。④ヒートスプレッダの内蔵により、高放熱特性を達成した高放熱パワー QFP。

# Abstracts

**Mitsubishi Denki Gihō: Vol.68, No.3, pp.103~106 (1994)**

## Fine Etching by Non-Biased ECR Plasma

by **Takahiro Maruyama, Nobuo Fujiwara, Masahiro Yoneda, Katsuhiro Tsukamoto, Tatsuo Dmori & Toshinobu Banjo**

The authors have investigated etching technology suitable for semiconductor devices employing 0.25~0.3  $\mu\text{m}$  geometries, and developed a new plasma-etching technology employing electron cyclotron resonance (ECR) with a composite magnetic field. The technology is capable of etching large-diameter wafers at high speed with excellent uniformity. The magnetic field gradient in the ECR region suppresses pattern aspect-ratio-dependent ion-path disturbances, resulting in highly selective and highly anisotropic etching.

**Mitsubishi Denki Gihō: Vol.68, No.3, pp.107~111 (1994)**

## Highly Functional, Highly Reliable Packaging

by **Ikuro Sasaki, Noriaki Higuchi, Namiki Moriga & Michitaka Kimura**

The article reports on the development of four new packages designed to meet needs for faster, smaller, lighter, and more functional semiconductor devices: (1) a small lead-on-chip (LOC) package designed to increase memory mounting density, (2) a high-reliability package that loosens restrictions on memory device storage conditions between the opening of moisture proof wrapping and mounting of the devices, (3) a fine-pitch quad flat package (QFP) designed to reduce the size and mounting area of microprocessors, gate arrays and other non-memory devices, and (4) a power QFP with an internal heat spreader to improve dissipation characteristics.

**Mitsubishi Denki Gihō: Vol.68, No.3, pp.94~98 (1994)**

## X-Ray Lithography Technology

by **Masaki Komaru, Kenji Marumoto, Yoshihiko Dzaki, Hiroki Shimano, Tetsuya Nakanishi & Nobuyuki Yoshioka**

Technological advances are applying X-ray radiation from a synchrotron source to lithography of quarter-micron and smaller semiconductor devices. The article reports on the corporation's developments in the areas of smaller synchrotron radiation sources, focusing optics that increase the intensity of the beam line radiation, maintaining vacuum; improvements in X-ray mask resolution and alignment precision, and transfer simulations used to evaluate system characteristics.

**Mitsubishi Denki Gihō: Vol.68, No.3, pp.99~102 (1994)**

## A CMOS Wafer Process for Half-Micron Logic Devices

by **Masahiko Nozaki, Kazutoshi Dku, Shigeru Harada, Keiichi Higashitani & Yoshifumi Takata**

The corporation has developed a half-micron CMOS wafer process capable of low-cost fabrication of high-performance LSI devices. The process supports multilayer metalization employing extremely fine lines, and realizes NMOS source-to-drain currents of 0.44mA/ $\mu\text{m}$  and PMOS source-to-drain currents of 0.22mA/ $\mu\text{m}$ . This advance will make it possible to integrate logic with 16Mbit DRAM technology to build high-performance monolithic systems.

常務取締役

半導体事業本部長

平林 庄司

半導体産業は1993年には回復するとの大方の予想を裏切って、日本市場の低迷に加え、円高のなかで、いまだ回復の兆しが顕著ではない。バブル崩壊で利益構造の弱点を露呈した日本の半導体企業各社は、適正利益の確保を求めて事業体質の改善に躍起となっている。

一方、半導体技術の高度化による開発費と開発設備投資の増大は、費用構造と開発体制の見直しを迫っている。国内外の有力メーカーとのグローバルアライアンスやパートナーシップによる共同開発や開発拠点の積極的な海外展開は、重要な開発戦略となっている。また、生産コスト削減のための海外展開が、特にNIESからASEAN、中国へと、政治・経済体制のボーダレス化として活発化している。

当社は、昨年6月に、事業戦略と開発戦略との有機的展開を図るため、従来開発本部に所属していた半導体関連の三つの研究所を半導体事業本部傘下にした。また、システムLSIの開発力強化と開発効率向上を図るため、三つの研究所を統合し、ULSI開発研究所・システムLSI開発研究所・光マイクロ波開発研究所として再編成し、タイムリーで効率の良い製品開発ができる体制を整えた。さらに、将来に向けた半導体の基盤技術を確立するため、半導体基礎研究所を開発本部に新たに設立し、役割分担を明確にした。

有望製品の見直しとバランスの良い製品構成を図ることが今後の事業運営に重要となるため、当社は、メモリ、マイコン/ASIC、及び個別半導体の3事業責任体制を明確にし、各々の事業体質に合わせた事業展開策を実行していく予定である。

メモリの分野では、コスト競争力強化のための4M、16MDRAMなど現有製品に対する徹底した低コスト化技術の適用と0.35~0.25ミクロンの次世代デバイスの要素技術

開発を行っている。

マイコン/ASICの分野では、時代に先行した付加価値のあるコアセル、メガセルを開発し、さらに、メモリと複合化したシステムLSIの開発を進めている。

個別半導体の分野では、MOS系先端品の開発・製品化、コスト競争力強化を進め、化合物半導体に関しては、通信用高性能光マイクロ波デバイスの開発を推進している。

着実に増えている研究開発費は売上げ比率をベースにした考え方を改める時期にきている。研究開発費の重点的投入、及びリスク分散とリソースの共有化を目的とした協業による研究開発の効率化は、従来の考え方から大きく変化している。

研究開発の成果は①事業に直接結び付く売上げ直結型、②ノウハウや特許等の技術蓄積型に分類される。後者に関しては、技術の蓄積をいかにドキュメント化し、財産として残すか、そしていかに早期に権利化を図るかが経営上重要である。蓄積した技術を共通技術として他の製品開発に素早く展開するため、そのデータベース化とマネジメントが重要となる。

今回の多くの半導体関連の技術論文は、このような開発のスタンスを十分考慮したものと期待している。

50年にも満たない半導体の歴史は、これまでに人類が蓄積した技術の上に成り立っているものが多い。シリコンという地球上に豊富に存在している石の上に、人間は自らの高度な技術と英知で、考える石につくり上げた。

その技術と英知がエネルギー問題を解決し、地球の環境を守り、すべての人間に豊かな生活空間を与えられるような価値ある役割を果たすよう、当社半導体35周年を迎えるなかで、祈念する次第である。

## パラダイムシフトの時代を迎えたマイクロエレクトロニクス

東北大学工学部

教授 大見 忠弘

今、エレクトロニクスがその技術体系を大きく転換しようとしている。

技術が貧困でプロセス変動が大きく精度の高いIC作りができなかった時代に最も整合性の良いブール代数を基礎とするバイナリデジタル技術と、四則演算の超高速処理に優れ、演算処理の結果のデータをレジスタを介してメモリ部に記憶させ、次段の演算処理ブロック部をプログラムに従ったスイッチ操作により探し出し、レジスタ部及び配線を介して必要なデータをメモリ部から送り出し、逐次直列的にデータ処理を行って答えを求めていくノイマン型コンピューティングシステムとの組み合わせが、現状の信号情報処理体系となっている。すなわち、演算処理ブロック、メモリブロックがそれぞれチップ上、ボード上に多数分離して局在し、巧妙なソフトウェアにより互いに膨大なデータ通信を膨大な配線を介して行なうながら情報処理を行っている。取り扱う情報量があまり多くなければ、この処理方式は厳密かつ正確で極めて有効である。

しかし、画像処理にみられるように対象とする情報量が多くなると、現状の電子システムの応答性は極端に劣化し、人間や種々の動物等の生命体が有する瞬時応答機能に全く歯が立たなくなる。LSIの配線に沿う信号伝搬速度は、生命体の神経の信号伝搬速度に比べて6桁以上速く、トランジスタの動作速度は生体ニューロンのそれに比べて7桁以上速いにもかかわらずである。

技術が貧困でIC、LSI製造プロセスの変動が大きく動作余裕が少ない時代に、エレクトロニクスの最大の使命である正確で厳密かつ確実な動作、すなわち完全な信頼性を求めて導入した情報処理体系をそのまま今日まで継続させた当然の結果である。

データが処理される場所を求めて演算処理ブロック部とメモリ部を往き来するのではなく、データフローパスがミニマムになされ、かつチップ間や演算処理ブロック間に情報の通信を必要としない、すなわちチップ間や演算処理ブロック間に複雑な配線を必要としない、データが同時完全並列処理される情報処理体系への転換が今や不可欠となっている。ソフトウェアがハードウェア中に一体となって埋め込まれ、演算処理部とメモリ部が巨大ブロック化されて分離して局在するのではなく、隣接して分散分布するとともに、演算処理部が前段の処理の結果等に基づいて要求される処理機能に実時間で変わっていくフレキシブルなハードウェアが必要となる。演算処理部間の複雑な配線を介したデータ通信も徹底的に少なくして、理想的にはゼロにすることにより、データフローパスがミニマムになるばかりでなく、データの同時並列処理が行われて瞬時応答性に優れた、文字どおり知的処理機能を備えた電子システムが実現されていく。

こうした演算処理部間の通信を伴わずデータフローパスミニマムで同時並列処理を行うには、従来のバイナリデジタル技術だけでは不可能で、数系を十分考慮した多値論理処理を縦横に駆使することが不可欠であるとの指摘が既に東北大学の樋口龍雄教授や亀山充隆教授によりなされている。これまで多値論理を具現化しようとすると、イオン注入の打ち分けにより、必要な多値レベルに相当する異なった閾値電圧を持つMOSトランジスタの導入が必要となり、製造プロセス

への負担が重く、性能は圧倒的に向上するにもかかわらず広く普及するには至らなかった。

音楽の分野でクラシックの爱好者は極めて多い。モーツアルト、ベートーヴェン、シューベルトといった天才達が到達した頂点を、その後100年～200年経過した今日においても乗り越える作曲者は現れない。何故だろうか。駆使できる楽器の種類が決まり、その演奏技術が頂点を極めた同一の条件下では、歴史上の大天才を後世の人間が乗り越えることは極めて困難なことである。もし、今後新しい交響曲の世界を拓こうとすれば、未だかつて誰も聞いたことがなくてかつ快適な音色の新しい楽器を創り出す以外に道はないのではないかと筆者は考える。楽器すなわち音楽の世界における基盤技術である。

すべての分野においてこのことは普遍的であろうと筆者は考えている。

20世紀のエレクトロニクスは、1906年に発明された3極真空管、1948年のバイポーラトランジスタ及び1960年のMOSトランジスタに代表される3端子デバイスによって創り上げられたと筆者は考えている。二つの主電極間に流れる電流を第3の制御電極の入力信号により制御できる機能を備えた3端子デバイスの出現により、増幅、発振、波形整形、スイッチング動作といったエレクトロニクスに不可欠な機能が実現された。真空管と異なり、Normally-Off特性を有するトランジスタは、入出力電圧が同極性電圧となることから直結型回路構成が可能のこと、及び相補型(Complementary)回路構成が可能であり、消費電力を徹底的に小さくできることから、集積化エレクトロニクスが一挙に開花し、今日のマイクロエレクトロニクス全盛の時代が築かれた。

しかし、我々はトランジスタ・3端子デバイスの世界に酔いしれすぎていたようである。そのために、未だに小動物の瞬時応答機能に全く歯が立たない電子システムしか考案できずにいたようである。第3の端子による電流制御そのものを制御する第4の端子を導入した4端子デバイスは、電流制御の自由度が1次元増えることから、単体デバイスレベルで実に多彩な機能を発揮する。4端子デバイスは、電子デバイスの超高速性能を備えながら、機能は生体ニューロンの多彩さを兼ね備えている。多値論理処理はもちろん、知的電子システムに不可欠のバイナリ・多値・アナログ融合動作を単体デバイスレベルで可能にする。ソフトウェアをハードウェア中に埋め込もうとしたときに、まさに格好の機能を備えたデバイスである。マイクロエレクトロニクスの分野に、従来は誰も使うことのできなかった新たな基盤技術が誕生したのである。瞬時応答機能を備えた知的電子システムに向けたパラダイムシフトが、この90年代に急速に進展する。

システムにフレキシビリティやプログラマビリティを持たせようとすると、ULSI製造技術は正確無比で極めて厳密なものでなければならなくなる。マイクロエレクトロニクスの分野に第2の革命期が訪れたのである。

三菱半導体技術陣の21世紀に向けた新たな飛躍を目指した一層の奮闘を祈念してやまない。

# 半導体の技術動向と展望

坂根英生\*

## 1. まえがき

急速な技術進歩と応用範囲の拡大によって目覚ましい成長を遂げてきた半導体産業も、1990年代に入り質的拡大、すなわち高性能化、小型化・低消費電力化、ディジタル化等を一層追求する時代へと転換してきている。

このような変化の中で、半導体応用市場からのニーズと半導体自身のシーズ技術の融合がますます重要になってきている。高性能化、小型化・低消費電力化、ディジタル化といったシステム側からのニーズは、LSIの微細化・高集積化、生産技術等のシーズ技術の進展によって実現が進み、またシステムLSIもハーフミクロン時代に入り、いよいよ本格化しようとしている。

この背景のもとに本稿では、最近の技術動向について、半導体の応用市場及び半導体デバイス・技術の両面からこの特集号の論文を引用しながら展望する。

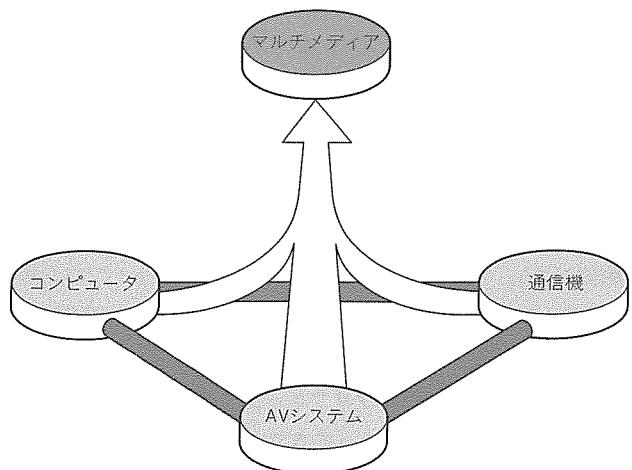

## 2. 半導体の応用市場の動向

半導体が応用される電子機器の世界では、技術の進展に伴って大きな変革が起こりつつある。それは、半導体の三大市場として独立に発展してきたコンピュータ、通信、AVが融合一体化し、いわゆるマルチメディアという形で、21世紀の情報化社会の主役になろうとしている点である(図1)。

### 2.1 コンピュータ市場の動向

過去の10年間はコンピュータ技術の大変革の時代であった。特に近年は半導体技術の進歩により、従来の大型機に匹敵する機能が机の上に載るサイズで、しかも数十万円程度のパソコンで実現できるようになったため、大型機から小型機へのシフト、いわゆるダウンサイ징が雪崩のように起こった。また、コンピュータの大衆化により、使いやすいOSやGUIや汎用応用ソフトウェア等のソフト産業の重要性が増した。今日でもダウンサイ징の勢いは止まっておらず、21世紀には手の平に載るスーパコンピュータが実現できるようになるであろう。周辺機器の小型化、高性能化も同時に進んでおり、超小型のHDDや、高品質印字のできるLBP、さらにはフラッシュメモリを使った固体ディスク等が登場してコンピュータ産業を支えている。また、コンピュータの高性能化で、数値データのみならず、画像、なかでも動画像までもパソコンで扱えるまでになってきた。こうなると、今後は単なるダウンサイ징にはとどまらず、全く新しい概念

の応用機器に変身していくように思われる。

### 2.2 通信分野の動向

高度情報化社会では、情報をいかに速く正確に伝えるかが極めて重要であり、通信技術が大きな役割を果たす。未来社会では、“いつでも、どこでも、だれとでも”という標語で示されているように、時間・空間を飛び越えてあらゆる情報が高速に行きかうようになる。最近では、この標語に“なにとでも”が追加され、人とコンピュータが通信で結び付こうとしている。これらを支えるのが通信機器のパーソナル化であり、高速通信網のインフラ整備である。パーソナル化では、既に自動車用携帯電話が現実のものとなっているが、より簡便な個人用の携帯電話(日本ではPHSの呼び名)が間もなくサービス開始予定されるなど、着々と準備が進んでいる。電話というのは、設置場所にかけるのではなく、それを保有している人に、居場所を意識せずにかけるという時代に間もなくなるだろうとしている。さらに、将来は音声のみならず携帯情報端末としてコンピュータ技術と結び付き、データ通信、画像通信をも扱えるいわゆるマルチメディア機器に発展するものと期待されている。

インフラの整備では、米国での情報スーパーハイウェイ計画で代表されるように、情報が高速に行きかう光ファイバによる情報ハイウェイが新社会資本の重要要素として認識されるようになってきた。また、通信衛星を多数打ち上げ、世界中どこでも移動体通信端末が使えるようにしようとの雄大な構想もあり、国境を越えた活動が盛んになろうとしている。これらの通信技術を支えるのが半導体技術であり、高周波を

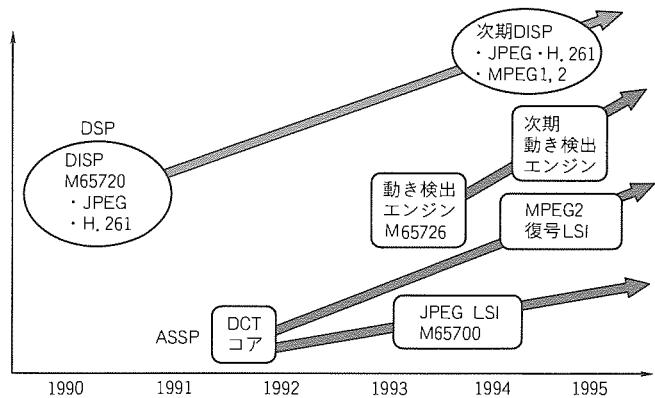

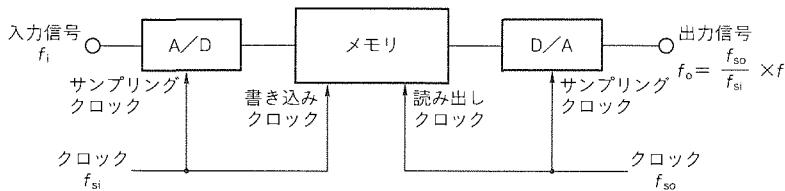

図1. システムの進展、融合と統合化

扱う半導体から、データ処理を行う半導体まで広範なデバイスが必要となる。

### 2.3 AV市場の動向

堅実な発展を遂げてきたAV市場も、ここ2~3年はやや伸び悩みの傾向を見せている。これは、TV、VTR、オーディオといった主力機種において、文化を変えるほどの革新性を持った概念の製品が登場しなかったためと思われる。しかし、ハイビジョンの本格化等、新しい芽が伸び始めており、技術の発展とともに新たな飛躍へと踏み出し始めている。その背景にあるのが、信号処理のデジタル化である。従来、アナログの世界であったAV市場でも、半導体技術の進歩によってデジタル処理化が可能になってきた。現在は、YC分離、ゴーストキャンセラ等の画質向上目的で従来路線の技術向上に使われているが、デジタル方式はコンピュータ技術との親和性が良いため、将来はコンピュータと結び付いてマルチメディアの一貫として、様々な応用機器に発展するものと考えられる。例えば、双方向通信のできるインタラクティブTV、携帯情報端末でのTV電話等が検討されている。

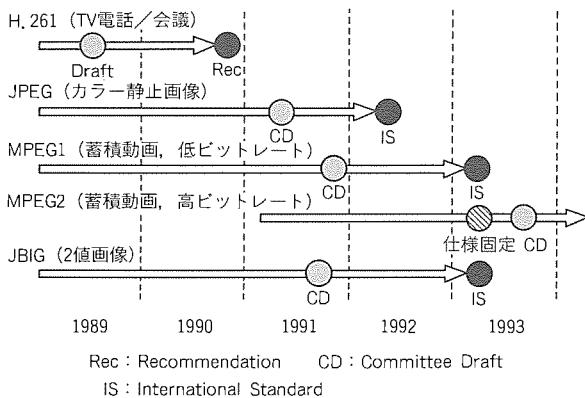

### 2.4 マルチメディア

以上述べたように、コンピュータ、通信、AVが融合してマルチメディア時代へ向かおうとしている。ただし、具体的な製品像はまだ暗中模索の状態であり、現在は、必ず(須)技術としての画像、音声の圧縮/伸長技術開発及びその半導体での実現の動きが主である。その中で、民生用途としてCDに圧縮した画像情報を載せ、現在のレーザディスクにとて変えようという動きが具体的に進みつつある。また、米国では、全米に既に張り巡らされているケーブルテレビ網をインフラとして利用し、デジタル技術を採用することにより、双方向のデータ通信が可能なインタラクティブTVへの具体化が進んでいる。さらに、将来は個人の持つ携帯情報端末に無線技術と高速通信網が結合して、本格的なマルチメディア時代が到来するものと考えられる。ただし、それを経済的に実現できる技術と提供できるソフト、サービスについてのインフラが必要である。

## 3. 主要半導体の動向

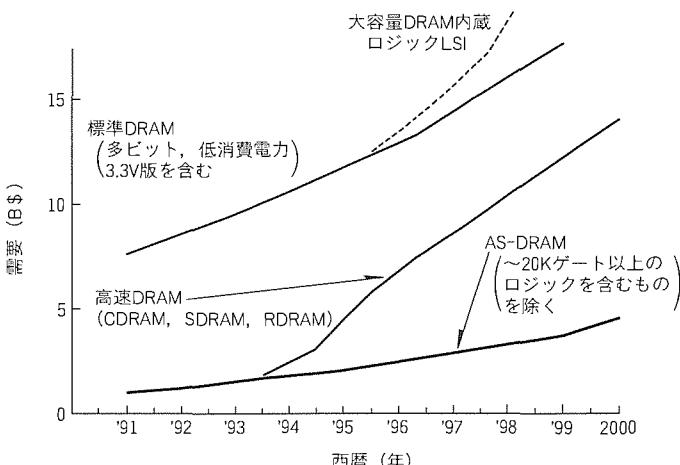

### 3.1 メモリ

(1) DRAMは、大容量化<sup>#</sup>とともに多機能化が進んできている。これは低消費電力を必要とする小型システムの台頭及びシステムの高機能化・特種機能化に伴うメモリ側への強い要求による。すなわちこの2~3年の間にノートパソコン等の携帯小型システム向けとして、小容量の主メモリ用又はバッファメモリ用多ビット品が開発・生産されるとともに、電池駆動機器用としてセルフリフレッシュ機能品を代表とする低消費電力版<sup>#</sup>が主流になってきている。さらに、低電圧化

(注) <sup>#</sup>印の付いた項目については、この特集号の論文に掲載されていることを示す。

が加速されており、今後低電圧品の比率が高くなっていく。スピードについてみれば、プロセッサの高速化に対してDRAMのスピードが追隨できなくなつて久しいが、新たな高速化技術が開発・展開されてきている。その例として、当社オリジナルの高速SRAM(キャッシュ)内蔵のCDRAMや、ほかにEDRAM/RDRAMやシンクロナスDRAMなどがある。さらに、グラフィック用メモリでは、システムの一部をチップ上に取り込むシステムオンチップ化が始まっている。図2にDRAMの品種別需要予測を示している。

(2) SRAMでは、PC用HDD、小型携帯機器やコンピュータに用いられる高速SRAMに、一層の低消費電力化・大容量化・高速化が要求されている。このため、1M、4Mの大容量低消費電力SRAMには、ハーフミクロン微細化CMOSプロセス、TFTなどの新技術を取り入れ、低電圧動作、超低スタンバイ電流を実現し、低消費電力性能を達成している。また、256K、1M高速SRAMでは、最新世代の微細化CMOSプロセスを適用して世代交代を進め、より高速のアクセスタイムと低電圧動作を実現<sup>#</sup>している。より高速の要求に対しては、BiCMOS技術を採用し10ns以下の超高速アクセスタイムを達成している。

(3) フラッシュメモリは、EPROMとEEPROMの特長を融合した、最も成長が期待される半導体メモリの一つである。サブミクロンプロセスで製造される1M/4Mビット品は、既存のEPROMの置き換え用途がメインであり5V/12Vの2電源、ソフトウェアコマンド制御が標準装備される。16Mビット品<sup>#</sup>は最初のハーフミクロンフラッシュメモリとして電池駆動の携帯情報機器向けを中心に低電圧対応となり、ワード線昇圧・行リダクションの採用によって実用化される。さらに、次世代フラッシュメモリは、単一電源化・高密度化が要求され、負電圧制御・新規セル構造の開発が進んでいる。

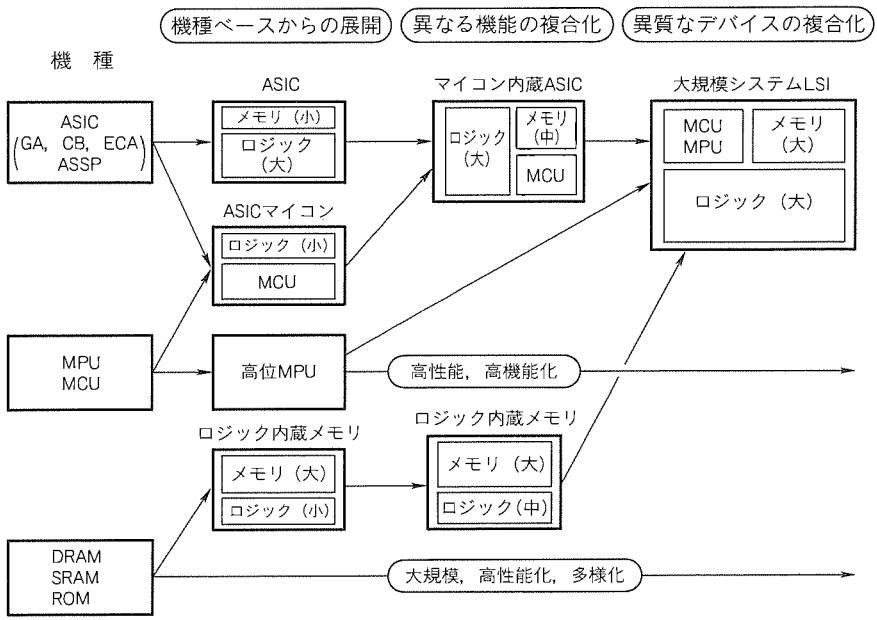

### 3.2 マイクロコンピュータ・ASIC

集積規模の増大とともに、システムをより少数のLSIに統合するシステムLSI化が進んでいる。今後ハーフミクロ

図2. DRAM世界需要の当社予測

ン時代を迎え本格的な展開が期待されるが、多品種を設計・生産する効率が問題となる。このため、設計手法・CAD・プロセスの標準化や統合による生産性の向上が図られている。システムLSIの展開は、ニーズとシーズが調和しなければならないが、図3に示すように、MPUをコアとしてASICを取り込む方向と、大容量メモリをベースに進展する方向がある。どちらも将来のシングルチップPCに向けて、これからが楽しみな応用と技術である。

(1) マイクロコンピュータでは微細化の進展により、CPU性能の向上、周辺機能の充実、高速動作、低電圧化、低消費電力化、内蔵メモリの大容量化、小型パッケージ化など、様々なメリットが出せるようになってきた。以下に当社のマイクロコンピュータでの幾つかの例を挙げる。

- CPU性能の向上では、高性能新16ビットマイコン(M16ファミリー)の開発<sup>#</sup>

- 周辺機能の充実では、自動車用マイコンでの16ビットタイマの24本化

- 高速動作では、8ビットマイコンで10MHzから20MHzに

- 低電圧化では、4ビットマイコンで1.1V動作の実現

- 低消費電流化では、16ビットマイコン(7700シリーズ)で4mA(3V, 8MHz時)の実現

- 内蔵メモリでは、自動車用マイコンでのROM 92Kバイト、RAM 3Kバイトの内蔵化

また、処理能力の更なる向上をねらい、CPUを複数内蔵する動きもある。この一つの例として、当社では通信処理専用にサブCPUを内蔵した8ビットマイコン<sup>#</sup>を開発中である。

微細化のメリットは、このように多種の成果を生み出しているが、それらを加速する上でネックとなるものも幾つか存在する。例えば、プログラム容量増大に伴うソフトウェア開発の難しさがある。その開発サポートツールの充実もメーカーとして必須である。また、大容量プログラム化時代に向けてプログラム開発の容易化<sup>#</sup>をねらったCPUコアの開発も重要である。

微細化のネックとして二つ目にノイズ問題がある。トランジスタの高速化に伴うノイズ発生と外部ノイズによる誤動作の両面で問題が発生する。マイクロコンピュータの機能が向上するほど、これを使用した機器では問題も大きくなる。また、高集積化を加速する上でも問題となる。そのため、当社

では特にこの問題に重点的に取り組み、技術的に回避できるようになった。

このように高集積化の壁も少くなり、マイクロコンピュータは今後とも大きく発展するとともに、システムオンチップの代表デバイスとしても発展が期待される。

(2) ASICは、コンピュータ、通信、AV機器等各応用市場対応のキーデバイスとして開発が一層活発化してきている。

コンピュータ・周辺機器用途では、メモリ制御、バス監視等の高速データ処理用に、高速・低消費電力の最先端0.5μmCMOSセミカスタムIC<sup>#</sup>の適用が既に始まっており、また、SCSI/LAN/FDD/プリント制御用LSIも開発されてきている。低消費電力パソコン用にはVGA表示/液晶表示コントローラ、バッテリマネジメントIC、HDD用にはローノイズR/Wアンプ+信号処理LSI等も実用化されている。

マルチメディア用としては、画像・音声の圧縮・伸長用LSI<sup>#</sup>がJPEG、MPEG等の世界標準規格に基づいて開発されており、画・音の変・復調LSIも開発されている。

通信機器の特に市場が急成長している携帯電話では、高速・低電圧・低消費電力・小型化へのニーズが非常に強く、選局用IC、音声コーデック等のLSIが超小型パッケージを適用して開発されている。

AV機器では、高画質・高音質化に対応して、MUSEデコーダ、ディジタルYC分離LSIを、また複合製品であるカラオケVTR用には音声処理LSI<sup>#</sup>が開発されている。また、TV信号等の画像処理用に多用される高速DAコンバータの低電圧、低消費電力化<sup>#</sup>へのニーズは大きい。MD・DCC用音声処理LSIも市場に出始めた。

OA機器としてプリンタ、複写機、FAX用に高画質・省メモリのための画像圧縮・伸長LSI、高画質化等の画像処

図3. システムLSIの発展過程

理 LSI, 高速・高精度モータドライブ LSI, モデム用 LSI 等が開発されている。

### 3.3 個別半導体・応用製品

(1) 最近のパワーエレクトロニクスは、電力・産業・情報・家電の各分野で“インバータ化”をキーワードとして目覚しい発展を遂げているが、この発展に大きく貢献しているパワーデバイスは、市場ニーズに対応して高周波化(MOS化)が一段と進んでいる。その中でも IGBT や、更なる使いやすさの追求とインテリジェント化を図った IPM が急速に広がっている。これらは微細化・高集積化の技術革新によって世代交代を重ねており、トレンチ MOS 構造 IGBT<sup>#</sup>もその開発トレンドの中で重要な位置を占める。

(2) 高周波光半導体素子は、高度情報化社会の通信技術に大きな役割を果たす重要なデバイスであり、その市場はますます広がろうとしている。当社ではこれら市場に対応し、携帯無線・自動車電話用に高効率高周波高出力モジュール、携帯電話用に低電圧化 GaAs IC, 衛星・地上通信用に高性能高出力 GaAsFET, 光通信用高性能 DFB レーザを開発・製品化している。

(3) メモリ応用製品として当社は、1987年に TSOP を搭載した世界初の 512K バイト大容量 SRAM や OTP カードを発表し、新しい市場の開拓を行ってきた。このたび、TSOP よりも更に薄い DTP (Dual Tape Carrier Package) を新たに開発し、これを使用したメモリと周辺 IC を搭載した大容量カード<sup>#</sup>を開発した。この DTP 搭載型カードは、TSOP カードと比べて 2 倍の大容量化が実現できるので、将来 HDD 代替の 100 ~ 150M バイト級カードも実現できる。

(4) 応用製品の他の例として自動車用半導体を見ると、地球環境保全に関連した燃費、排ガスの規制強化、さらに安全対策としてのエアバッグの改良などに幅広く使用されている。一例としてのエアバッグの衝突検知用加速度センサを、従来のスイッチ機能のみの機械式又は電気式からリニアセンシング機能を持つ電子式へ切り替える検討が進められているが、そこでは半導体式加速度センサ<sup>#</sup>が有望視されている。

## 4. 半導体の設計、製造技術

### 4.1 CAD技術

メモリ、MPU 等半導体の急激な進歩による高性能・低価格 EWS の実現とソフトウェアの充実により、LSI 設計用 CAD は論理設計／検証等上流設計から、レイアウト設計／検証等までを統合的に行えるようになった。さらに、LSI 製品それぞれの最適設計手法に対応し、メモリ／マイコン／ASIC (セルベース、GA, ECA)／アナログの各 CAD システムが開発、実用化された。CAD による設計は、コンピュータを駆使した自動化により、大規模 LSI を高精度、短期間に設計することである。レイアウト設計／検証の自動化か

ら、最近では、ASIC やマイコンの CAD において言語による機能記述／論理合成など上流設計の自動化<sup>#</sup>が実現された。メモリ対応の CAD ではプロセス／製品のコンカレント開発環境、超大規模レイアウト設計／マスクデータ処理用 CAD<sup>#</sup>が、またアナログ用 CAD ではアナログ／ディジタル混在 LSI 用設計環境が、実現されつつある。これらは、今後システム LSI 設計用 CAD へと進化していく。

### 4.2 ウエーハプロセス技術

DRAM をドライバとして、ハーフミクロン技術の量産化が始まった。デバイス技術では、16 MDRAM で培った技術が SRAM・フラッシュメモリへ、さらには先端ロジックデバイスの標準 CMOS プロセスへと展開されている。当社では、ASIC 用として市場のニーズに対応した高速トランジスタ構造を開発し、また最大 4 層配線を実現<sup>#</sup>した。これにより、システム LSI 対応プロセスのメニューがそろった。

クオーターミクロン技術では、i 線ステッパやエキシマステッパ、各種異方性エッチング技術更に平たん化技術、新配線材料技術等の開発<sup>#</sup>が行われている。

また、次世代メモリへの展開が有望視されている高誘電体薄膜材料<sup>#</sup>や、21世紀の技術として X 線リソグラフィ<sup>#</sup>などの基礎基盤技術の研究・開発が欠かせない。

今後は、増大する開発投資をいかに抑えるかを念頭に置きつつ、競争力のある微細化技術開発を継続する必要があろう。

### 4.3 アセンブリ技術

LSI の高集積化、高速化とともに、アセンブリ技術の重要性がますます増大してきた。従来の IC チップをシステムに実装する手段及び使用環境から保護する手段に加え、ダウンサイ징に伴う小型・軽量化、内蔵デバイスの高速化に対応した電気的特性改善、より一層の大規模化に伴う多ピン・高放熱特性の要求など、よりユーザーニーズに沿ったパッケージが求められるようになってきた。例えば、MPU を代表とするロジック系の IC では、ピン数の増大と 200 MHz にも及ぶ高速化と発熱の増大に対処できるパッケージが必要となってきた。これに対応して、ピン間隔の縮小と放熱板を内蔵した高放熱 QFP<sup>#</sup>を開発した。

今後も、一層の小型・高密度実装技術へのニーズに適応して新概念に基づくパッケージ構造開発が継続されよう。

## 5. むすび

本稿では、半導体応用市場と半導体デバイス及び技術の動向について主なトピックスを述べた。個々のシステムや半導体デバイスは今後とも一層進展していくが、一方マルチメディアやシステム LSI で代表されるように新たな応用市場やそれに対応する半導体デバイスの実現が加速されていく。

今後はニーズ側、シーズ側の双方にとって、従来以上にその融合と多面的なアプローチが重要な時代となってこよう。

## 64MビットDRAM

諸岡毅一\* 岡本龍郎\*\*

宮本博司\* 須賀原和之\*\*

古谷清広\*

## 1. まえがき

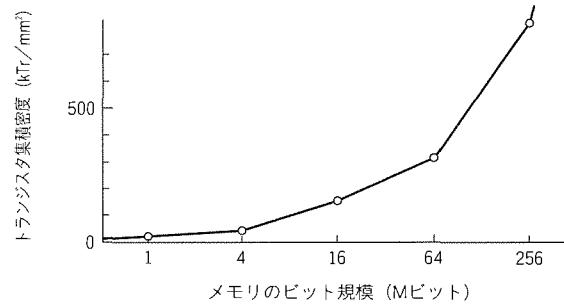

超LSIの代表品種であるダイナミックRAM(DRAM)は、半導体のテクノロジードライバと呼ばれるように先端技術を駆使して高集積化を実現し、そこでの技術開発がLSI技術全体に大きな影響を与えてきた。DRAMは、1トランジスタ+1キャッシュというメモリ素子の構成上高集積化に適しており、3年で4倍の比率で高集積化が進められ、微細加工技術の進展に応じて大容量化・高速化が図られてきた。

DRAMは、大容量化によるビットコストの低減によって市場規模を拡大してきており、また最大の市場であるコンピュータ市場では、そのアプリケーションが大容量のメモリを要求する傾向にあることから需要は年々増加している。一方、マイクロプロセッサに代表されるシステム側の高性能化の進化も著しく、DRAMにもより一層の高速化・低消費電力化が要求されている。

当社ではこのような大容量化・高性能化の要請にこたえるべく64MビットDRAM(64MDRAM)の開発を進め、ISCC'91(1991 IEEE International SolidState Circuit Conference)において新規テストモードを内蔵した64MDRAMを発表した<sup>(1)</sup>。

さらに、より高速、低消費電力を目指し、かつJEDEC(Joint Electron Device Engineering Council)の標準仕様である外部3.3V、LVTTL(Low Voltage TTL)インターフェース、500mil幅のSOJ(Small Outline J-leaded Package)、TSOP(Thin Small Outline Package)パッケージに封止するという要求に適合した64MDRAMを開発した。本稿では、その特長及び技術について述べるとともに、電気的特性を紹介する。

表1. 設計のねらい

|          |                                                                 |

|----------|-----------------------------------------------------------------|

| 高速化      | $t_{RAC}^{*1}=50\text{ns}$                                      |

| 低消費電力化   | 1/32分割動作、 $I_{CC1}^{*2}=120\text{mA}$<br>(@ $t_C=90\text{ns}$ ) |

| 生産性向上    | 品種切替え                                                           |

|          | ポンディング切替え                                                       |

|          | 冗長構成                                                            |

| 標準化      | 256ロウ/64コラム                                                     |

|          | テストモード                                                          |

|          | 32ビット並列                                                         |

| 電源電圧     | 3.3V                                                            |

| インターフェース | LVTTL                                                           |

| パッケージ    | 500mil SOJ/TSOP II                                              |

注 \*1  $t_{RAC}$  : RACアクセス時間

注 \*2  $I_{CC1}$  : 動作時平均電源電流

## 2. 設計技術

## 2.1 設計方針

システム側からの高性能化への要求、多ビット化に代表されるような幅広い用途への対応、チップ面積増大に対する歩留りの確保、ビット数増加に対するテストコストの低減等を目的とした設計のねらいを表1に示す。

- (1) 高速化: 最近のマイクロプロセッサの動作周波数の向上に対応するため、50nsのRASアクセス時間、25nsのコラムアドレスアクセス時間を実現する。

- (2) 低消費電力化: メモリアレーの分割動作により、サイクル時間90nsで動作時の電源電流120mAを目指す。

- (3) 生産性向上: ×1から×16の語構成及びすべての動作モードをポンディング切替えとし、冗長構成は自由度の高い256ロウ/64コラムを備える。また、32ビット並列のテストモードを備えることで、テスト時間の短縮を可能とする。

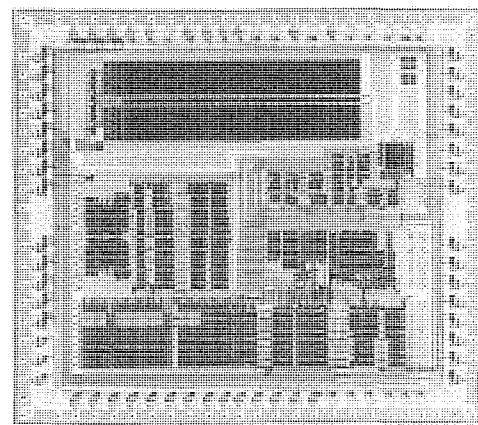

- (4) 標準化: JEDECの標準仕様である、低電圧(3.3V)のL

図1. 64MDRAMのチップ写真

図2. 64MDRAMのブロック図

図3. 64MDRAMのピン配置

VTTL インタフェースとし、500 mil の SOJ/TSOP に封止する。

## 2.2 チップ構成

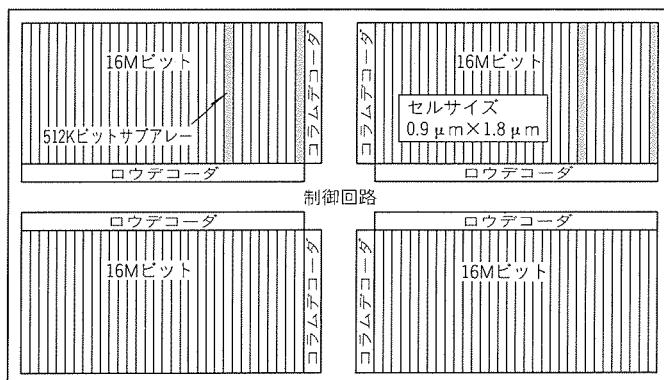

64 MDRAM のチップ写真を図1に、ブロック図を図2に示す。語構成は  $64M \times 1$  から  $4M \times 16$  までをボンディングによって切り替えている。チップサイズは、 $10.59 \times 20.6$  ( $= 218 \text{ mm}^2$ )、メモリセルサイズは  $0.9 \times 1.8$  ( $= 1.62 \mu \text{m}^2$ ) である。図に示すようにメモリセルアレーはロウデコーダ及びコラムデコーダにより、四つの  $16M$  ビットブロックに分割され、各  $16M$  ビットブロックはセンスアンプ列によって更に32個の  $512K$  ビットサブアレーに分割されている。

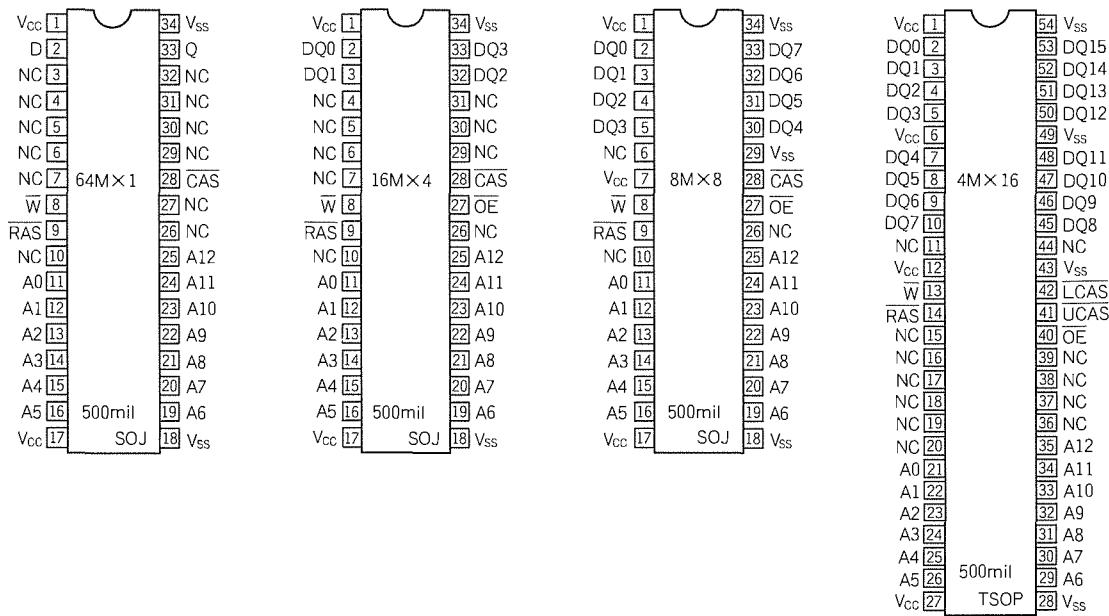

ボンディングパッドは、チップ中央部に長辺と平行な方向に配置してある。語構成及び動作モードの選択はすべてボンディングによって行われる。図3に語構成が  $\times 1$ ,  $\times 4$ ,  $\times 8$ ,  $\times 16$  のそれぞれのピン配置を示す。

## 2.3 高速・低消費電力化設計

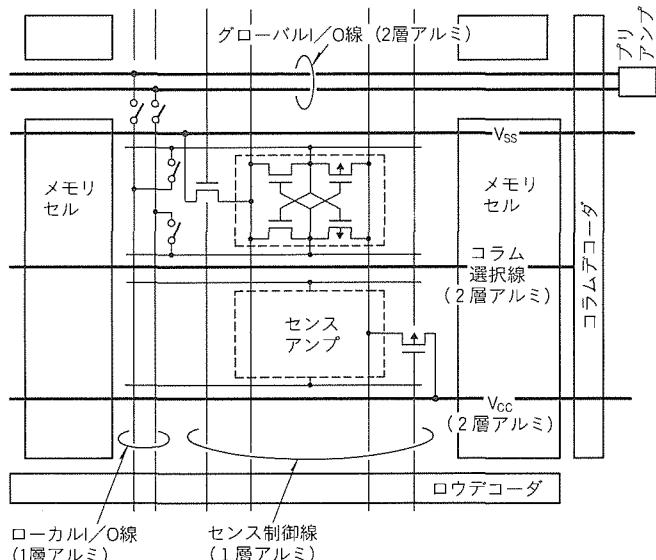

64 MDRAM の高性能化を実現する要素技術として、トランジスタの高性能化と2層アルミ配線技術による新規アレー構成の採用、メモリアレーの分割動作が挙げられる。

表2に第二世代16MDRAM<sup>(2)</sup>とのトランジスタパラメータの比較を示す。トランジスタのゲート長をPチャネル  $0.45 \mu \text{m}$ , Nチャネル  $0.4 \mu \text{m}$  に縮小し、ゲート酸化膜を  $12 \text{ nm}$  に薄膜化することによって高性能化を図った。

64 MDRAM では、チップサイズの増大に伴って信号配線長も増加し、メモリセルアレーからの読み出し信号の伝搬遅延がアクセス時間を決定する大きな要因となっている。2層アルミ配線技術を適用した新規アレー構成<sup>(3)</sup>を図4に示す。センスアンプ駆動回路を分散させてアレー内のセンスアンプの近くに配置し、センスアンプ駆動回路のための電源を2層目のA1配線でコラム選択線の間を通すことによって供給し

表2. トランジスタパラメータの比較

|                              | 64MDRAM       | 第二世代16MDRAM |

|------------------------------|---------------|-------------|

| ゲート長<br>( $\mu \text{m}$ )   | Nチャネル<br>0.4  | 0.6         |

|                              | Pチャネル<br>0.45 | 0.6         |

| ゲート酸化膜厚 $t_{\text{ox}}$ (nm) | 12            | 13          |

図4. 2層アルミ配線技術による新規アレー構成

ている。この電源線は、アレー内で1層目のA1配線によって結ばれ、網目状の配線を形成している。この構成を採ることでセンスアンプ駆動回路には安定した電源が供給され、かつセンスアンプとの距離も近くなっているので高速で安定したセンス動作が行える。センスアンプからの読み出しにも階層I/O構成を採用し、I/O線の配線容量を軽減させることにより、高速読み出しを実現した。

高速化に伴うサイクル時間の短縮は、消費電力を増加させ

る。64MDRAMでは図2に示すように、1/32の分割動作とすることでサイクル時間90nsで電源電流120mAの低消費電力を達成している。

#### 2.4 高生産性設計

パターンの微細化とチップ面積の増大に伴い、歩留り向上のための冗長回路の役割がますます重要になっている。64MDRAMでは冗長回路としてレーザプログラム方式を採用し、512Kビットサブアレーごとに2ロウ、及び16Mブロックごとに16コラムの計256ロウ/64コラムのスペアメモリセルを設け、歩留りの向上を図った。

DRAMの多岐にわたる用途に対応するため、 $\times 1$ 、 $\times 4$ 、 $\times 8$ 、 $\times 16$ 、の語構成、高速ページ、ニブル、スタティックコラムの動作モードを同一チップに搭載し、アセンブリ工程で選択可能なボンディング切替えとして生産性の向上を図った。

また、メモリ容量の増大に伴うテスト時間の増加に対応するため、32ビットの並列テストを行えるテストモードを搭載している。表3にテストモードの諸元を示す。コラムアドレスの最上位5ビット( $\times 1$ 構成時)から1ビット( $\times 16$ 構成時)がコンプレスアドレスとなっている。テストモード時の読み出しデータが32ビットすべて同じ("H"又は"L")のとき出力ピンに"H"が出力され、1ビットでもデータが異なるときには"L"が出力される。

表3. テストモード諸元

|           | 64M×1                                                  | 16M×4          | 8M×8     | 4M×16 |

|-----------|--------------------------------------------------------|----------------|----------|-------|

| 並列テストビット  | 32ビット                                                  | 32ビット          | 32ビット    | 32ビット |

| コンプレスアドレス | CA12, CA11, CA10, CA9, CA8                             | CA10, CA9, CA8 | CA9, CA8 | CA8   |

| データ入力ピン   | D                                                      | DQ3            | DQ7      | DQ15  |

| データ出力ピン   | Q                                                      | DQ3            | DQ7      | DQ15  |

| セットサイクル   | WCBR (Write CAS Before RAS)                            |                |          |       |

| リセットサイクル  | ROR (RAS Only Refresh)<br>CBR (CAS Before RAS Refresh) |                |          |       |

| 出力方式      | 2値出力 (H:一致, L:不一致)                                     |                |          |       |

表4. 64MDRAMのプロセス技術概要

|        |                                                                                                                          |

|--------|--------------------------------------------------------------------------------------------------------------------------|

| 素子分離   | 改良LOCOS                                                                                                                  |

| ウェル構成  | レトログレード型トリプルウェル                                                                                                          |

| メモリセル  | 埋め込みビット線型円筒 STACK<br>$t_{ox}(\text{eff})=5\text{nm}$ , $C_s=35\text{fF}$<br>セルサイズ: $0.9 \times 1.8 = 1.62 \mu\text{m}^2$ |

| トランジスタ | Nチャネル: $0.40 \mu\text{m}$ (LDD)<br>Pチャネル: $0.45 \mu\text{m}$<br>$t_{ox}=12\text{nm}$                                     |

| 配線構造   | ワード線: $\text{WSi}_2/\text{Poly Si} + 1\text{層 Al}$ (積層配線)<br>ビット線: $\text{WSi}_2/\text{Poly Si}$<br>コラム選択線: 2層 Al (積層配線) |

#### 3. プロセス技術

64MDRAMのプロセス技術の概要を表4に示す。メモリセルは最小設計ルール  $0.35 \mu\text{m}$  の微細加工技術を駆使することにより、 $0.9 \mu\text{m} \times 1.8 \mu\text{m}$  のセルサイズで、ビット線の上にキャパシタを形成する埋め込みビット線方式の円筒型スタックトキャパシタを実現し、 $\text{SiO}_2$ 換算で  $5\text{nm}$  のON膜を用いて  $35\text{fF}$  のキャパシタ容量を得た。

メモリセル内のビット線コンタクト、ストレージノードコンタクトなどの微細コンタクトでの接触抵抗増大を防ぐために、シリコン基板とCVD多結晶シリコン膜との界面制御技術を新たに開発し、比抵抗値  $1.5 \times 10^{-7} \Omega \text{ cm}^2$  以下の低抵抗オーミックコンタクトを実現した。

ウェル形成には、低ソフトエラー率、耐ノイズマージンを確保するために、高エネルギーイオン注入技術を用い、レトログレード型のトリプルウェル構造を採用した。

トランジスタ構造は、ゲート酸化膜厚  $12\text{nm}$ 、タンゲステンポリサイドゲート電極膜からなり、トランジスタの最小ゲート長はNチャネル、Pチャネルそれぞれ  $0.4 \mu\text{m}$ 、 $0.45 \mu\text{m}$  である。

アルミ配線は、エレクトロマイグレーション、ストレスマイグレーションに対する信頼性の観点から1層、2層ともに  $\text{AlCu}$  合金膜を用いた積層配線構造を採用した。

#### 4. 電気的特性

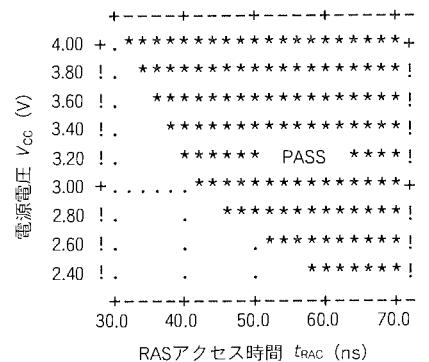

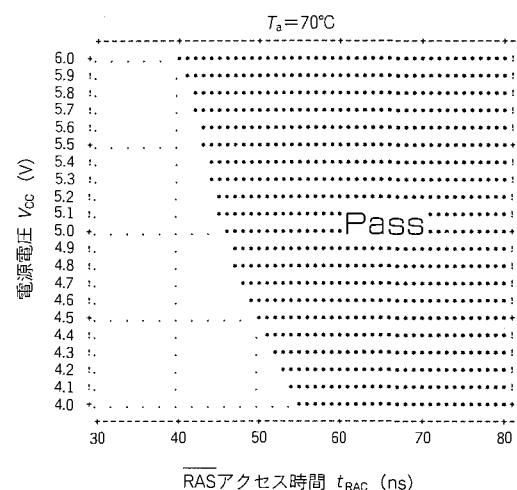

図5は周囲温度  $80^\circ\text{C}$  におけるRASアクセス時間( $t_{RAC}$ )の電源電圧( $V_{CC}$ )依存性を示すシュムーブロット図である。 $V_{CC} = 3.0\text{V}$ において  $t_{RAC} = 42\text{ns}$  の高速動作を達成しており、 $50\text{ns}$ 品として十分マージンを持っていることが分かる。また、サイクル時間  $90\text{ns}$  における動作時平均電源電流は  $97\text{mA}$ 、待機時の電源電流はCMOS入力レベルで  $28\mu\text{A}$  の値を得ている。表5に64MDR

図5. RASアクセス時間の電源電圧依存性(周囲温度  $80^\circ\text{C}$ )

表5. 64MDRAMの仕様一覧

|            |                                                                                                                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 構成         | 64M×1, 16M×4, 8M×8, 4M×16<br>(ボンディング切替え)                                                                                                                            |

| チップサイズ     | 10.59×20.6=218mm <sup>2</sup>                                                                                                                                       |

| セルサイズ      | 0.9×1.8=1.62 μm <sup>2</sup>                                                                                                                                        |

| プロセス技術     | 0.35 μm トリブルウェルCMOS                                                                                                                                                 |

| アクセス時間     | RASアクセス時間=50ns<br>コラムアドレスアクセス時間=25ns<br>(V <sub>CC</sub> =3.0V, T <sub>a</sub> =80°C)                                                                               |

| 電源電流       | 動作時平均電源電流=120mA<br>(t <sub>c</sub> =90ns, V <sub>CC</sub> =3.6V, T <sub>a</sub> =25°C)<br>待機時電源電流=0.5mA<br>(CMOS入力レベル, V <sub>CC</sub> =3.6V, T <sub>a</sub> =25°C) |

| リフレッシュサイクル | 8,192サイクル/64ms, 4,096サイクル/64ms                                                                                                                                      |

| 冗長回路       | 256ロウ/64コラム (レーザプログラム)                                                                                                                                              |

| 動作モード      | 高速ページ, ニブル, スタティックコラム<br>(×1, ×4ボンディング切替え)<br>高速ページ, スタティックコラム<br>(×8, ×16ボンディング切替え)                                                                                |

| テストモード     | 32ビット並列                                                                                                                                                             |

| パッケージ      | 500mil 34ピンSOJ, TSOPII (×1, ×4, ×8)<br>500mil 54ピンTSOPII (×16)                                                                                                      |

AMの仕様一覧を示す。

## 5. む す び

大容量化のみならず低消費電力化・多ビット化への要求にも対応した64MDRAMを開発した。0.35 μmCMOSプロセスを駆使し、高性能トランジスタと2層アルミ配線技術による新規アレー構成の採用により、RASアクセス時間50ns

を達成した。

×1, ×4, ×8, ×16の構成と高速ページ、ニブル、スタティックコラムの各動作モードを同一チップに搭載し、ボンディング切替えとしている。さらに、テストモード、冗長回路等の充実によって優れた生産性を持っている。

今回開発した64MDRAMは、16MDRAMの次世代のメモリとして幅広い用途からの要求にこたえ得るものと確信している。

## 参考文献

- (1) Mori, S., Miyamoto, H., Morooka, Y., Kikuda, S., Suwa, M., Kinoshita, M., Hachisuka, A., Arima, H., Yamada, M., Yoshihara, T., Kayano, S.: A 45ns 64Mb DRAM with a Merged Match-line Test Architecture, 1991 ISSCC Digest of Technical Papers, 110~111 (1991)

- (2) 宮元崇行, 梶本毅, 森茂, 野崎雅彦, 源城英毅: 5.0V/3.3V版第二世代16MビットDRAM, 三菱電機技報, 67, No.3, 308~311 (1993)

- (3) Miyamoto, H., Morooka, Y., Furutani, K., Yasuda, K., Kikuda, S., Tsukikawa, Y., Arima, H., Ozaki, H., Yoshihara, T.: A 32ns 64Mb DRAM with Extended Second Metal Line Architecture, ESSCIRC '93 Proceedings, 41~44 (1993-9)

# ブロック消去可能な 16Mビットフラッシュメモリ

中山武志\* 大井 誠\*

三原雅章\* 新井 肇\*\*

宮脇好和\*

## 1. まえがき

フラッシュメモリは、電気的に書換えが可能な不揮発性メモリであり、かつメモリセルサイズが小さいことから DRA M よりビットコストが下がると言われている。この特長を生かして、応用分野としてはメモリカード、HDD の置き換えなどが考えられ、今後需要が飛躍的に増大することが期待されている。

当社は 1M ビット<sup>(1)</sup>、4M ビット<sup>(2)</sup>を既に製品化し、16M ビットのプロトタイプを ISSCC91<sup>(3)</sup>で発表している。しかし、プロトタイプはチップ全体を消去する一括消去タイプであることや、電源電圧が 5V であることからユーザーにとって使いにくい仕様であった。そこで今回、ブロック消去、電源電圧 3.3V での高速アクセスタイムやユーザーの使いやすい機能を実現した 16M ビットフラッシュメモリ第一世代を開発した。

この論文では、16M ビットフラッシュメモリ第一世代の製品概要、プロセス技術、及び回路技術について紹介する。

## 2. 製品概要

今回開発した 16M ビットフラッシュメモリ第一世代の主な特長を以下に示す。

- (1) 語構成 2,097,152 語 × 8 ビット

(2) 電源電圧  $V_{CC} = 3.3V \pm 0.3V$

|             |                                                                    |

|-------------|--------------------------------------------------------------------|

|             | $V_{PP} = 12V \pm 0.6V$                                            |

| (3) アクセスタイム | 100ns/120ns/150ns (最大)                                             |

| (4) 消費電力    | 動作時 108mW (最大)<br>待機時 3.6mW (最大)<br>ディープパワーダウン時 3.6 $\mu$ W (標準条件) |

| (5) ブロック消去  | 64K バイト単位                                                          |

| (6) 書換え回数   | 10,000 回 (保証値)                                                     |

| (7) 書込み時間   | 10 $\mu$ s/バイト (最小)                                                |

| (8) 消去時間    | 0.5s/ブロック (最小)                                                     |

| (9) 機能      | 自動書込み、自動消去<br>ソフトウェアコマンド方式<br>消去サスペンド/リジューム<br>ステータスレジスタリード        |

| (10) パッケージ  | 44 ピン SOP<br>48 ピン TSOP                                            |

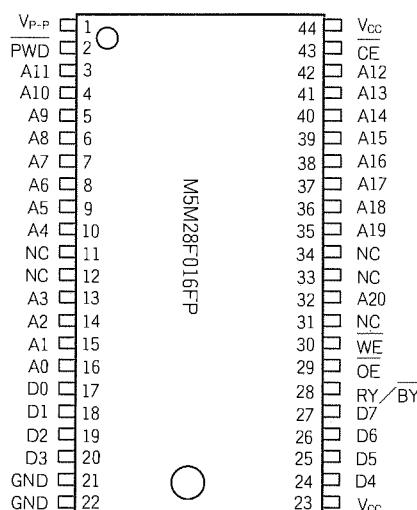

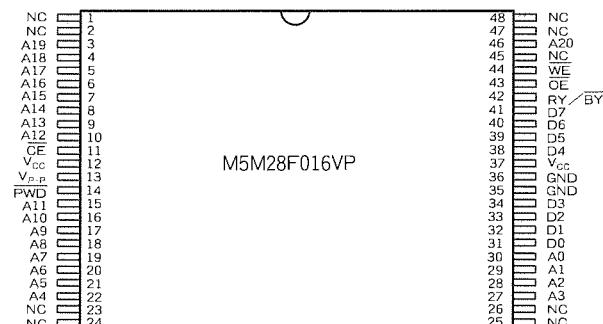

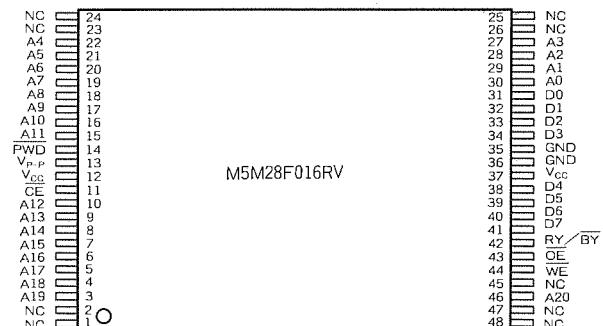

| (11) ピン配置   | 図 1 参照                                                             |

(a) 44P2A-A (SOP : FP)

(b) 48P3Q-E (TSOP : VP)

(c) 48P3Q-F (TSOP : RV)

図 1. ピン配置

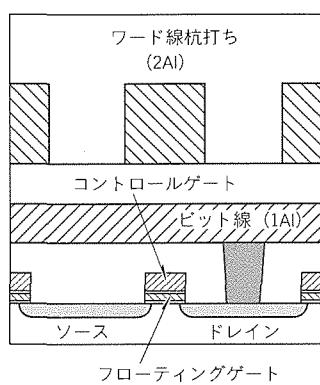

### 3. プロセス技術

図2にメモリセルの断面、表1にプロセス概要を示す。メモリセルは、現在フラッシュメモリで主流のNOR型セルを採用している。NOR型セルは書き込み動作をメモリトランジスタのドレイン近傍で発生するチャネルホットエレクトロンの注入によって行い、消去動作をフローティングゲートとソース拡散領域の重なり部分でFowler-Nordheimトンネル現象により、電子を引き抜くことによって行う。0.5 μmルールを採用して1.7 μm × 1.9 μmのメモリセルサイズを実現した。また、ポリシリコンのワード線を2層目のアルミ配線で補強して、ワード線電圧の立ち上がり速度を早め、アクセスタイムの向上を図っている。

図2. メモリセル断面

表1. プロセス概要

|          |                                               |

|----------|-----------------------------------------------|

| プロセス     | 0.5 μmルール<br>Twin Well CMOS<br>2-ポリシリコン、2-メタル |

| メモリセル    | NOR型セル<br>1.7 μm × 1.9 μm                     |

| トンネル酸化膜厚 | 10nm                                          |

| ポリ層間膜厚   | 25nm (酸化膜換算)                                  |

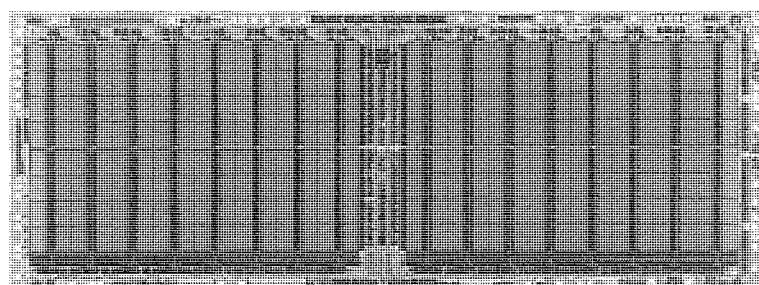

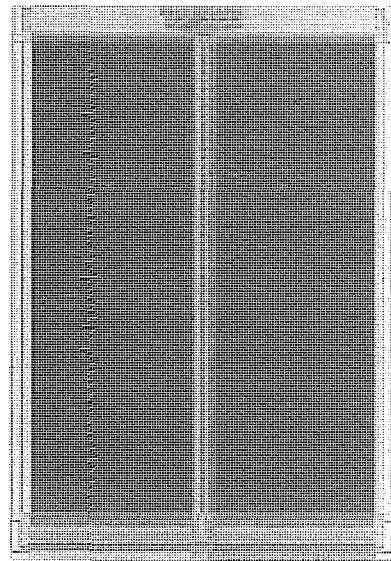

図3. チップ写真

ブロック消去タイプではワード線が複数ブロックにまたがることから、ゲートディスターブが問題になる。ゲートディスターブとは書き込み時に起る誤動作で、非選択メモリセルのフローティングゲートから電子が抜ける、又は注入される現象である。ゲートディスターブを抑えるためにフローティングゲート材質、フローティングゲートとコントロールゲートの間の層間絶縁膜の最適化を行っている。

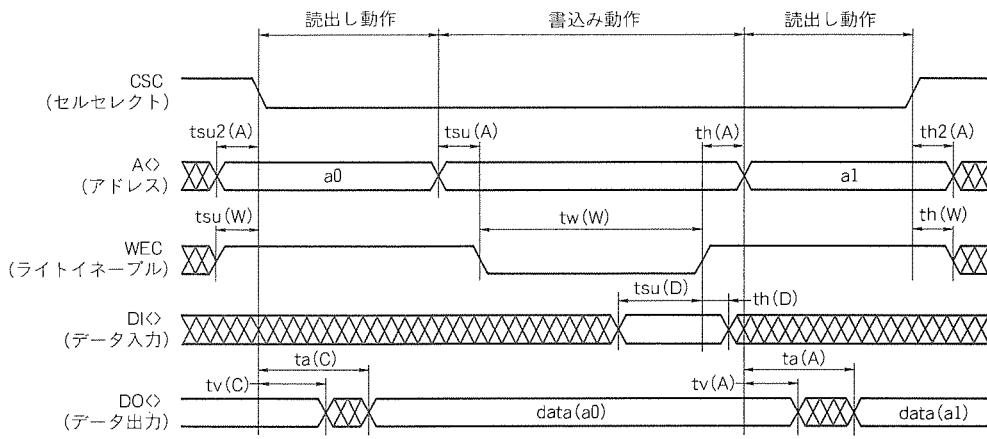

### 4. 回路技術

#### 4.1 チップ概要

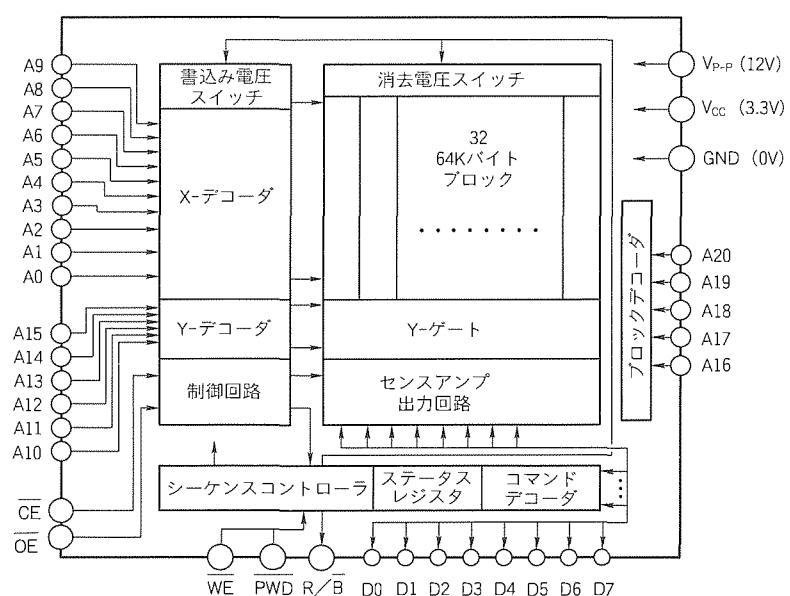

図3に16Mビットフラッシュメモリ第一世代のチップ写真を示す。チップサイズは9.3 mm × 11.5 mmを実現している。図4にブロック図を示す。メモリアレーは32のブロック(消去ブロック)に分割されており、1消去ブロックは64Kバイトからなっている。消去ブロックごとに消去電圧スイッチを配置しているため、それぞれ独立に書き込み、消去が可能になっている。外部から入力されたコマンドはコマンドデコーダに書き込まれ、デコードされてコマンドに応じた動作を開始する。ソフトウェアコマンドの一覧を表2に示す。

ステータスレジスタは、チップ内部の動作状態を外部に読み出すこと可能にする機能である。8ビットからなるレジスタのそれぞれのビットが書き込み、消去等の状態を示している。ステータスレジスタの一覧を表3に示す。

自動書き込み、自動消去はシーケンスコントローラで制御される。R/Bピンは内部の動作状況を示すピンで、“H”ならばレディー状態(書き込み、消去コマンド受付可能)、“L”ならばビジー状態(自動書き込み、又は自動消去中)を示す。PWDピンを接地レベルにすればディープパワーダウンモードになり、消費電流を1 μA以下に下げることができる。

図4. ブロック図

表2. ソフトウェアコマンド

| コマンド          | バスサイクル | 第1バスサイクル |                 |     | 第2バスサイクル |                   |                   |

|---------------|--------|----------|-----------------|-----|----------|-------------------|-------------------|

|               |        | モード      | アドレス            | データ | モード      | アドレス              | データ               |

| アレーリード        | 1      | Write    | X               | FFH | —        | —                 | —                 |

| IDコードリード      | 2      | Write    | X               | 90H | Read     | ADI <sup>*1</sup> | DDI <sup>*1</sup> |

| ステータスレジスクリード  | 2      | Write    | X               | 70H | Read     | X                 | SRD <sup>*2</sup> |

| ステータスレジスタクリア  | 1      | Write    | X               | 50H | —        | —                 | —                 |

| 消去            | 2      | Write    | Block Address   | 20H | Write    | Block Address     | D0H               |

| 消去サスペンド／リジューム | 2      | Write    | X               | B0H | Write    | X                 | D0H               |

| プログラム         | 2      | Write    | Program Address | 40H | Write    | Program Address   | Program Date      |

注 \*1 ADI=製品識別アドレス, DDI=製品識別出力コード

\*2 SRD=ステータスレジスタからの読み出しデータ

表3. ステータスレジスタ

| I/O | 出力内容                  | 出力状態定義                  |                       |

|-----|-----------------------|-------------------------|-----------------------|

|     |                       | “1”                     | “0”                   |

| 7   | 内部動作状態                | レディー状態                  | ビジー状態                 |

| 6   | 消去サスペンド状態             | 消去サスペンド状態               | 非消去サスペンド状態            |

| 5   | 消去状態                  | 消去不良                    | 消去OK                  |

| 4   | プログラム状態               | プログラム不良                 | プログラムOK               |

| 3   | V <sub>p-p</sub> 電圧状態 | V <sub>p-p</sub> 電圧低下検出 | V <sub>p-p</sub> 電圧OK |

| 2   | 未使用                   | —                       | —                     |

| 1   | 未使用                   | —                       | —                     |

| 0   | 未使用                   | —                       | —                     |

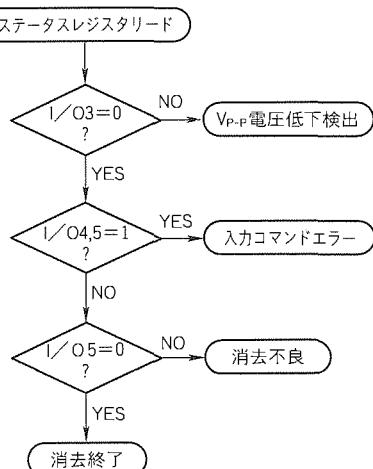

#### 4.2 自動書き込み, 自動消去機能

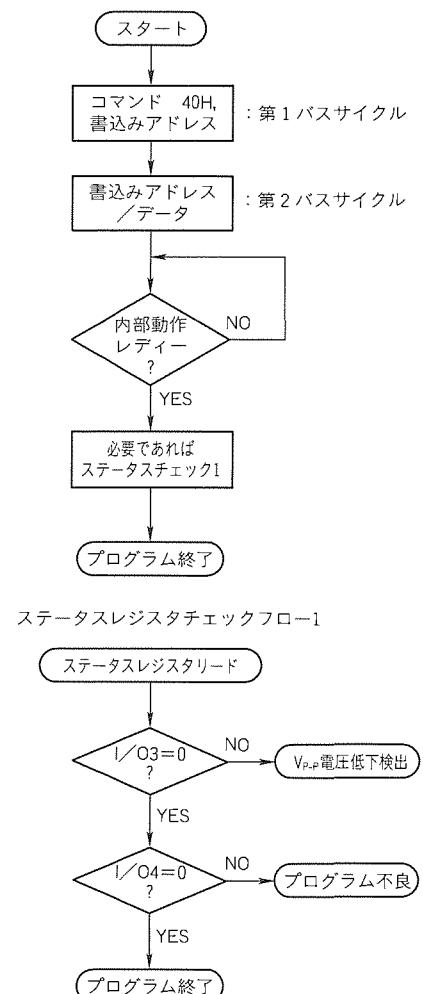

自動書き込み, 自動消去のフローチャートを図5, 図6に示す。自動書き込みは, 第1バスサイクルで自動書き込みコマンドと書き込みアドレスを入力し, 第2バスサイクルで書き込みアドレスと書き込みデータを入力することによって行う。上記動作後, チップは自動的に書き込み動作を開始する。チップが自動書き込みを終了したかどうかをR/Bピンのモニタ又はステータスレジスクリードにより, 確認することができる。自動書き込みの終了を確認した後, 必要であれば, 書き込みが正常終了したかどうかをステータスレジスタで確認することができる。

自動消去は, 第1バスサイクルで自動消去コマンドと消去ブロックアドレスを入力し, 第2バスサイクルで消去確認コマンドと消去ブロックアドレスを入力することによって行う。後は自動書き込みと同様に自動的に動作が進行し, ステータスレジスタによる動作の確認が可能である。また, 消去では自動消去中に後述する消去サスペンド動作が可能である。

こうした一連のシーケンスを論理回路で構成されたシーケンスコントローラで実現している。

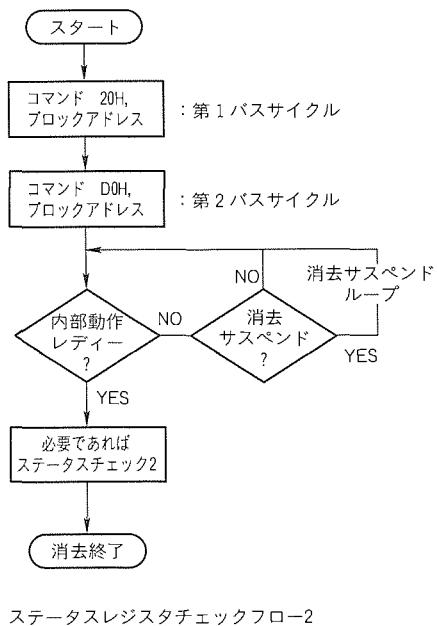

#### 4.3 消去サスペンド／リジューム機能

当社のフラッシュメモリでは16Mビットから搭載する機能の一つとして, 消去サスペンド／リジューム機能(消去中断／再開)がある。フラッシュメモリの自動消去は長い時間を要する。システムにおいて, 自動消去中に読み出しを行う要求があった場合, 従来は自動消去が終了してから読み出し動作

図5. 自動書き込みフローチャート

を行っていたが, これがシステム全体のパフォーマンスを落とす原因の一つになっていた。この不具合を解消するために, 消去サスペンド／リジューム機能を搭載した。自動消去中にマイクロコントローラから消去サスペンドコマンドが入力された場合, チップは直ちに消去動作を中断する。引き続きアレーリードコマンドを入力すれば, 消去を行っているブロック以外のブロックから読み出しを行うことができる。また, 読出し動作終了後, 消去リジュームコマンドを入力すればチッ

図6. 自動消去フローチャート

図7. 消去サスペンド/レジュームフロー

ブは先ほど消去中断したポイントから自動消去を実行する。消去サスペンド/レジュームのフローチャートを図7に示す。この機能により、消去時間の長さは見掛け上大きく改善され、システムとしてのパフォーマンス向上に寄与することができる。

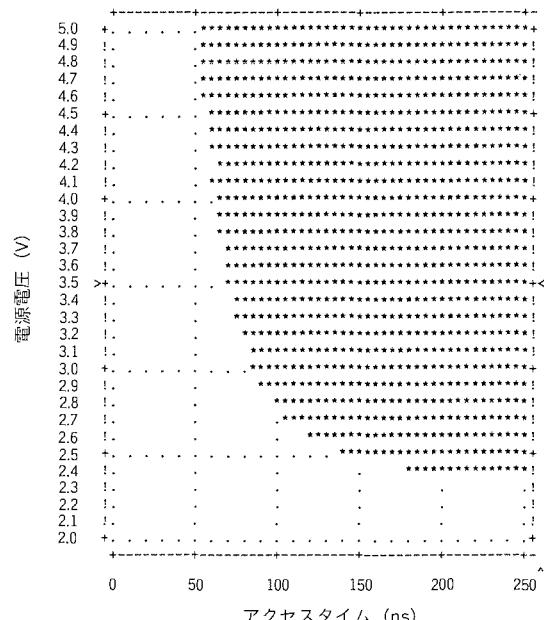

## 5. 電気特性

図8にアドレスアクセスのシムープロットを示す。測定条件は、室温で  $C_L$  (負荷容量) は 50 pF である。この結果から  $V_{CC} = 3.3 \pm 0.3$  V の範囲で 80 ns 以下であり、高速アクセスタイムが実現されていることが分かる。また、電源電圧 3.3 V の場合に重要な低電源電圧マージンも十分 (2.4 V 以上で動作) あることが分かる。

図8. アドレスアクセスシムープロット

## 6. むすび

0.5  $\mu$ m ルールのプロセスを用いて、ブロック消去可能な 16M ビットフラッシュメモリを開発した。電源電圧 3.3 V での高速アクセス、自動書き込み、自動消去、消去サスペンド/レジュームなどの高機能化を実現した。

今後、単一電源化、高速書換え等の更なる高機能化をコスト上昇を最小限に抑えつつ実現していく必要がある。

## 参考文献

- 小林和男、中島盛義、山本 誠、長田隆広：高速 1M ビットフラッシュ EEPROM, 三菱電機技報, 65, No. 4, 380 ~ 383 (1991)

- 野口健二、大川 実、山本 誠、新井 肇、伊庭智久：ブロック消去可能な高速 4M ビットフラッシュメモリ, 三菱電機技報, 67, No. 3, 312 ~ 315 (1993)

- Nakayama, T., Kobayashi, S., Miyawaki, Y., Terada, Y., Ajika, N., Ohi, M., Arima, H., Matsukawa, T., Yoshihara, T. : A 60 ns 16 Mb Flash EEPROM with Program and Erase Sequence Controller, ISSCC Digest of Technical Papers, 260 ~ 261 (1991)

# 高速QuadCAS付き第三世代4MDRAM

吹上貴彦\*

豆谷智治\*

## 1. まえがき

DRAM(ダイナミックランダムアクセスメモリ)は、汎用コンピュータ、EWS(エンジニアリングワークステーション)、PC(パーソナルコンピュータ)等のメインメモリとして主に使用されており、3年ごとに4倍の容量をもつDRAMが開発、生産してきた。4MDRAM(4MビットDRAM)は、1980年代後半に登場して以来、その生産性、価格対性能比の優位性から、現在DRAMの中で最も大量に使用されており、今後も強い需要が予測される。

また、4MDRAMに対する性能、機能等への要求としては以下の点が挙げられる。

- (1) CPU(中央演算処理装置)の高速化に伴った高速化の要求

- (2) ラップトップ、ノートブック型PC等での4MDRAMの需要が増加してきている。これらの分野での使用に伴い、電池によるバックアップを可能とする低消費電力化の要求

- (3) メモリモジュール、パリティメモリ用としてQuadCAS(コラムアドレスストローブ)機能付きDRAMの要求

以上のような要求に対して、第二世代4MDRAMをベースとしてセルフリフレッシュ機能、QuadCAS機能付き第三世代4MDRAMの開発を完了した。以下に、その技術内容の詳細について報告する。

## 2. 第三世代4MDRAMの概要

表1に第二世代4MDRAMと第三世代品の製品比較を示す。第三世代品は第二世代品と同様に、すべての製品はボンディング切替えによって生産できる設計になっており、生産性が高く、市場ニーズに素早く対応できる。さらに、ピン配置、パッケージ構成は互換性が保たれている。また、第三世代品は、QuadCAS機能、セルフリフレッシュ機能を新たに追加している。

## 3. 第三世代4MDRAMの高速化

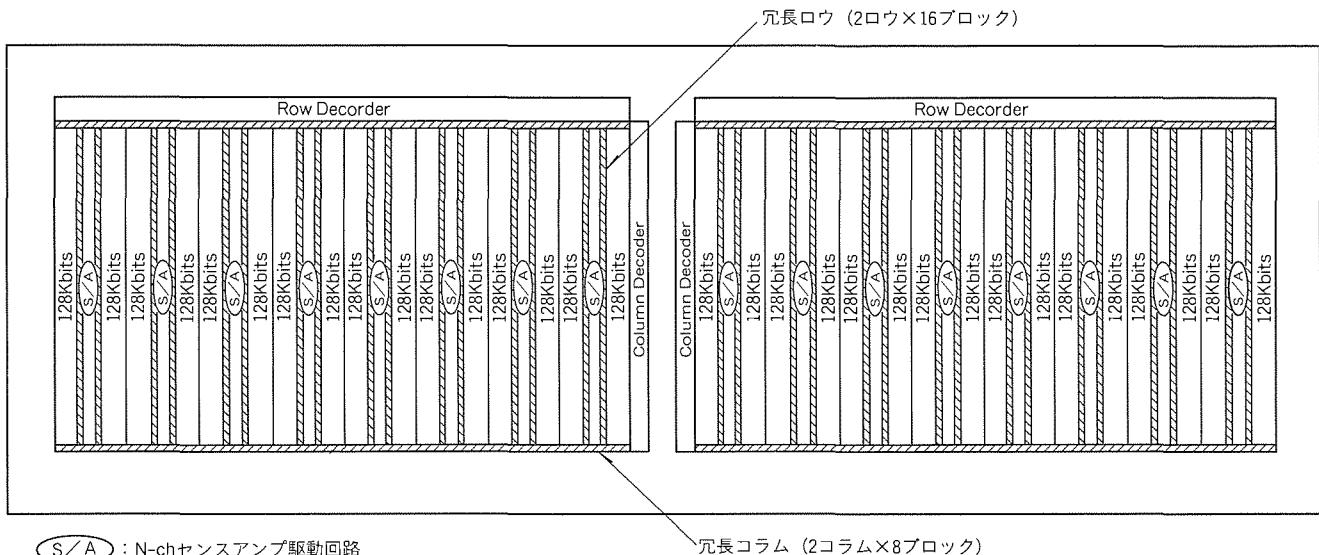

### 3.1 チップアーキテクチャ

図1にチップ写真、図2にチップアーキテクチャを示す。メモリセルアレーは、128Kビットの32個のサブアレーに分割されている<sup>(1)</sup>。ワード線はロウ(行)デコーダからチップ短辺方向に走っている。また、第一層ポリシリコンで構成されたワード線の抵抗を低減するために、9か所で第一層アルミ配線と接続している。コラム(列)方向については、コ

表1. 第二世代/第三世代4MDRAM製品規格の比較

|                                           |        | 第二世代4MDRAM                                            | 第三世代4MDRAM                                                  |

|-------------------------------------------|--------|-------------------------------------------------------|-------------------------------------------------------------|

| ビット構成                                     |        | ×1/×4<br>(ボンディング切替え)                                  | ×1/×4<br>(ボンディング切替え)                                        |

| パッケージ                                     |        | 300mil SOJ<br>350mil SOJ<br>400mil ZIP<br>300mil TSOP | 300mil SOJ<br>400mil ZIP<br>300mil TSOP                     |

| アクセスタイム                                   |        | 60/70/80/100ns                                        | (50) <sup>*1</sup> /60/70/80ns                              |

| 電源電流                                      | 動作時    | 100/85/75/65mA                                        | (125)/100/85/75mA                                           |

|                                           | スタンバイ時 | 1mA (MOS)<br>2mA (TTL)                                | 1mA (MOS)<br>2mA (TTL)                                      |

| 高速アクセスモード                                 |        | Fast Page<br>Nibble (×1のみ)<br>Static Column           | Fast Page<br>(Nibble (×1のみ)) <sup>*2</sup><br>Static Column |

| ライトペービット機能<br>(×4のみ)                      |        | あり                                                    | あり <sup>*2</sup>                                            |

| 4CAS機能 (×4のみ)                             |        | なし                                                    | あり                                                          |

| セルフリフレッシュ機能                               |        | なし                                                    | あり                                                          |

| ローパワー版<br>リフレッシュ電流<br>( $t_{ref}=128ms$ ) |        | 200 μA                                                | 150 μA                                                      |

| セルフリフレッシュ電流                               |        | なし                                                    | 150 μA                                                      |

注 \*1 50ns品は開発中

\*2 市場の状況によって開発を検討

図1. 第三世代4MDRAMのチップ写真

図2. チップアーキテクチャ

ラムデコーダがチップ中央部両側に配置され、第二層アルミ配線を用いたコラム選択線によってデータを選択する。各サブアレーの間には、センスアンプが配置されているため1本のビット線に接続されるメモリセルは64個のみとなり、センスの高速化を図ることができる。以上の構成は、第二世代4MDRAMと同一であるが、第三世代品は、更にセンスの高速化を図るために、センスアンプの中央部に(図2の丸印部分)Nチャネルセンスアンプ駆動回路を追加した<sup>②</sup>。なお、第二世代品では、Nチャネルセンスアンプ駆動回路はロウデコーダと反対側のみに配置されている。この方式を採用することにより、センス時間を短縮することが可能となり、アクセス時間の高速化が実現できた。

### 3.2 プロセス技術

第三世代4MDRAMで用いたプロセスパラメータを表2に示す。回路全体の高速化を図るために、Nチャネルトランジスタのゲート酸化膜厚を17 nm (= 170 Å)と薄膜化することにより、トランジスタの高性能化を実現した。

また、第三世代品は微細化プロセスの導入により、大幅に配線容量が低減されたことも高速化に寄与している。メモリセルは、キャパシタ絶縁膜の膜厚を薄膜化し、さらにSN(ストレージノード)膜厚を厚膜化させることにより、チップ縮小化によるメモリセル容量減少を抑えており、第二世代品と同程度のメモリセル容量を確保した。

図3にRASアクセス時間の電源電圧( $V_{CC}$ )依存性を示す。周囲温度70°C、 $V_{CC} = 4.5$  Vで50 nsというRASアクセス時間の高速化を実現した。

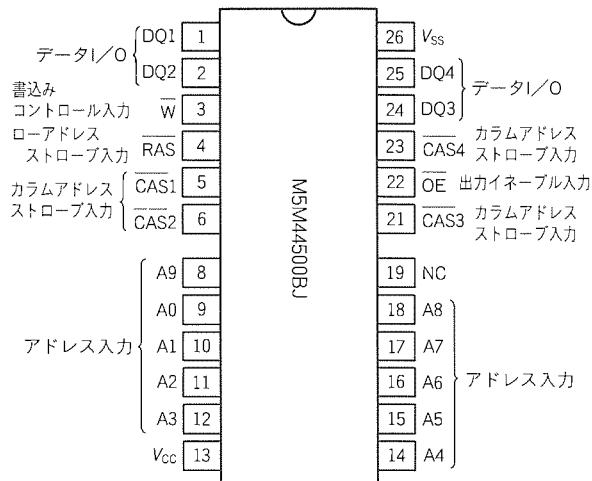

## 4. 新機能

### 4.1 QuadCAS機能DRAM

図4にQuadCAS機能DRAMの外形を示す。従来、4MDRAMの×4ビット構成(1Mワード×4ビット)品は

表2. 第二世代/第三世代4MDRAMのプロセス比較

|                 | 第二世代4MDRAM  | 第三世代4MDRAM   |

|-----------------|-------------|--------------|

| 分離              | シングルLOCOS   | シングルLOCOS    |

| ウェル             | 二重ウェル       | 二重ウェル        |

| メモリセル構造         | スタッカセル      | スタッカセル       |

| トランジスタ $t_{ox}$ | 18 nm       | 17 nm        |

| 内部配線            | 4ポリ2アルミ     | 4ポリ2アルミ      |

| 設計ルール           | 0.7 $\mu$ m | 0.65 $\mu$ m |

図3. RASアクセス時間

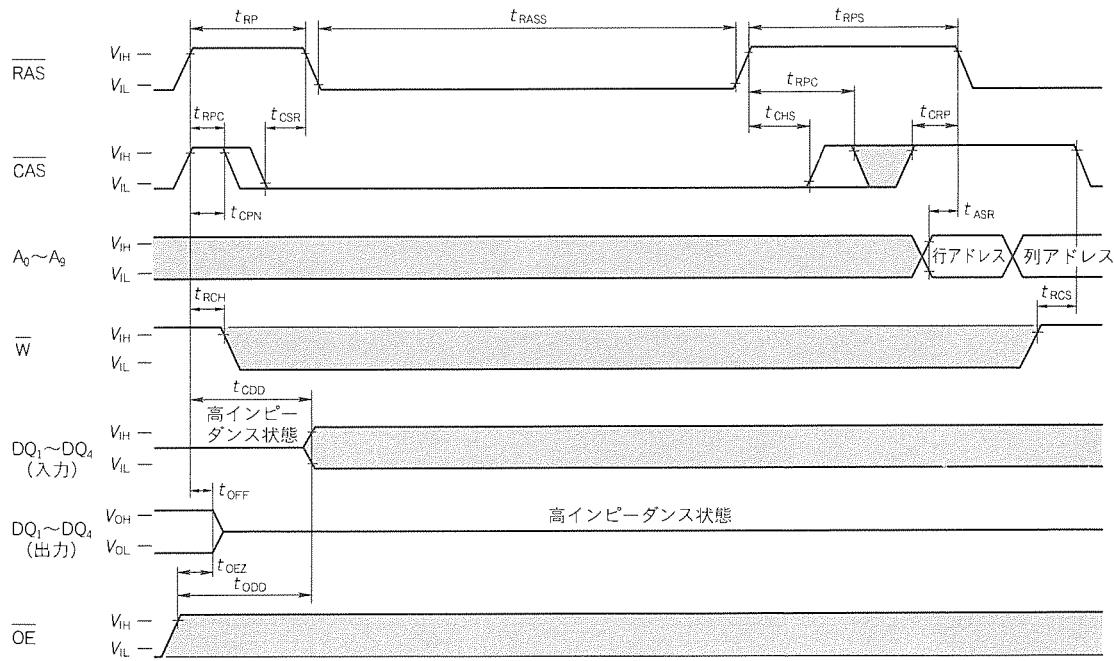

CASピンが一つであり、四つの入出力ピンに対して、同時に書込み、読み出しを行っていた。そのため、四つの入出力データを個々に制御することができなかった。QuadCAS機能は、四つの入出力データ各々に対応するCASが存在し、四つの入出力データを任意に書き込み、読み出しを可能にした。図5にQuadCAS機能動作例を示す。時刻  $t = T_0$ において  $\overline{RAS} = L$  (活性化状態)、 $t = T_1$  時に  $\overline{CAS}1 \sim 4 = L$ 、 $\overline{WE} = L$  になり、四つのDQ1～4(入出力ピン)に同時にデータが書き込まれる。続いて、時刻  $t = T_2$ において  $\overline{CA}$

図4. QuadCAS機能DRAMピン接続図

図5. QuadCAS機能タイミング

図6. セルフリフレッシュタイミング

$\overline{S}1, 2 = L, \overline{CAS}3, 4 = H$  (非活性化状態),  $\overline{OE} = L$  にすることによって DQ 1, 2 は、出力データ “0” が読み出されるが、DQ 3, 4 はハイインピーダンス状態となる。さらに、時刻  $t = T_3$  において  $\overline{CAS}1, 2 = H, \overline{CAS}3, 4 = L, \overline{WE} = L$  にすることにより、DQ 3, 4 に入力データ “1” が書き込まれるが、 $\overline{CAS}1, 2$  は非活性化状態であるため DQ 1, 2 にはデータ “1” が書き込まれない。そのため、時刻  $t = T_4$  において出力データとして DQ 1, 2 は “0”, DQ 3, 4 は “1” が読み出される。以上のように QuadCAS 機能は、高速ページモード ( $RAS = L$ ) においても、四つの任意の入出力ピンに対して書き込み、読み出しを可能にする。

#### 4.2 セルフリフレッシュ機能

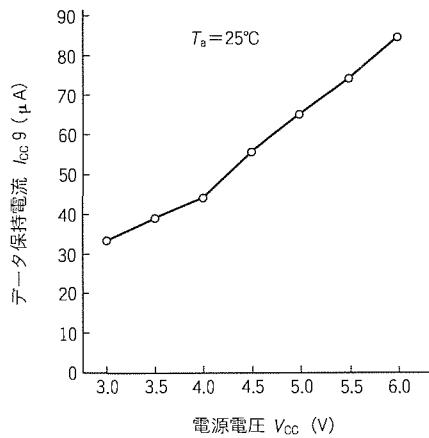

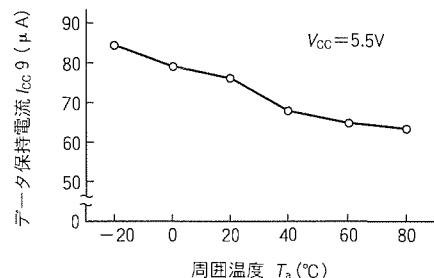

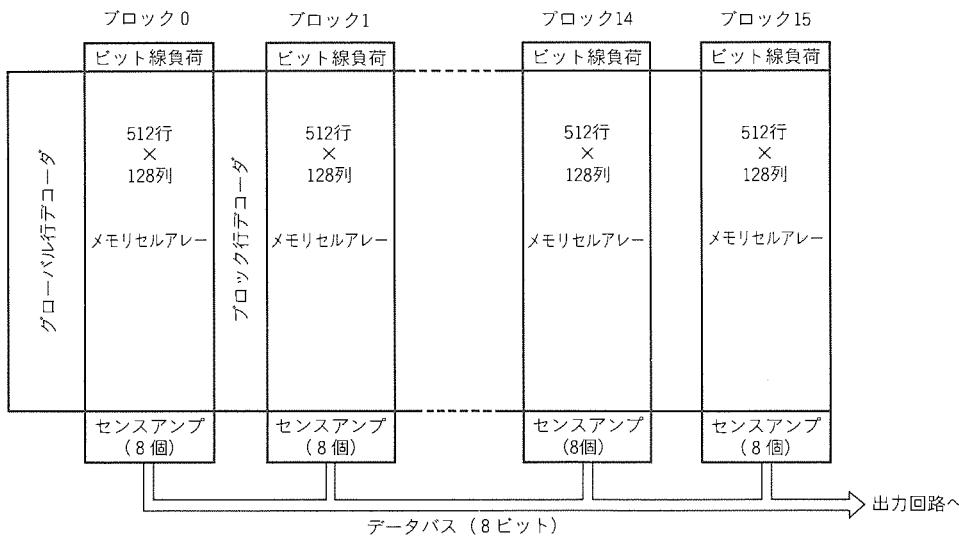

第三世代4 MDRAMは、バッテリバックアップシステム用メモリとして、より一層の低消費電力化を可能にするCB-Rセルフリフレッシュ機能を備えている。セルフリフレッシュ機能は、リフレッシュアドレス及びリフレッシュタイミングを内蔵するタイマにより、生成させるものである。図6にセルフリフレッシュタイミングを示す。図7にセルフリフレッシュ時のデータ保持電流 ( $I_{CC9}$ ) の電圧依存性、図8に  $I_{CC9}$  の温度依存性を示す。

$V_{CC} = 5.5V$ においてもデータ保持電流は  $80\mu A$  以下を示し、バッテリバックアップシステム用メモリに適合した特性をもっている。

#### 5. 信頼性

第三世代4 MDRAMのデバイス構造は、これまで実績のある第二世代品のスタックトキヤバシタメモリセル、2層ア

図7. セルフリフレッシュ電流の電圧依存性

ルミ配線プロセスを採用している。また、微細化プロセスを導入したにもかかわらず、第三世代品のメモリセル容量は、第二世代品と同レベルであるため、第三世代品のソフトエラー率は第二世代品同様に低く抑えられ、高信頼性が実現できた。

## 6. む す び

高速化・低消費電力化・多機能化という市場のニーズに対して、第三世代4 M DRAMを開発した。センス時間の高速化、トランジスタの高性能化等によってアクセス時間の高速

図8. セルフリフレッシュ電流の温度依存性

化を実現した。また、セルフリフレッシュ機能を備えることにより、バッテリバックアップシステム用メモリとして十分な低消費保持電流を実現した。さらに、QuadCAS機能の追加により、高速ページモードにおいても任意の入出力ピンにデータの書き込み、読み出しが可能になり、メモリモジュール、パリティメモリとして容易に使用できる。

## 参 考 文 献

- (1) 熊野谷正樹、飛田洋一、長友正男：第二世代4 M ビット DRAM，三菱電機技報，65，No.7，697～702 (1991)

- (2) 富上健司、豆谷智治、長山安治、長友正男：4 M ビットバイトワイド／ワードワイド DRAM，三菱電機技報，67，No.3，316～319 (1993)

# 高速 1 Mビット CMOS スタティックRAM

樺原洋次\* 田原良昭\*\*

坂口定則\* 南 ふゆみ\*

秋山義雄\*\*

## 1. まえがき

CMOS スタティック RAM (SRAM) は、他の MOS メモリと比較してアクセスタイムが高速であり、低電流でデータが保持できるという特長がある。このうち、低電力化に着目したものが低消費電力 SRAM であり、アクセスタイムの高速化を追求したものが高速 SRAM である。高速 SRAM の用途としては、ワークステーション及びパーソナルコンピュータのキャッシュメモリ、スーパコンピュータ及び大型コンピュータのメインメモリなどが挙げられる。

キャッシュメモリに要求されるのは、アクセスタイム 15 ns 以下の高速性、及び  $\times 8$  以上の広い語構成などであり、容量的にはそれほど大きいものは必要とされていなかったため  $8\text{K} \times 8$ 、 $32\text{K} \times 8$  等の高速 SRAM が使用されてきた。しかし、近年キャッシュメモリの容量増大に伴い、1 M クラスの大容量品の要求も高まってきている。一方、メインメモリには  $\times 1$ 、 $\times 4$  等の語構成のものが用いられ、1 M、4 M 等の大容量化が要求される半面、これまでにはアクセスタイムについては 25 ns 程度とそれほど高速化が必要とされていなかった<sup>(2)(3)</sup>。しかしながら、スーパコンピュータ等の著しい性能向上に伴い、近年はメインメモリの分野においても 15 ns クラスの高速品の要求が強まってきている。

このような要求を踏まえて、最大アクセスタイム 15 ns の 1 M ビット CMOS SRAM を開発した。本稿では 1 M ビットという大容量で 15 ns の高速アクセスタイムを実現するために用いた設計技術、製造技術、及び得られた電気的特性を紹介する。

## 2. 開発のねらい

### (1) 高速アクセス時間

15 ns 品の供給に支障が出ないように、標準条件でのアクセスタイムが 10 ns 程度となるようにする。

### (2) 語構成

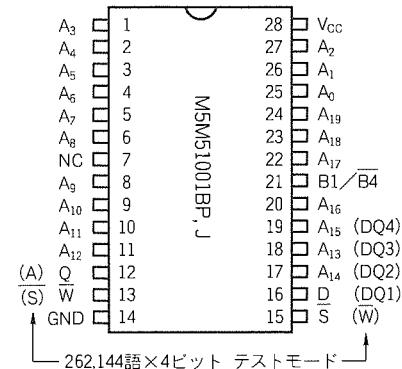

以下の 3 品種を 1 枚のマスクの差し替えのみで作り分ける。

- 1 M 語  $\times$  1 ビット (M5M51001B)

- 256 K 語  $\times$  4 ビット (M5M51004B)

- 128 K 語  $\times$  8 ビット (M5M51288B)

上記 3 品種のピン配置を図 1 に示す。

### (3) パッケージ

パッケージは各品種とも 2 種類を用意する。

• 400 mil 幅 28 ピン DIP

• 400 mil 幅 28 ピン SOJ

(M5M51001B/M5M51004B)

• 400 mil 幅 32 ピン DIP

• 400 mil 幅 32 ピン SOJ

(M5M51288B)

ただし、チップサイズを 300 mil 幅パッケージに収納可能な大きさとすることにより、300 mil 幅パッケージにも対応可能なようになる。

## 3. 設計技術

### 3.1 チップ構成

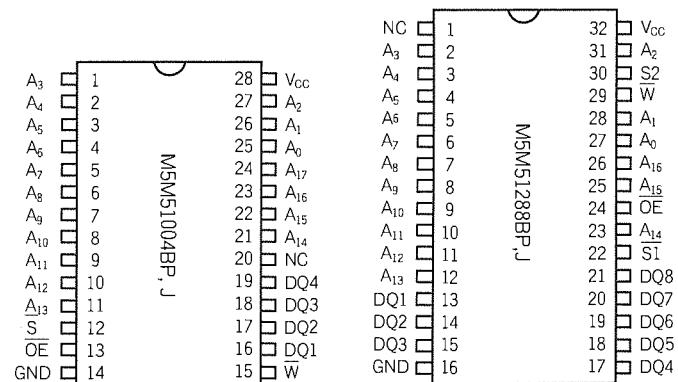

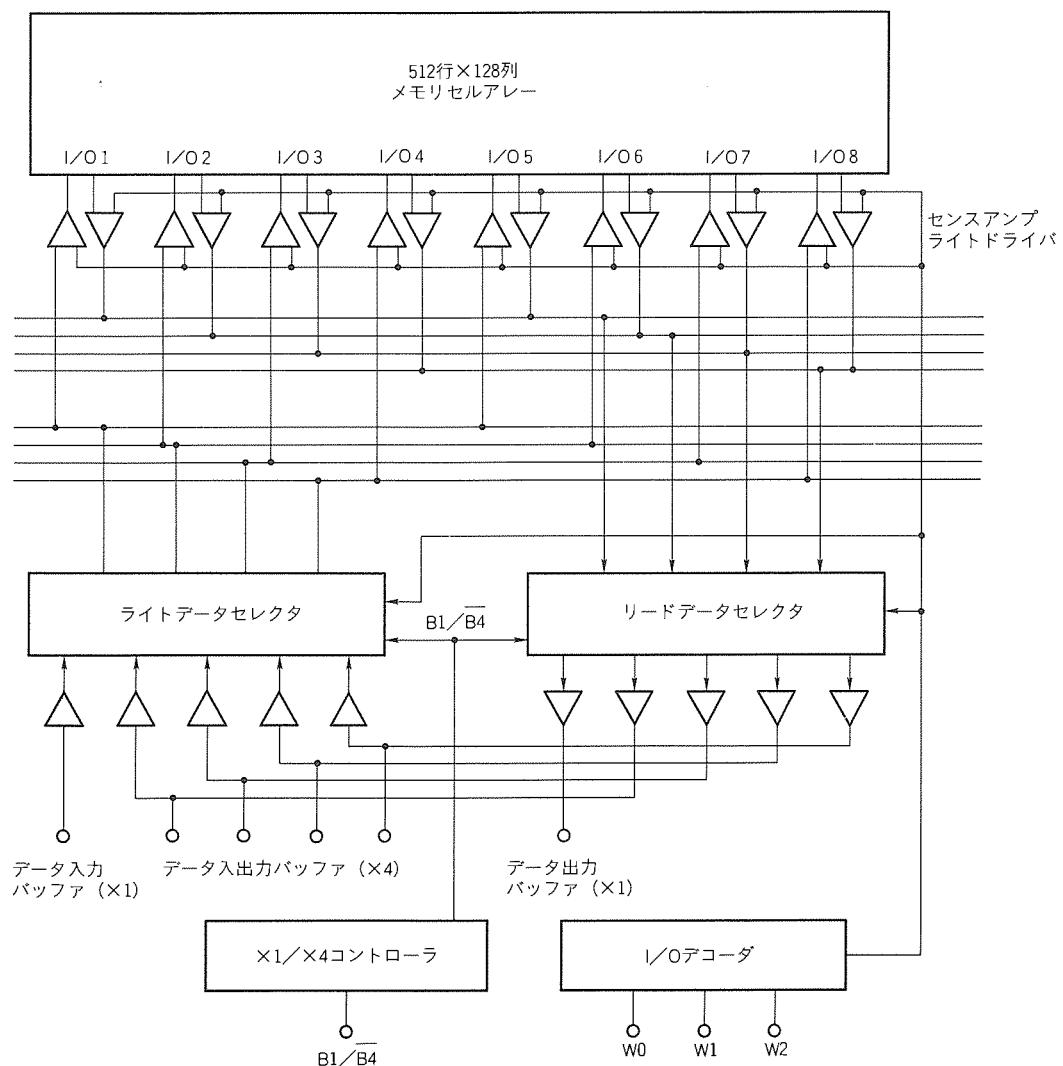

図 2 に M5M51001B/M5M51004B/M5M51288B のブロック構成を示す。メモリセルアレーは全体で 512 行  $\times$  2,048 列から構成され、これらをワード線方向に 16 ブロックに分割している。ブロック分割はアクセスタイムの高速化

(a)

(b)

(c)

図 1. ピン配置

図2. ブロック構成

図3. ワード線選択回路

図4. ATD信号発生回路

のために不可欠であり、これによってワード線長を短くすることができ、ワード線遅延の増大を抑えている。1ブロックは512行×128列からなっているが、さらに512行×16列からなる8個のサブブロックに分割され、それにセンスアンプを配置して128K語×8ビットに対応させている。また、256K語×4ビットの場合は8個のセンスアンプのうち4個のみを、1M語×1ビットの場合は8個のうち1個のみを動作させることにより、センスアンプの増加による不要な電流増加を防いでいる。

このようなセルアレーの中から任意のメモリセルを選択するためのアドレス入力は四つのグループ(X, Y, Z, W)に分かれており、X, Y, Zはそれぞれ行選択、列選択、ブロック選択に使用し、WはM5M51001B/M5M51004Bでサブブロックを選択するために使用される。

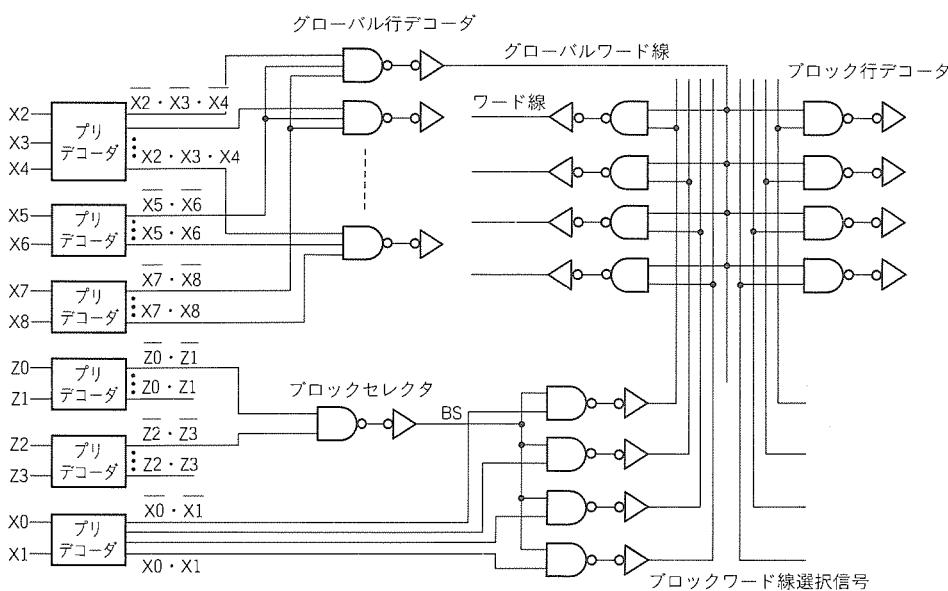

### 3.2 分割ワード線選択方式

ワード線選択の方法として図3に示すような分割ワード線選択方式を採用した。この方式では上位の行アドレス(X2~X8)はグローバル行デコーダでプリデコードされ、グローバルワード線を活性化する。一方、下位の行アドレス(X0~X1)は、ブロックアドレス(Z0~Z3)をプリデコードして作られたブロックセレクタ信号(BS)と論理積がとられ、ブロックワード線選択信号を活性化する。ワード線の

選択はグローバルワード線とブロックワード線選択信号の論理積によってなされるため、一度に活性化されるワード線は1ブロック分のみなので、カラム電流は大幅に低減できる。また、ワード線がポリシリコンで構成されるのに対し、グローバルワード線、ブロックワード線選択信号ともアルミニ配線で構成されるので、高速化にも役立っている。

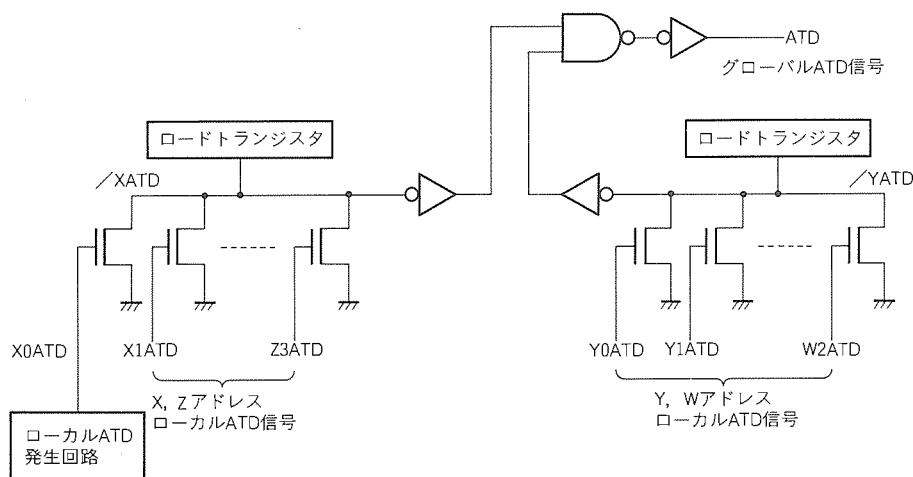

### 3.3 ATDと高速化技術

高速化を図るためにATD(Address Transition Detector)回路を用いて各ノードのプリチャージ及びイコライズを行っている。ATDが有効に機能するためにはアドレス変化に対応して迅速にATDパルスを発生させる必要があるが、1Mクラスの大容量品になるとチップサイズの増大によって配線長が増加し、寄生容量の増大のために負荷が重くなりATD波形が鈍る可能性がある。これを防ぐため、図4に示すようにXアドレス系、Zアドレス系のローカルATD信号とYアドレス系、Wアドレス系のローカルATD信号を別個のグローバルATD回路で集め、その論理積によって最終的なATD信号を生成している。このように、ローカルATD回路の位置が比較的接近しているアドレスのみで

グローバルATD信号を生成しているため、/XATD、/YATD信号の配線長が縮小でき、ATD波形の鈍りを最小限に抑えている。

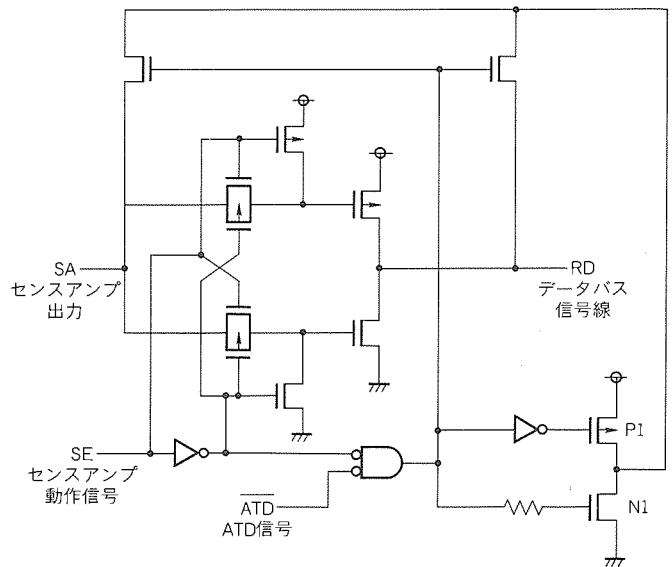

図5. データバス信号線イコライズ回路

図6. 語構成可変方式 (M5M51001B)

ATD 信号は主にリード系信号線のイコライズに使用されているが、特に重要なのがリードデータバス信号線のイコライズである。リードデータバスは各センスアンプの出力を出力バッファに伝えるための配線であり、多くのセンスアンプ出力のドレインにつな(繋)がる上、チップ長辺を走り、極めて長くなる。そのため、寄生容量が大きくなり、ここでのデータ遅延時間は無視できない。遅延時間を短くする対策としては、一般にリードデータバスを ATD 信号で中間電位にプリチャージするという方法がよく用いられるが、ここで問題となるのがプリチャージの方法である。なぜなら、リードデータバスは容量が重いため、容量の軽いノードとイコライズしても十分中間電位にならないことがあるからである。このような問題を解決するために、図 5 に示すようなデータバス信号線イコライズ回路を使用した。ATD 信号入力時には P チャネルトランジスタ P1 と N チャネルトランジスタ N1 が同時にオンし、リードデータバス信号線はセンスアンプ出力と同時に強力なトランジスタ P1, N1 によって強制的に中間電位にイコライズされる。したがって、データバス信号線には瞬時にセンスアンプ出力のデータが伝達し、データ遅延を最小限に抑えている。

### 3.4 語構成可変機能

M5M51001B では図 6 に示すような回路構成により、1 M 語 × 1 ビット構成を外部信号で 256 K 語 × 4 ビット構成に切替え可能になっている。これは 1 M 語 × 1 ビット構成を 256 K 語 × 4 ビット構成に変えることで、テスト時間の短縮を図るものである。実際の適用としては、21 ピンの B1/

B4 ピンを “L” にすることで 256 K 語 × 4 ビット構成のデバイスとして動作する。このピンは内部でプルアップされており、信号を与えなければ 1 M 語 × 1 ビット構成のデバイスとして動作する。

### 4. プロセス技術

表 1 に高速 1 M ビット SRAM の主要なプロセス技術を示す。今回用いたプロセスは N 型基板ツインウェル・3 層ポリシリコン・2 層アルミ配線の  $0.6 \mu\text{m}$  ルール CMOS プロセスである。ポリシリコン配線については、第一ポリシリコンは  $\text{WSi}_x$  ポリサイドで形成し、ゲート電極及びワード線として使用している。また、第二ポリシリコンはメモリセルの電源線として使用し、第三ポリシリコンには高抵抗専用の薄膜ポリシリコンを採用している。アルミ配線に関しては、アルミの層間膜を十分に平たん(坦)化することにより、第二アルミの配線ピッチを従来と比較して約  $1/2$  にすることが可能となり、第二アルミ配線をビット線として用いている。これによって、メモリセルの接地線を低抵抗の第一アルミ配線にすることが可能となり、メモリセルの安定化動作に寄与している。また、メモリセルの素子分離にはバーズピークを低減した LOCOS (Local Oxidation of Silicon) 法を採用している。トランジスタには LDD (Lightly Doped Drain) 構造が用いられ、ゲート長を短くしながら信頼性の高いトランジスタを形成している。これにより、N チャネルトランジスタ、P チャネルトランジスタともゲート長を  $0.6 \mu\text{m}$  と微細化することが可能となり、高駆動能力とゲート容量の低減が図られアクセスの高速化に寄与している。

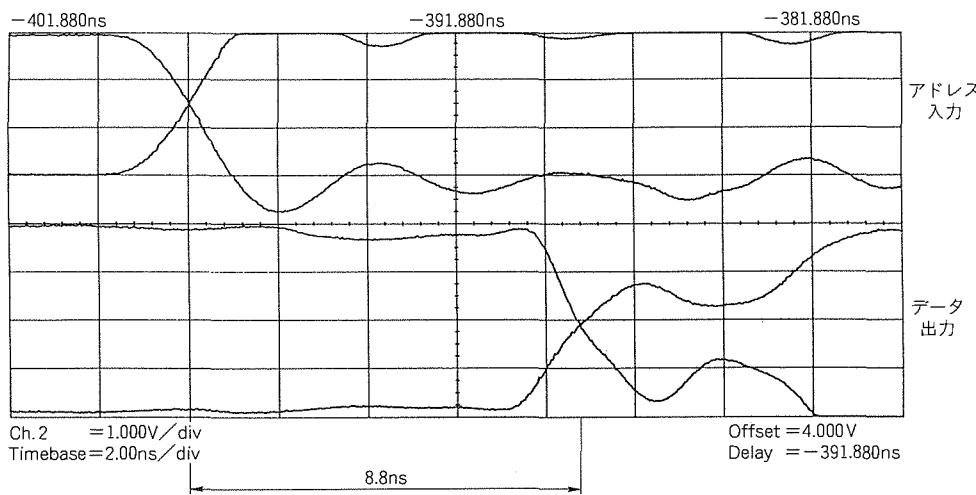

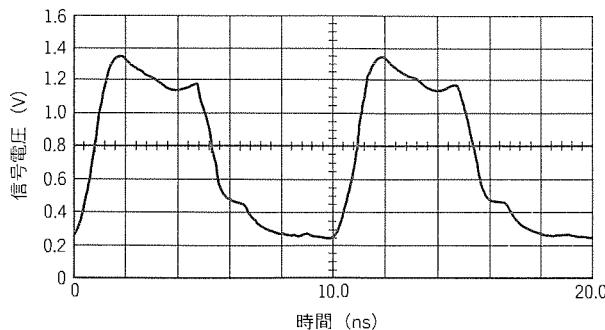

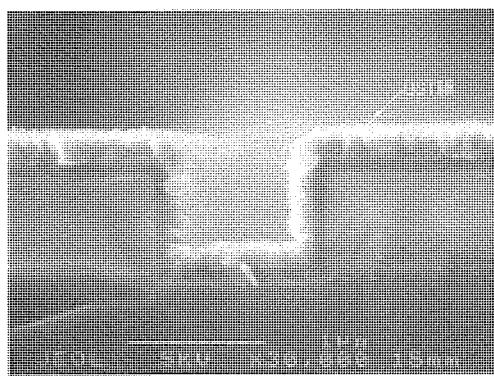

### 5. 電気特性

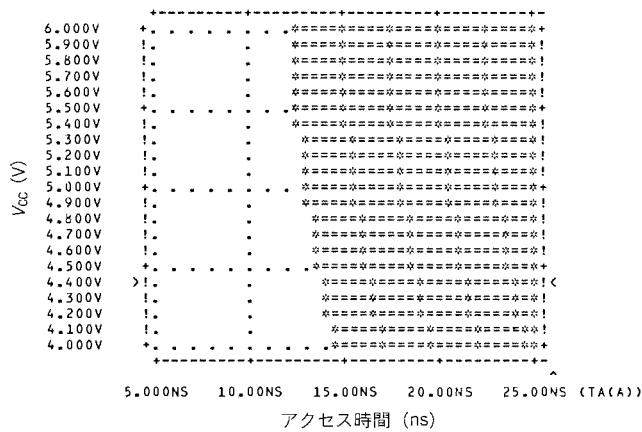

図 7 に電源電圧  $4.5\text{V}$ 、室温時の高速 1 M ビット SRAM の出力波形を示す。これより標準条件でのアドレスアクセス時間は  $9\text{ ns}$  以下が達成されていることが分かる。また、チップセレクトアクセス時間も同程度である。図 8

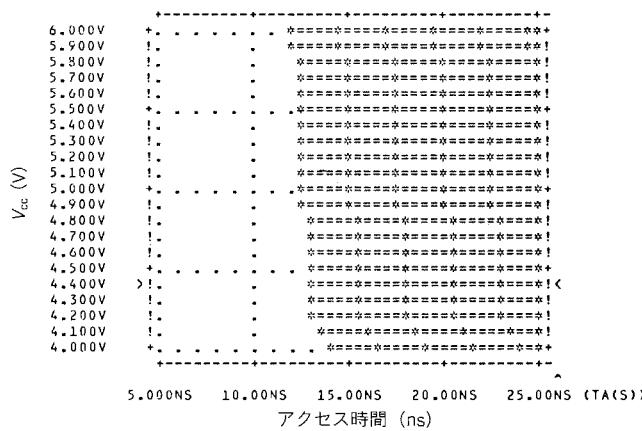

は  $T_a = 75^\circ\text{C}$  での  $V_{CC}$  対アドレスアクセス時間の、図 9 は同じく  $T_a = 75^\circ\text{C}$  での  $V_{CC}$  対チップセレクトアクセス時間のシミュレーションプロットであり、 $V_{CC} = 4.5\text{V}$  の最悪条件でアドレスアクセス時間は  $13.5\text{ ns}$ 、チップセレクトアクセス時間は  $13.0\text{ ns}$  であることが分かる。M5M51288B の動作時における  $I_{CC}$  (動作時の電源電流) のサ

表 1. プロセス技術

|        |                                                                                                                                    |

|--------|------------------------------------------------------------------------------------------------------------------------------------|

| プロセス方式 | $0.6 \mu\text{m}$ CMOS<br>N 基板ツインウェル<br>3 層ポリ 2 层 Al<br>$\text{WSi}_x$ ポリサイド<br>LDD 構造 ( $\text{LSi} = 0.6 \mu\text{m}$ )<br>LOCOS |

|--------|------------------------------------------------------------------------------------------------------------------------------------|

図 7. 出力波形 ( $V_{CC} = 4.5\text{V}$ , 室温)

図8. アドレスアクセス時間のシュムープロット

( $T_a=75^{\circ}\text{C}$ )

図9. チップセレクトアクセス時間のシュムープロット

( $T_a=75^{\circ}\text{C}$ )

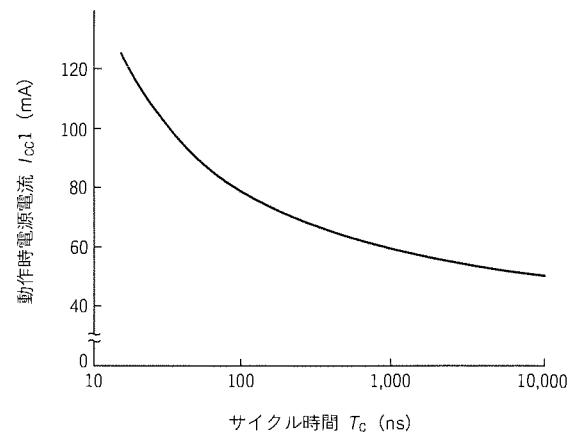

イクル時間依存性を図10に示す。サイクル時間15ns,  $V_{\text{CC}}=5.5\text{V}$  の最悪条件でも125mAと小さな値となっている。また、MOSレベル入力時のスタンバイ電流は、 $T_a=75^{\circ}\text{C}$ ,  $V_{\text{CC}}=5.5\text{V}$  の最悪条件で $10\mu\text{A}$ 以下と小さい値となっており、低消費電力版(Lバージョン)にも対応可能である。パッケージは、400mil DIP, SOJの2種類を用意しているが、300milパッケージにも対応する予定である。高速1MビットSRAMの性能一覧を表2にまとめる。

## 6. むすび

0.6 $\mu\text{m}$ 設計ルールの3層ポリシリコン、2層アルミ構造のツインウェルCMOSプロセスを用いて最大アクセス時間15nsの1MビットCMOS SRAM M5M51001B(1M×1), M5M51004B(256K×4), M5M51288B(128K×8)を開発した。信頼性を損なうことなく達成した高性能トランジスタ技術と変形分割ワード線方式等の高速回路技術を導入することによって、1Mビットという大容量でアクセ

図10. 電源電流特性 ( $V_{\text{CC}}=5.5\text{V}$ , 室温)

表2. 高速1MビットSRAMの性能一覧

|               |                                                                                                 |

|---------------|-------------------------------------------------------------------------------------------------|

| 語構成           | 1M語×1ビット (M5M51001B)<br>256K語×4ビット (M5M51004B)<br>128K語×8ビット (M5M51288B)<br>3層ポリシリコン 2層アルミ CMOS |

| プロセス          | 0.6 $\mu\text{m}$                                                                               |

| デザインルール       | 5V単一                                                                                            |

| 電源電圧          | TTL                                                                                             |

| 出力レベル         | 15ns (最大)                                                                                       |

| アドレスアクセス時間    | 15ns (最大)                                                                                       |

| チップセレクトアクセス時間 | 15ns (最小)                                                                                       |

| サイクル時間        | 140mA (最大)                                                                                      |

| 動作時電源電流       | 40mA (最大)                                                                                       |

| スタンバイ時電源電流    | 1mA (最大) (Lバージョンは $10\mu\text{A}$ )                                                             |

| TTLレベル入力時     | 28ピン400mil DIP, SOJ<br>(M5M51001B/51004B)                                                       |

| MOSレベル入力時     | 32ピン400mil DIP, SOJ<br>(M5M51288B)                                                              |

| パッケージ*        | 注 *300milパッケージにも対応予定                                                                            |

注 \*300milパッケージにも対応予定

タイム15nsという高速性能を実現することができた。

今後も高速SRAMに対する大容量化・高速化・多ビット化の要求にこたえて、更に次世代の高速SRAMの開発を推進する予定である。

## 参考文献

- 一瀬勝樹, 河野芳雄, 篠原尋史, 村上修二, 船越也寿宏: 高速256KビットCMOSスタティックRAM, 三菱電機技報, 61, No.4, 329~332 (1987)

- 菅野雅直, 和田知久, 杠幸二郎, 向井孝夫, 河野芳雄: 高速1MビットCMOSスタティックRAM, 三菱電機技報, 63, No.11, 895~898 (1989)

- 木原雄治, 坂口定則, 畑迫健一, 古賀剛, 安東亮: 超高速1MビットCMOS SRAM, 三菱電機技報, 65, No.4, 385~388 (1991)

# 超薄形パッケージICを搭載した 大容量ICメモリカード

郷地英伸\*

越智克則\*\*

寺岡康宏\*\*

## 1. まえがき

電子機器のポータブル化及び高機能化に伴い、高速性・低消費電力性・携帯性に優れたICメモリカードは、携帯型機器の外部記憶媒体として採用されている。特に、ノートブック型やパームトップ型のパーソナルコンピュータには、ICメモリカードのスロットが1個以上標準装備されるようになってきた。また、(社)日本電子工業振興協会(Japan Electronic Industry Development Association: JEIDA)は、1985年からこのICメモリカードの標準化に取り組み、1993年10月には“PCカードガイドラインVer.4.2”を発表した。この規格ではICメモリカードの完全互換を目指してシステム側ソフトウェアの規格が新たに策定された。このことにより、ICメモリカードの一層の普及促進が期待されている。また、市場では電子機器の高機能化・多機能化及びソフトウェアの高度化に伴い、データ処理量が増大している。このため外部記憶媒体としてのICメモリカードは大容量、高速化が要求されている。

一方、ICメモリカードに使用するメモリICは年々集積度が向上し、IC当たりのメモリ容量は大幅に増大する反面、ICのチップサイズも容量とともに大きくなってきており、現在主流のTSOP(Thin Small Outline Package)を基板に両面実装して、標準のカードサイズに納めた場合の搭載できるICの個数は、メモリICの世代交代ごとに少なくなってきた

(a) 断面構造

単位: mm

(b) 側面

図1. パッケージの断面構造及び側面

ている。この結果、メモリICの容量に比例してカードの容量を増大できない事態になっている。

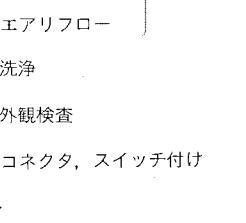

これに対処するため、当社ではTSOPよりも更に薄い0.5mm厚さの超薄形パッケージ(Dual Tape Carrier Package: DTP)を業界で初めて開発した。このDTPに1MビットSRAMを封入し、薄形基板に32個のDTP ICを両面実装することによってJEIDA規格に準拠した4MビットSRAMカード(形名: MF34M1-H1EATXX)を開発した。DTPは単体での完全なテストが可能であるため、この完全良品を基板上に多数搭載してもカードとして高歩留りが可能で、高品質・高信頼性が実現できる。

本稿では、今後の大容量ICメモリカードの開発に必ず(須)となるDTPの構造及びアセンブリ技術とこのDTP ICを使用して開発したMF34M1-H1EATXXのカードの構造及びアセンブリ技術と回路技術について述べる。

## 2. 超薄形パッケージ

### 2.1 パッケージ構造

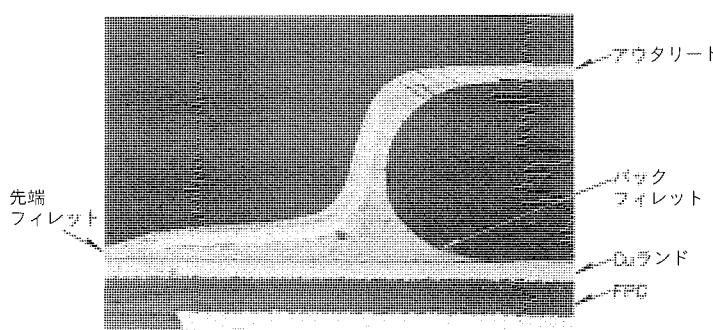

図1にDTPの断面構造及び側面を示す。大容量ICメモリカード用途を目的としてパッケージ厚0.5mmを実現するために、TAB技術及びウェーハの薄研磨を採用している。ウェーハ上に形成されたAuバンプはSnめっきされたテーブキャリアのインナリードと接合される。樹脂封止にトランスファーモールド技術を採用することによって、耐熱性が向上し、リフロー方式による表面実装が可能となった。

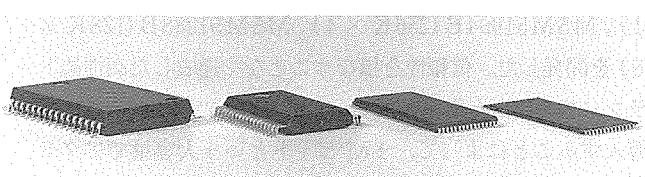

また、アウタリード部は、TSOPと同面積のフットプリント上に実装可能なようにフォーミングされ、かつバーンインなど後工程での熱履歴によるはんだ付け性劣化を防止するために、リード表面にははんだめっきが施されている。図2は各種40ピンパッケージの側面外観比較であり、このDTPの薄さがよく分かる。

### 2.2 アセンブリ技術

(左からSOP, SSOP, TSOP, DTP)

図2. 各種パッケージの外観比較(40pin)

DTPを開発する上での最重要課題は、パッケージ反りによるチップへの応力が最小となる構造するために0.5mmの厚さの中で、いかにチップをパッケージ中央に位置するようコントロールするかであり、特にILB (Inner Lead Bonding) 及びモールド工程において対策を施した。ここでは、この二つのプロセスについてのみ概略を説明する。

### 2.2.1 インナリードボンディング(ILB)

ILB工程は、IC上のAuバンプとテープキャリアのインナリードとを接合する工程である。なお、テープキャリアは、ポリイミド、接着剤、Cuはく(箔)の3層構造のものを使用している。インナリードは表面に約0.5μmのSnがめっきされた約35μm厚のCu箔で、最適荷重と加熱によってAuバンプとAu-Sn共晶合金を形成し接合が行われる。

この工程では、パッケージの厚さ方向に対するICの位置をコントロールするために、ボンディング後のテープキャリアに対するICの高さ方向の位置関係及び傾き量が30μm以内になるように管理している。

### 2.2.2 モールド

モールド工程は、ILBを完了したテープキャリア上のチップを外部環境から保護するために樹脂封止する工程である。TCP (Tape Carrier Package) では液状樹脂の塗布が一般的であるが、このパッケージは、外形厚みの要求精度が高いこと、表面実装可能な高信頼性パッケージを得るために、モノリシックICで培われてきたトランシスタモールド技術を適用した。

この工程では、ICチップがパッケージの中央に位置するように、成形樹脂の低粘度化と流動フローの最適化がプロセス開発のキーポイントである。成形樹脂の低粘度化に対して

図3. DTPの外観 (32pin)

両面実装基板を二つ折りにして従来のカード外形の中に納める

図4. DTPカードの構造

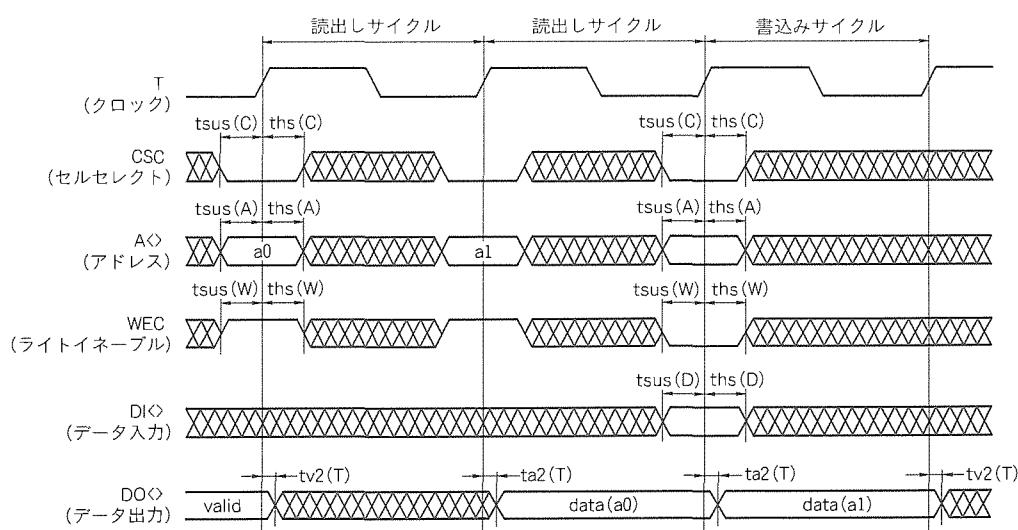

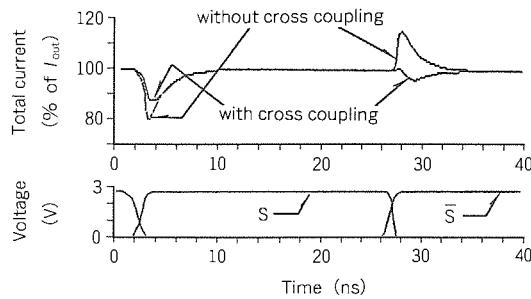

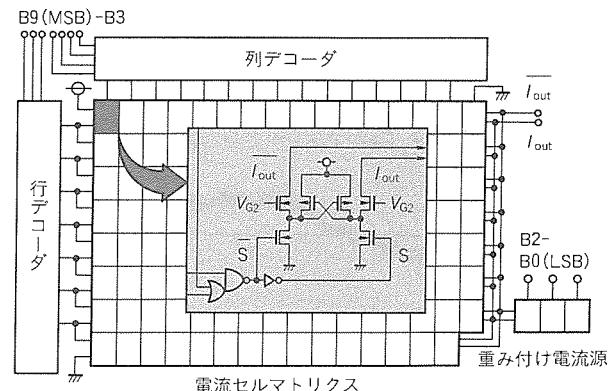

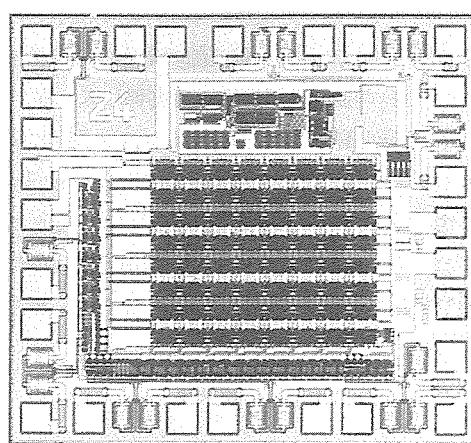

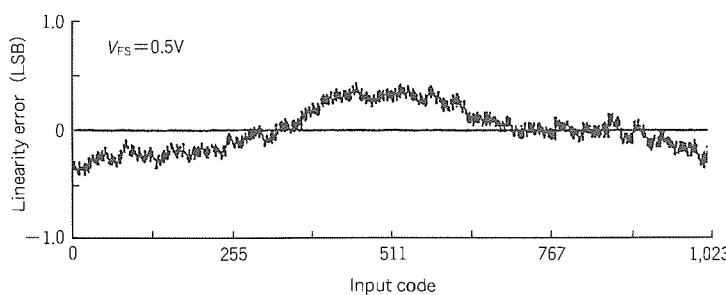

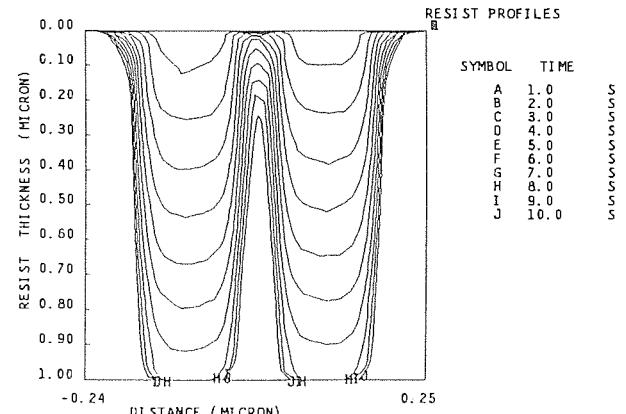

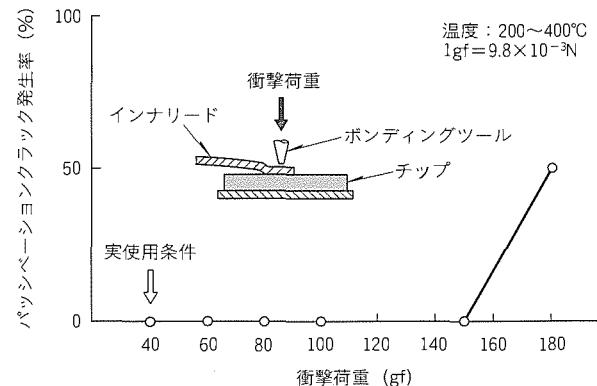

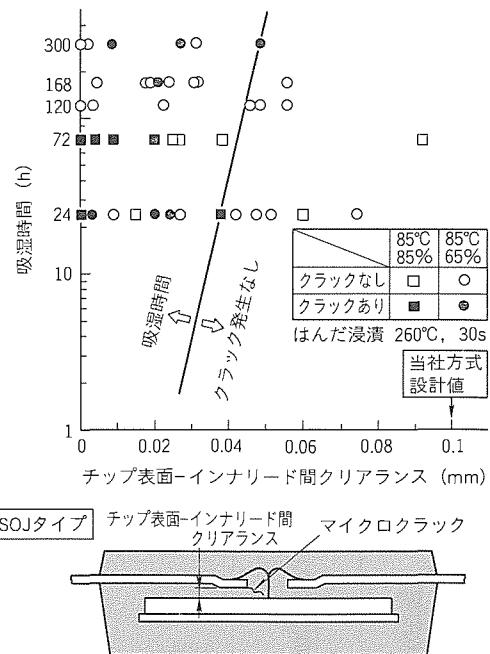

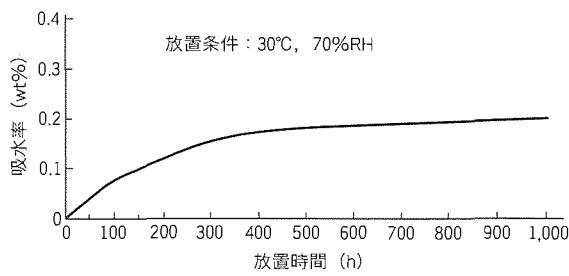

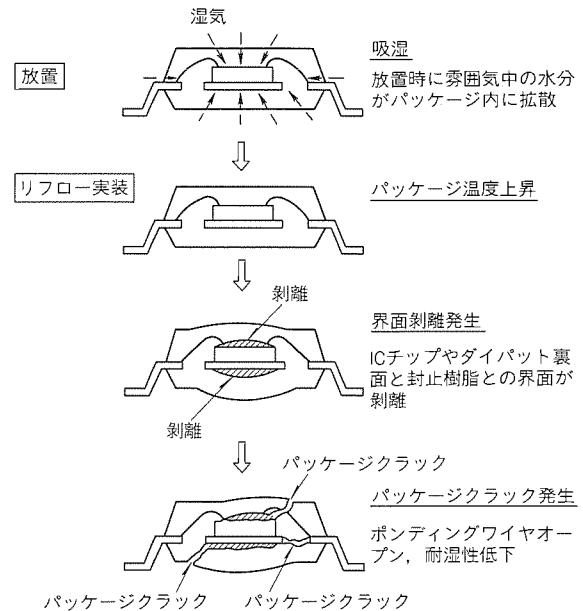

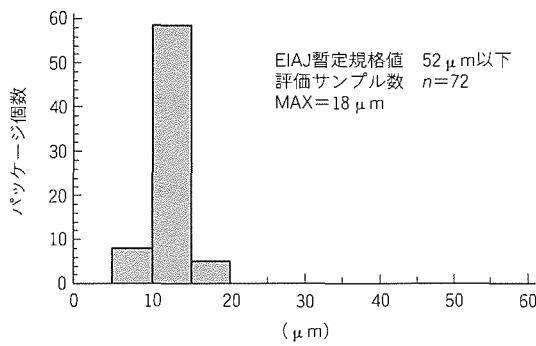

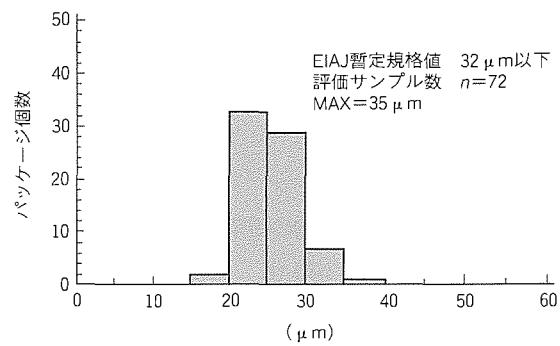

は、従来の樹脂の基本組成・物性を劣化させることなく、フィラーの粒度分布や粒径をコントロールすることにより、粘度を約1/6に下げたTCP用の樹脂を開発し、また成形樹脂の流動フローの最適化に対しては、モールド金型におけるゲート部のランド長さ、樹脂注入速度などのプロセス条件の適正化により、ICの位置を変化させることなく安定して樹脂を注入することが可能となった。さらに、後工程に対して問題となる樹脂バリについても、テープ設計とモールド装置を改良することによって対策を施した。