# MITSUBISHI 三菱電機技報

MITSUBISHI DENKI GIHO Vol.67 No.3

3

1993

特集 “システムVLSI”

## 特集 “システム VLSI”

### 目 次

#### 特集論文

|                                                  |       |

|--------------------------------------------------|-------|

| 半導体新時代                                           | 1     |

| 新良由幸                                             |       |

| システムオンチップ時代における VLSI の展望                         | 2     |

| 吉富正夫                                             |       |

| 0.5 μmCMOS ゲートアレー                                | 6     |

| 荒川隆彦・前野秀史・東谷恵市・斎藤 健・加藤周一                         |       |

| 0.8 μmCMOS エンベッデッドセルアレー                          | 10    |

| 岡辺雅臣・奥野義弘・富岡一郎・井上善雄・朝比奈克志                        |       |

| 画像圧縮 LSI 用高速 DCT コア                              | 16    |

| 高畠明彦・浦本紳一・井上喜嗣・竹田 淳・山下征大                         |       |

| セルベース設計用データバスジェネレータ                              | 21    |

| 辻橋良樹・松本 尚・宮西篤史・西巻秀克・中尾博臣・北田 修                    |       |

| キャッシュメモリを含んだメインメモリ用 4M ビットキャッシュ DRAM             | 25    |

| 早野浩司・阿部英明・石塚康宏                                   |       |

| 2M ビットデュアルポート DRAM                               | 29    |

| 松本淳子・松岡秀人・三木武夫・山脇 実                              |       |

| 高密度 SRAM 内蔵 ASIC                                 | 33    |

| 中島三智雄・越久和俊・上田清年・黒肥地 稔・磯井則次                       |       |

| オフィスコンピュータ用 32 ビット CPU プロセッサ                     | 38    |

| 清水 徹・島津之彦・斎藤祐一・白井健治・藤岡 熱・阪尾正義                    |       |

| ATM スイッチ用 LSI                                    | 42    |

| 野谷宏美・近藤晴房・中山秀昭・斎藤泰孝・小浜茂樹・松田吉雄                    |       |

| 広帯域 ISDN 対応 BiCMOS LSI                           | 46    |

| 植田昌弘・埴潤敏明・東谷恵市・川畑英雄・飛田康夫                         |       |

| 移動体通信用音声コードック LSI                                | 50    |

| 見学 徹・寺岡栄一・安井郁夫・藤山等章・徳田 健                         |       |

| 自動車用 LAN コントローラ、トランシーバー IC                       | 54    |

| 岡本 泰・在本昭哉・菊山誠一郎・高井一兆・村松菊男                        |       |

| クローズドキャプションコントロール用マイクロコンピュータ                     | 59    |

| 藤高繁明・松本誠之・高橋直樹・上村省一・木村方昭                         |       |

| プロトコル制御用マイクロコンピュータ                               | 64    |

| 林 良紀・倉持昌司・竹内 稔・広川祐之                              |       |

| 高速高密度 TSOP メモリモジュールシリーズ                          | 67    |

| 田原次夫・上村俊一                                        |       |

| ミックスメモリカード                                       | 72    |

| 田淵正行・木村正俊・渡辺忠勝・白土修一                              |       |

| ISDN インタフェースボード                                  | 76    |

| 中林竹雄・藏永 寛・後藤宏二・木村隆一・宮城 明・小林和男                    |       |

| <b>普通論文</b>                                      |       |

| 5.0V/3.3V 版第二世代 16M ビット DRAM                     | 80    |

| 宮元崇行・梶本 純・森 茂・野崎雅彦・源城英毅                          |       |

| プロック消去可能な高速 4M ビットフラッシュメモリ                       | 84    |

| 野口健二・大川 実・山本 誠・新井 肇・伊庭智久                         |       |

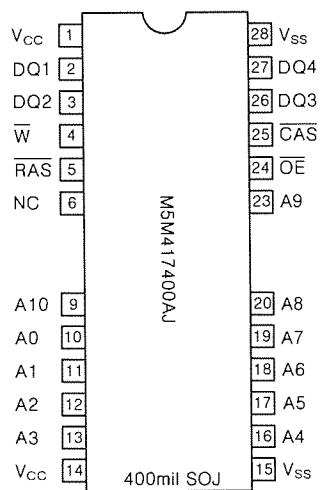

| 4M ビットバイトワイド/ワードワイド DRAM — バッテリ駆動型システム用 3.3V 版 — | 88    |

| 富上健司・豆谷智治・長山安治・長友正男                              |       |

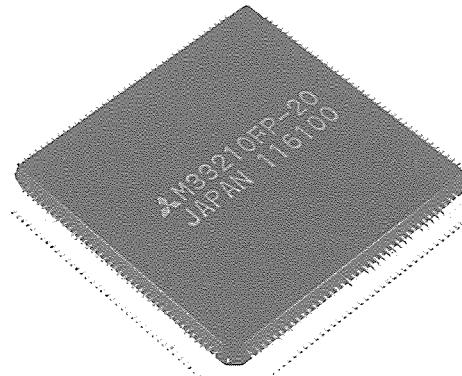

| 高放熱プラスチック QFP に封止した 32 ビットマイクロプロセッサ              | 92    |

| 中野直佳・樋口徳昌・平井達也・中村伸哉・倉野新一                         |       |

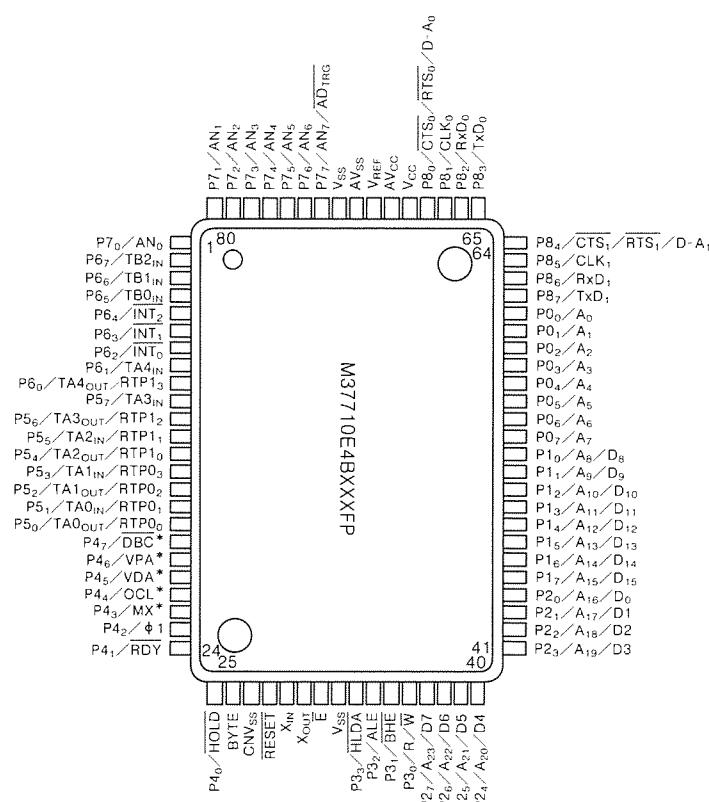

| アナログ機能を強化した 16 ビットワンチップマイクロコンピュータ                | 96    |

| 上木雄詞・神崎照明・樋口光誠・高橋 壘・藤原俊夫                         |       |

| <b>特許と新案</b>                                     |       |

| 紫外線消去形プログラマブル読出専用メモリ装置の試験方法,                     |       |

| 相補形 MOS 集積回路装置                                   | 101   |

| 昇圧回路                                             | 102   |

| <b>スポットライト</b>                                   |       |

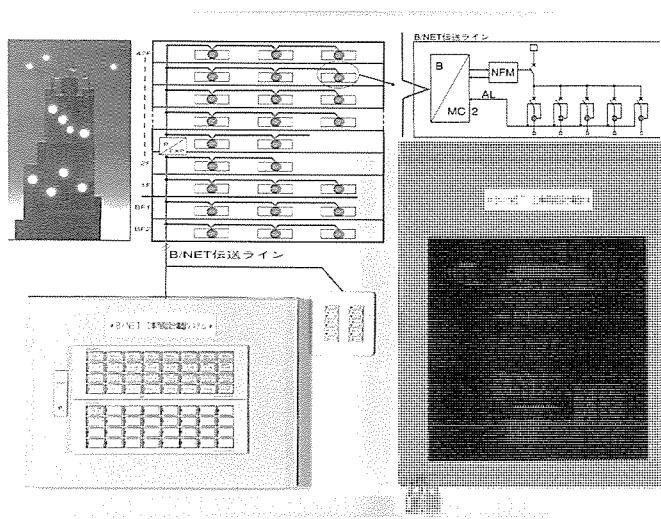

| 三菱セルベース IC M652XX, M653XX シリーズ                   | 100   |

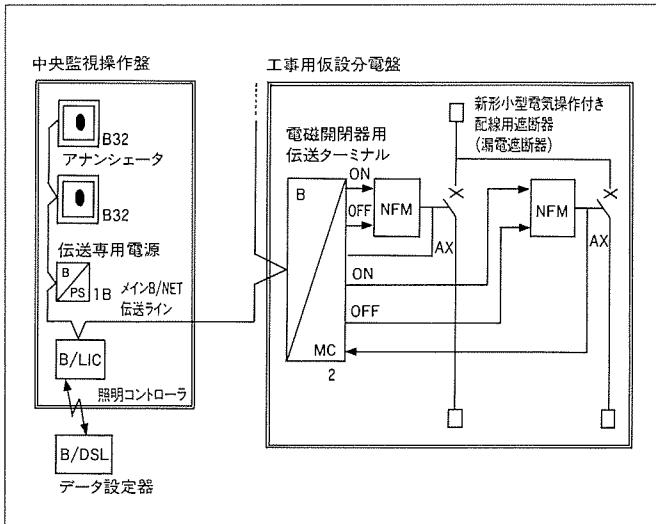

| B/NET 工事用仮設分電盤システム                               | (表 3) |

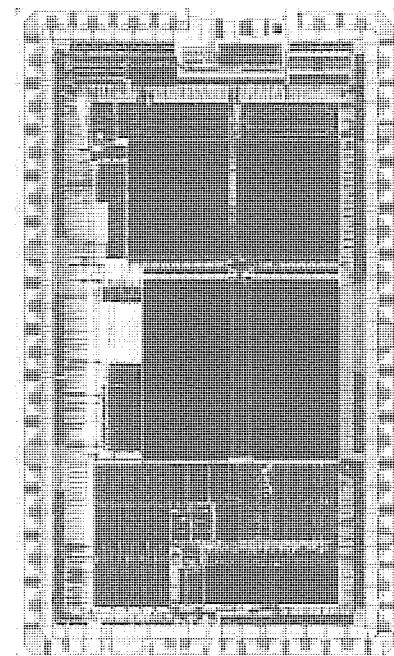

### 表紙

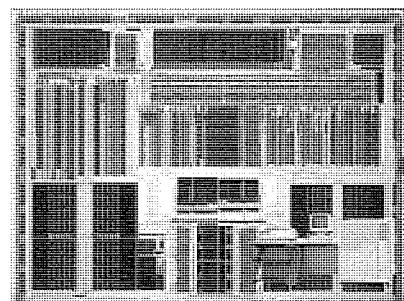

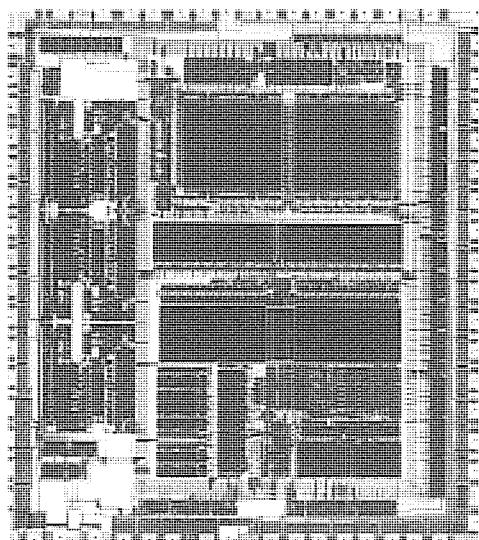

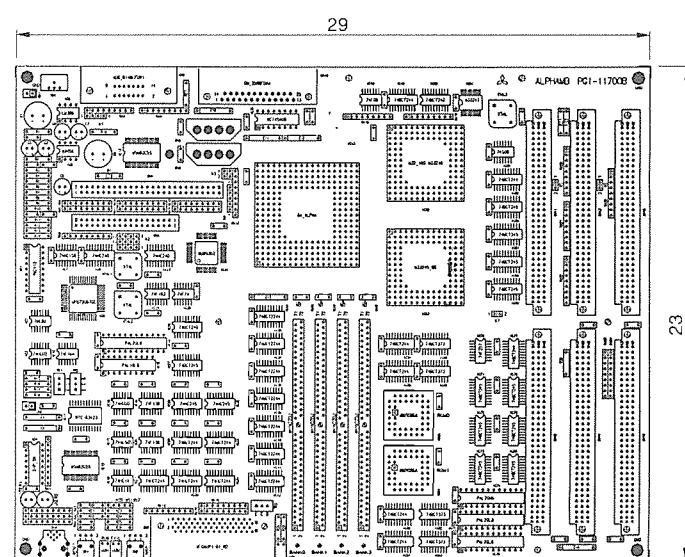

#### オフィスコンピュータ用 CPU プロセッサ

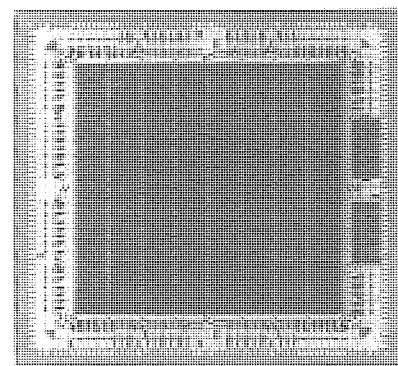

表紙の写真は、CPU プロセッサのチップとそのチップを搭載したオフィスコンピュータ MELCOM80 “GS ファミリー” の最上位機 GS700/10 である。

このチップは、16K バイトのキャッシュメモリを内蔵し、0.8 μm ルール CMOS のプロセス技術を用いて 16.3mm × 12.7mm のサイズに 170 万トランジスタを集積している。

(本文 38 ページ参照)

三菱電機技報に掲載の技術論文では、国際単位“SI”(SI 第 2 段階(換算値方式)を基本)を使用しています。ただし、保安上、安全上等の理由で、従来単位を使用している場合があります。

## アブストラクト

### システムオンチップ時代におけるVLSIの展望

吉富正夫

三菱電機技報 Vol. 67・No. 3・p. 2~5 (1993)

システムVLSIの展望について述べる。システムのデジタル化、複合化の流れの中で半導体は微細化を中心に進展し、今やシステムの主要部分が一つのシリコンチップ上に集積される、いわゆるシステムオンチップの時代を迎えた。システムVLSIを実現するための環境条件について述べ、システムVLSIの具体例としてエンベッテッドセルアレー、画像DSP、SCSI専用コントローラについて解説した。

### 0.5 μmCMOSゲートアレー

荒川隆彦・前野秀史・東谷恵市・斎藤 健・加藤周一

三菱電機技報 Vol. 67・No. 3・p. 6~9 (1993)

0.5 μmCMOS、3層配線プロセスを採用した高集積全面敷き詰め型ゲートアレーについて述べる。0.5 μmCMOS技術と当社独自のゲートアイソレーション方式により世界最大1ミリオングートを達成、3.3V電源で低消費電力(0.9 μW)、高速性(190ps)を実現している。また、システムの高速化に対応し、位同期回路を利用したクロック管理機能や高速小振幅信号インターフェース回路も内蔵している。

### 0.8 μmCMOSエンベッテッドセルアレー

岡辺雅臣・奥野義弘・富岡一郎・井上善雄・朝比奈克志

三菱電機技報 Vol. 67・No. 3・p. 10~15 (1993)

ゲートアレー(GA)では達成できない高速性・高集積性をGAと同じ短納期で実現するために、PLL(Phase-Locked Loop)、GTL(Gunning Transceiver Logic)、高速RAM等の回路を内蔵可能とした0.8 μmCMOSエンベッテッドセルアレー(ECA)を開発した。ECA用に開発したEWSベースの設計システムを用いてLSIを設計した。2層配線でも等価200Kゲート以上を集積可能で、LSIを製作して評価した結果、50MHz以上の高速動作が確認できた。

### 画像圧縮LSI用高速DCTコア

高畠明彦・浦本紳一・井上喜嗣・竹田 淳・山下征大

三菱電機技報 Vol. 67・No. 3・p. 16~20 (1993)

画像圧縮LSIの核となるDCT(Discrete Cosine Transform)コアを開発した。高速アルゴリズムと分散演算を採用することにより、大量の積和演算を効率的に処理するアーキテクチャを実現した。また、DCTと逆DCTの二つの直交変換を同一のハードウェアで実行可能とするために最適な2ポート/2プレーンROM等の回路技術の開発も行った。これらにより、最高動作周波数100MHz、面積21mm<sup>2</sup>という世界最高水準の性能を達成した。

### セルベース設計用データバスジェネレータ

辻橋良樹・松本 尚・宮西篤史・西巻秀克・中尾博臣・北田 修

三菱電機技報 Vol. 67・No. 3・p. 21~24 (1993)

0.8 μmCMOSプロセスにて開発したデータバスジェネレータに関して、基本セル構造及びレイアウトデータ生成方法の特長を述べる。新規なレイアウト生成手法として、セル上配線と、配線数に応じたセル高可変機構、任意の配線トラックと接続可能なセル入出力端子をもち、これを可能とする基本セル構造を開発した。これにより、集積度7kTr/mm<sup>2</sup>以上の高密度なデータバスレイアウトが実現できる。

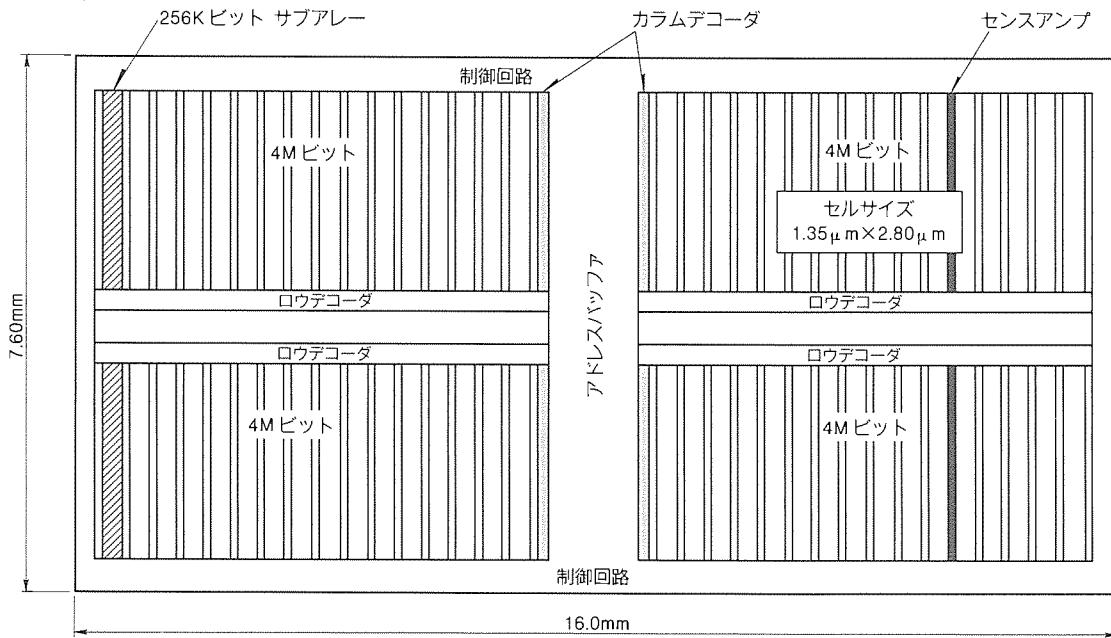

### キャッシュメモリを含んだメインメモリ用4MビットキャッシュDRAM

早野浩司・阿部英明・石塚康宏

三菱電機技報 Vol. 67・No. 3・p. 25~28 (1993)

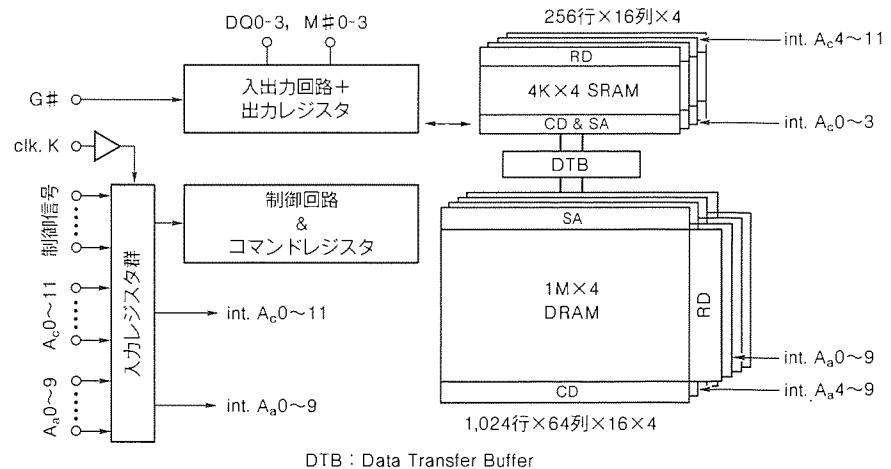

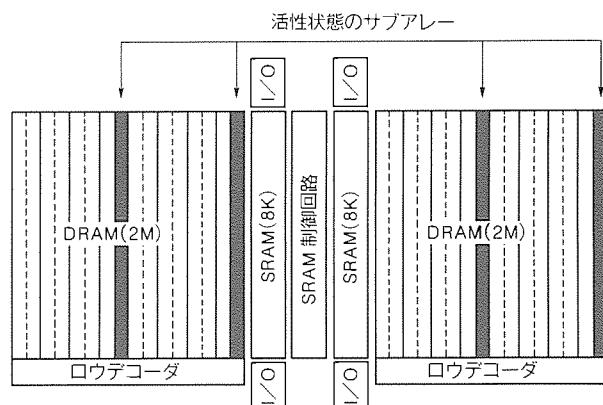

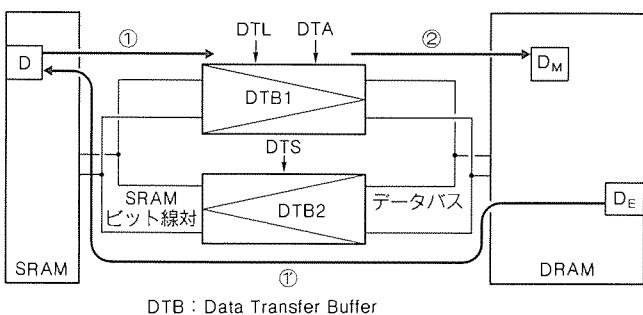

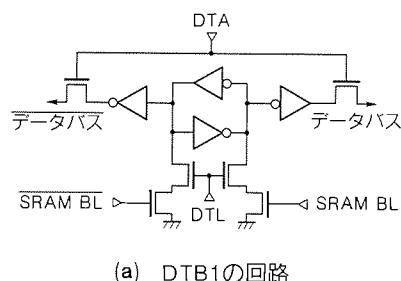

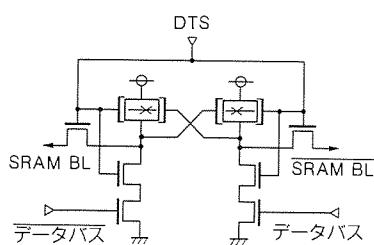

16Kビットの高速SRAMと4Mビットの大容量DRAMを同一チップに集積した当社独自のキャッシュDRAMの概要・機能・特長・用途について述べる。キャッシュアクセス時間は従来の1/3に高速化したファーストコピーバック方式の採用、高速キャッシュアクセスを可能にしたSRAM局所配置のチップレイアウト、16×4ビットのキャッシュブロックサイズが主な特長である。

### 2MビットデュアルポートDRAM

松本淳子・松岡秀人・三木武夫・山脇 実

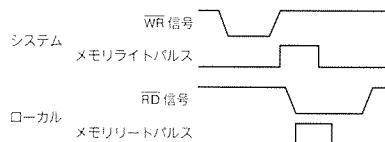

三菱電機技報 Vol. 67・No. 3・p. 29~32 (1993)

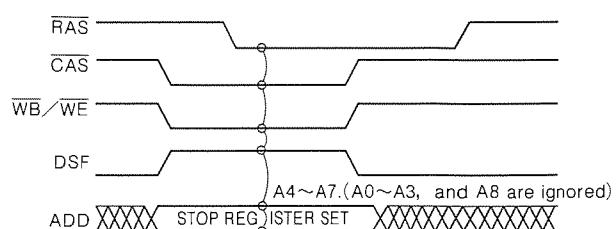

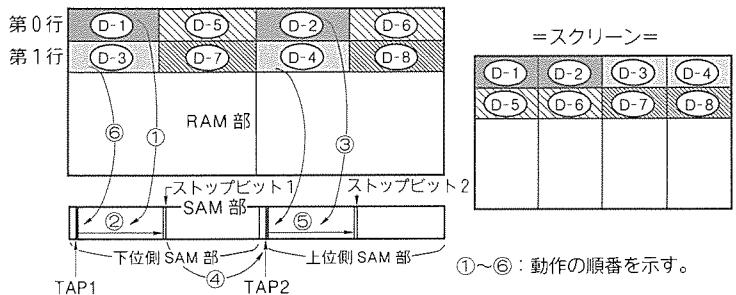

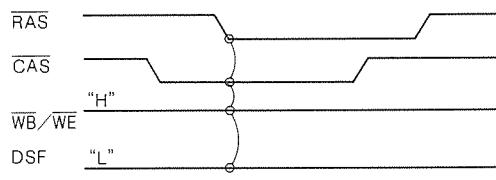

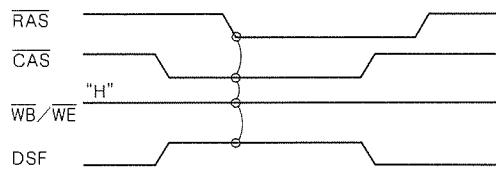

近年の画像処理技術の向上には著しいものがあり、VRAMに求められる機能、性能も世代ごとに発展してきている。今回開発した2MビットVRAMはそのようなニーズにこたえるべく、新たにハイバーベージ機能、ストップレジスタ機能等を備え、性能の向上を図った。特に、今回はRAM部の動作に1/4分割動作を採用することにより、最小サイクル時のリード・ライト動作電力を495mWに抑えて低消費電力化を実現した。

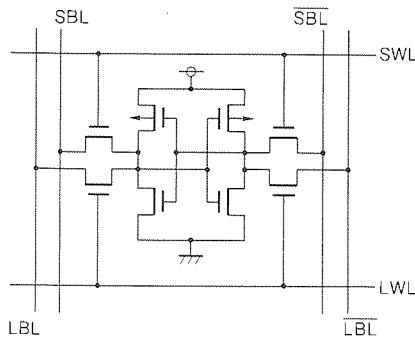

### 高密度SRAM内蔵ASIC

中島三智雄・越久和俊・上田清年・黒肥地 稔・磯井則次

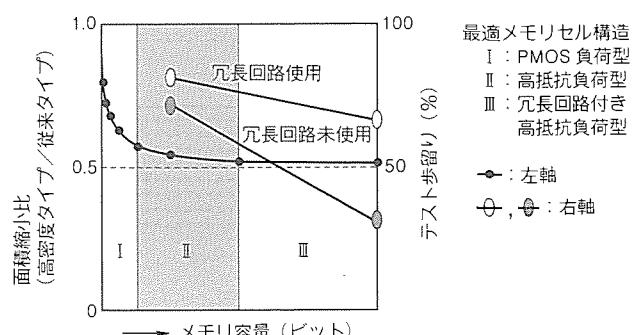

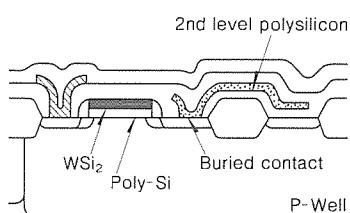

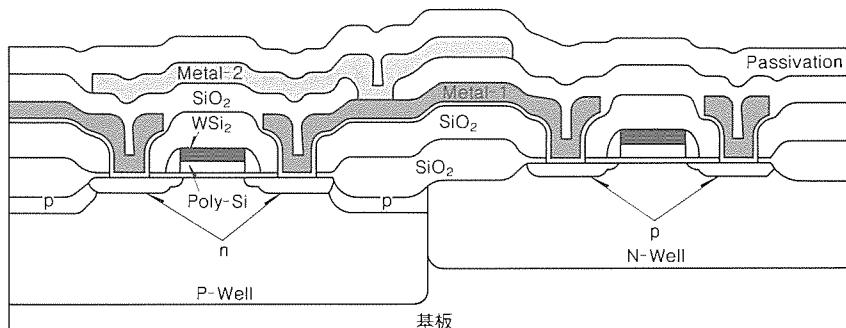

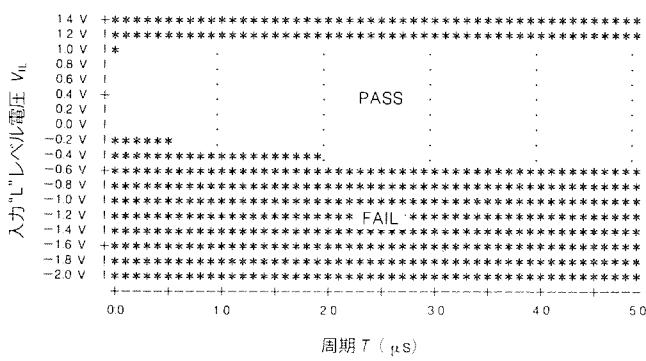

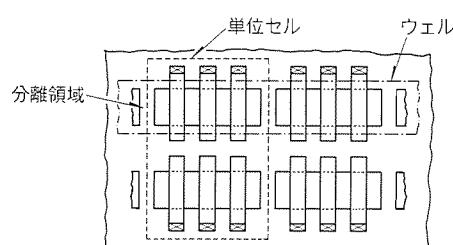

三菱電機技報 Vol. 67・No. 3・p. 33~37 (1993)

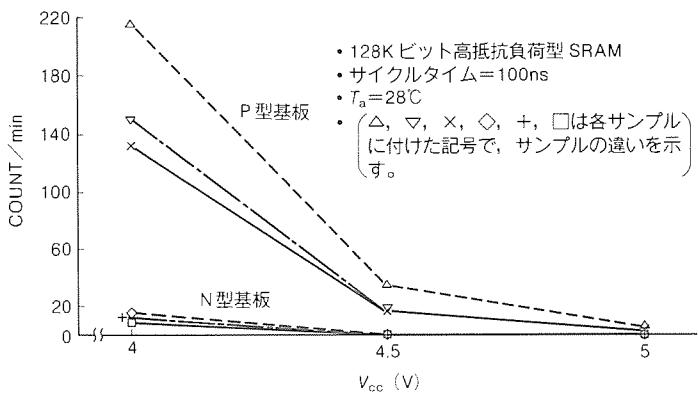

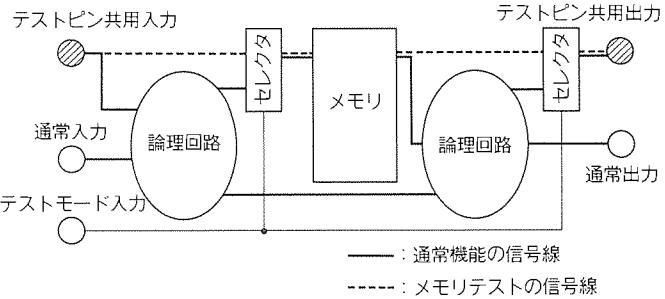

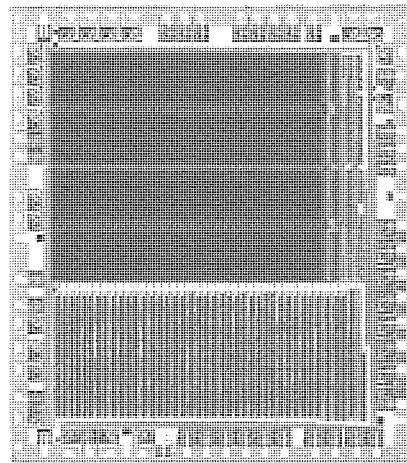

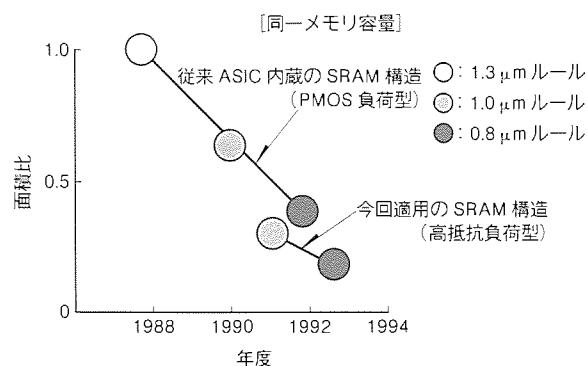

電子機器分野のシステムの小型化、ワンチップ化に伴い、ASICに内蔵されるSRAMの大容量化が求められている。この市場要求にこたえるため、従来比約2倍のビット密度をもつ高抵抗負荷型メモリセルをASICに初めて適用した。新プロセス構造により、ASIC適用における高抵抗負荷型メモリセル特有の問題を解決した。新プロセスの概要と将来的な発展について述べる。

### オフィスコンピュータ用32ビットCPUプロセッサ

清水 徹・島津之彦・斎藤祐一・白井健治・藤岡 勲・阪尾正義

三菱電機技報 Vol. 67・No. 3・p. 38~41 (1993)

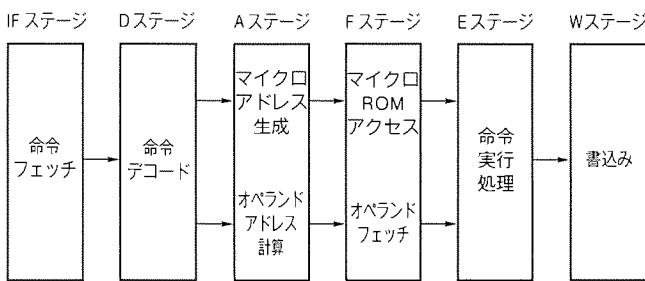

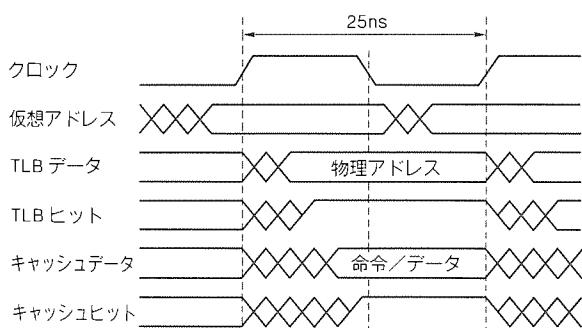

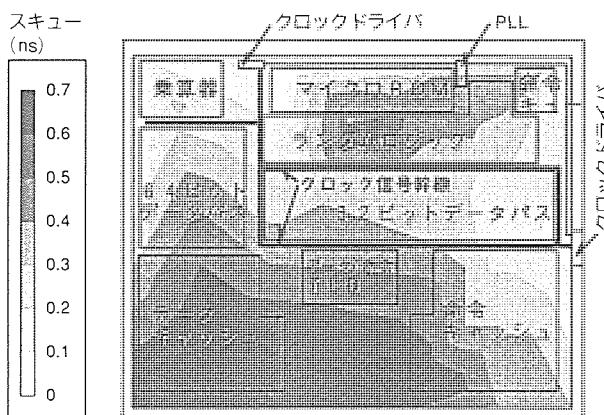

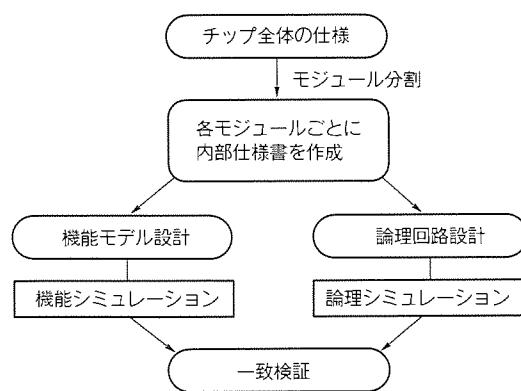

当社オフコン MELCOM80“GSファミリー”最上位機を対象に32ビットCPUプロセッサを開発した。0.8 μmCMOS 2層ポリシリコン2層メタルのプロセス技術とフルカスタム設計技術によって170万トランジスタを集積し、CPUの基本機能すべてを1チップ化した。6段のパイプライン処理、命令/データキャッシュ各々8Kバイト等の最新のアーキテクチャ採用によりメモリオペランドを含めて1クロック/命令、40MHzの性能を実現した。

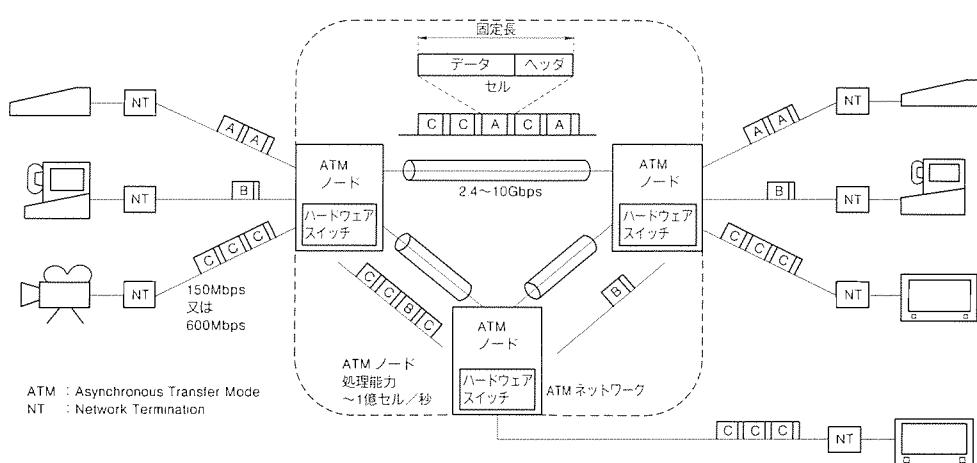

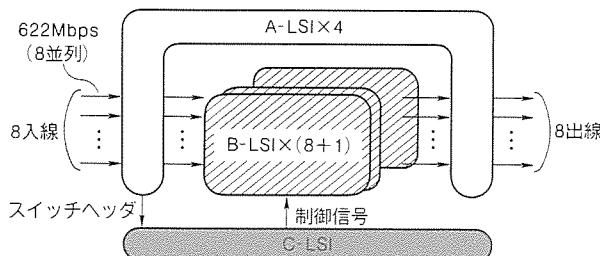

### ATMスイッチ用LSI

野谷宏美・近藤晴房・山中秀昭・斎藤泰孝・小浜茂樹・松田吉雄

三菱電機技報 Vol. 67・No. 3・p. 42~45 (1993)

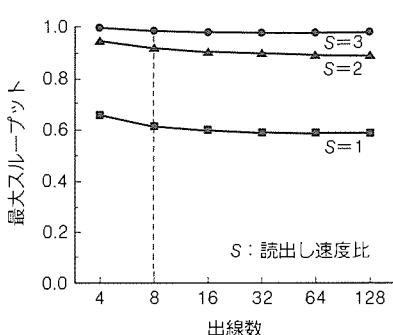

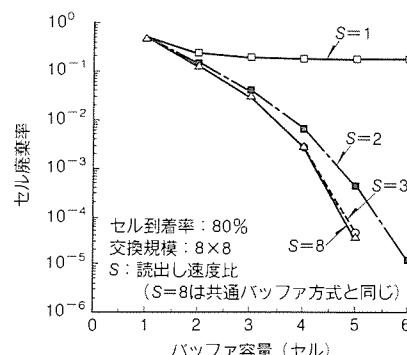

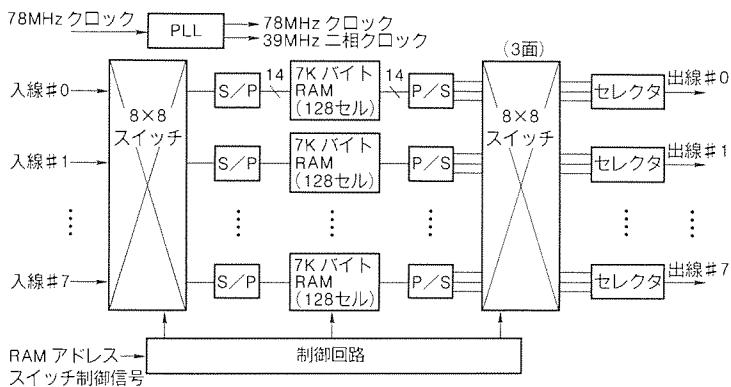

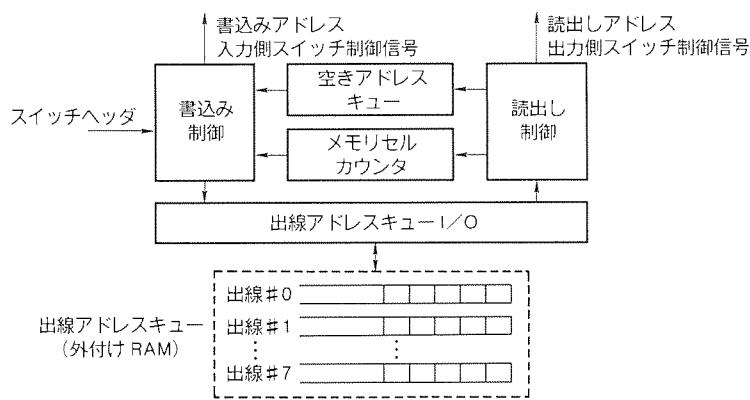

622Mbps、8×8のATM(Asynchronous Transfer Mode)スイッチ用チップセットを開発した。当社独自の分割共通バッファ方式を採用して、小容量のバッファメモリで、低いセル廃棄率のATMスイッチを実現した。開発したLSIは、アライナLSI、バッファ・スイッチLSI、コントロールLSIの3品種で、いずれも0.8 μmBiCMOSプロセスを採用し、90MHz(実使用周波数78MHz)動作を達成している。

# Abstracts

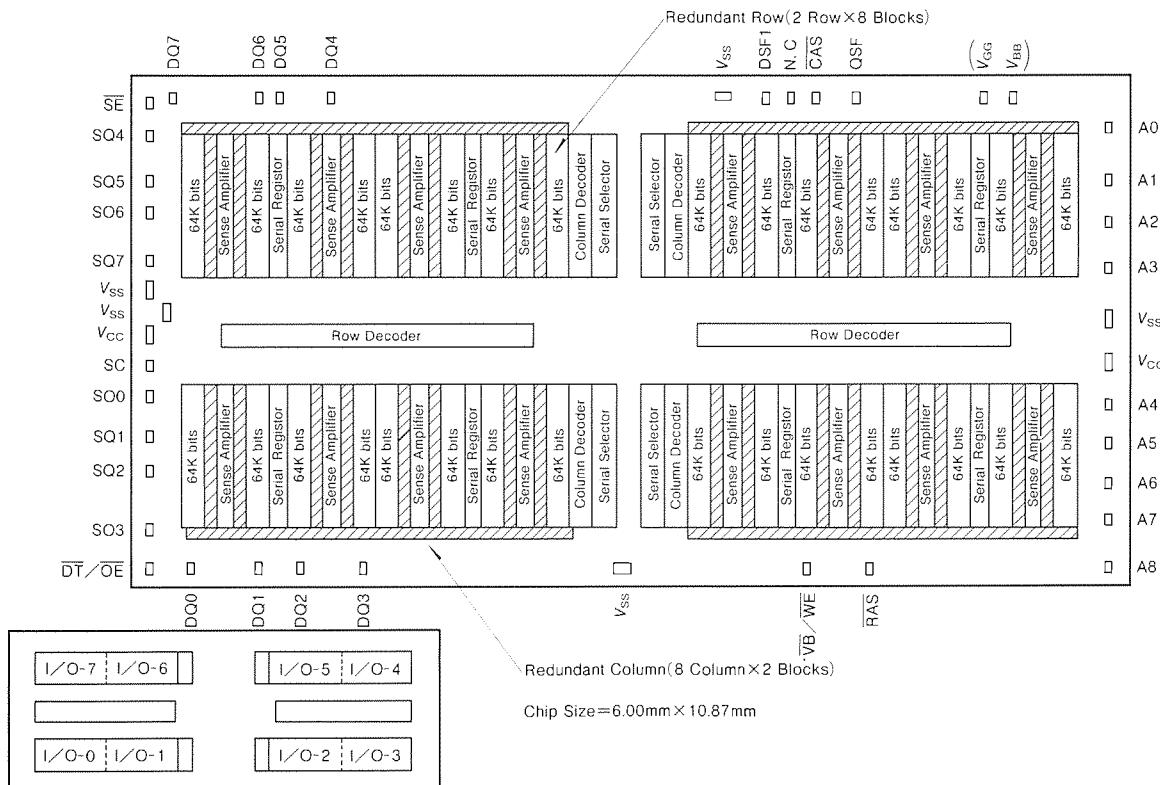

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 25~28 (1993)

## A 4Mb DRAM with On-Chip Cache

by Koji Hayano, Hideaki Abe & Yasuhiro Ishizuka

The article describes a 4Mb DRAM device with a high-speed 16Kbit on-chip SRAM cache. The cache access time has been reduced to 210ns, one-third of the previous time, by use of a fast copyback method. The cache employs a  $16 \times 4$ -bit block size, and its memory cells are locally distributed to maximize cache access speed.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 29~32 (1993)

## A 2Mb Dual-Port DRAM

by Junko Matsumoto, Hideto Matsuoka, Takeo Miki & Minoru Yamawaki

A 2Mb video RAM device with enhanced performance and hyperpage and stop register functions has been developed. The RAM is organized for quarter-duty operation, which reduces the minimum cycle read/write power dissipation to 495mW.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 33~37 (1993)

## ASICs with High-Density SRAM Cells

by Michio Nakajima, Kazutoshi Oku, Kiyotoshi Ueda, Minoru Kurohiji & Noritsugu Itoi

High-density SRAM cells with double the bit density of previous devices have been developed for use in ASICs. Structure and process innovations have solved the specific problems related to incorporating high-density memory cells into ASICs. The article details this process and its future possibilities.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 38~41 (1993)

## A 32-Bit CPU Processor for Business Computers

by Toru Shimizu, Yukihiko Shimazu, Yuichi Saito, Kenji Shirai, Isao Fujioka & Masayoshi Sakao

A new CPU processor has been developed for the top model business computer in the MELCOM 80 GS Family. Most of the CPU functions have been integrated in a single monolithic device comprising 1.7 million transistors. The device was developed using full-custom design technology and a  $0.8\mu m$  CMOS process with two-layer polysilicon and two-layer metalization. The device achieves one-instruction-per-clock-cycle performance for most instructions, including memory load and store, using such advanced architecture features as a six-stage pipelining, and 8Kb data and instruction caches. The device operates at 40MHz.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 42~45 (1993)

## An ATM Switch Chipset

by Hiromi Notani, Harufusa Kondoh, Hideaki Yamanaka, Hirotaka Saito, Shigeki Kohama & Yoshiro Matsuda

The corporation has developed a 622Mbps,  $8 \times 8$  asynchronous transfer mode (ATM) switch chipset. Use of an original shared multibuffer architecture made it possible to realize an ATM switch with high speed and a low cell-loss ratio. The chipset consists of three VLSI devices: an aligner, a buffer switch and a controller. All are fabricated using  $0.8\mu m$  BiCMOS process technology. The chipset is capable of 90MHz operation.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 2~5 (1993)

## VLSI Prospects in the System-on-Chip Age

by Masao Yoshitomi

The article discusses system VLSIs. Semiconductor technology has advanced to the point that the main functions of an electronic system can be incorporated entirely on a single chip. Replacement of analog technology by digital has contributed to this integration. The article looks at the infrastructural requirements for building system VLSIs, and introduces an embedded cell array, video DSP and SCSI controller.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 6~9 (1993)

## A $0.5\mu m$ CMOS Gate Array

by Takahiko Arakawa, Hideshi Maeno, Keiichi Higashitani, Ken Saito & Shuichi Kato

The article introduces a sea-of-gates CMOS gate array with  $0.5\mu m$  geometry and three-layer metalization. One million gates on a single chip has been realized owing to a gate isolation technique. The device has a high-speed performance of 190ps/gate and power dissipation of  $0.9\mu W/gate$ , even at the low voltage of 3.3V. A phase-locked loop circuit for the clock signal and high-speed low-voltage-swing interface support high-frequency operation.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 10~15 (1993)

## Development of an $0.8\mu m$ CMOS Embedded Cell Array

by Masatomi Okabe, Yoshihiro Okuno, Ichiro Tomioka, Yoshiro Inoue & Katsushi Asahina

The corporation has developed an embedded cell array (ECA) based on  $0.8\mu m$  CMOS technology that allows the realization of phase-locked loops, Gunning transceiver logic, RAM and other high-speed circuits that cannot be implemented using a conventional gate array. A workstation-based CAD system is used to support the ECA chip design. The employment of two-layer metalization allows more than 200 kilogates to be integrated on the ECA chip. Experimental data revealed that application of a typical ECA chip enables operation at a frequency over 50MHz.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 16~20 (1993)

## A High-Speed Discrete Cosine Transform Core Processor for Image Compression ICs

by Akihiro Takabatake, Shin'ichi Uramoto, Yoshitsugu Inoue, Jun Takeda & Yukihiko Yamashita

The corporation has developed a discrete cosine transformation (DCT) core processor for use in image compression ICs. The circuitry can efficiently perform large numbers of computations due to the use of fast algorithms and distributed arithmetic processing. Dual-port dual-plane ROM technology was also developed to enable the same hardware to perform both DCT and inverse DCT. Applications of the DCT core processor will support operating frequencies up to 100MHz. The processor occupies a chip area of just 21mm<sup>2</sup>, an integration scale among the highest in the world.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 21~24 (1993)

## A Data Path Generator for Cell-Based Design

by Yoshiki Tsujihashi, Hisashi Matsumoto, Atsushi Miyanishi, Hidekatsu Nishimaki, Hiro'omi Nakao & Osamu Kitada

The article describes a module generator that is capable of generating data-paths with both the speed and transistor density comparable to handcrafted designs. A new cell structure suitable for over-the-cell routing was developed as the generator's bit-slice element. I/O terminals can be connected with any wiring track over a cell, and cell height is adjustable to suit the number of tracks. Configurable function blocks -- components of the data-path -- are developed using  $0.8\mu m$  two-layer metalization CMOS technology. The generator can create data paths with densities of more than 7kTr/mm<sup>2</sup>.

## アブストラクト

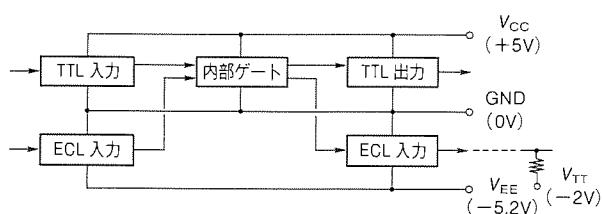

### 広帯域 ISDN 対応 BiCMOS LSI

植田昌弘・埴渕敏明・東谷恵市・川畑英雄・飛田康夫

三菱電機技報 Vol. 67・No. 3・p. 46~49 (1993)

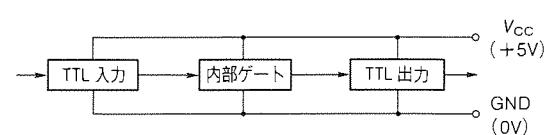

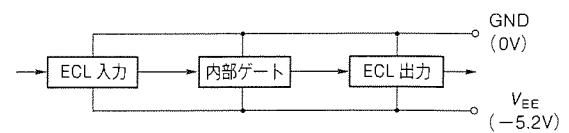

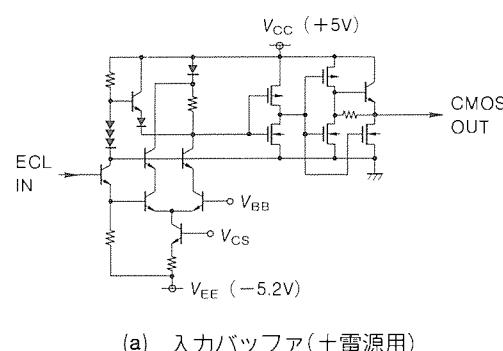

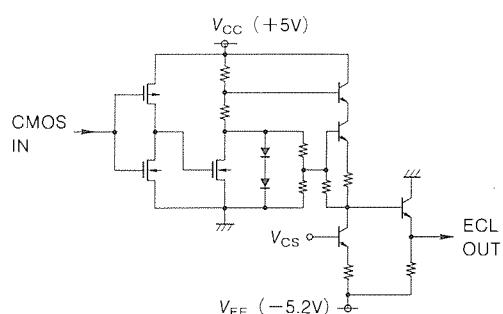

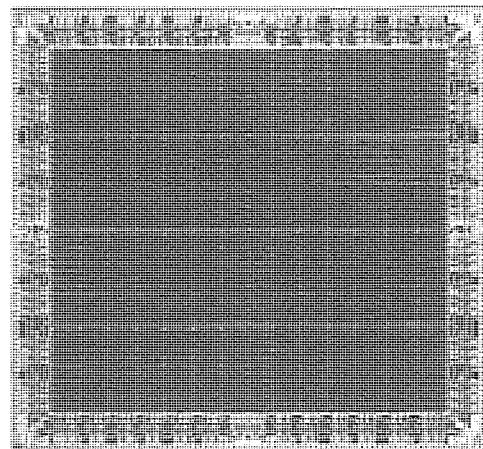

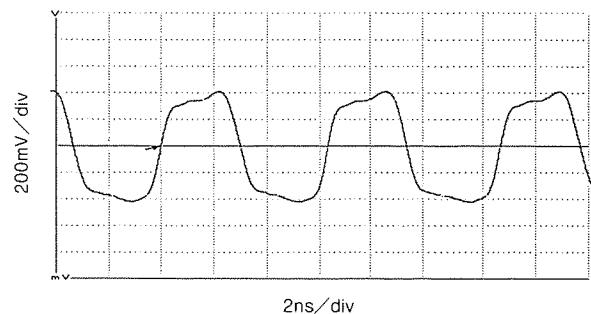

バイポーラトランジスタと CMOSトランジスタを一つのチップ上に構成するディジタル系の BiCMOS 技術が開発され、高速 SRAM を始めとする様々な分野への応用が図られている。

今回、ゲートアレー手法を用いて ECL と TTL レベルの同時インターフェースが可能な BiCMOS LSI を開発し、広帯域 ISDN 用のユーザー・網インターフェース LSI の 1 チップ化に適用した。

### 移動体通信用音声コーデック LSI

見学 徹・寺岡栄一・安井郁夫・藤山等章・徳田 健

三菱電機技報 Vol. 67・No. 3・p. 50~53 (1993)

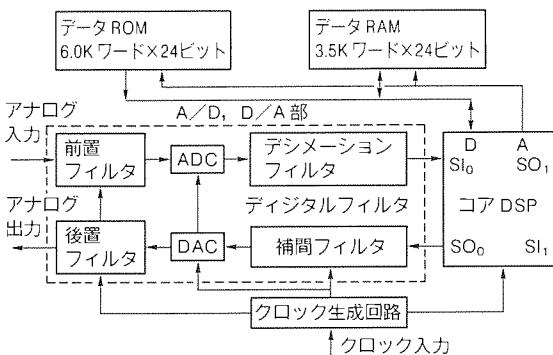

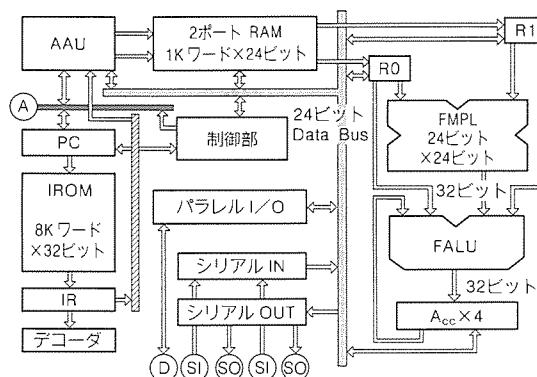

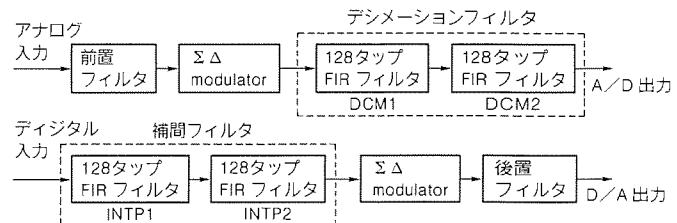

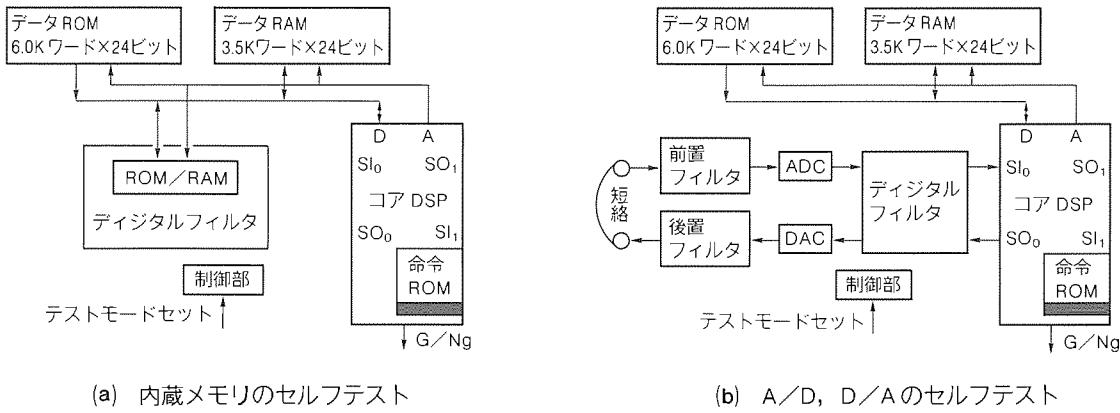

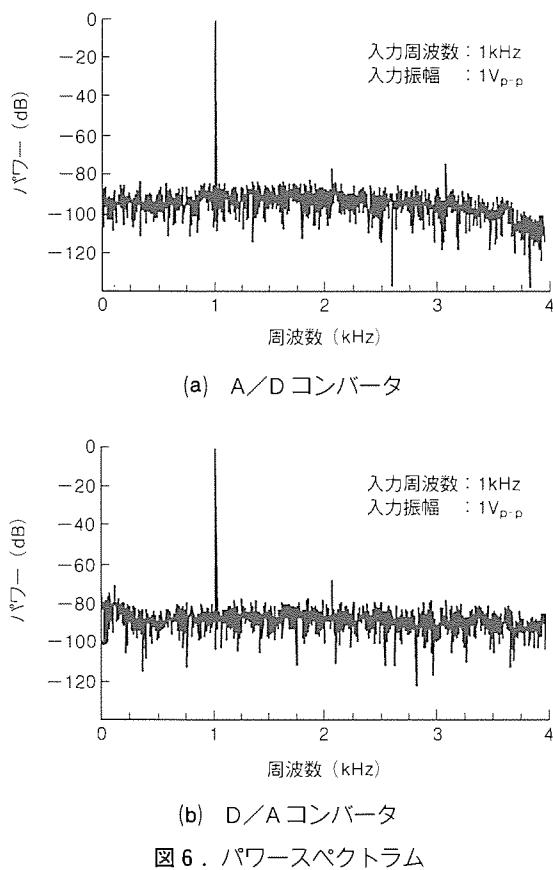

車載／携帯電話等のディジタル通信の発展に対応すべく 24ビット浮動小数点ディジタルシグナルプロセッサ、13ビット A/D, D/A, 大容量メモリを 1 チップに集積した。1 μm CMOS 2 層ポリ、2 層アルミプロセスを用いて 130 万トランジスタを集積し、1 マシンサイクル 60ns の高速性と 490mW (VSELP 実行時) の低消費電力を実現しており、高能率音声符号化／複合コーデック等の音声信号処理に使用可能である。

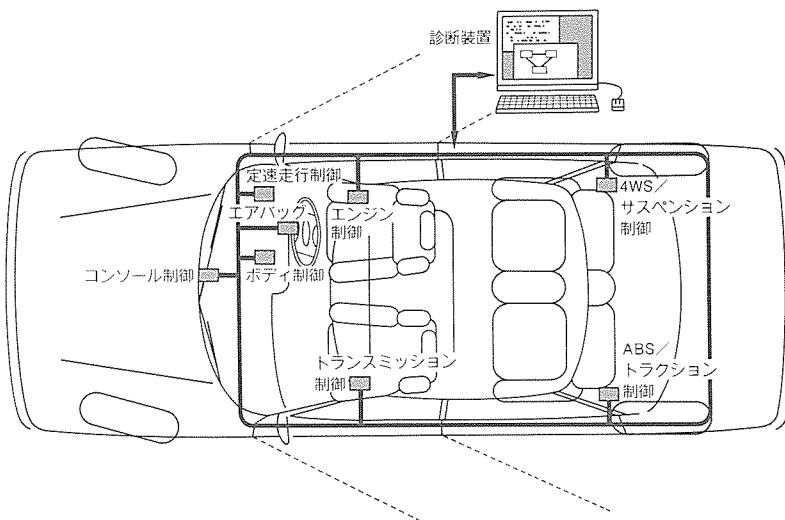

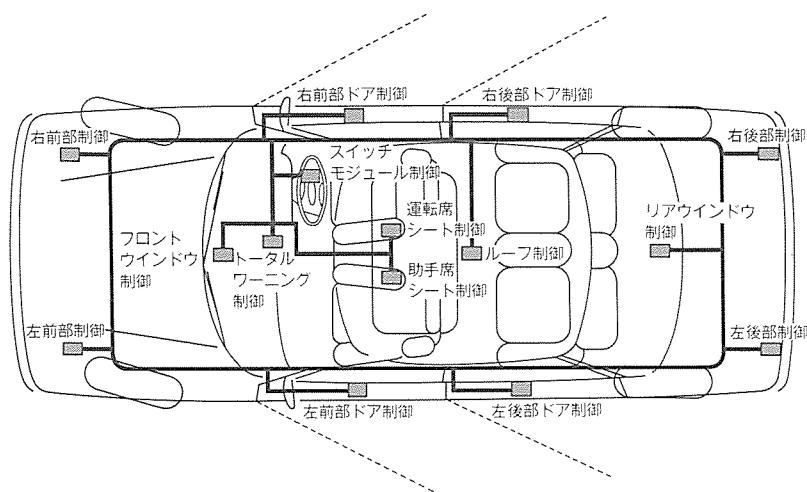

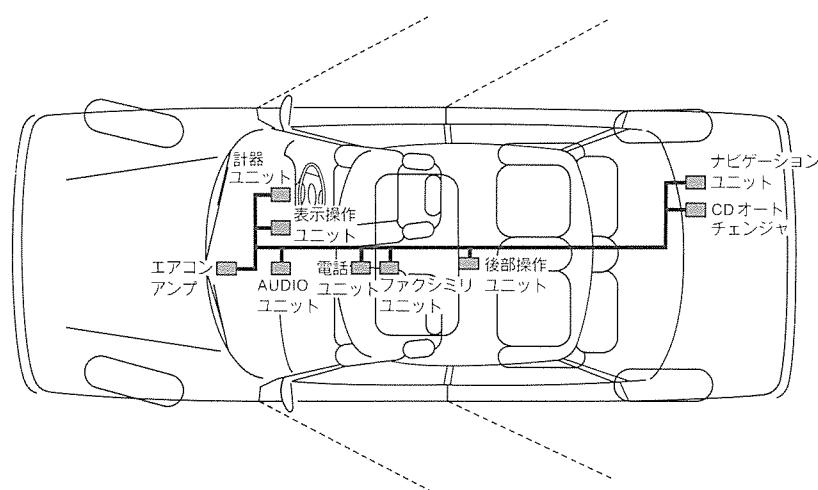

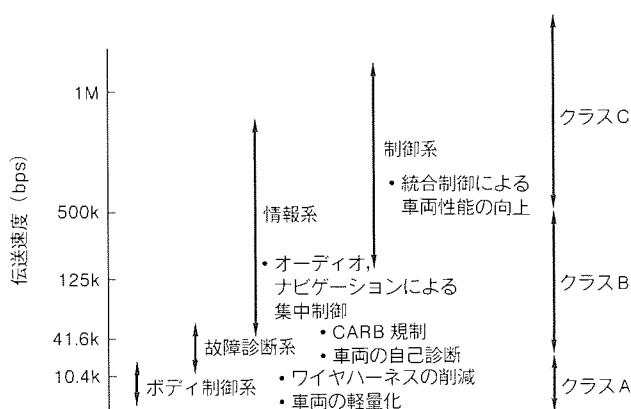

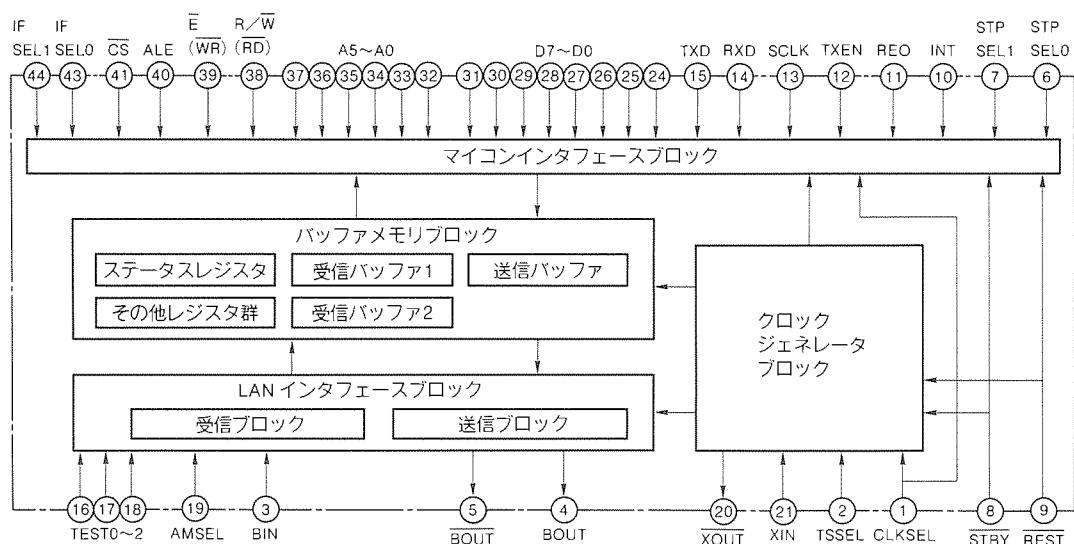

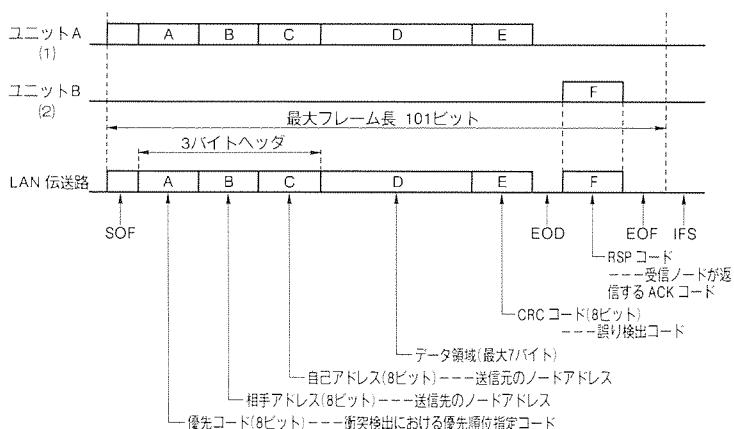

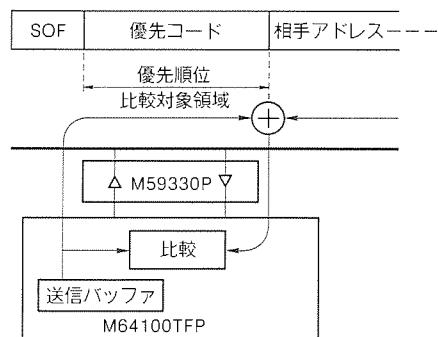

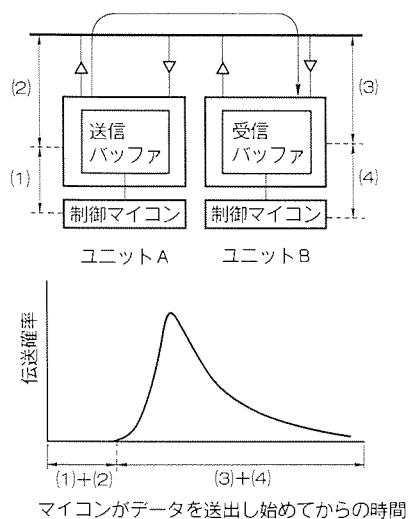

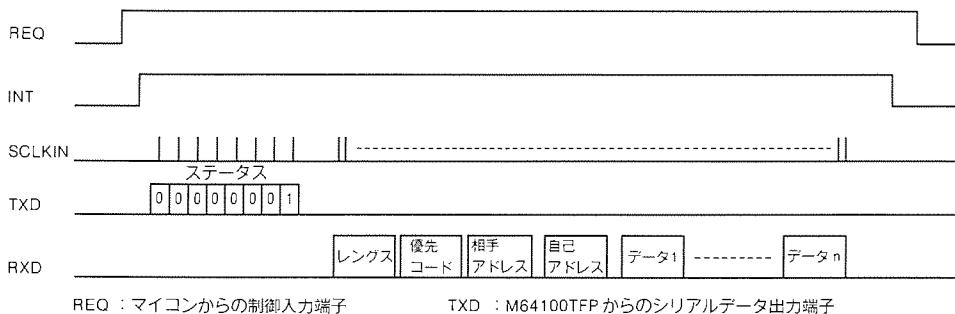

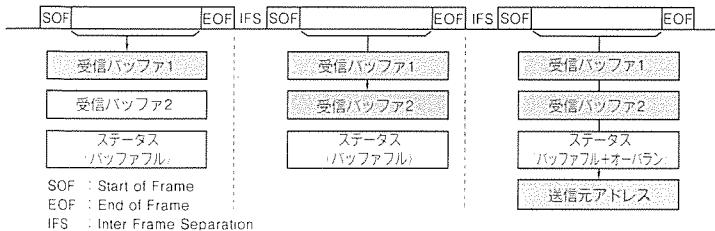

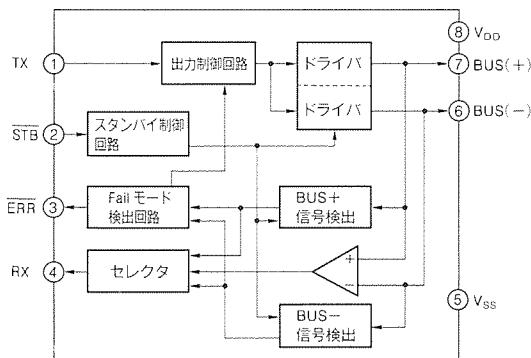

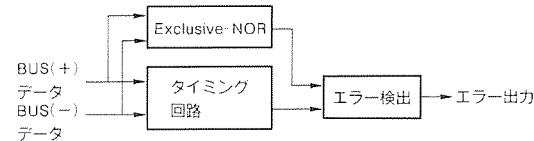

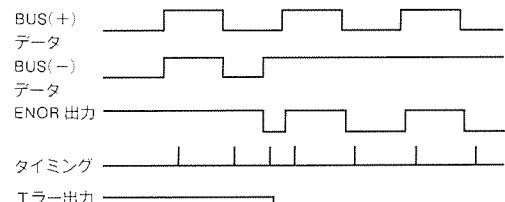

### 自動車用 LAN コントローラ、トランシーバー IC

岡本 泰・在本昭哉・菊山誠一郎・高井一兆・村松菊男

三菱電機技報 Vol. 67・No. 3・p. 54~58 (1993)

LAN コントローラ用 IC (M64100TFP) 及び LAN トランシーバー用 IC (M59330P) は、自動車内の電子ユニット間でデータ通信を行う上で、自動車 LAN システムの応答性の向上、確実な通信の確保を目的として開発されたデバイスである。これらの IC の機能概要を説明するとともに、通信プロトコル (SAE-J1850)、自動車 LAN システム、及び将来の自動車用 LAN システムへの展開について述べる。

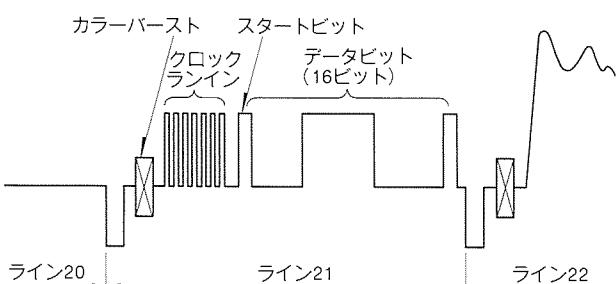

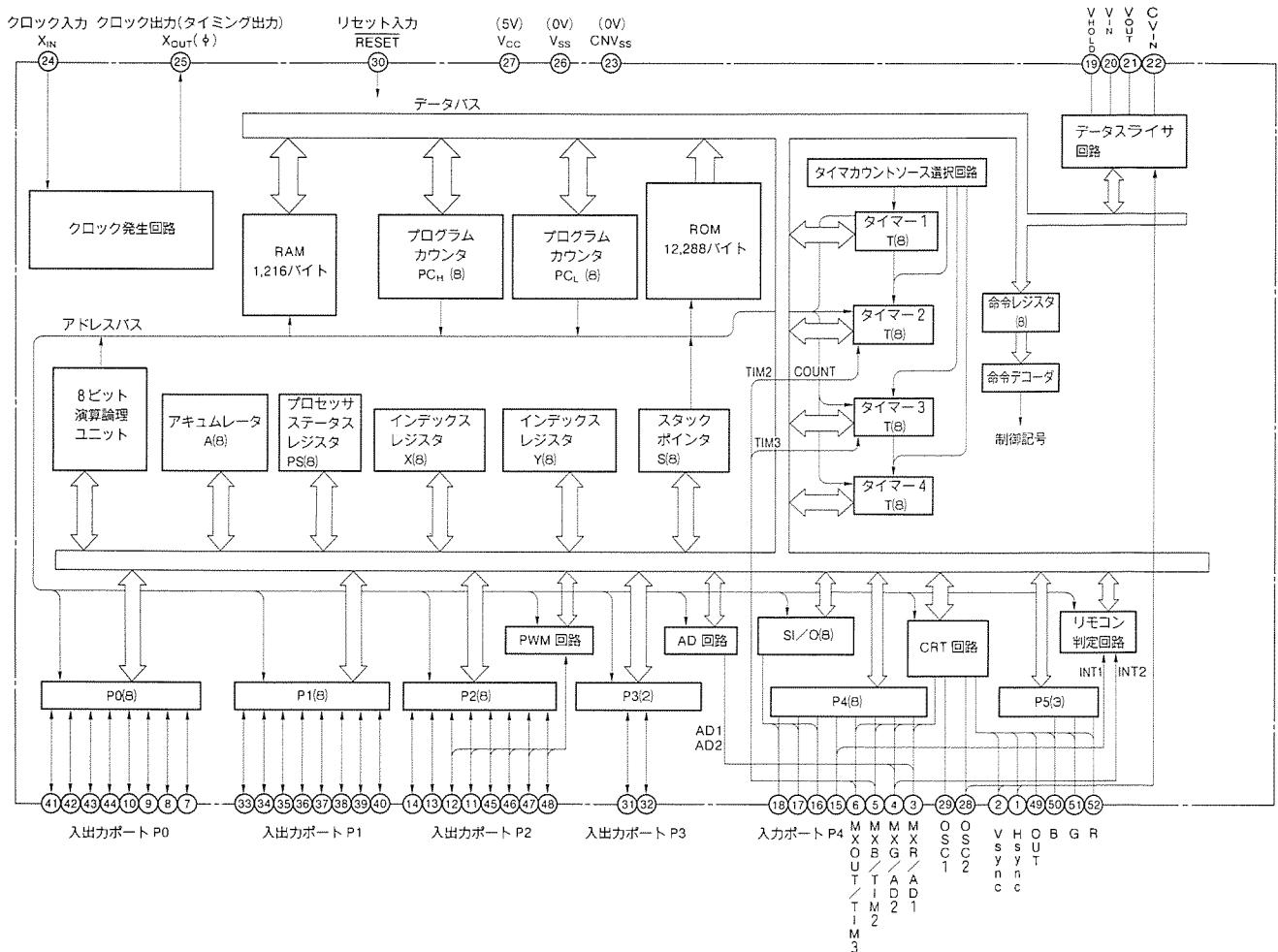

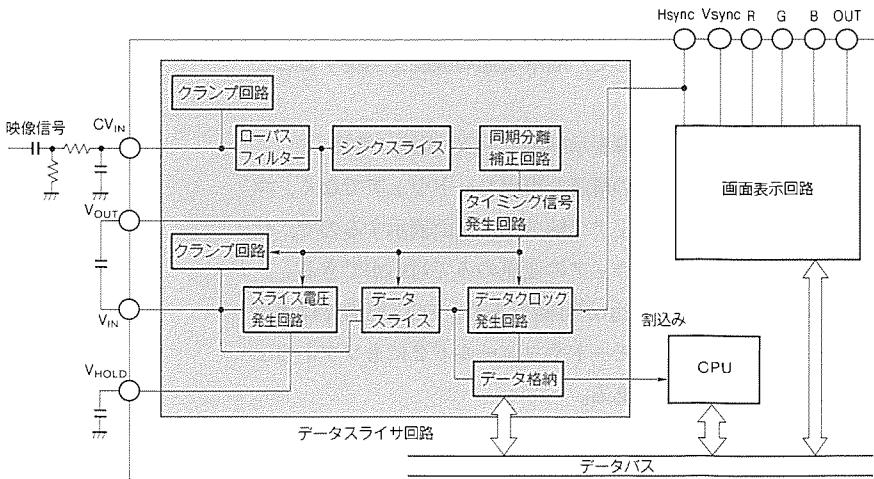

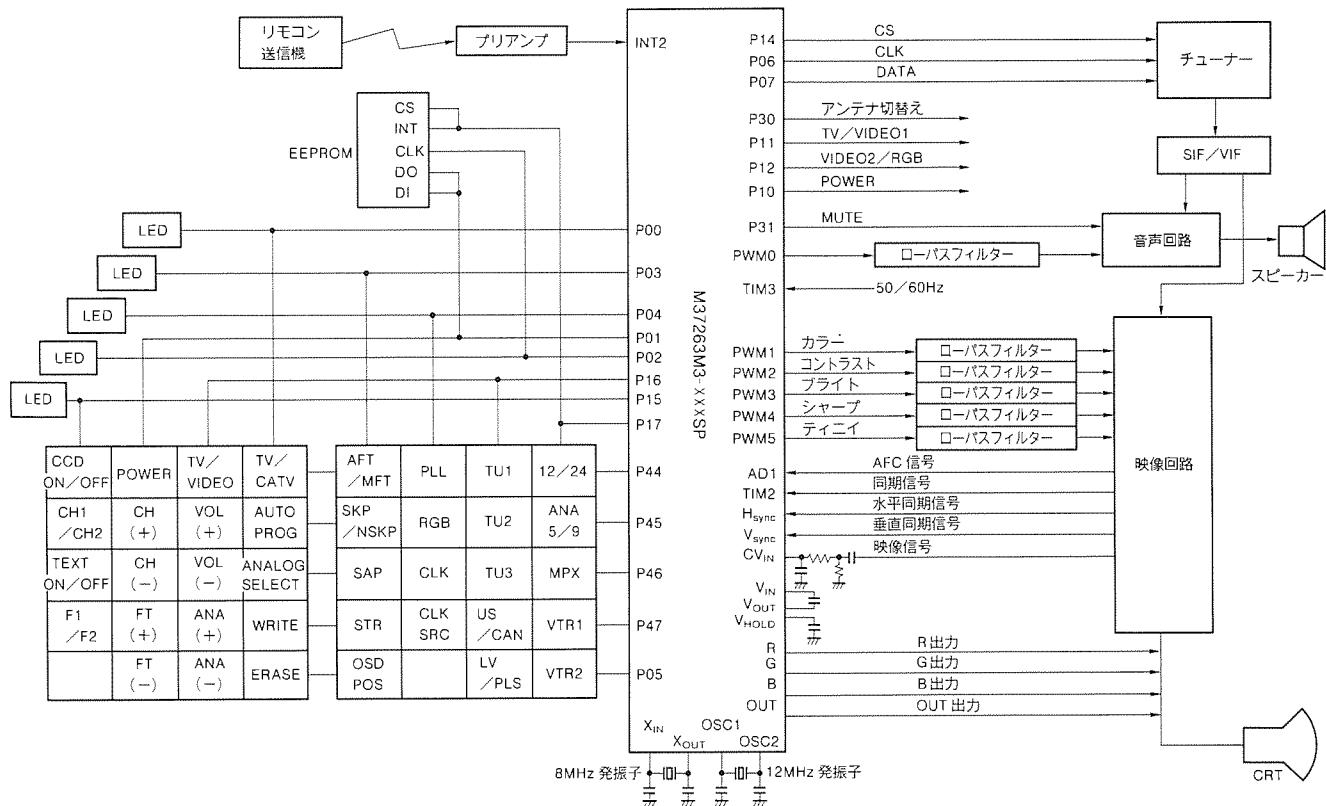

### クローズドキャプションコントロール用マイクロコンピュータ

藤高繁明・松本誠之・高橋直樹・上村省一・木村方昭

三菱電機技報 Vol. 67・No. 3・p. 59~63 (1993)

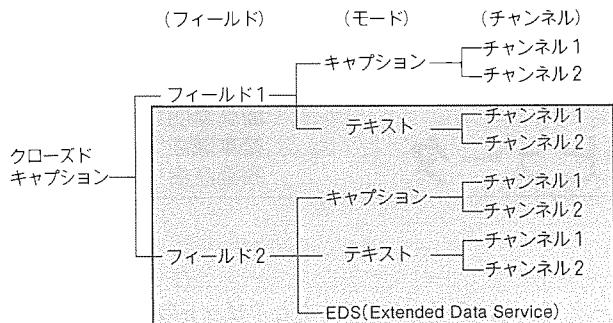

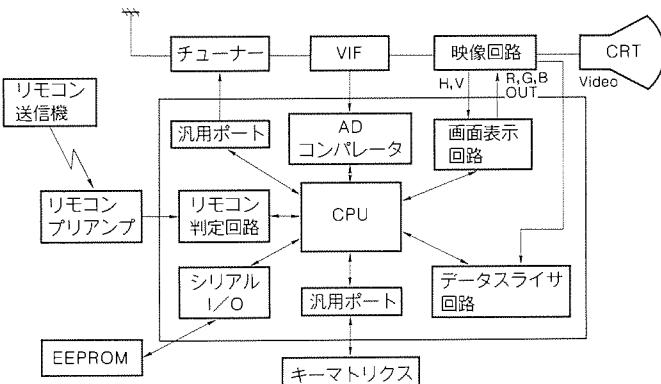

米国におけるクローズドキャプション (Closed Caption) 放送用デコーダに対応した TV 用 CMOS マイコンを開発した。

この製品は、映像信号内に多重されるキャプションデータを抜き取るためにのアナログ回路と、キャプションデータをデコードし、データに応じて TV 画面上に字幕を表示する画面表示回路を内蔵し、FCC (Federal Communications Commission) の規格に準拠した機能をもつシングルチップマイコンである。

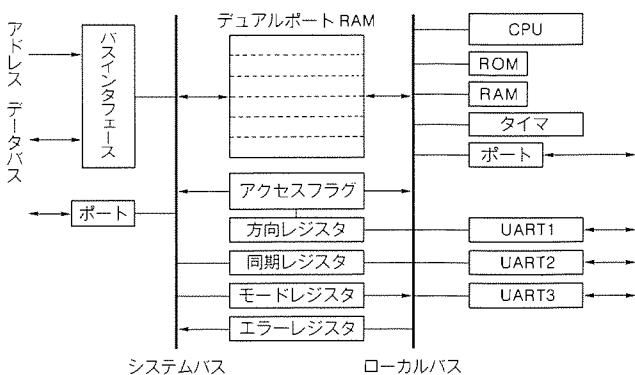

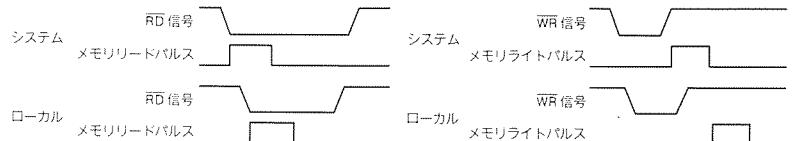

### プロトコル制御用マイクロコンピュータ

林 良紀・倉持昌司・竹内 稔・広川祐之

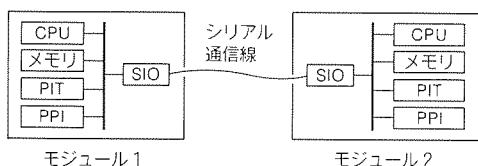

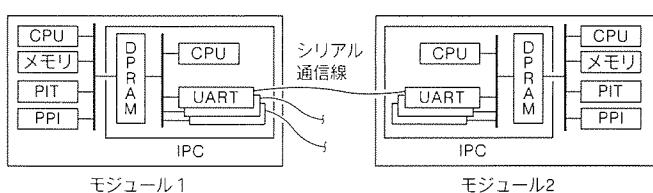

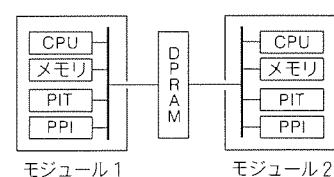

三菱電機技報 Vol. 67・No. 3・p. 64~66 (1993)

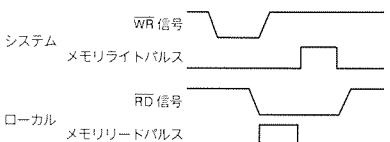

マルチプロセッサシステムのプロセッサ間のデータ通信を容易化するプロトコルコントローラを開発した。プロセッサの高速化に対応して、バスインターフェースの高速化を行い、16ビットマイコン MELPS 7700 シリーズに直接接続可能である。通信手順の制御は内蔵されている 8 ビットマイコンで行うため、ユーザーがプログラムによって様々なプロトコルを設定できる。さらに、CRC によるエラー検出機能をもつため、通信の高速化と信頼性の向上を同時に可能とした。

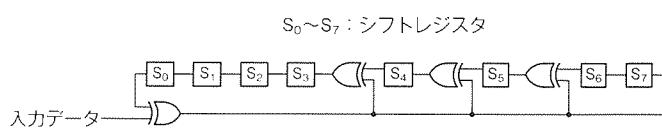

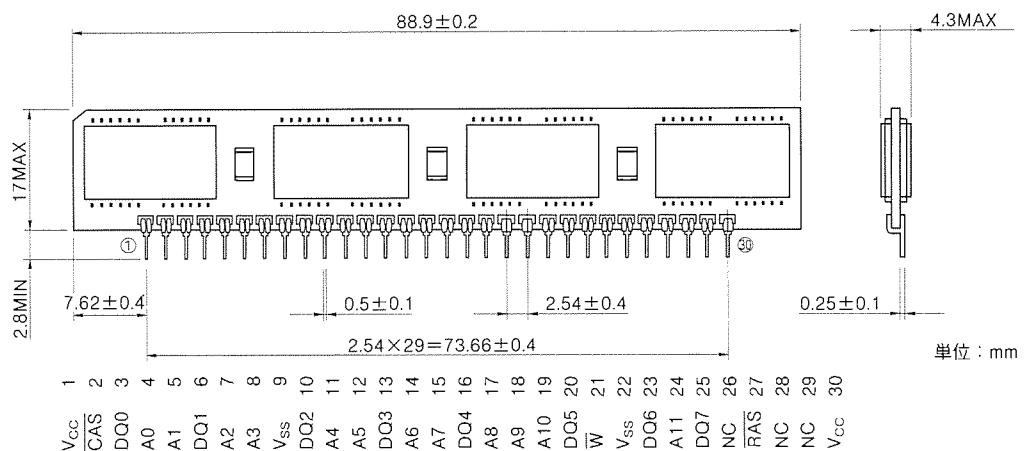

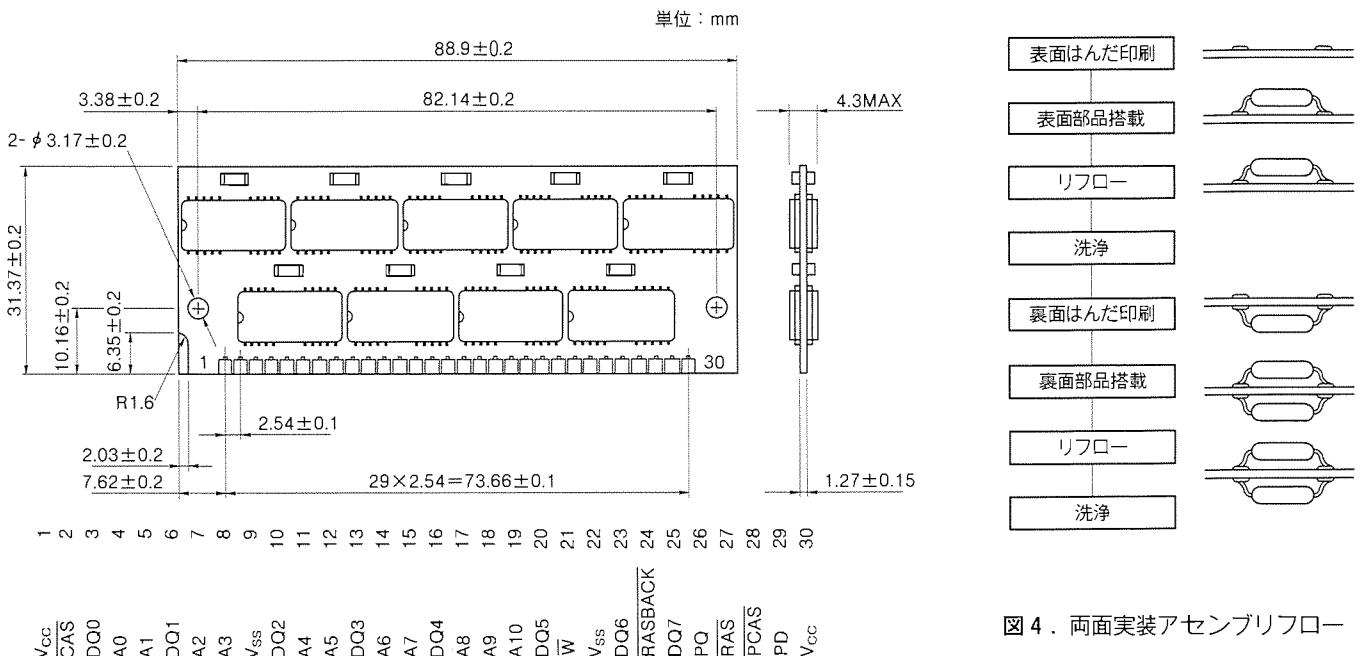

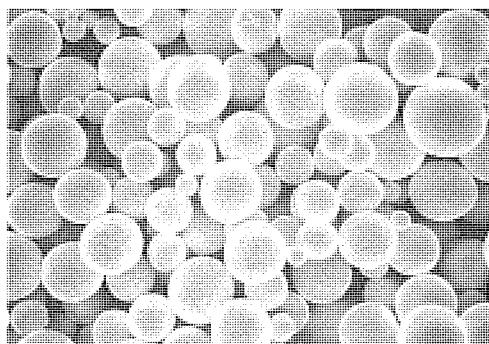

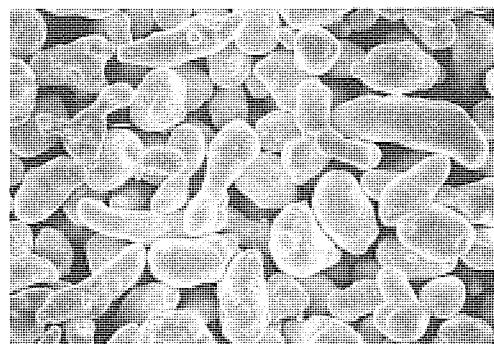

### 高速高密度 TSOP メモリモジュールシリーズ

田原次夫・上村俊一

三菱電機技報 Vol. 67・No. 3・p. 67~71 (1993)

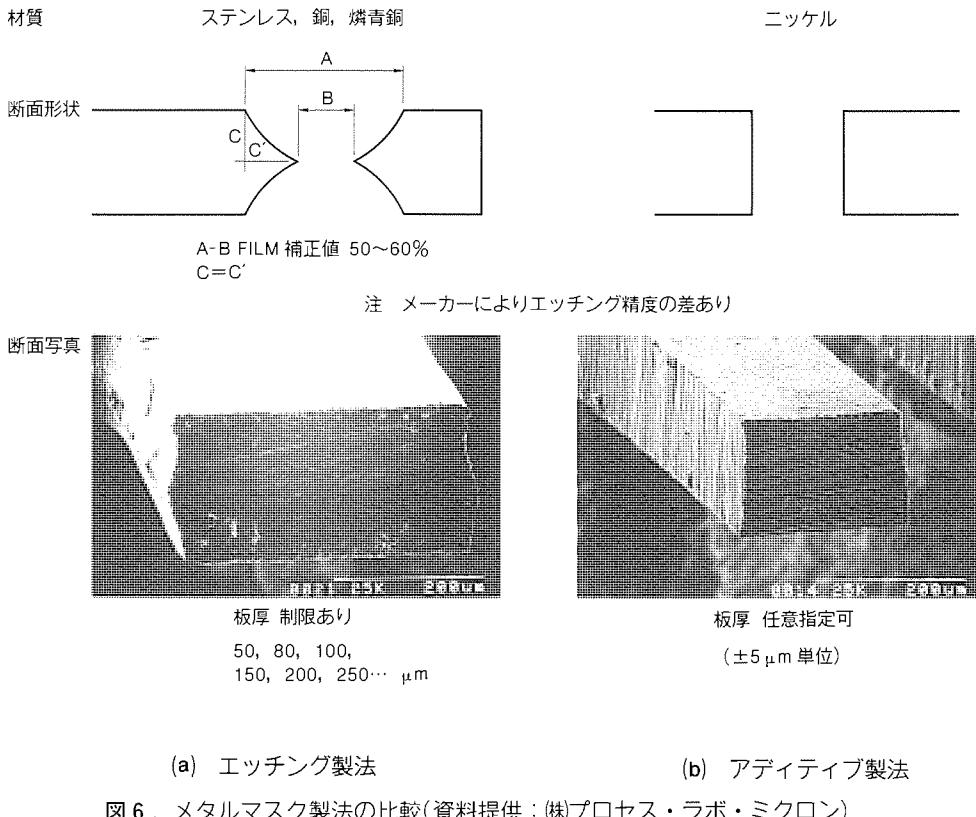

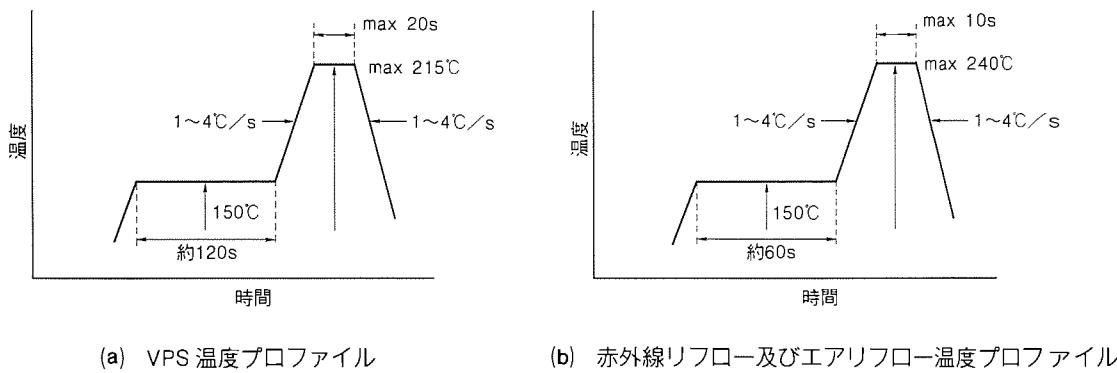

高速高密度 TSOP メモリモジュールシリーズ (DRAM, 中速 SRAM 及び高速 SRAM 搭載) について、製品概要・特長及び製品動向の紹介を行い、TSOP 実装時のはんだ成分及びプリント基板へのはんだ印刷時のメタルマスクの実施例を紹介するとともに、TSOP 実装時の注意事項を説明する。また、TSOP パッケージとプリント基板との熱膨張係数の差に起因する、温度サイクルの信頼性を向上するための改善対策を紹介する。

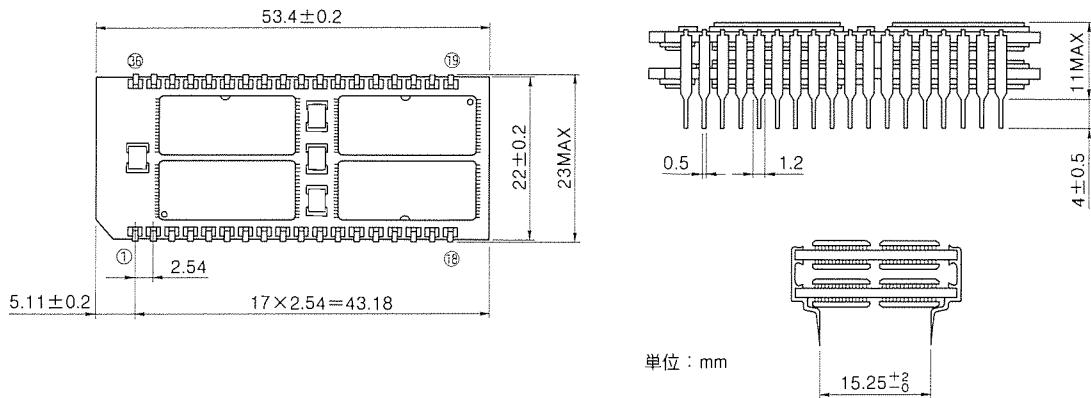

### ミックスメモリカード

田渕正行・木村正俊・渡辺忠勝・白土修一

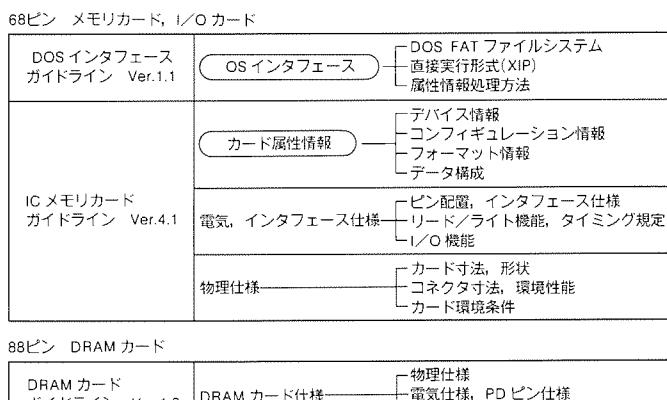

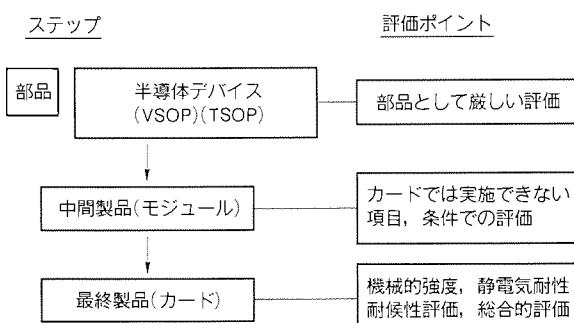

三菱電機技報 Vol. 67・No. 3・p. 72~75 (1993)

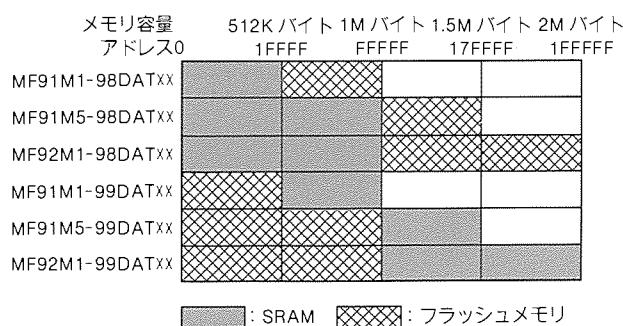

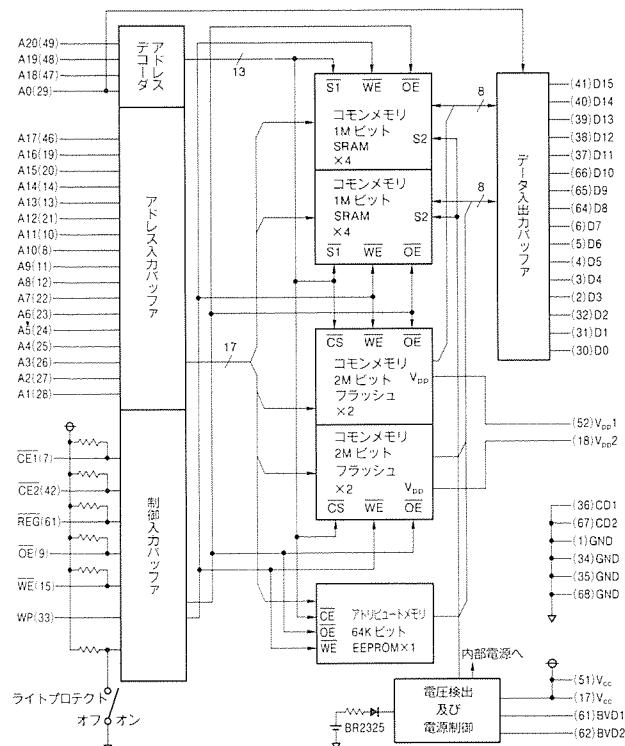

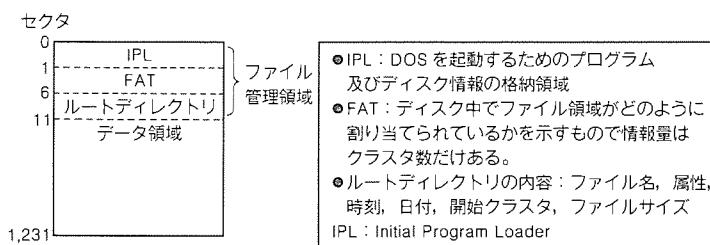

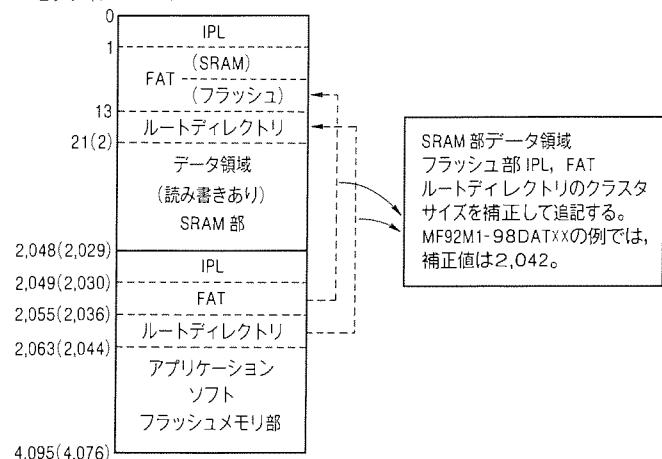

メモリカードは、携帯用機器の記憶装置として幅広く用いられているが、最近ではカードに対する要求も、機器の用途ごとに多様化している。このニーズにこたえるため、電気的に書き込み及び消去ができるフラッシュメモリと高速で読み書きができる SRAM を組み合わせ、それぞれの長所を生かした JEIDA 準拠のミックスメモリカードを開発した。開発に当たっては、IC カードスロットが一つのみの携常用機器の利便性向上を考慮した。

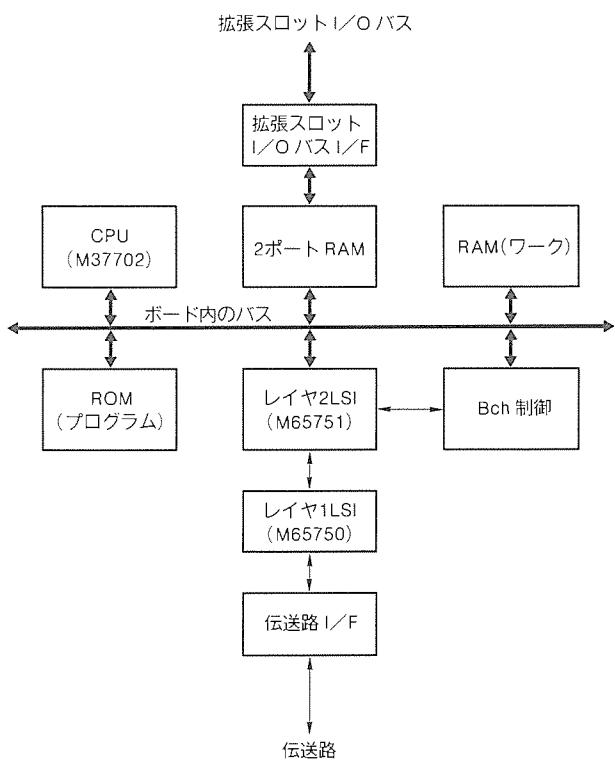

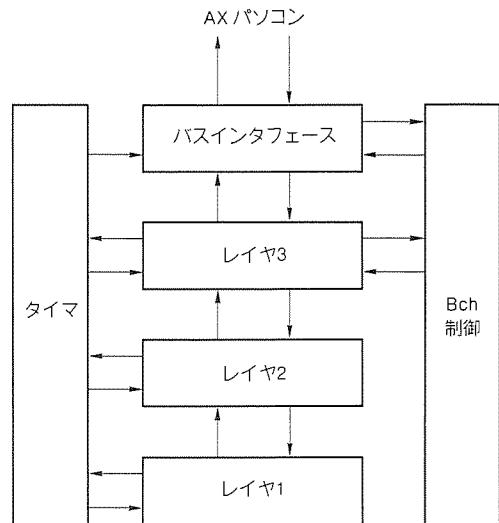

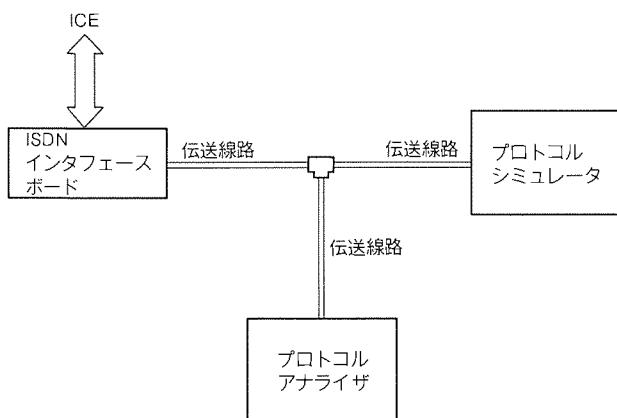

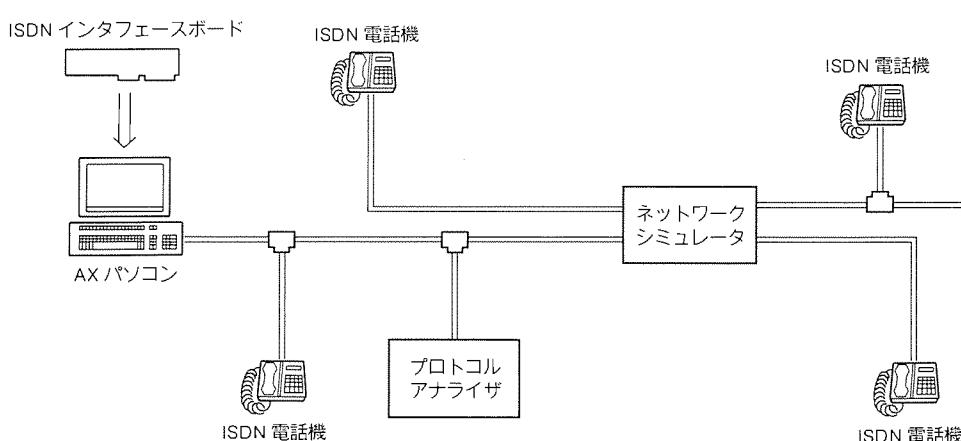

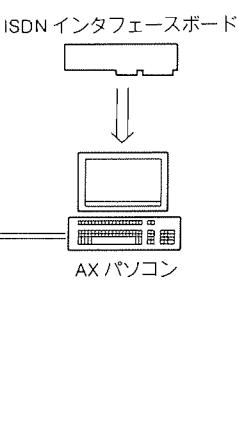

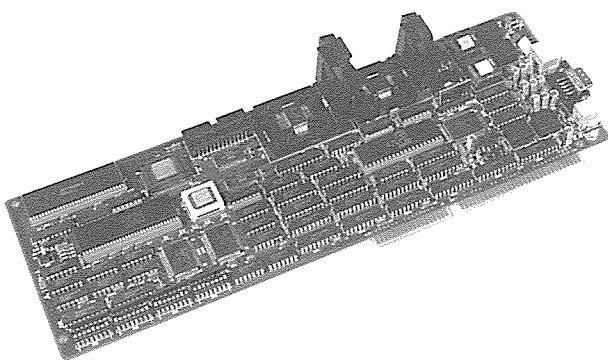

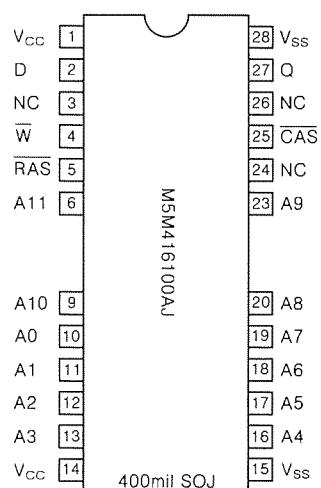

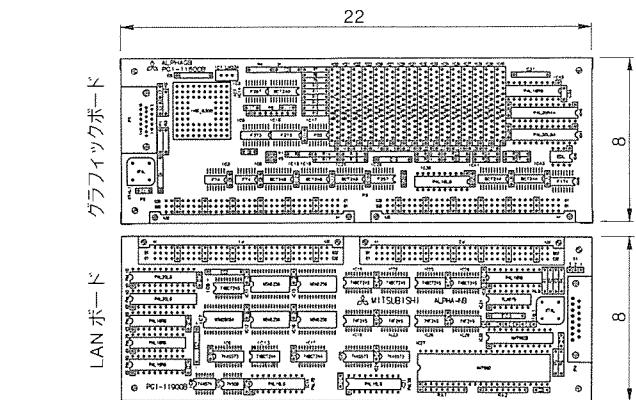

### ISDN インタフェースボード

中林竹雄・蔵永 寛・後藤宏二・木村隆一・宮城 明・小林和男

三菱電機技報 Vol. 67・No. 3・p. 76~79 (1993)

ISDN 用のインターフェースボードを開発した。ハードウェアとしては、CPU に 16 ビットワンチップマイコン (M37702) を用い ISDN 用 LSI として、レイヤ 1 LSI (M65750), レイヤ 2 LSI (M65751) を用いた。ソフトウェアについては、リアルタイムモニタを使用し、インターフェース機能を複数のタスクにより実現した。本ボードを AX パソコンに装着し、疑似ネットワークを用いて ISDN 通信の機能を確認した。

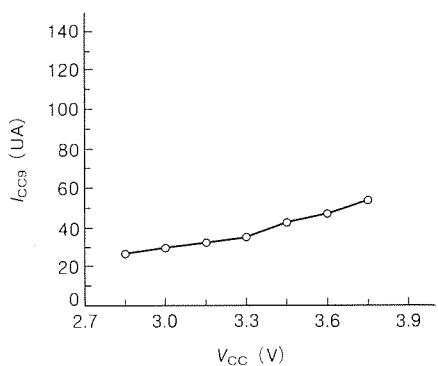

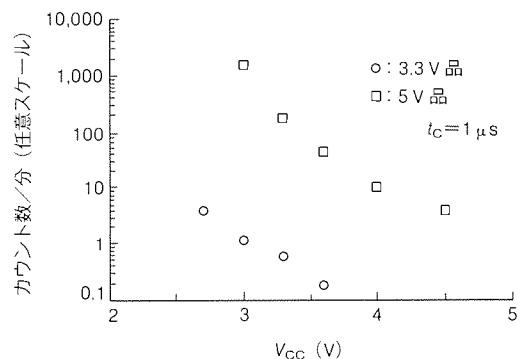

### 5.0V/3.3V版第二世代16Mビット DRAM

宮元崇行・梶本 毅・森 茂・野崎雅彦・源城英毅

三菱電機技報 Vol. 67・No. 3・p. 80~83 (1993)

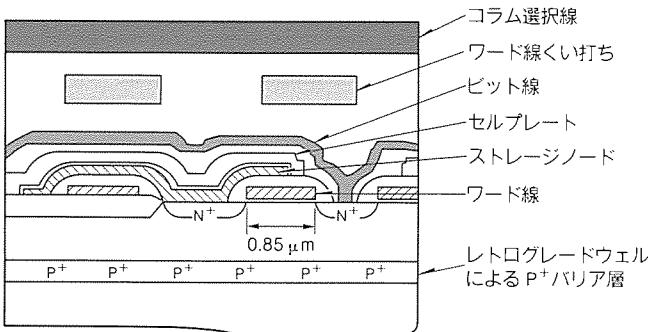

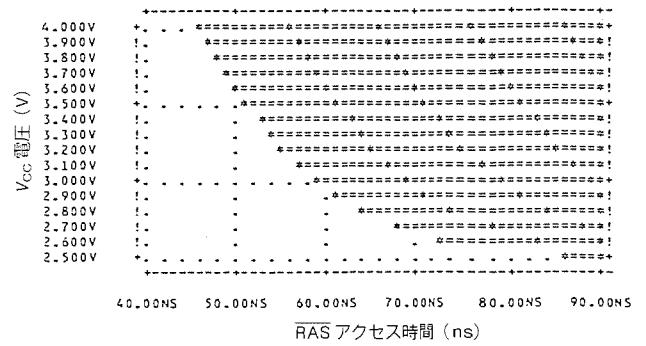

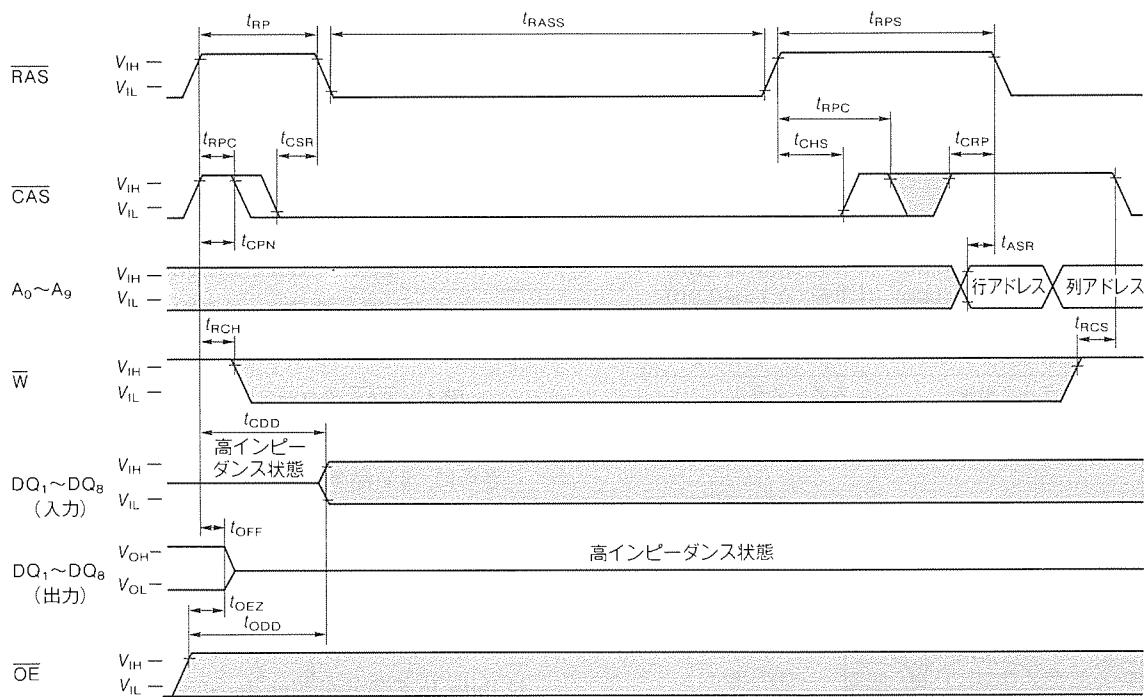

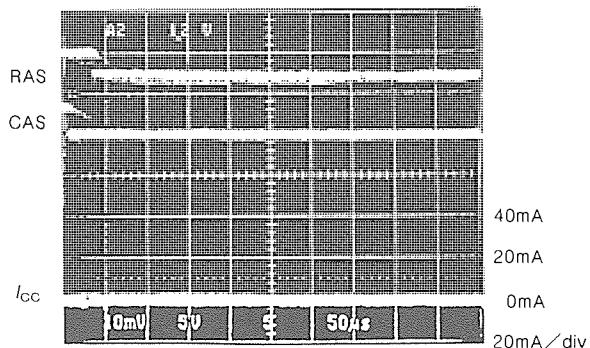

16M ビット DRAM 第二世代品を開発した。ビット構成は ×1, ×4, ×8 の 3 種類である。パソコン等のバッテリ駆動化に対応するため、0.5 μm 微細加工、レトログレードウェルなどのプロセス技術と内部電源回路のローパワー化などの回路技術を採用した。これにより、電源電圧 3.3V でも高速アクセス、低ソフトエラー率を実現した。セルフリフレッシュ機能などの新機能も追加し、電源電圧 3.3V 版の製品も系列化した。

### ブロック消去可能な高速 4 M ビットフラッシュメモリ

野口健二・大川 実・山本 誠・新井 肇・伊庭智久

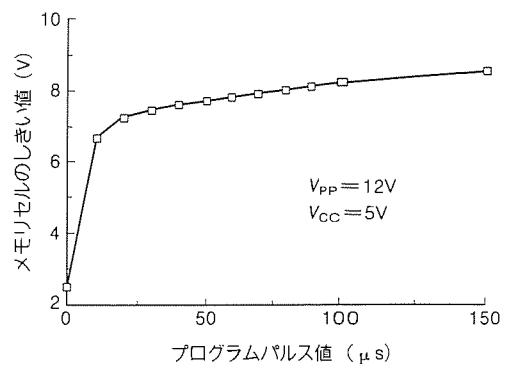

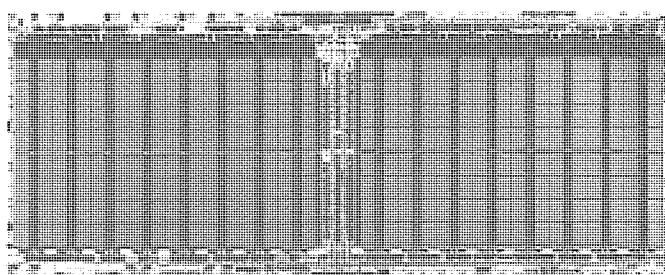

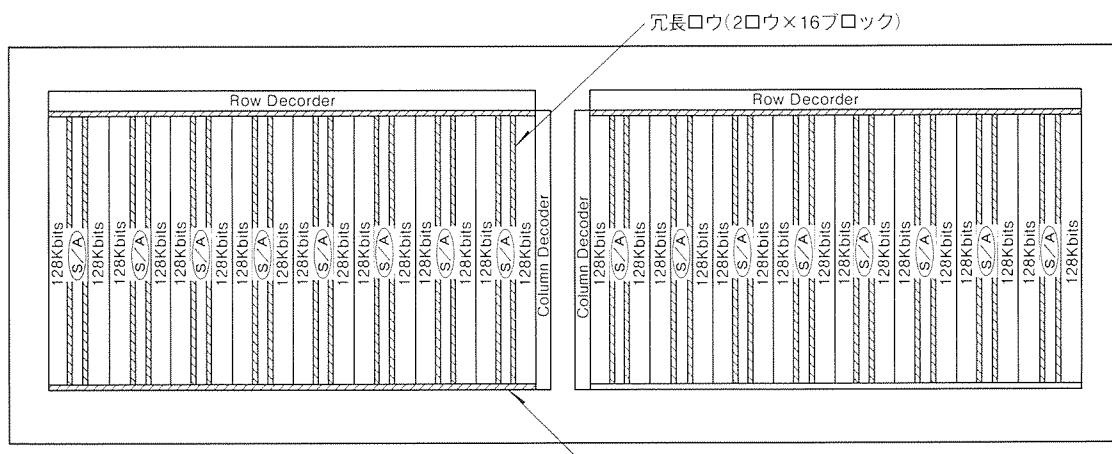

三菱電機技報 Vol. 67・No. 3・p. 84~87 (1993)

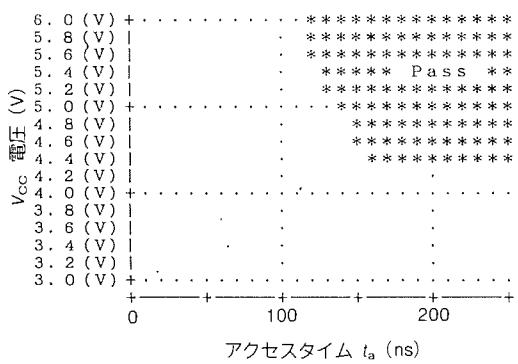

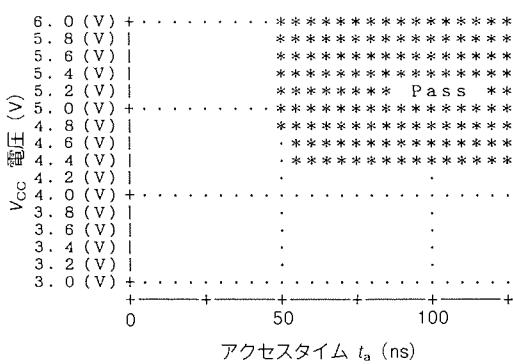

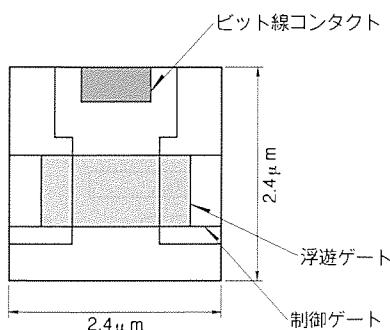

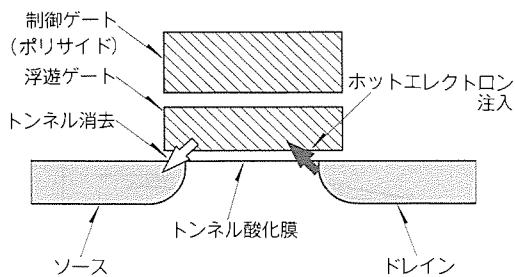

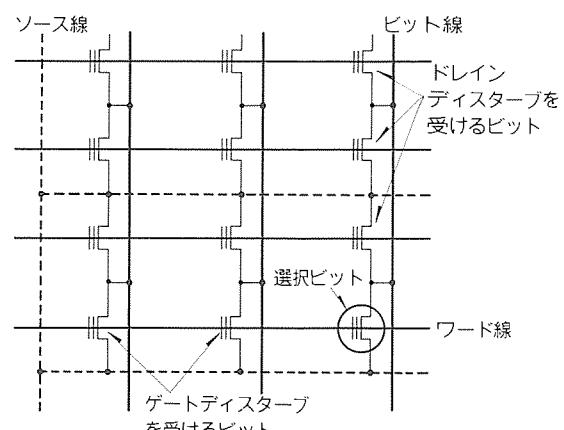

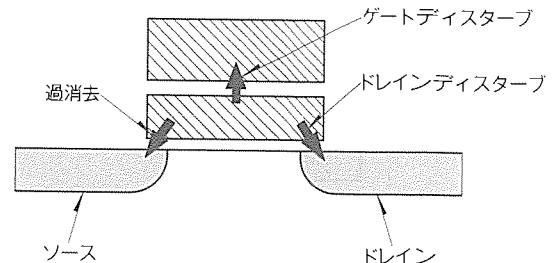

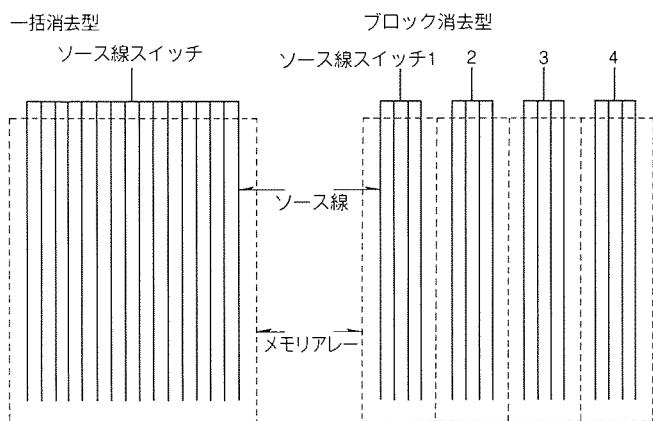

電気的に一括及びブロック消去可能な 2 電源型 4 M ビット (512K 語 × 8 ビット / 256K 語 × 16 ビット) フラッシュメモリを開発した。0.7 μm ルールのツインウェル CMOS プロセスを用い、セルサイズは 2.4 μm × 2.4 μm で、チップサイズは 8.90mm × 10.25mm である。パッケージは 44 ピン SOP, 48 ピン TSOP を用意した。アクセスタイムは、100, 120, 150ns の高速品 3 品種をそろえた。

# Abstracts

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 67~71 (1993)

## High-Speed, High-Density TSOP Memory Module Series

by Tsugio Tabaru & Shun'ichi Uemura

The article describes the features and mounting procedures for Mitsubishi high-speed high-density TSOP memory modules, which incorporate DRAM and medium- and high-speed SRAM devices. The solder-printing process for PCB mounting is described, including details of the solder paste composition, and examples of metal masks used for solder printing are provided. Procedures are described for reducing the effects of differences in the thermal expansion coefficients of the TSOPs and the PCBs. These measures increase the thermal cycle reliability of the mounted PCBs.

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 72~75 (1993)

## A Mixed Memory Card

by Masayuki Tabuchi, Masatoshi Kimura, Tadakatsu Watanabe & Shuichi Shiratsuchi

Memory cards are currently enjoying widespread use in handheld and portable electronic equipment; however, demand has recently diversified. The corporation has developed a JEIDA-compliant mixed-memory card that combines electrically writable and erasable flash memory with high-speed SRAM. By use of this card, many applications previously requiring two card slots can be implemented using a single card, enhancing equipment portability.

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 76~79 (1993)

## An ISDN Interface Board

by Takeo Nakabayashi, Hiroshi Kuranaga, Koji Goto, Ryuichi Kimura, Akira Miyagi & Kazuo Kobayashi

The corporation has developed an ISDN interface board. The hardware includes a M37702 16-bit monolithic microprocessor, the M65750 ISDN Layer 1 LSI processor and the M65751 ISDN Layer 2 LSI processor. The software includes a realtime monitor and interface functions that are realized as separate tasks. Performance of the interface board was verified by installation in AX personal computers and testing over a virtual ISDN network.

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 80~83 (1993)

## 5.0/3.3V Second-Generation 16Mb DRAM

by Takayuki Miyamoto, Takeshi Kajimoto, Shigeru Mori, Masahiko Nozaki & Hideki Genjo

A second-generation 16Mb DRAM has been developed that offers 5.0/3.3V operation and is available with 1,4 and 8-bit word organizations. The  $0.5\mu m$  microlithography process, retrograde well fabrication and low-power design optimize performance in battery-operated personal computers. The new DRAM realizes high-speed data access and a low soft error rate under 3.3V operation, and has a self-refresh function.

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 84~87 (1993)

## 4Mb Flash Memories with a Block Erase Function

by Kenji Noguchi, Minoru Okawa, Makoto Yamamoto, Hajime Arai & Tomohisa Iba

The corporation has developed dual-power-supply 4Mb flash memory devices that allow electric erasure of data chips or entire blocks in a single operation. The memory is organized as either 512k 8-bit words, or 256k 16-bit words, and is available with 100, 120 and 150ns access times. The devices are implemented in a  $0.7\mu m$  twin-well CMOS process, employing a cell size of  $2.4 \times 2.4\mu m$  and a chip size of  $8.90 \times 10.25mm$ . The packages are 44-pin SOPs and 48-pin TSOPs.

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 46~49 (1993)

## A BiCMOS LSI for Broadband ISDN

by Masahiro Ueda, Toshiaki Hanibuchi, Keiichi Higashitani, Hideo Kawabata & Yasuo Tobita

BiCMOS technology--allowing bipolar transistors to be configured with CMOS devices in the same silicon layer--has been used to realize high-speed SRAM and for other special purposes. The authors have employed BiCMOS technology to develop LSIs for broadband ISDN applications. A user-network interface LSI comprising TTL and ECL circuits has been developed using a gate array method.

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 50~53 (1993)

## A Speech Codec IC for Mobile Telecommunications

by Toru Kengaku, Eiichi Teraoka, Ikuo Yasui, Toshiki Fujiyama & Takeshi Tokuda

The corporation has developed a monolithic device combining a 24-bit floating point digital signal processor, 13-bit D/A and A/D converters, and a large memory area for use in digital mobile telecommunications equipment. The device, containing 1.3 million transistors, was implemented by a one micron CMOS process using two-layer polysilicon and two-layer metalization. It features a fast 60ns machine cycle and low-power 490mW dissipation when executing vector-sum excited linear-prediction (VSELP) functions. It is intended to perform signal processing for high-efficiency speech codecs.

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 54~58 (1993)

## LAN Control and Transceiver ICs for Automotive Use

by Yasushi Okamoto, Akiya Arimoto, Seiichiro Kikuyama, Kazuyoshi Takai & Kikuo Muramatsu

The corporation has developed two ICs for automotive use that implement the SAE-J1850 LAN protocol. The M64100TFP LAN controller IC and M59330P LAN transceiver IC improve the response and reliability of the automotive LAN systems used to convey data between electronic control units. The article introduces these devices, the SAE-J1850 protocol, automotive LAN systems and future prospects for automotive LAN development.

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 59~63 (1993)

## A Closed-Caption Decoder and Display IC

by Shigeaki Fujitaka, Seiji Matsumoto, Naoki Takahashi, Shoichi Kamimura & Masaaki Kimura

The corporation has developed a monolithic CMOS closed-caption decoder IC for receiving U.S. telecasts. The device comprises a microprocessor, an analog signal section for demodulating caption data imposed on the video signal and a circuit that displays the decoded data in a text band on the TV screen. The device complies with FCC regulations.

Mitsubishi Denki Giho: Vol. 67, No. 3, pp. 64~66 (1993)

## A Microcomputer for Protocol Control

by Yoshinori Hayashi, Masashi Kuramochi, Minoru Takeuchi & Masayuki Hirokawa

The corporation has developed a protocol controller to simplify implementing interprocessor communications in multiprocessor systems. The device has a high-speed bus interface that allows direct connection to microprocessors of the Mitsubishi MELPS 7700 Series. Since the device employs an 8-bit microcomputer to implement the communications protocol, it can be user-programmed for a variety of protocols. The device also includes CRC error detection functions that raise communications speed and reliability.

## アブストラクト

### 4 Mビット バイトワイド／ワードワイド DRAM ——バッテリ駆動型システム用 3.3V 版——

富上健司・豆谷智治・長山安治・長友正男

三菱電機技報 Vol. 67・No. 3・p. 88~91 (1993)

ノート型パソコン等のバッテリ駆動型システムに適したセルフリフレッシュ機能付き低電圧・低消費電力動作の×8 及び×16ビット構成4 M DRAM 製品を開発した。2層アルミ配線、 $0.6\text{ }\mu\text{m}$ 微細加工、レトログレードウェルプロセス及び新回路技術採用により、低電圧での高速アクセス及び耐ソフトエラー率等を含めて高性能・高信頼性を実現した。

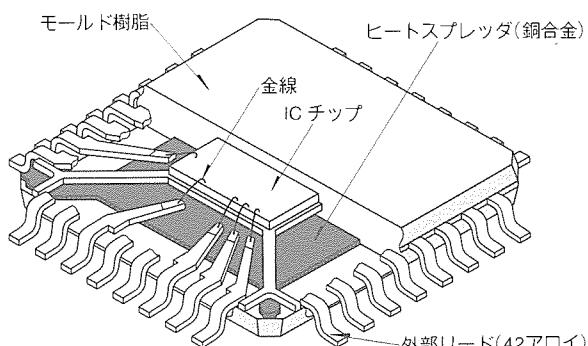

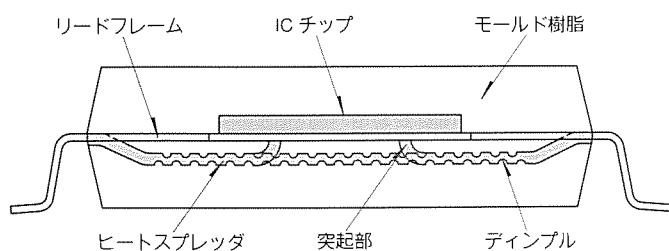

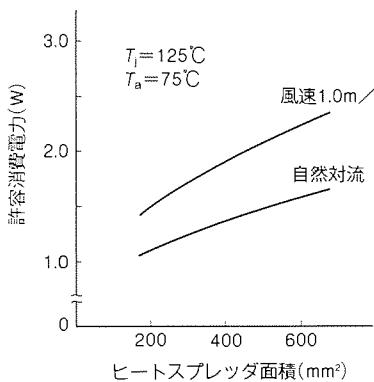

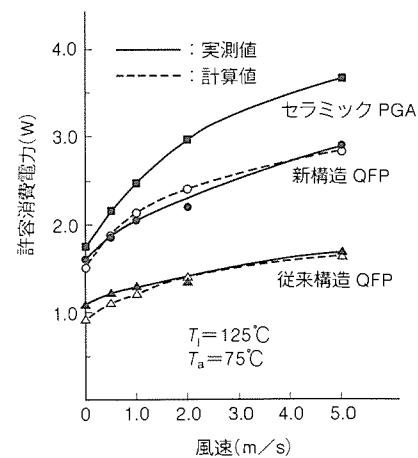

### 高放熱プラスチック QFP に封止した 32ビットマイクロプロセッサ

中野直佳・樋口徳昌・平井達也・中村伸哉・倉野新一

三菱電機技報 Vol. 67・No. 3・p. 92~95 (1993)

TRON仕様32ビットマイクロプロセッサ M32／100の高放熱プラスチック QFP 品を開発した。20MHz動作時の最大消費電力が $1.3\text{W}$ である M32／100チップを封止するため、リードフレーム直下にヒートスプレッダを配置し、パッケージの低熱抵抗化を図った。また吸水率の低い樹脂の使用とモールド時の構造物位置のファイン制御により、パッケージ信頼性が向上し、機器組込み制御ボードの小型・低価格化が期待できる。

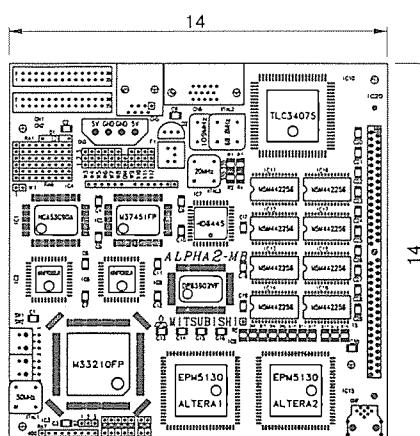

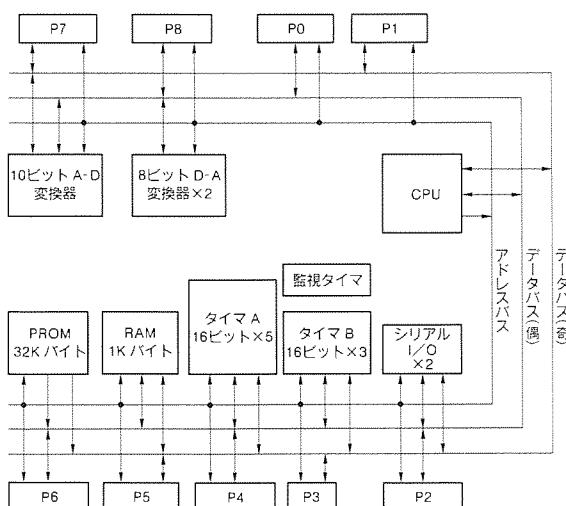

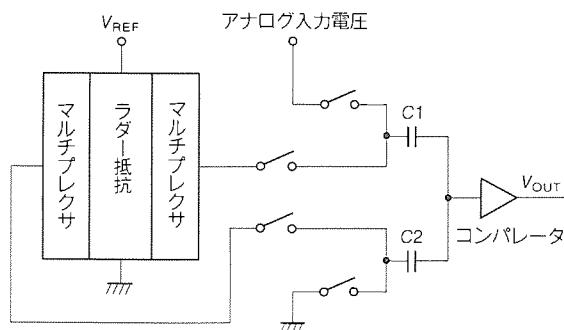

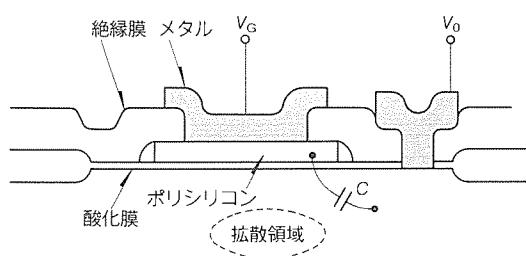

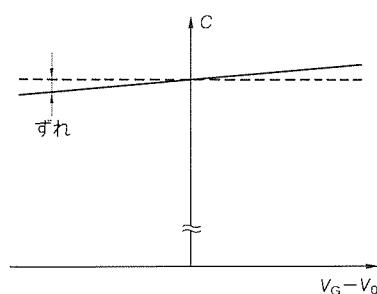

### アナログ機能を強化した 16ビットワンチップマイクロコンピュータ

上木雄詞・神崎照明・樋口光誠・高橋 肇・藤原俊夫

三菱電機技報 Vol. 67・No. 3・p. 96~99 (1993)

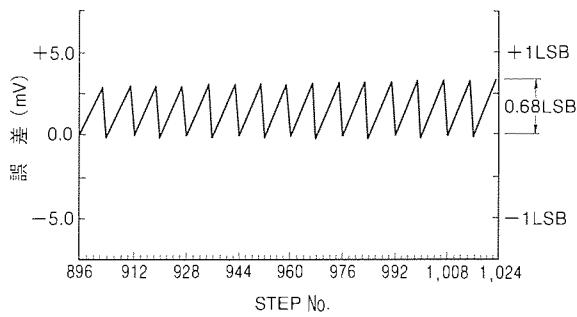

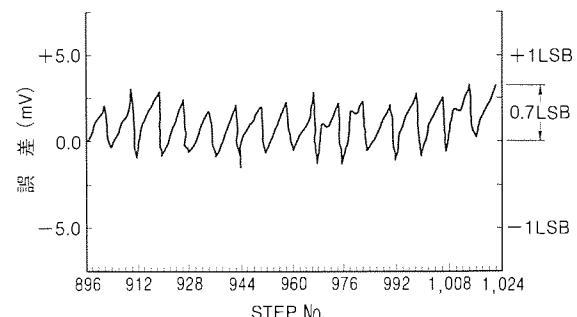

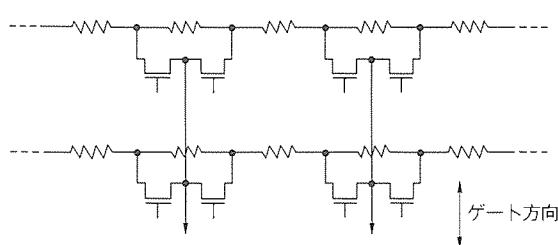

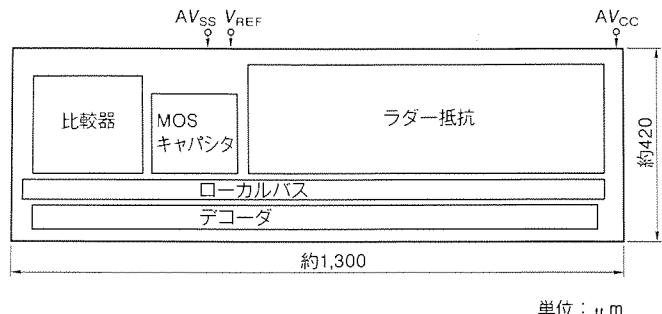

汎用16ビットマイクロコンピュータ MELPS 7700の上位シリーズとしてアナログ機能(A-D変換器、D-A変換器)を強化した製品を開発した。内蔵A-D変換器は、分解能8ビットから10ビットに高め、またD-A変換器は従来内蔵していなかったものを新規に内蔵させた。A-D変換アナログ回路(ラダー抵抗、比較器等)のセルサイズは、 $1,300\text{ }\mu\text{m} \times 420\text{ }\mu\text{m}$ とコンパクトなサイズにしている。

# Abstracts

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 88~91 (1993)

A 4Mb 3.3V Low-Power Byte-Wide and Word-Wide DRAM for Battery Operation

by Kenji Tokami, Tomoharu Mometani, Yasuji Nagayama & Masao Nagatomo

The corporation has developed 4Mb DRAMs with 8- and 16-bit organization, low power consumption, 3.3V operation and self-refresh functions for notebook-size personal computers and other battery-powered applications. The devices are implemented employing a  $0.6\mu\text{m}$  CMOS process with retrograde wells and two-layer metalization to achieve low-voltage operation, fast access and low soft-error rate.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 92~95 (1993)

A 32-Bit Microprocessor in a Plastic QFP with a Heat Spreader

by Tadayoshi Nakano, Noriaki Higuchi, Tatsuya Hirai, Shinya Nakamura & Shin'ichi Kurano

The corporation has developed a high-dissipation plastic QFP package for the M32/100 32-bit TRON-specification micro-processor. A heat spreader immediately under the lead frame lowers the package's thermal resistance, making it possible to dissipate the required 1.3W maximum when the chip operates at 20MHz. Package reliability is improved through use of a plastic resin with low moisture absorption and through precise die positioning during the encapsulation process. The QFP is expected to reduce the size and cost of embedded controller boards.

Mitsubishi Denki Gihō: Vol. 67, No. 3, pp. 96~99 (1993)

The Development of a 10-Bit Analog-to-Digital Converter for 16-Bit Single-Chip Microcomputers

by Yuji Ueki, Teruaki Kanzaki, Kosei Higuchi, Hajime Takahashi & Toshio Fujiwara

The corporation has developed new top-end models of its 16-bit MELPS 7700 Series microprocessors with internal A/D and D/A converters. The resolution of the A/D converter has been boosted from 8 to 10 bits. The analog circuit containing the resistance ladders and comparators has a compact cell size of  $1.3 \times 0.4\text{mm}$ . The internal 8-bit D/A converter is a new addition. The article reports on the steps used to miniaturize the A/D converter.

## 卷頭言

### 半導体新時代

常務取締役

電子デバイス事業本部長

新良 由幸

半導体はトランジスタの発明以来、集積回路(IC)として驚異的な速度で技術開発と事業拡大を達成してきた。例えば、DRAMは日本においては“テクノロジードライバ”と位置づけられ、メモリ容量が3年ごとに4倍という速度で開発が進展してきた。しかし、世の中の常識よりもはるかに速い進歩は、当然ながら何時かニーズを追い越すこととなる。現に、一部の用途においてニーズを越え始めたとの論議もある。また、最近見え始めている多世代同居、あるいは最先端機種の量的な立ち上がり鈍化傾向等も進歩の速度と無関係ではあるまい。

そして、今や半導体を使用していない製品を見付けることが至難の状態になってきている。このように用途が広くかつ深くなるにつれ、ICに対して単一機能(例えばDRAMのメモリ機能)のみでなく複合化した機能が要求され始めている。初期のトランジスタを“点”とすれば単一機能のICは“線”，複合機能のICは“面”に例えることができよう。これが本号の主題の“システムLSI”である。

このシステムLSIは目前に迫りつつあるマルチメディア時代の主役となるべき半導体技術である。昨今、マルチメディアに関しては“実体がよく分からない”とか“まだまだ先の話”とかの議論もあるが筆者の見解はやや異なる。今、世界的に核家族化、都市化が進むとともに個人生活の上で人間関係が疎遠になっている悩みを多くの人が抱いている。それを少しでも緩和しようとするマルチメディアは既に確実に進行しつつある。また、通常の業務においても人的リソース、その他の面からマルチメディアが必須になりつつあることが認識され始めている。やがて近い将来、これらは巨大な市場に育つ期待がある。それらのシステムを安価

に、かつ使いやすい形で提供するためのキーデバイスがシステムLSIであると考える。

このような半導体の役割の質的な変化は“半導体新時代”的到来を実感させてくれる。要するに“作れば売れる”という供給者論理は成り立たず、“消費者の求める物は何か”を第一に考えるべき消費者論理の時代——それがむしろ正常な状態であるが——に突入しつつある訳である。その意味では、生産のための設備投資競争時代の終わりの始まりとも言える。

しかし、実はこの新時代への対応は、口で言うほど簡単ではない。システムLSIは顧客が構築しようとするシステムの中枢部そのものであり、責任が極めて大きいデバイスである。したがって、顧客の意図やノウハウを入念に理解し、双方向のコミュニケーションを密にしなければ開発は成功しない。すなわち、顧客とメーカーとの信頼が固くなければ進歩発展しえない技術である。この点がコモディティ製品との本質的な差である。

当社はこれに備えて、関西(北伊丹製作所)に集中していた技術拠点を一部分割り、昨年関東地区にも半導体技術センターを設立し着々と機能の充実を果たしつつある。また、同時にシステム研究所群の力を結集してシステムLSIの開発を加速する体制をも整えている。これらの充実により、総合メーカーとして永年蓄積してきた多くの分野の技術力をシステムLSIに具現化して世に問いたいと念願する次第である。

ユーザー各位の変わらぬ御指導、御鞭撻をお願い致します。

# システムオンチップ時代におけるVLSIの展望

## 1. まえがき

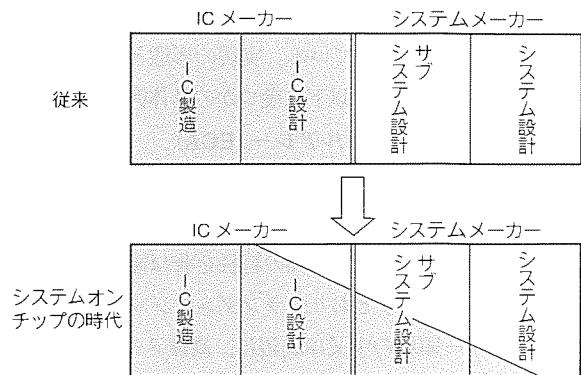

1947年にゲルマニウムトランジスタが世界で初めて実用化されて以来、半導体は目覚ましい発展を遂げてきた。特に1960年代から始まるシリコンモノリシックICの時代において微細化を中心とする技術の目覚ましい進歩によって性能と経済性が高められ、その結果、応用範囲が拡大しシステムの中におけるキーデバイスとして重要性をますます強めている。今や100万以上の素子を1チップに集積できるようになり、システムの中の主要部分が一つのシリコンの中に入るいわゆる“システムオンチップ”の時代を迎えた。これらVLSIを実現するためにはLSI設計技術面、システム設計技術面でICメーカーとユーザー(システムメーカー)との間で新しい役割分担が必要になってくる。

本稿では“システムオンチップ”時代におけるVLSIの展望について述べる。

## 2. システムの動向と半導体の進展

半導体のけん(革)引役である電子機器において、アナログからデジタルへの展開が始まっている。一般に自然界の

現象はアナログ信号であるため、これを取り扱う機器もアナログ処理が用いられてきた。しかしながら、コンピュータを代表とするデジタル処理によってアナログにはない新しい機能の実現が可能となってきた。一般にデジタル処理を行うと電子回路の複雑さと動作速度はアナログ処理の10倍以上を必要とするが、LSIの技術革新によって上記要求が経済的に実現できるようになったため、デジタル化が加速されてきた。図1にシステムのデジタル化の動向を示す。オーディオにおいてCDに代表されるようにデジタル処理によってひずみ、SN比特性やランダムアクセス機能が大幅に改善された。TV/VTRの画像処理においてもデジタル化してメモリに記憶した画像を様々に加工することによって特殊効果や画質改善が実現され、ハイビジョンへと進展している。

OA分野においても複写機及びプリンタ等においてデジタル化による高画質と多機能さが生かされており、さらに通信分野においてもネットワークのISDN(Integrated Service Digital Network)により、デジタル化が加速しようとしている。

また、システムの複合化も進んでいる。OAと通信(PPC

| システム \ 年  | 1980                        | 1985                                                                 | 1990                                 | 1995                     | 2000                      |

|-----------|-----------------------------|----------------------------------------------------------------------|--------------------------------------|--------------------------|---------------------------|

| オーディオ     | ▽ CD<br>音場制御                | ▽ DAT<br>衛星放送<br>PCM                                                 |                                      | ▽ DCC, MD<br>マイクロ<br>DAT |                           |

| TV        | ▽<br>シンセサイザチューナー            | ▽<br>文字多重<br>PIP IDTV クリア HDTV ワイド ディジタル<br>(小画面) ビジョン (MUSE) TV ル放送 | ▽<br>▽<br>▽<br>▽<br>▽                | ▽<br>▽<br>▽<br>▽         | ▽<br>▽                    |

| VTR       | ▽<br>デジタルサーボ                | ▽<br>デジタル特再                                                          | ▽<br>デジタル<br>信号処理                    | ▽<br>デジタル<br>記録          | ▽<br>デジタル<br>HD ムー<br>ル放送 |

| 複写機       | ▽<br>パーソナル                  | ▽<br>デジタル<br>カラー                                                     | ▽<br>デジタル<br>複合機<br>(FAX, LBP, PPC)  | ▽                        | ▽                         |

| プリンタ      | ▽<br>NLO 多ドット印字<br>プリント     | ▽<br>レーザープリント                                                        | ▽<br>PLD(画像記述語)による<br>アウトラインフォントプリント | ▽<br>フルカラー<br>プリント       | ▽                         |

| 伝送・交換系    | ▽<br>伝送路の<br>光ファイバ化         | ▽<br>ISDN ベーシック I/F<br>サービス開始                                        | ▽<br>グローバル ISDN                      | ▽<br>B-ISDN<br>サービス開始    |                           |

| 電話        | ▽<br>デジタル<br>電話             | ▽<br>DRAM 式 静止画<br>音声録音                                              | ▽<br>デジタル携帯<br>電話                    | ▽<br>PHP                 |                           |

| FAX       | ▽<br>帯域圧縮                   | ▽<br>G4機                                                             | ▽<br>デジタル<br>カラー                     | ▽<br>ISDN 用<br>FAX       |                           |

| FA(インバータ) | ▽<br>正弦波 PWM エアコン用<br>インバータ | ▽<br>オールデジタル<br>汎用インバータ                                              | ▽<br>DSP 応用<br>(ペクトル制御)              |                          |                           |

| 自動車       | ▽<br>エンジン制御                 | ▽<br>GPS<br>(ナビゲーション)                                                | ▽<br>電気自動車                           |                          | ▽<br>危険回避<br>制御           |

図1. システムのデジタル処理の発展

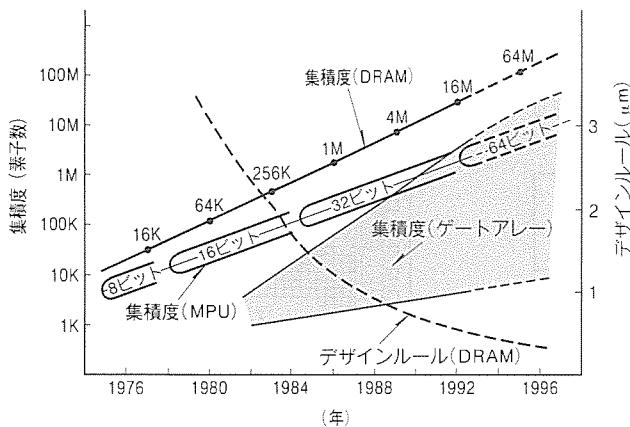

図2. 先端LSIの集積度の推移

+FAX), AVと通信(ニューメディア), コンピュータとAV(マルチメディアパソコン)等新しい機器が誕生しており、今後様々なマルチメディアインフォメーションシステムへと進展していくものと思われる。

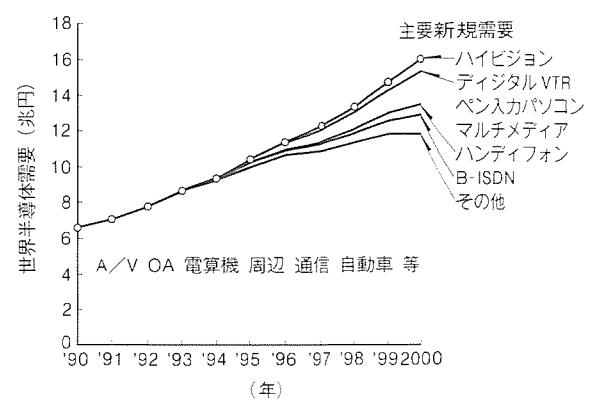

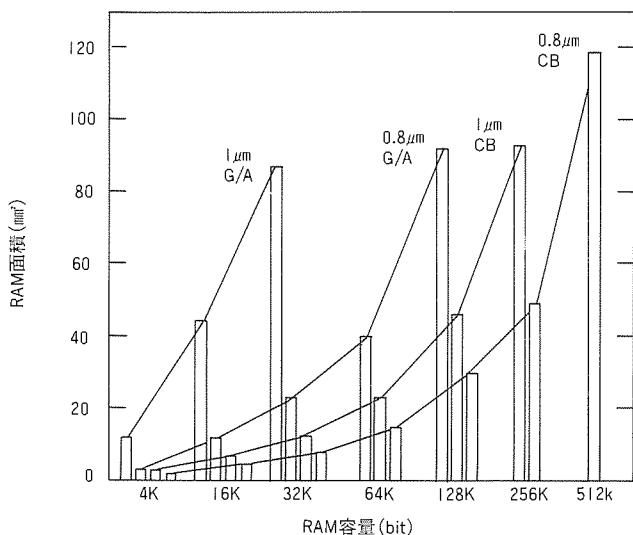

一方、半導体の技術革新は図2に示すとおり微細化において著しく、その結果集積度が飛躍的に増大し、今や1チップ当たりの集積度はメモリで1,000万、マイクロコンピュータやゲートアレーでは100万以上の素子が集積できるようになってきた。そのため、小規模な電子システムでは小信号電子回路を1チップにのせることが可能となり、LSIは使われるシステムごとの対応が必要になってくる。図3に半導体の用途別需要予測を示す。半導体は従来から微細化等の技術革新がもたらす経済性と用途の広がりによって高い成長を続けてきた。今後とも新市場対応の需要が期待され、従来にも増してシステムオンチップとしての対応が必要になってくる。

### 3. システムVLSIのための環境整備

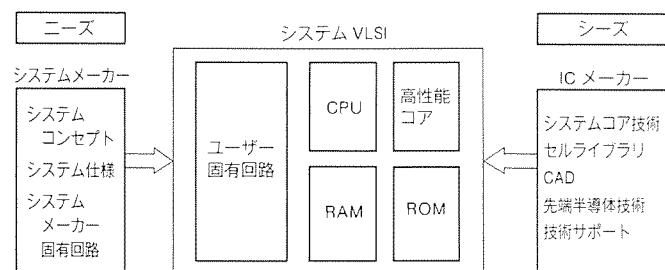

図4に代表的なシステムVLSIの構成を示す。ICメーカーが提供する各種コアセル(CPU, RAM, システム要素コア等)と、システムメーカー固有の回路を同一チップ上に集積するもので、この実現のためには以下の環境整備が必要となる。

#### (1) コアセルの整備

システムの構成要素となるサブシステム又はファンクションをセルライブラリとしてICメーカーが整備することによって、システムVLSIの開発が容易になる。ICメーカーでの各セルライブラリのハードマクロセル化によって高性能、高密度が実現できる。さらに、デザインルールの進展に対応したセルライブラリのシリーズ化も必要になってくる。

#### (2) ICメーカーとシステムメーカーの役割分担

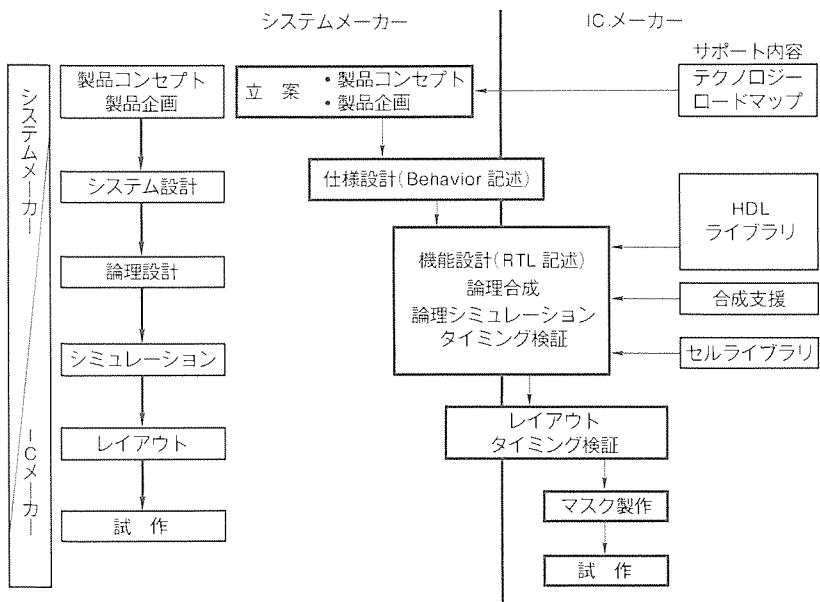

図5に開発におけるICメーカーとシステムメーカーの役割を示す。システムオンチップの時代にはシステム設計とLSI設計は同時に行われることが多く、システムメーカーに近いロケーションにデザインセンターを備え、セットメーカ

図3. 世界半導体需要における将来市場予測

図4. システムVLSI構成例

図5. システムVLSI開発におけるICメーカー、システムメーカーの役割

ーとICメーカーが共同で開発する環境が必要になってくる。

#### (3) CAD環境

システムVLSI設計においてCADは必ず(須)になってきた。図6に示すとおり、集積度の増大に伴い、機能記述による仕様設計、論理合成による論理設計等CADによる上流設計がますます重要になってくる。さらに、システムメーカーとICメーカーとの共同開発に伴うCADツールの統一、インターフェースの整合が必要である。

#### (4) ウェーハプロセスの統合化、標準化

同一チップにロジック回路、マイコン、メモリ等を集積するためにはウェーハプロセスの共通化が必須条件となる。從

図6. トップダウンCADによるシステム／ICメーカーのLSI共同開発

来それぞれのデバイスに最適化されていたウェーハプロセスは、CMOS化への大きな流れと複合LSIへの必要性から特にサブミクロンの時代において統合化と標準化の方向へ進んでいる。

#### 4. システム VLSI の実際例

これまで述べてきた動向と環境整備によって、システムVLSIの実用化が始まっている。実現の形態としては種々の展開がなされているが、以下に幾つかの具体例を示す。

##### 4.1 エンベッテッドセルアレー(ECA)

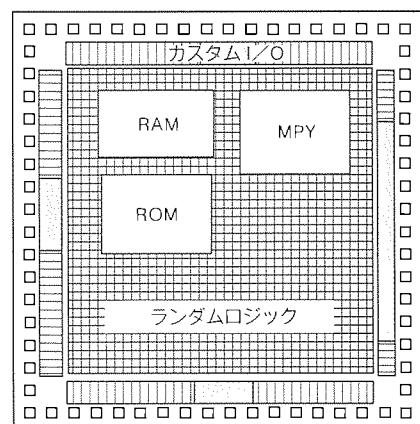

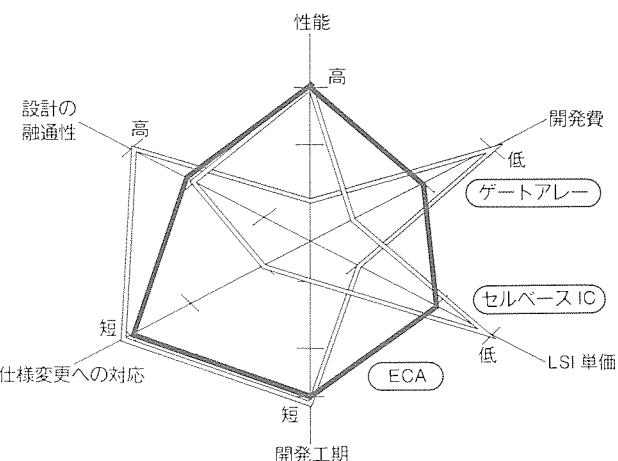

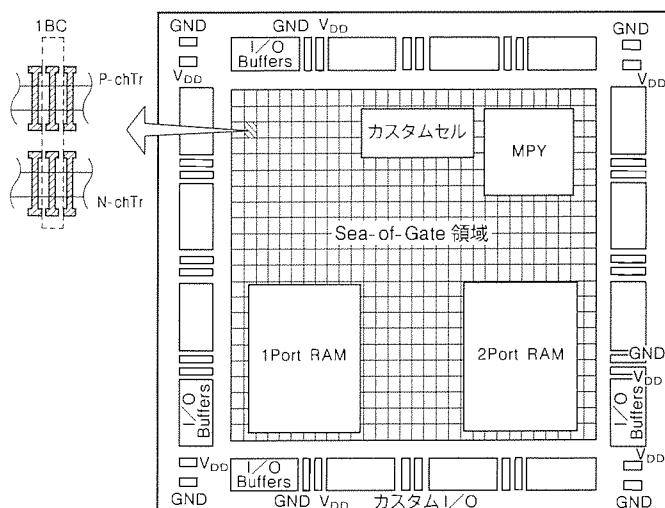

ASIC(Application Specific IC)の中で従来のゲートアレーとセルベースの手法に加え、最近注目されている手法であり、高性能特性と開発工期短縮の特長を兼ね備えたものである。図7の構成に示すとおり、ランダムロジック部を形成するゲートアレー領域の中又は周辺に、高速メモリ(RAM, ROM), 乗算器(MPY)及びカスタムI/O(高速PLL, 高速インターフェース回路)等のハードウェアマクロセルを集積したものである。システムメーカーの製品企画の段階でマスタチップの仕様を決め、システムメーカーのシステム設計、論理設計と並行にICメーカーでマスタチップの開発が進められる。論理設計が終了した後、ランダムロジック部をゲートアレーの手法でスライス工程によって短工期で形成できるため高性能なチップを短工期で実現できる。さらに、ランダムロジック部の仕様変更に対しても安い開発費で速く対応できる。図8にASICの各方式の比較を示す。ECAは各方式の特長を兼ね備えているがカスタムチップのため開発費を償却するために中規模の数量が必要となる。電算機及びOA機器等の分野での応用が広まりつつある。

##### 4.2 画像用 DSP<sup>(1)</sup>

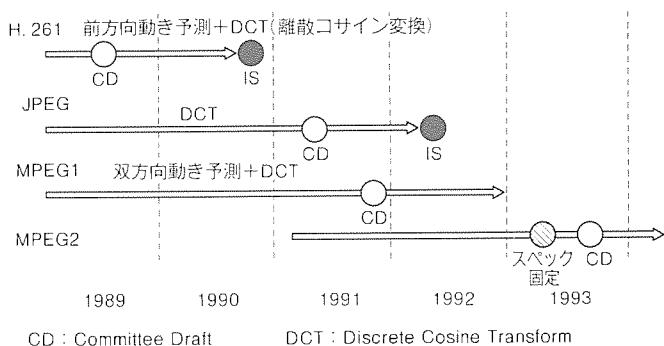

デジタル化の流れの中で画像通信、画像蓄積メディア、

図7. エンベッテッドセルアレー構成

図8. ASIC開発手法での比較

図9. 画像圧縮標準化動向

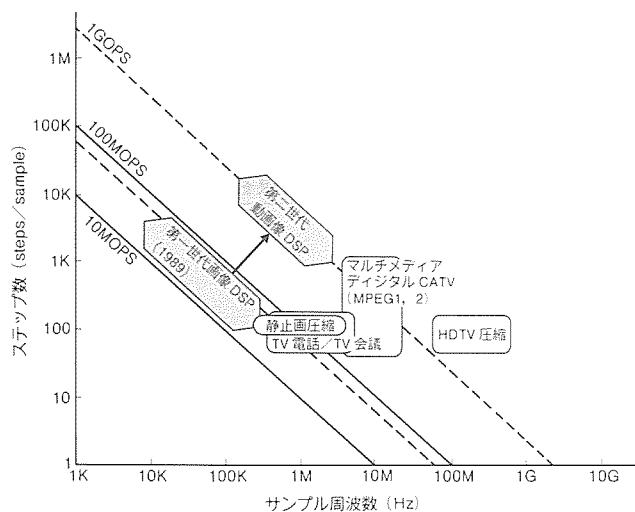

マルチメディア等において画像圧縮符号化技術は非常に重要な役割を担っている。図9に示すとおり、画像の高能率符号化方式の国際標準規格作りがCCITTとISOで進められており、静止画から動画そしてより高画質へと審議が進められている。DSP(Digital Signal Processor)による画像処理のメ

図10. 画像 DSP に対する性能の改善

リットは柔軟性があり、各種標準及び各種仕様変更に対し、ソフトウェアで対応できることにある。当社は図10に示すとおり1989年第一世代画像 DSP (M 65720) を実用化した。さらに、LSI の微細化の進展及びアーキテクチャの改善を行った第二世代動画像 DSP を開発中であり、国際標準の進展及び応用分野の広がりに対応していく。

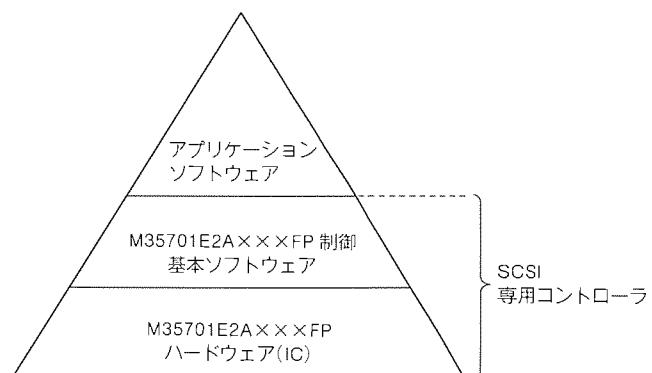

#### 4.3 SCSI 専用コントローラ<sup>(2)</sup>

コンピュータと外部入出力装置間の標準インターフェースである SCSI (Small Computer System Interface) 用コントローラ (M 35701 E 2 AXXXFP) の製品化を行った。図11のチップ写真に示すとおり16ビット MCU (Micro Controller Unit) と専用回路を内蔵した IC である。図12において高速プロトコル処理を専用回路 (ハードウェア) で行い、低速処理部及びアプリケーション (カスタマイズ) 部分はソフトウェアで処理することによって、融通性を保ちながら LSI の経済性を向上させている。

#### 5. む す び

システムオンチップの時代を迎え、システムの動向と VLSI の在り方について述べた。LSI は今後ともシステムの中

図11. M35701E2AXXXFP のチップ写真<sup>(2)</sup>図12. M35701E2AXXXFP におけるソフトとハードの役割<sup>(2)</sup>

におけるキーデバイスとしてますます重要になり、システムとともに表裏一体となって発展していくものと思われる。

#### 参 考 文 献

- (1) 吉本雅彦：画像圧縮用 LSI, テレビジョン学会誌, 46, No. 3, 253~260 (1992)

- (2) 堀 俊彦, 須田眞二, 小林 洋, 遠藤茂行, 川嶋健司：SCSI 専用コントローラ, 三菱電機技報, 66, No. 2, 214~220 (1992)

# 0.5 μmCMOS ゲートアレー

荒川隆彦\* 斎藤 健\*

前野秀史\* 加藤周一\*\*\*

東谷恵市\*\*

## 1. まえがき

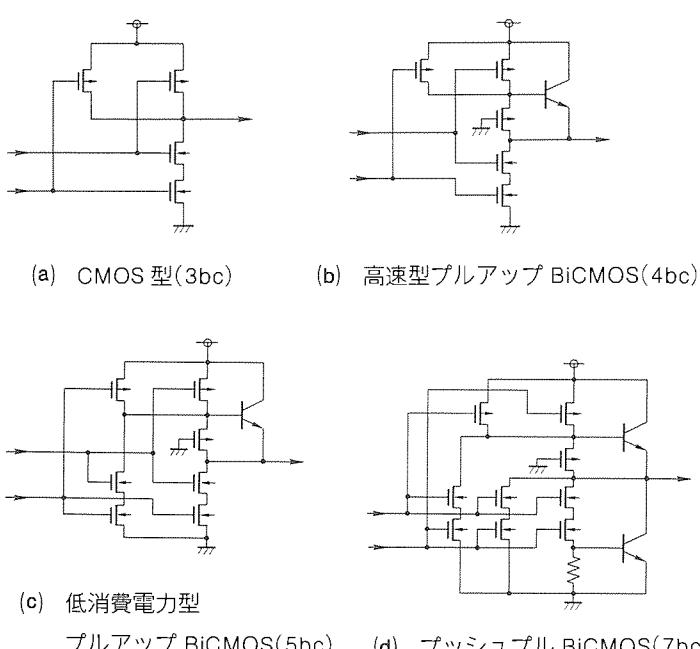

最近のワークステーションを始めとした情報処理機器や通信機器の発展は目覚ましいものがあり、ASIC (Application Specific IC) はその原動力として急速な進歩を遂げている。システムの高性能化及び差別化を達成し、他社製品に対する優位性を保つには、システムを構成する ASIC 開発が重要となってきており、ASIC はより一層の高速化・大規模化・低消費電力化が期待されている。の中でも CMOS ゲートアレーは、集積度・性能・価格・納期などの要求をバランス良く満足し、今後も ASIC の中核をなすデバイスである。

当社では、市場からの更なる高集積化・高性能化の要請にこたえるべく、最先端の0.5 μmCMOS・3層メタル配線プロセス技術を用いた世界最大級の全面敷き詰め (Sea-of-Gates : SOG) 型 1 ミリオングート (1 MG) CMOS ゲートアレーのデバイス開発と、システム動作周波数 100 MHz 時代に対応するための高速化設計技術の開発を進めてきた。

本稿では、今回開発した大規模・超高速 1 MG CMOS ゲートアレーの設計技術及びウェーハプロセス技術について述べるとともに、0.5 μmCMOS ゲートアレーの特長について紹介する。

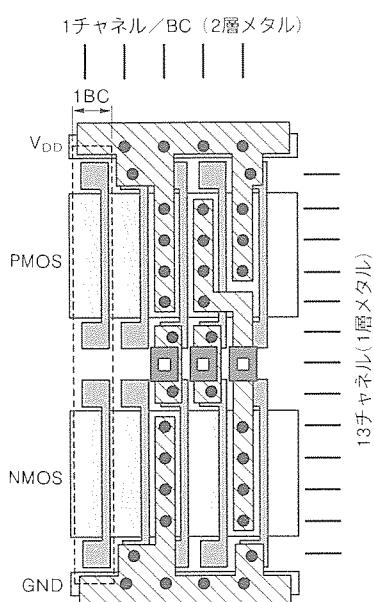

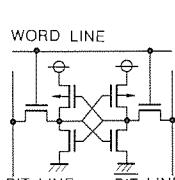

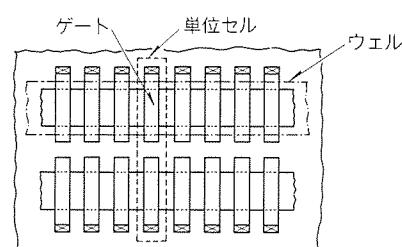

図1. ベーシックセル(BC)構造

—2入力NANDゲートセル—

## 2. LSI 設計

### 2.1 ベーシックセル(BC)設計

SOG は、ベーシックセル(BC)を規則正しくアレー状に並べて内部セル領域が構成されるため、BC の構成でチップの集積度、速度等の性能が左右される。高速性を維持しつつ高集積化を達成するために BC 構造は、図1に示すように当社独自のゲートアイソレーション方式<sup>(1)(2)</sup>を採用している。この方式の BC は 1 ペアの PMOS、NMOS トランジスタをもち、隣接する BC のトランジスタとソース又はドレイン領域を共有し、素子分離には酸化膜を使わない構造になっている。隣接するトランジスタと電気的に分離する必要があるときは一つの BC を使用し、PMOS ゲートを高電位に、NMOS ゲートを低電位に接続する。

このゲートアレーでは、敷き詰めゲート数 100 万ゲートの実現と 3 層配線による高集積化及び低消費電力化に重点を置き、以下の指針で設計した。

- (1) 3.3/3 V 電源でも高速性を維持する。

- (2) 使用頻度の高いマクロセル及びメモリセルにおいて、BC セル列内でセル配線を完結できる最小のゲート幅に設定する。

- (3) 1 BC 当たりの配線チャネル数は、第 1 層メタルが水平方向に 13 本、第 2 層メタルが垂直方向に 1 本割り当てる構造とする。

図2. 1MGマスタのフロアプラン

ゲートアイソレーション方式及び上記(1)～(3)による効果と配線の微細加工技術により、論理ゲート並びにRAMの密度で1.7倍以上(当社比)の高集積化を達成している。

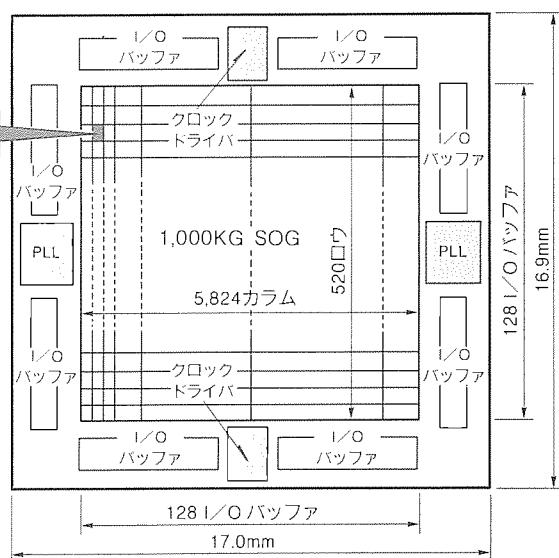

## 2.2 マスタ設計

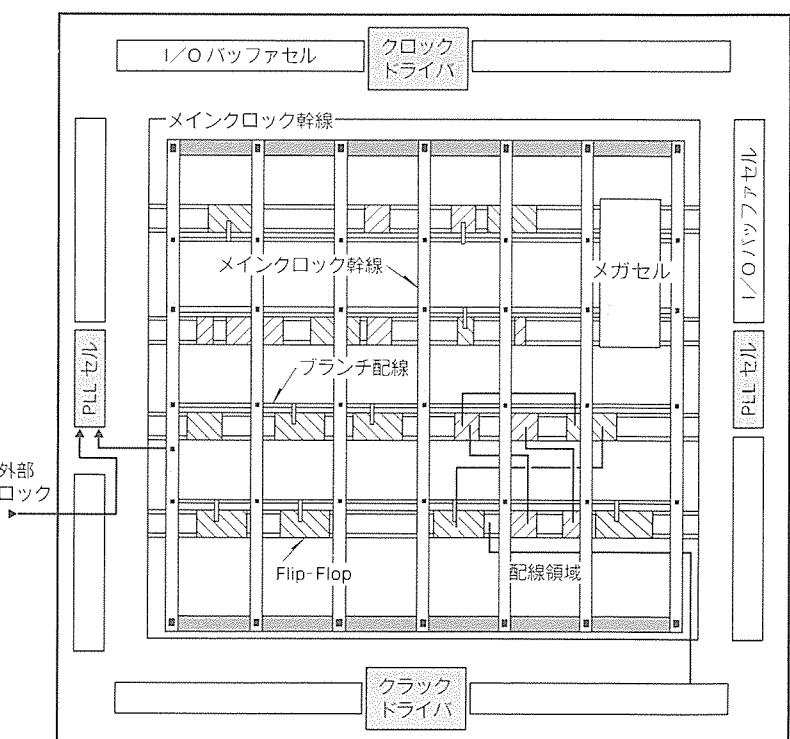

図2に1MGマスタのフロアプランを示す。チップサイズは17.0mm×16.9mmであり、BC数は3.02MBC、I/O数は最大512である。I/Oバッファ領域は80μmピッチで設計され、スルーレート制御回路<sup>(3)</sup>や小振幅信号インターフェース回路<sup>(4)</sup>等の必要な機能はすべてこの領域に盛り込まれている。 $I_{OL}=24\text{ mA}$ までのLVC MOSタイプ出力バッファや $I_{OL}=40\text{ mA}$ の小振幅信号インターフェースバッファ(Gunning Transceiver Logic: GTL)が1個のI/Oバッファセルで実現できるため、高速／高駆動タイプのI/Oセルを使用してもピン数を損なうことなくTAB(Tape Automated Bonding)による多I/Oピン化が図れる。クロックスキュー管理用のクロックドライバセル群と位同期回路(Phase-Locked Loop: PLL)セル群は、複数クロック分を周辺領域にI/Oバッファ領域とは分離して配置している。

## 3. 0.5μmCMOSゲートアレーの特長

### 3.1 低スキュークロック管理方式

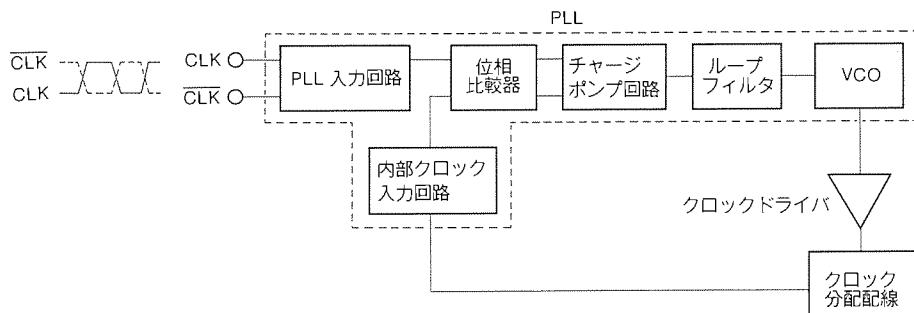

ASICの大規模化に伴ってラッチ、F/F等の順序回路の数が増加し、10万ゲート以上ではクロックの負荷となる順序回路数は2千個から1万個にも達する。一方、システムの高速化を図るためにクロックサイクルの短縮化が必要なため、LSI内部だけでなくシステムを構成している各LSI間のクロックスキューを1ns以下に低減するクロック管理技術がゲートアレーにも要求されている。LSI内部のクロックと外部クロックの位相を同期させるために、PLL回路を応用したクロックスキュー管理方式を開発した。図3にその管理方式を示す。

LSI内部では、クロックドライバと内部セル領域内に走るメッシュ状のクロック幹線によって各F/Fにクロック信号を一括分配することにより、内部のスキューを低減する。また、従来クロックドライバの遅延によってLSI外部クロックとの間で生じていた位相差は、PLL回路によってキャンセルされる。その結果1MG CMOSゲートアレーにおいて、内部セル領域上に配置された5,000個のF/Fに伝達されるクロックの位相とLSI外部クロックの位相の差を500ps以内に管理する事が可能になった。この方式の概略を図4に示す。RAM/ROM等のブロックを配置しても自動配置配線が可能であり、4相クロックま

で対応できる構造になっている。

### 3.2 高速低振幅信号入出力インターフェース

マイクロプロセッサの動作周波数が100MHzに達し、CPU周辺を構成しているゲートアレーにもデータ転送の高速化が要求される。従来のTTLインターフェースでは電磁放射雑音やグランドバウンスなどが深刻になり、低信号振幅の入出力インターフェースが必要となってくる。このゲートアレーではCMOSでECLに似た信号振幅0.8Vの小振幅インターフェース回路GTLを構成し、100MHz以上の高速データ転送を達成した。

### 3.3 モジュールジェネレータ生成セル

システムの高機能化・高速化に対応するため、非同期型2ポートRAM(1write 1read)及び非同期型3ポートRAM(1write 2read)のモジュールジェネレータを開発した。各ポートは独立に動作可能であり、“書き専用”“読み専用”的いづれかに設定することができる。生成されるRAMは最

図3. PLL応用クロックスキュー管理方式

図4. PLL内蔵クロックスキュー管理概略

図5. RAM生成セル

(72ビット×256ワード・2ポートRAM)

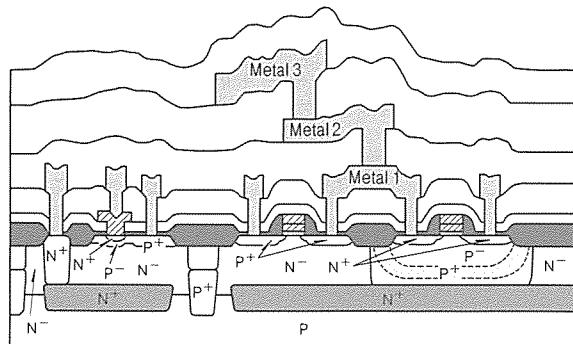

図7. 0.5 μm CMOSプロセス断面

大容量18Kビットであり、ビット数は1~72、ワード数は16~2,048の範囲で可変である。1MGマスタチップに搭載する場合、内部セル領域の45%を利用して容量96Kビットの2ポートRAMが実現できる。アクセストライムは、32ビット×128ワード構成で4.7nsである。図5に、モジュールジェネレータで生成した72ビット×256ワード・2ポートRAMの写真を示す。

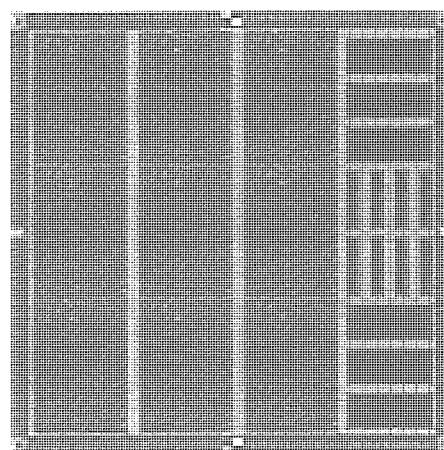

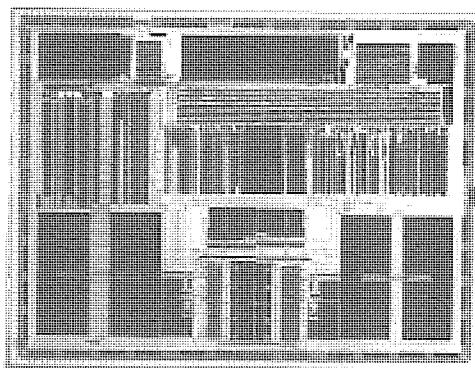

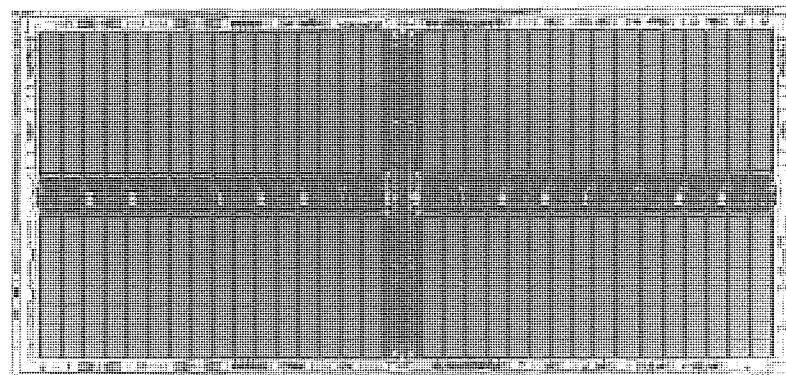

#### 3.4 レイアウト設計

ASICの大規模化・高速化に伴い、レイアウト設計期間の増大や論理設計/レイアウト設計間のタイミング見積りの相違は非常に大きな問題となってくる。階層レイアウト及びタイミング駆動型レイアウト手法を提供し、LSI設計期間の短縮並びに回路のタイミング保証に対処できるようにした。図6に論理ゲート約252Kゲート、12ビット×256ワード・2ポートRAMを6個、4ビット×128ワード・2ポートRAMを8個搭載した1MG CMOSゲートアレーのレイアウトを示す。この手法を用いることにより、従来と比較してレイアウト設計期間を約1/5に短縮することができた。

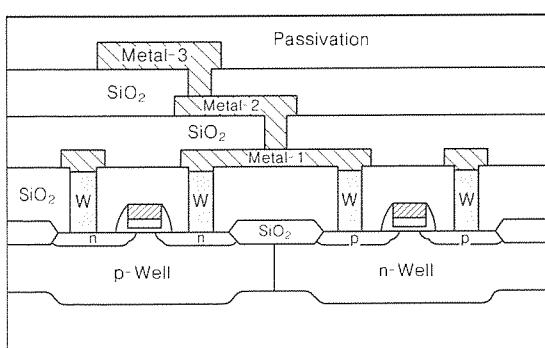

#### 4. 0.5 μm CMOSプロセス技術

使用したウェーハプロセスは、0.5 μmルール、1層ゲー

図6. 1 MGチップレイアウト

表1. 1 MG CMOSゲートアレー主要諸元

|                |                                                 |

|----------------|-------------------------------------------------|

| 総敷き詰めゲート数(ゲート) | 1,000K                                          |

| チップサイズ(mm)     | 17.0×16.9                                       |

| 最大I/O数         | 512                                             |

| 最大RAM容量(ビット)   | 128K                                            |

| 内部ゲート          | 190ps: 2NAND(×4), 標準負荷                          |

| RAM            | 4.7ns: 32ビット×128ワード, 2ポート                       |

| 出力バッファ         | 2.0ns: $I_{OL}=12\text{mA}$ , $C_L=15\text{pF}$ |

| 出力電流(mA)       | $I_{OL}=2, 4, 8, 12, 16, 24, 40$<br>0.5 μmCMOS  |

| テクノロジー         | 3層メタル配線<br>TAB                                  |

ト、3層メタル配線構造のCMOS技術であり、図7に断面を示す。このプロセスの主な特長を以下に述べる。

#### 4.1 レトログレード・ツインウェル構造

CMOS LSIの基板として作用するウェルの深さ方向の不純物分布は、多くの素子特性(しきい値、接合耐圧、パンチスルーエンジニアリング、基板定数等)を決める。したがってウェル内の深さ方向の不純物濃度を独立に制御できれば、それに対応した素子特性をほぼ独立に向上させることができる。この観点から基板内の不純物分布を最適化するために、新たに高エネルギーイオン注入技術を開発した。その結果、素子間の分離間隔が縮まるとともに狭チャネル効果が抑制でき、ウェルと同時に素子分離のチャネルストップ等を形成することにより、マスク枚数の削減も実現できた。

#### 4.2 トランジスタ

MOSトランジスタのゲート長は、P、N両チャネルとも0.5 μmである。また、電源電圧の低電圧化に伴い、従来の5V電源系のドレイン構造ではn-層の寄生抵抗が無視できなくなったため、高い耐ホットエレクトロン性を維持しつつ最大の駆動能力が得られるようにドレインの不純物分布を最適化した。

#### 4.3 多層配線技術

このゲートアレーでは3層配線を用いており、メタル配線

の信頼性を確保するため従来の AlSi 系の材料から AlCu に変更し、さらに高融点金属系材料との積層構造を採用した。また、新たに開発したタンゲステンプラグによる埋込み技術を適用することにより、1層配線下部の層間絶縁膜厚を従来に比べて約2倍厚くすることが可能になり、メタル配線の対基板容量が大幅に低減した。

## 5. 主要特性

表1に1MG CMOS ゲートアレーの主要特性を示す。動作速度は、高駆動能力タイプの2入力NANDゲートで85 ps (F.O.=1), 190 ps (F.O.=2, 配線長=2 mm) と非常に高速である。また、3.3 V電源による低電圧化とマクロセルの最適化により、低消費電力タイプの2入力NANDゲートで $0.9 \mu\text{W}/\text{MHz}$  (F.O.=1) と低消費電力性を達成した。基本マクロセルとして低消費電力／標準／高速／高駆動能力の4種類のマクロセルを用意しており、高密度、低消費と高速の最適化設計が可能である。

## 6. むすび

システムの高性能化及び差別化を達成するために、CMOS ゲートアレーはより一層の高速化・大規模化・低消費電力化が期待されている。本稿では、超高速・高集積・低消費電力化のための $0.5 \mu\text{m}$ CMOS・3層メタル配線プロセス技術を

採用した世界最大級の1 MG CMOS ゲートアレーの概要を述べた。また、超高速動作の設計をサポートするためのクロックスキー管理技術やインターフェース技術などについて紹介した。今後も更に高性能化が進む情報処理機器や通信機器分野への応用に対処するため、高速インターフェースや高速RAM等のライブラリ拡充による高性能化を図っていく予定である。

## 参考文献

- (1) 岡辺雅臣, 柿沼守男, 国岡美千子, 村井正弘, 川端啓二 :  $0.8 \mu\text{m}$ CMOS ゲートアレー, 三菱電機技報, 65, No. 2, 156~160 (1991)

- (2) 鈴木正博, 中村博隆, 布上裕之, 小野眞司, 瀧口真美, 福永利之 :  $1.0 \mu\text{m}$ CMOS ゲートアレー M 60060 シリーズ, 三菱電機技報, 65, No. 2, 161~166 (1991)

- (3) Tomioka, I., Hyozo, M., Okabe, M., Kishida, S., Arakawa, T., Kuramitsu, Y. : Current Control Buffer for Multi Switching CMOS SOG, Proceedings of 1990 CICC, 11.7.1~11.7.4 (1990)

- (4) Gunning, B., Yuan, L., Nguyen, T., Wong, T. : A CMOS Low-Voltage-Swing Transmission-Line Transceiver, 1992 ISSCC Digest of Technical Papers, WP 3.7, 58 ~59 (1992)

# 0.8 μm CMOS エンベッデッドセルアレー

岡辺雅臣\* 井上善雄\*

奥野義弘\*\* 朝比奈克志\*\*\*

富岡一郎\*\*

## 1. まえがき

ASIC (Application Specific IC) は、高度情報化社会の発展を促している電算機・通信機等の高性能化・小型化の進展の原動力として急速に進歩を遂げている。

当社でも1990年に世界最高レベルの高速性・高集積性を実現した0.8 μmCMOS ゲートアレー M 6008Xシリーズを製品化し<sup>(1)</sup>、電子機器の高性能化に寄与してきた。その過程で市場から ASIC へ寄せられた要求は 150 K ゲートを優に超える高集積性、50 MHz クロック動作以上の高速性等とますます高度化されてきた。一方、ASIC を用いて電算機などのシステムを実現する場合、早期製品化による他社への差別化が必要な理由等から、やはりゲートアレー並みの短納期を要求する顧客からの声が圧倒的である。当社では、このような市場の要求にこたえるべく、セルベース(CB)の高集積・高速性とゲートアレー(GA)のQTAT(Quick-Turn-Around)という特長を両立可能とする0.8 μmCMOS エンベッデッドセルアレー(ECA)を新たに開発した。さらに、高速クロック管理に必ず(須)のPLL(Phase Locked Loop)回路や入出力信号の高速伝送に有効な低振幅信号インターフェースGTL(Gunning Transceiver Logic)回路等を開発し、高速動作システム実現の要求を容易に満たすことを可能とした。

本稿では、このECAの特長、高速化回路設計、設計システム及びLSI実現例について紹介する。

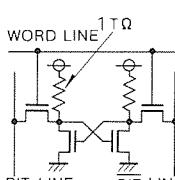

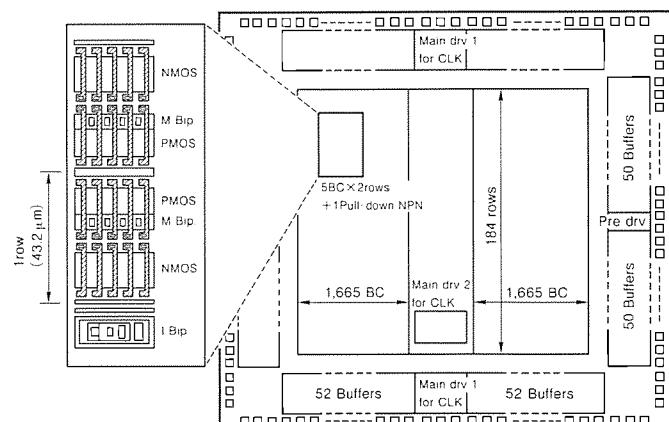

## 2. 0.8 μmCMOS ECA の特長

### 2.1 特 長

ECA は顧客が概略回路設計を終えた段階で、ランダムロジックのゲート数、RAM、MPY(乗算器)のような機能ブロックの仕様、I/O 数に応じて、専用のマスタチップを設計しマスタチップの製造(GA のマスタ工程に相当する。)を開始する。図1にECAのマスタチップ基本構造例を示す。RAM、MPYといった高集積化・高速化が必要な回路ブロックは当社0.8 μmCMOS CB用に開発したモジュールジェネレータ(MG)によって生成し、トランジスタレベルから埋め込む。また、個々の用途に応じたカスタムセルも埋込み可能である。種々の変更が予測されるランダムロジック部は、メタル配線工程のみで対応できるよう、M 6008Xシリーズで世界最高レベルの高集積・高速性能を達成した当社独自のゲートアイソレーション構造<sup>(2)</sup>によるベーシックセル(BC)を

敷き詰めたSOG(Sea-of-Gate)構造を作り込んでおく。一方、顧客はマスタチップの製造と並行して詳細な回路設計を行い、検証が完了した段階でマスタチップ上にメタル配線を形成する(GA のスライス工程に相当)。この手法により、ECAでは回路検証後のES出荷までの期間をGA並みに短くできる。このようにECAはCBの高集積性・高速性とGAの短納期という特長を併せもっている。

### 2.2 ECA用ライブラリ

#### (1) マクロセル、I/Oバッファライブラリ

BCを敷き詰められた領域を用いて構成されるランダムロジックの設計には、M 6008Xシリーズ用の210種のマクロセルライブラリを用いることができる。ゲート遅延時間は215 ps(2入力NAND, ×4セル, FO(Fan Out)=2, Al=2 mm, V<sub>DD</sub>=5 V)を達成し、高速回路の設計に十分な性能をもっている。マクロセルライブラリにはSCAN機能付きのフリップフロップやJTAG設計用セルもサポートされており、テスト容易化設計にも対応している。また、周辺のI/O領域にはM 6008Xシリーズの592種のバッファセルを用いる。

#### (2) MG生成機能ブロック

MGで生成される非同期式高速SRAMは、設計者の要求に応じて最適なビット、ワード構成(1~72ビット、16ワード~8Kワード)を生成可能であり、アクセスタイムも36ビット×2Kワード構成で6.8 ns(5 V、標準条件)と極めて高

図1. ECAのマスタチップ基本構造例

表1. モジュールジェネレータによる機能ブロック

|                | 構成                         | 生成範囲                                                    | 規格例                                            |                                |                                 |

|----------------|----------------------------|---------------------------------------------------------|------------------------------------------------|--------------------------------|---------------------------------|

|                |                            |                                                         | 構成                                             | 遅延時間(Typ)                      |                                 |

|                |                            |                                                         |                                                | $V_{DD}=5.0V$                  | $V_{DD}=3.0V$                   |

| RAM            | 同期型                        | 1~72ビット                                                 | 72K(18ビット×4Kワード)                               | $t_a(c)=10.5ns$                | $t_a(c)=18.9ns$                 |

|                |                            | 16ワード~8Kワード                                             | 16K(8ビット×2Kワード)                                | $t_a(c)=6.0ns$                 | $t_a(c)=10.8ns$                 |

|                |                            | 合計256ビット~72Kビット                                         | 1K(4ビット×256ワード)                                | $t_a(c)=4.4ns$                 | $t_a(c)=7.9ns$                  |

| ROM            | 非同期型フィールドマスク又はコンタクトマスクの選択可 | 4~64ビット                                                 | フィールド512K(32ビット×16Kワード)                        | $t_a(A)=17.3ns$                | $t_a(A)=29.4ns$                 |

|                |                            | 64ワード~32Kワード                                            | フィールド64K(16ビット×4Kワード)                          | $t_a(A)=7.5ns$                 | $t_a(A)=12.8ns$                 |

|                |                            | 合計11~512Kビット                                            | フィールド1K(4ビット×256ワード)                           | $t_a(A)=4.3ns$                 | $t_a(A)=7.3ns$                  |

| PLA            | 同期型                        | 入力数:2~40                                                | 入力40, 出力82, 項数200                              | $t_{pd}=14.6ns$                | $t_{pd}=26.3ns$                 |

|                |                            | 出力数:1~82                                                | 入力20, 出力41, 項数100                              | $t_{pd}=10.1ns$                | $t_{pd}=18.2ns$                 |

|                |                            | 積項数:1~200                                               | 入力5, 出力10, 項数25                                | $t_{pd}=6.7ns$                 | $t_{pd}=12.1ns$                 |

| MPY<br>(乗算器)   | 2の補数方式<br>Boothのアルゴリズム     | X:8~32ビット                                               | X32ビット, Y32ビット                                 | $t_{pd}=20.0ns$                | $t_{pd}=40.0ns$                 |

|                |                            | Y:8~32ビット                                               | X24ビット, Y16ビット                                 | $t_{pd}=12.9ns$                | $t_{pd}=25.8ns$                 |

|                |                            | X8ビット, Y8ビット                                            | X8ビット, Y8ビット                                   | $t_{pd}=8.4ns$                 | $t_{pd}=16.8ns$                 |

| 高速SRAM         | 非同期型                       | 1~72ビット                                                 | 72K(36ビット×2Kワード)                               | $t_a(A)=6.8ns$                 | $t_a(A)=12.2ns$                 |

|                |                            | 16ワード~8Kワード                                             | 16K(8ビット×2Kワード)                                | $t_a(A)=5.4ns$                 | $t_a(A)=9.7ns$                  |

|                |                            | 合計256ビット~72Kビット                                         | 1K(4ビット×256ワード)                                | $t_a(A)=3.8ns$                 | $t_a(A)=6.8ns$                  |

| マルチポートRAM      | 非同期型                       | 1W1R, 1W2R,<br>1RW, 2RW, 1RW1R                          | 1W1R, 36ビット, 64ワード                             | $t_a(A)=8.0ns$                 | $t_a(A)=14.4ns$                 |

|                |                            | 1~72ビット, 4ワード~1Kワード                                     | 1W1R, 12ビット, 16ワード                             | $t_a(A)=4.2ns$                 | $t_a(A)=7.6ns$                  |

|                |                            | 最大36Kビット                                                | 2RW, 16ビット, 1Kワード                              | $t_a(A)=8.8ns$                 | $t_a(A)=15.8ns$                 |

|                |                            | 1W, 2R, 16ビット, 64ワード                                    | 1W, 2R, 16ビット, 64ワード                           | $t_a(A)=4.0ns$                 | $t_a(A)=7.2ns$                  |

| データバス<br>(開発中) | ビットスライス                    | 4~64ビット ALU, ラッチ,<br>マルチプレクサ, デマルチプレクサ加算/減算器, パarelシフタ等 | 64ワードデコーダ, レジスタファイル<br>付き32ビットビットスライスマイクロプロセッサ | $t_{pd}=6.0ns^*$<br>(32ビット加算器) | $t_{pd}=12.0ns^*$<br>(32ビット加算器) |

注 \*開発目標値

速な性能が得られている。

その他, ECAにはMGによって生成される表1に示す機能ブロックが搭載可能である。

### (3) ECA 高速化回路ライブラリ

ECAには上記ライブラリのほかに高速化回路としてPLL, GTLを搭載することができる。その特長については3章で述べる。

### 2.3 製品仕様

表2に0.8μmCMOS 2層/3層メタルプロセスを採用したECAの製品仕様を示す。その特長を以下にまとめる。

(1) 0.8μmCMOS CB M653XXシリーズと同等の高集積・高速MG生成セルライブラリ搭載可能

(2) 0.8μmCMOS GA M6008Xシリーズと同等のLSI開発期間

(3) PLLと数種類の低スキューロック分配回路による高速クロック管理可能

(4) GTL回路搭載によって高速データ転送可能

表2. 0.8μmCMOS ECA仕様

|                      |                                                                                       |                                    |

|----------------------|---------------------------------------------------------------------------------------|------------------------------------|

| プロセス技術               | 0.8μmCMOS メタル2層/3層配線                                                                  |                                    |

| 総敷き詰めゲート数(GA換算)      | 50~400Kゲート(11マスタチップ)                                                                  |                                    |

| チップサイズ               | 14.46mm×14.56mm (Max)                                                                 |                                    |

| SOG領域ベーシックセル         | ゲートアイソレーション構造 38.4μm×3.2μm                                                            |                                    |

| 遅延時間(Typ)<br>5Vライブラリ | 内部セル                                                                                  | 215ps(2入力NAND×4駆動FO=2, 配線長=2mm)    |

|                      | 入力バッファ                                                                                | 0.62ns(TTL入力FO=2, 配線長=2mm)         |

|                      | 出力バッファ                                                                                | 2.5ns( $I_{OL}=8mA$ , $C_L=50pF$ ) |

| 遅延時間(Typ)<br>3Vライブラリ | 内部セル                                                                                  | 370ps(2入力NAND×4駆動FO=2, 配線長=2mm)    |

|                      | 入力バッファ                                                                                | 1.1ns(TTL入力FO=2, 配線長=2mm)          |

|                      | 出力バッファ                                                                                | 4.3ns( $I_{OL}=8mA$ , $C_L=50pF$ ) |

| 消費電力                 | 4.8μW/MHz(2入力NAND FO=1, at $V_{DD}=5V$ ),<br>1.3μW/MHz(2入力NAND FO=1, at $V_{DD}=3V$ ) |                                    |

| 高速化回路                | PLL, 差動疑似ECLレベル信号入力回路, GTL                                                            |                                    |

| 最大I/O数               | 140~512(M60080L~M60089H)                                                              |                                    |

| 出力電流                 | CMOS                                                                                  | $I_{OL}= I_{OH} =1/2/4/8/16/24mA$  |

|                      | GTL                                                                                   | $I_{OL}=20/40mA$                   |

| パッケージ                | 120~208QFP, 328~576QTCP, 240~304CQFP(開発中)                                             |                                    |

- (5) ゲートアイソレーションを用いたBCによるロジック部高集積性(最大敷き詰め400Kゲート)

- (6) 2入力NANDゲート(×4駆動) 215psの高速性

- (7) 最大512 I/Oを可能とするTCP(Tape Carrier Package)技術

- (8) 3Vライブラリ使用による低電力化可能

### 3. ECA 用高速化回路設計

従来の CMOS ゲートアレーでは、最大公約数的なセル設計がなされているので、高度な最適化設計が必要なアナログ的な要素が強い回路で高性能を発揮することは困難であった。この ECA では PLL 回路による内部クロックと外部クロックの同期、差動疑似 ECL レベルによる高速クロック信号入力回路、高速バス駆動用 CMOS 小振幅インターフェース GTL 回路を準備した。PLL、PECL、GTL セルは当社 M 6008X シリーズの I/O バッファ領域のセルを置換することで搭載され、コアエリアの集積度を低下させることはない。

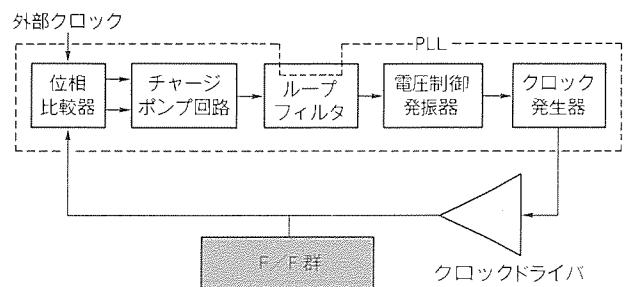

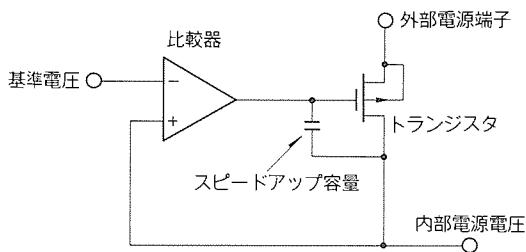

#### 3.1 PLL 回路

デバイスの集積度が向上し、LSI のクロック信号線に接続される負荷の数が増大すると、クロックドライバの伝達遅延が増大し、外部から印加されるクロック信号と LSI 内部のクロック信号の位相差が大きくなる。この問題を解決することは、特に高集積・高速の LSI デバイスでは重要になる。このため、PLL 回路を開発した。PLL 回路は図 2 に示すように内部に電圧制御発振回路 (VCO) を内蔵しており、LSI 内部のクロック信号と外部から印加されたクロック信号の周波数と位相を一致させる働きをする。これより、LSI 内部のクロック信号の駆動・分配回路の遅延がキャンセルされる。今回の試作例では、PLL 回路を含んだクロック信号回路の性能が、電圧制御発振回路の発振周波数範囲 25~60 MHz、デューティ比 45~55%，ロック時のジッタが ±150 ps 以下 (50 MHz のとき) となるように設計した。

#### 3.2 差動疑似 ECL レベル信号入力回路

高速のクロックをチップ間で伝送するには、反射雑音の発生を終端された伝送線路を駆動できるデバイスで、インピーダンス整合のとれた伝送線路によって伝送する必要がある。市販の半導体デバイスでこの要求を満足するディジタル IC ファミリーとして ECL デバイスがある。通常の ECL デバイスの使用方法は負電源系で使用するが、正電源系の CMOS ロジック素子と信号電位を適合させるために、ECL デバイスを正電源系で使用し  $V_{il}=3.3\text{ V}$ ,  $V_{ih}=4.1\text{ V}$  の信号として使用する。この信号を CMOS LSI のクロック信号として印加できるように疑似 ECL レベル信号入力回路を作成した。疑似 ECL レベル信号の信号振幅が 800 mV と小さ

図 2. PLL 構成

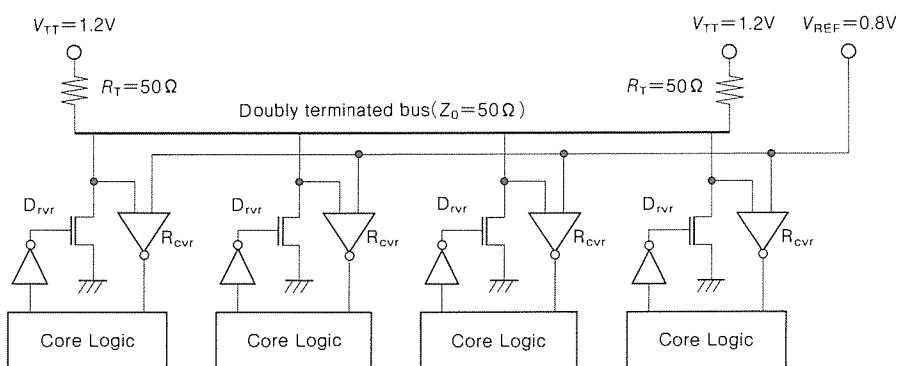

図 3. GTL インタフェース信号伝送構成

表 3. GTL インタフェース DC 規格

| DC 項目     | Max                      | Typ   | Min                      | 条件                          |

|-----------|--------------------------|-------|--------------------------|-----------------------------|

| $V_{ih}$  |                          |       | $V_{ref} + 0.05\text{V}$ | *                           |

| $V_{il}$  | $V_{ref} - 0.05\text{V}$ |       |                          | *                           |

| $V_{ref}$ | 0.9V                     | 0.8V  | 0.7V                     |                             |

| $V_{oh}$  |                          | $V_t$ |                          |                             |

| $V_{ol}$  | 0.4V                     | 0.2V  |                          | * , at $I_{ol}=40\text{mA}$ |

| $I_{oh}$  | $10\text{ }\mu\text{A}$  |       | $-10\text{ }\mu\text{A}$ | $0 < V_0 < 2.0\text{V}$     |

注 \*  $V_{DD}=5\text{V}\pm 5\%$ ,  $0^\circ\text{C} < T_j < 100^\circ\text{C}$ , プロセス条件(最悪~最良)

いので耐雑音性能と高速動作を実現するために相補信号による差動入力とした。

#### 3.3 GTL インタフェース回路

CMOS デバイスで低振幅信号インターフェースを実現する方法の一つとして JEDEC に提案されている GTL 回路をエンベッドセルとして開発した。GTL インタフェースは表 3 に示すような信号電位でチップ間やバックプレーン間の信号伝送を行うものである。

GTL インタフェースを使用した複数チップ間の信号伝送の構成を図 3 に示す。GTL 出力回路は NMOS オープンドライン出力回路で構成され、両端を  $50\text{ }\Omega$  の抵抗で  $1.2\text{V}$  の電源に終端された伝送線路を駆動する。GTL インタフェースの信号振幅が小さいのでチップの寄生インダクタンス等に起

因する出力信号のリンクを抑制する回路が設けられている。GTL 入力回路は外部からの入力信号とともに論理しきい基準電圧を印加されることで動作する。基準電圧の±0.2 V の変動に対して入力電圧換算のオフセット電圧を±50 mV 以下にできる高いCMRR (Common Mode Rejection Ratio) をもつ增幅回路を備えている。

このGTL インタフェース回路により、50 MHz を超える高速の信号を LSI チップ間で伝送することが可能になる。

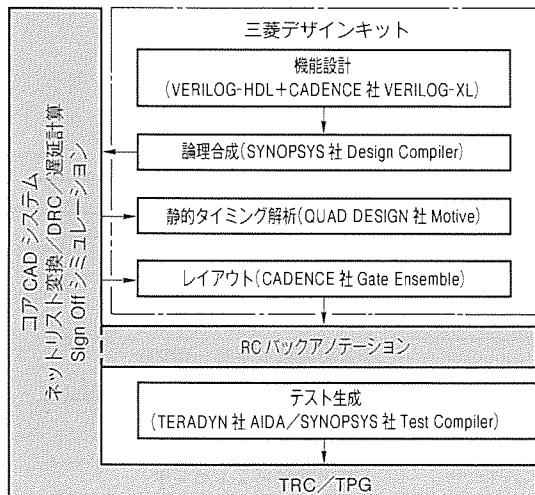

#### 4. CAD フロー

先に紹介したECAを開発するに当たり、以下の点を実現することを目標にCADシステムを新規に開発、構築した。

- (1) スケマチックレスなトップダウン設計

- (2) 静的タイミング解析ツールのサポート

- (3) RC モデルによる詳細なバックアノテーション

- (4) ATPG ツールのサポート

- (5) 高速テスト

- (6) フロントエンドからバックエンドまでの全工程を EWS 上で実現

- (7) ポーティングを容易にし、複数のプラットホームで稼働

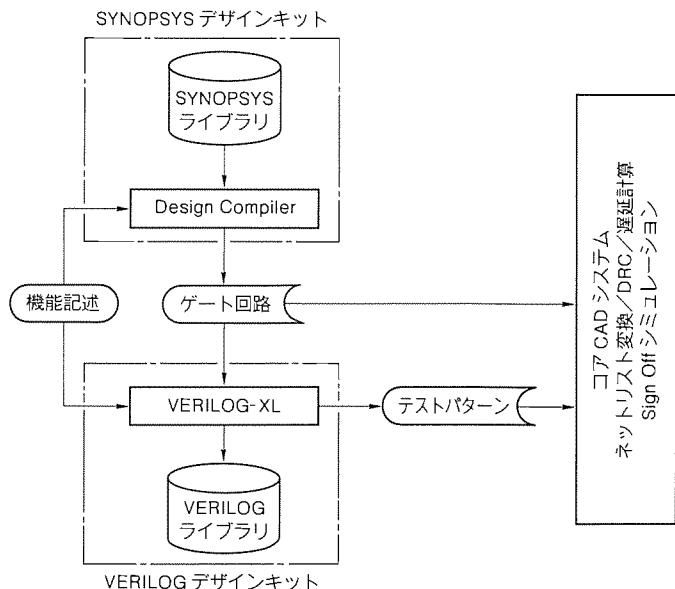

この CAD システムの構成概要は、図 4 のとおりである。図に示すように、システムは当社のコア CAD をベースに市販ツールのデザインキットを組み合わせて構成しており、ユーザーの希望に応じたシステム構成を ME/RISC, SUN, HP/APOLLO の各ワークステーション上に構築可能である。

以下に主な構成内容を説明する。

##### 4.1 トップダウン設計サポート

このシステムでは、トップダウン設計対応として当社北伊丹製作所で開発した CADENCE 社 VERILOG-XL 用デザインキット及びSYNOPSYS 社 Design Compiler デザインキットをベースとして構築している。

このほかユーザーの要求に応じ、MENTOR 社 Quick SIM,

図 4. CAD システム概要

Auto Logic, CADENCE 社 SYNEGY の選択も可能である。

図 5 に示すようにユーザーが記述したビヘイビアレベル(又は RTL レベル)のVERILOG-HDL 記述の機能的妥当性をVERILOG-XL の機能レベルシミュレーションで確認し、妥当であれば Design Compiler を用いてゲート回路への論理合成を行う。

論理合成実行時、パス遅延/タイミング等の制約条件を Design Compiler に与え論理合成を行うが、論理機能/パス遅延等が希望どおりに合成されたかどうかの検証として仮想配線長を用いた Pre-Layout シミュレーションを実行することもできる。

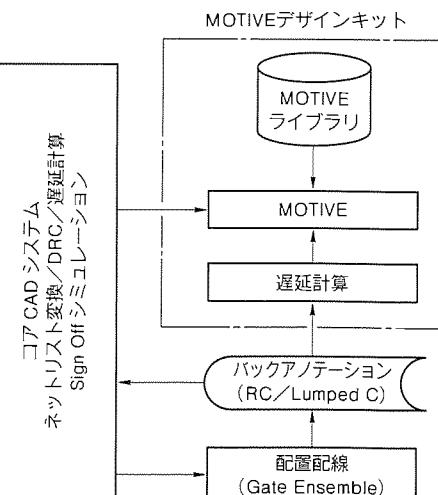

##### 4.2 静的タイミング解析ツールのサポート

一般的に大規模ゲート回路になるとダイナミックなタイミング解析手法では、膨大な解析時間を要しきつすべての可能性を網羅的にチェックすることは不可能である。

図 5. トップダウン設計サポート

図 6. 静的タイミング解析サポート

このCADシステムでは、静的タイミング解析ツールの採用によってこの問題を解決している(図6)。

静的タイミング解析ツールには、QUAD DESIGN社のMOTIVEを採用しており、システムレベルからのタイミング解析をサポート可能としている。

#### 4.3 RCモデルの実現

プロセスの微細化により、配置配線結果を従来と同様に配線容量のみをバックアノテーションしたのでは正確なタイミング検証ができなくなっている。信号配線自身に生じる遅延を考慮したRCモデルによるタイミング検証を行う必要が出てきている。

信号配線自身に生じる遅延を計算するためには、配線の抵抗、容量のほかに信号を駆動するゲートの負荷条件に応じた出力インピーダンスが必要であるが、一般的なCADシステムでは、負荷条件によらず固定値を用いている。

このCADシステムでは、従来の共通遅延情報ファイル(DLF)に定義された遅延パラメータを用いて各ゲートの負荷容量に応じた出力インピーダンスを計算して求めている。

これにより、信号配線遅延をより詳細に考慮可能とした高精度なRCモデルを実現している。

この方法により、今までのCADシステムを用いながら遅延計算プログラムの差し替えのみで配線経路ごとの詳細なタイミング検証が可能となった。

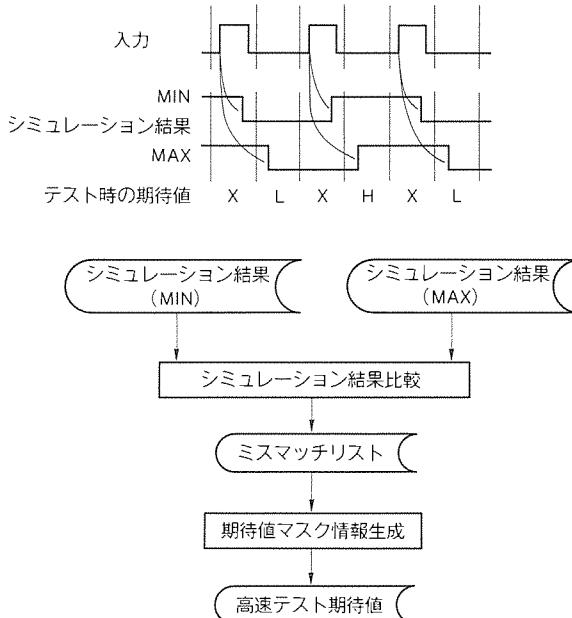

#### 4.4 テスト CAD

テストCADでは、テスト生成に対応するためにATPGツールとしてTERADYNE社のAIDA/SYNOPSYS社のTest Compilerをサポートしており、両ツール共に当社のテストデータフォーマット(TD)の出力が可能である。そのため、直接トランシスレータへ各ATPGツールの生成したテストパターンをインターフェースできる。

また、システムの高速化に伴う高速テストへの対応も行っている(図7)。

高速テストを行うまでの問題点は、テスト条件(MIN/MAX)によって期待出力値が異なる場合があることで、テス

ト時にどの期待値でテストを実施するか決定できることである。

このCADシステムでは、MIN/MAX両モードでのシミュレーションを実行し、その結果から自動的にテスト時の期待値を生成可能としている。

### 5. LSI試作例及び評価結果

#### 5.1 テストチップ試作、評価結果

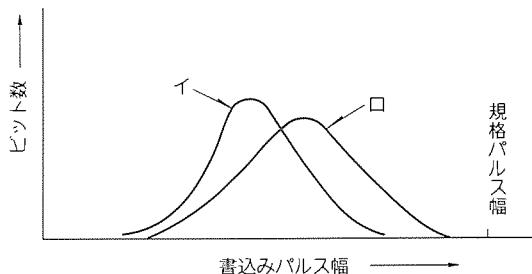

上記で述べたPLL、GTL及びRAM等、各特殊セルの動作検証のために、特性評価用テストチップを0.8μmCMOSプロセス技術を用いて試作した。試作したTEGはウェーハプロセスにおいて、最良/標準/最悪の三つの条件を設定した。最悪条件のプロセスを用いて試作したTEGの評価結果を表4に示す。この評価結果から、今回新規回路技術を用いて設計した各特殊セルの高周波領域における安定動作が確認できた。

図7. 高速テスト

表4. ECA用高速化回路評価結果

| 回路                      | 評価結果( $V_{DD}=4.75V$ , $T=85^{\circ}\text{C}$ )                                                        | 評価条件                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------|

| GTL入力セル                 | 遅延時間: $t_{PLH}=1.60\text{ns}$ , $t_{PHL}=1.32\text{ns}$<br>しきい値: $V_T=V_{ref}+45\text{mV}$             | 標準負荷( $FO=2$ , 配線長=2mm)<br>$V_{ref}=0.8V$ |

| GTL出力セル                 | 遅延時間: $t_{PLH}=1.64\text{ns}$ , $t_{PHL}=1.51\text{ns}$<br>出力電流: $I_{OL}=52\text{mA}$ at $V_{OL}=0.4V$ | $R_{TT}=25\Omega$ , $V_{TT}=1.2V$         |

| PLL(PECL I/F)           | Jitter $\leq 196\text{ps}$ (Min-Max)<br>Offset $\leq 100\text{ps}$                                     | 入力周波数=25~70MHz<br>入力周波数=50MHz             |

| 1P-RAM<br>(2Kビット×31ワード) | アクセスタイム=8.8ns<br>アドレスセットアップタイム=アドレスホールドタイム=0 ns                                                        | 最大遅延ビットワード<br>最大遅延ビットワード                  |

| 2P-RAM<br>(72ビット×64ワード) | アクセスタイム=4.4ns<br>アドレスセットアップタイム=アドレスホールドタイム=0 ns                                                        | 最大遅延ビットワード<br>最大遅延ビットワード                  |

| クロックドライバ                | クロックスキュー: $\leq 600\text{ps}$                                                                          | 2,400 F/F loaded, $f=50\text{MHz}$        |

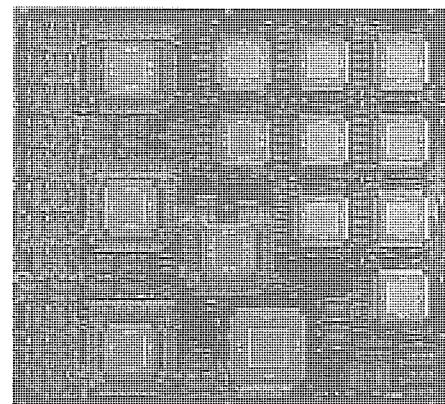

図8. 0.8 μmCMOS ECA 製作例

(チップサイズ 14.46mm×14.56mm)

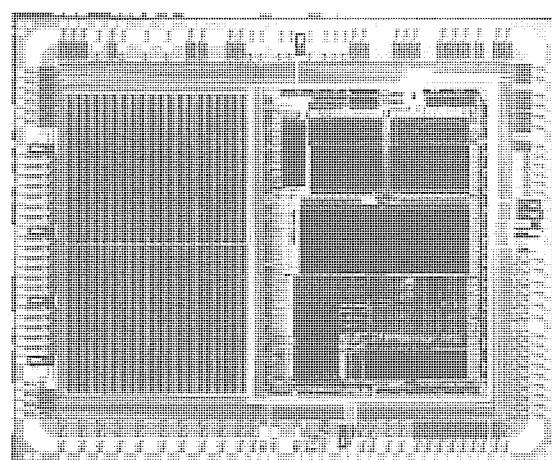

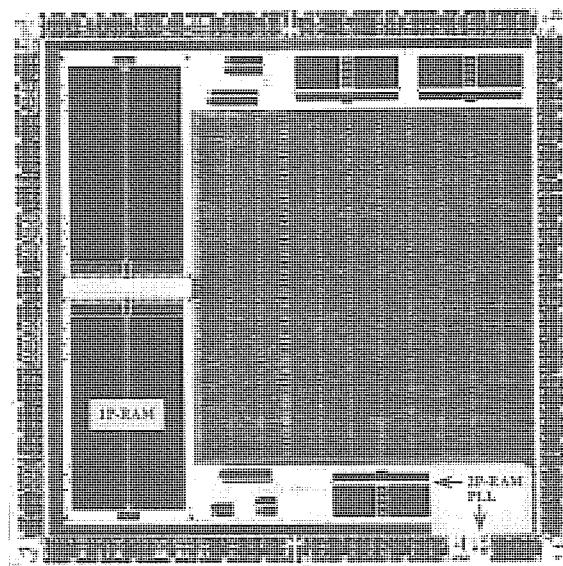

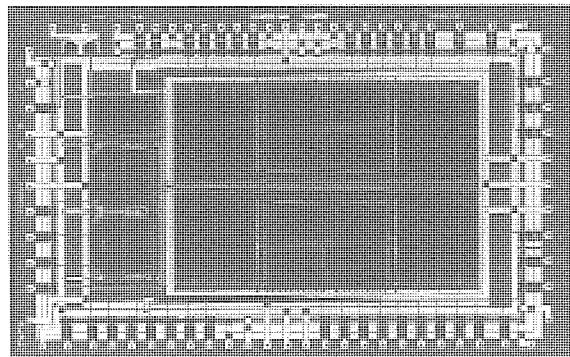

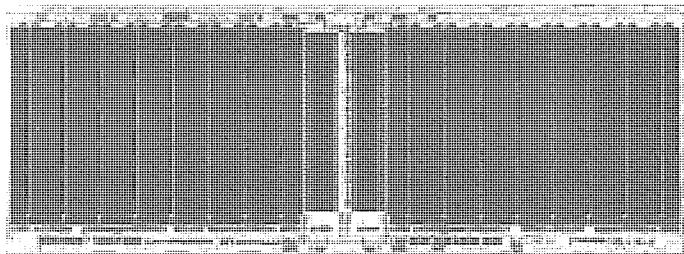

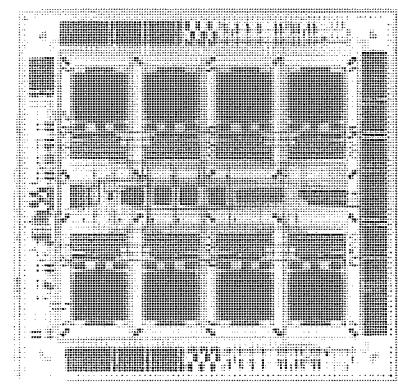

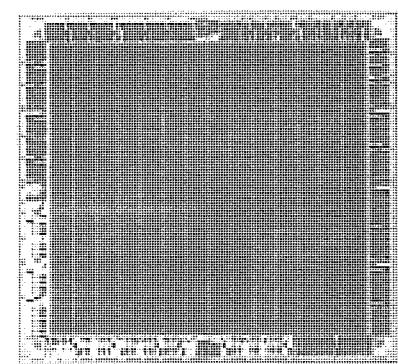

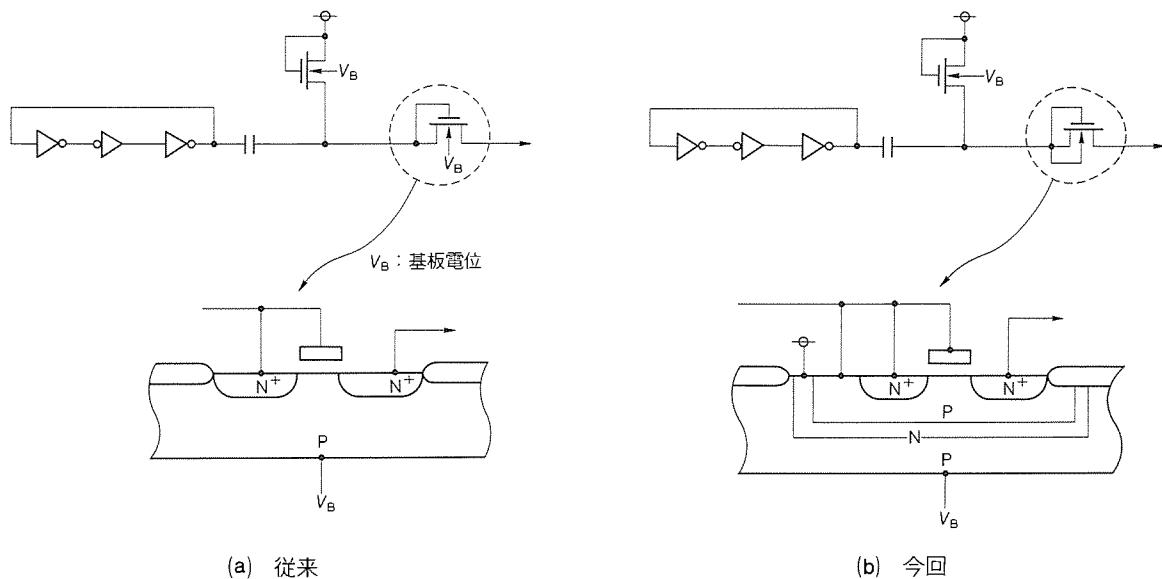

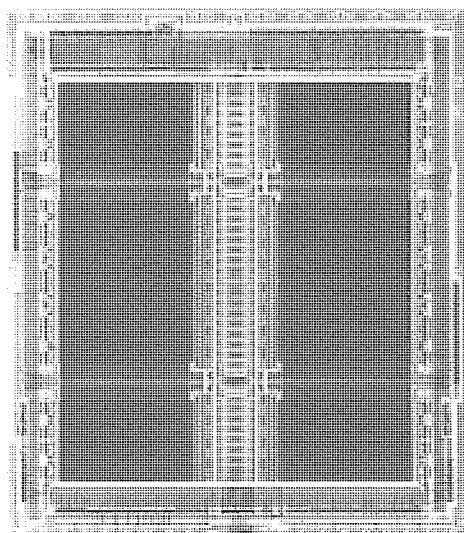

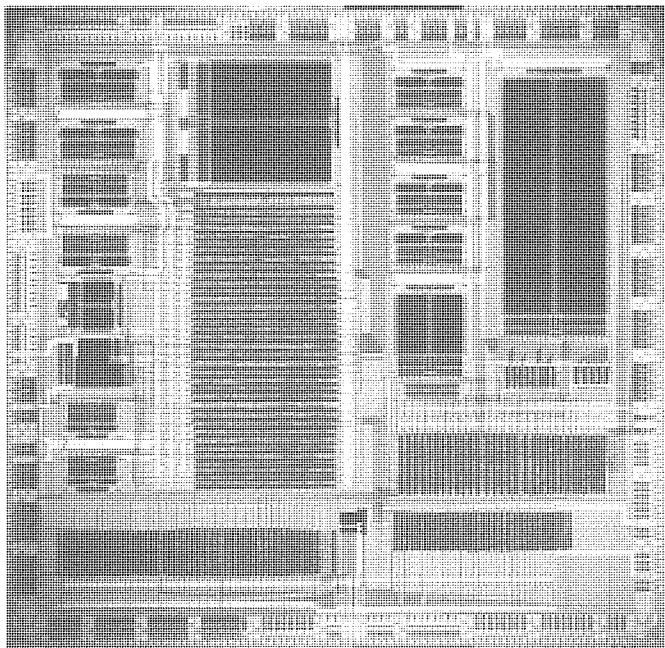

## 5.2 LSI 製作例

図8に0.8 μmCMOS ECA 技術を用いて実現したLSIの例を示す。このECAのシリーズ最大の14.46 mm × 14.56 mm のチップサイズの中に40K ゲートの論理回路とトータル160K ビットの高速・高集積CB用RAMを集積しており、ゲートアイソレーションの高集積性と相まって等価換算ゲート数200K ゲート以上の回路を2層メタルプロセスで実現できた。

クロック入力部にはPECL回路、他のほとんどのI/OはGTL回路を用いた。ジッタ±150 ps以下のPLL及び2,400 F/Fに対しスキーを600 ps以下に抑えるクロック分配回路を搭載し50 MHz以上の高速動作が可能であることを確認した。

## 6. む す び

このECAはPLL、GTL等の高速化回路及びCB用ライブラリ等を自由に搭載できるため、今までGAでは達成できなかった高速性・高集積性を必要とする用途にも適用可能であり、今後の電子機器の更なる高性能化・小型化に十分貢献できるものと確信している。

最後に、開発に当たり御指導及び御協力をいただいた関係各位に対し深謝する。

## 参 考 文 献

- (1) 岡辺雅臣, 柿沼守男, 国岡美千子, 村井正弘, 川端啓二 : 0.8 μmCMOS ゲートアレー, 三菱電機技報, 65, No. 2, 156~160 (1991)

- (2) Ohkura, I., Noguchi, T., Sakashita, K., Ishida, H., Ichiyama, T. Enomoto, T. : Gate Isolation-A Novel Basic Cell Configuration for CMOS Gate Arrays, Proceedings of Custom Integrated Circuits Conference, 307~310 (1982-5)

# 画像圧縮 LSI 用高速 DCT コア

高畠明彦\* 竹田 淳\*

浦本紳一\* 山下征大\*

井上喜嗣\*

## 1. まえがき

画像データを圧縮する高能率符号化方式の国際標準において、離散コサイン変換 (Discrete Cosine Transform : DCT) を用いた変換符号化方式が採用されている。TV会議/TV電話用低レート動画像符号化方式に関するCCITTの標準勧告H.261<sup>(1)</sup>、JPEG<sup>(2)</sup>が規定したカラー静止画像符号化方式、そしてMPEG<sup>(3)</sup>による動画像蓄積メディアに関する符号化方式のそれぞれで、DCTベースの符号化方式が標準化されている。

また、デジタルTVやHDTVのような高いデータレートの応用分野においても、DCT方式が採用されつつある。そのため、DCTを高速に演算するコアが、画像圧縮LSIにおいて重要となる。DCTは後に述べるように、大量の積和演算を必要とするために、LSIにおいて高速化と小面積化の両立が難しい。筆者らは、この問題を解決した高性能DCTコアを開発した。HDTVのスタジオ規格のベースバンド信号(輝度信号の画素レートが74.25MHz)に対応可能な100MHz動作が可能であり、また面積も21mm<sup>2</sup>と小さく、画像圧縮LSIや高性能動画像DSPにコアとして搭載が可能である。本稿では、DCTコアの高性能化を達成するためのアーキテクチャ技術と回路技術について述べる。

## 2. 二次元 DCT

画像符号化において、画像の空間的冗長度を取り除くために空間的周波数変換がよく用いられる。DCT<sup>(4)</sup>はその一つであり、画像信号に対して二次元DCTは特に有効であるので、多くの標準方式に採用されている。二次元DCTは次式で示される。

図1. DCTコアのブロック図

$$X(u, v) = \frac{2}{N} C(u) \cdot C(v) \cdot \sum_{i=0}^{N-1} \sum_{j=0}^{N-1} x(i, j) \cdot \cos \frac{(2i+1)u\pi}{2N} \cos \frac{(2j+1)v\pi}{2N} \quad \dots \dots \dots (1)$$

ここで、 $x(i, j)$  は原信号、 $X(u, v)$  はDCT係数である。 $u=v=0$  のときは  $C(u)=C(v)=2^{1/2}$  で、 $u, v \neq 0$  のときは  $C(u)=C(v)=1$  である。また、逆DCTは次式で示される。

$$x(i, j) = \frac{2}{N} \sum_{u=0}^{N-1} \sum_{v=0}^{N-1} C(u) \cdot C(v) \cdot X(u, v) \cdot \cos \frac{(2i+1)u\pi}{2N} \cdot \cos \frac{(2j+1)v\pi}{2N} \quad \dots \dots \dots (2)$$

ここで、例として8点 ( $N=8$ ) の二次元DCTの演算量を考えると、積和演算を単純に実行した場合、4,096回の積和演算が必要となる。このように、二次元DCT及び逆DCTは大量の積和演算を必要としている。そのため、この積和演算を高速に実行することが、高速DCTコアを実現するための重要なポイントとなる。

## 3. DCTコアのアーキテクチャ

### 3.1 高速アルゴリズムの採用

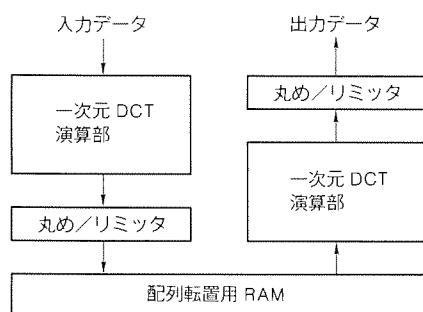

図1にDCTコアのブロック図を示す。DCTコアは、二つの二次元DCT演算部と中間データの転置のためのRAMから構成されている。二次元DCTは、行方向及び列方向の二つの一次元DCTに分解して行われる。まず、入力データに対して行方向の一次元DCTを実行し、RAMによってブロックデータを転置した後、列方向の一次元DCTを実行する。また、行及び列方向の一次元DCT処理の最後において、データの丸めが行われる。

図2. 一次元 DCT 演算部のブロック図

DCTについて、多くの高速アルゴリズムが提案されている。しかし、データ処理の過程に複数回の乗算を含んでいるために、これを有限語長の固定小数点演算器で実行した場合に、演算精度劣化の問題が生じてしまうものが多い。

DCTコアでは、Chenの高速アルゴリズム<sup>(5)</sup>を採用した。この手法では、一次元DCTの処理の過程で、データに対する乗算が1回ですむために、演算精度劣化の問題がない。Chenの高速アルゴリズムによる8点の一次元DCTは式(3), (4)で示される。

$$\begin{bmatrix} X_0 \\ X_2 \\ X_4 \\ X_6 \end{bmatrix} = \frac{1}{2} \begin{bmatrix} A & A & A & A \\ B & C & -C & -B \\ A & -A & -A & A \\ C & -B & B & -C \end{bmatrix} \cdot \begin{bmatrix} x_0 + x_7 \\ x_1 + x_6 \\ x_2 + x_5 \\ x_3 + x_4 \end{bmatrix} \quad \dots (3)$$

$$\begin{bmatrix} X_1 \\ X_3 \\ X_5 \\ X_7 \end{bmatrix} = \frac{1}{2} \begin{bmatrix} D & E & F & G \\ E & -G & -D & -F \\ F & -D & G & E \\ G & -F & E & -D \end{bmatrix} \cdot \begin{bmatrix} x_0 - x_7 \\ x_1 - x_6 \\ x_2 - x_5 \\ x_3 - x_4 \end{bmatrix} \quad \dots (4)$$

$$A = \cos \frac{\pi}{4}, B = \cos \frac{\pi}{8}, C = \sin \frac{\pi}{8}, D = \cos \frac{\pi}{16}, \\ E = \cos \frac{3\pi}{16}, F = \sin \frac{3\pi}{16}, G = \sin \frac{\pi}{16}$$

ここで $x(i, j)$ は原信号、 $X(u, v)$ はDCT係数である。また、8点の一次元逆DCTは式(5), (6)のようになる。

$$\begin{bmatrix} x_0 \\ x_1 \\ x_2 \\ x_3 \end{bmatrix} = \frac{1}{2} \begin{bmatrix} A & B & A & C \\ A & C & -A & -B \\ A & -C & -A & B \\ A & -B & A & -C \end{bmatrix} \cdot \begin{bmatrix} X_0 \\ X_2 \\ X_4 \\ X_6 \end{bmatrix} \\ + \frac{1}{2} \begin{bmatrix} D & E & F & G \\ E & -G & -D & -F \\ F & -D & G & E \\ G & -F & E & -D \end{bmatrix} \cdot \begin{bmatrix} X_1 \\ X_3 \\ X_5 \\ X_7 \end{bmatrix} \quad \dots (5)$$

$$\begin{bmatrix} x_7 \\ x_6 \\ x_5 \\ x_4 \end{bmatrix} = \frac{1}{2} \begin{bmatrix} A & B & A & C \\ A & C & -A & -B \\ A & -C & -A & B \\ A & -B & A & -C \end{bmatrix} \cdot \begin{bmatrix} X_0 \\ X_2 \\ X_4 \\ X_6 \end{bmatrix} \\ - \frac{1}{2} \begin{bmatrix} D & E & F & G \\ E & -G & -D & -F \\ F & -D & G & E \\ G & -F & E & -D \end{bmatrix} \cdot \begin{bmatrix} X_1 \\ X_3 \\ X_5 \\ X_7 \end{bmatrix} \quad \dots (6)$$

式(3)～(6)から分かるように、Chenの高速アルゴリズムによれば、積和演算の前後で加減算を行うだけで、1画素当たりの乗算回数を半分に減らすことができる。

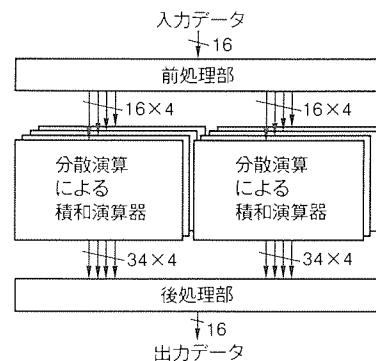

図2に一次元DCT演算部のブロック図を示す。前処理部、積和演算部、そして後処理部によって構成されており、前処

理部と後処理部において加減算を実行している。前処理部はDCT演算のときに、後処理部は逆DCT演算のときに、それぞれ用いられる。

### 3.2 分散演算による積和演算

積和演算には分散演算(Distributed Arithmatic)<sup>(6)</sup>を用いた。分散演算は、積算係数が固定されている積和演算に対して非常に有効な手法である。これによると並列乗算器を用いて積和演算を実行できるので、ハードウェア(H/W)を大幅に削減できる。さらに、乗算器を用いず、ROMと加算器によって演算を行うため、加算器において最悪遅延経路が形成されるので、高速化も可能である。

ここで、分散演算の原理について説明するために、次のような一般的な積和演算について考える。

$$y = \sum_{k=1}^K a_k \cdot x_k \quad \dots (7)$$

ここで、 $K$ は積和の項数、 $a_k, x_k$ はそれぞれ $k$ 項目の係数、入力データである。入力データ $x_k$ は $N$ ビットの2の補数表現を用いて表すと次式のようになる。

図3. 分散演算による積和演算器の構成

図4. インタリープ配置したメモリによる積和演算回路

$$x_k = -b_{k,0} + \sum_{n=1}^{N-1} b_{k,n} \cdot 2^{-n} \quad \dots \dots \dots \quad (8)$$

ここで、 $b_{k,n}$  は 0 又は 1 であり、 $2^{-n}$  は各ビットの重みを表す因子である。式(8)を用いて(7)を書き直すと次式のようになる。

$$y = \sum_{k=1}^K a_k \cdot (-b_{k,0} + \sum_{n=1}^{N-1} b_{k,n} \cdot 2^{-n}) \quad \dots \dots \dots \quad (9)$$

これを変形して次式を得る。

$$y = \sum_{n=1}^{N-1} (\sum_{k=1}^K a_k \cdot b_{k,n}) \cdot 2^{-n} + \sum_{k=1}^K a_k \cdot (-b_{k,0}) \quad \dots \dots \dots \quad (10)$$

ここで関数  $f$  を次式で定義する。

$$f(b_{1,n}, b_{2,n}, \dots, b_{K,n}) = \sum_{k=1}^K a_k \cdot b_{k,n} \quad \dots \dots \dots \quad (11)$$

関数  $f$  は、1 ビットの入力データに対する式(8)と同じ積和演算を表すものである。式(11)を式(10)に代入すると式(12)のようになり、これは式(8)に示した積和演算と等価なものである。

$$\begin{aligned} y &= \sum_{n=1}^{N-1} 2^{-n} \cdot f(b_{1,n}, b_{2,n}, \dots, b_{K,n}) \\ &\quad + \{-f(b_{1,0}, b_{2,0}, \dots, b_{K,0})\} \quad \dots \dots \dots \quad (12) \end{aligned}$$

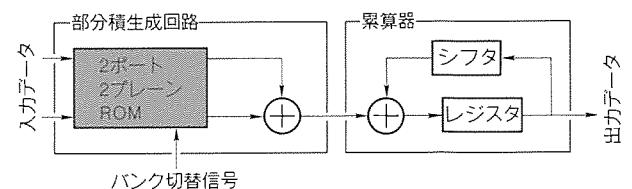

もし、関数  $f$  が並列乗算器なしに実現可能ならば、式(12)で表される演算は加算器とシフタによる累算器で実行できる。係数  $a_k$  が定数であるので、関数  $f$  は  $b_{k,n}$  の値に応じて  $2^k$  どおりの値をとる。この値を部分積と呼ぶ。この部分積をあらかじめ計算しておき、 $(b_{0,j}, b_{1,j}, b_{2,j}, \dots, b_{K-1,j})$  がアドレスとして入力されると関数  $f$  の値を出力するように、ROM にデータを格納すれば、並列乗算器を用いずに関数  $f$  が実現できる。したがって、式(12)に示した演算は ROM と累算器によって実現できる。

#### 4. 回路設計

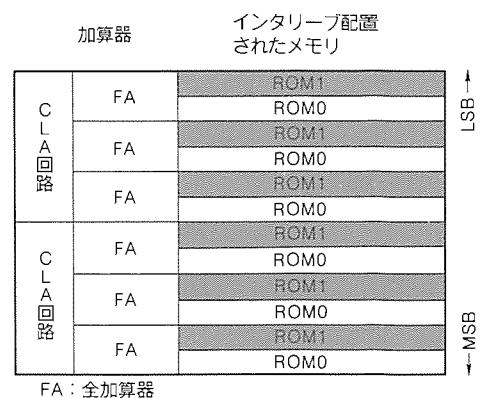

##### 4.1 インタリーブ配置した ROM による分散演算

分散演算による積和演算では、式(12)に示したように、あ

図 5. 2 プレーン ROM 回路

らかじめ計算した部分積を ROM に格納しておき、この部分積を、最下位ビットから最上位ビットまでビット順に読み出して累算する。よって、処理に要するサイクル数は入力データの語長に依存する。DCT コアでは、入力画素データに対する実時間処理を可能とするために、1 サイクルで 2 ビットのデータを処理するように回路を構成した。この手法は、式(12)を変形して得られる次式で表される。

$$\begin{aligned} y &= \sum_{m=1}^{N/2} 2^{-(2m-1)} \cdot f(b_{1,2m-1}, b_{2,m-1}, \dots, b_{K,2m-1}) \\ &\quad + \sum_{m=1}^{N/2-1} 2^{-2m} \cdot f(b_{1,2m}, b_{2,2m}, \dots, b_{K,2m}) \\ &\quad + f(b_{1,0}, b_{2,0}, \dots, b_{K,0}) \quad \dots \dots \dots \quad (13) \end{aligned}$$

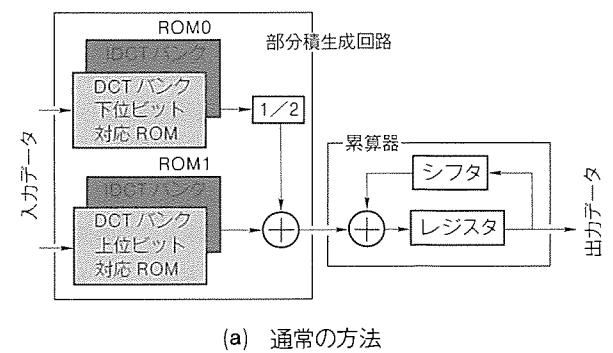

式(13)における二つの累算を同時に実行することにより、処理速度が 2 倍となる。図 3 (a) は、DCT と逆 DCT を式(13)で表される分散演算を用いて実現した場合の、通常の回路構成を表す。まず、上位側ビットと下位側ビットに対する部分積を同時に二つの ROM から読み出し、これらの和をとる。この和を入力データの最下位ビットから順番に累算することにより、積和演算が実行される。また、DCT と逆 DCT の演算は、ROM のバンクを切り替えて、それぞれ実行される。

図 3 (a) に示した回路を LSI で効率良く実現するため、図

図 6. 2 ポート／2 プレーン ROM を用いた積和演算回路

図 7. DCT コアにおける加算器

4に示すレイアウト手法をとった。図3(a)における二つのROMを、ビット列ごとに交互(インタリーブ)に配置し、その直下に二つの部分積の和をとる加算器を配置した。この手法により、ROMと加算器の間の配線が短くなって配線領域が縮小され、また配線容量の低減によって高速化もなされた。

#### 4.2 2ポート／2プレーン ROM

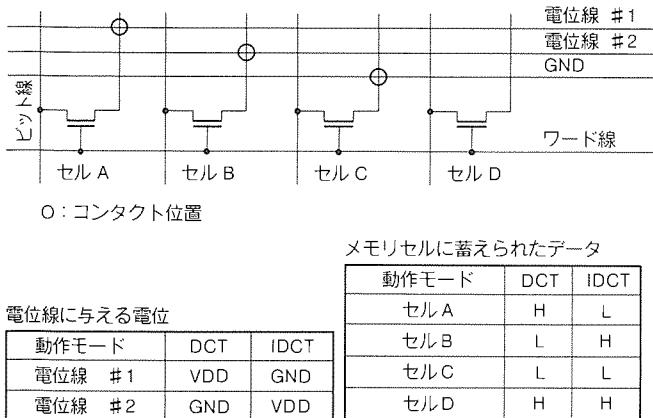

DCTと逆DCTの二つの演算を同一のH/Wで実行可能とするためには、それぞれに対する部分積を記憶したROMが必要である。このため、図3(a)に示すように、積和演算器中のROMにはDCTと逆DCTに対する二つのバンクが必要となる。しかし、DCTと逆DCTが同時に実行されることではなく、二つのバンクが同時に使われることはない。そこで、シリコン面積を有効に活用するために、2プレーンROMを開発し、小面積化を行った。

図5に2プレーンROMの回路を示す。2プレーンROMのメモリセルは、メモリセルトランジスタのソースと電位線との接続関係をコンタクトによってプログラムする。そして電位線を外部から制御することにより、出力データを制御する。メモリセルには図5に示すように四つのタイプがあり、コンタクトのとり方がそれぞれ異なっている。電位線#1と#2の電位を切り替えることによって、一つのトランジスタで二つの情報を読み出せる。DCT演算と逆DCT演算のどちらを行うかの選択に従って、この電位線の切替えを行えば、一つのROMによって両方の演算が実行できる。

DCT及び逆DCTの演算時における電位線の制御法、及びそのときの各メモリセルの出力電位は図5に示すとおりで

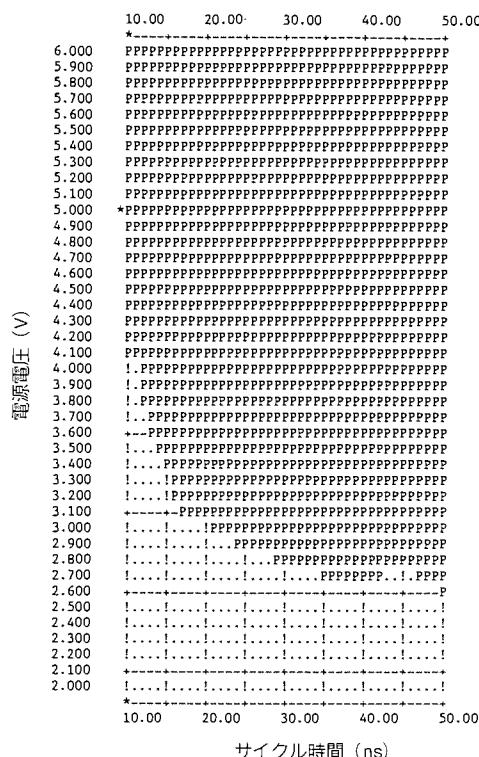

図8.DCTコア動作速度評価結果

ある。この2プレーン／2ポートROMを用いることで、DCTコアでは約10kトランジスタが削減された。

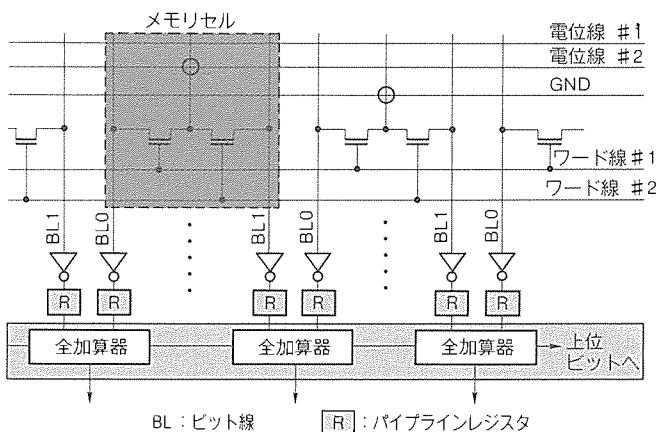

DCTコアでは入力データの2ビットを同時に処理しており、図3(a)に示すように上位側ビットと下位側ビットに対する二つのROMが必要となっている。しかし、この二つのROMに記憶されるデータは同じものであるので、代わりに2ポートのROMを用いることが有効である。図6に示すように、2ポートメモリは一つのメモリセルから二つのビット線で同時にデータを読み出すことが可能である。これら二つのビット線を、入力データの上位側ビットと下位側ビットに対する部分積の読み出しに用いる。そして、図6に示すようにメモリセルと全加算器を配置することによって、メモリのインターリーブ配置が実現される。図3(b)に2ポート／2プレーンROMを用いた場合の積和演算器の回路構成を示す。

メモリをインターリーブ配置した積和演算器の構成と、2ポート／2プレーンROMの開発によって、積和演算を小規模H/Wで高速に実現することが可能となった。

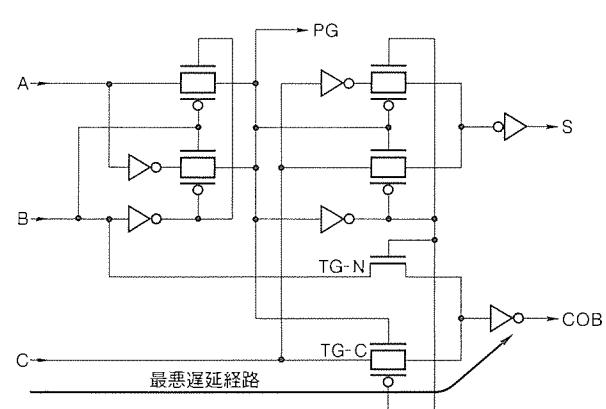

#### 4.3 加算器の高速化

DCTコアにおける最悪遅延経路は18ビット累算器である。18ビット累算器には、比較的少ない素子数の増加で高速化が可能であるCLA(Carry Look Ahead)加算器を用いた。CLA加算器は、その最悪遅延経路においてノードの寄生容量が少なくなるような回路構成とした。図7にDCTコアに用いた全加算器の回路を示す。図に示すように、最悪遅延経路に対して余分な負荷容量となるTG-NをCMOSではなくNチャネルトランジスタで構成している。この最悪遅延経路の回路構成に加えて、トランジスタサイズの最適化によって加算器を更に高速化した。これにより、コアの100MHz動作が可能となった。図8にDCTコアの動作速度評価結果を

表1. 逆DCT演算精度評価結果

| 評価項目*           | CCITT規定値 | 精度評価結果   |

|-----------------|----------|----------|

| 最大誤差            | 1        | 1        |

| 二乗平均誤差(最大値)     | 0.06     | 0.0080   |

| 二乗平均誤差(ブロック内平均) | 0.02     | 0.0056   |

| 平均誤差(最大値)       | 0.015    | 0.0018   |

| 平均誤差(ブロック内平均)   | 0.0015   | 0.000064 |

注 \* CCITT勧告(H.261)に定められた逆DCT演算精度の評価方法に従い、-256～+255の入力1万ブロックに対する評価結果。

表2. DCTコア諸元

|         |                                           |

|---------|-------------------------------------------|

| 機能      | 二次元DCT／IDCT                               |

| ブロックサイズ | 8×8固定                                     |

| データ形式   | 9bit signed(画素データ)<br>12bit signed(DCT係数) |

| 最大動作速度  | 100MHz                                    |

| トランジスタ数 | 102kTr                                    |

| コア面積    | 6.4mm×3.3mm                               |

| テクノロジー  | 0.8μm 2層メタル CMOS                          |

図9. DCT コアのチップ写真

示す。

## 5. 演算精度

表1にDCTコアの演算精度評価結果を示す。評価方法はCCITT勧告(H.261)に規定された逆DCT演算精度の評価方法に従っている。表に示すとおり、すべての評価項目において規定値を十分に満足する結果が得られている。

## 6. むすび

高速アルゴリズムと分散演算を用いた積和演算アキテクチャと、それをシリコン上に効率的に実現する回路/レイアウト技術により、高速かつ小面積であるDCTコアを開発した。表2にこのDCTコアの諸元、図9にチップ写真を示す。

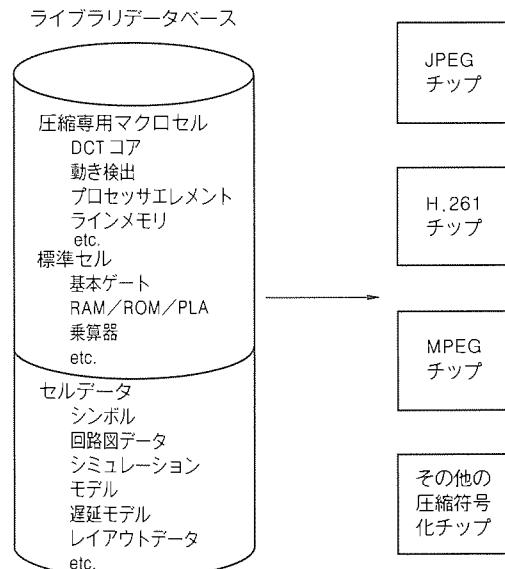

各種画像圧縮LSIを短期間で開発するためには、“圧縮専用マクロセル”ベースの設計アプローチが有効である。これは、各種圧縮アルゴリズムに共通の処理が含まれることに由来する。図10にこのセルベース設計の概念を示す。DCTコアは、このライブラリの核となるものである。このDCTコアを含めた専用ライブラリの構築により、高速かつ高集積な画像圧縮LSIの早期開発が可能である。

## 参考文献

- (1) CCITT SG XV Working Party XV / 1 : Video Codec for Audio Visual Services at p \* 64 kb / s, Recommendation H.261 (1990)

図10. 画像圧縮専用マクロセルベース設計アプローチ

- (2) ISO-IEC / JTSC 1 / SC 2 / WG 10 JPEG : Digital Compression and Coding of Continuous-Tone Still Images, CD 10918-1 (1991)

- (3) ISO / MPEG : Coding of Moving Pictures and Associated Audio, Committee Draft of Standard (1990)

- (4) Ahmed, N., Natarajan, T., Rao, K.R. : Discrete Cosine Transform, IEEE Trans. Comput., C-23, No. 1, 90~93 (1974)

- (5) Chen, W. H., Smith, C. H., Fralick, S. C. : A Fast Computational Algorithm for Discrete Cosine Transform, IEEE Trans. Commun., COM-25, No. 9, 1004~1009 (1977)

- (6) Peled, A., Liu, B. : A New Hardware Realization of Digital Filters, IEEE Trans. Acoust., Speech, Signal Processing, ASSP-22, No. 12, 456~462 (1974)

- (7) Uramoto, S., Inoue, Y., Takabatake, A., Takeda, J., Yamashita, Y., Terane, H., Yoshimoto, M. : A 100 MHz Discrete Cosine Transform Core Processor, IEEE J. Solid-State Circuits, 27, No. 4 (1992)

# セルベース設計用データパスジェネレータ

辻橋良樹\* 西巻秀克\*

松本尚\* 中尾博臣\*

宮西篤史\* 北田修\*

## 1. まえがき

近年、VLSI 設計技術の進歩に伴って、ASIC (Application Specific IC) 手法によるシステムオンチップが普及してきている。システム設計者が設計を行うセミカスタム IC の設計方式は、ゲートアレーとセルベースに大別される。共に、あらかじめ準備されたライブラリ中のセルを用いてチップを構築する方式であるが、特にセルベース方式は最適に回路・レイアウト設計されたライブラリセルを使用できるため、ゲートアレーでは実現が難しい高性能・高機能な LSI に適した設計方式である。一方、ASIC の中でも従来フルカスタム手法に近い設計を行っていた分野では、規模と品種数の増加傾向に伴って設計負荷が増大しており、設計効率改善が重要な課題となっている。そこで、品種特有の専用セルと共に通のライブラリセルを用いる形態でセルベース設計方式が採用されてきている。

したがって、どのようにして高性能・高機能なライブラリを豊富に提供するかが、セルベース事業の展開を図る上で重要である。一般的 LSI を構成する回路を、制御部・メモリ部・演算処理部の 3 ブロックに分類し、ライブラリの現状と問題点を以下に述べる。

制御部に多く見られる、いわゆるランダムロジック回路に対しては、論理ゲートやフリップフロップ等の標準セルライブラリが適用可能である。また、メモリ部は規則的内部構造をもっているため、“アレー型”のモジュールジェネレータが有効である。これは、RAM でいえばビット幅やワード数等の簡単なパラメータを入力するだけで、所望の構成のモジュールセルを自動生成するシステムである。当社では、既に 1.0 μm 並びに 0.8 μm CMOS プロセス技術に対応したセルベース用 RAM・ROM<sup>(1)</sup> ジェネレータを実用化しており、多数の LSI に適用して<sup>(2)(3)</sup>、実績を挙げている。なお、メモリではないが、規則的内部構造をもつ大規模モジュールセルである PLA・乗算器に関しても、これらを生成するモジュールジェネレータを実用化している<sup>(1)</sup>。しかし、LSI の演算処理部であるデータパスブロックは、ある程度以上の性能が要求される場合、専用セルとして人手設計せざるを得ない部分であり、設計期間短縮の妨げとなってきた。

高性能な信号処理プロセッサ等では、データパスがチップの性能を決めており、面積も大きい。データパスは ALU・レジスタ・シフタ等の機能ブロックで構成されるが、複数ビ

ット幅のデータに対して各ビットともほぼ同一の処理を行うため、機能ブロック間の配線は、ほとんどが同一ビット内で閉じている。このため、手設計によるレイアウトは各機能ブロックが一次元に並べられ、同一ビットのセル高が等しいビットスライス構造をしている。そこで、このレイアウト上の特長を考慮したジェネレータを開発することにより、集積度・性能ともに手設計のものに劣らないデータパスの自動生成が可能であると考えた。これにより、LSI 設計者が開発するセルベース ASIC の設計効率改善に貢献できると同時に、システム設計者が標準セルライブラリを用いて設計していたセミカスタム IC の高性能化と高集積化も図れる。本稿では、今回開発したデータパスジェネレータの特長と適用例を中心述べる。

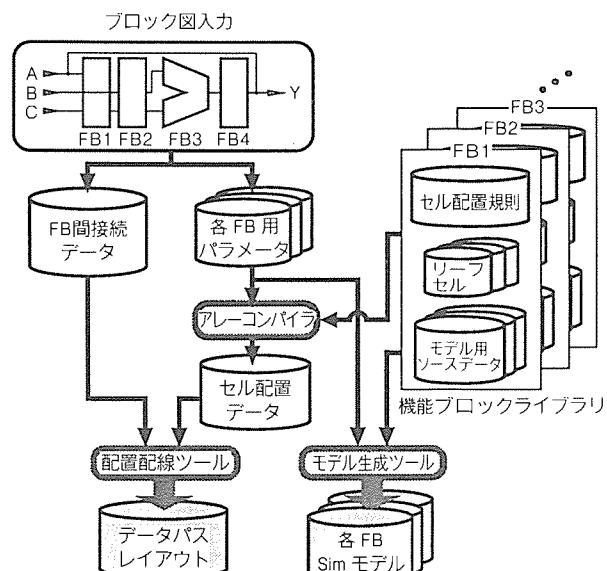

## 2. 開発の基本方針

データパスジェネレータは、LSI 設計者が開発する高性能なプロセッサ LSI や信号処理 LSI、特に開発期間の短いセルベース ASIC の設計効率向上、並びにシステム設計者が設計するセルベース手法によるセミカスタム IC の高性能化と高集積化を開発の目的としている。このため、開発の基本方針を以下のように定めた。

### (1) 高機能性

ALU やシフタ等データパスの構成要素（機能ブロック）をパラメータ可変な専用ライブラリとして用意する。データパスに必要とされる典型的な機能ブロックはあらかじめ整備するが、さらなる機能面の拡充を図ることができるよう新た

図 1. 生成データパスのレイアウト構造

な機能ブロックの追加が可能なシステム構成にする。

## (2) 自由度の高い設計環境

様々な仕様のデータパス設計を可能するために、ユーザー（データパスの設計者）の入力は、機能ブロックライブラリを用いたブロック図とする。そして、どの機能ブロックを何個使い、どのように相互接続するかに関する制約は設けない。また、ユーザーが入力したデータパスを検証するために、各機能ブロックのシミュレーションモデルを生成する。

## (3) 高集積と高性能

概念的には、必要な機能ブロックを生成し、それらを配置配線してデータパス全体のレイアウトを生成する。高集積を実現させるため、新規セル構造を各機能ブロックの構成セル（リーフセル）に適用し、配線専用領域を使わずにセル上配線を行う。また、タイル方式のモジュール生成手法<sup>(4)</sup>によって各機能ブロックを生成することにより、人手設計に近い高性能化を図る。

## 3. データパスジェネレータの特長

### 3.1 レイアウト構造

生成データパスのレイアウト構造の特長は以下のとおりで

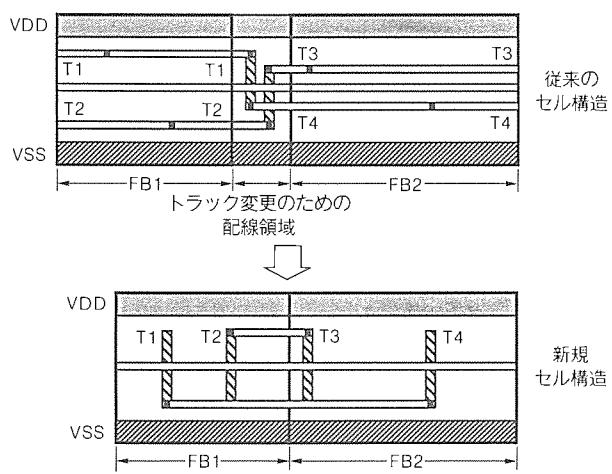

図2. 新規セル構造の概略

図3. 従来のセル構造との比較

ある（図1参照）。

(1) 機能ブロックは水平方向に配列され、互いに隣接配置されている。ただし、異なるビット間の配線を行う場合には、機能ブロックと機能ブロックの間にフィードスルー領域が存在する。

(2) 各機能ブロックは（アドレスデコーダやフラグ生成回路といった）制御部と演算実行部から成る。

(3) 演算実行部はビットスライス構造をもっている。ビットごとに一对の電源供給線（VDD, VSS）が第2層アルミで水平に走り、隣り合うビットは一方の電源供給線を共有する。

(4) 機能ブロック内の制御信号線は第1層アルミで垂直に走り、同一ビット内の機能ブロック間配線（データ配線）は第2層アルミで水平に走る。また、ビットをまた（跨）ぐデータ配線はフィードスルー領域上を第1層アルミで垂直に走る。

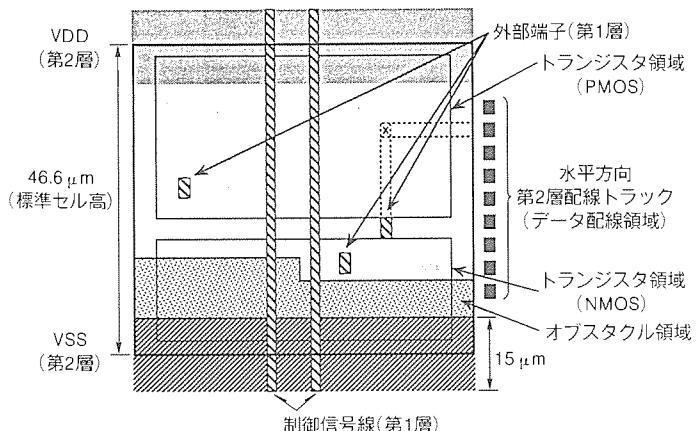

### 3.2 新規セル構造

このデータパスジェネレータで採用した新規セル構造の概略を図2に示す。この構造に従って各機能ブロックを設計した。

一对の電源供給線に挟まれたトランジスタ配置領域上に、データ配線領域が存在する。機能ブロックの内部配線は、原則としてポリシリコンと第1層アルミで接続されており、外

部端子（機能ブロック間を接続するための端子）は第1層アルミでレイアウトされている。内部配線に第2層アルミを使用した領域は、オブスタクル（データ配線禁止）領域として扱う。外部端子の上（又は下）端から、接続すべきデータ配線トラックまで第1層アルミで垂直に配線が施され、配線トラックの交点にバイアホールが配置される。このように、端子は任

(a) 配線前

図4. レジスタ1ビット分のレイアウト

表1. 機能ブロックライブラリ諸元

|          | 主な特長                                                        | 性能                |              |        |       |

|----------|-------------------------------------------------------------|-------------------|--------------|--------|-------|

|          |                                                             | 構成                | 遅延値(ns)      | 幅(μm)* | 集積度** |

| 加算器      | 速度選択オプション<br>・キャリールックアヘッド(CLA) 1階層／2階層<br>・キャリーセレクトアダム(CSL) | 64ビット 2階層 CLA+CSL | $t_{pd}=6.5$ | 185    | 7.21  |

|          |                                                             | 32ビット 1階層 CLA     | $t_{pd}=6.8$ | 119    | 8.56  |

| ALU      | 16通りの算術／論理演算                                                | 64ビット 2階層 CLA     | $t_{pd}=9.5$ | 204    | 7.64  |

|          | 速度選択オプション<br>・キャリールックアヘッド(CLA) 1階層／2階層                      | 32ビット 1階層 CLA     | $t_{pd}=8.1$ | 147    | 8.36  |

| パarelシフタ | シフト動作：右方向／左方向／ローテート<br>算術シフト／論理シフト<br>最大シフト幅：0～ビット幅-1       | 64ビット，最大シフト幅63ビット | $t_{pd}=5.3$ | 599    | 5.64  |

|          |                                                             | 32ビット，最大シフト幅31ビット | $t_{pd}=3.8$ | 446    | 5.96  |

| 1ビットシフタ  | シフト動作：右方向／左方向／ローテート／キャリー付きローテート<br>算術シフト／論理シフト              | 64ビット             | $t_{pd}=2.3$ | 83     | 3.98  |

| レジスタファイル | 非同期動作<br>ポート構成：3ポート(2R1W)，2ポート(1R1W)<br>ワード数：4～64           | 64ビット×64ワード 2R1W  | $t_a(A)=6.2$ | 1,192  | 10.60 |

|          |                                                             | 32ビット×32ワード 2R1W  | $t_a(A)=4.7$ | 560    | 10.18 |

| レジスタ     | リセット／セットの有無選択可                                              | 64ビット，リセット／セットなし  | $t_{pd}=1.0$ | 27     | 7.75  |

| ゼロディテクタ  | クロック同期動作                                                    | 64ビット             | $t_{pd}=1.8$ | 24     | 3.94  |

| マルチプレクサ  | 入力数：2～8                                                     | 64ビット，8入力         | $t_{pd}=1.2$ | 66     | 4.45  |

注 \* 機能ブロック高さ: 46.6 μm/ビット      \*\* 単位: kTr/mm<sup>2</sup>

意の配線トラックと接続可能であり、機能ブロック同士の同一ビット内の端子間は直線（1 トラックのみを使用して）で配線できる。従来セル上配線に使用されていたセル構造では、端子が接続されるトラックや、配線が通過可能なトラックが固定（又は限定）されていたため、途中で配線トラックを変えるための余分な配線領域を必要としていた（図3参照）が、今回のセル構造を採用することにより、この領域を削減することができた。

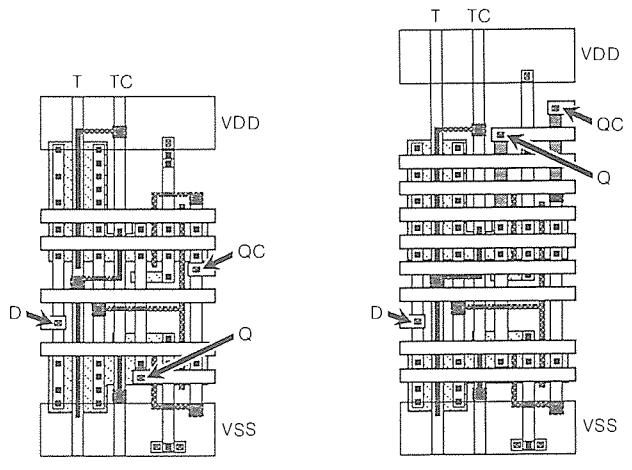

標準(最低)のセル高  $46.6 \mu\text{m}$  内に最高 9 本までデータ配線トラックを取ることができる。使用する機能ブロックの数が増えて配線トラックが不足した場合は、電源線(VDD)とPMOSトランジスタ領域の間を広げて追加の配線トラックを挿入する(これをセルのストレッチという。)。図4に、新規セル構造の一例として、レジスタの1ビット分のレイアウトを示す。このセルには3個の端子(D, Q, QC)が存在する。図4(a)はデータ配線前、(b)はデータ配線7本を使用してセルのストレッチがない場合、(c)はデータ配線11本を使用してセルのストレッチがある場合を各々示している。(b)や(c)に示されているように、どの端子も任意の配線トラックと接続可能である。また、(c)では配線トラックが2本挿入されて、内部制御信号線(T, TC)と、PMOSトランジスタとVDDをつなぐ配線が伸びている様子が分かる。

### 3.3 機能ブロックライブラリ

表1にこのデータバスジェネレータが提供する主な機能プロックの諸元を示す。プロセス技術は、標準の $0.8\text{ }\mu\text{m}$  2層アルミ1層ポリシリコンを使用しており、すべての機能プロックはデータビット幅64まで対応できるよう設計されている。また、データ出力にはトライステートオプションがあり、駆動能力は3種類切替え可能である。このほかに、機能プロ

図5 システム構成

ックごとに機能指定用パラメータがある。例えば、加算器や ALU には速度選択オプションがあり、ユーザーは自分のデータパスに最適な回路を使用することができる。

表1には、機能ブロックの性能も併せて載せている。例えば、64ビット加算器(高速型)の遅延時間(標準プロセス条件・電源電圧5V・常温)は6.5ns、集積度は7.21 kTr/mm<sup>2</sup>であり、速度・集積度ともに手設計のものと同レベルにある。

### 3.4 システム構成

図5にデータパスジェネレータのシステム構成を示す。ユーザーは機能ブロックライブラリを用いてデータパスのプロック図を入力する。論理検証用に機能ブロックごとにシミュレーションモデルが生成される一方、各機能ブロックのレイ

図6. 入力ブロック図例(ユーザーインターフェース画面)

図7. 生成データバス例

アウトがアレーコンパイラによって生成される。あらかじめ手設計されたリーフセルがセル配置規則に従って配列される。最後に、機能ブロックが配置配線されてデータバス全体のレイアウトが生成される。なお、アレーコンパイラや配置配線ツールは独自開発のものを使うことにより、当社のプロセス技術を十分に生かしたレイアウトが実現可能となつた。

図5には記載していないが、配置配線ツールはデータバス全体のレイアウトを生成するとともに、データ配線各々の配線容量と、ビットごとのストレッチ長をシミュレーションモ

デルにフィードバックする。これにより、レイアウト生成後の詳細な遅延解析とタイミング検証が可能である。

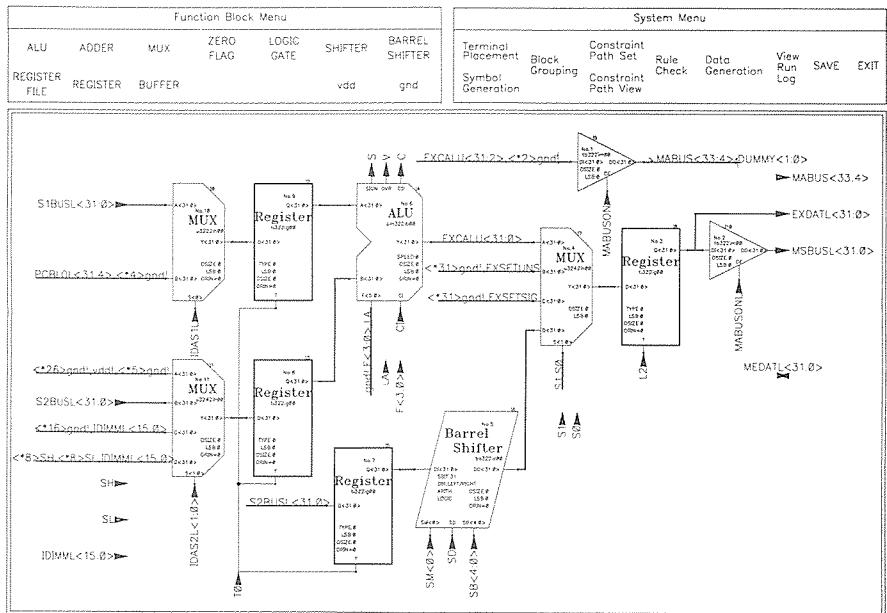

#### 4. 適用例

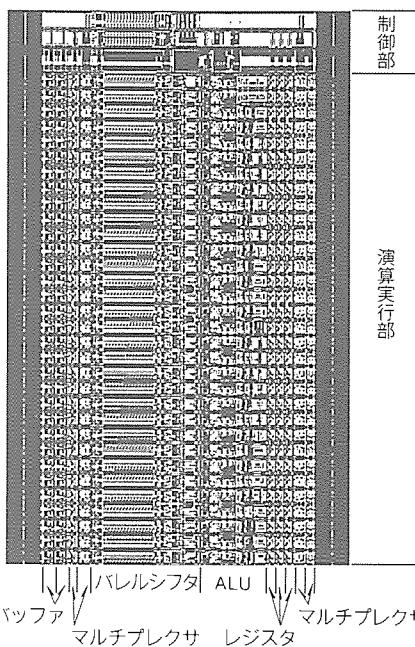

このデータバスジェネレータを32ビットの標準的なデータバスに適用した場合の、入力ブロック図(ユーザーインターフェース画面)を図6に、生成されたレイアウトを図7に示す。このデータバスは6種類(ALU、バレルシフタ、2入力及び4入力マルチプレクサ、レジスタ、バッファ)，11個の機能ブロックで構成されており、面積は約0.81 mm × 1.68 mm、集積度は約6.7 kTr/mm<sup>2</sup>、クリティカルパスはALUの約7 nsである。また、性能評価用テストチップに搭載した他の例では、集積度は5.8～7.3 kTr/mm<sup>2</sup>であった。

#### 5. むすび

新規セル構造と当社独自のCADツールを使用して、0.8 μmCMOSプロセスに対応したセルベース用データバスジェネレータを開発した。これにより、7 kTr/mm<sup>2</sup>を超える人手設計並みのデータバス自動生成が可能となり、今後実品種に適用していく予定である。

#### 参考文献

- (1) 篠原尋史、辻橋良樹、塙本美智子、津田和彦、藤森久美子、松本憲昌、味岡佳英：セルベース設計用モジュールジェネレータ、三菱電機技報、65, No. 2, 150～155 (1991)

- (2) 中林竹雄、近藤晴房、藏永 寛、長谷川浩一、山本誠二：ISDN基本インターフェース用LSI、三菱電機技報、65, No. 2, 186～189 (1991)

- (3) 覚埜高音、鈴木孝昌、川畑英雄、岸田 悟、長谷川浩一：CB-1設計システムを用いた8 kbps単位交換可能の大容量時分割スイッチLSI、三菱電機技報、65, No. 2, 190～193 (1991)

- (4) Preas, B., Lorenzetti, M. : Physical Design Automation of VLSI Systems, The Benjamin / Cummings Publishing Company, Inc., 317～321 (1988)

- (5) 中尾博臣、北田 修、塙本美智子、岡崎 芳、辻橋良樹、松本 尚：高密度データバスコンパイラのレイアウト生成方法、情報処理学会、設計自動化研究報告、63-2 (1992)

# キャッシュメモリを含んだメインメモリ用 4MビットキャッシュDRAM

早野浩司\*

阿部英明\*

石塚康宏\*\*

## 1. まえがき

半導体プロセス技術の進歩によるLSIの高速化傾向は、メインメモリよりもマイクロプロセッサ(MPU)において目覚ましいものがある。このため、メインメモリの高速化はメインフレームのみならずパーソナルコンピュータにおいても必要となってきた。MPUとメインメモリの速度ギャップを埋める方法としてはMPU自身にキャッシュメモリを内蔵する方法やメインメモリへのアクセスを高速化する方法がある。