# MITSUBISHI 三菱電機技報

MITSUBISHI DENKI GIHO Vol.66 No.2

2

1992

メモリ・マイクロコンピュータ特集

### メモリ・マイクロコンピュータ特集

#### 目 次

|                                           |      |

|-------------------------------------------|------|

| 卷頭言                                       | 1    |

| 北岡 隆                                      |      |

| 現状と動向                                     |      |

| メモリ・マイクロコンピュータの現状と動向                      | 2    |

| 平林庄司                                      |      |

| 最先端デバイス技術                                 |      |

| 64Mビット DRAM技術                             | 9    |

| 宮本博司・諸岡毅一・有馬秀明・蜂須賀敦司                      |      |

| 16Mビット フラッシュメモリ技術                         | 15   |

| 寺田 康・味香夏夫・中山武志・小林真一・宮脇好和                  |      |

| 学習機能付きニューロチップ                             | 20   |

| 有馬 裕・村崎充弘・山田 強・前田 敦                       |      |

| 大規模並列処理用データ駆動型マイクロプロセッサ                   | 24   |

| 小守伸史・田村俊之・浅井文康・佐藤尚和・高田英裕                  |      |

| メモリ                                       |      |

| 16Mビット DRAM                               | 30   |

| 有本和民・日高秀人・平山和俊・若宮 互・野崎雅彦                  |      |

| 4Mビット バイト／ワードワイド DRAM                     | 35   |

| 長瀬功一・源城英毅・豊本英晴                            |      |

| 低消費電力 4Mビット CMOS スタティック RAM               | 41   |

| 藤田雄明・塘 一仁・須賀原和之・福本晃二・浮田 求                 |      |

| 超高速256Kビット BiCMOS SRAM                    | 46   |

| 塙見 徹・大林茂樹・本田裕己・石垣佳之・梶澤正哉                  |      |

| 高速ページモード16Mビット マスク ROM                    | 51   |

| 牧原浩泰・香田憲次・外山 穀・山内直樹                       |      |

| 高速高密度メモリモジュール シリーズ                        | 55   |

| 田原次夫・福元孝和・宮武秀司                            |      |

| マイクロコンピュータ                                |      |

| GMICRO M32ファミリー及びソフトウェア                   | 61   |

| 小山和美・日向純一・坂本直史・有岡武志・亀井達也                  |      |

| GMICRO M32／100のページプリンタへの応用                | 70   |

| 山内直樹・大橋伸一郎・中嶋純子・的場成浩・松山景洋                 |      |

| VTRソフトウェアサーボ用                             |      |

| 16ビット マイクロコンピュータ                          | 75   |

| 林 和夫・尚永幸久・武部秀治・山田国裕・元吉啓登・鈴木次男             |      |

| SCSI専用コントローラ                              | 84   |

| 堀 俊彦・須田眞二・小林 洋・遠藤茂行・川嶋健司                  |      |

| 8ビット マイクロコンピュータ“38000シリーズ”                | 91   |

| 竹内 稔・阿部 稔・林 良紀・石丸善行・武部秀治                  |      |

| ワンチップ マイクロコンピュータの                         |      |

| 応用技術とソフトウェア                               | 99   |

| 山田国裕・川原林 隆・松井秀夫・藤沢行雄・浅野真弘・玉木浩子            |      |

| 要素技術                                      |      |

| 超高集積 DRAM 用キャパシタ誘電体膜形成技術                  | 106  |

| 小林清輝・中野 豊・福本晃二・林出吉生・奥平智仁                  |      |

| 位相シフトリソグラフィ技術                             | 111  |

| 吉岡信行・宮崎順二・楠瀬治彦・青山 哲・Maaiice Op de Beeck   |      |

| 先端デバイス開発における信頼性評価解析技術                     | 116  |

| 三橋順一・小守純子・石井達也                            |      |

| 0.5mm厚 TABパッケージとその応用                      | 121  |

| 寺岡康宏・島本晴夫・立川 透・竹村誠次・上田哲也・御祓如 英也           |      |

| 生産技術                                      |      |

| ユーザーニーズにこたえる販売・生産統合情報ネットワーク               | 126  |

| 奥野治臣・続木捷雄・山本武夫                            |      |

| 最先端工場における生産システム                           | 131  |

| 山崎雅敏・青木利明・御堂洋一                            |      |

| 特許と新案                                     |      |

| 半導体メモリ装置・位相比較器                            | 139  |

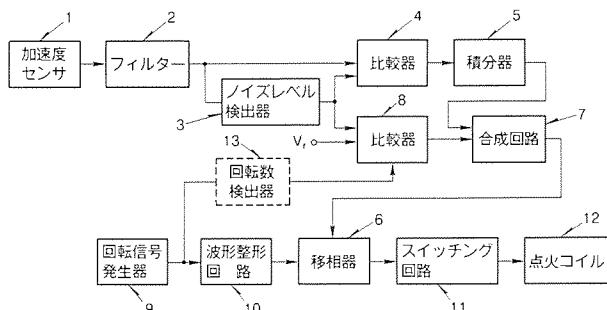

| 内燃機関の点火時期制御装置                             | 140  |

| スポットライト                                   |      |

| プレアラームリレー“BE-Pシリーズ”                       | 137  |

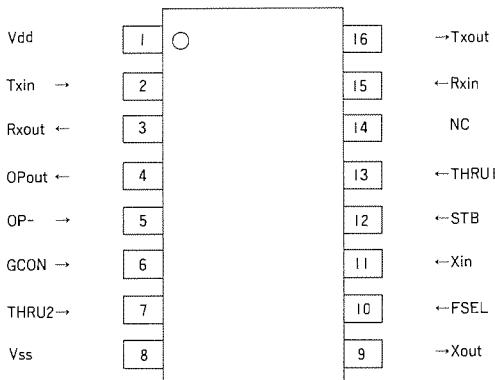

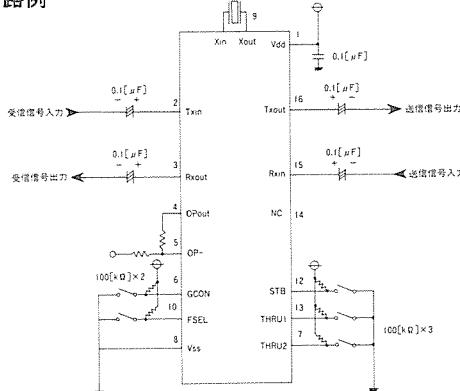

| コードレス電話用秘話 IC M64021FP                    | 138  |

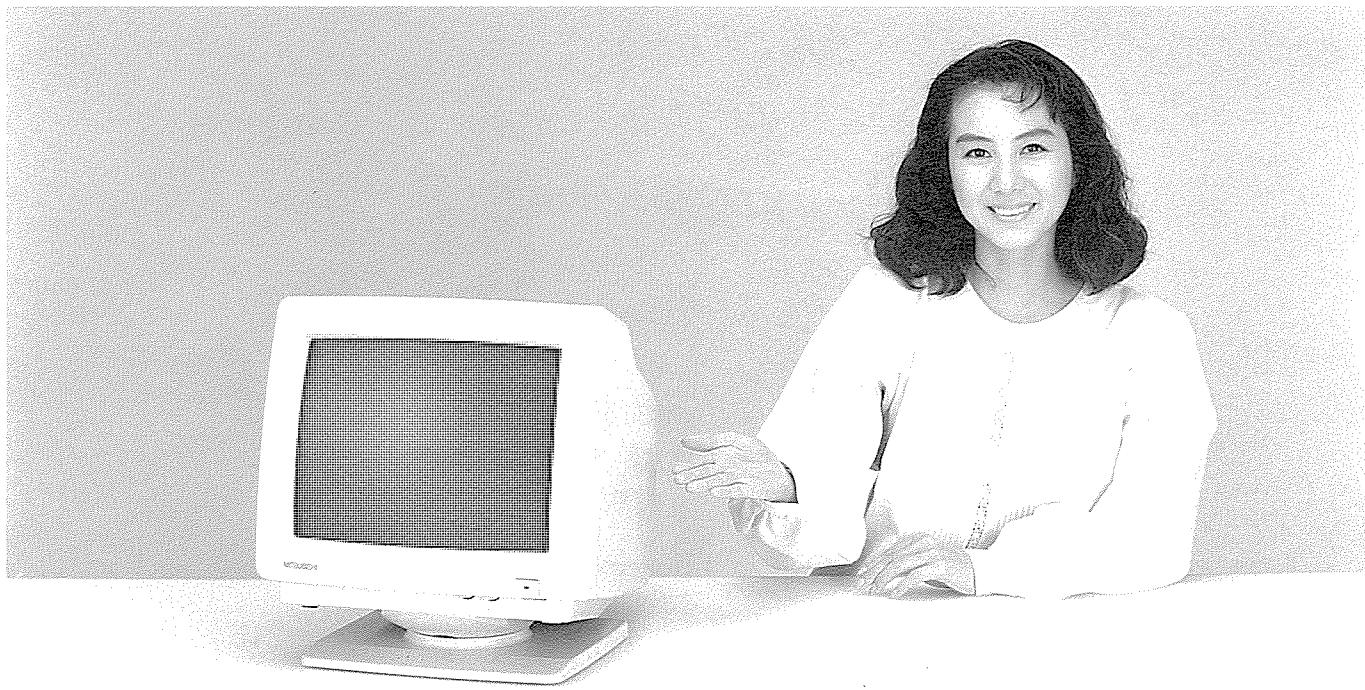

| Windows3.0 対応 14" 高解像度モニタ XC-98V3         | 141  |

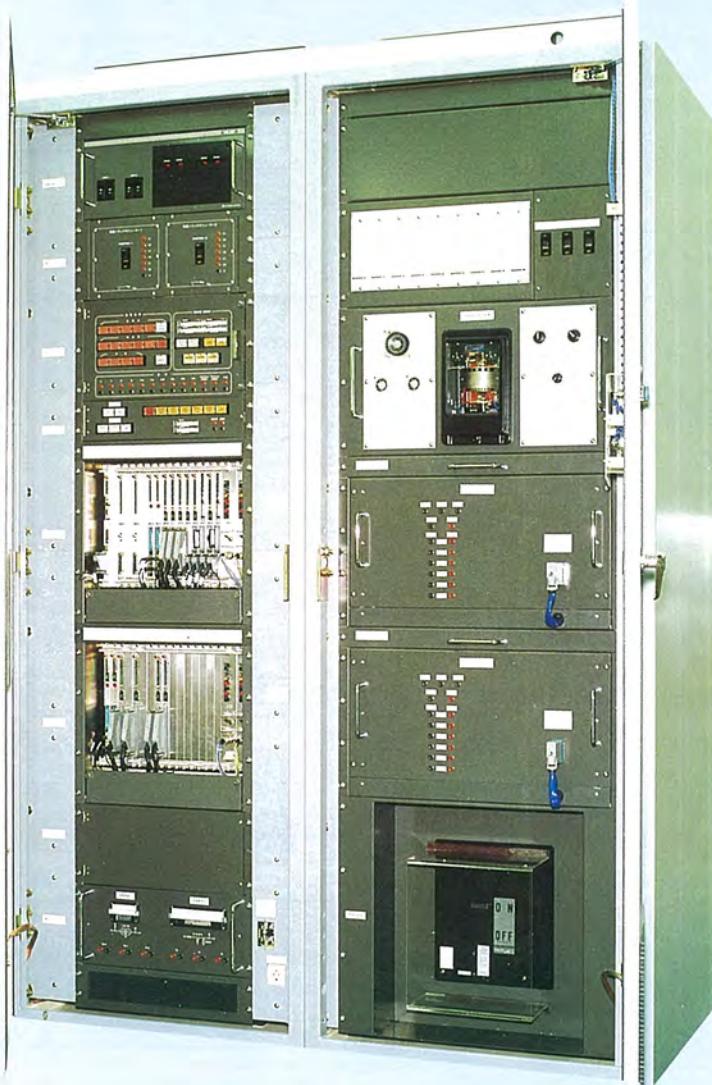

| ディジタル式励磁制御装置                              | 142  |

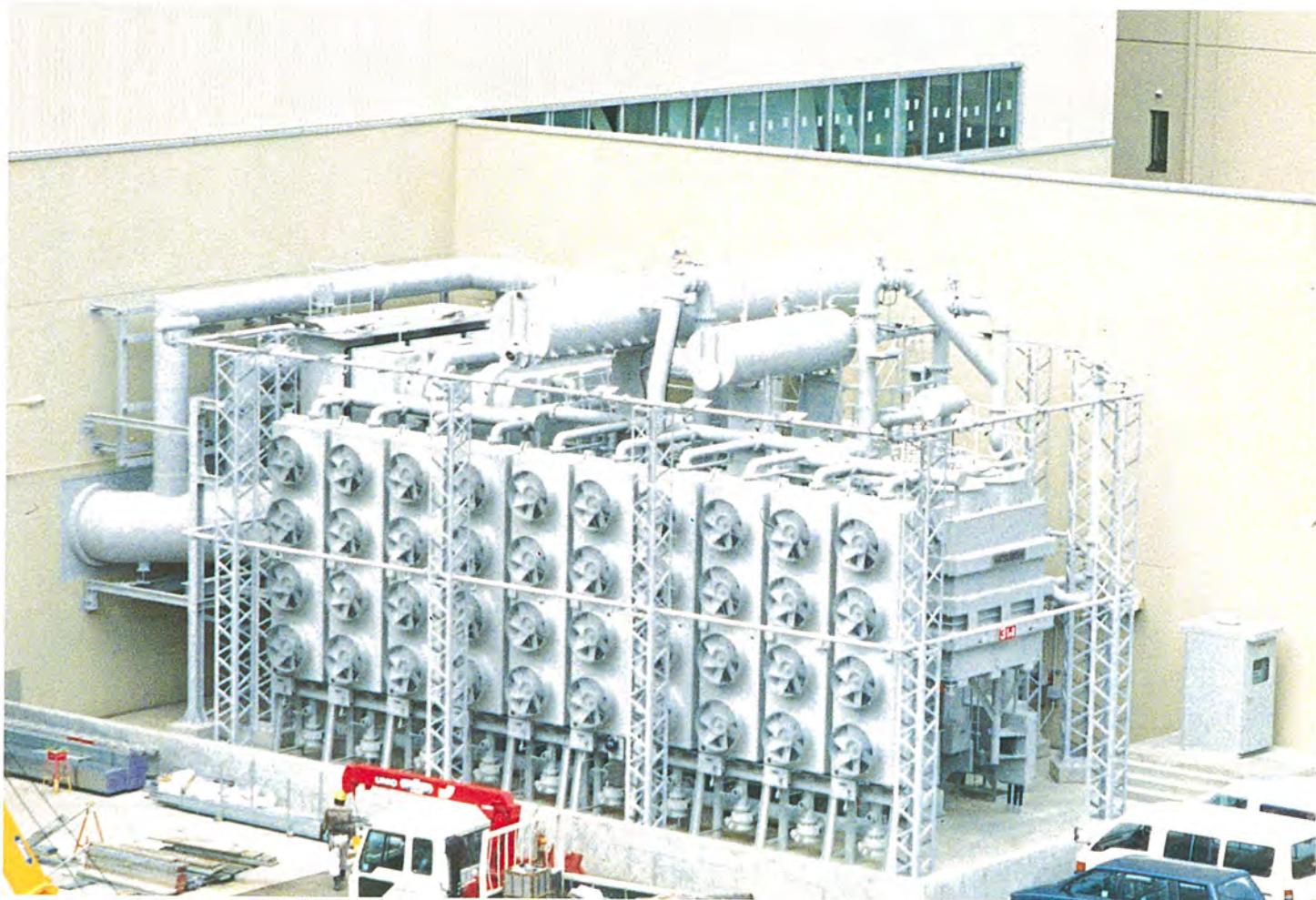

| 関西電力(株)大飯発電所向け515kV, 1,260MVA<br>3,4号主変圧器 | (表3) |

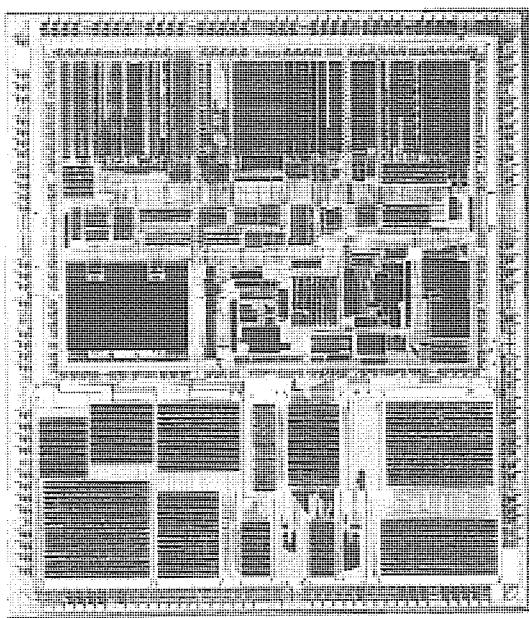

#### 表紙

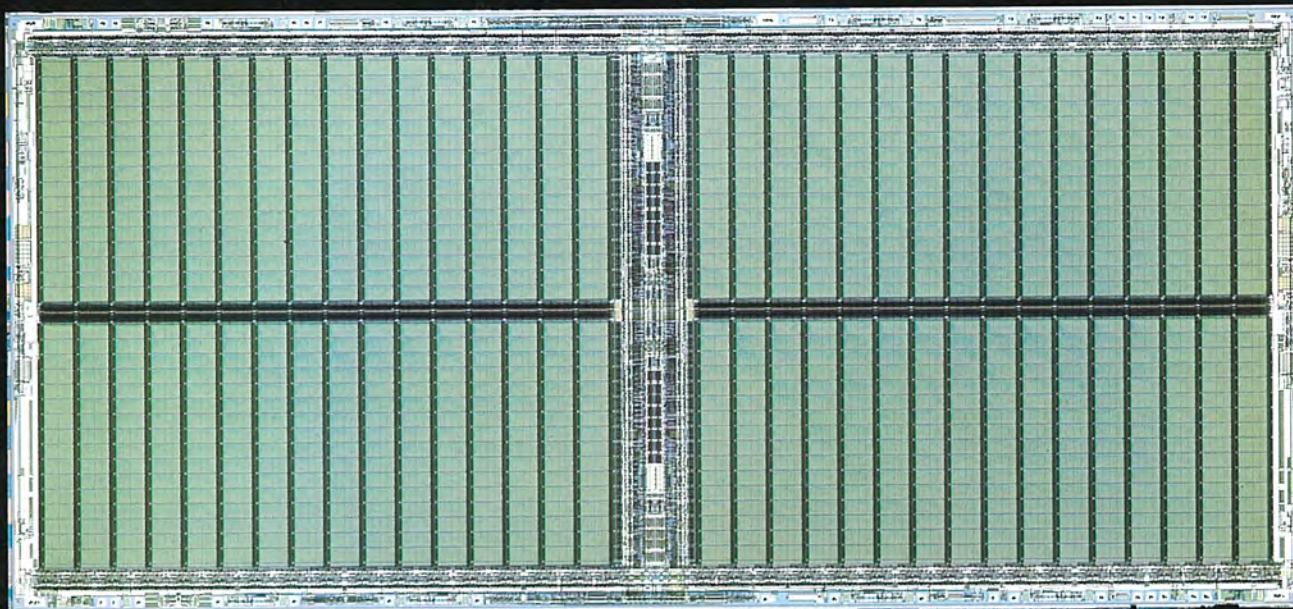

##### 16Mビット DRAM のチップ写真と西条工場の全景

16Mビット DRAM (M5M416100/M5M416400) は、当社におけるハーフミクロンの最先端半導体プロセス技術を駆使して実現した大容量、高速、低消費電力の超 LSI である。

西条工場(愛媛県西条市)は全体がFAを駆使した最先端工場でメモリの主要生産からマイクロコンピュータ、ASIC(特定用途向けIC)も生産できる当社の1大拠点である。当社の半導体生産拠点としてはこの他に国内に4拠点、海外に2拠点を持っており研究所として3拠点を含めて開発・生産には万全を期している。

三菱電機技報に掲載の技術論文では、国際単位“SI”(SI 第2段階(換算値方式)を基本)を使用しています。ただし、保安上、安全上等の理由で、従来単位を使用している場合があります。

## アブストラクト

### メモリ・マイクロコンピュータの現状と動向

平林庄司

三菱電機技報 Vol. 66 · No. 2 · P 2 ~ 8

メモリとマイクロコンピュータの現状と動向について述べる。市場のニーズと向上を続ける半導体技術によるメモリとマイクロコンピュータの製品化傾向を特に明らかにした。また、この特集の個別論文の掲載のねらいを明確にする紹介を併せて示した。

### 64M ビット DRAM 技術

宮本博司・諸岡毅一・有馬秀明・蜂須賀敦司

三菱電機技報 Vol. 66 · No. 2 · P 9 ~ 14

高集積かつ高性能の64M DRAM を実現する技術を開発した。ストレージノードを上下2層のセルプレートで包んで容量を増大させたDCP(Dual Cell Plate)メモリセル、高速アクセス時間とテスト時間の短縮(テスト時間の1/16,000化)を同時に実現するマージド マッチラインテスト(MMT)方式、及びMMT方式に適合したカスケード冗長方式を開発した。これらの技術によって64M DRAM を試作し、45ns の高速アクセス時間を実現した。

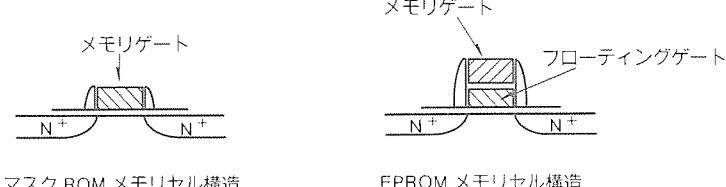

### 16M ビット フラッシュメモリ技術

寺田 康・味香夏夫・中山武志・小林真一・宮脇好和

三菱電機技報 Vol. 66 · No. 2 · P 15 ~ 19

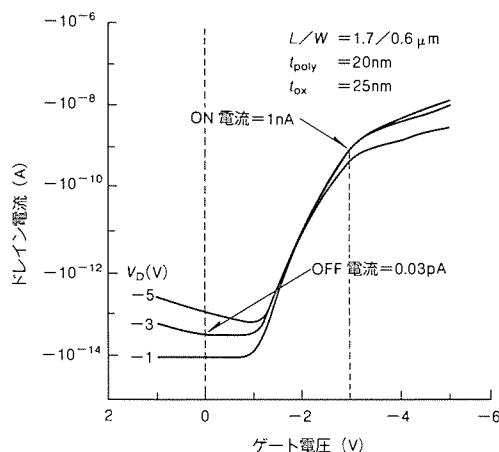

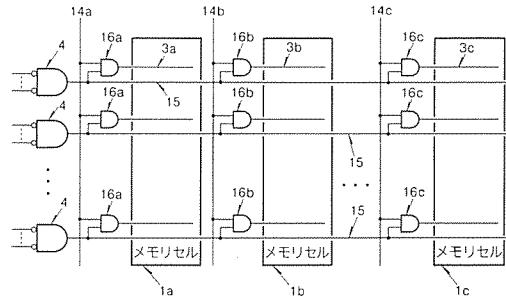

0.6 μm のCMOSプロセスを用いて、EPROMと同様のセル構造で電気的消去機能を実現した不揮発性メモリについて述べる。消去時に電子を過剰に引き抜き、しきい値が負になるという過剰消去を、メモリアレーを分割して各々に消去制御回路を設けることによって回避した。シーケンスコントローラを内蔵しているので消去や書き込みを指示するコマンドを入力するだけによく、オンボードで書換えが可能。さらに、高機能化を実現するデバイス/回路技術についても紹介する。

### 学習機能付きニューロチップ

有馬 裕・村崎充弘・山田 強・前田 敦

三菱電機技報 Vol. 66 · No. 2 · P 20 ~ 23

ニューラルネット情報処理の特徴の一つである自己組織化機能(学習機能)を半導体集積回路で実現した学習機能付きニューロチップを開発した。アナログ・デジタル混在設計により、学習制御回路を備えたシナプス回路を70 μm 角で実現し、28,224個のシナプスと336個のニューロンを1チップに集積できた。また、複数チップの相互接続による回路規模拡張を速度性能低下無しに行うため、Branch-Neuron-Unit アーキテクチャを開発した。

### 大規模並列処理用データ駆動型マイクロプロセッサ

小守伸史・田村俊之・浅井文康・佐藤尚和・高田英裕

三菱電機技報 Vol. 66 · No. 2 · P 24 ~ 29

ピーク性能50M FLOPS の1チップデータ駆動型マイクロプロセッサを開発した。0.8 μm 2層メタル2層ポリシリコンの微細CMOSプロセスを用いて、70万素子を1チップ上に集積した。このプロセッサは、動的数据駆動アーキテクチャを基本とし、科学技術計算の高速化のためのベクトル演算処理機能、マルチプロセッサ並列処理をサポートする諸機能をチップに内蔵し、大規模並列処理を効率的に行うこと目標にしている。

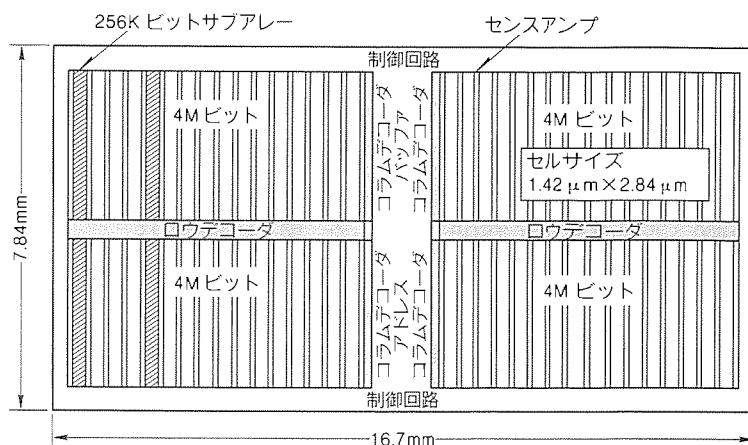

### 16M ビット DRAM

有本和民・日高秀人・平山和俊・若宮 亘・野崎雅彦

三菱電機技報 Vol. 66 · No. 2 · P 30 ~ 34

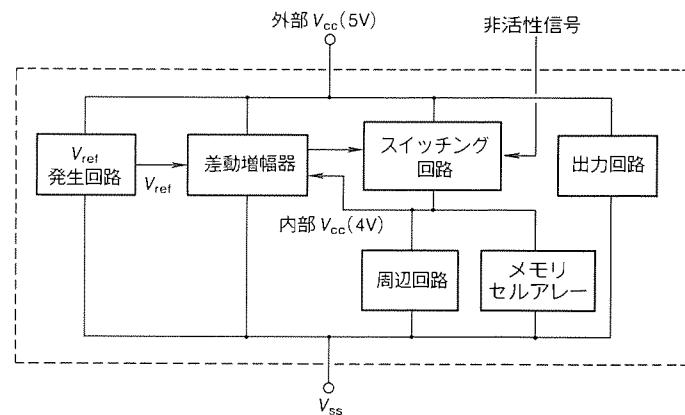

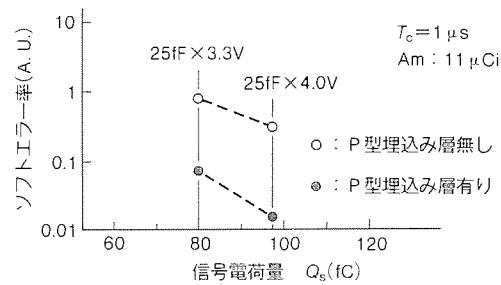

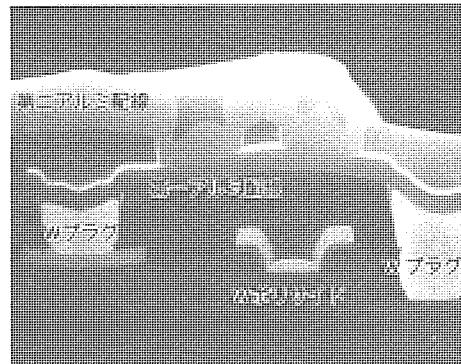

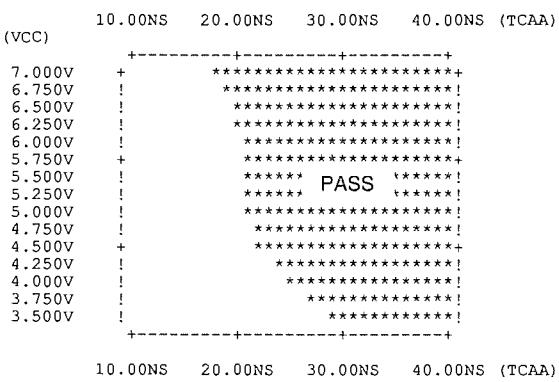

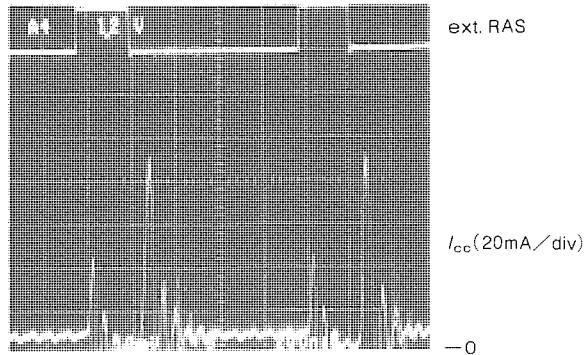

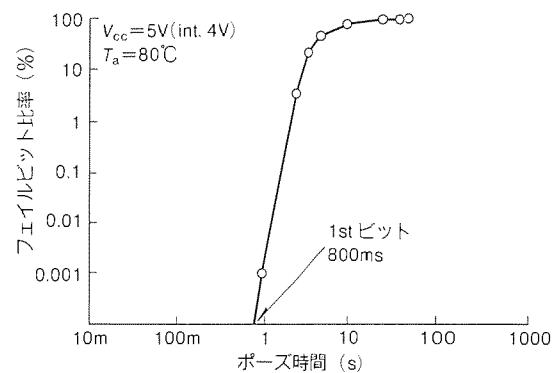

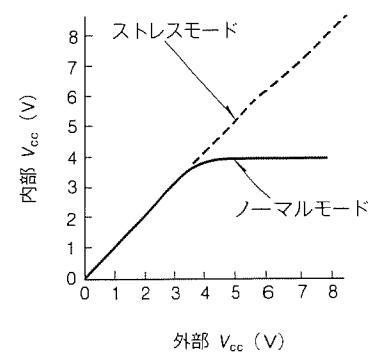

第一世代の16M DRAMを開発した。チップ面積は130.9mm<sup>2</sup>であり、内部降圧回路を搭載してデバイスの信頼性を確保している。また、2層アルミ配線、高性能トランジスタの採用でRASアクセス時間60ns(4.5V, 80°C)を実現した。0.5 μm の微細加工技術に加え、高濃度P型埋込み層、Wプラグのプロセス技術を採用してソフトエラー等信頼性上の問題に対して良好な結果を得た。さらに、テスト方式、冗長構成に設計上の工夫を加えて生産性向上を図っている。

### 4M ビット バイト/ワードワイド DRAM

長瀬功一・源城英毅・豊本英晴

三菱電機技報 Vol. 66 · No. 2 · P 35 ~ 40

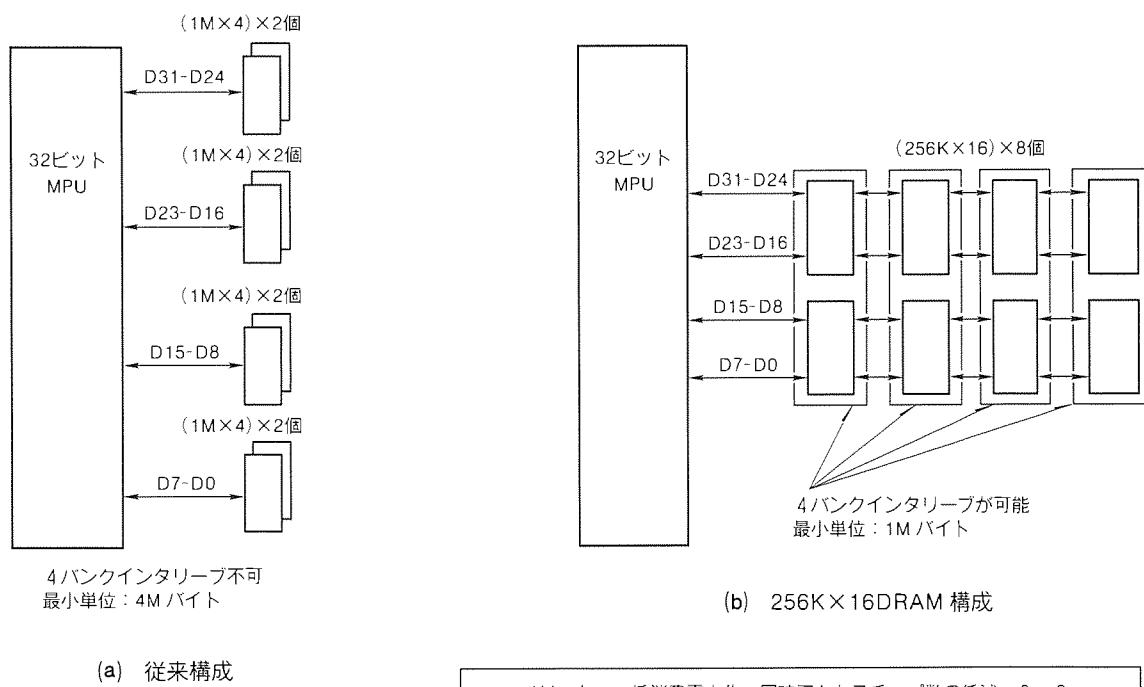

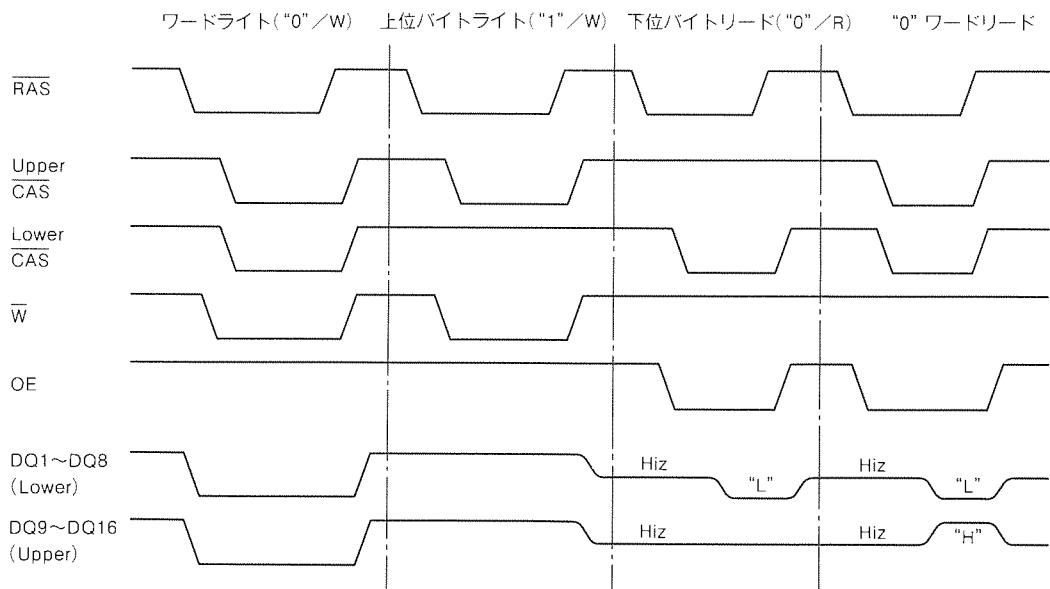

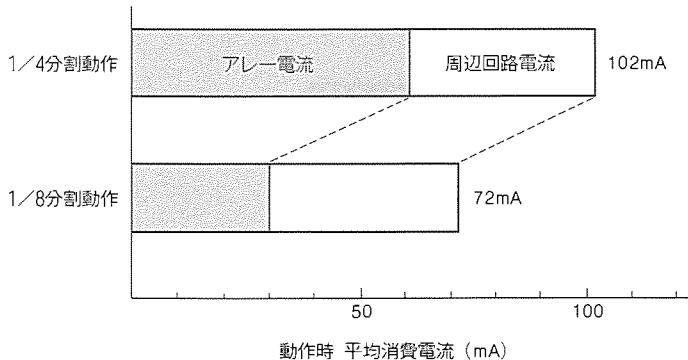

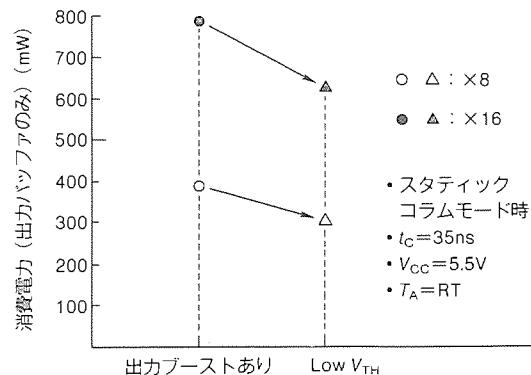

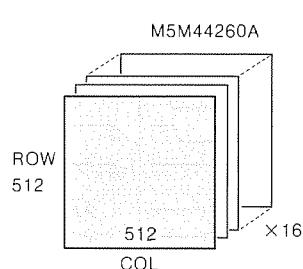

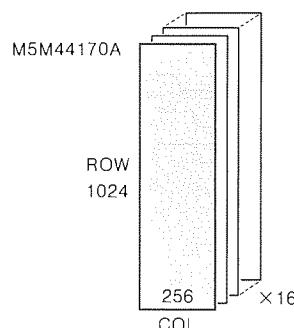

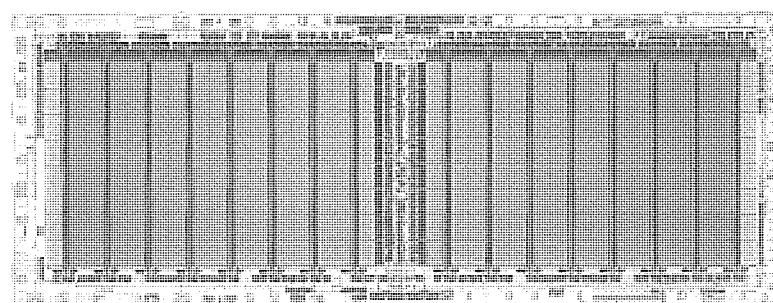

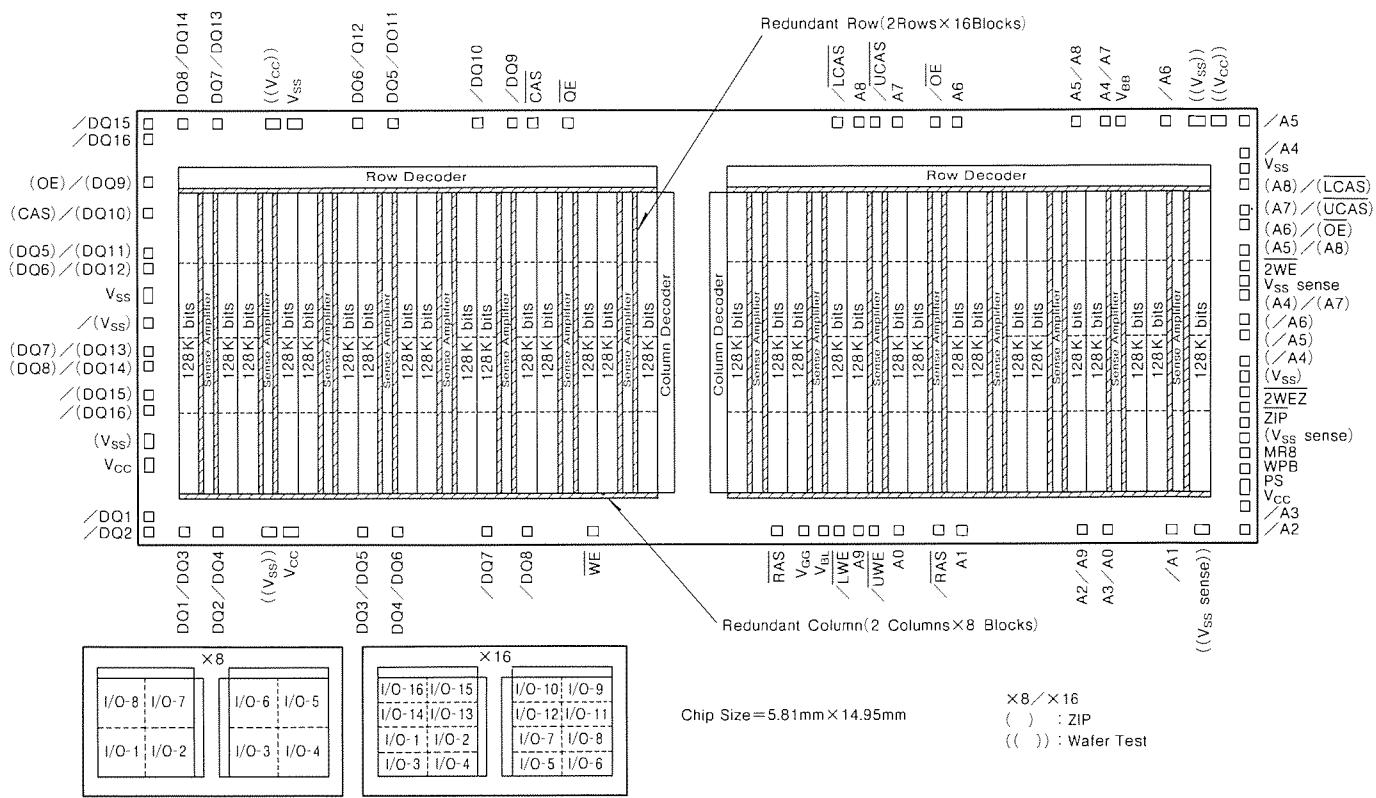

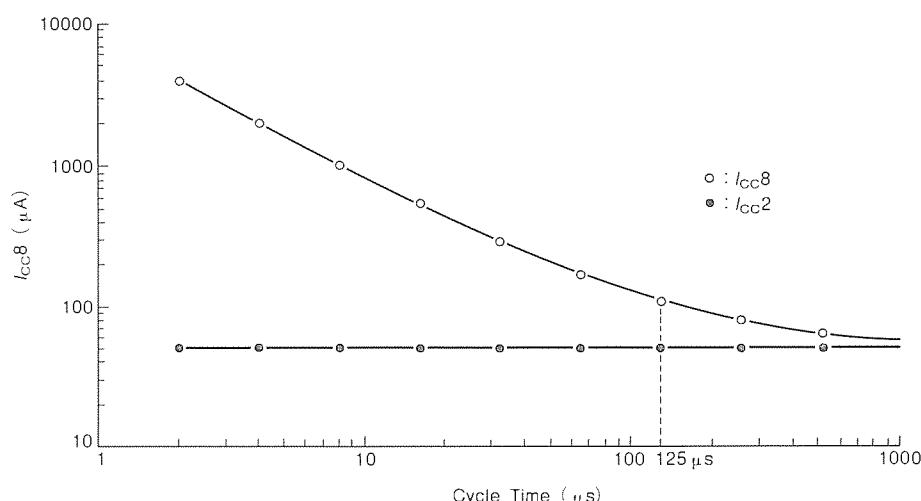

当社4Mビット第二世代品をベースとして×8/×16構成のメモリM5M44800A(512K×8), M5M44260A/M5M44170A(256K×16)の3機種を開発した。×16構成ではバイト/ワードコントロール機能を持たせるとともにリフレッシュの選別を可能とした。2層アルミ配線プロセス及び0.7 μm プロセスを採用するとともに一部回路の見直しにより、高品質を保つとともに低消費電力版の安定生産を可能としている。

### 低消費電力 4M ビット CMOS スタティック RAM

藤田維明・塘 一仁・須賀原和之・福本晃二・浮田 求

三菱電機技報 Vol. 66 · No. 2 · P 41 ~ 45

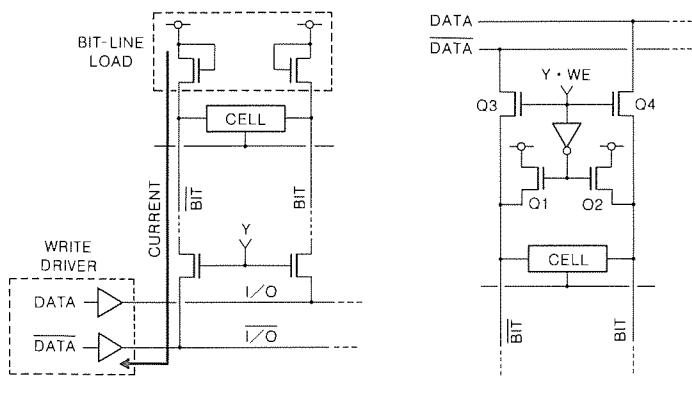

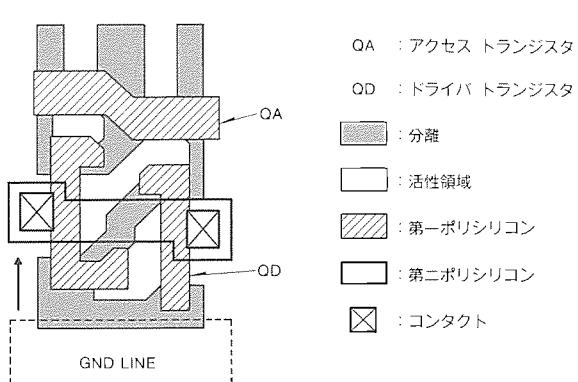

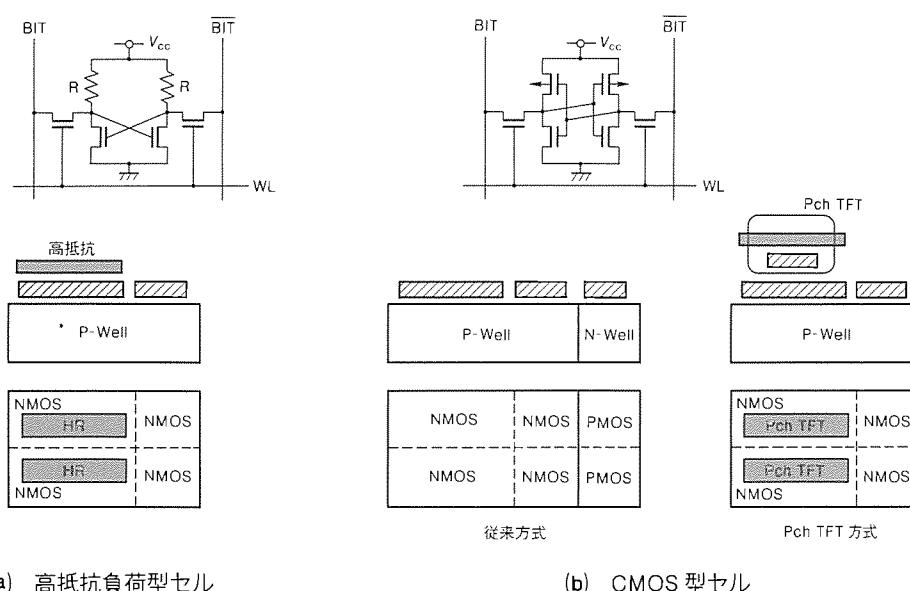

0.5 μm デザインルールと4ポリ2アルミプロセスを用いた512K語×8ビット構成の4MビットCMOS SRAMを開発した。低スタンバイ電流を実現するために、メモリセルを従来の高抵抗負荷型セルに替えて薄膜トランジスタ負荷型セルを用い、スタンバイ電流1 μA(電源電圧3V)以下を得ている。また、メモリセルアレーの64分割を始めとする低電力化技術により、動作時消費電流30mA(最悪条件)を実現している。

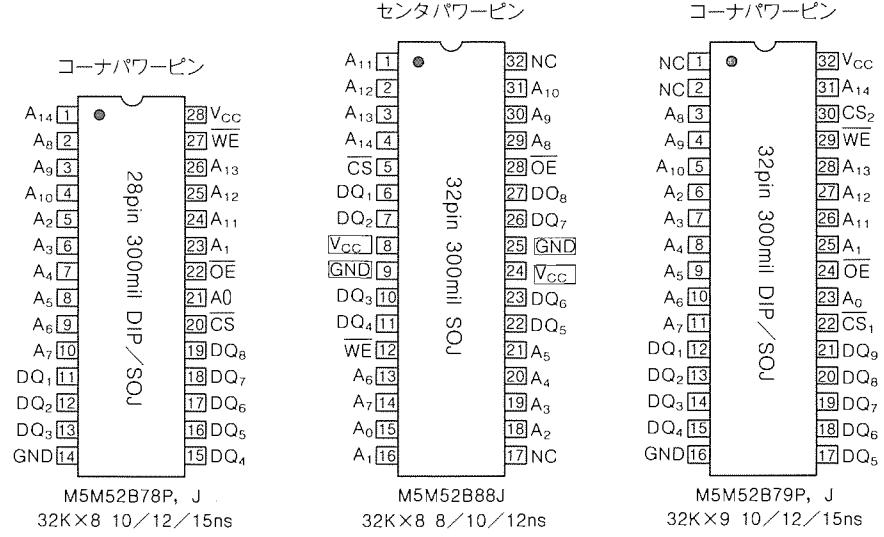

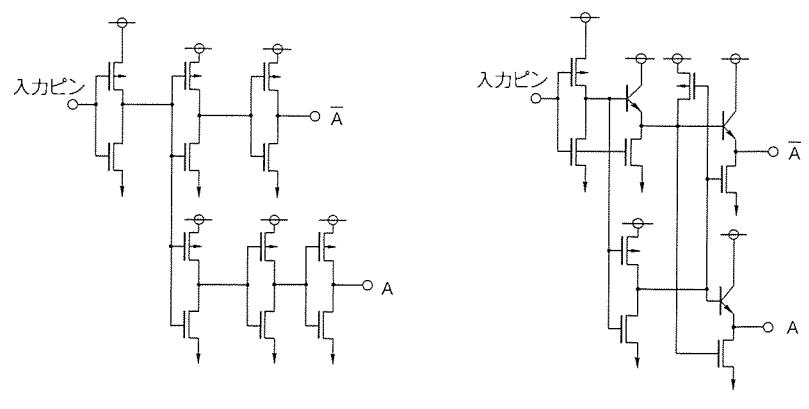

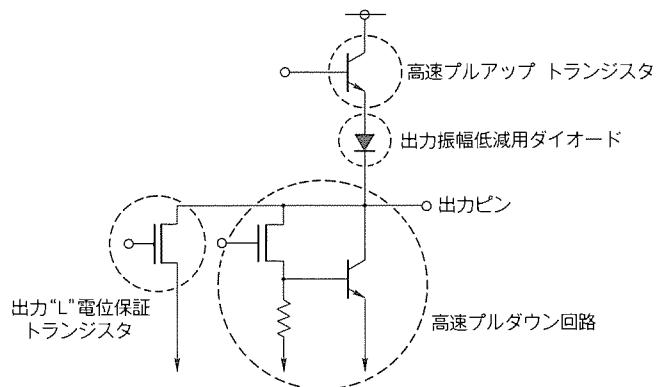

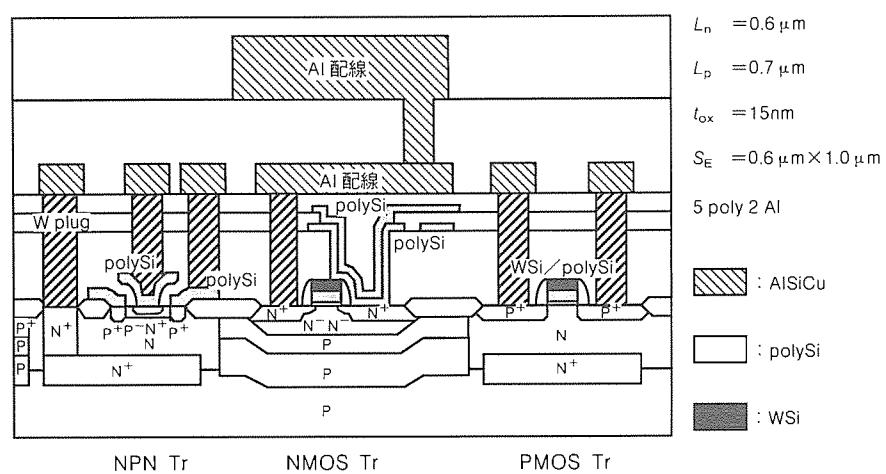

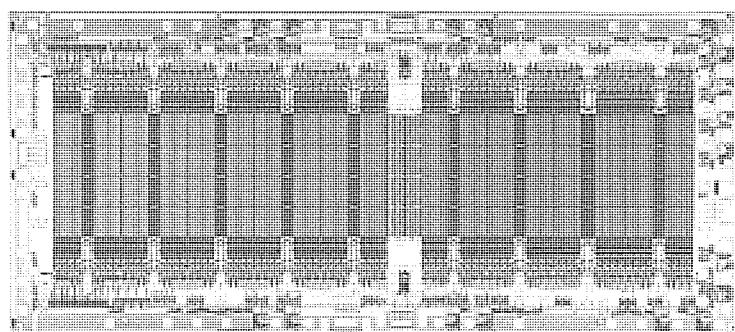

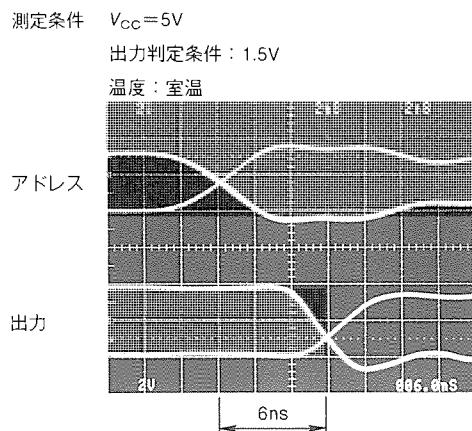

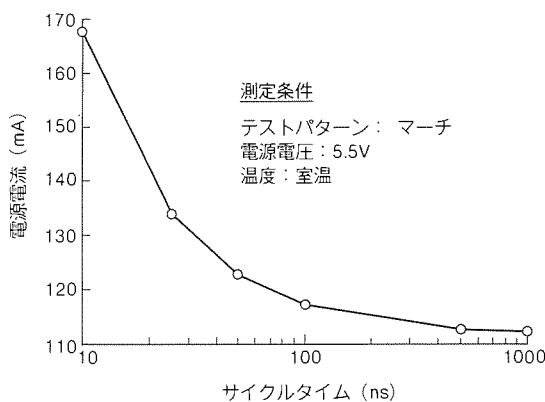

### 超高速256K ビット BiCMOS SRAM

塩見 徹・大林茂樹・本田裕己・石垣佳之・桃澤正哉

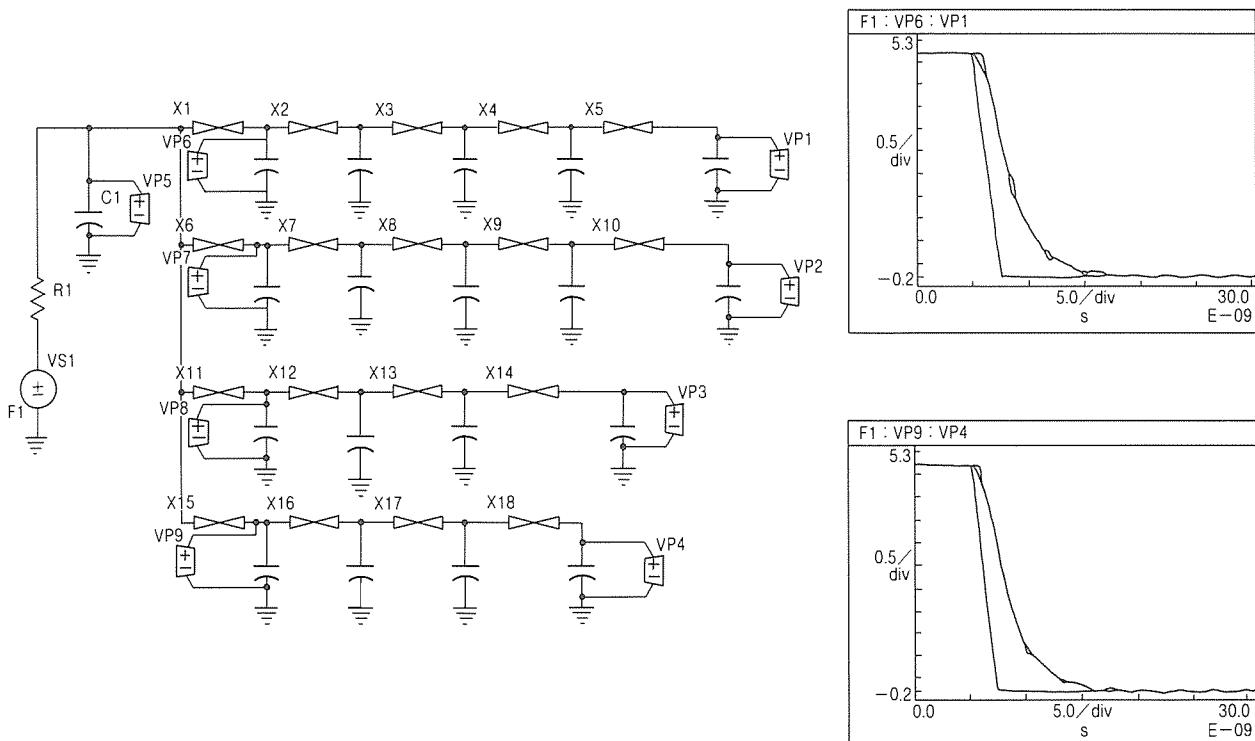

三菱電機技報 Vol. 66 · No. 2 · P 46 ~ 50

0.6 μm デザインルールと5ポリ2アルミBiCMOSプロセスを用いた32K語×8ビット構成の256KビットTTL入出力のSRAMを開発した。超高速アクセスタイムを実現するために、ピン配置をデュアルセンターパワーピンとし、チップサイズを4.0mm×8.8mmと従来より約35%縮小し、BiCMOS回路、プロセス技術を駆使して、アクセスタイム8nsを得ている。また、動作時消費電流は約170mAに抑えている。

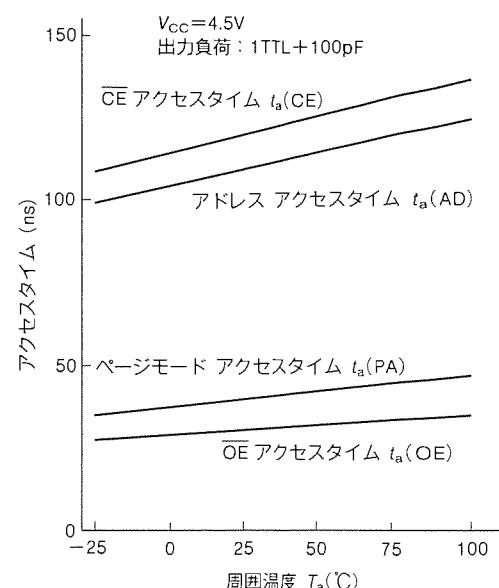

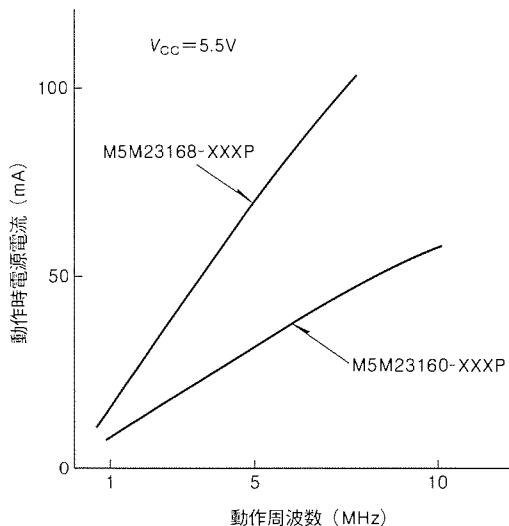

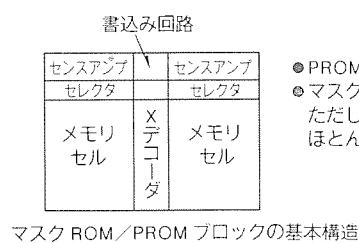

### 高速ページモード16M ビットマスク ROM

牧原浩泰・香田憲次・外山 肇・山内直樹

三菱電機技報 Vol. 66 · No. 2 · P 51 ~ 54

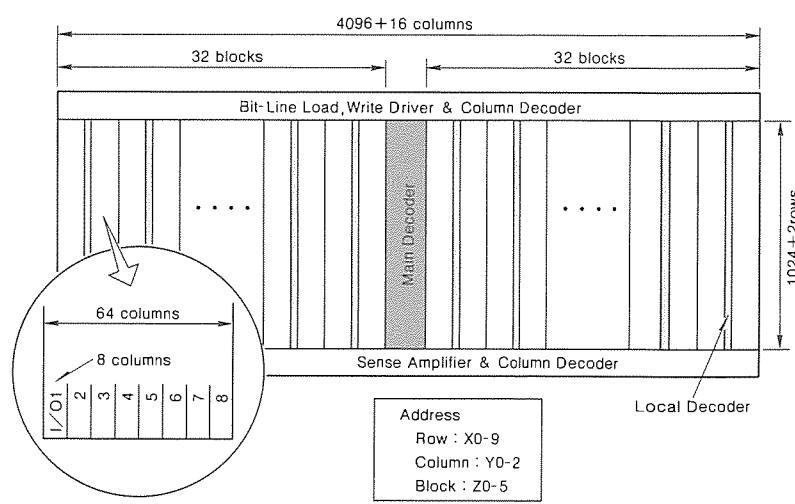

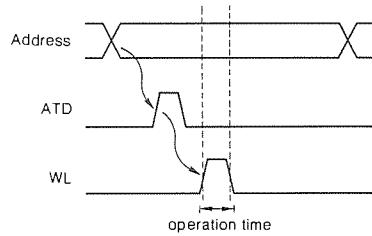

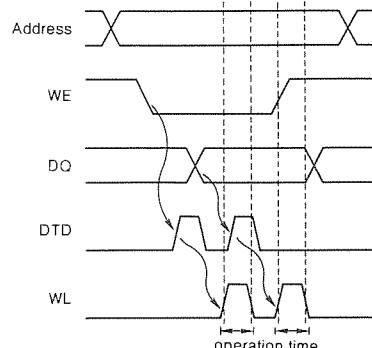

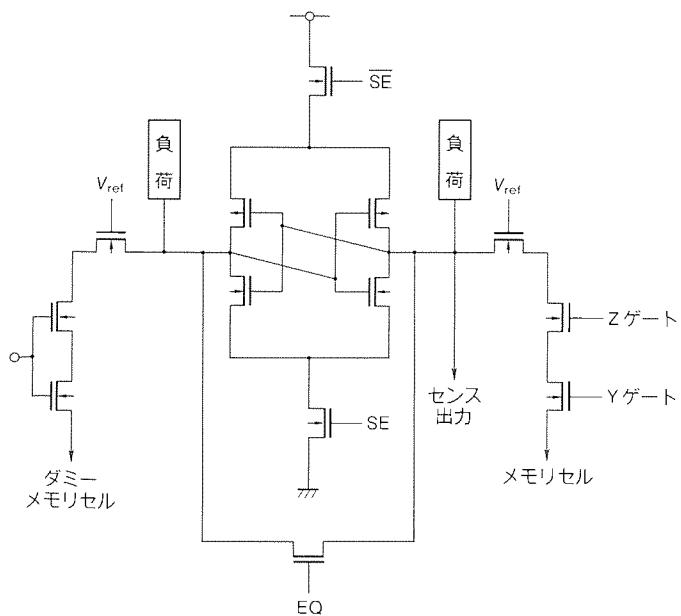

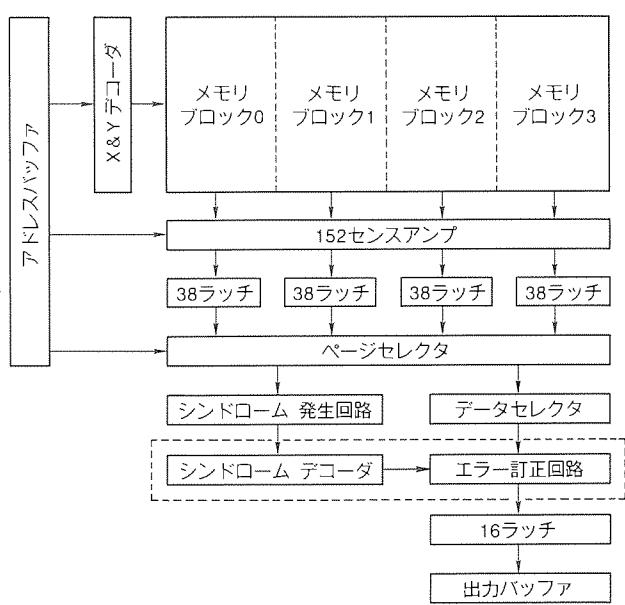

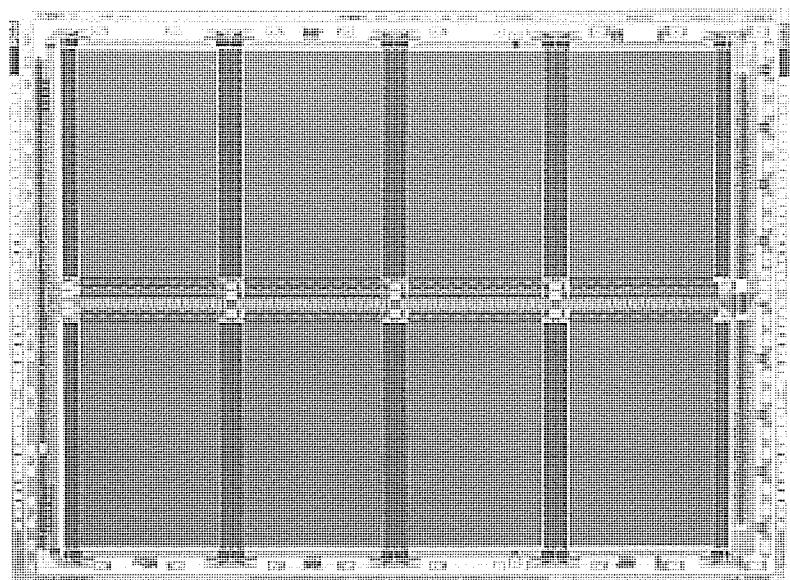

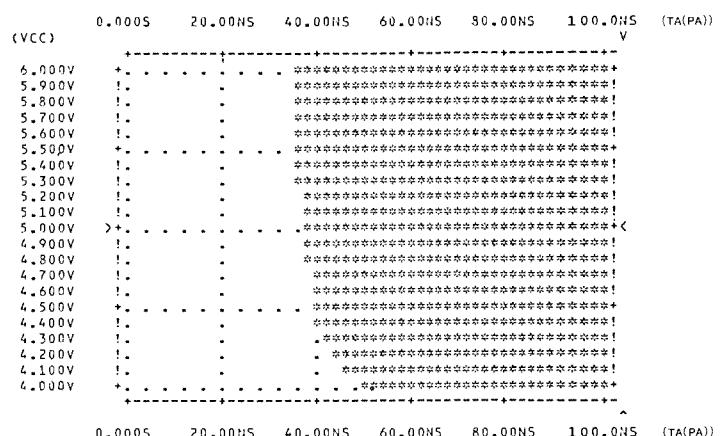

高速70nsのページモード付き16MビットマスクROMを開発した。ページモードは、8ワード又は16バイトの高速連続読出しを実現している。また、低消費電力化のためにATD(Address Transition Detection)信号で制御するラッチ型センサアンプを採用しており、高歩留り・高信頼性をECC回路を用いて実現している。

# Abstracts

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 30~34 (1992)

## A 16Mbit DRAM Device

by Kazutami Arimoto, Hideto Hidaka, Kazutoshi Hirayama, Wataru Wakamiya & Masahiko Nozaki

A first-generation 16Mbit DRAM device has been developed. The chip size is 130.9mm<sup>2</sup> and the device incorporates an internal voltage-dropping converter that improves reliability. Double-level aluminum wiring and high-performance transistors realize an RAS access time of 60ns at 4.5V and 80°C. Soft error problems in the 0.5μm geometry have been overcome by employing buried p+ layers and a tungsten plug process. Productivity has been improved by the development of suitable test methods and a redundancy scheme.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 35~40 (1992)

## 4Mbit Byte- and Word-Wide DRAM Devices

by Koichi Nagase, Hideki Genjo & Hideharu Toyomoto

The corporation has developed three new memory devices with × 8 and × 16 configurations based on its second-generation 4Mbit DRAM. M5M44800A is a 512k × 8bit configuration, and M5M44260A and M5M44170A are 256k × 16bit configurations. A byte/word control function and capability to select a refresh mode have been implemented in the 16-bit devices. The use of 0.7μm geometry and double-layer Al metalization, combined with a redesign of some circuit sections, has yielded low-power devices with stable production characteristics.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 41~45 (1992)

## A 4Mbit CMOS Static RAM Device

by Koreaki Fujita, Kazuhito Tsutsumi, Kazuyuki Sugawara, Koji Fukumoto & Motomu Ukita

A 512k × 8bit, 4Mbit CMOS SRAM device has been developed using a 0.5μm design rule, four polysilicon layers and two Al layers. The standby current has been reduced to less than 1μA under a 3V supply by employing a thin-film transistor load memory cell instead of the conventional high-resistance load type. The active current has also been reduced to 30mA by dividing the memory cell array into 64 blocks and applying other power-saving techniques.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 46~50 (1992)

## An Ultrahigh Speed 256kbit Bi-CMOS SRAM Device

by Toru Shioiri, Shigeki Ohbayashi, Hiroki Honda, Yoshiyuki Ishigaki & Masaya Kabasawa

A 256kbit SRAM device with a 32k × 8bit configuration, TTL-level I/O and an 8ns access time has been developed using a Bi-CMOS process with a 0.6μm design rule, quintuple polysilicon layers and double Al layers. The high speed has been achieved by employing a pinout with dual centered power pins, a 4.0 × 8.8mm chip size 35% smaller than previous devices, Bi-CMOS circuits, and optimized process technology. The active current consumption has been held to approximately 170mA.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 51~54 (1992)

## A Fast Page-Mode 16Mbit Mask ROM Device

by Hiroyasu Makihara, Kenji Koda, Tsuyoshi Toyama & Naoki Yamauchi

A 16Mbit mask ROM device with a 70ns page-mode access has been developed. The page mode realizes high-speed readout of eight words or 16 bytes. A latch-type sense amplifier controlled by the address transition detector (ATD) signal reduces power dissipation while an error checking and correction (ECC) circuit raises the device yield and reliability.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 2~8 (1992)

## The Current State and Trends in Memory and Microcomputer Technology

by Shoji Hirabayashi

The article discusses the current state and trends in two key semiconductor devices—memory chips and microcomputers—examining both devices and basic technologies. Market needs and product trends are identified. This article also provides an overall introduction to the articles in this issue.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 9~14 (1992)

## Technologies for 64Mbit DRAM Devices

by Hiroshi Miyamoto, Yoshikazu Morooka, Hideaki Arima & Atsushi Hachisuka

Technologies to implement high-density, high-performance 64Mbit DRAM devices have been developed. The storage node has been sandwiched between dual cell plates to increase the memory cell capacitance. A merged match-line test architecture has been developed that reduces the access time while shortening the device testing period by a factor of 16,000. A cascaded redundancy scheme compatible with the testing architecture has also been developed. Prototype devices have demonstrated access times of 45ns.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 15~19 (1992)

## 16Mbit Flash Memory Device Technology

by Yasushi Terada, Natsuo Ajika, Takeshi Nakayama, Shin'ichi Kobayashi & Yoshikazu Miyawaki

A 16Mbit flash memory device manufactured by a 0.6μm CMOS process is described. The memory cell structure is almost identical to that of UV-EPROM devices. An over-erasing problem that occurs during erasure when the excessive release of electrons from the floating gate causes the threshold voltage to go negative has been suppressed. The sequence controller is built-in, so that write and erase processes can be performed simply by applying the appropriate command input. Onboard rewriting is also possible. The article reports on this device and also introduces the device and circuit technologies used in its implementation.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 20~23 (1992)

## A Self-Learning Neural Network Chip

by Yutaka Arima, Mitsuhiro Murasaki, Tsuyoshi Yamada & Atsushi Maeda

An integrated circuit that implements self-methodical (self-learning) functions of neural networks has been developed. The use of a mixed-signal approach has realized a single synapse circuit on a 70μm square. This technique has been used to integrate 28,224 synapses and 336 neurons in a single device. The device also incorporates a branch-neuron-unit architecture that allows several devices to be linked together to increase the network scale without loss of speed.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 24~29 (1992)

## A Data-Driven Microprocessor for Large-Scale Parallel Processing

by Shinji Komori, Toshiyuki Tamura, Fumiyasu Asai, Hisakazu Sato & Hidehiro Takata

A 50MFLPS data-driven microprocessor has been developed. The device consists of 700,000 transistors integrated on a single chip using a 0.8μm, double-level metal, double-level polysilicon CMOS process. The dynamic data-driven architecture is supplemented by vector processing and multiprocessor parallel-processing support functions that make the device suitable for large-scale parallel applications.

## アブストラクト

|                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                              |

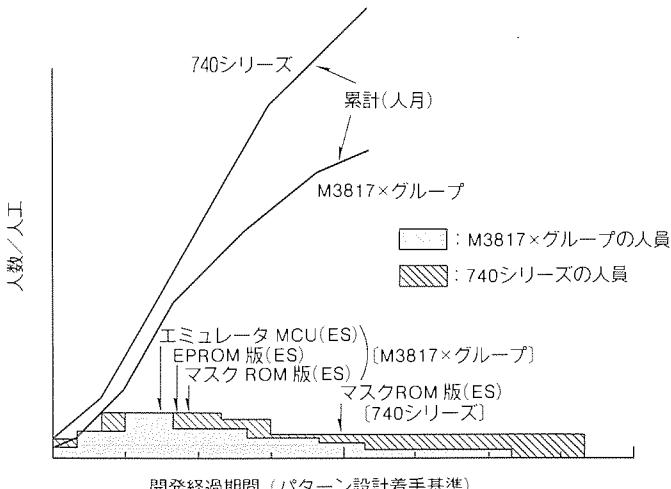

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

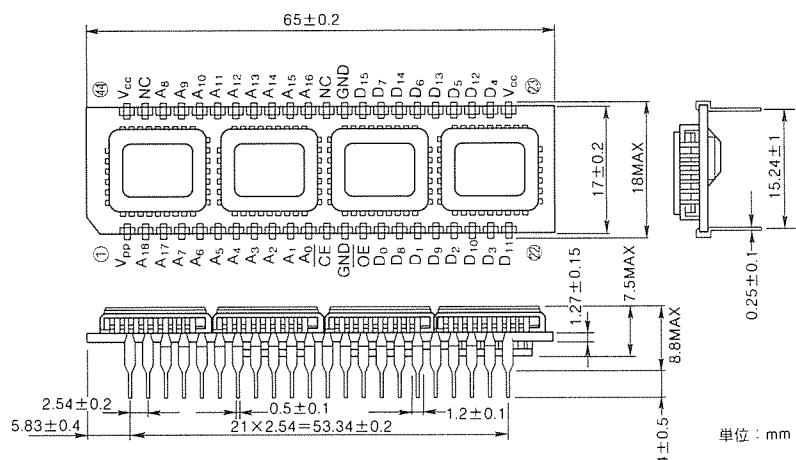

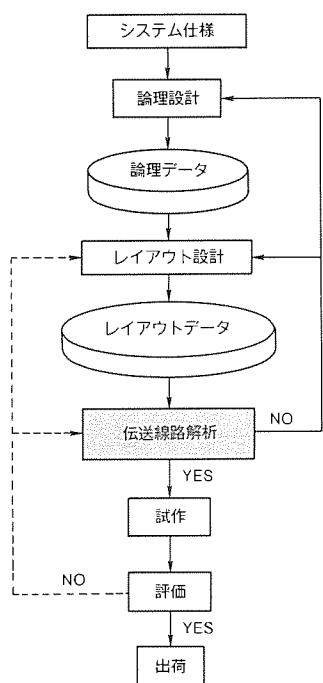

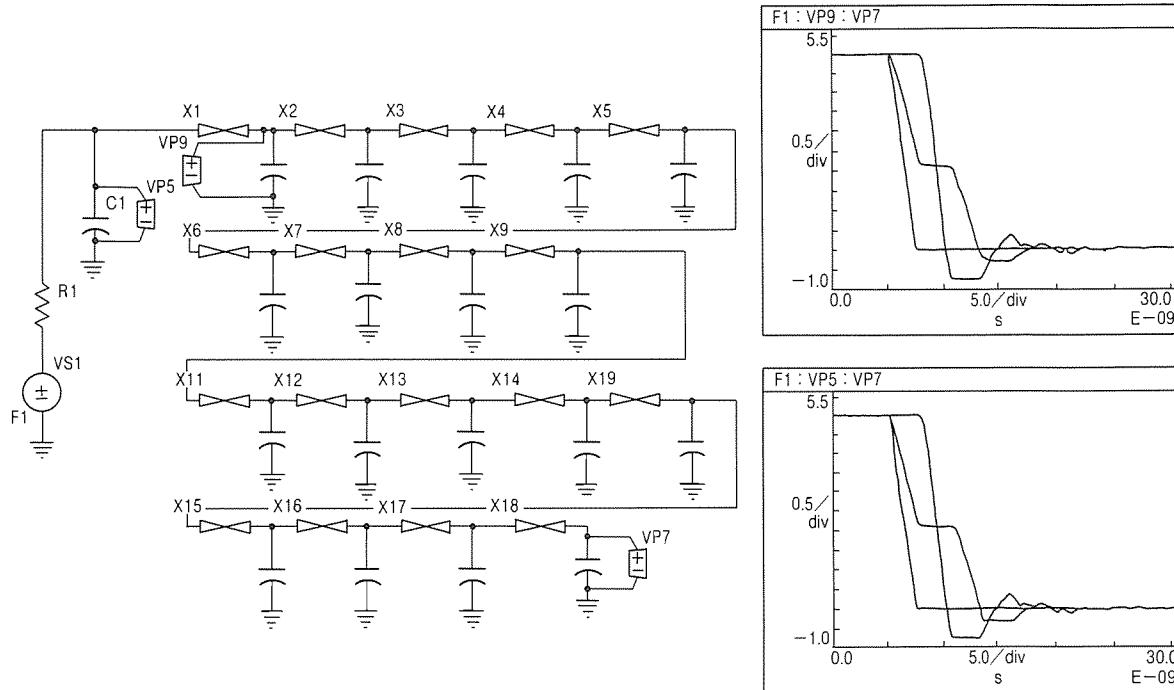

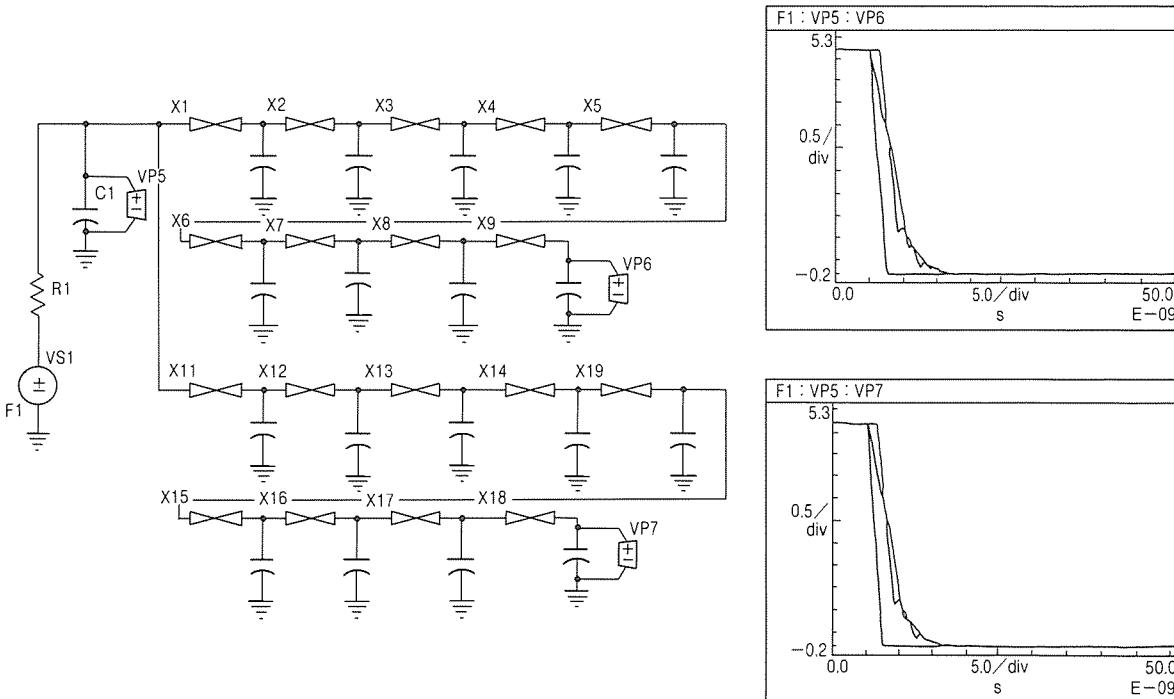

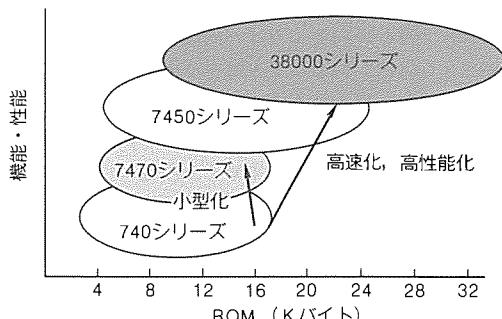

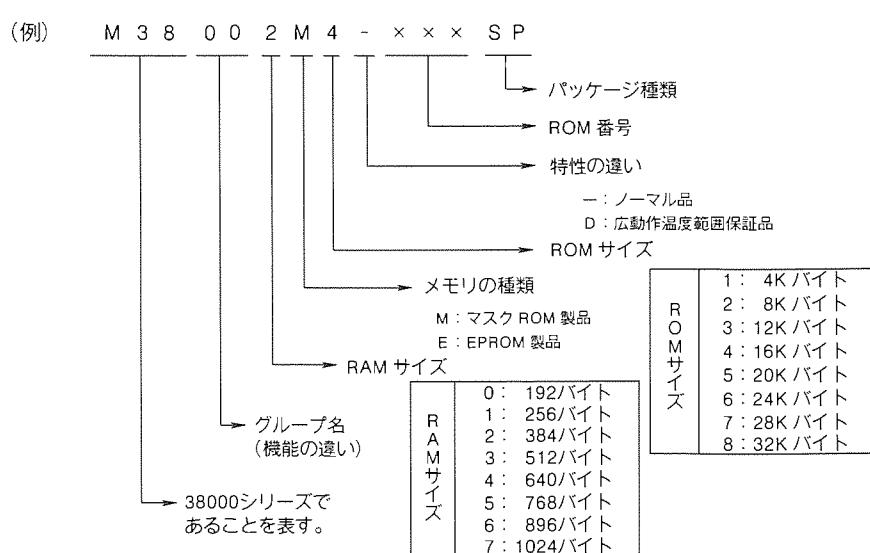

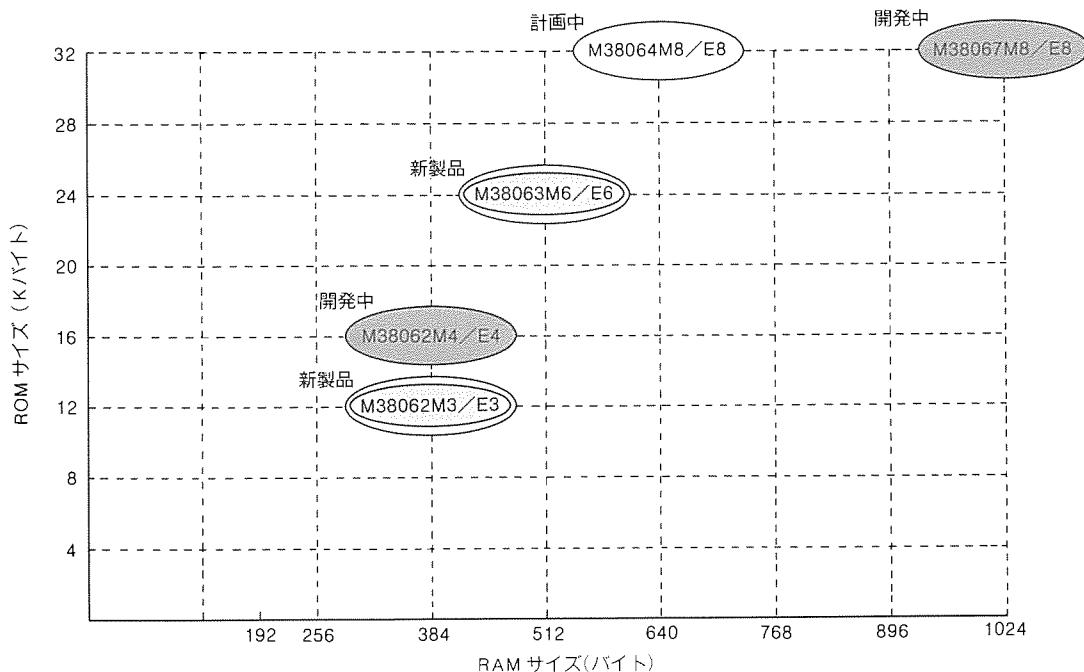

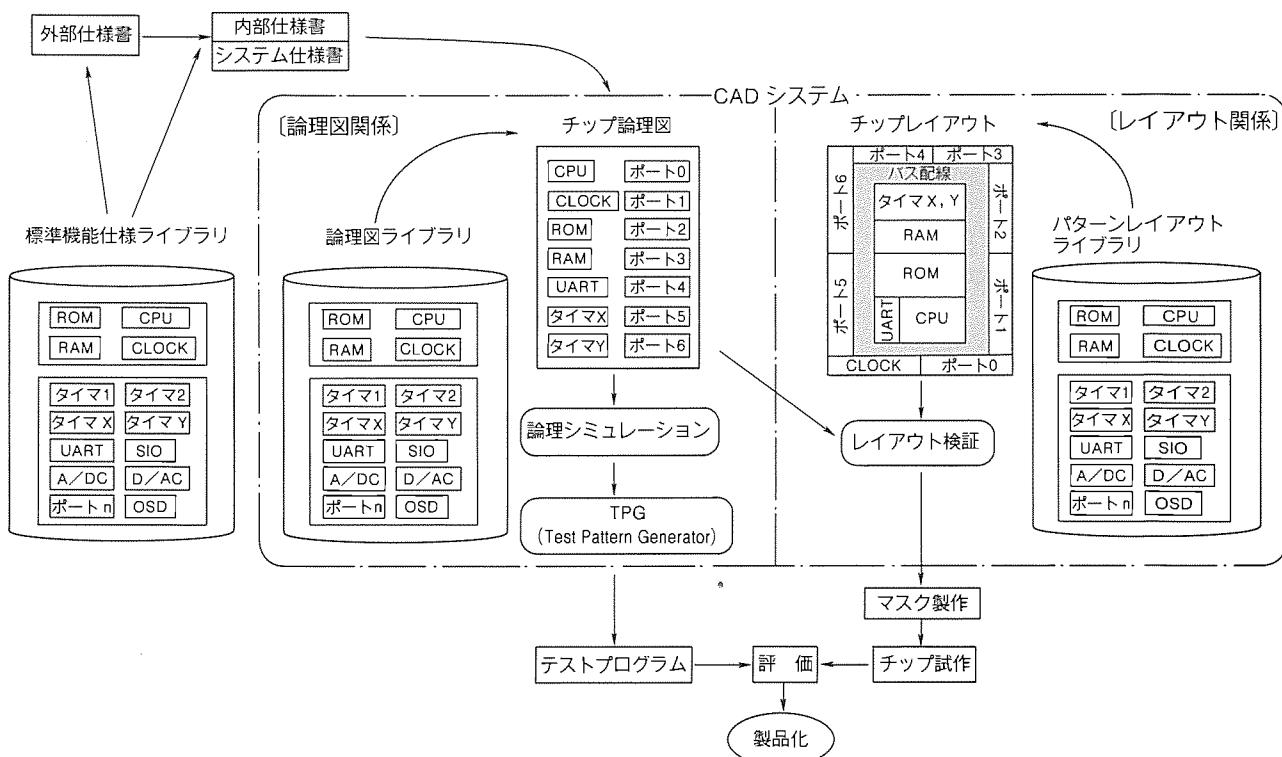

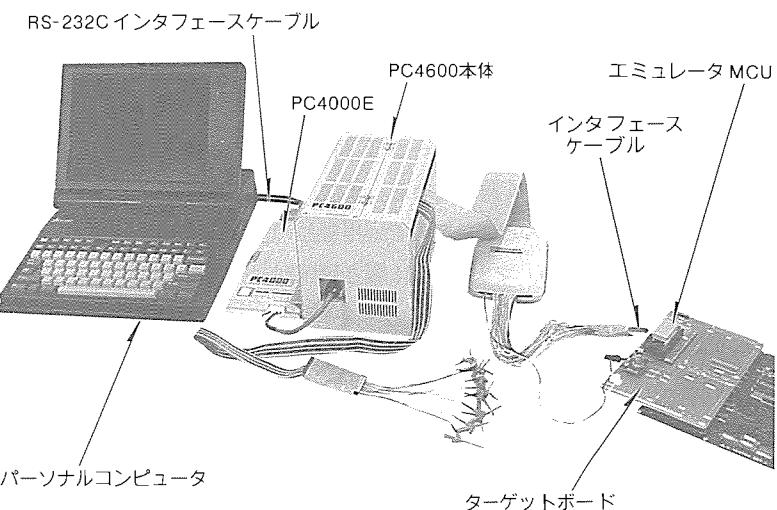

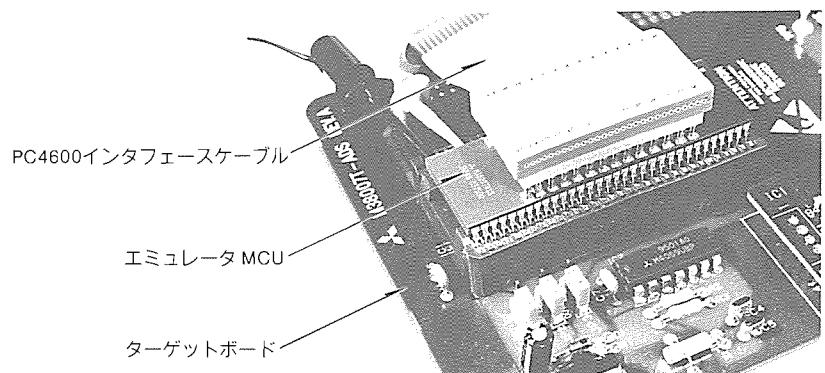

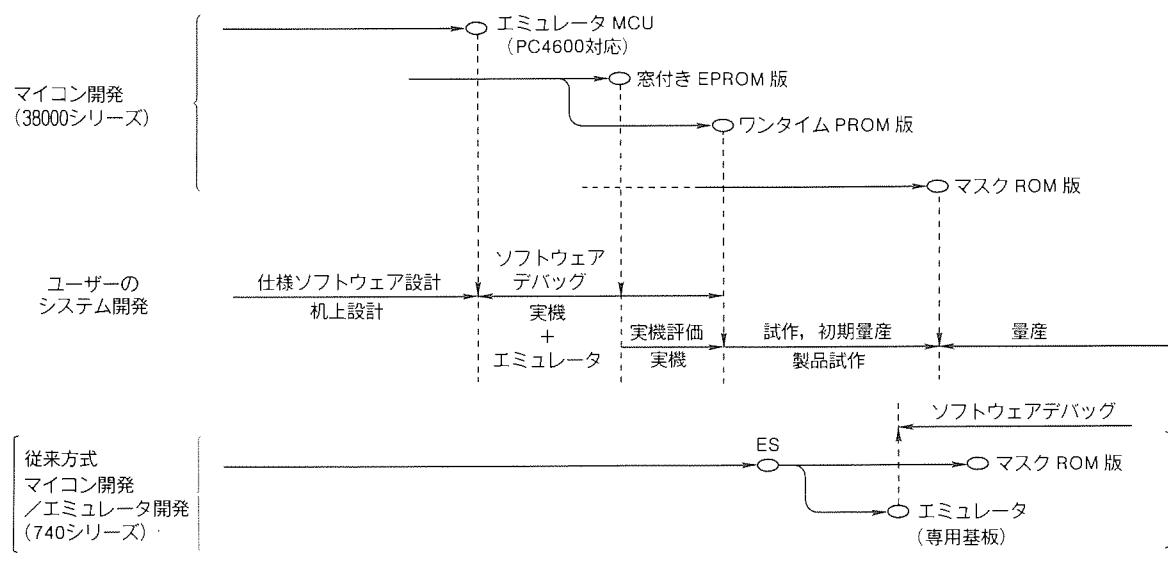

| <p><b>高速高密度メモリモジュール シリーズ</b><br/>田原次夫・福元孝和・宮武秀司<br/>三菱電機技報 Vol. 66・No. 2・P 55~60</p> <p>メモリ LSI の表面実装パッケージを搭載したメモリモジュールは各種のメリットのため、急速に用途と需要が拡大するとともに、多様で多品種な製品へと展開している。当社のメモリモジュールの製品コンセプト、新開発のメモリモジュールを紹介し、高性能化設計を目的とした CAD による伝送線路シミュレーションの具体例を紹介する。</p>                                                                         | <p><b>8ビット マイクロコンピュータ “38000シリーズ”</b><br/>竹内 稔・阿部 稔・林 良紀・石丸善行・武部秀治<br/>三菱電機技報 Vol. 66・No. 2・P 91~98</p> <p>8ビットマイコン MELPS 740の最上位の38000シリーズを開発した。740シリーズの後継に位置付けられ、幅広い機能別ラインアップと豊富なメモリサイズバリエーションを特長とする。開発に当たって開発効率の向上を徹底追求し、設計環境の完全EWS化、標準化設計手法の導入、標準機能ブロックライブラリの構築を行った。さらに、マスクROM版とEPROM版の同時設計技術を開発した。また、高機能な新エミュレータ PC4600を開発した。</p>                                                                                       |

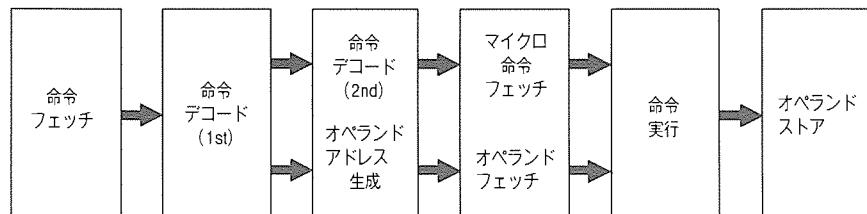

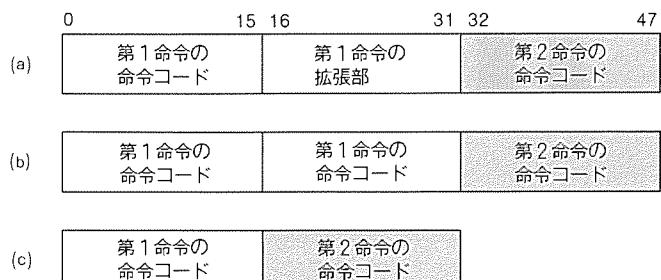

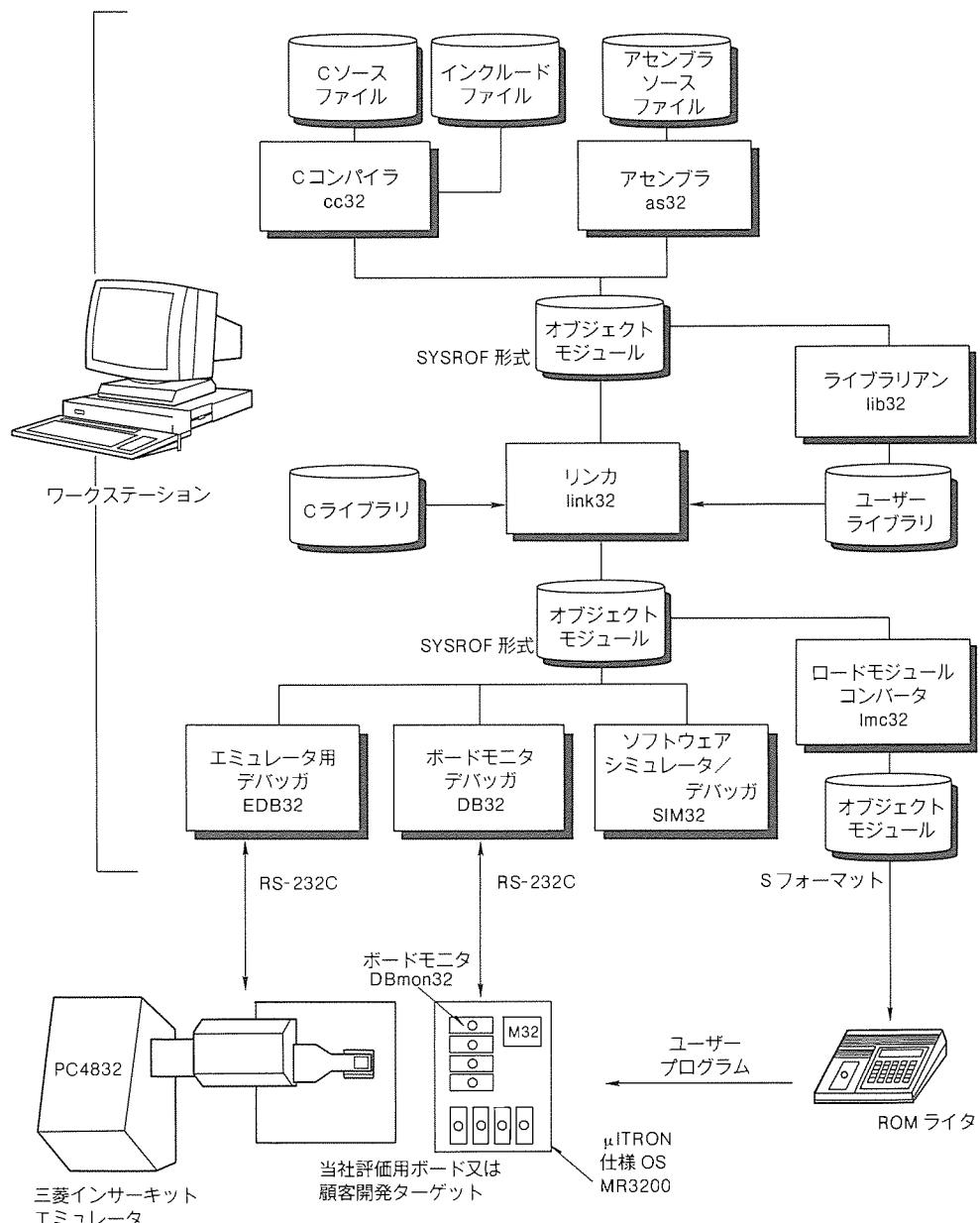

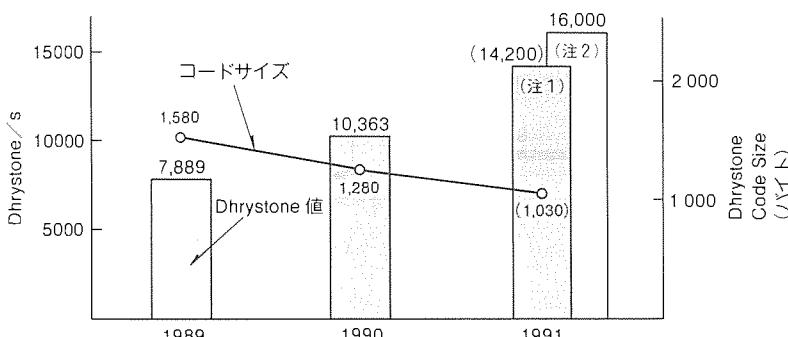

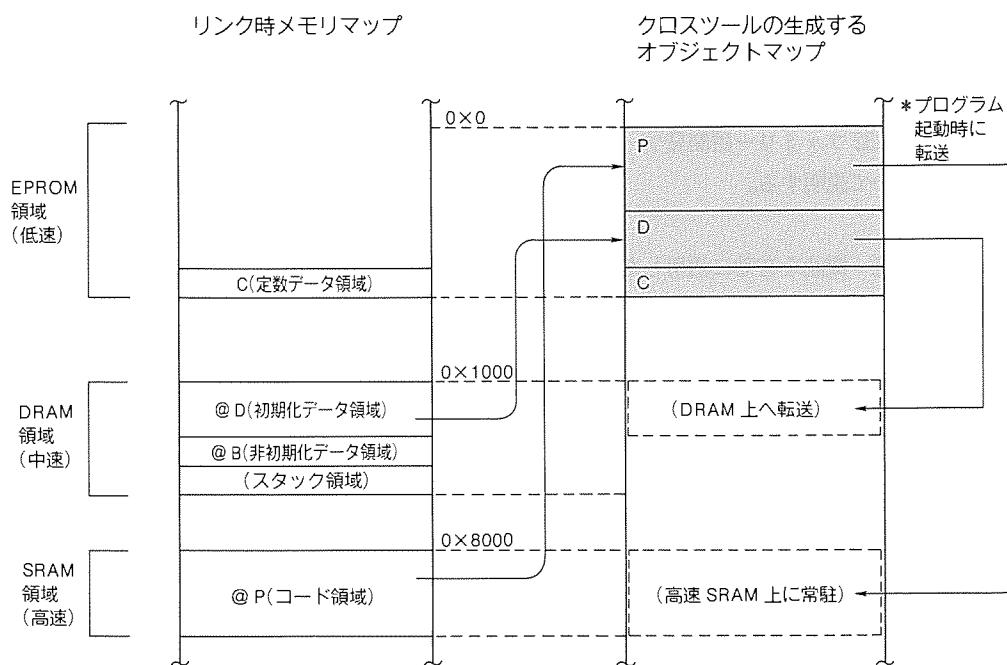

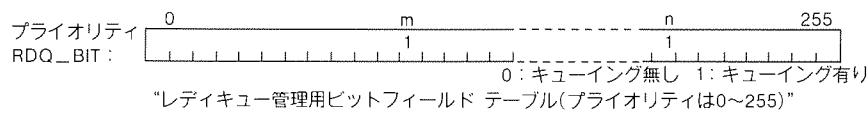

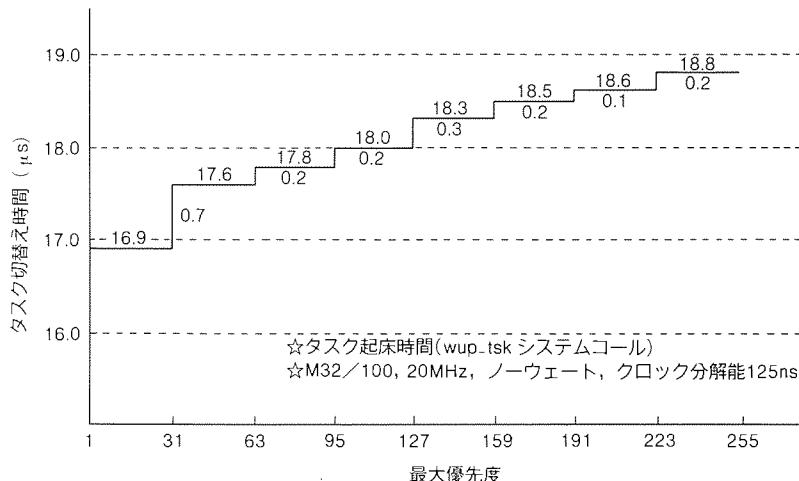

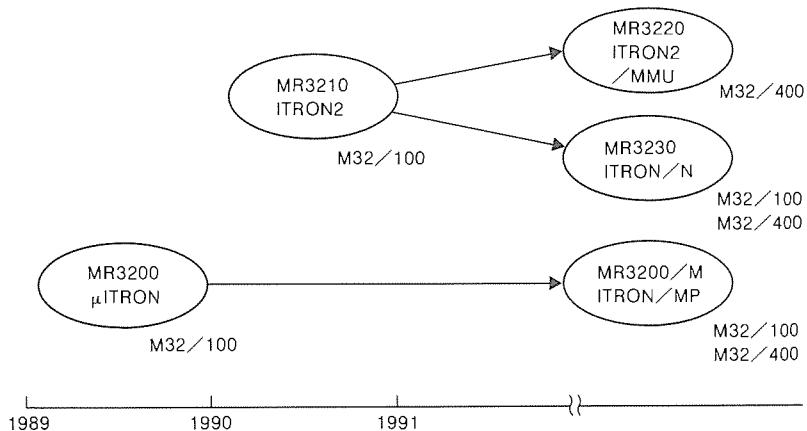

| <p><b>GMICRO M32ファミリー及びソフトウェア</b><br/>小山和美・日向純一・坂本直史・有園武志・亀井達也<br/>三菱電機技報 Vol. 66・No. 2・P 61~69</p> <p>トロン仕様準拠32ビットマイクロプロセッサ M32ファミリー及び開発ツールやリアルタイムOSを開発・製品化した。M32／100は5段のパイプラインや先行ジャンプ機構の採用やCコンパイラの改善により、8MIPS(20MHz動作時)を実現した。本稿では、M32ファミリーの特長と開発ツール体系などのソフトウェアについて紹介するとともに、上位マイクロプロセッサ及びリアルタイムOSの展開について報告する。</p>                 | <p><b>ワンチップ マイクロコンピュータの応用技術とソフトウェア</b><br/>山田国裕・川原林 隆・松井秀夫・藤沢行雄・浅野真弘・玉木浩子<br/>三菱電機技報 Vol. 66・No. 2・P 99~105</p> <p>ワンチップマイコンの応用製品は多くの分野にわたり、その機能向上は仕様の変更や機能の拡大に柔軟に対処できる利点から、ソフトウェアで実現される。小型化や原価低減のために専用周辺回路を含めた統合化されたワンチップマイコンが開発される。また、このようなソフトウェアは複雑化しており、これを開発するためにワンチップマイコン用に特化した構造化アセンブリ、簡易リアルタイムモニタを開発した。</p>                                                                                                          |

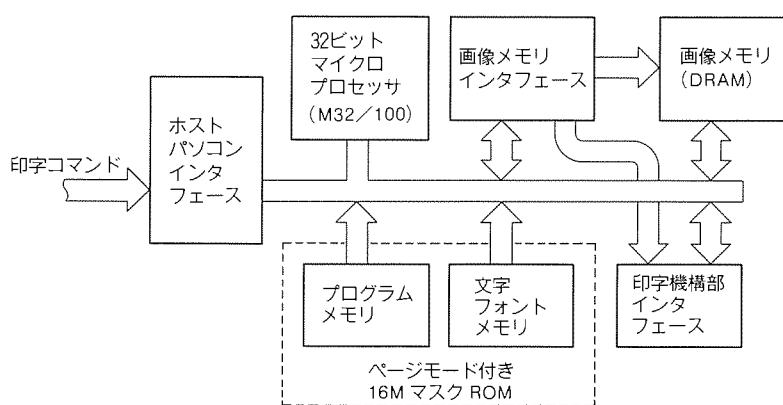

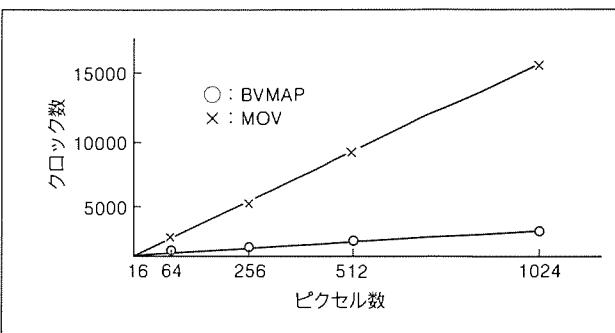

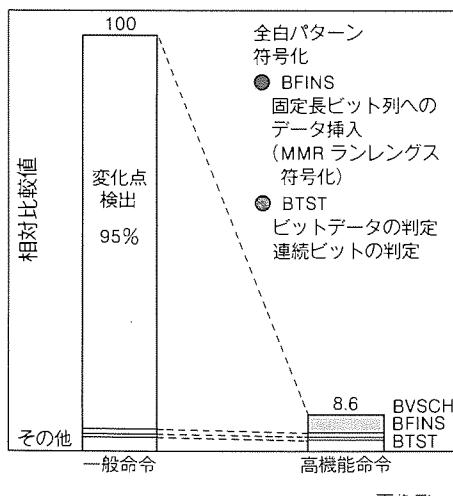

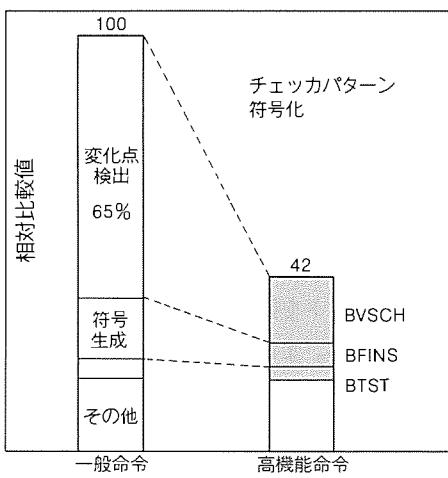

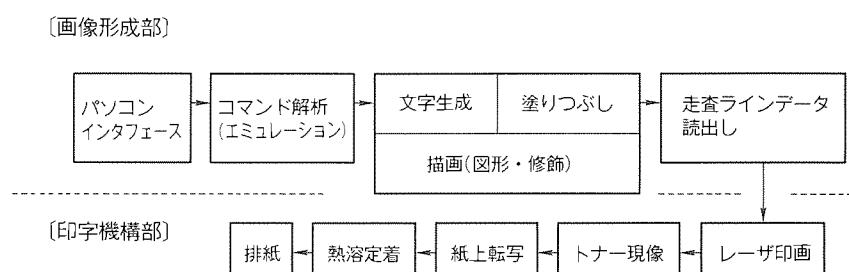

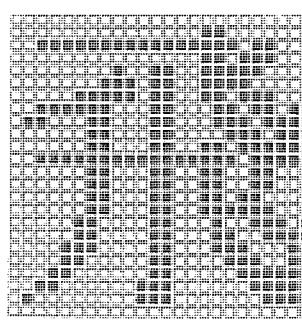

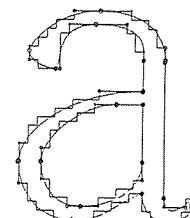

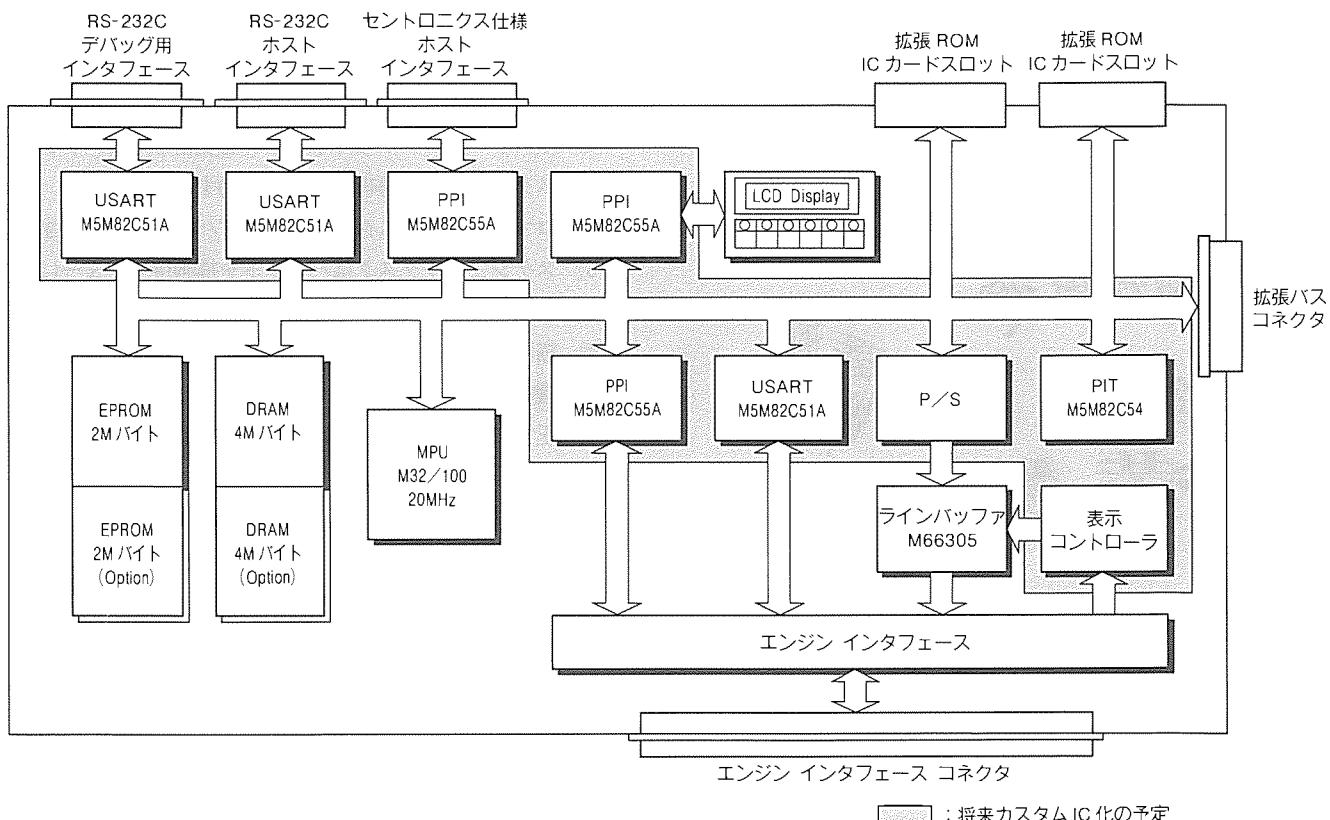

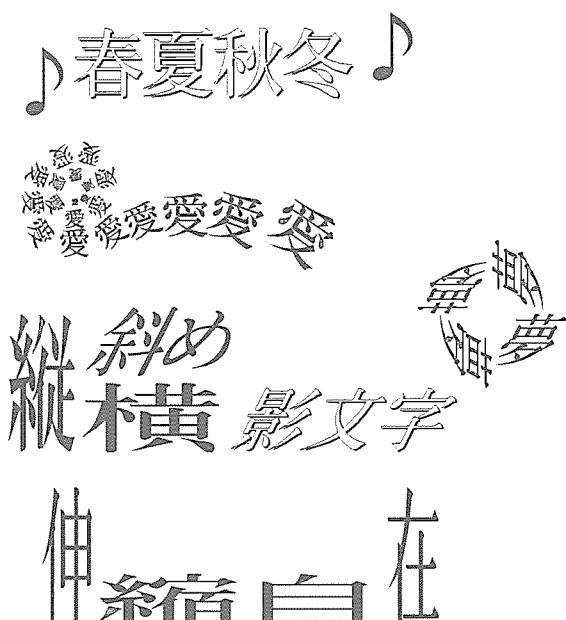

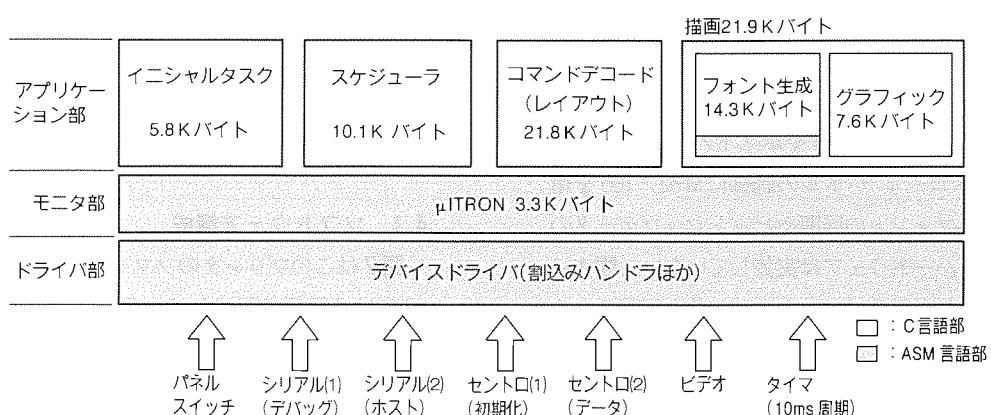

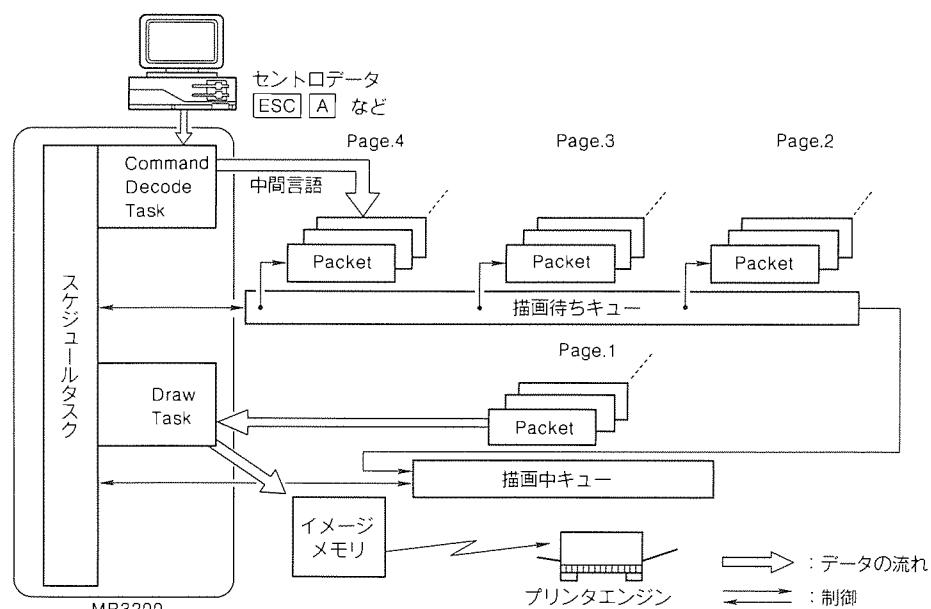

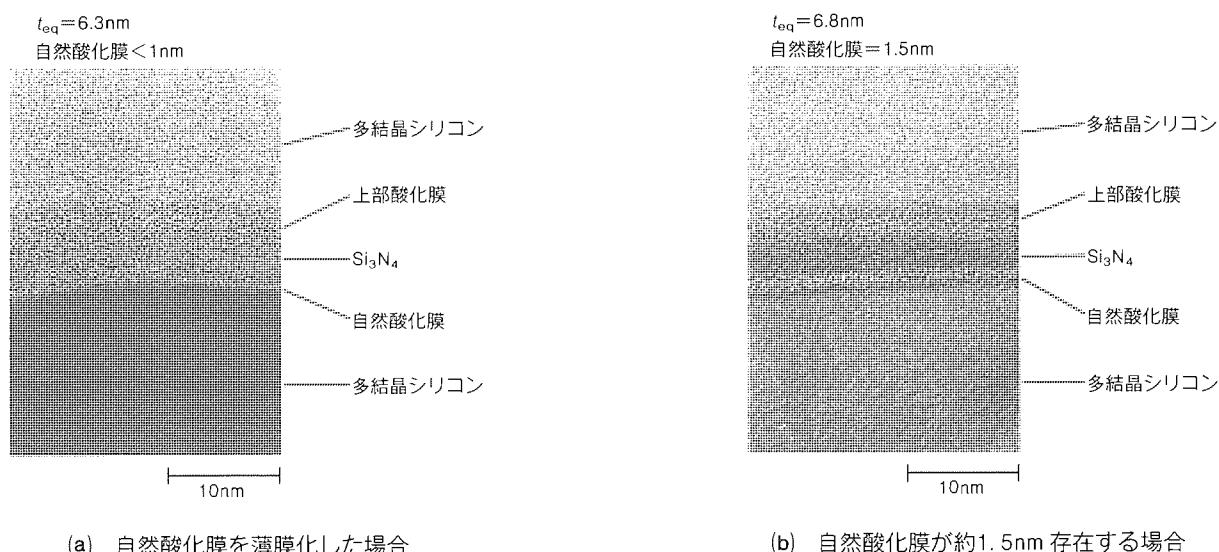

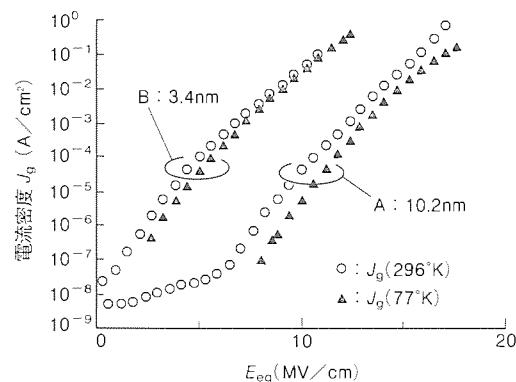

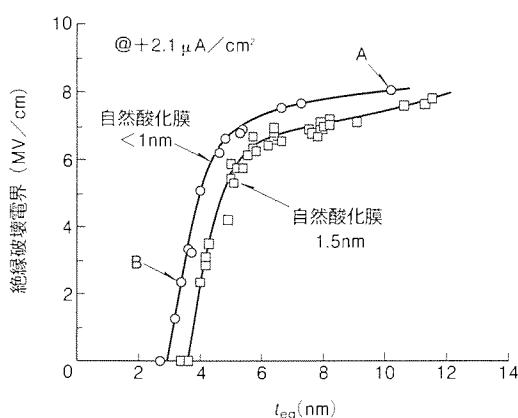

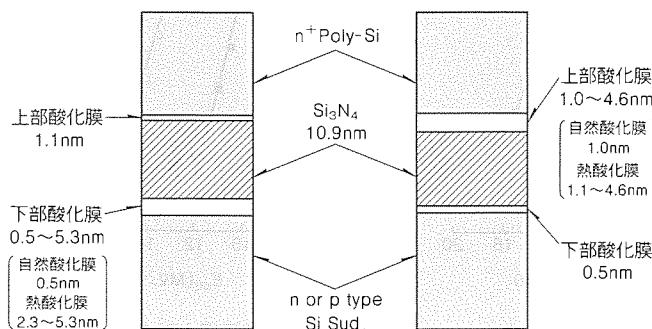

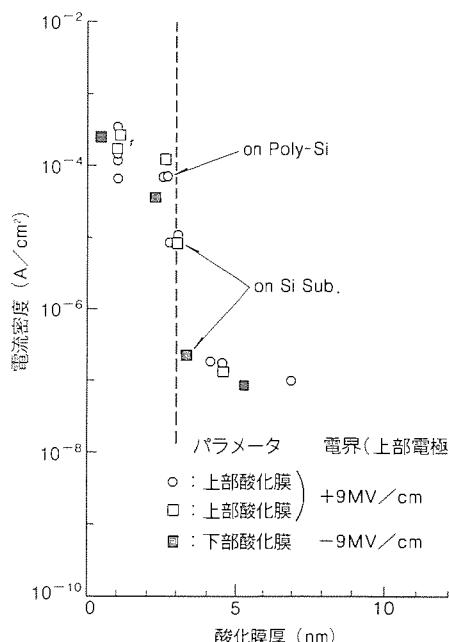

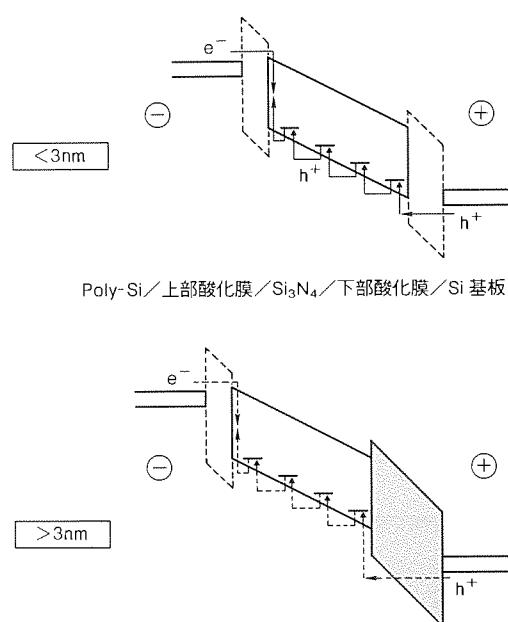

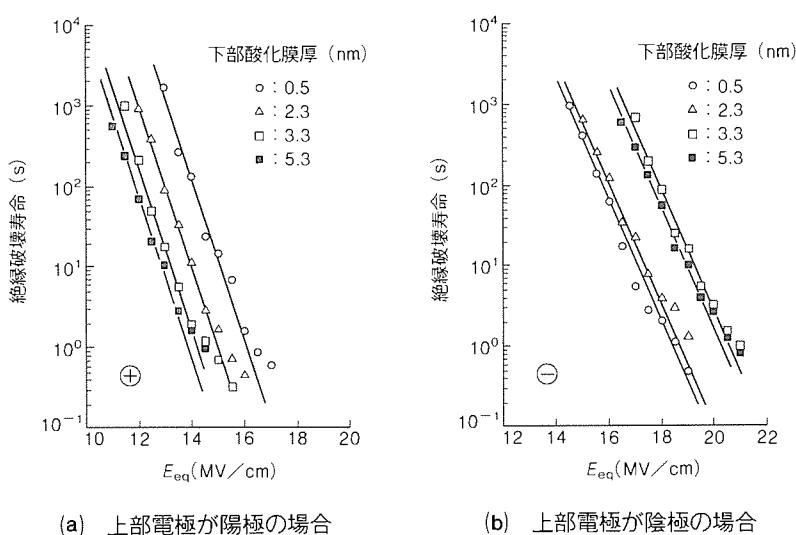

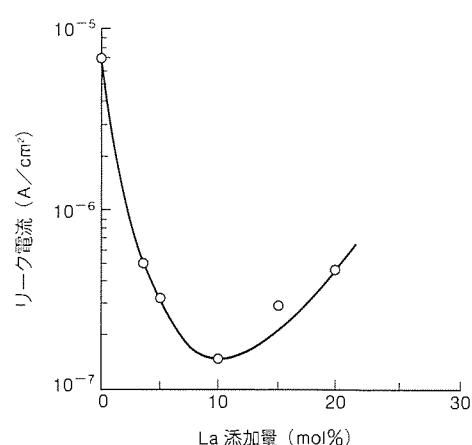

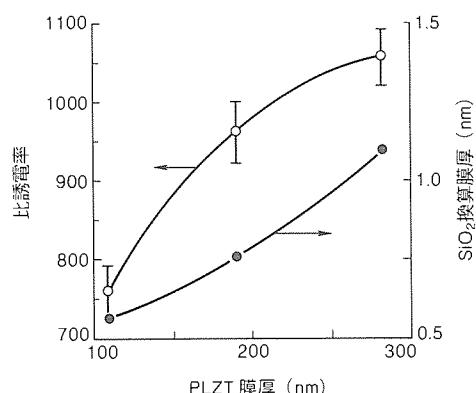

| <p><b>GMICRO M32／100のページプリンタへの応用</b><br/>山内直樹・大橋伸一郎・中嶋純子・的場成浩・松山景洋<br/>三菱電機技報 Vol. 66・No. 2・P 70~74</p> <p>パソコンの周辺機器として普及してきているページプリンタにおいて、印字品質の向上や文字生成速度の向上が求められている。一方でセットの小型化や性能対価格比の改善が必要となっている。今回、GMICRO M32／100マイクロプロセッサの特長である専用命令を活用し、また高速演算ソフトウェアパッケージの開発も行って、ページプリンタへの応用を実現し得る試作プリンタを開発した。</p>                             | <p><b>超高集積 DRAM 用キャバシタ誘電体膜形成技術</b><br/>小林清輝・中野 豊・福本晃二・林出吉生・奥平智仁<br/>三菱電機技報 Vol. 66・No. 2・P 106~110</p> <p>DRAM キャバシタへの応用に関する誘電体膜と電極の形成技術についての動向を述べた。現在実用化されている SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub>積層膜の薄膜化に対しては、自然酸化膜を薄膜化した SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub>積層構造を用いることが重要である。キャバシタ表面積拡大の手法として粗面化電極形成技術が有効である。次世代の DRAM 用の高誘電率キャバシタ材料として、強誘電体薄膜は SiO<sub>2</sub>に比べて 2~3 けた高い誘電率を持ち、大きな可能性を持っていることを示した。</p> |

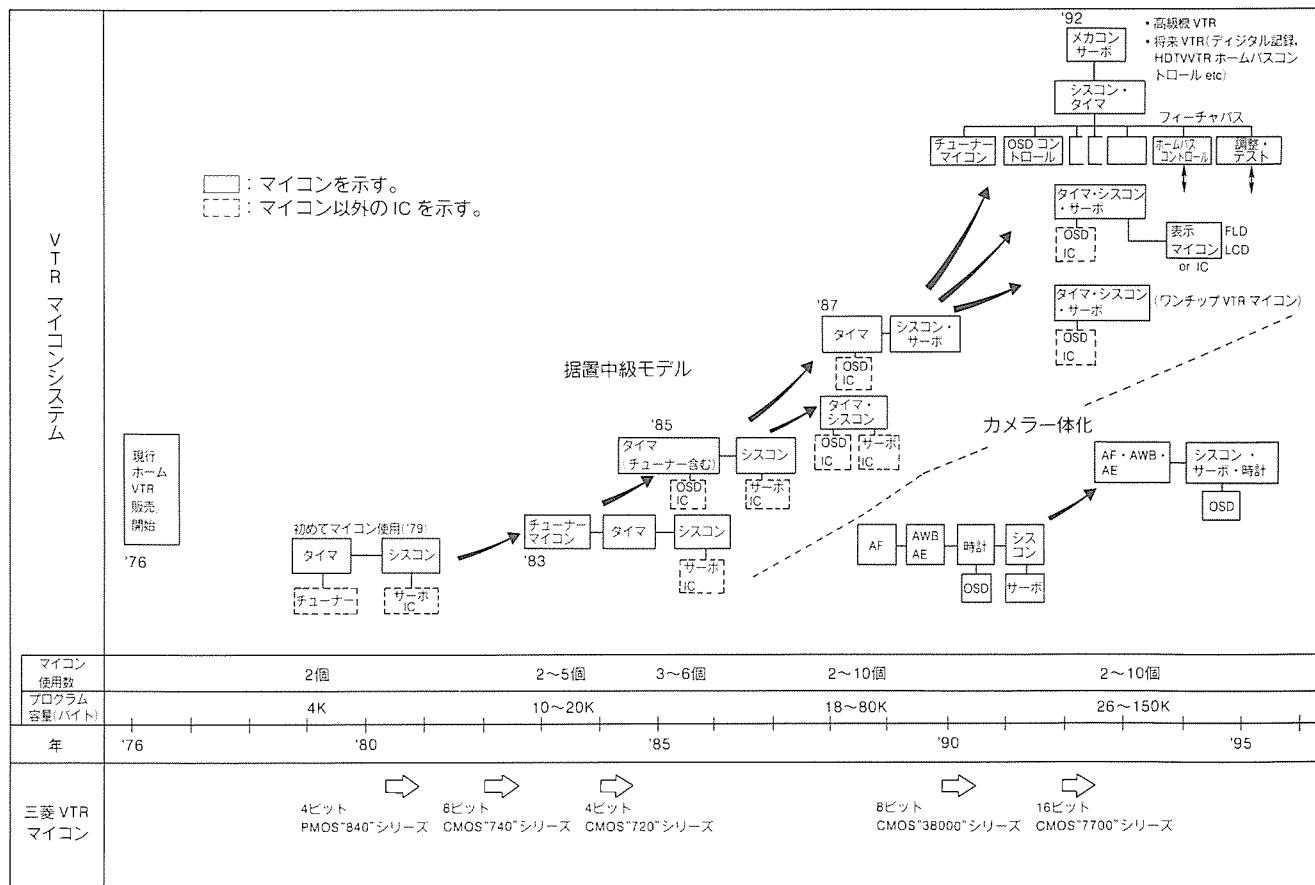

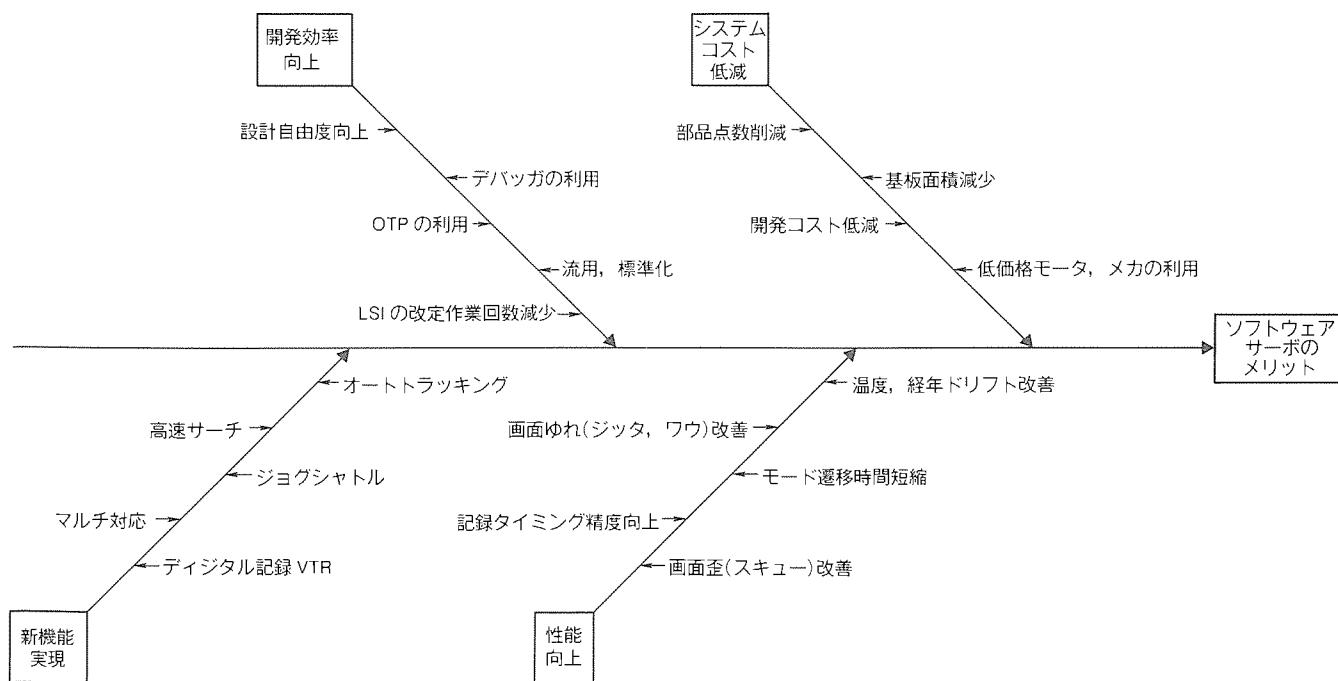

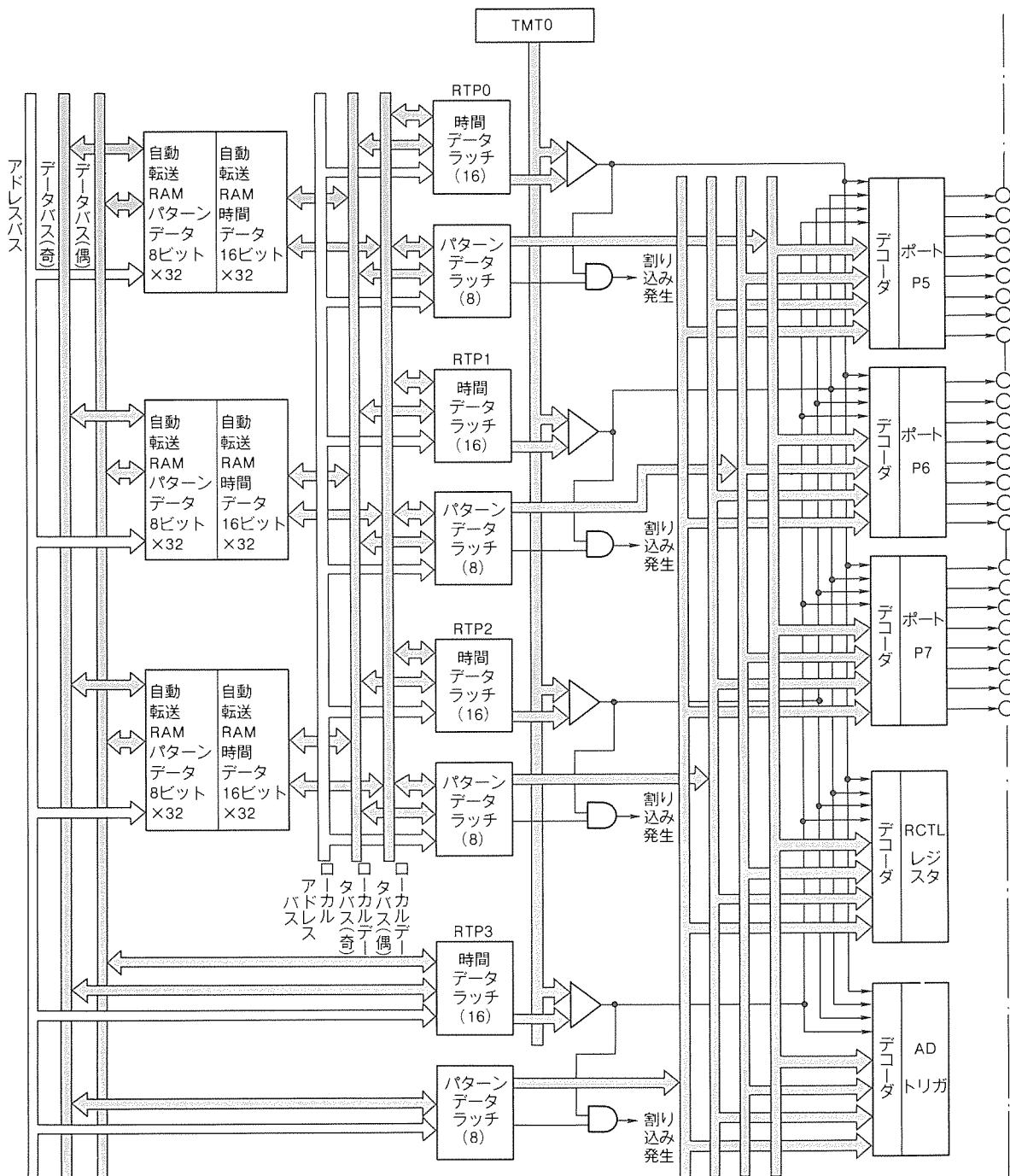

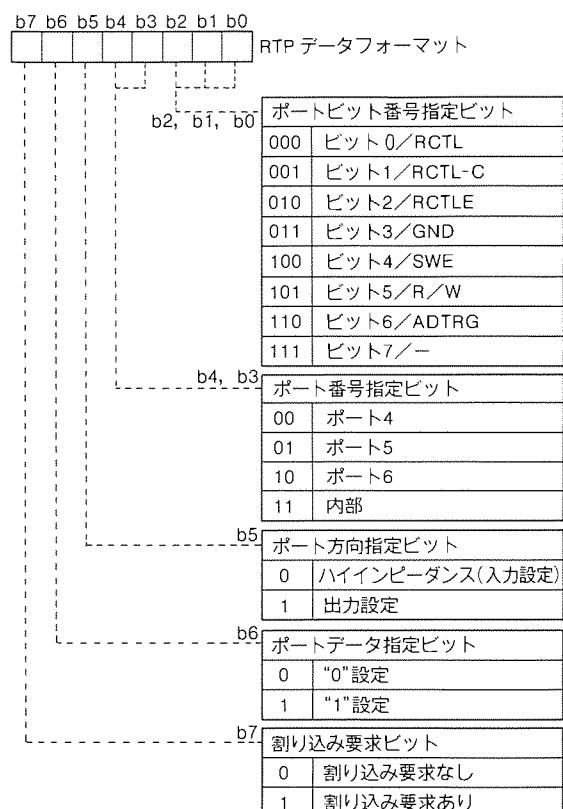

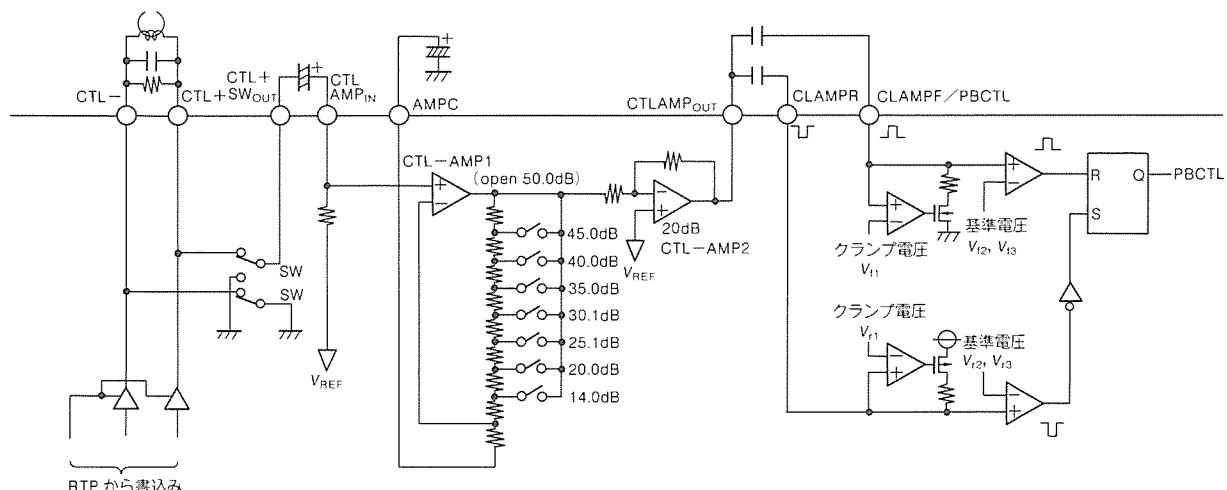

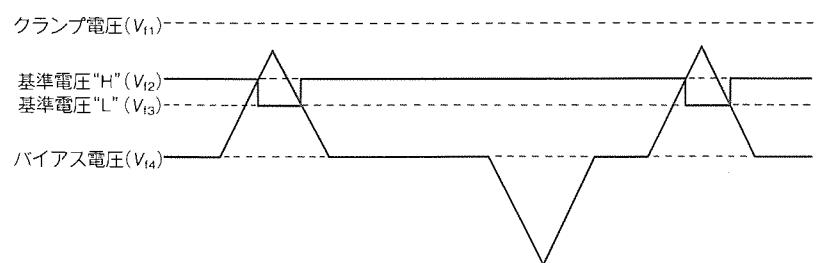

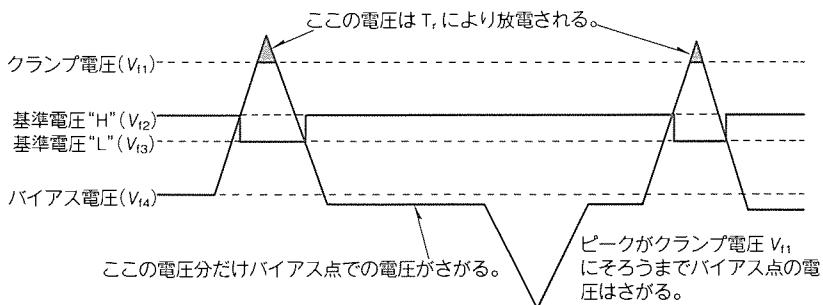

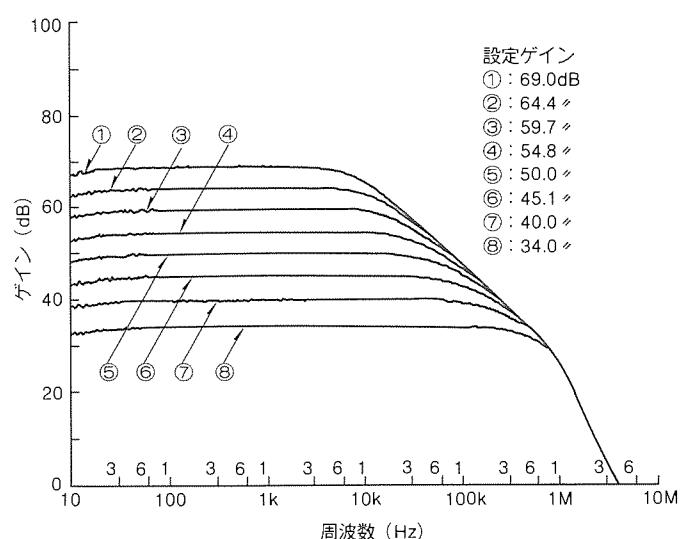

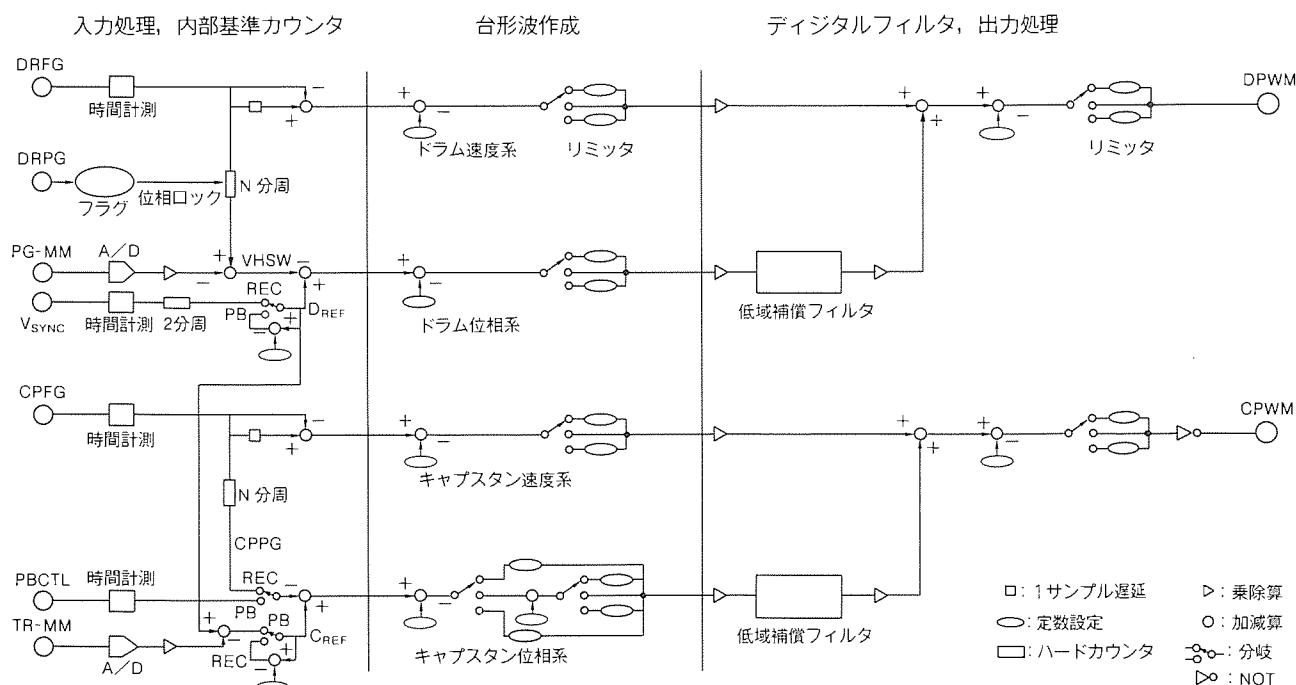

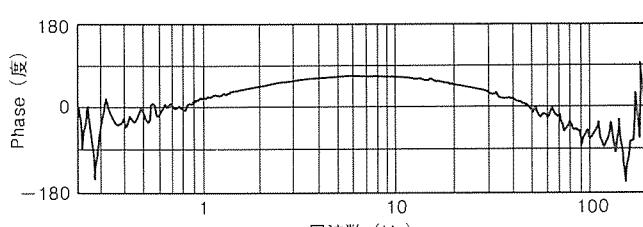

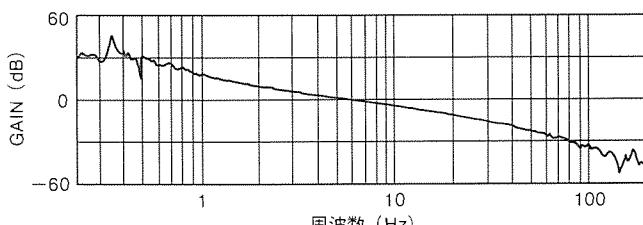

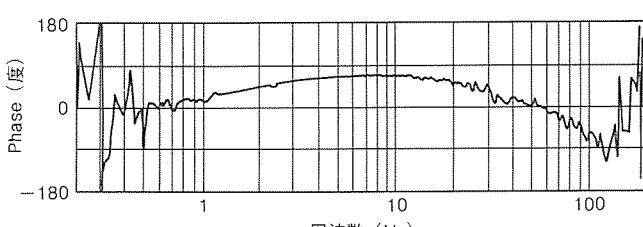

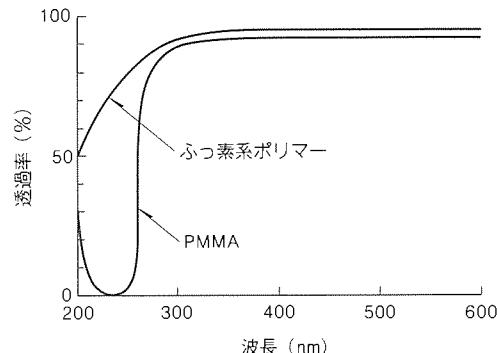

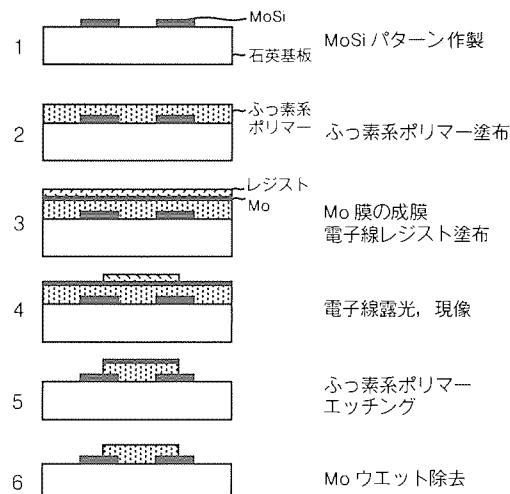

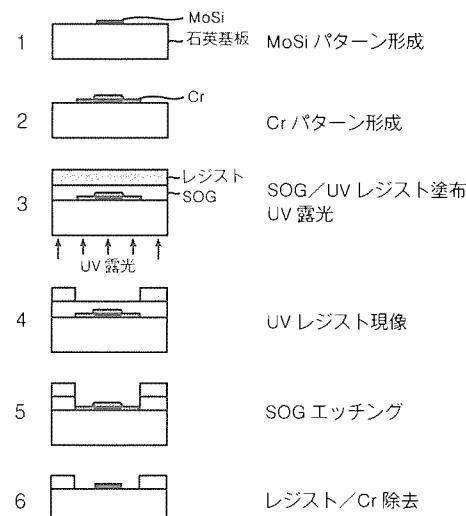

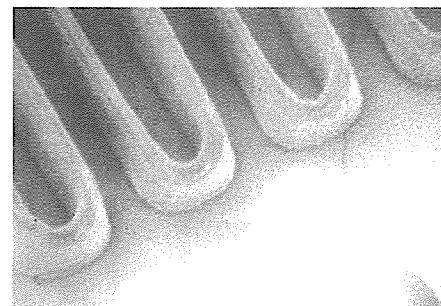

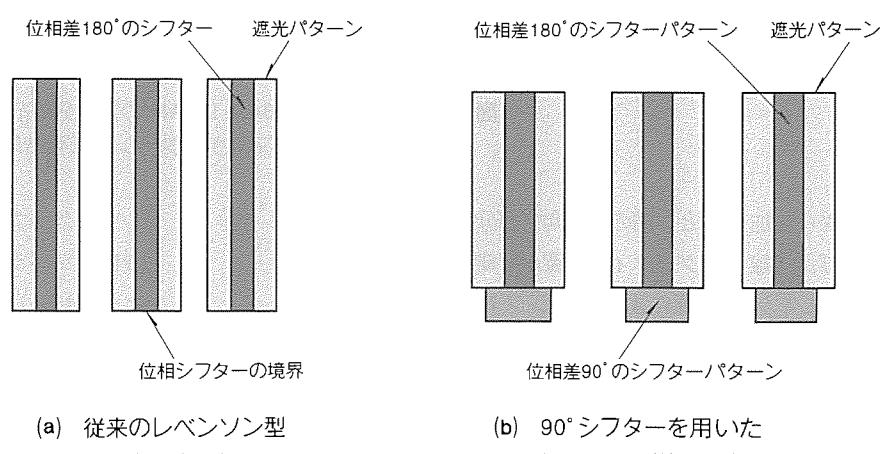

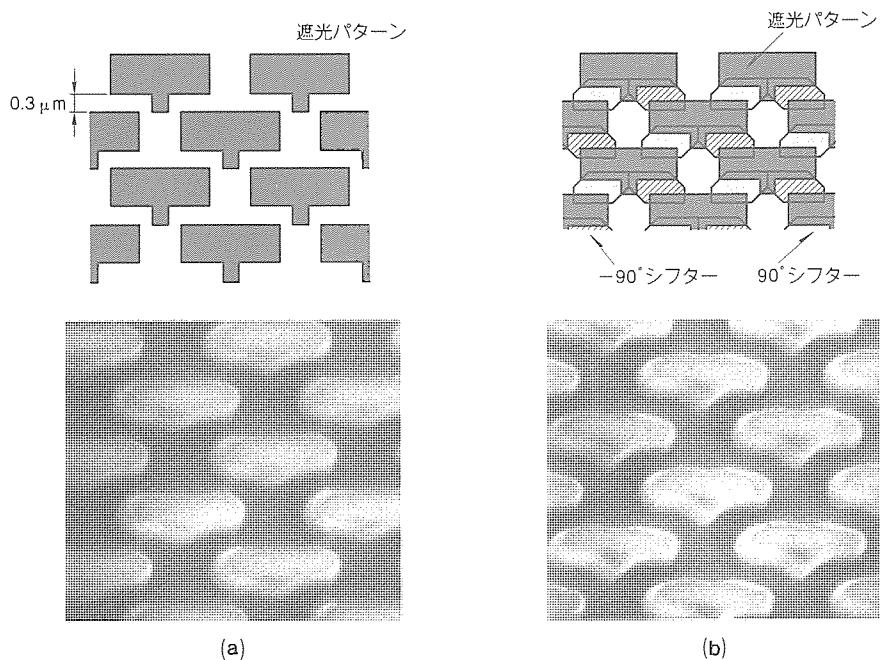

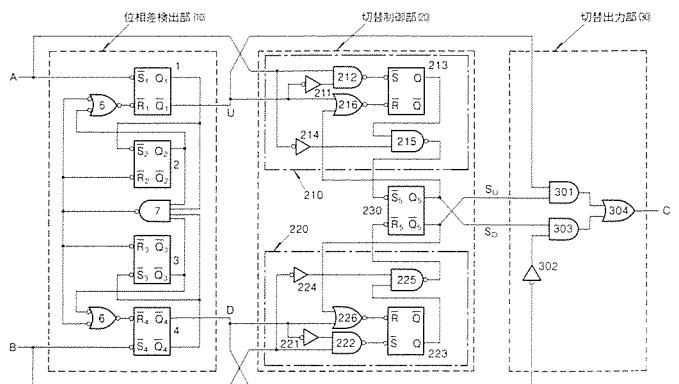

| <p><b>VTRソフトウェアサーボ用16ビットマイクロコンピュータ</b><br/>林 和夫・尚永幸久・武部秀治・山田国裕・元吉啓登・鈴木次男<br/>三菱電機技報 Vol. 66・No. 2・P 75~83</p> <p>VTR用ソフトウェアサーボマイコンとしては初めて16ビットCPUを搭載したM37770M4AXX×HPを開発した。VTRマイコンシステムにおけるマイコン統合化、ソフトウェアサーボ化の流れの中で、ソフトウェア負荷、システムコストアップの2点が大きな課題であった。このマイコンでは、CPUの16ビット化、周辺CTLアンプの内蔵、ソフトウェア開発手法の確立によって上記課題を解決し“統合化サーボマイコン”を実現した。</p> | <p><b>位相シフトリソグラフィ技術</b><br/>吉岡信行・宮崎順二・楠瀬治彦・青山 哲・Maaiice Op de Beeck<br/>三菱電機技報 Vol. 66・No. 2・P 111~115</p> <p>光の位相を制御するシフターパターンを設けたフォトマスクを用いる位相シフト露光法は、フォトリソグラフィの解像力を向上させ64M、256M DRAM の製造技術として期待されている。この論文は、当社で進めているふっ素系ポリマー及び SiO<sub>2</sub>膜をシフター材料に用いる位相シフトマスクの開発、ポジレジストに対応した i 線位相シフト露光法の開発、KrF エキシマ光源に対応した位相シフト露光法の開発について紹介する。</p>                                                                                    |

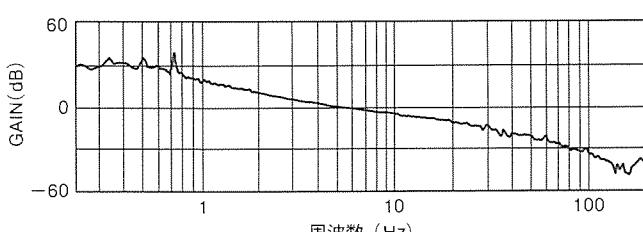

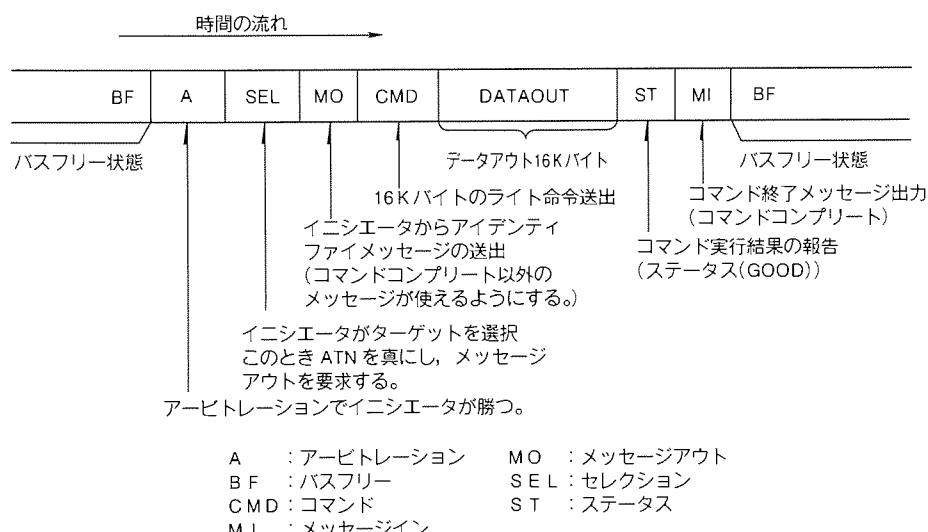

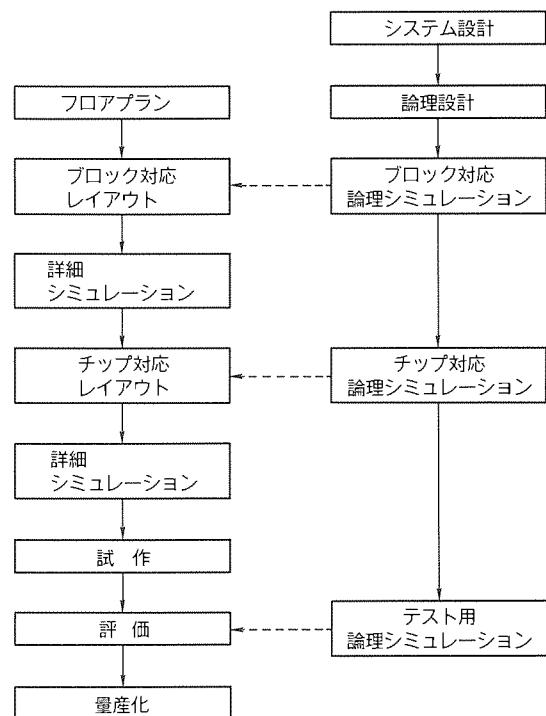

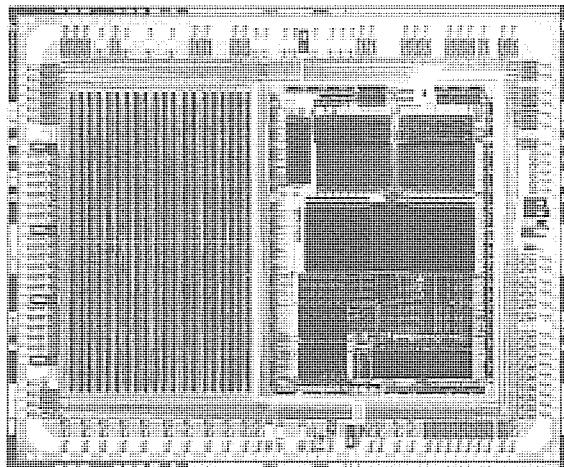

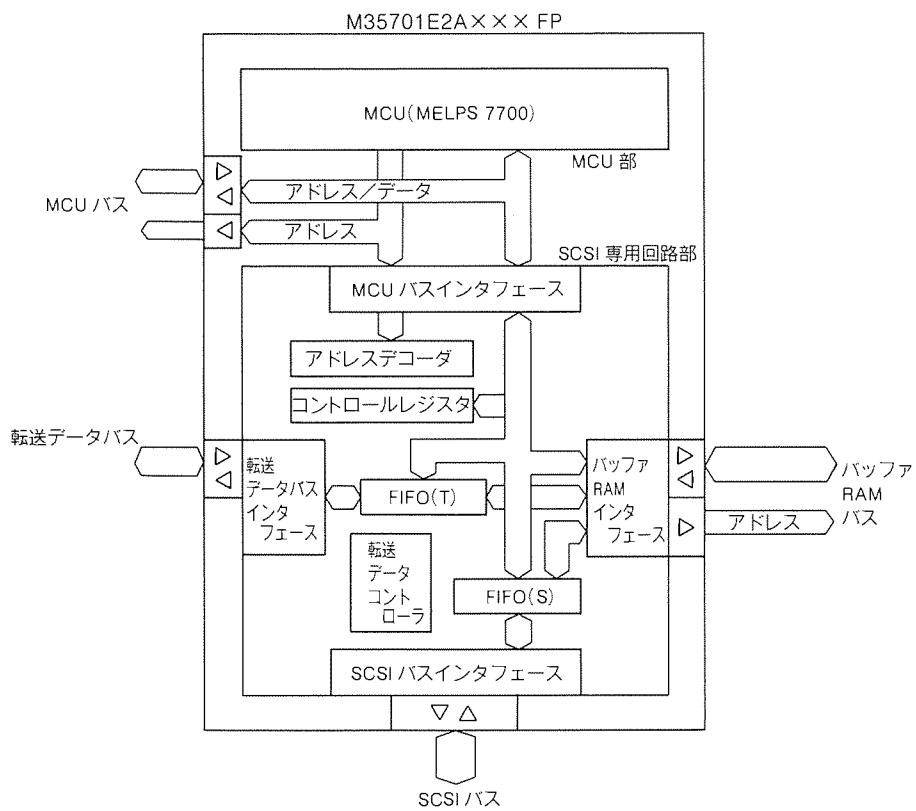

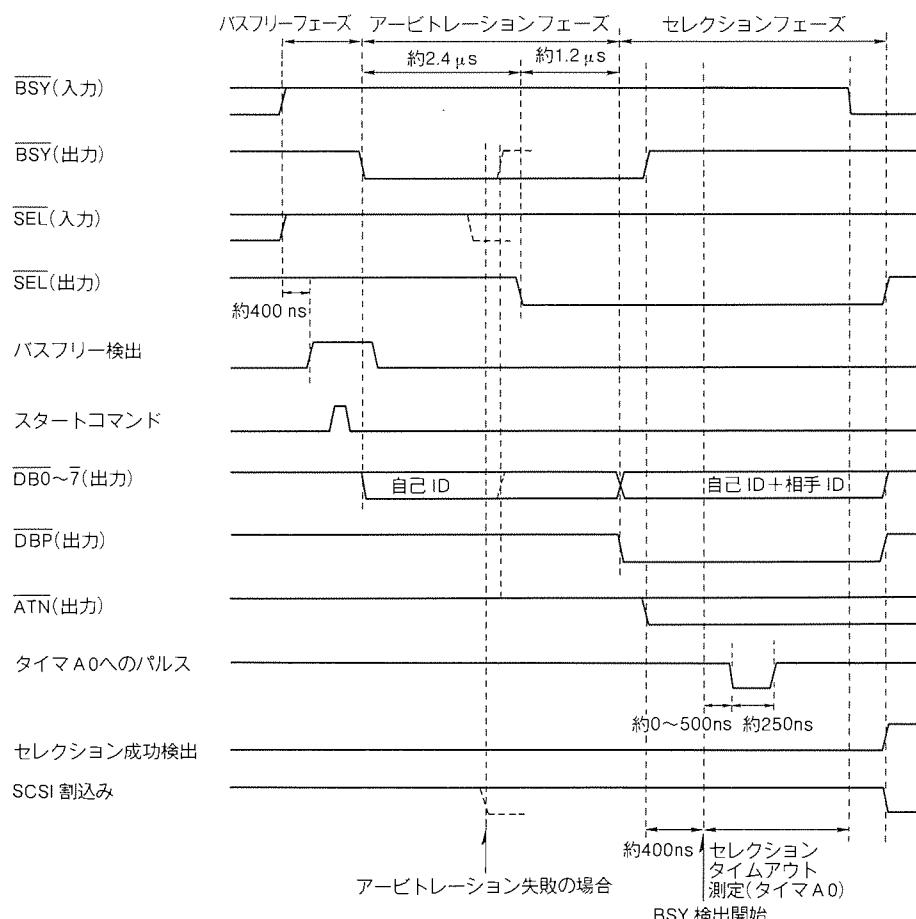

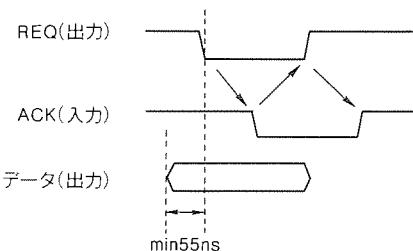

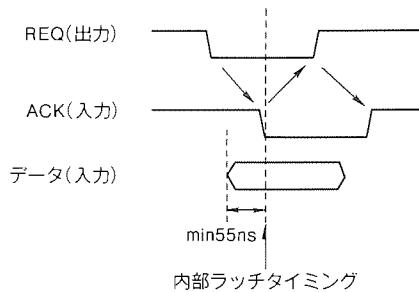

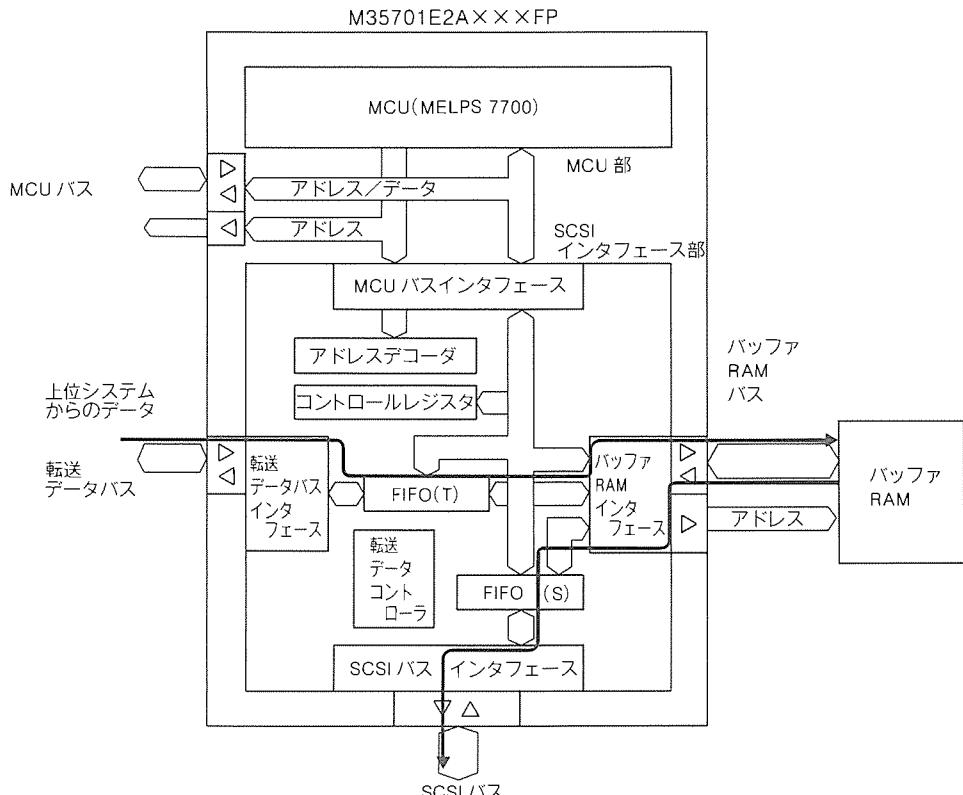

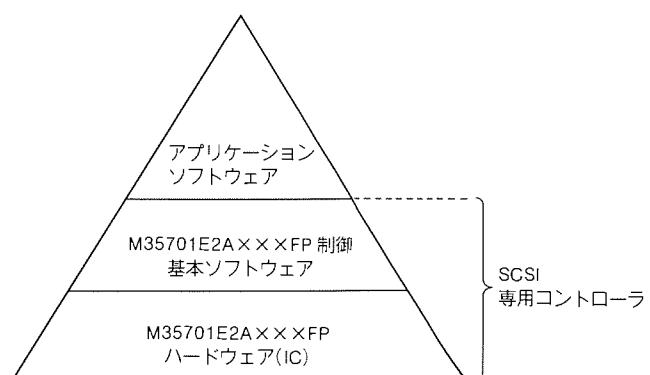

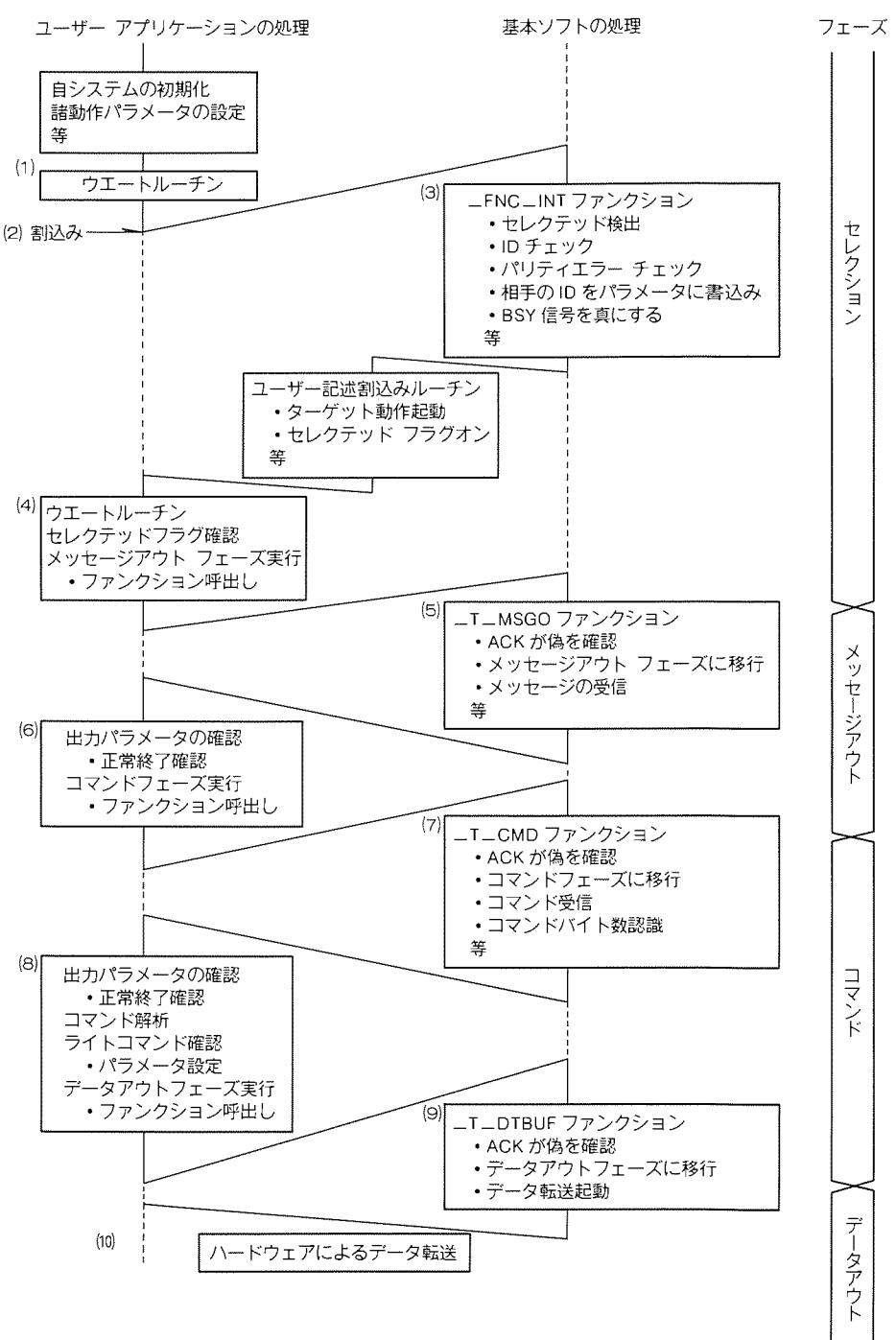

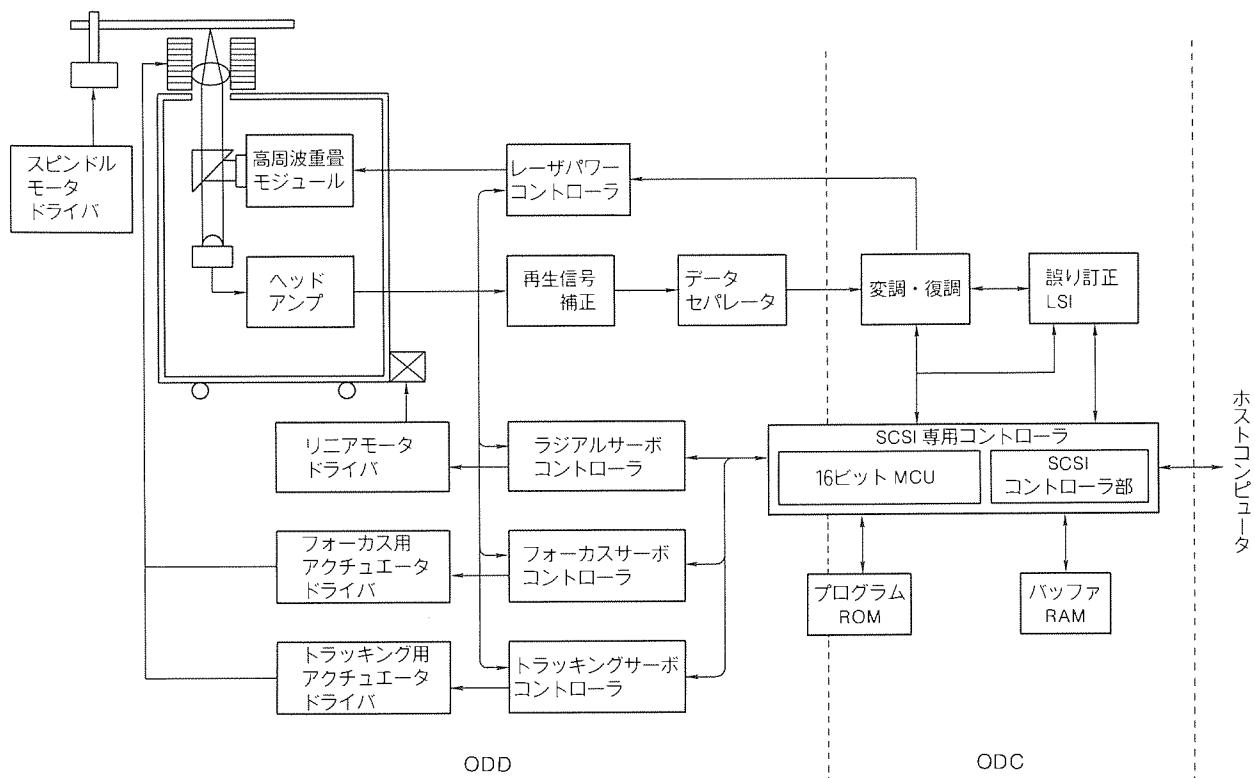

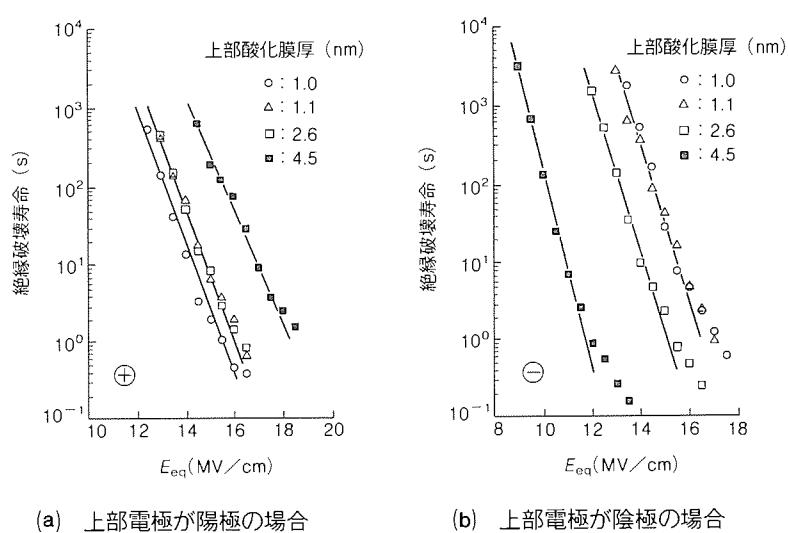

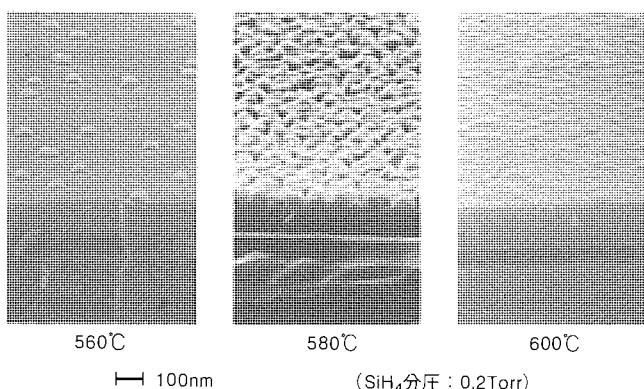

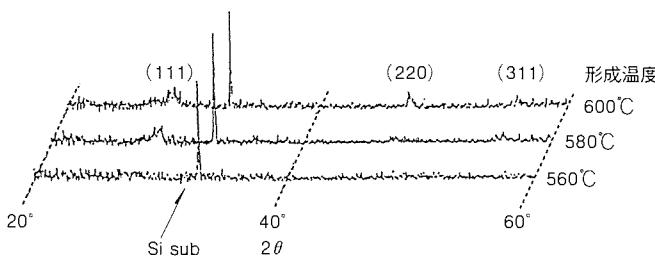

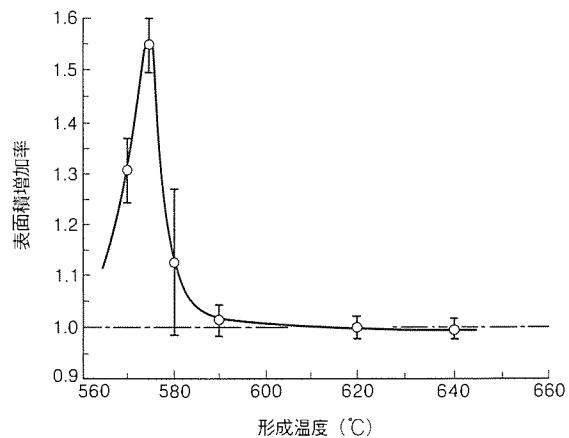

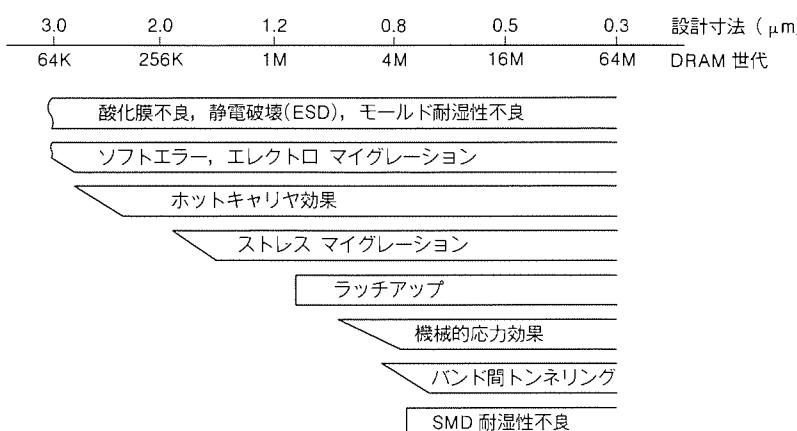

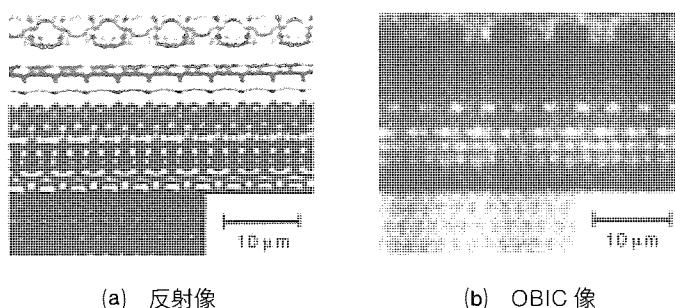

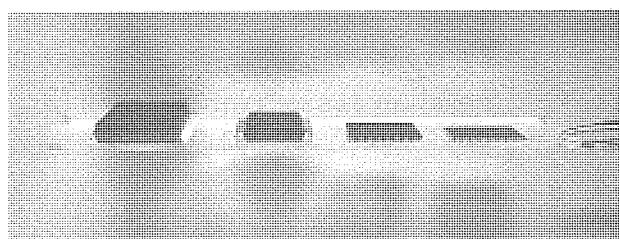

| <p><b>SCSI専用コントローラ</b><br/>堀 俊彦・須田眞二・小林 洋・遠藤茂行・川嶋健司<br/>三菱電機技報 Vol. 66・No. 2・P 84~90</p> <p>パソコンコンピュータ等と入出力機器との標準インターフェースの一つである SCSI (Small Computer System Interface) を持つ SCSI 専用コントローラを16ビットMCU、MELPS 7700シリーズの一貫として開発した。プロトコル処理等条件判断を必要とするところは MCU 部が行い、高速処理を必要とする箇所を専用回路部が行うことで SCSI 機能を実現することにより、高性能で柔軟性のあるシステム構築が可能となった。</p> | <p><b>先端デバイス開発における信頼性評価解析技術</b><br/>三橋順一・小守純子・石井達也<br/>三菱電機技報 Vol. 66・No. 2・P 116~120</p> <p>LSIデバイス開発において、信頼性を製品に作り込むいわゆる Building-in Reliability の重要度は微細化・高集積化が進むにつれて高まっている。ウェーハレベル TEG 評価技術を駆使し、設計及び要素プロセスの信頼性を高精度かつ短期間に評価し、データをフィードバックする。一方、複雑化するデバイスに対応して、故障解析技術の高度化も不可欠であり、FIB 解析及び発光解析や OBCC 解析による故障箇所の同定技術等を開発実用化している。</p>                                                                                           |

# Abstracts

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 91~98 (1992)

## 38000 Series Single-Chip 8-bit Microcomputers

by Minoru Takeuchi, Minoru Abe, Yoshinori Hayashi, Yoshiyuki Ishimaru & Shuji Takebe

The corporation has developed a new 8-bit microcontroller as a successor to the MELPS 740 8-bit microcontroller family. The 38000 Series offers a wide variety of function and memory-size options. A workstation-based development environment with standardized design methodology and functional block libraries support a rapid MCU design. A new wafer processing technology makes it possible to implement either mask ROM or EPROM devices using the same pattern layout. A new high-performance emulator, the PC4600, has also been developed.

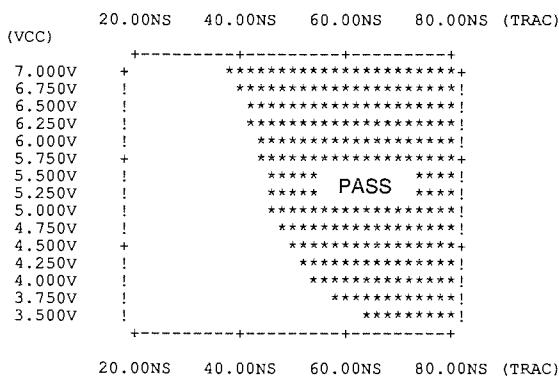

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 55~60 (1992)

## High-Speed, High-Density Memory Module Series

by Tsugio Tabaru, Takakazu Fukumoto & Hideshi Miyatake

Memory modules manufactured using surface-mounted memory devices offer superior reliability over the COB types. Applications and demand for them have increased rapidly, and many types of modules have been developed. The article introduces the concepts of Mitsubishi Electric's module product line and recent products. It also describes the use of data line CAD simulation to boost module performance.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 99~105 (1992)

## Trends in Software Technology for Single-Chip Microcomputers

by Kunihiro Yamada, Takashi Kawarabayashi, Hideo Matsui, Yukio Fujisawa, Masahiro Asano & Hiroko Tamaki

Single-chip microprocessors are being used in many fields. Many functions are generally implemented in software to facilitate upgrading and modifications. Considerations of cost and size have led to the inclusion of specialized peripheral circuits on chips, bringing about the development of integrated single-chip microcomputer products. Specially structured assemblers and simple real-time monitors have been developed to handle the more complex software development requirements of these chips.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 61~69 (1992)

## GMICRO M32-Family Microprocessors and Software

by Kazumi Koyama, Jun'ichi Hinata, Tadashi Sakamoto, Takeshi Arizono & Tatsuya Kamei

The corporation has developed commercial M32-family 32-bit microprocessors that comply with the TRON architecture, and development tools and a real-time operating system that take advantage of the microprocessors' capabilities. The M32/100 employs a five-stage pipeline, a prejump mechanism, and improved C compiler to realize 8MIPS performance at 20MHz. The article reports on the development of this high-performance microprocessor and real-time operating system, and introduces the features of the M32 family and its development tools.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 106~110 (1992)

## Advanced Technologies for the Capacitor Dielectrics of High-Density DRAM Devices

by Kiyoteru Kobayashi, Yutaka Nakano, Koji Fukumoto, Yoshio Hayashide & Tomohito Okudaira

The article reports on trends in technologies for forming the capacitor dielectric layer and electrodes for high-density DRAM memory cells. Current work on  $\text{SiO}_2\text{-Si}_3\text{N}_4$  stacked films is focused on the thinning of the native layer. The fabrication of a rough-textured polysilicon electrode improved strength and has proven to be an effective way to increase storage capacitance. Ferroelectric films have dielectric constants two to three orders of magnitude higher than  $\text{SiO}_2$ , offering substantial capacitance improvements for the next generation of DRAM devices.

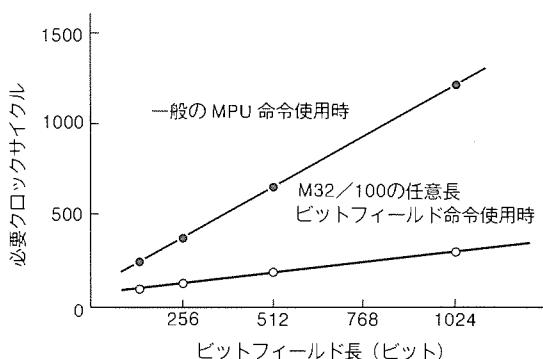

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 70~74 (1992)

## Page Printer Application of the GMICRO M32/100 Microprocessor

by Naoki Yamauchi, Shin'ichiro Ohashi, Junko Nakajima, Narihiro Matoba & Akihiro Matsuyama

Market demand for page printers with better printing quality and faster character generation is accompanied by pressures for compact dimensions and cost-effective design. The corporation has developed a prototype page printer based on the GMICRO M32/100 microprocessor and a new software package making it possible to exploit the microprocessor's variable-length bit field. The design is suitable for commercial implementation.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 111~115 (1992)

## Photolithography with a Phase-Shifting Mask

by Nobuyuki Yoshioka, Junji Miyazaki, Haruhiko Kusunose, Satoshi Aoyama & Maaika Op de Beeck

The phase-shift mask technique is an advanced lithographic technique in which the phase-shifting masks are utilized to improve the resolution and focus latitude of small resist features. It is a promising method to achieve the high resolution required to produce 64Mbit and 256Mbit DRAM devices. The article reports on the corporation's development work in this area, including phase-shift masks fabricated using fluoro-polymer and  $\text{SiO}_2$  films as shifter materials, in-line phase-shift exposure methods for positive resists, and phase-shift exposure methods with KrF excimer laser light sources.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 75~83 (1992)

## A 16-Bit Microcomputer for Software-Implemented VCR Servos

by Kazuo Hayashi, Yukihisa Naoe, Hideharu Takebe, Kunihiro Yamada, Yoshinori Motoyoshi & Tsugio Suzuki

Mitsubishi Electric has developed a VCR controller chip with a 16-bit microcomputer. The M37770M4A  $\times \times \times$  HP has sufficient processing capability to implement servo-control functions when using software and to integrate general-purpose control functions without excessive loading. A built-in peripheral control track (CTL) amplifier and software development tools help to lower development and implementation costs.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 116~120 (1992)

## Reliability Evaluation Technologies for Developing Advanced LSI Devices

by Jun'ichi Mitsuhashi, Junko Komori & Tatsuya Ishii

Reliability evaluation plays a key role in developing new LSI devices. High inherent reliability results from use of test element group (TEG) chips from the first stages of circuit development and thorough reliability evaluation during various stages of process development. Implementing such processes requires a variety of TEG patterns, high-sensitivity reliability evaluation technology, and fault analysis technology. These combined technologies allow the realization of built-in reliability in advanced LSI devices.

Mitsubishi Denki Gihō: Vol. 66, No. 2, pp. 84~90 (1992)

## An Intelligent SCSI Protocol Controller

by Toshihiko Hori, Shinji Suda, Hiroshi Kobayashi, Shigeyuki Endo & Kenji Kawashima

The corporation has developed a small computer systems interface (SCSI) controller LSIC based on the MELPS 7700 family of 16-bit microcontrollers. The microcontroller performs general protocol processing and makes control decisions while dedicated high-speed circuits implement specialized SCSI functions. This design achieves flexibility and high-performance. SCSI is one of the I/O interface standards for personal computers and workstations.

## アブストラクト

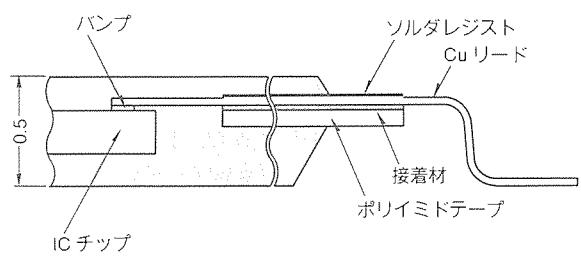

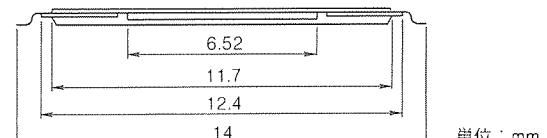

### 0.5mm厚 TAB パッケージとその応用

寺岡康宏・島本晴夫・立川 透・竹村誠次・上田哲也・御祓如 英也

三菱電機技報 Vol. 66・No. 2・P 121~125

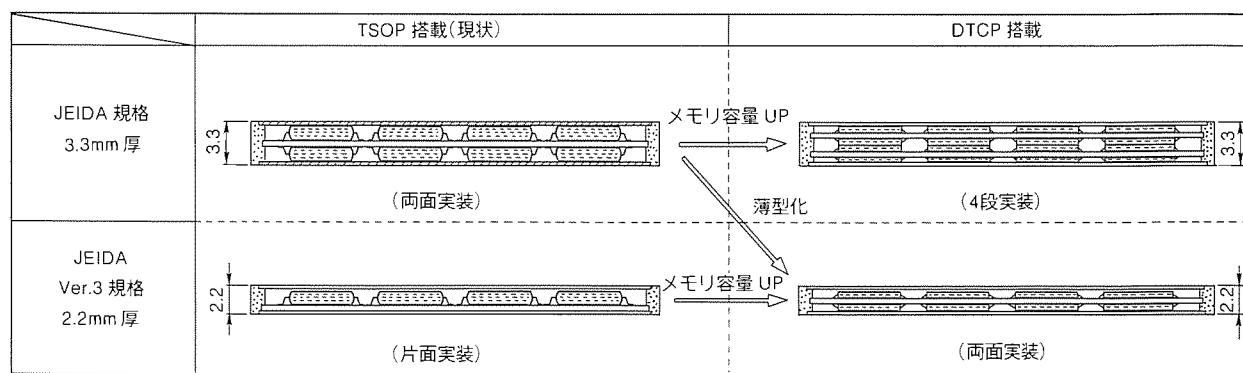

電子機器の小型化・多機能化とともに半導体パッケージの小型化が要求される。この要求にこたえて、厚さ0.5mmの超薄型パッケージをTAB (Tape Automated Bonding) 技術とトランスマルチ樹脂封止技術を用いることによって開発した。これによって信頼性面では、現在普及しているTSOP (Thin Small Outline Package) と同等レベルであることを確認した。また、従来の表面実装技術が適用可能なため、このパッケージを用いた薄型ICメモリカードへの展開が可能となった。

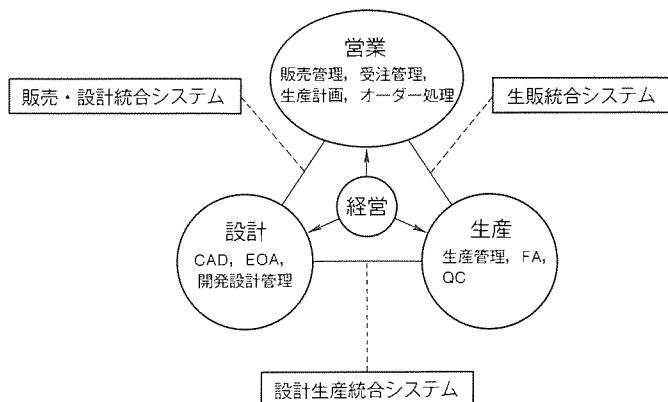

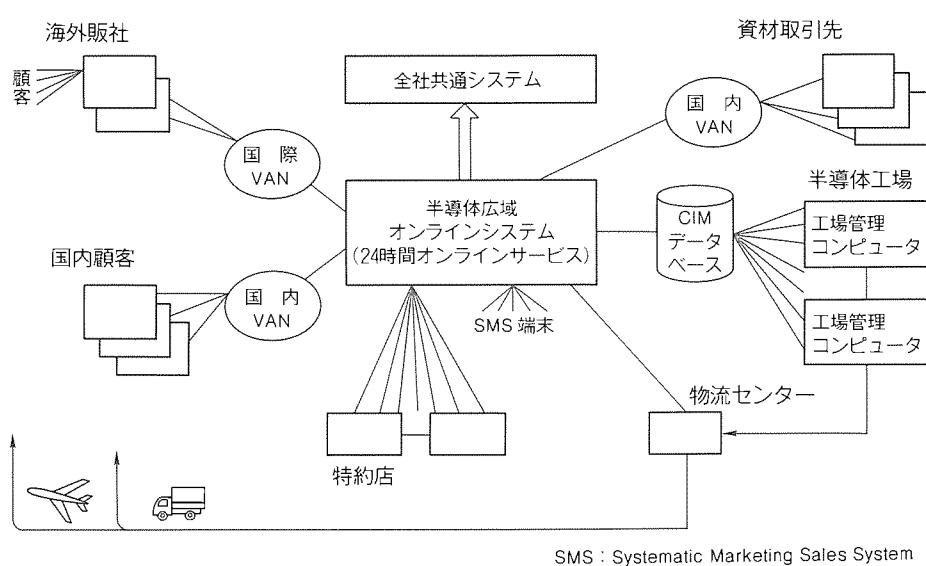

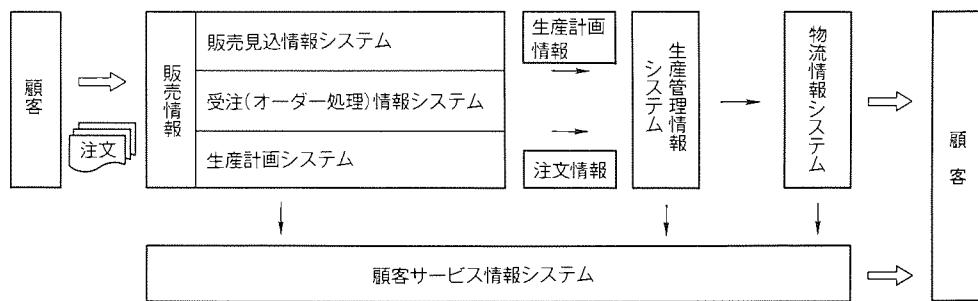

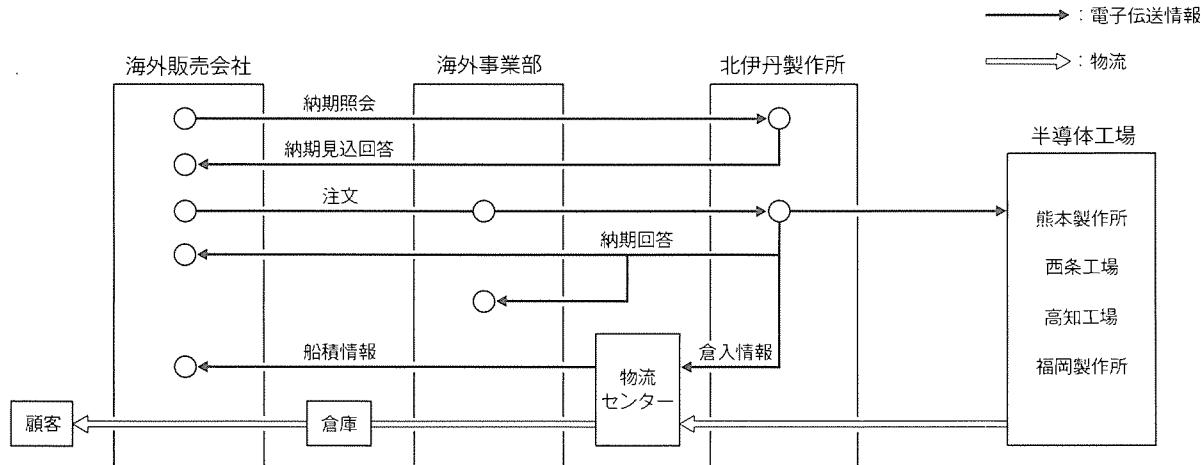

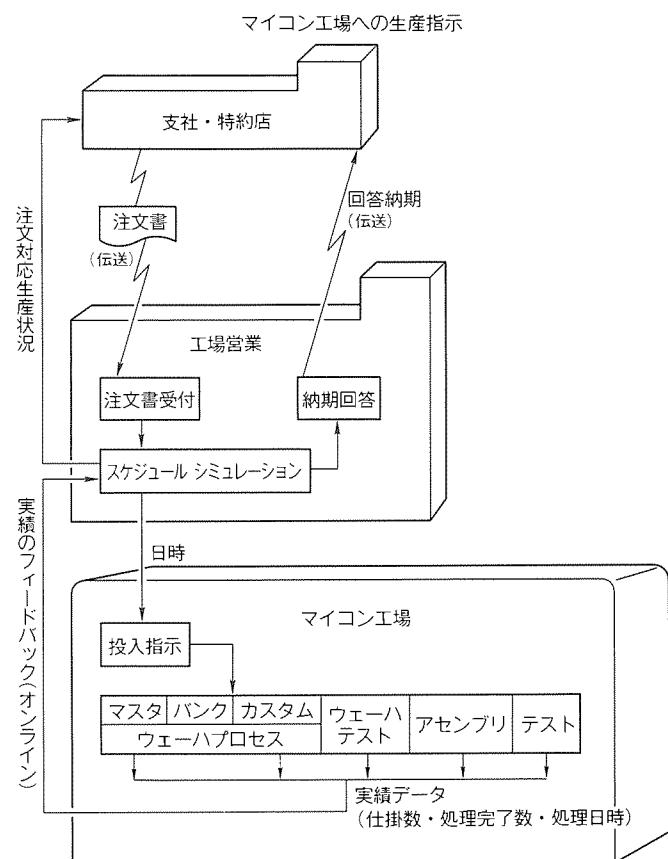

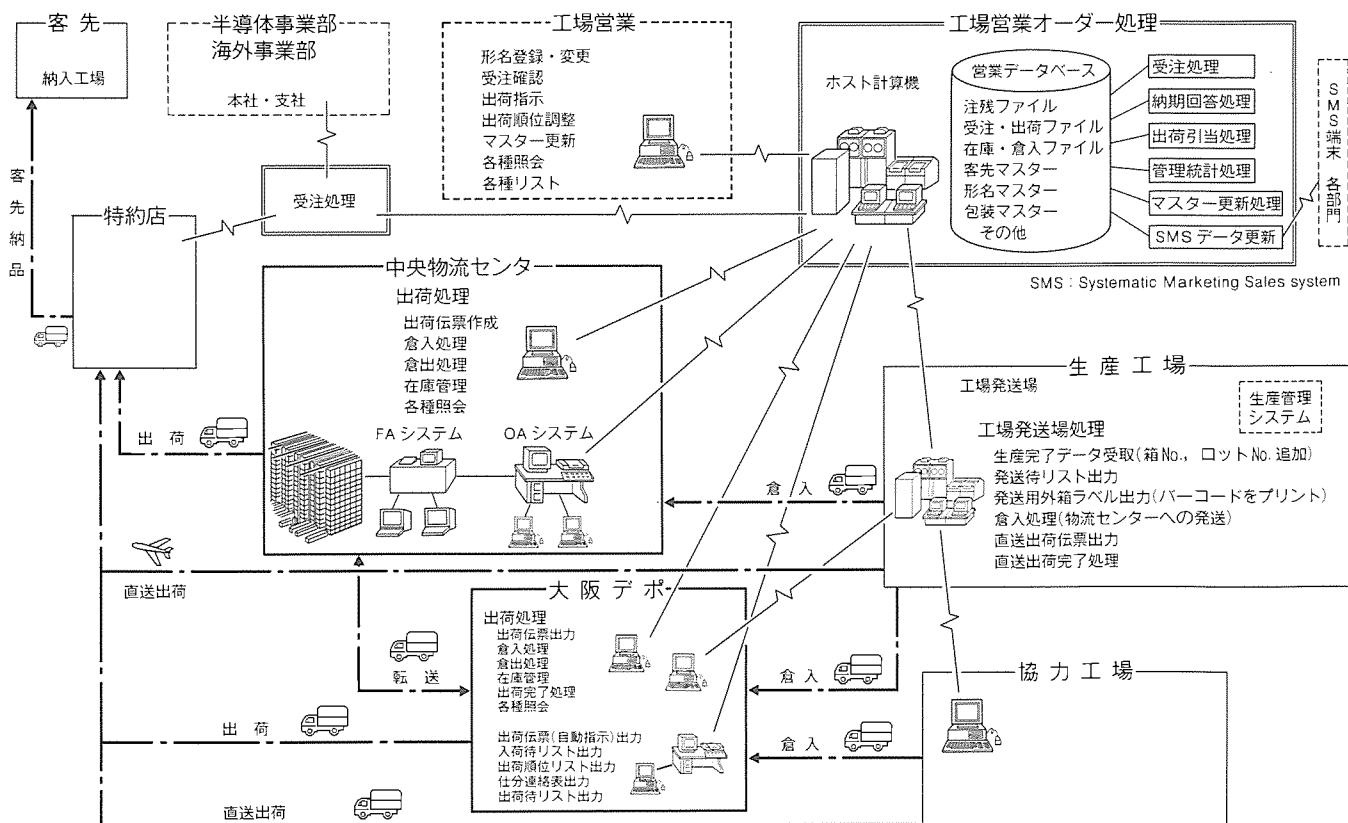

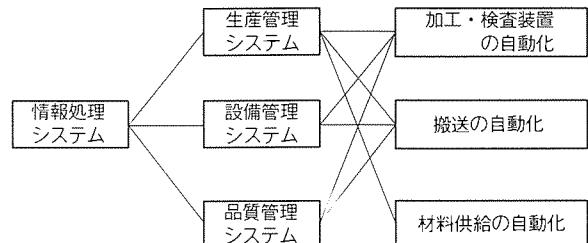

### ユーザーニーズにこたえる販売・生産統合情報ネットワーク

奥野治臣・続木捷雄・山本武夫

三菱電機技報 Vol. 66・No. 2・P 126~130

半導体事業では、マイコン、セミカスタムIC等のカスタム製品を中心に客先仕様に応じた物作りができる体制を築くために販売生産部門の情報を一元化し、販売生産活動のキーとなる“生販情報の統合システム”を半導体CIM (Computer Integrated Manufacturing) システムの一部として、現在構築を進めている。販売情報システム、生産管理システム、物流情報システムに関し、受注から生産・出荷・納品にわたる体制作りとしてその概要を紹介する。

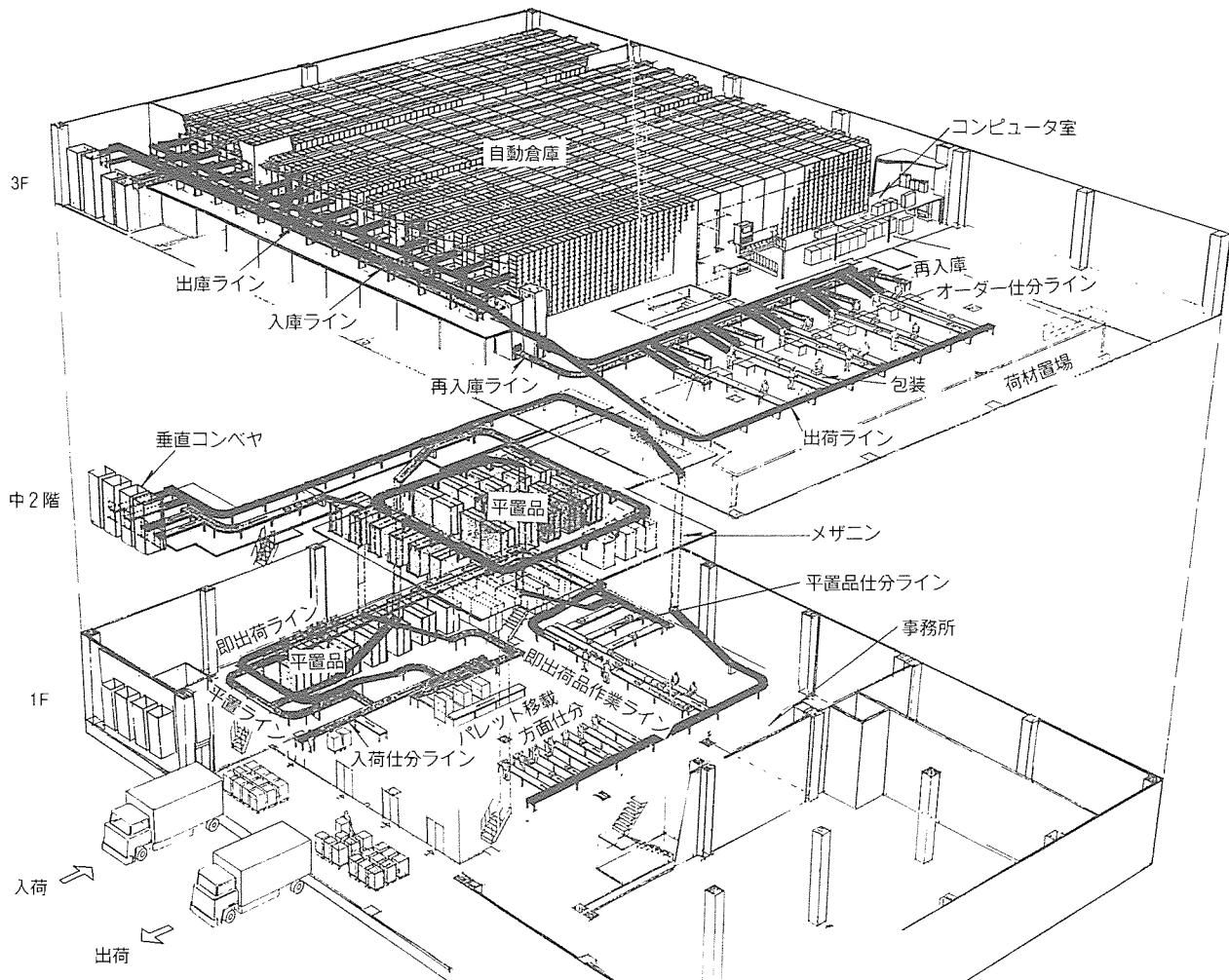

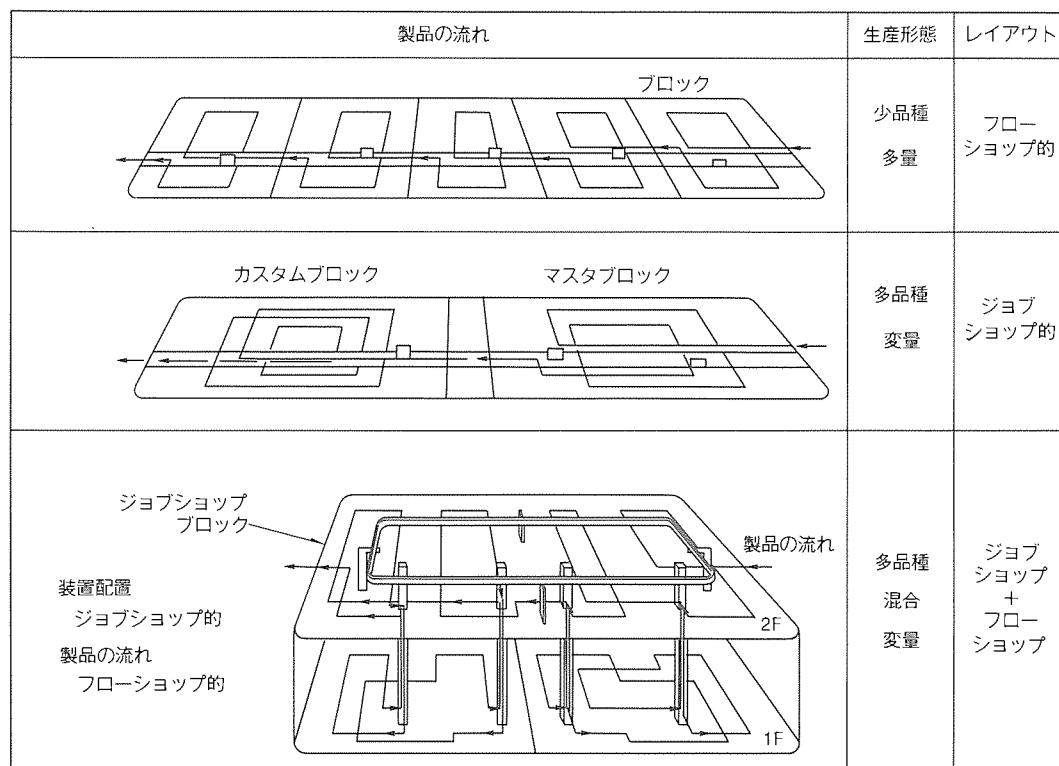

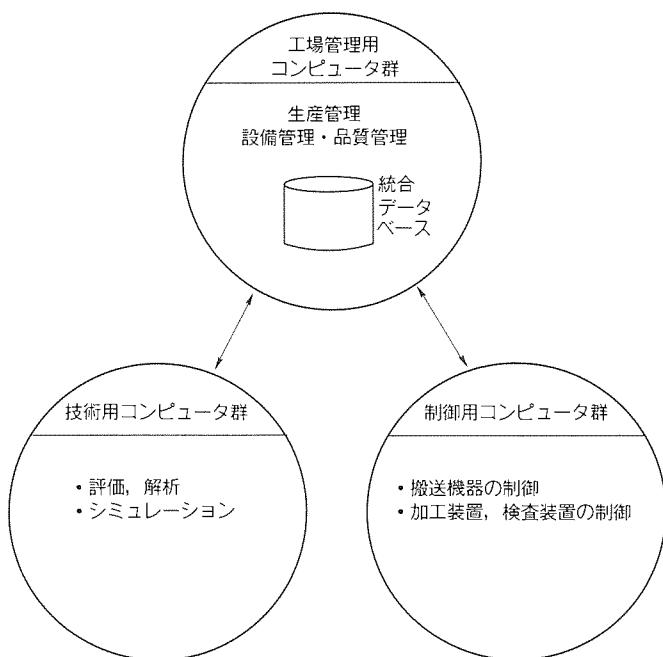

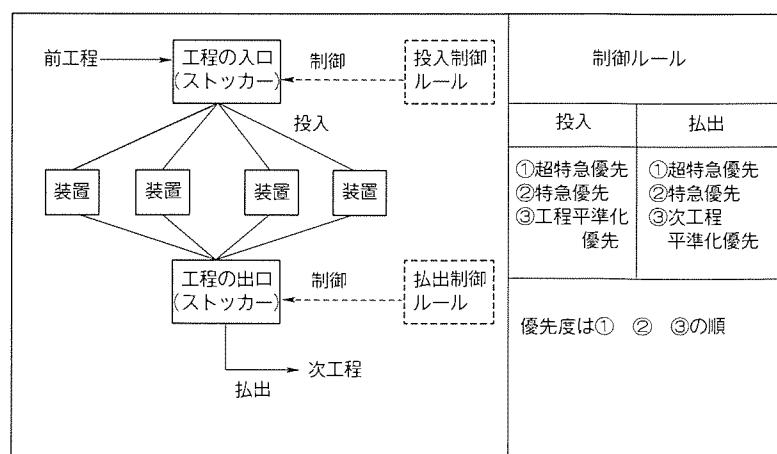

### 最先端工場における生産システム

山崎雅敏・青木利明・御堂洋一

三菱電機技報 Vol. 66・No. 2・P 131~136

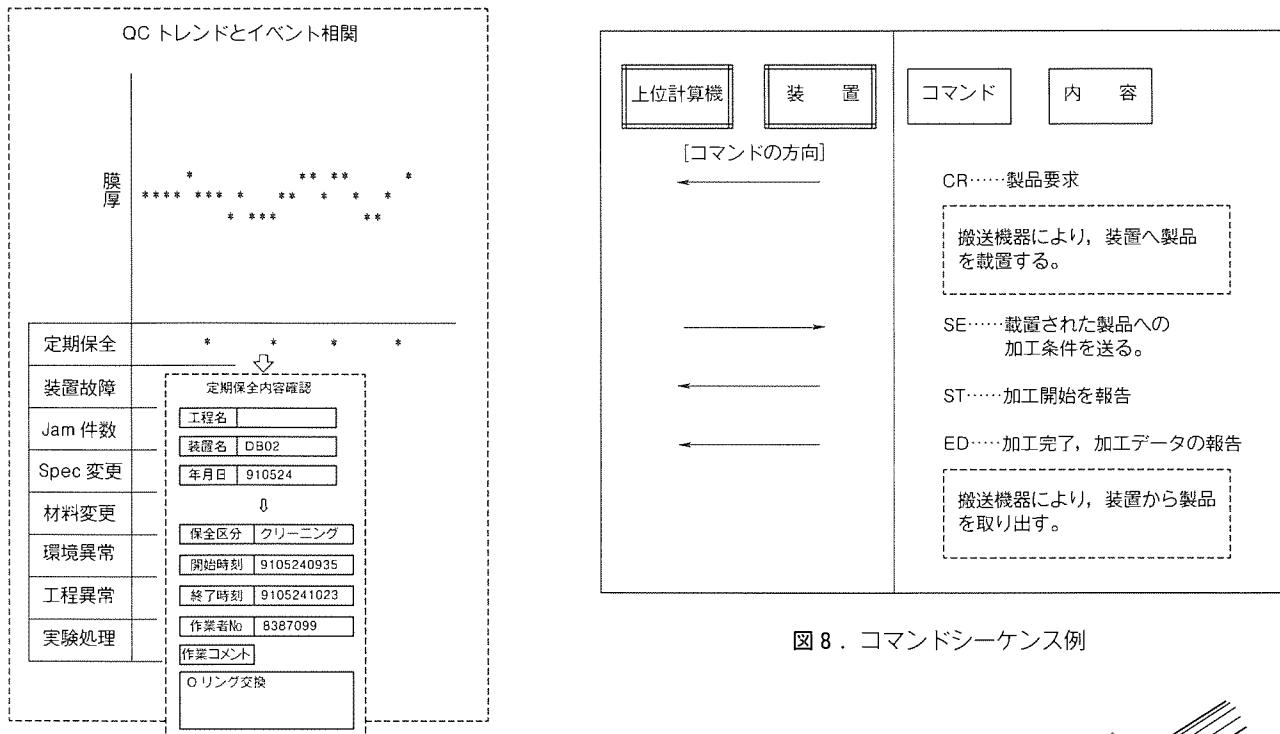

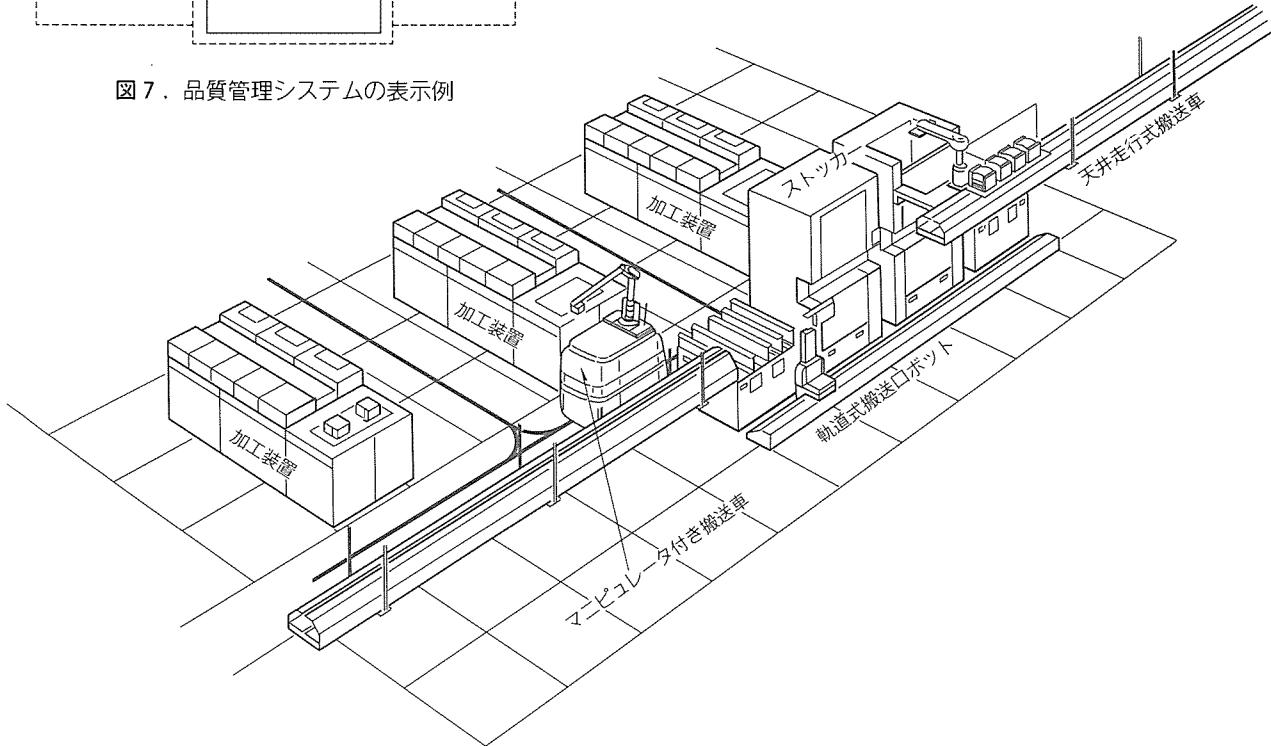

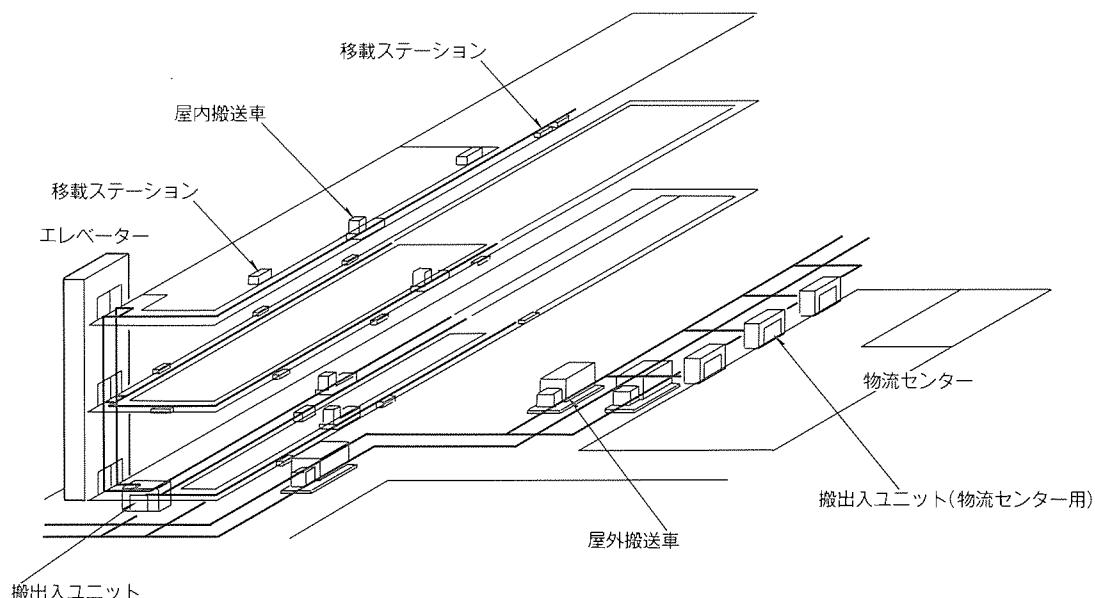

最先端メモリの製造拠点である当社西条工場A棟ウェーハラインに、多品種変量生産に対応できるフレキシブルな生産システムを導入した。このシステムは、製品や材料搬送のフレキシビリティの向上はもとより、FAコンピュータとEWS・パソコンをネットワークで結ぶことにより、生産管理・品質管理・設備管理にかかる情報の統合化と情報処理の高機能化を実現した。

# Abstracts

Mitsubishi Denki Giho: Vol. 66, No. 2, pp. 121~125 (1992)

## A 0.5mm-Thick TAB Package and Its Applications

by Yasuhiro Teraoka, Haruo Shimamoto, Toru Tachikawa, Seiji Takemura, Tetsuya Ueda & Hideya Yagoura

An extremely thin 0.5mm package has been developed by use of tape automated bonding (TAB) and transfer molding technologies. The package reliability has been investigated and found to be nearly equal to current thin small-outline packages (TSOPs). The new package supports conventional surface-mounting techniques, making it suitable for implementing thin IC memory cards.

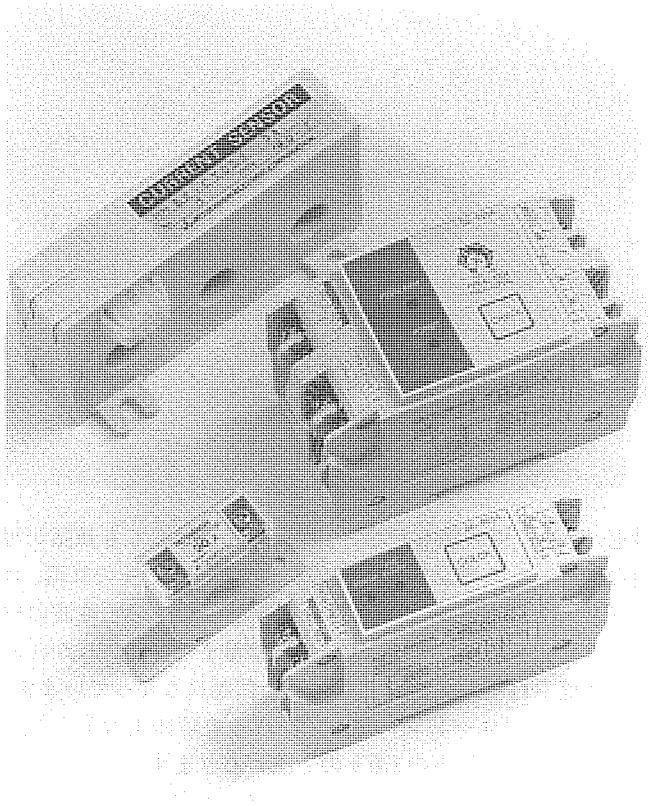

Mitsubishi Denki Giho: Vol. 66, No. 2, pp. 126~130 (1992)

## An Integrated Production and Sales Information Network that Satisfies User Needs

by Haruo Mi Okuno, Hayao Tsuzuki & Takeo Yamamoto

The corporation is setting up an integrated production and sales information system as part of a computer integrated manufacturing (CIM) system for production of embedded microcontrollers and semicustom ICs. This information system will enable the CIM system to produce devices on the basis of user's requested specifications. The article describes the organization of the information system, from ordering to delivery. It covers the sales information systems, production control system, and distribution system.

Mitsubishi Denki Giho: Vol. 66, No. 2, pp. 131~136 (1992)

## Production Systems for Advanced Semiconductor Fabrication Lines

by Masatoshi Yamazaki, Toshiaki Aoki & Yoichi Mido

Factory automation (FA) technologies have been introduced in the wafer line at Mitsubishi Electric Saitama Works Building A to support multivariant, variable-lot production in the corporation's most advanced memory device production facility. Information storage and processing support for the line has been implemented by networks of FA computers and engineering workstations (EWS), and FA computers and personal computers, enabling more sophisticated data processing and a unified data-management strategy. The new technology has brought benefits in terms of production control, quality control, and facility management as well as enhanced flexibility in terms of products and materials transport.

## 卷頭言

三菱電機株式会社

代表取締役副社長

電子デバイス事業本部長 北岡 隆

半導体業界は、ここ20年間その技術進歩と応用範囲の拡大によって飛躍的に成長してきたが、最近では質的变化が求められる時期にさしかかっている。例えば、コンピュータ分野のワークステーションやパソコンではLSIの高性能化・高集積化・低消費電力化の進展がダウンサイ징と呼ばれる市場変化の一要因となっている。AV分野では多くのシステムLSIが使用されることによってデジタル化が進展し、これによって高品位、高画質が実現され、新たな需要を喚起している。

このように今後は半導体の量的拡大にとどまらず、最先端半導体技術による新たな性能・機能の実現と、それによる市場の拡大が必要となっている。また、これらの分野ではハードウェアよりソフトウェアが市場のかぎ(鍵)をにぎるようになってきているのも注目すべきことであり、半導体分野においてもデバイス開発は当然のことながら、ソフトウェアに関連するシステムLSIの開発が重要となってくる。

これらの変化に対応するための基盤技術として、デバイス技術ではCAEによるシステムオンチップの設計技術やサブミクロン、ハーフミクロンの微細加工技術の進展や、それを支える超クリーン環境や高度な生産システムの実現が必要であり、また、これらの諸技術を統合化させるための横断的な活動も欠かすことのできない重要な項目である。

本特集号のメモリ及びマイクロコンピュータは当社半導体における最重点製品であり、今後とも開発・生産の両面において力を入れて伸ばしていく分野である。

メモリはこれからもLSIのリーディングデバイスとして微細化へのけん(牽)引的役割を果たしていく。当社では大容量・高集積化とあわせて多ビット化・高速化・低電圧化などの展開や応用指向型メモリの開発も積極的に行っていく。マイクロコンピュータでは多くの応用分野でシステムの高度化とそぞ野の広がりが更に進む。16ビット、32ビットといった高性能・高機能製品の開発とあわせ、用途別製品開発とソフトウェア技術の開発を強力に進めていく。将来技術としてデータ駆動型プロセッサやニューロチップの開発も推進していく。

一方、生産面においても西条工場の新棟完成による最先端メモリの生産、各工場におけるフレキシブル生産方式の拡充、ドイツ工場での生産などにより、一層の能力向上と納期・品質等の質的向上を図っていく。

上述したように、今後応用システムにおけるニーズと半導体技術におけるシーズの融合はますます重要であり、また、双方にとって多面的なアプローチが必要な時代である。当社では総合電機メーカーの特長を生かしながら半導体の総合力をこれからも高めていく所存である。

ユーザーの皆様方の暖かい御支援をお願いしたい。

# メモリ・マイクロコンピュータの現状と動向

平林庄司\*

## 1. まえがき

IC が産業の米と言われるようになって久しい。なかでも電子機器の頭脳を形成するマイクロコンピュータ（以下“マイコン”という。）とメモリの重要性は極めて大きいものである。メモリは常に高集積化の先頭に立ち、テクノロジードライバとしての役割を果たすと同時にその巨大市場の存在から、ビジネスドライバとしても半導体産業を牽引してきた。一方、電子機器ではハードと並んでソフトが重要な要素として浮かびあがっているが、このソフトをハードのなかに取り込み、一種の文化を形成しているのがマイコンである。ハードの代表のメモリとソフトを伴うマイコン、この二つが車の両輪として半導体産業を引っ張っていると言っても過言ではないであろう。この特集号ではこの両者を取り上げているが、ここでは両者の全体的な動向を述べる。

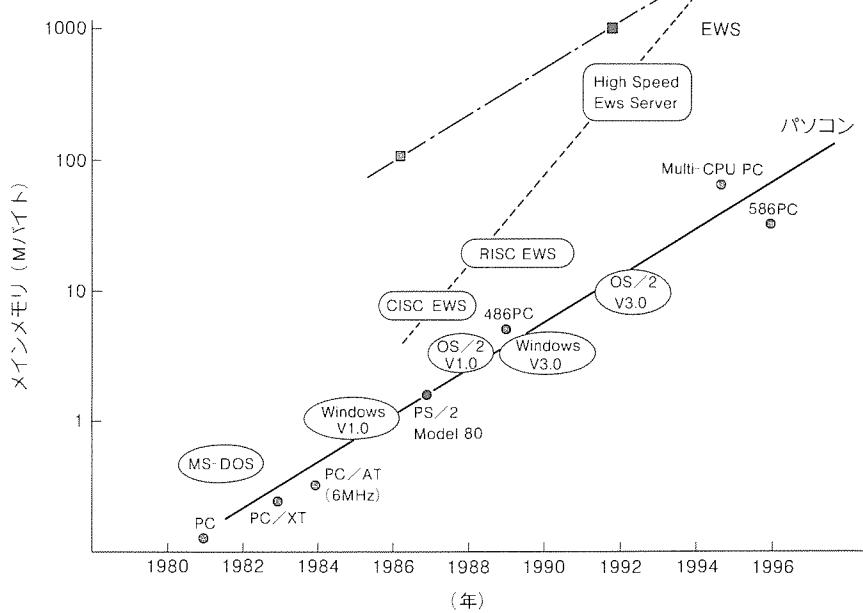

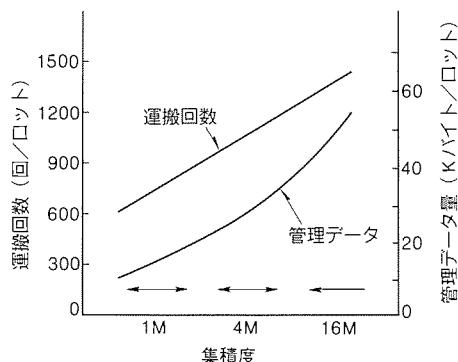

## 2. メモリの動向

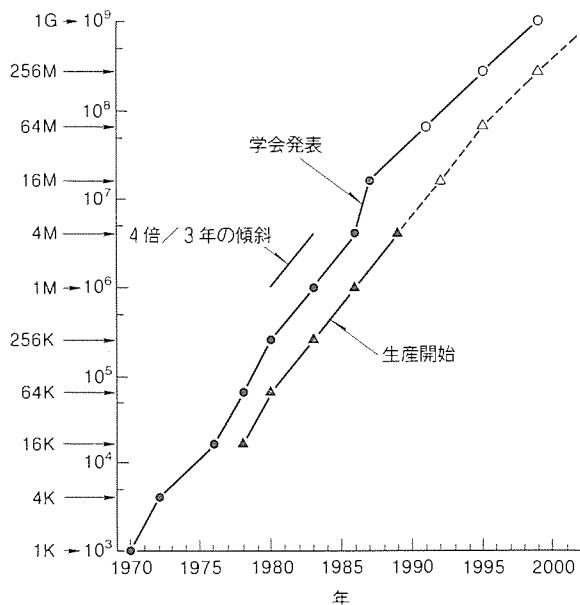

メモリはコンピュータの必ず（須）部品として、コンピュータの発展を支える形で、飛躍的な成長・発展を遂げてきた。メモリの代表的応用であるコンピュータのメインメモリの例をとると、図1のように、メモリ容量は指数関数的に増大している。これを、技術的・経済的に実現させているのが、メモリの高集積化技術である。図2に示すように、代表的メモリであるDRAMでは、過去20年間、3年で4倍のペースで高集積化を実現してきている。現在市場では4MビットDRAMが主流になりつつあるが、研究所段階では、既に64MビットDRAMが精力的に研究され、256Mの実現も確実視されるようになるなど、まだこのペースは続くと見られる。

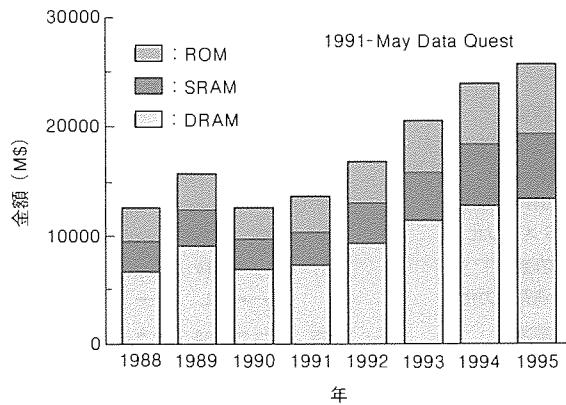

ビジネス的にもメモリはシリコンサイクリの影響を受けながらも順調に成長することが見込まれている。図3に示すように、年15%程度の成長率で今後も推移し、半導体産業の浮沈をかけたデバイスとなっている。

### 2.1 多様なメモリ

ユーザーから見れば、理想のメモリというのは、自由に読み書きができる、

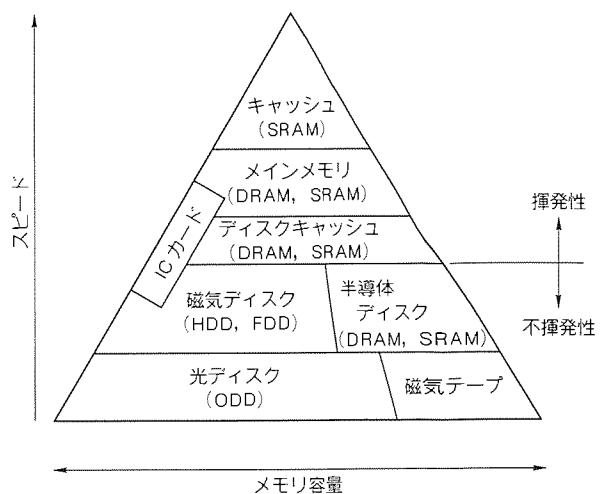

一度書き込めば決して消えず、それも高速に読み書きができる、しかも大容量かつ安価なものがよいということになるが、残念ながら現実にはそういうものはいまだ存在せず、DRAM以外にも多様なメモリがその特長を生かす分野で使い分けがなされている。図4には、コンピュータでのメモリの階層構成を示す。

半導体RAMの最大欠点である揮発性を補うため、膨大なデータを蓄える外部メモリにはディスクや磁気テープが使われる。しかし、この応用にもスピードのギャップを埋めるために、ディスクキャッシュとしてDRAMやSRAMが一部併用されている。また、半導体メモリの大容量化により、磁気ディスクそのものをDRAM・SRAMで置き換えるよういう動きもある。さらに、この分野の将来動向としては、新しい書き込み・記憶原理によるフラッシュメモリやFRAM(Ferroelectric Nonvolatile RAM)に熱い視線が注がれ、新しい応用が広がるものと期待される。

メインメモリとしては主にDRAMが用いられているが、低消費電力化・電池バックアップ化のために一部のシステムではSRAMが使用されている。特に、携帯小型機器にはなくてはならない存在であり、電子機器のパーソナル化の一役を担っている。

半導体RAMの中でも高速SRAMは、DRAMでは実現で

図1. コンピュータのメモリ動向

図2. DRAMの歴史

図3. メモリの需要予測

きない高速性を持っているため、キャッシュとしてメモリ階層の内側に置き、アクセス頻度の高いデータや近い将来アクセスされる可能性の高いデータを格納しておく。近年のコンピュータの飛躍的な高速化を支えたデバイスであり、ますます重要性が増している。

また、書換えを必要としない用途には、マスク ROM が広く用いられており、大容量化とともに新しい応用が広がっている。

## 2.2 DRAMの動向

ひたすら大容量化を目指してきたDRAMも、大容量化と同時に多様化が進み始めている。これは、1チップの規模が大きくなり、もはや多数個のDRAMを必要としない小型システムが出現し始めたことや、システムの性能を最大にあげるために特殊機能を盛り込み始めたことによる。いわば、システムオンチップの方向へDRAMも進みだしたといえよう。具体的には、当社ではパソコン用の×8, ×16等の多ビット品、電池駆動機器用の低電圧・低消費電力品、画像専用メモリ、さらにはキャッシュを内蔵したCDRAM等を開発し

図4. コンピュータにおけるメモリ階層

ている。64Mを筆頭とする高集積化技術をベースに将来も更に多様化を進める予定である。

## 2.3 SRAMの動向

低消費電力(中速)SRAMでも高集積化の動きは激しく、16M DRAMと同等の技術を使用して、4M SRAMを開発した。SRAMの持ち味である低スタンバイ電流に磨きをかけるため、立体構造のTFT(薄膜トランジスタ)をメモリセルに採用して超低スタンバイ電流を実現している。TFTはいわば初步の三次元素子であり、将来のLSIの一方向を示しているといえよう。

高速SRAMはCPUチップと並ぶコンピュータのキーパーツとして、ますます重要性を増している。コンピュータの高速化に対応するため、動作速度は年々向上するばかりである。当社でも、BiCMOS技術を用いて、256Kで初めて10nsの壁を破る製品を実現した。しかしながら、メモリの中ではシステム化の波は高速SRAMにまず押し寄せると考えられ、今後はシステムオンチップへのアプローチが必須になってくる。

## 2.4 ROMの動向

従来から書換えのできるROMとして、EPROMが広く使われてきたが、近年新しい概念のフラッシュメモリが現れ、EPROMを置き換えるようとしている。さらに、将来はHDD、FDDを置き換えて、DRAMに匹敵する規模の市場を形成するといわれている。当社では既に1Mビットフラッシュメモリを製品化しているが、さらにより高集積で使いやすく、完成度の高いデバイスを目指して研究を行っている。

マスクROMは、そのシンプルなメモリセル構造のため、DRAM以上の高集積度を実現できる。書換えはできないものの、その大容量性・不揮発性を生かして、フォントメモリ、辞書メモリに使われ、地味ながらなくてはならないデバイスとなっている。

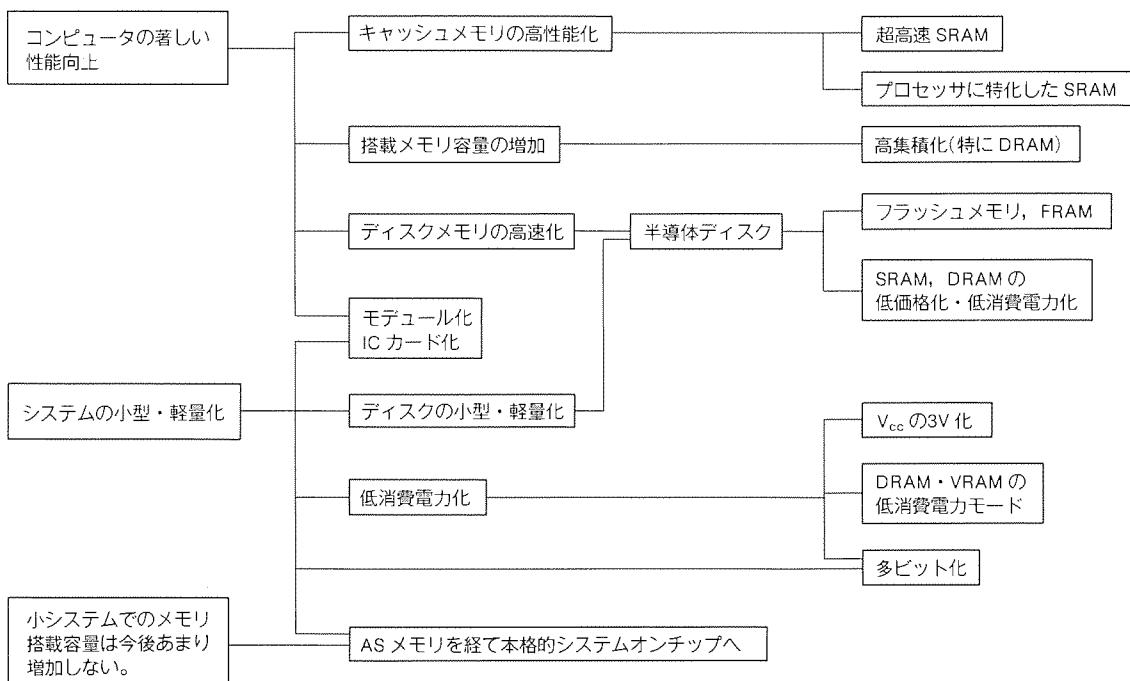

以上の各種メモリの動向をまとめると、図5のようになる。

当社では、これらの要求にこたえられるように、図6に示す方向の開発を行っていく予定である。同時に、新しい動作原理のメモリの研究等、シーズの掘り下げも精力的に進めている。

### 3. マイコンの動向

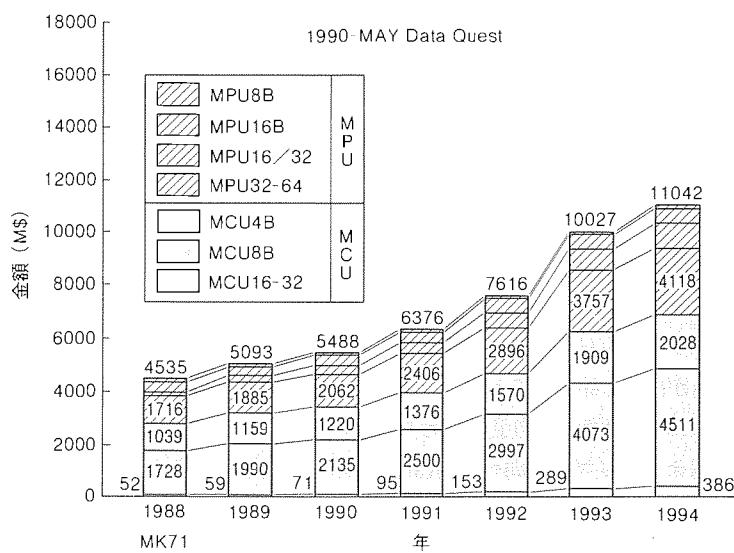

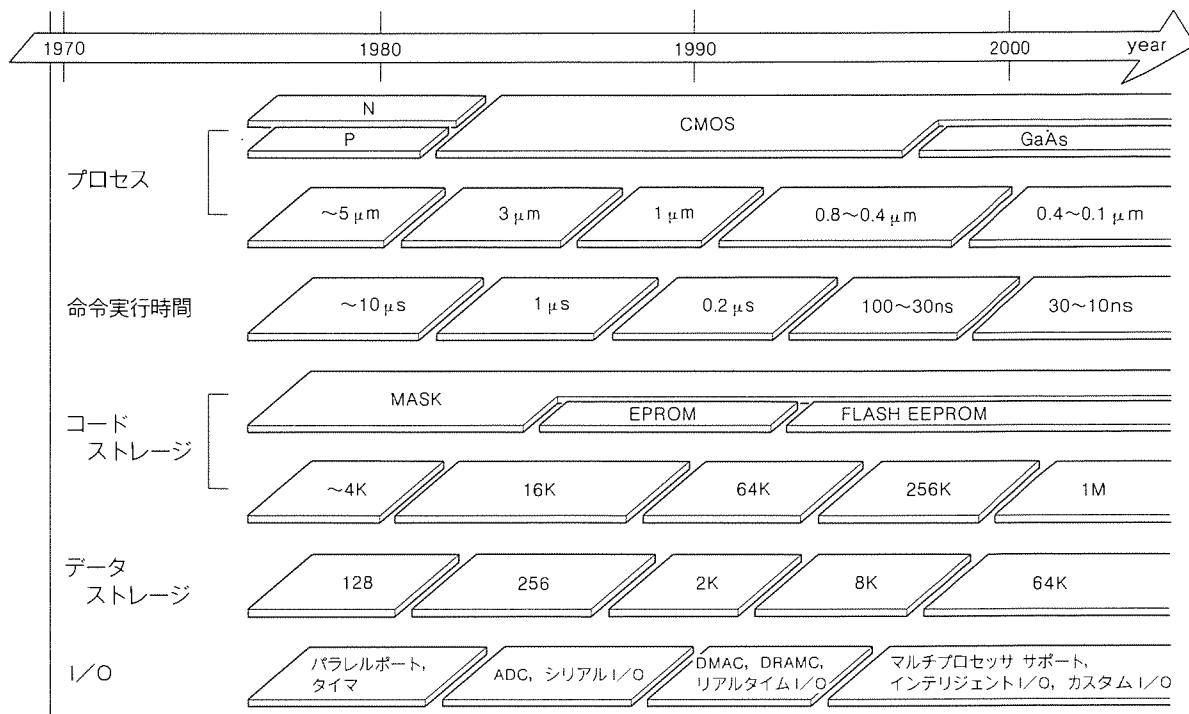

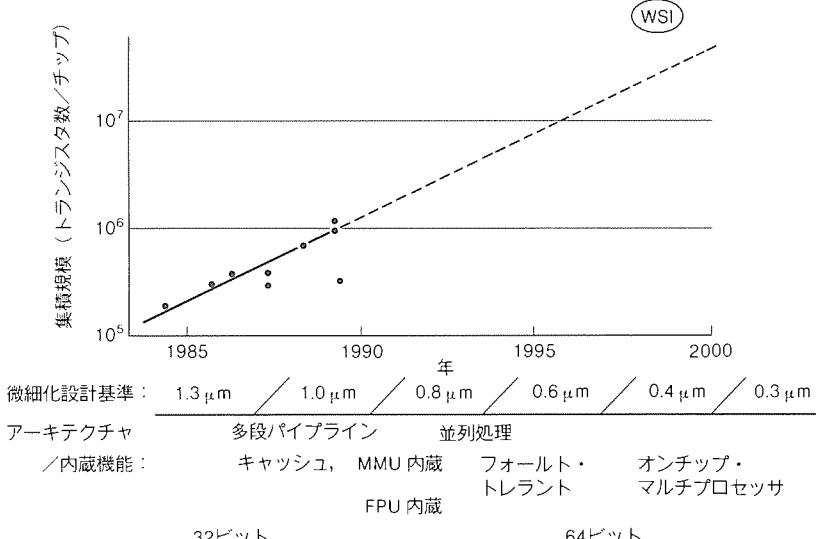

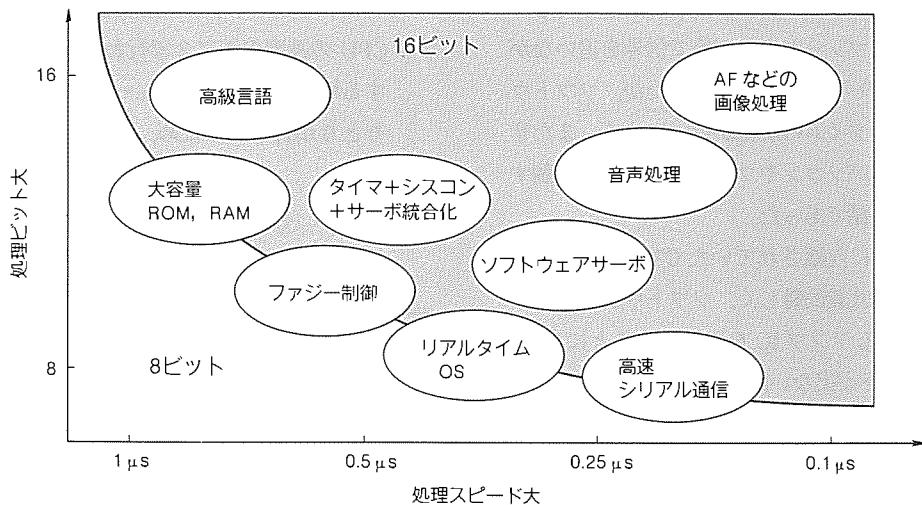

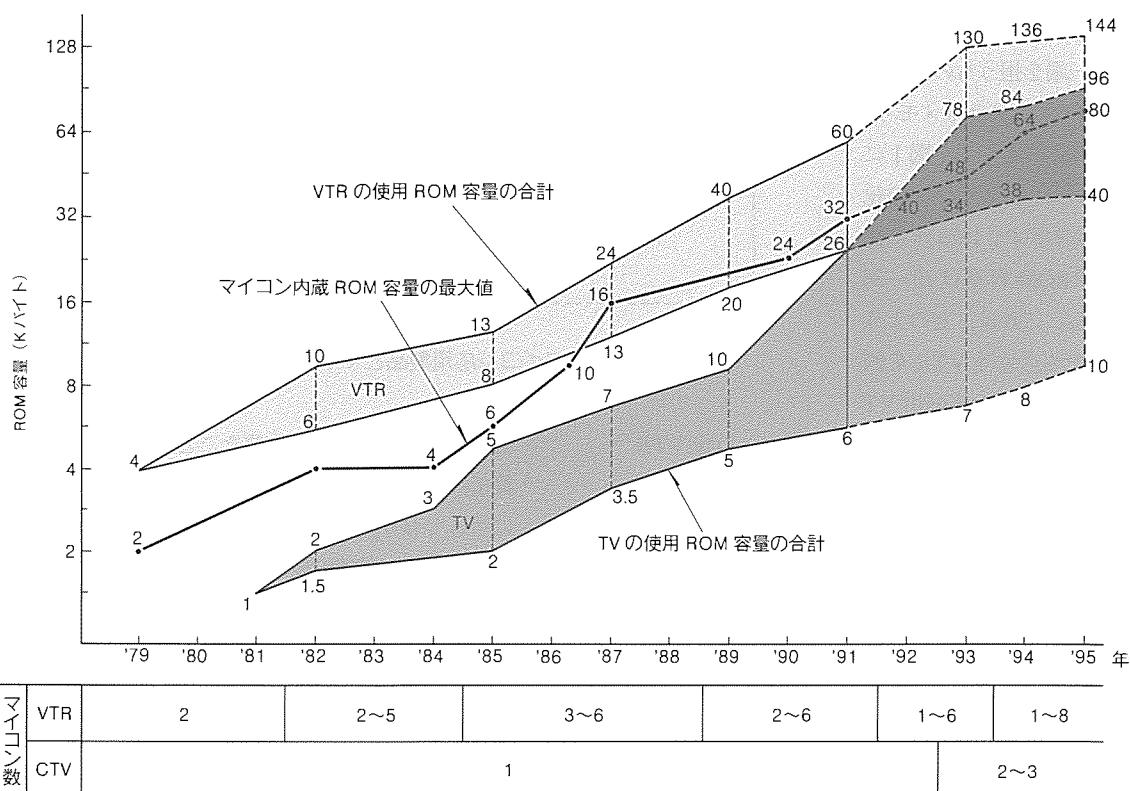

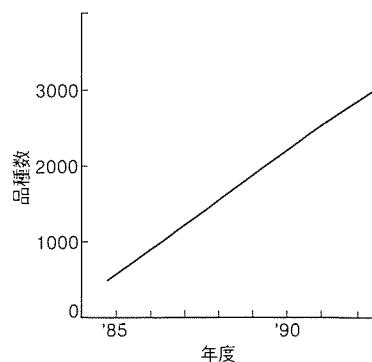

マイコンは、民生機器から情報・通信機器や産業機器に至るまで幅広く使用されている。これは商品の多様化、機能の複合化、また商品の開発サイクルの短縮にソフトウェアで対応することが一層進められていることによるものと考えられる。マイコンの需要は今後とも拡大し、図7に示すように今後とも年平均15%の成長が見込まれている。このような需要の拡大は半導体技術の進展により高性能、高機能なチップが実現されていることによるものと考えられる。図8にマイコンの性能向上を示す。

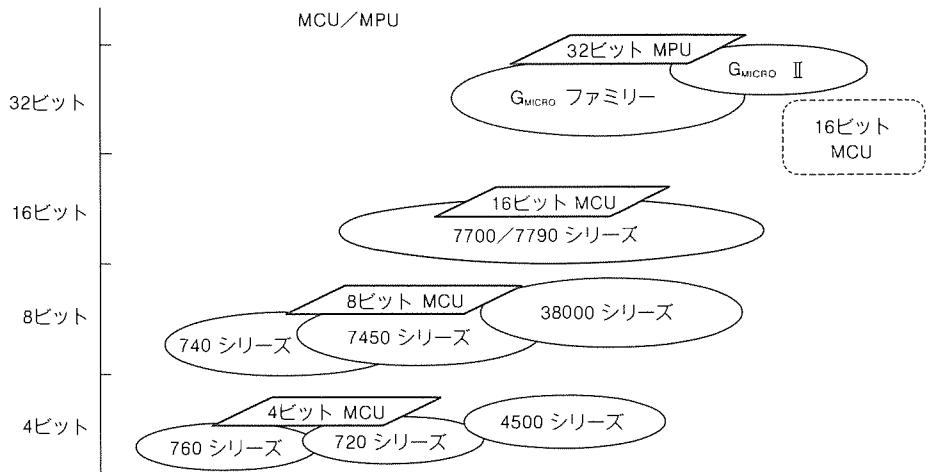

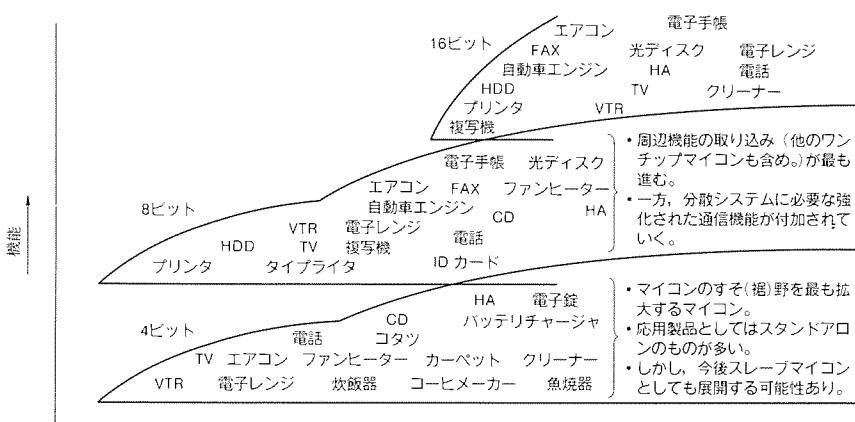

#### 3.1 三菱マイコンのラインアップ

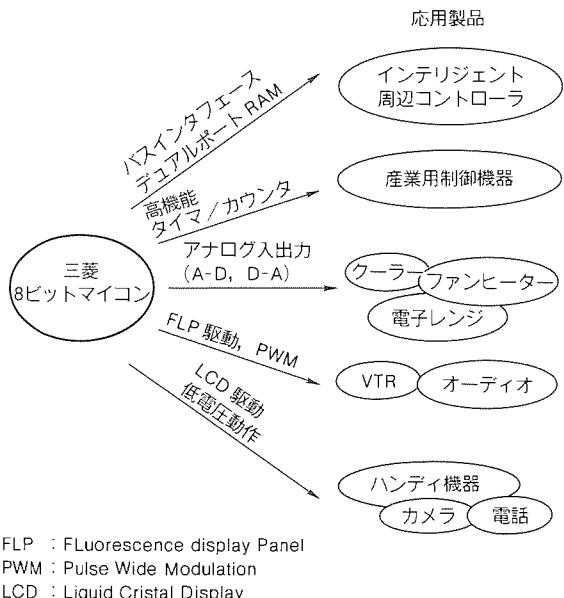

三菱マイコンのラインアップを図9に示す。当社は4ビットマイコンを1978年から量産を始め、現在はMELPS 720シリーズ、TV用マイコン、リモコン用マイコンなど多数開発、製品化している。応用製品の制御に必要な機能を内蔵するとともに、電源電圧1.1Vの低電圧動作も実現しており、主に家庭用機器への組込み用として使われている。8ビットマイコンは図10に示すように応用製品別に適合するよう制御機能を内蔵し、製品群を開発・製品化してい

|                   |                                           |                                                                                                         |

|-------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------|

| <b>DRAM</b>       | 大容量化<br>多ビット化<br>低電圧化<br>低消費電力化<br>ASメモリ化 | 4M → 16M → 64M<br>×1, ×4 → ×8, ×9, ×16, ×18<br>5V → 3.3V, 3V<br>L version<br>Video RAM, CDRAM, シリコンファイル |

| <b>低消費電力 SRAM</b> | 大容量化<br>低消費電力化                            | 1M → 4M → 16M<br>L → LL → UL                                                                            |

| <b>高速 SRAM</b>    | 超高速化<br>大容量化<br>ASメモリ化                    | 15ns → 8ns → 6ns<br>256K → 1M → 4M<br>標準品 → 各 MPU 用 → 本格的 ASSRAM                                        |

| <b>EPROM</b>      | フラッシュメモリ化                                 | 1M → 4M → 16M                                                                                           |

| <b>MASK ROM</b>   | 大容量化                                      | 16M → 32M → 64M                                                                                         |

図6. 三菱メモリの開発方向

図7. 全世界マイコン需要予測

図8. マイコンの性能向上とプロセス技術の進展

る。また、内蔵メモリ容量やパッケージのバリエーションもそろえ、多様な市場ニーズに対応しており、民生機器からOA機器などに幅広く使われている。16ビットマイコンは制御用途として自動車用、コンピュータ周辺機器やFA機器などに用途が拡大しているが、家庭用機器の高機能化により採用が始まっている。32ビットマイクロプロセッサ(GMICRO)は先端の設計技術や微細加工技術を用いて開発・製品化をしている。

### 3.2 三菱ソフトウェア開発環境

言語については、4ビット・8ビットはアセンブラーが主体であるが開発効率を向上させるための構造化記述アセンブラーを製品化している。16ビットでは応用ソフトウェアの増大とともにC言語の使用が増している。32ビットではC言語にとどまらずCOBOL, FORTRANなど様々な言語が製品化されている。

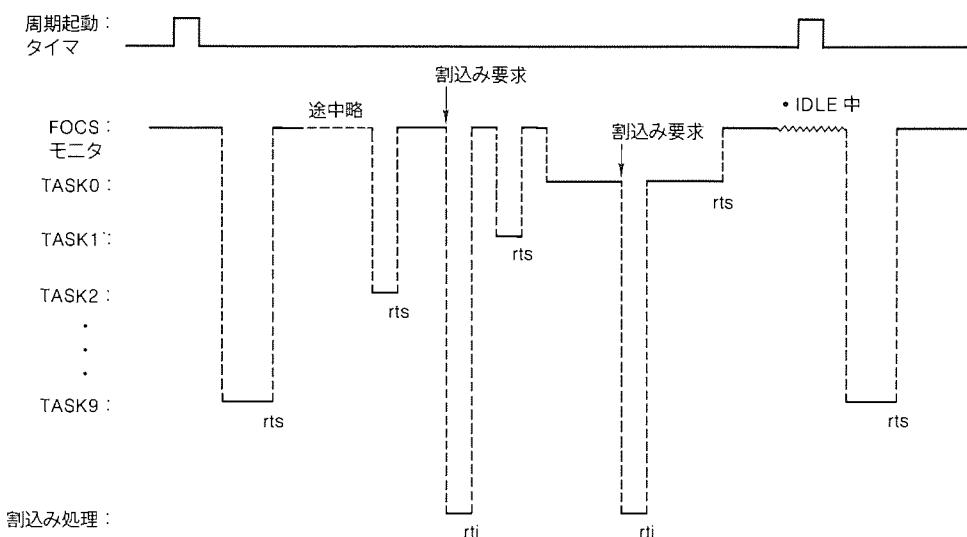

複雑なリアルタイム処理を行う応用ではリアルタイムOSの利用が進んでいる。8ビット・16ビットマイコンでも内蔵ROM容量の増大や、マイコンの処理速度の向上に伴いリアルタイムOSの使用が高まっている。当社ではμITRON仕様の展開を図っている。

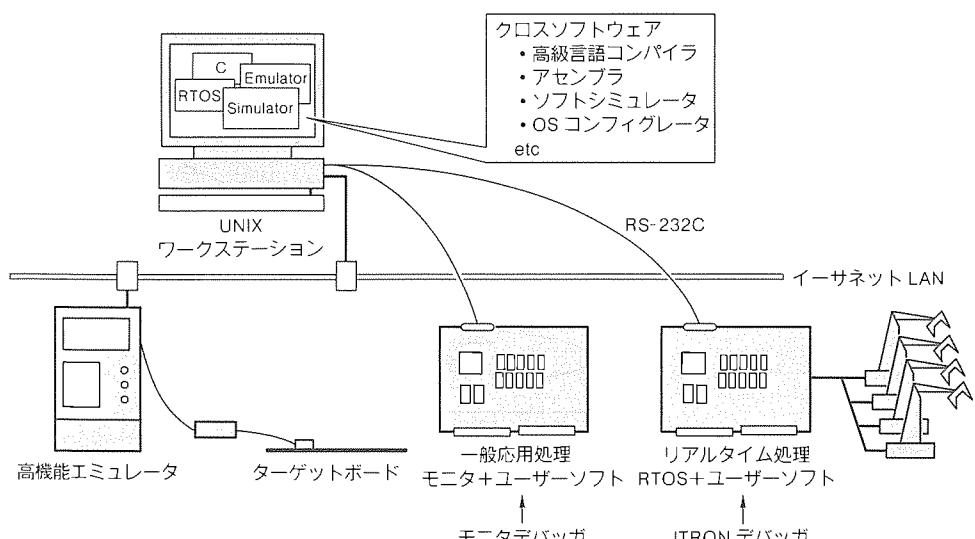

また、インサーキットエミュレータの高機能化・高性能化が進んでいるが、これらの開発ツールを用いてソフトウェ

図9. 三菱マイコンのラインアップ

ア開発のスタート時からデバッグまで性能評価を統合して行える開発環境の提供が求められており、パソコンやワークステーションのうえでの統合化開発ツールの開発・製品化を進めている(図11)。

### 3.3 今後の展開

現在、主流となっているノイマン型のプロセッサの開発については、次のように開発を進めていきたいと考えている。高速化アーキテクチャとしてはスーパースカラーや多段パイプラインの実用化を一層進め、プロセスの微細化の進展により64ビット化も検討していく。汎用マイクロプロセッサの技術トレンドを図12に示す。

一方、非ノイマン型のプロセッサの開発も進めている。データ駆動型マイクロプロセッサは入力データの到着により、

図10. 8ビットマイコン新シリーズの製品展開例

複数の処理を並列に駆動するものであるが、多段パイプライン分割で高速処理が可能であり、大規模なマルチプロセッサ構成が容易なことが特徴となる。応用として音声・画像等の信号処理や高速演算処理機能を活用した制御用途が考えられる。ファジーチップも研究開発を進めており、高速演算用としてのLSIは今後ワンチップマイコンへの組込みが検討され、カメラや自動車など高速処理が求められる用途に期待されている。ファジーチップの研究開発の開発動向を図13に示す。ニューロチップはまだ試作段階である。学習効果によって複雑な連想処理を短時間で実行できることから、知的データベース処理や認識処理に期待されている。

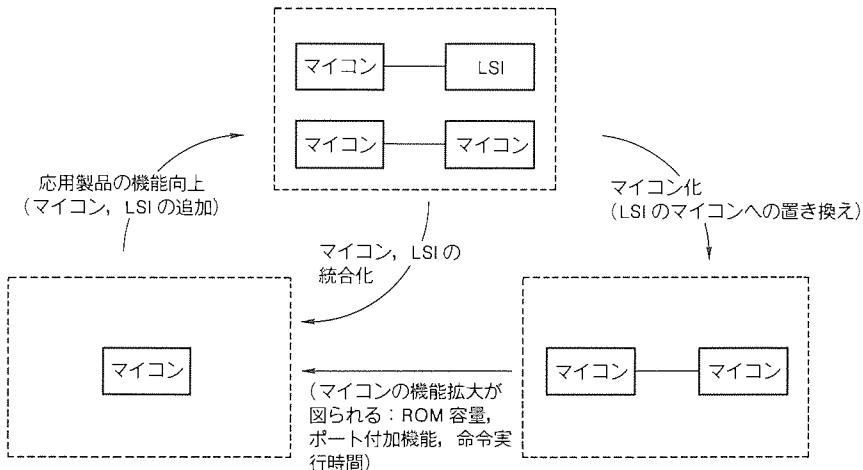

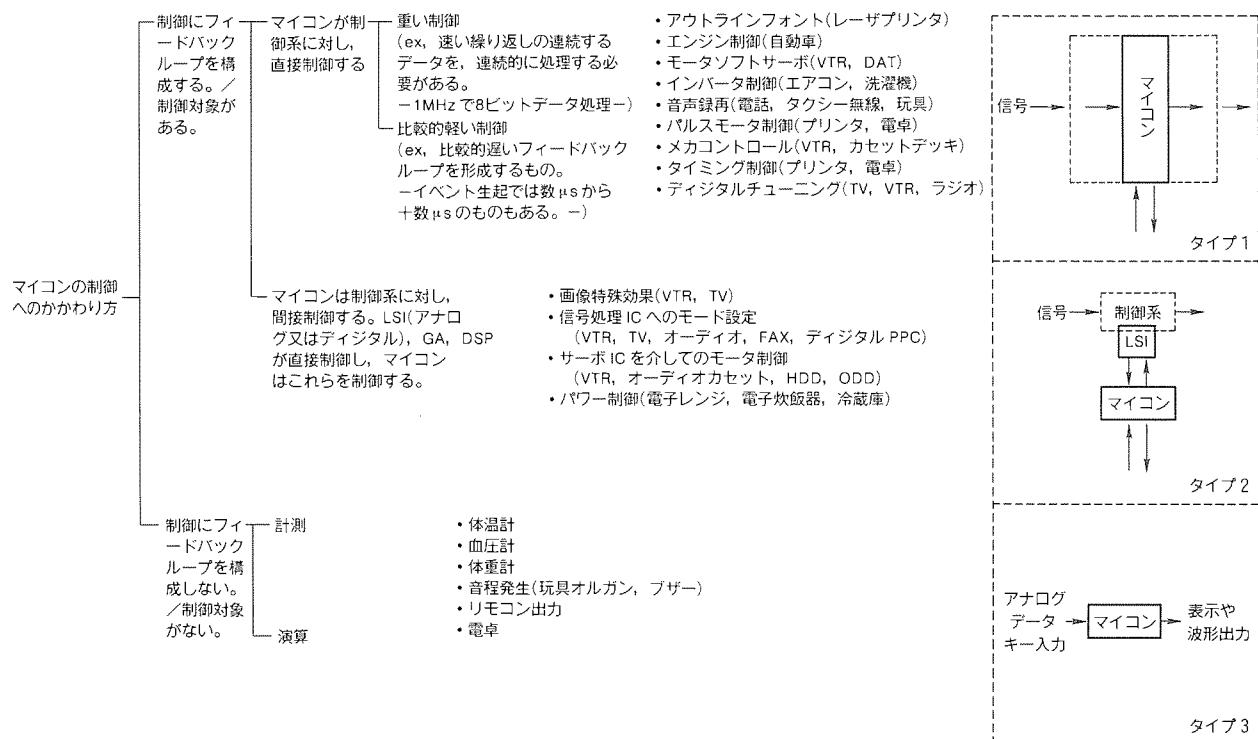

### 3.4 マイコンの応用

半導体技術の向上は、マイクロプロセッサ(MPU)及びワンチップマイコン(MCU)の高性能化を促し、それらの応用製品の一層の機能向上と市場の拡大に寄与してきた。

MCUにおける4ビット、8ビット、16ビットの応用製品への適応の推移を図14に示す。

民生機器、OA、産業機器ともそれぞれ高ビット化が進行している。マイコンの揺らん(籠)期では、4ビットMCUは主に民生機器に、8ビットMCUは主にOA、産業機器に使われていた。しかし、現在では8ビットMCUでは両者が混在し、16ビットMCUでは、OA、産業機器が主流であるが、VTRやエアコンなどの民生機器が、仲間入りしてきている。また、4ビットMCUでは、現在新規にマイコンを使う機器が最も多く登場するところもある。

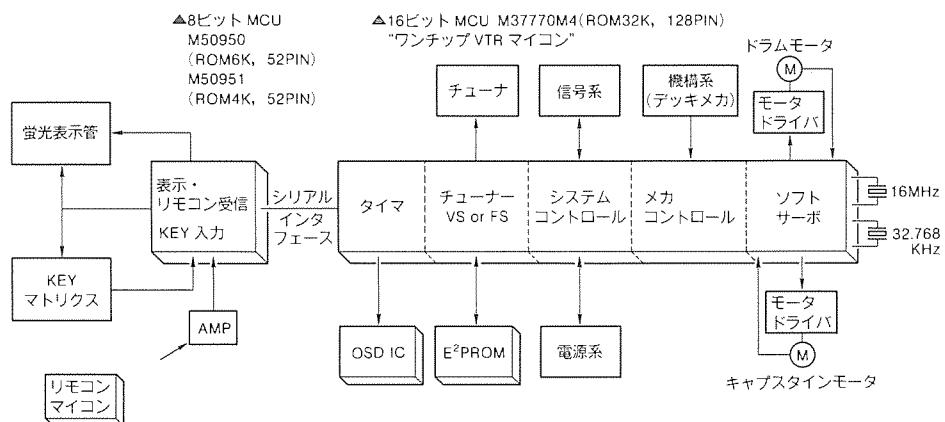

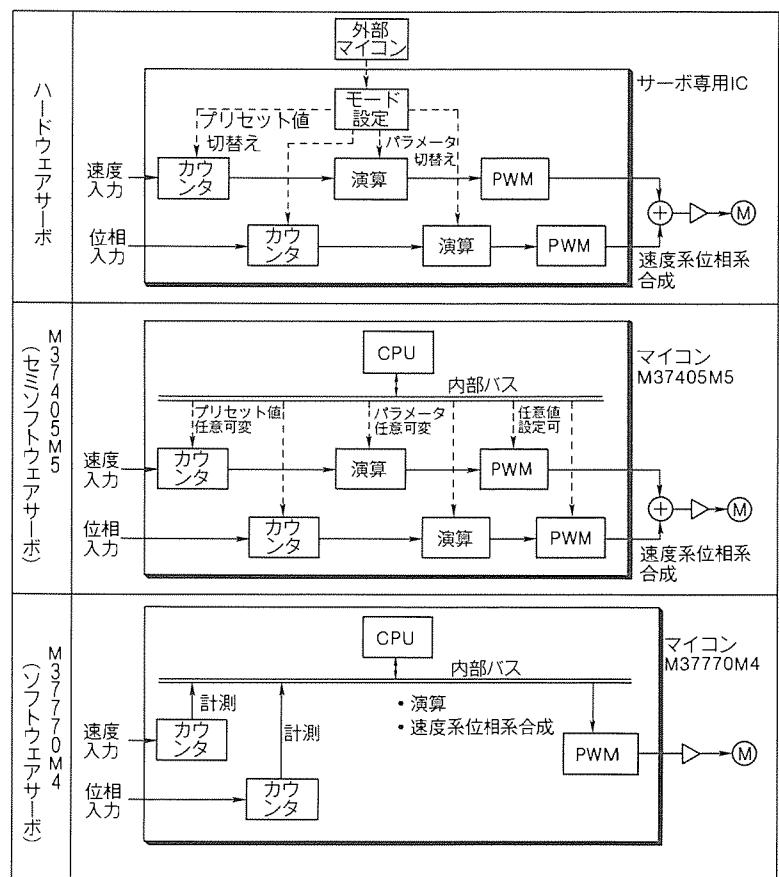

一つのマイコン応用製品において、4ビット、8ビット、16ビットと高ビット化が進む傾向がある。それはどのような役割を果たすためか、民生機器のなかで最も早く16ビットマイコンを使おうとしているVTRとエアコンの場合について、表1に示す。この表で明らかなように4ビットMCUから8ビットMCUへの移行は、幾つかの機能追加のためであった。ところが8ビットMCUから16ビットMCUへは、VTR・エアコンとも、応用製品の基本性能を

図11. 統合化開発環境

図12. 汎用マイクロプロセッサの技術トレンド

著しく向上させるモータ制御方式の大改良を目的としたのであり、この点で両者の16ビットMCUを使う目的は、偶然にも一致していた。ここでいう応用製品の基本性能向上とは、単に幾つかの機能追加をすることではない。VTRの場合、従来外付けの専用ICによるディジタルサーボでモータを制御していたが、それをマイコンに内蔵したハードウェアとブ

| 演算時間／推論     | 実現手段                                                                  |

|-------------|-----------------------------------------------------------------------|

| 10μs以下      | 機能を限定した専用ハードウェア                                                       |

| 10~500μs    | ファジー推論専用マイクロプロセッサ<br>(メンバシップ関数、ファジー推論ルール数等が)<br>(プログラム可能でファジー推論を高速実行) |

| 300μs~100ms | ファジー演算向き命令を持たせた汎用マイクロプロセッサ                                            |

| 100ms以上     | 汎用マイクロプロセッサとソフトウェア                                                    |

図13. ファジーチップの研究開発動向

図14. MCUの各ビットごとの応用製品の展開推移

表1. マイコンの高ビット化による機能拡大性能向上例

|                                | 機能項目                             | 4ビット<br>PMOS | 8ビット<br>CMOS      | 16ビット<br>CMOS     |

|--------------------------------|----------------------------------|--------------|-------------------|-------------------|

| VTR<br>(メカ制御<br>マイコン)          | ・メカ制御<br>(シーケンシャル制御)             | ○            | ○                 | ○                 |

|                                | ・KY入力処理                          | ○            | ○                 | ○                 |

|                                | ・リモコン入力処理                        |              | ○                 | ○                 |

|                                | ・特殊再生処理                          |              | ○                 | ○                 |

|                                | ・他のマイコン、周辺LSI<br>とのシリアルインターフェース  |              | ○                 | ○                 |

|                                | ・モータのソフトサーボ制御<br>(外付け専用ICの機能取込み) |              |                   | ○                 |

| エアコンディ<br>ション<br>(室外機<br>マイコン) | ・コンプレッサモータ制御                     | ○            | ○                 | ○                 |

|                                | ・室内マイコンとのインターフェース                | ○<br>ストローブ   | ○<br>シリアルインターフェース | ○<br>シリアルインターフェース |

|                                | ・ヒートポンプ処理                        |              | ○                 | ○                 |

|                                | ・室外温度センス                         |              | ○                 | ○                 |

|                                | ・コンプレッサモータのインバータ制御               |              |                   | ○                 |

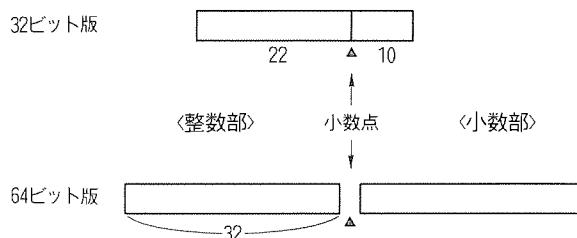

ログラム(一般にソフトサーボ方式と呼ばれている)で、きめ細かい制御が可能なサーボを実現させることにより、操作性の向上を図り、また再生画像の画質改善を果たす。今後更に、モータやメカの精度のばらつきの自動調整ができるようになると、目指す一つの方向である。また、図15に示すように16ビット化したことにより、ビット幅拡大によって演算が高速化され、従来二つのマイコンと一つのLSI(サーボ)を一つのマイコンで実現することも可能にしている。

エアコンでも、16ビット化による演算の高速化により、モータのインバータ制御を実現した。このことにより、冷房及び暖房能力をリニアに可変することが可能になり、設定温度と実際に制御された温度差の時間的な振幅幅が小さくでき快適性を増すことになる。また、省エネルギーと低雑音といった特性改善もこのインバータ制御は可能にした。

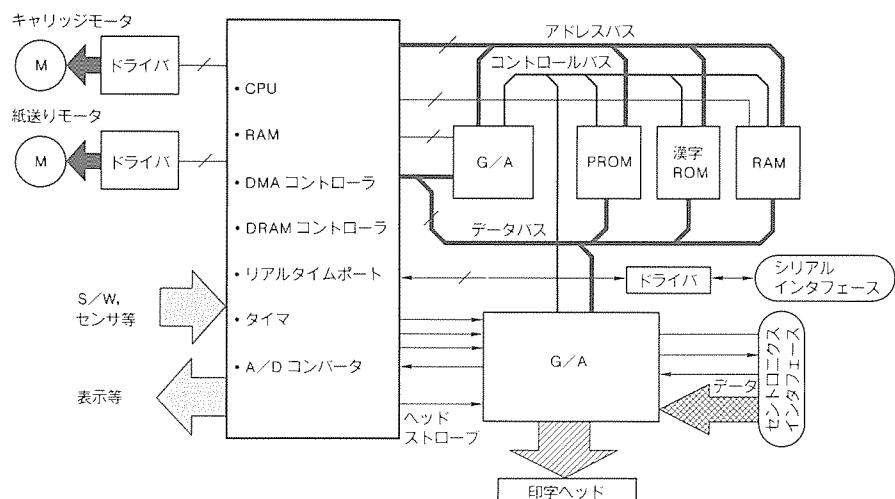

OA、産業機器では、8ビットMCUから16ビットMCUへの移行が激しい。プリンタ、ファックス、HDDなどにおいては現在の半導体技術では、MCUの内に取り込めない大容量メモリを必要とするものが主流になりつつある。これらのマイコンはプログラムメモリや大規模データメモリを外付けとし、必要なRAMとDMAコントロール、DRAMコントロール、リアルタイム出力、タイマ、A/Dコンバータなどの附加機能を内蔵する。

これらの一例として、プリンタへの16ビットマイコンの応用例を図16に示す。このようなOA、産業機器用のマイコンは、16ビットマイコンへ移

図15. VTRへの16ビットマイコン応用例

図16. 16ビットマイコン M37720S1によるシリアルプリンタへの応用例

行しプログラムメモリを外付けにした。

## 4. むすび

この特集号では、近未来のデバイス技術、新製品、要素技術に分け掲載している。

先端デバイスではメモリ関連では64M DRAMを例にとってキー技術を紹介し、それに関係する要素技術として膜形成技術やリゾグラフィ技術の近況や今後の課題について詳述した。今後急速な成長が期待されるフラッシュメモリについては開発動向と当社の取組みを紹介した。新製品の稿ではマイクロプロセッサの高速化が進むなかでメモリとの速度ギャップが顕著になっているが、当社高速SRAMの技術を紹介するとともに特殊モード付きのマスクROMの開発を紹介している。今後も応用製品の多様化が進むなかで、多ビット化や低電圧化、低消費電力化に対応した新製品を述べた。

一方、マイクロコンピュータでは今後期待される非ノイマ

ン型コンピュータである、ニューロチップやデータ駆動型プロセッサを紹介し今後の開発動向と応用動向について述べた。新製品の稿では32ビットプロセッサの製品展開やその応用技術について述べた。16ビットマイコンについて応用製品の多機能化にこたえて用途別に展開を進めている幾つかの新製品を紹介した。また、半導体事業におけるソフトウェア技術、応用技術についても記述した。

要素技術として先端デバイスの信頼性評価技術やパッケージ技術も重要な項目であり、当社開発の極薄型パッケージの技術紹介をした。また生産面においては、受注から納品にまたがる情報ネットワークの構築と最先端工場における生産システムを採り上げた。

これら先端諸技術を結集することにより、顧客のニーズに今後ともこたえていきたいと考えている。読者の参考になれば幸いである。

# 64M ビット DRAM 技術

宮本博司\* 蜂須賀敦司\*

諸岡毅一\* 有馬秀明\*

## 1. まえがき

ダイナミック RAM (DRAM) は高度情報化社会を支えるキーデバイスとして、さらに他の LSI のテクノロジードライバとして、ほぼ3年で4倍のペースで高集積化が進んできた。現在、4 M ビット DRAM が量産され、16 M ビット DRAM がサンプル出荷の段階にある。当社もこれまでの各世代の DRAM の開発で、表1に代表される数々の技術を開発してきた<sup>(1)~(5)</sup>。この間、DRAM の設計ルールは 4 M DRAM でサブミクロ領域に入り、16 M DRAM ではハーフミクロ領域に達しており、64 M DRAM ではサブハーフミクロとなる。このような DRAM の開発の流れの中で、今回、より高集積かつ高性能な 64 M DRAM の実現に必要な技術を開発した。

本稿では、今回開発した 64 M DRAM 技術について述べるとともに、これらの技術を検証する目的で試作した 64 M DRAM チップの特性について紹介する。

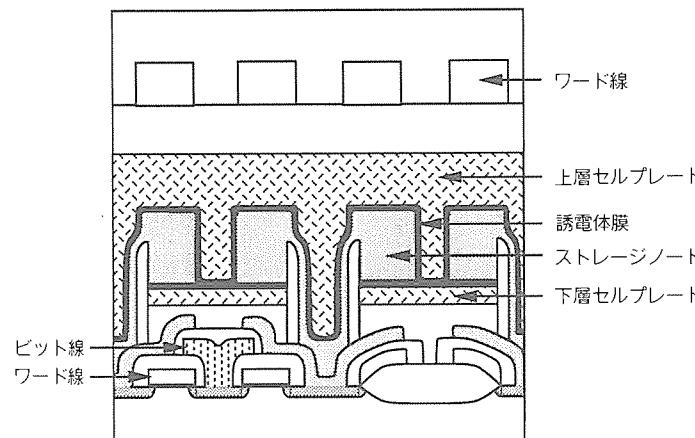

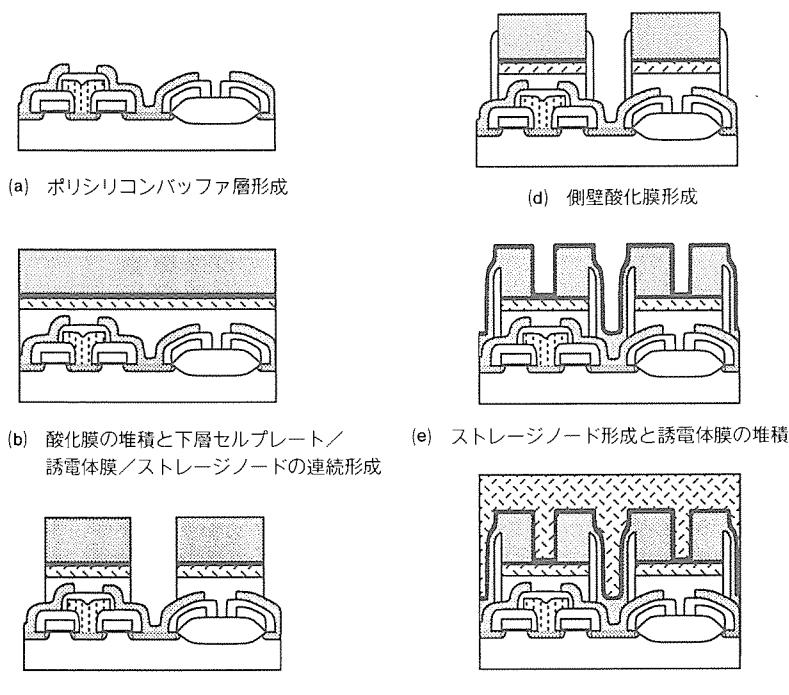

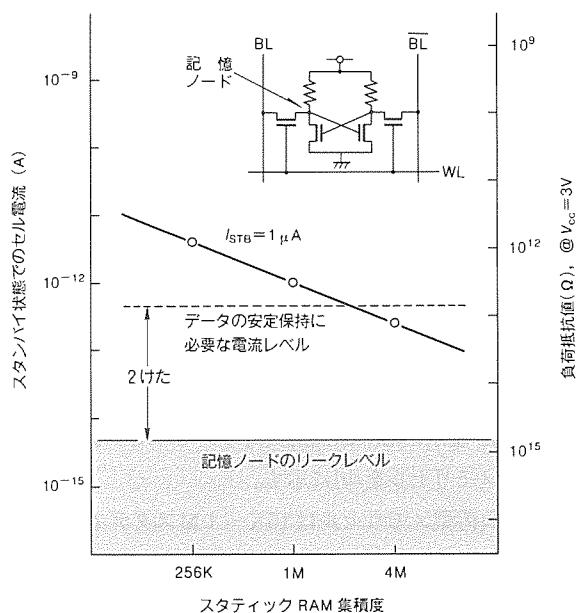

## 2. メモリセル技術

図1に今回開発した DCP (Dual Cell Plate, 2層セルプレート) セルと名付けた新しいスタック型メモリセル<sup>(6)</sup>の断面模式を示す。シールドビット線構造を採用して、キャパシタをビット線上にも形成することにより、メモリセル1ビット当たりのストレージノードの平面投影面積をリソグラフィーの限界まで拡大した。DCP セルの特徴は、セルプレートが上下2層のポリシリコンで形成されている点にある。上層セルプレートは、ストレージノードの上面と外側面及びコンタクト部の内面においてキャパシタを形成する。一方、下層セルプレートはストレージノードの下面をキャパシタとして利用可能にしている。上下2層のセルプレートは、メモリセルアレーの外部で互いに接続される。上下2層のセルプレートによってストレージノードを三次元的に包み込むこと

により、DCP セルでは通常のスタック型セルに比べて大幅にセル容量を増大させることができた。

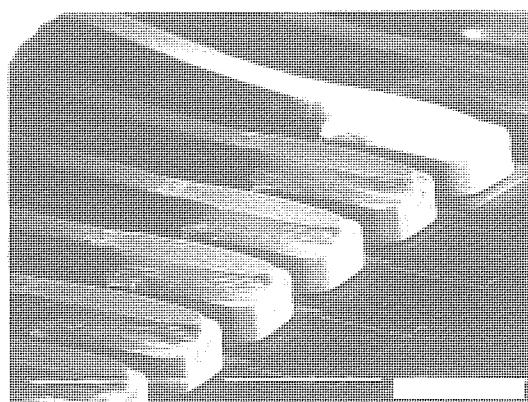

図2に DCP セルの主要なプロセスフローを示す。ワード線及びビット線形成後、コンタクトホールを開孔してポリシリコンバッファ層を形成する(図2(a))。次に酸化膜をたい(堆)積し、表面を平たん化する。下層セルプレートとなるポリシリコン、第1キャパシタ誘電体膜及びストレージノード ポリシリコンを連続して堆積する(図2(b))。この複合膜にポリシリコンバッファ層に達するコンタクトホールを開孔する(図2(c))。酸化膜を堆積後、コンタクトホール内壁に側壁酸化膜を形成し、下層セルプレートと次に形成するストレージノードとを絶縁する(図2(d))。ポリシリコンを堆積してポリシリコンバッファ層とストレージノードを接続する。ストレージノードをエッチング加工した後、第2の誘電体膜を形成する(図2(e))。上層セルプレートとなるポリシリコンを堆積する(図2(f))。コンタクトホール部分と隣接セルとの分離領域は上層セルプレートを形成するポリシリコンで埋め込まれる。図3に試作した DCP セルの断面 SEM 写真を示す。

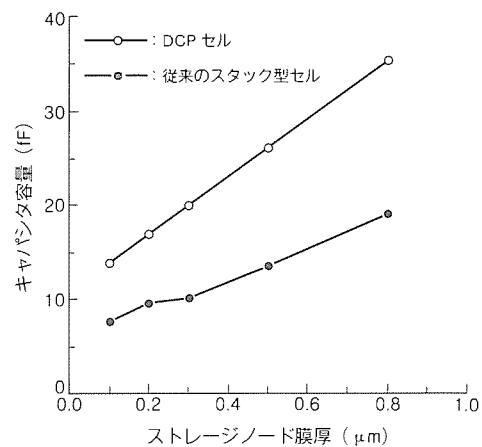

図4は DCP セルと通常のスタック型セルにおいてキャパシタ容量のストレージノード膜厚依存性を計算した結果である。ストレージノード膜を厚くすると外側面及びコンタクト部の内面の容量が増えるため、全体の容量が増加する。図から、DCP セルによれば通常のスタック型セルの約2倍のキャパシタ容量が得られることが分かる。DCP セルにおいてストレージノード膜厚 0.5 μm のとき、メモリセルサイズが 1.3 μm<sup>2</sup> あってもキャパシタ容量 26 fF が得られる。

## 3. 高速化・テスト時間短縮化回路技術

アクセス時間の高速化は、DRAM の設計において常に重要な要素である。一方、DRAM の高集積化に伴って DRAM のテスト時間の増大が問題となってきた。64 M DRAM では

表1. DRAM 各世代における主な技術開発項目

| DRAM 世代     | 1M                                   | 4M      | 16M           | 64M                               |

|-------------|--------------------------------------|---------|---------------|-----------------------------------|

| 新<br>技<br>術 | プロセス技術<br>CMOS プロセス                  | スタック型セル | 改良スタック型<br>セル | DCP(Dual Cell<br>Plate) セル        |

|             | 設計技術<br>高速ページモード<br>スタティック<br>コラムモード | テストモード  | 内部降圧回路        | マージド マッチ<br>ラインテスト方式<br>カスケード冗長方式 |

高速アクセス時間とテスト時間の短縮を両立させる回路技術が必要になる。

## 3.1 マージド マッチラインテスト方式

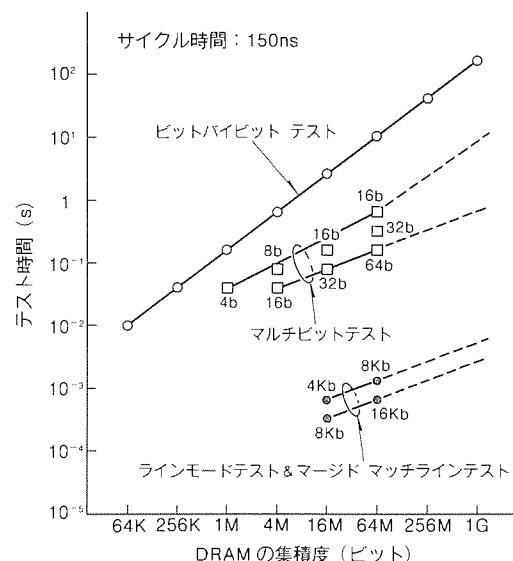

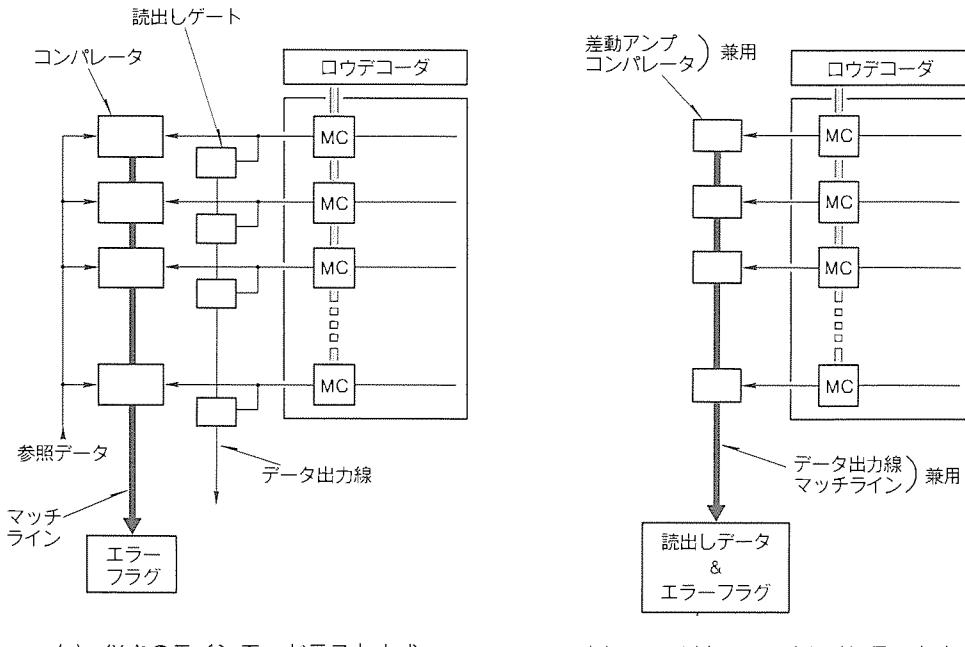

図5にDRAM各世代に対するテスト時間を示す。1ビットごとにテストするビットバイビット テストでは64M DRAMの全ビットを1回読み出すだけで10s(サイクル時間150ns時)かかる。このテスト時間の増大に対処するために、複数ビットを同時にテストするマルチビットテスト(MBT)方式が提案され、4M DRAM等で実用化されているが、並列テストビット数が4~64ビットであるため大幅なテスト時間の短縮はできない。そこで、1ワード線分(数Kビット)を一括してテストするラインモードテスト(LMT)方式が提案されている。しかし、従来のLMT方式では図6(a)に示すように読み出しデータと期待値とのコンパレータが各ビット

図3. DCPセルの断面 SEM写真

図1. DCPセルの断面模式図

図2. DCPセルのプロセスフロー

図4. キャパシタ容量のストレージノード

ポリシリコン膜厚依存性の計算結果

(メモリセルサイズ $1.3\mu\text{m}^2$ 、誘電体

膜は5nmのONO膜を仮定)

図5. DRAM各世代に対するテスト時間

(全ビットを1回読み出すのに要する時間)

図 6. 従来の LMT 方式と MMT 方式の比較

ト線対ごとに必要になるほか、LMT 方式専用のマッチラインや参照データを与える配線が必要となり、チップ面積の増大を回避することが困難であった。

今回開発したマージド マッチラインテスト (MMT) 方式では、図 6(b)のように通常の読み出し動作時にデータ出力線として使用される配線をテストモード時にはマッチラインとして使用し、さらに通常の読み出し動作時に差動アンプとして動作する回路をテストモード時には Wired OR 回路 (一種のコンパレータ) として動作させることにより、チップ面積の増大を 0.1 % 以下に抑えた<sup>(7)</sup>。

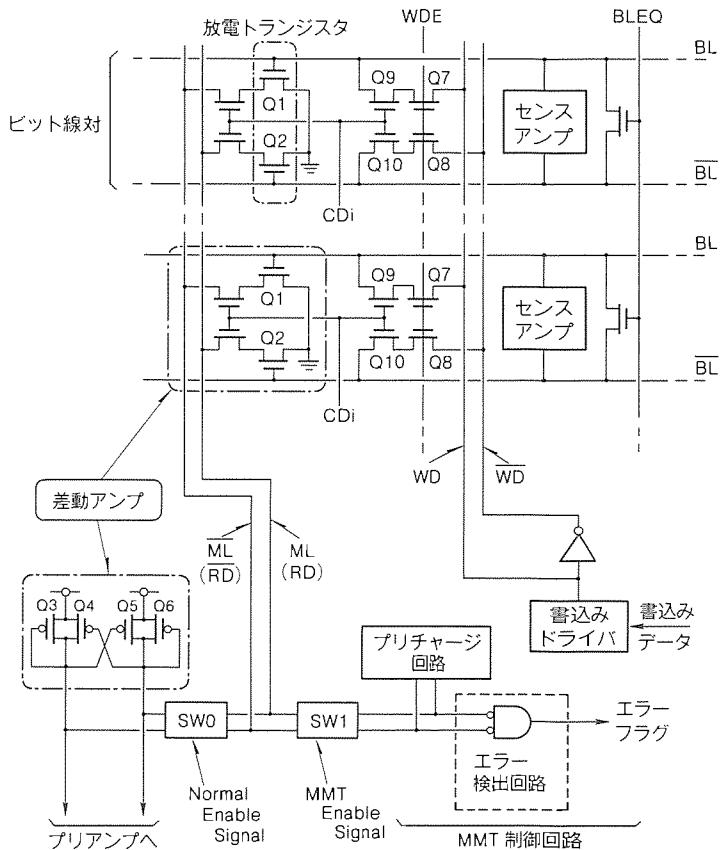

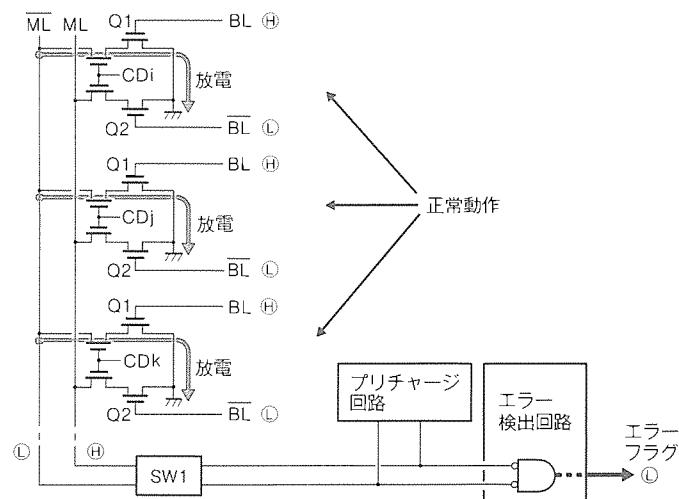

MMT 方式の詳細な構成を図 7 に示す。データ入力線対 ( $WD, \overline{WD}$ ) とデータ出力線対 ( $RD, \overline{RD}$ ) とは分離され、コラム選択線 ( $CD_i, CD_j, \dots$ ) がビット線対 ( $BL, \overline{BL}$ ) を選択する。NMOS トランジスタ  $Q_1$  及び  $Q_2$  とスイッチ  $SW_0$  を通して接続される PMOS プルアップトランジスタ  $Q_3 \sim Q_6$  によって差動アンプが構成され、通常の読み出しに使用される。一方、テストモード読み出しのためにスイッチ  $SW_1$  を通してマッチライン対 ( $ML, \overline{ML}$ ) を、電源電位  $V_{cc}$  レベルにプリチャージするプリチャージ回路及び読み出しだけの一致／不一致を検出して、エラーフラグを発生するエラーチェック回路が設けられている。 $WDE$  は書き込み時に活性化される信号であり、データ入力線 ( $WD, \overline{WD}$ ) からトランジスタ  $Q_7 \sim Q_{10}$  を通して書き込みデータをビット線対に伝達する。

### 3.2 アクセス時間の高速化

MMT 方式における通常の読み出し動作の場合には、図 7

図 7. MMT 方式の構成

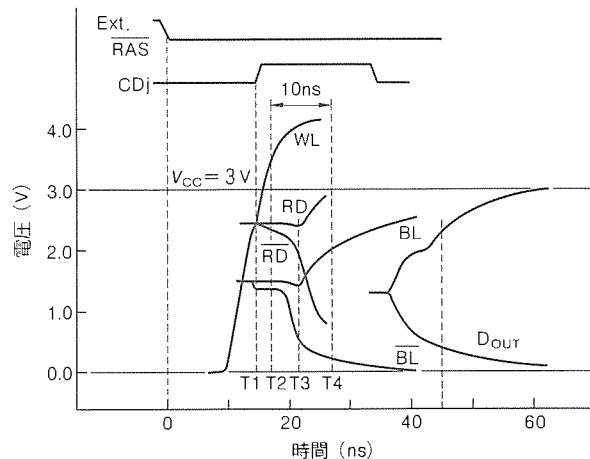

においてスイッチ  $SW_0$  がオン、 $SW_1$  がオフになる。コラム選択線によって所望のビット線対が選択されると、トランジスタ  $Q_1, Q_2$  及び  $Q_3 \sim Q_6$  によって差動アンプが形成される。図 8 に通常読み出し動作の回路シミュレーション波形を示す。時刻  $T_1$  にワード線 (WL) が立ち上がってメモリセル

のデータがビット線に現れると、ビット線対間の電位差はトランジスタ Q1 と Q2 のゲートに伝達される。時刻 T1 とほぼ同時にコラム選択線 (CDj) が立ち上がり、差動アンプが活性化され始めるため、時刻 T2 にはデータ出力線対 (RD, RD̄) に電位差が現れ始める。次に、時刻 T3 にセンスアンプが活性化され、ビット線対の電位差が増幅され始めると、データ出力線対の電位差も更に増大していく。これに対し、データ入力線とデータ出力線が共通である従来の I/O コモン方式では、早くコラム選択線を立ち上げるとデータ線とビット線とが干渉して誤動作するため、センスアンプによってビット線対間の電位差を十分増幅した後 (時刻 T4) コラム選択線を立ち上げる必要があった。

MMT 方式ではワード線の立ち上がりとほぼ同時に差動アンプを活性化できるため、従来の I/O コモン方式に比べて 10 ns 速い (シミュレーション値) RAS アクセス時間を得ることができ、アクセス時間の高速化に寄与する。

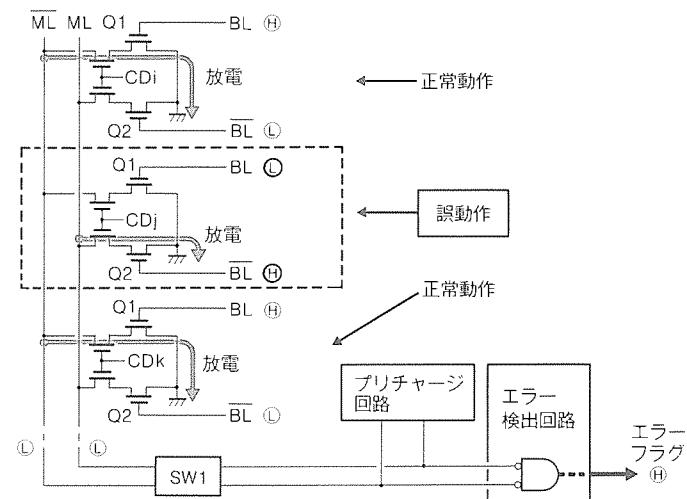

### 3.3 MMT 方式におけるテストモード動作

テストモード読出し時には図 7 の各コラムのトランジスタ Q1 と Q2 がマッチライン対 ML, ML̄ によって Wired OR 接続されコンパレータの役割を果たす。したがって、テストモード時には通常動作時と異なり、コラム選択線活性化のタイミングを、ビット線対間に十分な電位差が生じる時刻 T4 まで遅延させている。

図 9 にエラーがない場合のテストモード読出し動作を示す。テストモードがセットされると図 7 におけるスイッチ SW0 がオフで、スイッチ SW1 がオンの状態になる。これにより、マッチライン対 (ML, ML̄) はプリチャージ回路によって RAS が “H” レベルの期間に  $V_{cc}$  レベルにプリチャージされる。ここで、あらかじめ 1 本のワード線につながる 512 ビットのメモリセルには “0” または “1” の同一データを書き込んでいる (ここでは BL が “H”, BL̄ が “L” になる)。次に、RAS が立ち下がる時点からテストモードによる読出しサイクルが開始される。ワード線が立ち上がってメモリセルのデータがビット線に現れ、さらにセンスアンプが活性化されてビット線対間の電位差が十分に増幅された時点 (図 8 の時刻 T4) に、512 ビット分のコラム選択線が全部立ち上がる。これにより、マッチライン ML̄ はトランジスタ Q1 を通して 0 V に放電される。一方、マッチライン ML はトランジスタ Q2 がオフしているので (BL̄ は “L”)  $V_{cc}$  レベルを保持し、NOR 回路で構成されるエラー検出回路はエラーフラグを発生しない。

図 10 はエラーがある場合の動作であり、マッチライン ML̄ は正常動作しているコラム (CDi, CDk) のトランジスタ Q1 を通して 0 V に放電される。一方、マッチライン ML も誤動作しているコラム (CDj) のトランジスタ Q2 を通して (BL̄ は “H”) 0 V に放電され、エラー検出回路はエラーフラグを発生してエラーがあることを検出する。

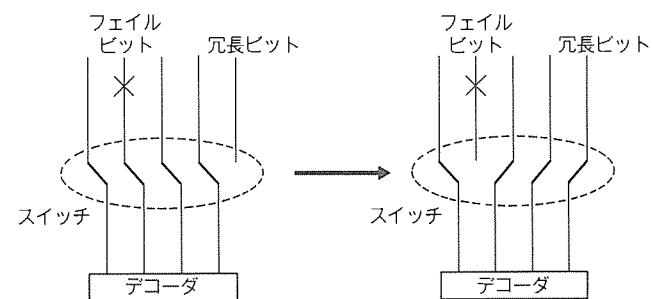

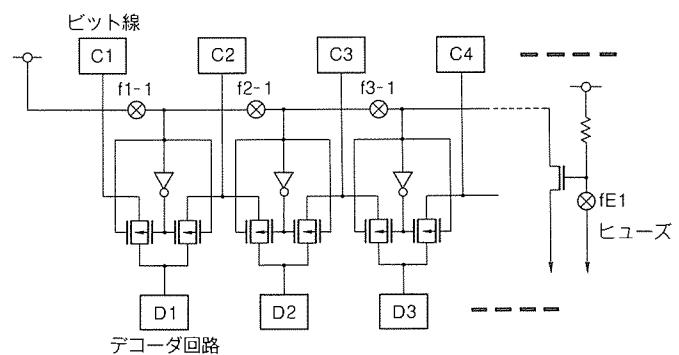

## 4. 冗長回路技術

冗長回路は歩留りを向上させるために今や必ず (須) の手段であるが、MMT 方式に適したコラム冗長方式が必要となる。

図 8 . MMT 方式の通常読出し動作(回路シミュレーション)

図 9 . MMT 方式のテストモード読出し(エラーがない場合)

図10. MMT 方式のテストモード読出し(エラーがある場合)

入力アドレスと不良アドレスとを比較して、一致した場合に不良アドレスに対応したコラムを電気的に不活性にし、スペアコラムを活性化する NED (Normal Element Disable) 方式は広く使用されているが、この NED 方式は MMT 方式には適用できない。すなわち、不良アドレスに対応するコラム選択線は常に非選択であるべきにもかかわらず、MMT 方式では全コラムがマッチライン対によって Wired OR 接続されているため、テストモード読出し時に不良アドレスを含む全コラムが選択されてしまう。

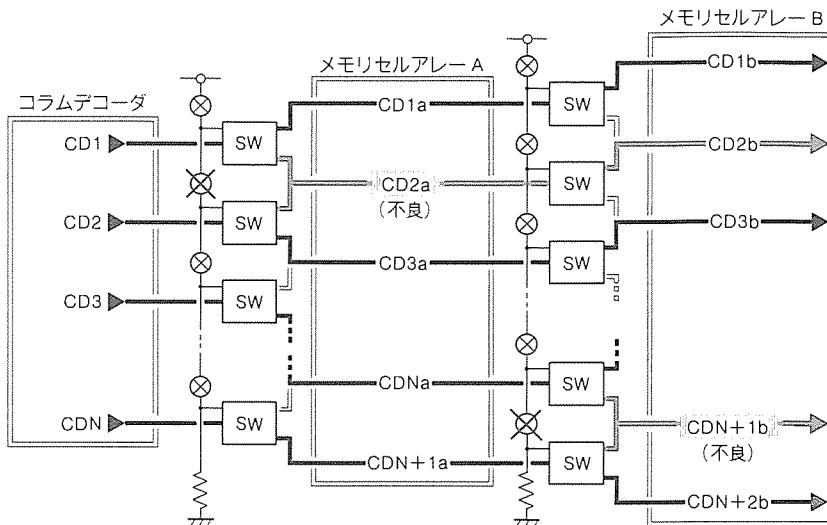

次に、2層金属配線を使用してコラムデコーダをメモリセルアレーの端に配置

し、2層目の金属配線をコラム選択線としてメモリセルアレーの一方の端から他端まで配線する方式がある。この場合、不良を持つコラムとスペアコラムとを置換するとき、従来はメモリセルアレーの左端から右端までそっくり置換していたため、置換されるビット数が多くなり過ぎ冗長回路の効率が悪くなる欠点があった。

以上の問題点を解決し、MMT 方式に適したカスケード冗長方式を開発した。カスケード冗長方式の構成は図11に示すように、コラムデコーダをメモリセルアレーの左端に配置し、第1のスイッチ群をコラムデコーダとメモリセルアレー A の間に、第2のスイッチ群をメモリセルアレー A と B の間に設けている。そしてヒューズのプログラムにより、第1と第2のスイッチ群を切り替えて不良のあるコラムを不活性状態にする。コラムデコーダは  $N (=512)$  本のコラム選択線を持ち、メモリセルアレー A は  $N+1$  本、メモリセルアレー B は  $N+2$  本のコラム選択線を持っている。第1のスイッチ群により、メモリセルアレー A 内の不良コラム 1 本を不活性状態にする。各スイッチは 1 入力 2 出力のマルチプレクサであり、出力の選択をヒューズによって行う。同様に、第2のスイッチ群により、メモリセルアレー B 内の不良コラム 1 本を不活性状態にする。図ではコラム CD 2 a 及びコラム CDN + 1 b に不良がある場合を示している。カスケード冗長方式ではヒューズによってコラム選択線の接続を変更しており、アクセス時間の遅延は生じない。

## 5. 64 M DRAMへの応用

以上述べた技術を用いて試作した 64 M DRAM のチップ写真を図12 に示す。チップは  $0.4 \mu\text{m}$  CMOS 技術で製作されている。表2 にプロセス技術をまとめて示す。チップ構成は、16M ビットごとに独立に制御回路を設けており、通常 4 個のうち 1 個の制御回路が活性化される。メモリセルアレーは全体の  $1/16$  の部分が同時に活性化される。メモリセルア

図11. カスケード冗長方式の構成

図12. 64M DRAM のチップ写真

表2. 64M DRAM のプロセス技術

|        |                                                                                      |

|--------|--------------------------------------------------------------------------------------|

| プロセス   | $0.4 \mu\text{m}$ CMOS, 2層メタル                                                        |

| 設計基準   | $0.4 \mu\text{m}$ (最小)                                                               |

| トランジスタ | $L=0.4 \mu\text{m}$ (NMOS), $0.5 \mu\text{m}$ (PMOS)<br>$T_{\text{ox}}=12 \text{nm}$ |

| メモリセル  | DCP セル, セル容量 $30 \text{fF}$                                                          |

レーだけでなく制御回路も含めた分割動作を行うこと、及び電源電圧の低電圧化 ( $3.3 \text{V}$ ) によってチップ全体の低消費電力化を図っている。MMT 方式により、1 対のマッチラインから 512 ビット分のデータを一括して読み出すことができる所以、チップ全体として 16K ビットが一括してテストできる。したがって、64 M ビット全体の 1 回の読出し時間は  $614 \mu\text{s}$  (サイクル時間  $150 \text{ns}$  時) となり、ビットバイビットテストの  $1/16,000$  になる。表3 にチップ諸元をまとめた。RAS アクセス時間は  $45 \text{ns}$  であり、動作電源電流は  $160 \text{mA}$  であった。

表3. 64M DRAMのチップ諸元

|            |                                                         |

|------------|---------------------------------------------------------|

| 構成         | 64M語×1ビット／16M語×4ビット                                     |

| チップサイズ     | 12.5×18.7=233.8mm <sup>2</sup>                          |

| セルサイズ      | 1.0×1.7=1.7μm <sup>2</sup>                              |

| 電源電圧       | 3.3V                                                    |

| アクセス時間     | $t_{RAC}=45\text{ns}$ ( $V_{CC}=3.0\text{V}$ , 室温)      |

| 動作電源電流     | 160mA ( $V_{CC}=3.3\text{V}$ , $t_{cyc}=120\text{ns}$ ) |

| リフレッシュサイクル | 4,096サイクル／64ms                                          |

| 冗長回路       | 128ロウ／32コラム(レザプロウ)                                      |

## 6. むすび

64M DRAMを実現するための技術を開発した。メモリセル技術として、ストレージノードを上下2層のセルプレートで包み込むことにより、セル容量を増大させたDCPセルを開発した。また、回路技術として、高速アクセス時間とテスト時間の短縮を同時に実現するDRAMアーキテクチャであるマージドマッチラインテスト(MMT)方式、及びMMT方式に適合した冗長方式であるカスケード冗長方式を開発した。さらに、これらの技術によって64M DRAMを試作し、メモリセルアレーのみならず制御回路も分割動作させること、及び電源電圧の低電圧化(3.3V)によって低消費電力化を図るとともに、45nsの高速アクセス時間を実現した。MMT方式によれば64M DRAMのテスト時間を1ビットごとのテストの1/16,000にすることが可能であり、MMT方式を搭載するために必要なチップ面積の増大は0.1%以下と、実用的見地からも有効な方式である。

以上、今回開発した技術により、高集積かつ高性能の64M DRAMが実現できることを示した。

今後、更に技術開発を進め、より高性能な64M DRAMを開発していく。

## 参考文献

- (1) 山田通裕、佐藤真一、古田 熊、尾崎英之、長山安治：CMOS 1Mビット ダイナミックRAM、三菱電機技報、61, No. 7, 581～584 (1987)

- (2) 長山安治、宮武秀司、熊野谷正樹、古田 熊、水津克巳：第二世代1Mビット ダイナミック CMOS RAM、三菱電機技報、62, No. 7, 628～633 (1988)

- (3) 宮本博司、長友正男、山田通裕、長山安治、水津克巳：4Mビット ダイナミック RAM、三菱電機技報、63, No. 11, 891～894 (1989)

- (4) 熊野谷正樹、飛田洋一、長友正男：第二世代4Mビット DRAM、三菱電機技報、65, No. 7, 697～702 (1991)

- (5) 松田吉雄、若宮 亘、有本和民、藤島一康、佐藤真一：16Mビット ダイナミック RAM、三菱電機技報、63, No. 8, 681～685 (1989)

- (6) Arima, H., Hachisuka, A., Ogawa, T., Okumura, Y., Matsui, Y., Motonami, K., Matsukawa, T., Tsubouchi, N. : A Novel Stacked Capacitor Cell with Dual Cell Plate for 64Mb DRAMs, IEDM Tech. Dig., 651～654 (1990)

- (7) Mori, S., Miyamoto, H., Morooka, Y., Kikuda, S., Suwa, M., Kinoshita, M., Hachisuka, A., Arima, H., Yamada, M., Yoshihara, T., Kayano, S. : A 45ns 64Mb DRAM with a Merged Match-line Test Architecture, ISSCC Dig. Tech. Papers, 110～111 (1991)

# 16Mビット フラッシュメモリ技術

寺田 康\* 小林真一\*\*

味香夏夫\* 宮脇好和\*\*

中山武志\*\*

## 1. まえがき

フラッシュメモリは、EEPROM<sup>(注1)</sup>の電気的書換え機能をEPROM<sup>(注2)</sup>と同様の集積度で実現しようとしたものであり、近年最も盛んに開発が行われている不揮発性メモリである。5V単一電源で動作し、バイト単位の書換えが可能なEEPROMに比べると機能は劣り、消去／書込みに高電圧源が必要で、消去単位はチップ若しくはブロックであるが、将来、DRAM<sup>(注3)</sup>よりもビット単価が下がると予想され、大きな市場が期待されている。

これまでに各種のメモリセルが提案されているが、現在の開発の中心はEPROMとほぼ同様の構造をしたスタックゲート型と呼ばれるものである。当社でもこのセル構造で1M～16Mビットのフラッシュメモリの製品開発／試作を行っている<sup>(1)(2)</sup>。さらに、5V単一電源動作等の高機能化についても検討を行っている。

この論文では、まず、現在開発中の16Mフラッシュメモリについてその概要を紹介し、大容量フラッシュメモリを実現するための技術的課題を述べる。3章で高機能化を実現するデバイス・回路技術について、すなわち負電圧を利用するにより、5V単一電源での動作及び書換え耐性の向上が実現されること<sup>(3)</sup>並びに低電源電圧動作<sup>(4)</sup>について紹介する。

## 2. 16M フラッシュメモリ

### 2.1 開発課題

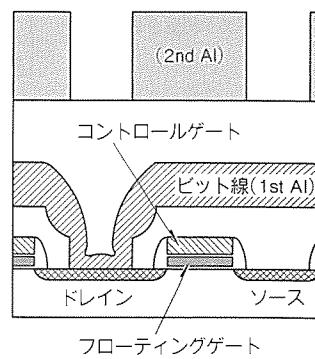

大容量フラッシュメモリの市場としてまず挙げられるのはEPROMの置き換える。このためにはコストをEPROMより下げなくてはならない。そこで、チップサイズを小さくすることを第1の目標として仕様の決定を行った。機能は、1Mのフラッシュメモリと同様であり、2電源一括消去型である。メモリセルとしてスタックゲート型を採用している。断面を図1に示す。書込みはドレイン及びゲートに高電圧を印加し、ホットエレクトロンをフローティングゲートに注入することによって行う。消去はゲートを接地してソースに高電圧を印加し、フローティングゲートから電子を引き抜くこ

とによって行う。書込みによつてしきい値は6V以上になり、消去によつて3V以下に低くなる。読出しは選択されたワード線に電源電圧である5Vを印加し、メモリトランジスタが導通するか否かをセンサアンプで検出することによって行う。このスタックゲート型メモルセルを採用した場合、開発課題として次の事柄が挙げられる。

- (1) 過剰消去の防止

- (2) 消去時間の短縮

- (3) ディスターープの低減

過剰消去とは、フローティングゲートから電子が過剰に引き抜かれ、メモリトランジスタのしきい値が負になってしまうことである。これが起こると、読出し／書込み時に、過剰消去されたセルを介してリーク電流が流れるので同一ビット線上のメモリセルの読出し／書込みが阻害される。次節で過剰消去を防ぐ回路技術について説明する。ディスターープとは読出し／書込み時に選択セルや非選択セルの保持データが破壊されてしまうことである。これはメモリセルが1トランジスタで形成されており選択トランジスタがないため、非選択状態でもゲートやドレインに電圧が印加されるからである。EPROMでも同様の現象が生じるがフローティングゲート－基板間の酸化膜厚が10nmと薄いため、よりディスターープを受けやすい。絶縁膜の膜質を向上させること及びドレンやソースの注入プロファイルを最適化させることによって防いでいる。

### 2.2 消去回路

上述のようにスタックゲート型のメモリセルを採用した場合、最も大きな課題は過剰消去をどのようにして抑えるかということである。もちろん、メモリセル特性のばらつきを抑えるということが必要なわけだが、回路的にも何らかの対策

図1. メモリセル断面

(注1) EEPROM : Electrically Erasable and Programmable Read Only Memory

(注2) EPROM : Electrically Programmable Read Only Memory

(注3) DRAM : Dynamic Random Access Memory

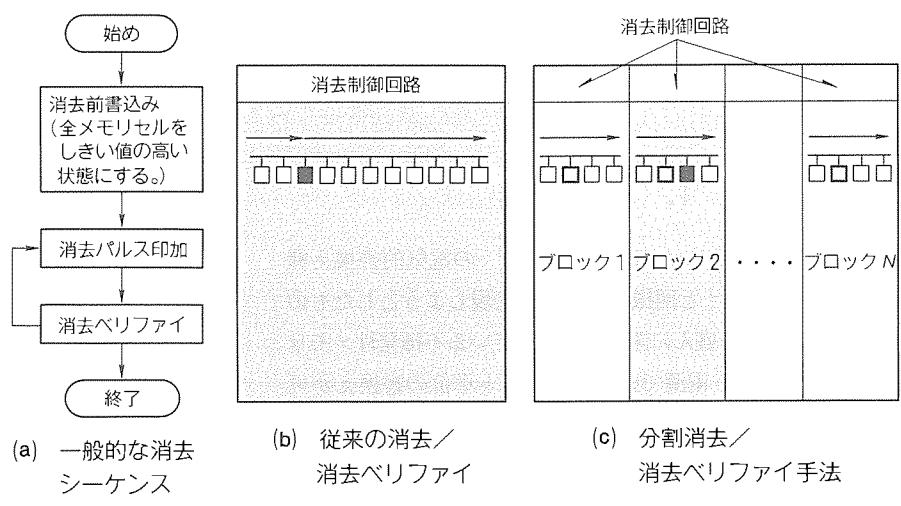

をとることが必要となってくる。一般的に、短い消去パルスを印加し、その後消去ペリファイを行って消去不十分のメモリセルが存在したならば、再度消去パルスを印加するという手法がとられている。また、最初の消去パルスが印加される前にすべてのメモリセルに書き込みがなされる。これを消去前書き込みと呼んでいるが、これは消去状態のメモリセルに消去パルスが印加されるとそのセルが過剰消去してしまうからである。

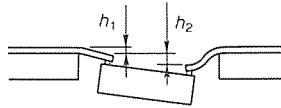

図2(a)に一般的な消去シーケンスを示す。消去パルスの印加は1Mビットのフラッシュメモリでは全メモリセルに同時に行われていたが、容量が大きくなり、メモリアレーの面積が増大するとともにメモリセル特性のばらつきが大きくなることが予想されるので、16Mのアレーを64分割し256Kビットのアレーごとに消去パルス印加／消去ペリファイが行われるように構成した。この場合、消去ペリファイの手法が消去時間に大きな影響を及ぼす。

図2(b)に従来のペリファイ方法を示す。最初の消去パルスの印加後、先頭番地からペリファイが行われ、消去不十分なセルが検出された時点でペリファイを中止し、再度消去パルスを印加する。ペリファイ動作はそのセルから再開する。しかしながら、この手法を分割消去に適用すると、同一のブロック内アドレスに消去不十分のセルが検出されたブロックにのみ同時に消去パルスが印加されることになり、非常に消去の効率が悪くなる。そこで図2(c)に示すように、1本のワード線上のメモリセルについて、すべてペリファイを行った後、消去不十分のセルを含むブロックに消去パルスが印加されるよう構成した。

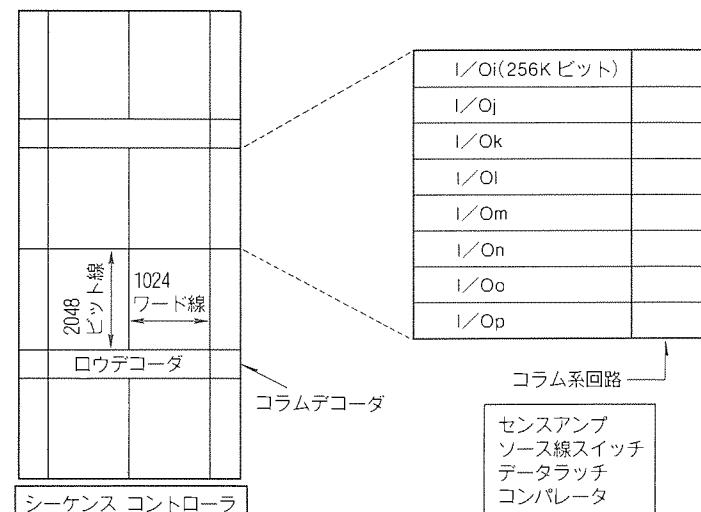

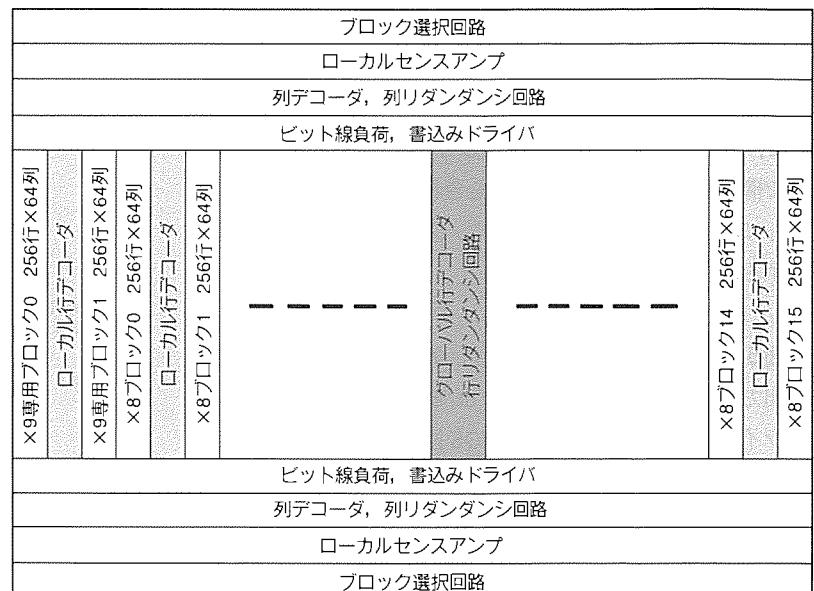

具体的なメモリアレーのブロック図を図3に示す。ロウデコーダにより、四つの4Mブロックに分割されている。各々16のI/Oに対応するメモリセル群に分けられているので、64分割されることになる。1本のビット線には1K個のメモリセルが接続されており、1本のワード線には2K個のメモリセ

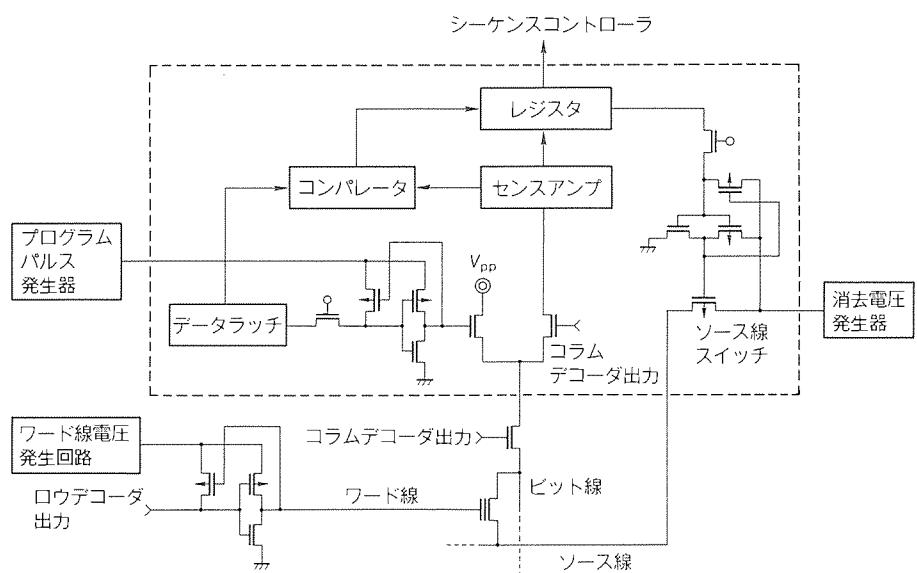

ルが接続されている。64ブロックの各々に消去／消去ペリファイ／書き込み回路が設けられている。構成を図4に示す。センスアンプ、消去パルスの印加の制御を行うソース線スイ

図2. 消去シーケンス

図3. 16M フラッシュメモリのブロック図

図4. コラム系回路

ッチ、書き込みデータをラッチするデータラッチ、ベリファイ動作のためのコンパレータ、レジスタから構成されている。消去前書き込み時にはすべてのデータラッチがセットされ、64のセルに同時に書き込みがなされる。書き込みパルス幅は10μsであり、このときは書き込みベリファイは行われない。

コンパレータは書き込みベリファイ時に活性化される。書き込みが十分なされたと判定されたコラムのデータラッチはリセットされ、過剰な書き込みパルスは印加されない。センサアンプは、高速アクセスを達成するための差動増幅型センサアンプと、ベリファイ動作時に活性化される電流センサ型センサアンプから構成されている。ワード線電圧発生回路は書き込み高電圧、書き込み／消去ベリファイ電圧を発生する。これらの回路により、書き込み／消去時のメモリセルのしきい値のばらつきを抑えることができる。

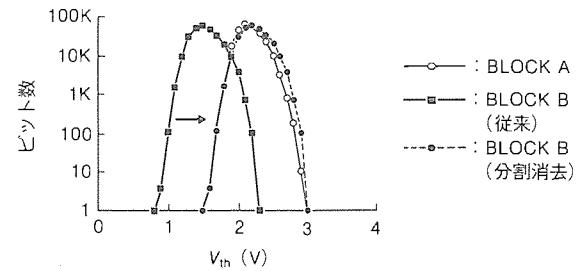

図5に上述の分割消去を行った場合のしきい値の分布についてテストデバイスによる測定結果を示す。2.2Vの分布が分割消去手法により、1.5Vに狭めることができることが分かる。

### 2.3 試作結果

0.6μm CMOS技術を用いて試作を行った。セルサイズは1.8μm×2.0μm、チップサイズは18.4mm×6.5mmである。高速化のために2層Al配線を用いている。消去／書き込み動作はシーケンスコントローラによって制御される。諸特性を表1に、チップ写真を図6に示す。シーケンスコントローラはチップ内部に設けられた発振器によってタイミングが制御される同期式回路で構成されている。トランジスタ数は、ほぼ7,000である。歩留り向上のためレーザプロウにより、プログラムされるリダンダント回路を設けている。過剰消去を防ぐため、スペアロウや置換されたロウに対しても消去前書き込みを行うよう構成した。

## 3. フラッシュメモリの高機能化

### 3.1 5V単一電源動作及び書き換え耐性の向上

スタッガートゲート型フラッシュメモリでは、通常、消去はゲートを接地し、ソースに高電圧を印加して行われる。このと

き、ソース拡散領域がトンネル酸化膜と接する部分で起こるバンド間トンネリングによって生成されるホールが、ソース－基板間の大きな電位差によって加速され、ホットホールとなり酸化膜中に注入されるという現象が生じる。ホットホールが注入されると書き換え耐性が劣化することが知られている。そこで、消去時にゲートに負の高電圧を印加し、ソースの電圧を下げることによってホットホールの生成を抑制することを提案した<sup>(3)</sup>。

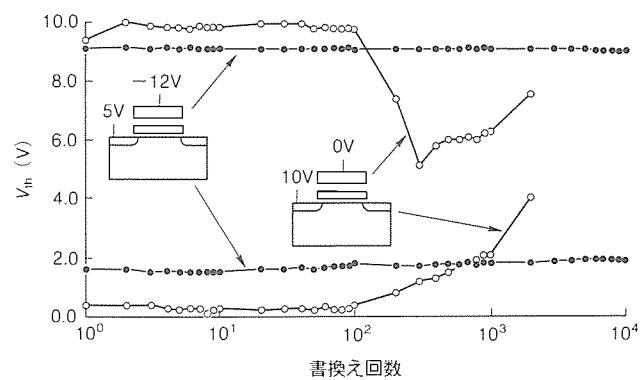

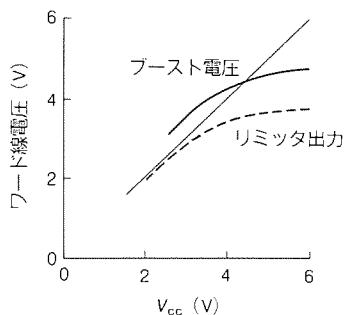

図7に従来法と負電圧利用の場合の書き換え耐性の差を示す。横軸は消去／書き込み回数、縦軸はしきい値である。測定対象のメモリセルは16M対応のセルサイズではあるが、ソースの耐圧を8V程度と低くしたものである。これは、より微

図5. 分割消去による消去しきい値分布特性の改善

(128K テストデバイスによる測定)

表1. 16M フラッシュメモリの諸元

|                 |                                                                   |

|-----------------|-------------------------------------------------------------------|

| プロセス            | 0.6 μm lithography<br>P-sub N-well CMOS<br>2-PolySilicon, 2-Metal |

| 構成              | 2M語×8ビット／<br>1M語×16ビット                                            |

| セルサイズ           | 1.8 μm×2.0 μm                                                     |

| チップサイズ          | 6.5mm×18.4mm                                                      |

| $V_{cc}/V_{pp}$ | 5V/12V                                                            |

| アクセス時間          | 60ns                                                              |

| 書き込み時間          | 1.25 μs/バイト<br>(8バイトのページモード)                                      |

| リダンダント          | 32コラム/8ロウ                                                         |

| パッケージ           | 42ピン DIP                                                          |

図6. チップ写真

細化されたメモリセルの耐圧に相当する。従来の消去手法では書換え回数が100サイクルを越えるとメモリウインドウが狭くなるのが観測されたが、負電圧利用の消去では10,000サイクルでもしきい値の変動がほとんど無い。ゲートすなわちワード線に印加する負電圧は、リークがほとんど無く電流が必要とされないのでチップ上に設けたチャージポンプで発生することができる。また、ソースには $V_{cc}$ を印加すればよいので5V単一電源での消去が可能となる。

さらに、書き込み特性を向上させドレイン電圧を5V以下にすることができるれば、ワード線に印加する高圧は消去時同様チャージポンプで発生が可能なので、5V単一電源での動作が実現される。また、消去時に消去を行いたいワード線に選択的に負の高電圧を印加するように構成すればセクタ消去が可能となる。ただし、この時はディスターブ、特にドレンディスターブについて十分耐性があるよう対策をとることが必要である。

### 3.2 低電圧動作

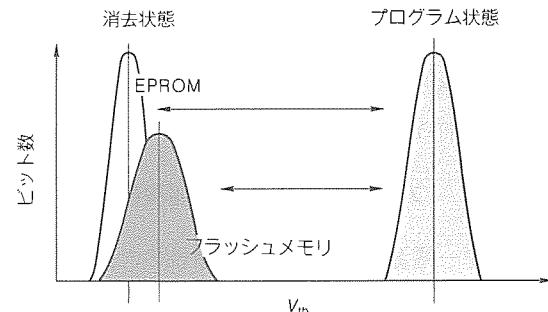

EPROMやフラッシュメモリでは、選択ワード線に電源電圧を印加したときにメモリトランジスタがオンして電流が流れれるか否かを判定して保持されているデータの読み出しを行う。EPROMでは紫外線の照射により、消去が行われるのでフローティングゲートは電気的に中性となり、メモリトランジスタのしきい値の分布は狭いが、フラッシュメモリではトンネル現象を用いてフローティングゲートから電子を引き抜くので、メモリセルパラメータのわずかな変動により、トンネル電流が変動し消去しきい値の広い分布を引き起こす。さらに、過剰消去を防ぐためしきい値の中心値はあまり低くできない。図8にしきい値分布を模式的に示す。

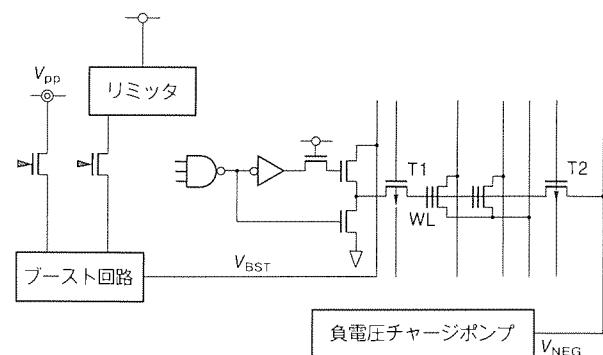

従来のロウデコーダでは選択されたワード線には電源電圧が印加されるため、読み出し時の電源電圧の下限は消去されたメモリトランジスタのしきい値の最大値で決まる。このためフラッシュメモリではEPROMより高くなってしまう。よって、低電圧読み出しを可能とするためにはDRAMで行われているようにワード線電圧をブーストすることが望ましい。しかしながら、電源電圧が高いときにもブーストされると信頼性の問題を引き起こすので、電源電圧が高い場合にはクラシップされることが必要となる。さらに、上述のように消去時にはワード線に負電圧を印加しなければならない。これらの条件を満足するロウデコーダを図9に示す。ロウデコーダ最終段はPチャネルトランジスタで形成され、これに入力される電圧を発生する回路は電圧制限回路とブースト回路から構成されている。負電圧はロウデコーダとは反対側に接続されたPチャネルトランジスタT2を介して印加される。PチャネルトランジスタT1は負電圧がロウデコーダに伝わらないようにするためのものである。このロウデコーダの出力電圧、すなわちワード線電圧のシミュレーション結果を図10に示す。16Mフラッシュメモリに適用した場合についてシミュ

レーションを行ったところ、3Vでも安定な読み出しが可能なことが確認された。

フラッシュメモリの高機能化の他の課題として、消去時間の短縮が挙げられる。消去は2.1節述べたように、消去前書込み／消去パルス印加／消去ベリファイから構成されているが、大容量化に伴い消去前書込みを要する時間が増大する。これは通常の書き込みと同様の書き込みをすべてのメモリセルに対して行うためである。書き込みパルス幅を10μs、8バイトのページモード書き込みをしたとしても16Mチップで2.6sかかる。この問題を解決するためにフラッシュプログラミング手法を開発した。書き込みをホットエレクトロン注入ではなくトンネル現象を用いて全メモリセル同時に行おうとするものである。ただし、スタッガゲート型のメモリセルの容量

図7. ゲート負電圧印加による書換え耐性の向上

図8. しきい値分布

図9. 低電圧動作を可能とするロウデコーダ

図10. ワード線電圧のシミュレーション結果

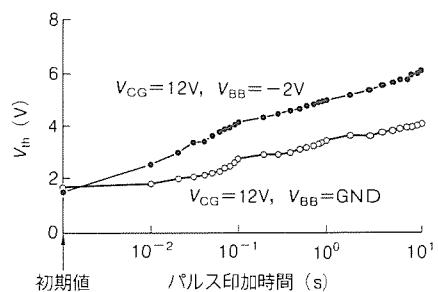

結合比が一般の EEPROM に比べて悪いため、ホットエレクトロン注入に比べて高電圧を印加しなければならない。そこで、基板に負電圧を印加することを検討した。単体メモリセルのトンネル書き込み特性を図11に示す。ゲートに 12V、基板に -2V を印加した場合 500 ms でしきい値が 5V 程度に上昇することが確認された。このフラッシュ プログラミングを用いると消去時間は従来の 1/2 程度に短縮されると見積られる。

#### 4. む す び

以上、フラッシュメモリの大容量化、及び 5V 単一電源化、低電圧動作、高速消去、高書換え耐性という高機能化を実現するデバイス・回路技術について紹介を行ってきた。フラッシュメモリは、EEPROM に比べると機能は劣るがコストが DRAM 以下になる可能性があることから注目を浴びている。市場動向をみながら次世代のフラッシュメモリの仕様を決めていく計画であるが、高機能化によるコスト上昇を最低限に抑えられるよう努力を続けていく予定である。

図11. フラッシュ プログラミング特性

#### 参考文献

- (1) 小林和男、中島盛義、山本 誠、長田隆弘：高速 1M ビット フラッシュ EEPROM, 三菱電機技報, 65, No. 4, 380~384 (1991)

- (2) Nakayama, T., Kobayashi, S., Miyawaki, Y., Terada, Y., Ajika, N., Ohi, M., Arima, H., Matsukawa, T., Yoshihara, T. : A 60ns 16Mb Flash EEPROM with Program and Erase Sequence Controller, ISSCC Digest of Technical Papers, 260~261 (1991)

- (3) Ajika, N., Ohi, M., Arima, H., Matsukawa, T., Tsubouchi, N. : A 5 Volt Only 16M Bit Flash EEPROM Cell with a Simple Stacked Gate Structure, IEDM Technical Digest, 115~118 (1990)

- (4) Miyawaki, Y., Nakayama, T., Kobayashi, S., Ajika, N., Ohi, M., Terada, Y., Arima, H., Yoshihara, T. : A New Erasing and Row Decoding Scheme for Low Supply Voltage Operation 16Mb / 64Mb Flash EEPROMs, Symposium on VLSI Circuit, 85~86 (1991)

# 学習機能付きニューロチップ

有馬 裕\* 前田 敦\*

村崎充弘\* 山田 強\*

## 1. まえがき

近年、計算機の能力進展に伴い、脳の情報処理様式を模倣したニューラルネットワーク（以下“ニューラルネット”という。）のシミュレーションが高速に実行できるようになり、ニューラルネット応用技術の研究開発が活発化してきた。制御、認識、予測など一部の分野では既に実用化されている例もあり、その有用性が認知されつつある。しかし、ニューラルネットの情報処理は高度な分散並列性を特徴としているので、従来の計算機による直列逐次処理に置き換えたエミュレーション手法では処理時間が膨大になってしまう。現状のスーパーコンピュータをもってしても、はえ（蠅）の脳程度のシミュレーションでさえ10倍以上の処理時間を要する。そこで、リアルタイム応用に必要な生体脳並み、又はそれ以上の処理速度を実現するためには、ニューラルネット専用チップ（ニューロチップ）の開発が不可欠である。

ニューロチップには、高速演算処理、大規模回路網の表現に加えてオンチップ学習機能が求められる。ニューラルネットは、それを構成する各ニューロン間の信号伝達効率（シナプス荷重値）を適当に設定することによって、目的の情報処理機構を実現する。したがって、従来のプロセッサに処理手続きを提示するプログラムを与えないければならないように、ニューロチップでは各シナプス荷重値を処理目的に合わせて設定しなければならない。しかし、この値を直接決めることは、その情報分散表現機構により困難である。そこで、ニューラルネットの特徴の一つである自己組織化機能を活用して、ニューロチップ自身が提示された例題を基に各シナプス荷重値を最適化する機能が重要となる。この荷重値の最適化処理がいわゆる学習と呼ばれるものである。従来のプロセッサの汎用性が、プログラム制御方式によって高められたのと同様に、汎用性の高いニューロチップの実現には学習機能の搭載が必要である。

## 2. ニューロチップの概要

高速演算を実現するには、ニューラルネット情報処理方式に準拠して演算処理の並列性を高めることが現実的である。アナログ回路は少ない素子数で演算機能を表現できるため大規模な並列処理回路構成に有効である。そこで、今回開発したニューロチップ<sup>(1)</sup>は、チップ内部の演算処理をアナログ回路で実現する一方、各種装置に組み込みやすくするた

め、チップの制御及び入出力データに関する回路をデジタル回路で構成する方法を採用した。このアナログ・デジタル混在回路設計によってオンチップ学習機能を備えた300ニューロンを越える規模のニューロチップが実現でき、スーパーコンピュータより4けた以上の高速処理を可能とした。また、このチップは並列回路が非同期で動作する。

大規模な非同期並列処理能力を発揮するため、このチップは時分割処理では効率良く表現できない相互結合型ニューラルネットモデルの一つである完全フィードバック結合のボルツマンマシン<sup>(2)</sup>を基本構造としている。ボルツマンマシンは、ニューロンの状態が確率的に遷移することを特徴としており、ニューラルネットの状態がポテンシャルエネルギーの極小値にトラップされ難く、大局的な極小値（良好な解に対応）に収束しやすい性質を持っている。また、対称なシナプス結合の条件によって振動解（リミットサイクル）の発生を防ぐことができ、効率的な学習、想起が実行できる利点を持っている。

## 3. ニューロチップの学習機能

学習機能を半導体チップ上に実現することは、学習過程が高速に実現できるという直接的な利点だけではなく、チップの自己補償機能を実現する。つまり、チップ内の素子パラメータのばらつきやプロセス変動によるシフト、又は部分的素子不良などの不良因子は、自己組織化によってある程度吸収される。したがって、学習機能を備えたニューロチップは、製造歩留りの悪化を回避するために必要とされる設計上の制約や製造工程での様々な制限が大幅に緩和されることになり、製造コストを低減することができる。

### 3.1 学習機能付きシナプス回路

オンチップ学習を高速に行い、自己補償機能を有効に実現するためには、各シナプスごとに学習機能を設けることが望ましい。一方、シナプスはニューロチップの最大構成要素であり、シナプス回路のサイズがニューロチップの集積度に最も強く影響する。そこで、シナプス回路を極力小さくするために、シナプス結合演算をアナログ回路で表現し、学習制御機能を簡単なデジタル論理回路で実現した。アナログ回路は素子特性のばらつきが演算精度に直接影響を及ぼすので高い精度を実現しにくいといった問題があったが、各シナプス回路ごとの学習機能で実現される自己組織化によって、この問題が解決されている。

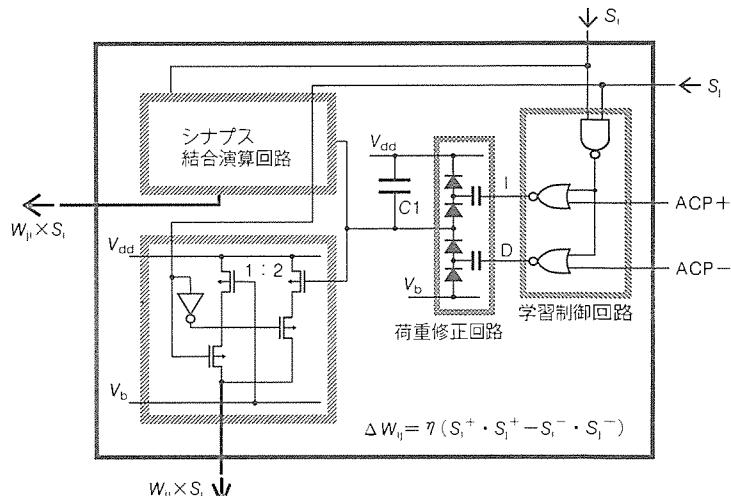

図1にシナプスユニットの回路を示す。対称な結合を効率良く表現するために、一つのユニットで双方向の結合を表現できる構成になっている。シナプス荷重値は、キャパシタC1に蓄えられた電荷量で表現し、二つのシナプス結合演算回路は、C1の蓄積電荷量に比例して生じる電圧に規定される電流量（荷重化出力信号、 $W_{ij} \times S_i$ 、 $W_{ji} \times S_j$ ）を出力する。C1の蓄積電荷量は、荷重修正回路によって修正される。荷重修正回路は、学習則に従って荷重値を修正するように学習制御回路によって制御される。全シナプスユニットに共通な学習制御信号ACP+、ACP-は、非学習時には共に“High”レベルに固定されており、学習時には+フェーズではACP+に、-フェーズではACP-にそれぞれ負のパルス信号が与えられる。+フェーズは人間の覚せい（醒）時、-フェーズは睡眠時に例えられ、それぞれ与えられた教師パターンの記憶を深める操作と不要な記憶を忘れる操作に対応している。これによって、ボルツマンマシンの学習則<sup>(2)</sup>の平均場近似  $|\Delta W_{ij}| = \eta \cdot (S_i^+ \cdot S_j^+ - S_i^- \cdot S_j^-)|$  が実現できる。ここで、 $\Delta W_{ij}$ は荷重値の修正量で、 $\eta$ は学習係数で各ACPに与えるパルス数又はパルス幅によって変化させることができる。シナプス荷重値は5ビット以上（32階調以上）の分解能を持っている。学習機能を備えたシナプスユニットは、このアナログ・ディジタル混在回路設計によって  $70\text{ }\mu\text{m} \times 70\text{ }\mu\text{m}$  のセル面積で実現できた。

### 3.2 学習モード付きニューロン回路

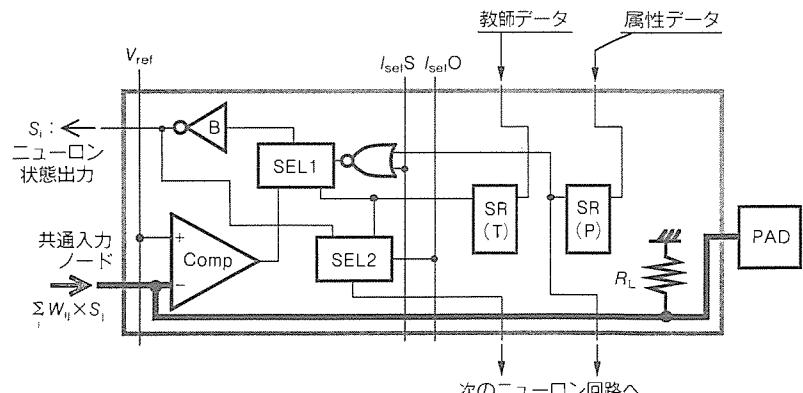

図2にニューロンユニットの回路を示す。シナプスユニットからの出力電流（荷重化出力信号）が太線で示した入力共通ノードで足し合わされ（キルヒホフアダ），抵抗 $R_L$ によって電圧に変換されてコンパレータCompに入力される。Compの他方の入力端子には、チップ外部から基準電圧 $V_{ref}$ が与えられる。 $V_{ref}$ はニューロンのしきい値を表現する。Compの出力は、ニューロンの内部活性値に対応した状態を表す。ボルツマンマシンのシミュレーテッドアニーリングは、 $V_{ref}$ を減衰振動させることで擬似的に実現できる。

シフトレジスタSR(T)には、このニューロンの教師パターンデータが格納され、SR(P)には、このニューロンの属性（隠れ又は入力・出力）データが格納される。NORゲートとセレクタSEL1は、このニューロンの状態出力を制御する。すなわち、SR(P)に格納された属性データと制御信号 $I_{selS}$ とに従って、表1に示すように、このニューロンの状態出力 $S_i$ には、内部活性値による状態が教師データかが出力される。この構成によって、各ニューロンご

とに任意の属性と教師データを設定できる。なお、 $I_{selS}$ は、42ニューロンごとに共通で、この単位で入力か出力ニューロンかが区別される。

教師パターンを各ニューロンのSR(T)に格納した後、シナプスの学習制御信号ACP+、ACP-とニューロンの制御信号 $I_{selO}$ を、学習フェーズに従って操作することによって、ニューロンチップは与えられた教師パターンを学習する。教師パターンを変えて、この操作を繰り返すことによって、チップの記憶（学習したパターンの）は深められる。

SEL2は、各ニューロンの状態をモニタするのに使われる。すべてのニューロン状態は、制御信号 $I_{selO}$ に従って、同時に次のニューロンユニットのSR(T)に格納された後、通常のシフトアウト動作によってチップ外部に出力することができる。太線に接続された信号端子PADは、ニューロンの内部活性値モニタ用、又は回路網の拡張時にチップ間接続端子として用いられる。

## 4. 大規模回路網の実現手法

一般にニューラルネットは、それを構成するニューロンとシナプスの規模に伴って能力が増大する。したがって、より

図1. シナプス回路

図2. ニューロン回路(BNU)

大規模な回路網を実現するために、マルチチップ接続手段は重要な技術である。

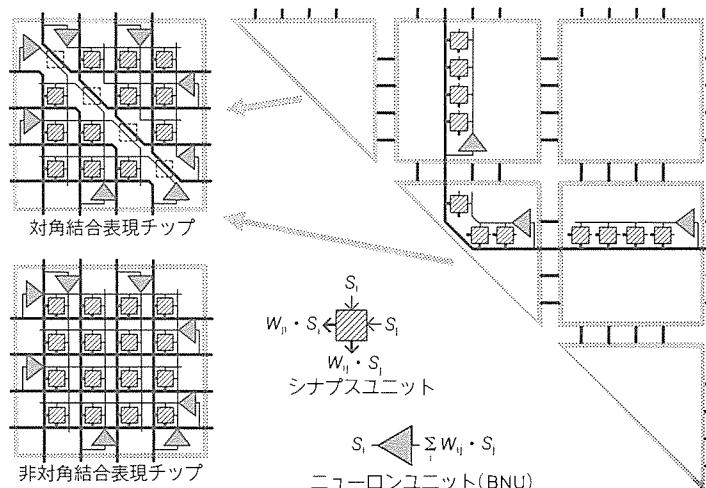

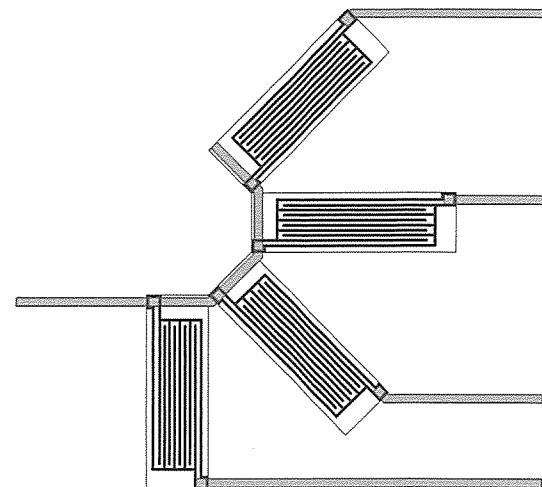

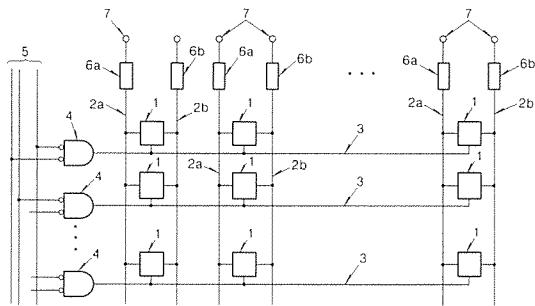

完全フィードバック結合構造を保った規模拡張を効率良く実現するため、BNU (Branch-Neuron-Unit) アーキテクチャを開発した。その概要を図3で説明する。このアーキテクチャは、一つのニューロンの機能を各チップに分散したBNUで表現することを特徴としている。図は3個の非対角結合表現チップと3個の対角結合部分(1.5個の対角結合表現チップに相当)を接続したニューラルネットを表しており、一つのニューロンを三つのBNUで表現している。各BNUは入力信号のみが共通接続されている。この共通入力ノードは、拡張接続するチップ数に比例して容量成分が増大するが、抵抗成分が減少するので、平均の時定数は拡張チップ数によらず一定である。また、各BNUはチップ内のシナプスのみ駆動するので拡張チップ数によらずBNUの負荷は一定である。したがって、チップ間接続線に寄生する抵抗・容量・インダクタンスが無視できる値であれば、拡張接続するチップ数によらずサイクル時間は一定に保たれ、並列度に比例した速度性能が得られる。

拡張接続に必要な2種類のチップは、三角形の対角結合部分を二つ向かい合わせることによって、対角結合表現チップは非対角結合表現チップとよく似た構成となり、マスター スライス方式によって配線の変更のみで2種類を作り分けることができる。

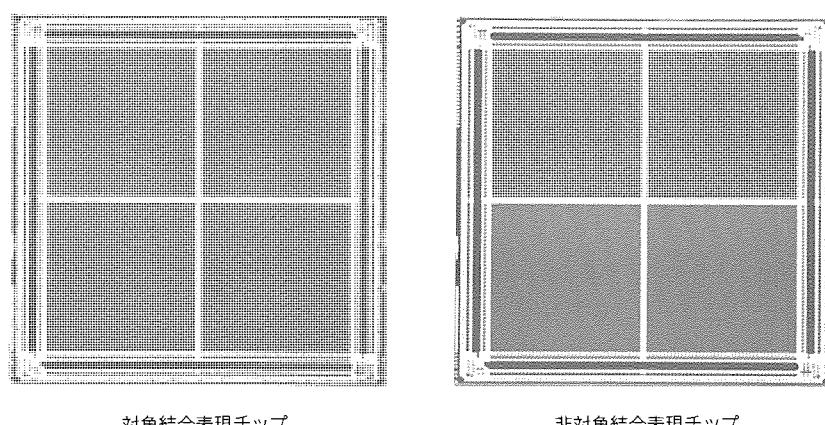

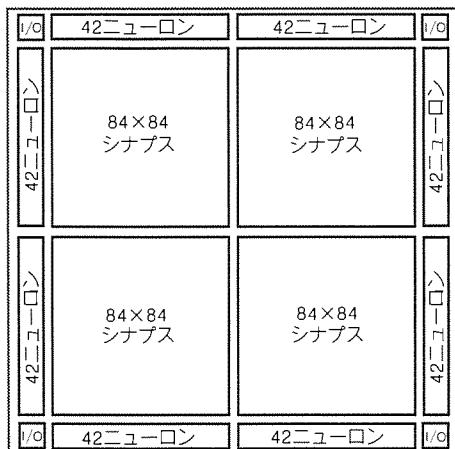

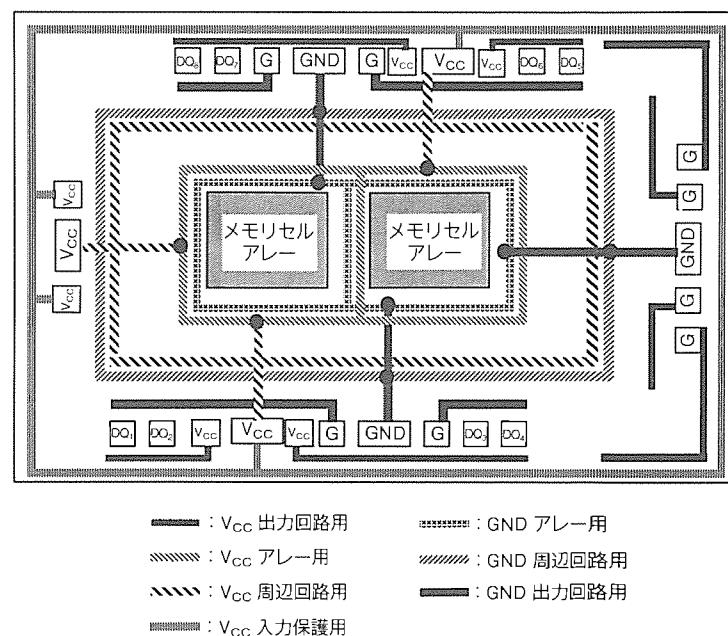

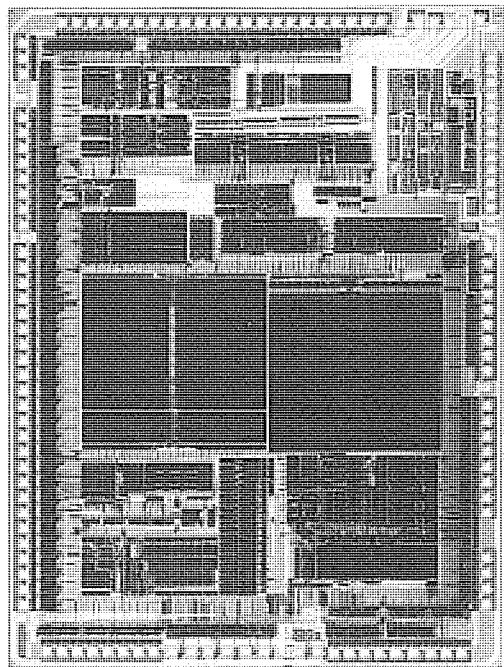

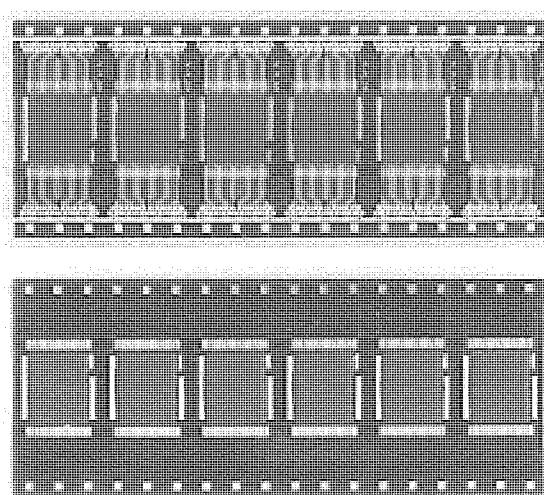

## 5. チップ構成

1.0  $\mu\text{m}$  CMOS 技術を使って 14.5 mm 角のチップに 336 個のニューロンユニットと 28,224 個のシナプスユニットを集積した。図4にチップ写真を示す。対角結合表現チップと非対角結合表現チップは共にチップ中央に 168 行 168 列のシナプスマトリクスが配置されており、そのシナプスマトリクスの四辺に沿って、それぞれ一辺に 84 個のニューロンユニットが一列に配されている。二つのチップの違いは、シナプスマトリクスの対角線上にあるシナプスユニットの配線が異なっているだけである。チップレベルのブロック構成を図5に示す。

前述したシナプスとニューロンの回路構成によって、シナプスにおける結合積演算と、ニューロンにおけるシナプス出力信号の総和演算、そして、そのしきい値処理(非線形変換)が、アナログ演算処理される。しかも、これらの処理は完全に並列・同期で動作するので高速な処理が実現できる。このようにチップ内

部では多くの部分でアナログ信号処理を行っているが、チップ外部の制御系とのデータのやり取りはすべてデジタル信号で行える構成であり、既存情報処理装置との整合性は良好である。

## 6. 評価結果

このチップは 50 ns で演算処理を実行でき、 $1 \times 10^{12}$  CPS

表1. ニューロンの属性と出力状態

| ニューロン<br>の属性 | 学習<br>フェーズ | SR(P)<br>データ | $I_{sel}S$ | ニューロン<br>の状態出力 |

|--------------|------------|--------------|------------|----------------|

| 隠れ           | +          | H            | L          | 内部活性値          |

|              | -          |              | H          | 内部活性値          |

| 出力           | +          | L            | L          | SR(T) 反転データ    |

|              | -          |              | H          | 内部活性値          |

| 入力           | +          | L            | L          | SR(T) 反転データ    |

|              | -          |              | L          | SR(T) 反転データ    |

図3. BNU アーキテクチャによる拡張接続

対角結合表現チップ

非対角結合表現チップ

チップサイズ : 14.5mm × 14.5mm

ニューロン数 : 336

シナプス数 : 28,224

シナプス結合数 : 56,448

図4. チップ写真

図5. チップレベルブロック図

(Connections Per Second) の処理速度に匹敵する。学習処理では  $28 \times 10^9$  CUPS (Connections Update Per Second) の速度性能が得られた。また、等ハミング距離の教師パターンによる学習評価によれば、シングルチップで 30 パターン程度までの記憶が可能で、その学習は 1 ms 以下で収束した。シナプス荷重値はキャパシタの蓄積電荷で表現されているので、構造上避けられない電荷のリークによって、学習後時間経過とともに変化する。この電荷のリークによる認識率の変化は、室温で約 300 ms 後に認識率 98 % まで低下した。しかし、学習に要する時間より 2 けた長いので、定期的な学習によって高い認識率を維持することが可能である。

実際の拡張システム構築で問題になる各 BNU 間の性能ばらつきやチップ間接続線に寄生する抵抗・容量・インダクタンスなどの不良因子は、各チップの学習機能（自己組織化能力）によってある程度吸収される。接続評価によって、数百チップまでの拡張接続が可能であることが見積もられている。試作したチップの諸元を表2にまとめる。

## 7. む す び

ニューロチップに強く求められる、高速、大規模、学習機能を実現するべく開発したこのニューロチップは、ニューラルネットの特徴である自己組織化機能を活用することに着目したアナログ・ディジタル混在回路設計によって、学習機能

表2. チップ諸元

|        |                                         |

|--------|-----------------------------------------|

| 構成     | 336ニューロン／28K シナプス                       |

| 演算速度   | $1 \times 10^{12}$ CPS* (1ビット × 5ビット精度) |

| 学習速度   | $28 \times 10^9$ CUPS**                 |

| 表現回路網  | 完全フィードバック結合                             |

| チップサイズ | 14.5mm × 14.5mm                         |

| 使用プロセス | 1.0 μm CMOS, 2poly, 2metal              |

| パッケージ  | 393PGA                                  |

| 消費電力   | 最大 3.0W                                 |

注 \* CPS : Connections Per Second

\*\* CUPS : Connections Update Per Second

を備えながら高集積高速性能を実現できた。また、BNU アーキテクチャの開発によって、実用規模のニューラルネットの構築を可能とした。例えば、200 チップの拡張接続によって、3,360 ニューロン、5,644,800 シナプス (11,289,600 結合) のニューラルネットワークが実現でき、 $200 \times 10^{12}$  CPS の処理速度が期待できる。この性能は既存のニューロ アクセラレータ付きワークステーションの実現できる 2 倍以上の規模に匹敵し、約 7 けた以上速い処理速度である。

学習機能を持ったニューロチップの開発は始まったばかりであり、今後この分野の研究が進むにつれて多くの新たな課題が明らかになるだろう。新たな課題を明らかにするためにもこのようなニューロチップの開発は重要なステップである。また、これらのニューロチップで実現可能な応用分野の開拓もニューラルネット情報処理技術の展開に大いに役立つと思われる。

## 参 考 文 献

- (1) Arima, Y., Mashiko, K., Okada, K., Yamada, T., Maeda, A., Notani, H., Kondoh, H., Kayano, S. : A 336 Neuron, 28K Synapse. Self-Learning Neural Network Chip with Branch-Neuron-Unit Architectuere, ISSCC '91, Digest of Technical papers, 182~183 (1991)

- (2) Ackley, D. H., Hinton, G. E., Sejnowski, T. J. : A Learning Algorithm for Boltzmann Machines, Cognitive Science, 9, No. 1, 147~169 (1985)

# 大規模並列処理用データ駆動型 マイクロプロセッサ

小守伸史\* 佐藤尚和\*

田村俊之\* 高田英裕\*

浅井文康\*

## 1. まえがき

ハイエンドコンピュータの分野では、し烈な高速化競争が繰り広げられている一方で、これまで高速化を支えてきたデバイスの高速化は物理的な限界に近づいてきている。今後は、マルチプロセッサによる並列処理が、性能限界をブレークスルーするための中心的な技術課題と考えられている。

データ駆動方式は、非ノイマンすなわち並列処理コンピュータの代表的なアーキテクチャであり、データフローとも呼ばれている。プログラムを構成する命令同士のデータ依存関係をプログラム実行時に動的に検出し、データ依存のない命令を並列にスケジューリングすることにより、命令レベルの細かい並列処理を実現するアーキテクチャとして注目されている。この分野では、米国マサチューセッツ工科大学(MIT)における1970年代の研究が先駆的な役割を果たした。その後、日本を中心に実用化の研究が進められ、種々のシステムやLSIが開発されてきたが<sup>(1)~(3)</sup>、研究レベルのものや画像処理などの特定用途向けのものが多かった。

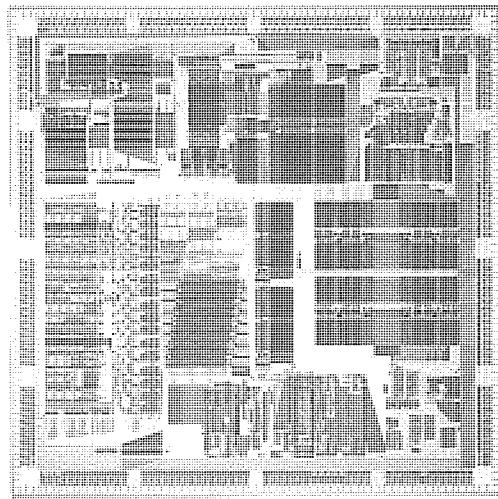

この論文のデータ駆動型マイクロプロセッサ(以下“本プロセッサ”という。)は、データ駆動アーキテクチャを採用することにより、マルチプロセッサ構成による並列処理を効率的に行うことを目指している。チップ単体としては、最新の0.8μmCMOSプロセスを用いることにより、32ビット浮動小数点演算を1秒間に5,000万回実行できる高性能(50MFLOPS)を達成した<sup>(4)</sup>。これは従来のデータ駆動型プロセッサ<sup>(3)</sup>の性能の約2.5倍に当たる。さらに、大規模並列処理への適用を想定した幾つかのハードウェア機能をチップ内に搭載した<sup>(5)</sup>。この論文では、1チップデータ駆動型マイクロプロセッサの概要を説明した後、本プロセッサのベクトル演算機能、並列処理向きの機能及び応用分野について述べる。

## 2. データ駆動方式

ノイマン型のコンピュータの理論的な裏付けが有限状態機械であるとすれば、データ駆動型のコンピュータの理論的なよ(拠)り所はペトリネット<sup>(6)</sup>と呼ばれる有向グラフであり、ペトリネット上を流れる複数のデータ(トーケンという。)の振る舞いによって並列処理のモデルを構築している。

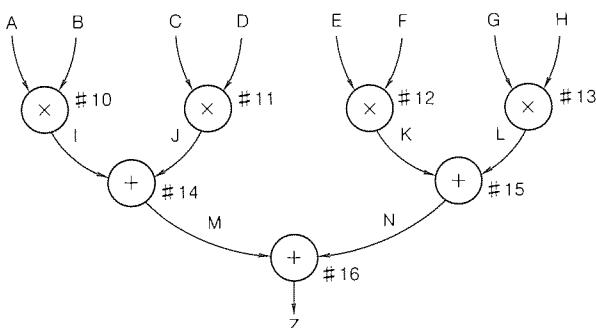

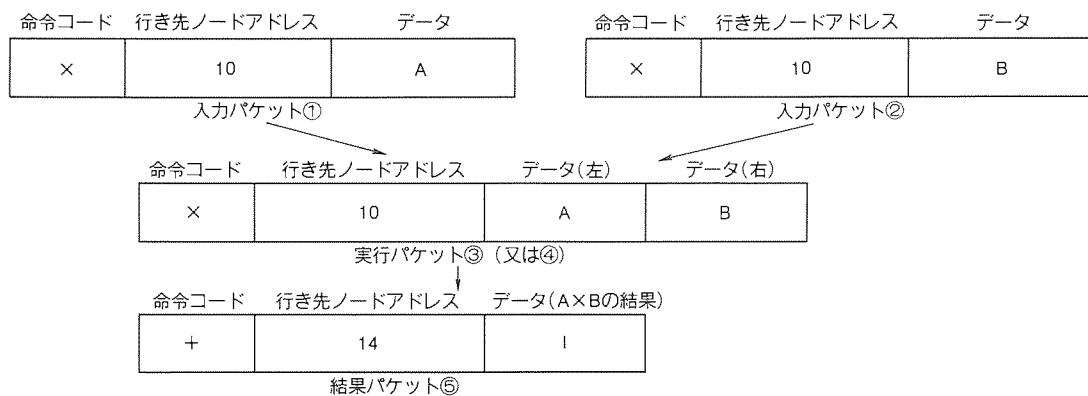

図1は、ペトリネットと等価な表現であるデータフローグラフを示している。データフローグラフは、データ駆動型の

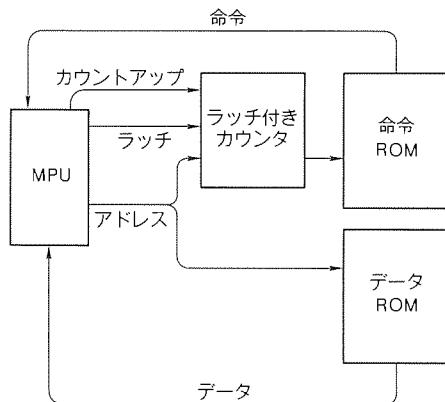

コンピュータにおける機械語レベルのプログラム表現形式であり、命令コードを表す円(ノード)と、ノード間のデータ依存関係を表す矢印(アーカ)から構成されている。データ駆動方式では、命令ノードの入力端子にパケット(制御情報を附加したデータ)が到着することによって各命令は演算実行可能となり、ハードウェア資源の許す限りにおいてこれらの命令は並列に処理される。

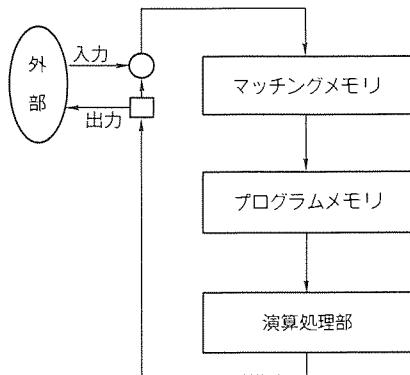

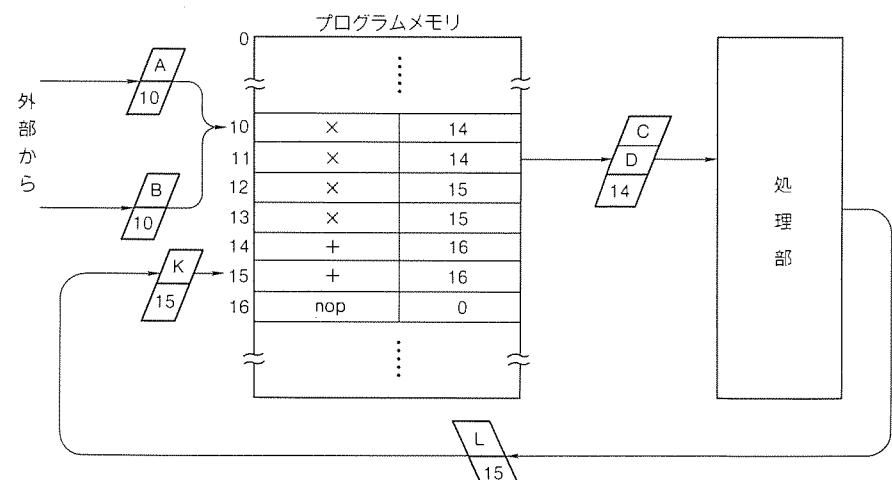

データ駆動方式でプログラムを実行するために必要な操作は、①“あるノードに対する二つの入力がそろったことの検出”，②“命令コードの読み出し”，③“命令の実行”的三つである。これをハードウェアに対応させると、データ駆動型コンピュータに必ず(須)の機能部は、①マッチングメモリ、②プログラムメモリ、③演算処理部の三つであるといえる(図2)。このうち、プログラムメモリと演算処理部はノイマン方式でもほぼ同一機能のハードウェアが用いられるが、マッチングメモリはデータ駆動方式に特有かつ重要な機能部である。

図3は、データ駆動方式におけるプログラム実行のイメージを示したものであり、複数のパケットが並行にプログラムメモリをアクセスし、これらのパケットが並列かつ独立に処理される様子を示している。図3中のプログラムメモリの内容は、図1のデータフローグラフを表している。

データ駆動型プロセッサの中では、各々のデータはパケット形式で通信されており、命令コード、行き先ノードアドレス、カラー／世代番号などの制御情報を含むタグ部を伴っている。各々のパケットに付けられた行き先ノードアドレスは、次に実行すべき命令の格納アドレスを示しており、ノイマン

$Z = A \times B + C \times D + E \times F + G \times H$  と等価な演算を行うデータフローグラフ。各ノードに付加した番号はノードアドレスを示す。

図1. データフローグラフの例

方式におけるプログラムカウンタと同一の役割を果たしている。データ駆動方式では、活性化されているデータが個別にプログラムカウンタをもっていることになり、これらのデータを独立に処理することができる。

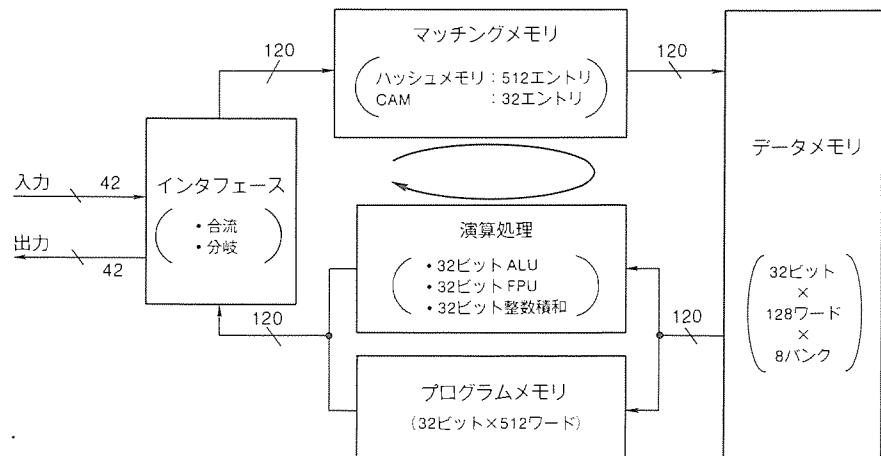

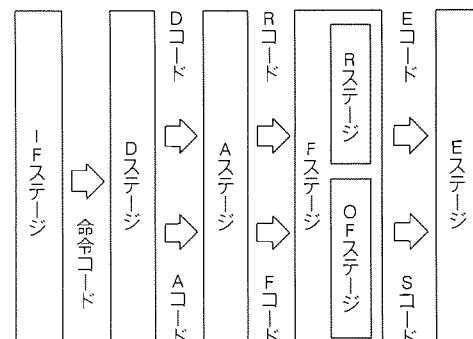

### 3. 1 チップデータ駆動型マイクロプロセッサ

#### 3.1 プロセッサの概要

本プロセッサは、図4に示すように基本的には機能ブロックを環状に接続した巡回型パイプライン方式を採用しており、一つのパケットがパイプラインを1周回することにより、1命令が実行される。パイプライン中でのパケットのスループットは最高毎秒50Mパケットである。この高スループットを実現するために、本プロセッサは各機能ブロックを更に多段のパイプライン段に分割するスーパーパイプライン構造を採用し、さらにパイプライン中のデータ転送を高速に行うために自己同期回路を用いた<sup>(7)</sup>。

インターフェース部は、プロセッサ外部とのパケットの入出力を制御するブロックであり、外部からの入力パケットに対して行き先プロセッサ番号をチェックした後、内部の巡回パイプラインに合流させる“合流機能”と、巡回パイプラインから他のプロセッサ行きのパケットを分岐させて出力する“分岐機能”をもっている。

マッチングメモリ部<sup>(8)</sup>は、2項演算命令のための二つの入力データの待ち合わせを行うブロックである。パケットが到着すると行き先ノードアドレス及びカラー／世代番号をキーワードとしてメモリ内容を検索し、これらが一致する相手データを探し出す。検索がヒットすれば2項演算用のパケットを出力し、ミスした場合には入力したパケットをメモリ内に格納し、相手パケットの到着を待たせる。カラー／世代番号をキーワードとすることにより、いわゆる動的データ駆動方式を1チップ上で実現することができ、多世代データの同時処理や、複数タスクからの同一関数同時呼出などが可能となった。動的データ駆動方式の採用により、プロセッサ効率を飛躍的に向上させることができることを5章で示す。

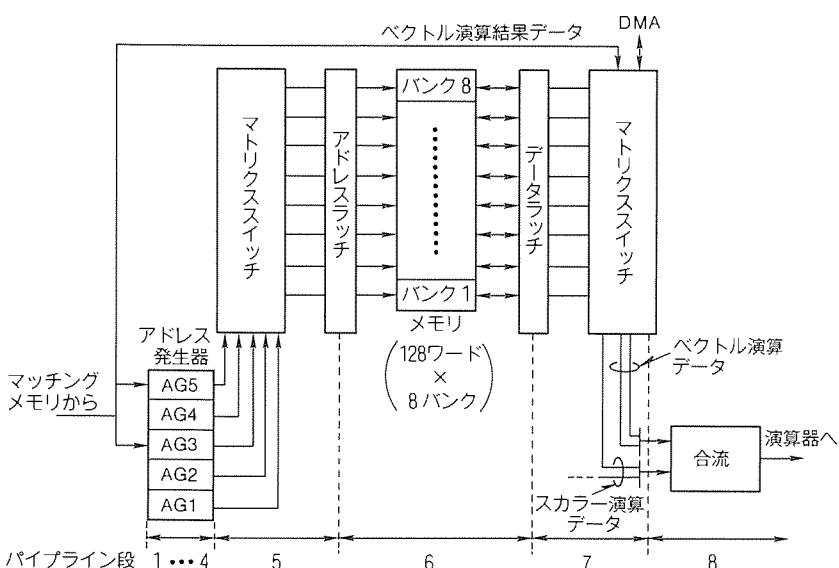

データメモリ部は、配列データ及

び定数データを格納する。配列データにベクトル演算を施すための五つのアドレス発生器を備えている。

本プロセッサは、入力パケットに対する応答時間を短縮するために、演算処理部とプログラムメモリ部を並列配置している。演算処理と並行に、プログラムメモリ部では次の周回

図2. データ駆動型プロセッサの基本構成

図3. データ駆動方式におけるプログラム実行のイメージ

図4. 1チップデータ駆動型プロセッサのブロック構成

図5. パケットフロー

時に実行すべき命令を先読みしてパケットのタグ部を更新している。

図5にスカラーデータ処理時のパケット内容の変遷を示す。外部から入力される初期パケット①、②には、プログラムメモリを通過することなく命令を実行させるために、命令コード、行き先ノードアドレス等があらかじめ与えられている。マッチングメモリ部で待ち合わせが完了すると、実行パケット③が生成される。データメモリ部では、命令コードに従ったメモリアクセスが行われる。データメモリから出力されたパケット④を構成するフィールドのうち、行き先ノードアドレスはプログラムメモリ部、また命令コードとオペランドデータは演算処理部に入力される。プログラムメモリ部で読み出された次の行き先ノードアドレスと、演算処理部で演算された結果データは一つの結果パケット⑤に統合される。結果パケットは、インターフェース部を経由して再び処理されるか、若しくは最終結果として外部に出力される。

図6に本プロセッサのチップ写真、表1に諸元を示す。本プロセッサは、 $0.8\mu\text{m}$  の2層メタル2層ポリシリコンCMOSプロセスを用いて、約70万素子を $14.65\text{ mm}^2$  角のチップ上に集積している。オンチップメモリの大容量化を図るために、2層目のポリシリコンを負荷抵抗として用いた高抵抗負荷型メモリセルのSRAMを用いた。

### 3.2 最小遅延マッチングメモリ

上でも述べたように、マッチングメモリは高性能なデータ駆動型プロセッサ実現のかぎ(鍵)となる重要な機能部である。マッチングメモリとしては、従来からハッシュメモリが一般的に採用されている<sup>(3)</sup>。ハッシュメモリは、大規模な論理アドレス空間を小容量の物理メモリにマップするために用いられるメモリであり、何らかのハッシュ関数を用いてアドレスのビット幅が圧縮される。しかし、圧縮時に複数のアドレスが同一のハッシュアドレスにマップされているため、ハッシュ衝突と呼ばれる現象が起こる。ハッシュ衝突が起きた場合には、ポインタチェインをたどりながら予備メモリ領域の逐次アクセスを行う必要があり、時間的なペナルティが大きい。

図6. 1チップデータ駆動型プロセッサのチップ写真

本プロセッサでは、この問題を解決するためにハッシュメモリと小容量の連想メモリを併用した<sup>(8)</sup>。ハッシュ衝突パケットが発生すると連想メモリに格納しておき、後続の入力パケットに対しては両方のメモリを同時に検索せることにより、ハッシュ衝突の有無にかかわらず、最小の遅延時間でマッチング処理を行うことができる。なお、連想メモリは、同時刻にハッシュ衝突しているパケットを格納することができればよいので、比較的小容量で十分な効果があり、本プロセッサでは32エントリとした。

### 3.3 ベクトル演算機能

データ駆動型プロセッサは、プログラム実行時に命令の実行順序が動的に決定されるため、スカラーデータの並列処理には適しているが、命令の実行順序が固定的であるベクトルデータに対しては余計なスケジューリングを行っていることになり、効率が良いとはいえない。本プロセッサは、エンジニアリング分野で頻繁に必要となるベクトル演算性能を向上させるために、ベクトル演算のためのパケット発生機構をチップに内蔵した。

図7に示すように、本プロセッサのデータメモリ部は、独立に動作する五つのアドレス発生器と、8つのメモリバンク

表1. 1チップデータ駆動型マイクロプロセッサの諸元

|        |         |                                                                         |

|--------|---------|-------------------------------------------------------------------------|

| チップ諸元  | プロセス    | 0.8 μm 2層メタル 2層ポリシリコン CMOS プロセス技術                                       |

|        | 素子数     | 約70万個                                                                   |

|        | チップサイズ  | 14.65mm×14.65mm                                                         |

|        | 最高性能    | 50MFLOPS*                                                               |

|        | 演算命令    | 56命令(32ビット整数、及び浮動小数点)                                                   |

| メモリサイズ | チップ内蔵   | データメモリ 32ビット×1,024ワード<br>プログラムメモリ 32ビット×512ワード<br>マッチングメモリ 56ビット×512ワード |

|        | 外部拡張メモリ | データメモリ $2^{24}$ バイト<br>プログラムメモリ $2^{21}$ ワード                            |

注 \* MFLOPS : Million FLoating-point Operations Per Second

1MFLOPSは、1秒間に100万回の演算を行うことを示している。

図7. ベクトルデータ生成機能付きデータメモリ

図8. 分散型共有メモリアクセス

を備えている。五つのアドレス発生器のうち、AG 5 はスカラーデータのアクセスに当てられるが、残りの四つはベクトル演算のために用いられる。

ベクトル演算時には、ベクトル演算用のアドレス発生器 AG 1, 及び AG 2 を用いて二つのオペランド(被演算データ)

を連続的に読み出しながら、あらかじめ設定されている命令コードとともに演算部に送り込み、ベクトル演算を実行する。結果データが巡回型パイプライン内を経由して再びデータメモリ部に到着すると、アドレス発生器 AG 3 を用いて結果格納用のメモリバンクに連続的に書き込みを行う。

アドレス発生器 AG 4 は、メモリバンクと外部拡張メモリ間のブロックデータ転送用であり、ベクトル演算と並行して、次のベクトル演算に必要なデータを読み込むことができる。

#### 4. 並列処理のサポート機能

##### 4.1 ネットワーク機能

マルチプロセッサ間でのパケット通信を支援するために、ネットワーク機能をチップ内に実現した。ホストコンピュータから送信される初期化パケットによって、各プロセッシングエレメント(PE)のPE番号をソフト的に設定できるようにした。行き先PE番号が一致しない入力パケットは、出力ポートに転送されるのでこのチップのみでディジタルエンジンを構成することができる。また、開発中のルーティングチップと組み合わせることにより、さらに多様なネットワークを構築することが可能となる<sup>(9)</sup>。

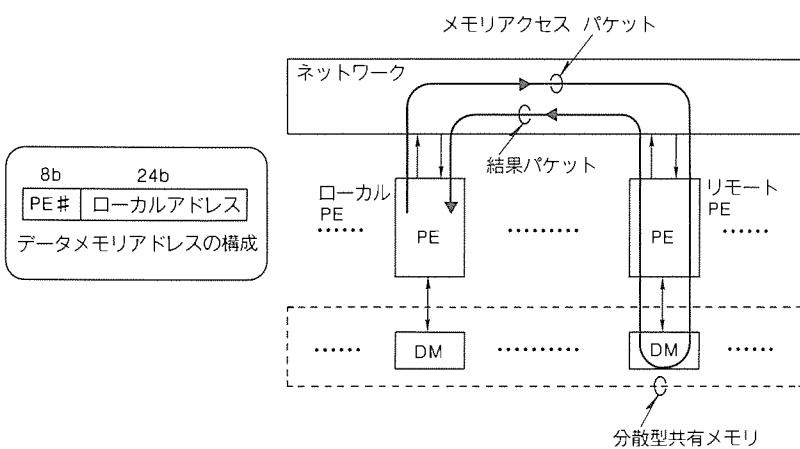

##### 4.2 分散型共有メモリのアクセス機能

大規模並列処理システムでは、メモリアクセスのボトルネックを避けるために分散型のメモリシステムが望ましい。一方、共有メモリに対する必要性も高いので、メモリシステムとしては分散型共有メモリの実現が必要となる。

本プロセッサでは、マルチプロセッサ構成時に他のPEのローカルメモリを透過的にアクセスするための機能をハードウェアで実現した。図8に示すように、32ビットのグローバルメモリアドレスは、行き先PE番号とローカルメモリアドレスから構成されている。分散型共有メモリをアクセス

するためのパケットは、グローバル メモリアドレステップ8ビットのPE番号に従って自動的に行き先PEに転送され、そこで下位24ビットのローカル メモリアドレステップでデータメモリをアクセスした後、もとのPEに自動的に戻ってくる。

この機能の実現により、プログラマは分散メモリ上での物理的なメモリ割り付けを意識することなく効率的にプログラムを作成することができる。さらに、グローバル メモリアアクセスのためのパケットハンドリングは完全にハードウェアで実現されているため、行き先PEのプログラム実行に与える影響を最低限にとどめることができる。実際、自PEのローカルメモリをアクセスする場合と比較したオーバヘッドはネットワークの通信時間のみであり、極めて高速な分散型共有メモリのアクセスが実現できたと考えられる。

#### 4.3 テスト アンド セット機能

分散型共有メモリの高速アクセス手法については上で述べたが、並列処理環境における共有メモリのアクセスで最も重要な問題の一つはメモリ内容の一貫性の維持である。例えば、複数タスク間でデータを共有している場合には、タスクAが共有データを操作している間は、原則として他のタスクに対して同一データ領域に対するアクセスや操作を禁止する必要がある。

本プロセッサでは、メモリ内容の一貫性をソフトウェアで保証することを可能とするために、データメモリのテストアンドセットのための命令を用意した。各タスクが共有データへのアクセスを行う前に、共有データの占有状態を示す特定のデータメモリアドレスに対してテストアンドセット操作を実行し、成功した場合のみ共有データ操作を許可するようにプログラムすることにより、メモリ内容の一貫性を保証することができる。

テストアンドセットの機能は、共有データの排他的アクセスに限らず、並列処理環境における資源管理に広く用いることができる。

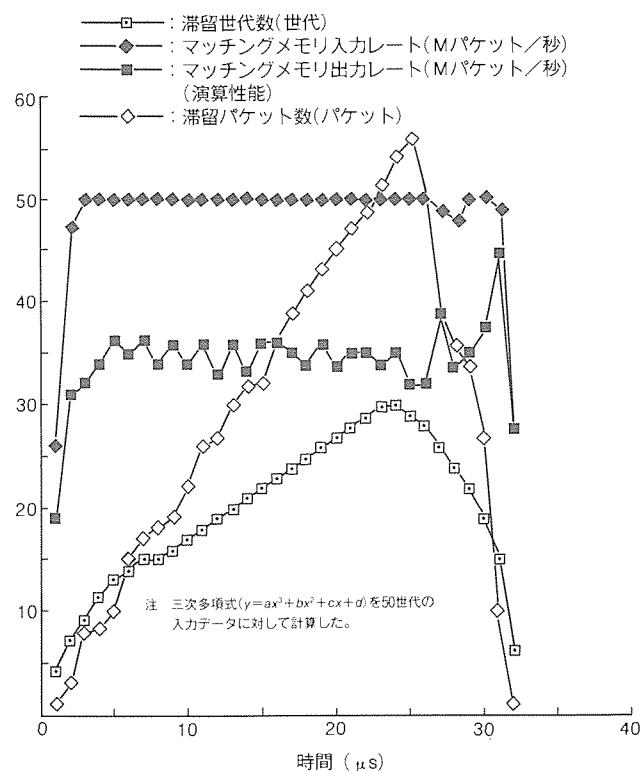

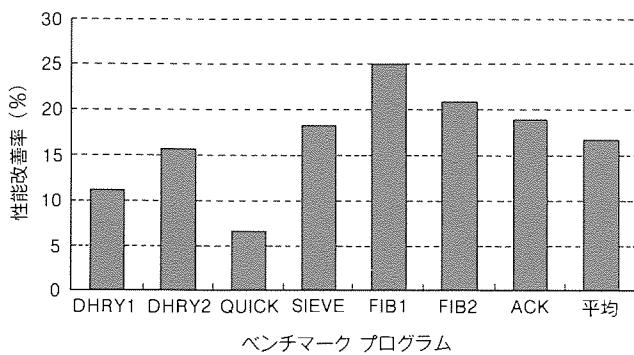

### 5. 応用プログラム評価

図9に示すグラフは、三次多項式の計算プログラムに対して50世代のデータを連続投入した時のシミュレーション結果を示している。図中のマッチングメモリ出力レートはプロセッサの演算性能を表しており、例えば35Mパケット/秒の出力レートは35MFLOPSの演算性能に相当している。プログラム実行を開始した当初、プロセッサ内の滞留世代数が5世代以下では、データの並列度が小さいためにパイプラインの充足率が低く、性能も20MFLOPS程度であるが、十数世代が滞留する状態ではおよそ35MFLOPSの性能が得られていることが分かる。

これはスカラー演算の場合であるが、例えばベクトル化が容易な高速フーリエ変換の場合には、ほぼ50MFLOPSの性

能を発揮し、1,024点のフーリエ変換を約1msで実行することができる。これは、信号処理専用のプロセッサ(DSP)と比べても高速である。

### 6. 今後の展開

本プロセッサは、高速ベクトル演算、効率的なマルチタスク処理、台数効率に優れたマルチプロセッサ並列処理などの特長を持っている。これらの特長を生かすことにより、次のような分野に適用していくことができると考えている。

#### (1) ベクトル演算機能

高速ベクトル演算機能を生かして、信号処理(FFT、種々のディジタルフィルタ)や大規模シミュレーション(流体、ニューラルネット等)を高速化することができる。

#### (2) マルチタスク処理

本プロセッサでは、プログラムメモリにあらかじめダウンロードした複数のタスクに対して入力データを同時に投入することにより、タスク切替えのオーバヘッドなしで、複数のタスクを同時並行に実行することができる。このため、従来は割込み処理を用いて複雑かつ非効率なタスク切替えを行っていたリアルタイム制御を高速化でき、機器組込み制御や、ロボット制御などに用いることができる。

#### (3) マルチプロセッサ並列処理

大規模なプログラム(データフローグラフ)は、適当なサイズに分割してマルチプロセッサに割り付けることができる。プロセッサ間の通信は、分割時に切断されたアーケ上を流れれるパケットによる、いわゆるメッセージ通信によって実現さ

図9. 性能シミュレーション結果

れ、ノイマン方式のマルチプロセッサ間同期で必要となる割込み処理やタスク切替えなどは不要である。このため、プロセッサ間の同期オーバヘッドのない効率的な並列処理システムを構築することができる。

論理シミュレーションなどのイベント駆動型シミュレーション、負荷分散によるコンピュータ グラフィックスの高速化、及び実時間動画処理などに威力を発揮する。

現在、応用評価用として、本プロセッサを4PE搭載したマルチ プロセッサボードを開発中である。このボードは、EWS のバックエンド プロセッサとして用いることも想定しており、VME バスインターフェースをもっている。さらに、複数のボードを連結してより大規模な並列処理システムを構築するための相互接続ポートを備えているので、広い範囲の応用システムのテストベッドとして活用できると考えている。

## 7. む す び

並列処理のための機能を中心に、50 MFLOPS の演算性能を持つ1チップデータ駆動型マイクロプロセッサについて述べた。本文では割愛したが、C コンパイラ及びシミュレータなどのソフトウェア環境の整備も並行して行った。本プロセッサの開発により、超高性能コンピュータ実現のためのマイクロプロセッサの新たな利用形態の可能性がひら(拓)けると考えている。今後、大規模並列処理分野における本プロセッサの諸機能の有効な活用法に関して、具体的な応用に即して実証的に評価していく予定である。

## 参 考 文 献

- (1) Shimada, T. : Evaluation of a prototype dataflow processor of the sigma-1 for scientific computation, IEEE Compcon Dig. Tech. Papers, 226~234 (1986)

- (2) Nukiyama, T., Matsumoto, K., Kurokawa, H., Hoshi, T.,

Goto, H., Tenma, T. : A VLSI Image Pipeline Processor, IEEE ISSCC Digest of Technical Papers, 208~209 (1984)

- (3) Komori, S., Shima, K., Okamoto, T., Miyata, S., Terada, H. : The Data-Driven Microprocessor, IEEE Micro, 45~59 (1989-6)

- (4) Komori, S., Tamura, T., Asai, F., Tsubota, H., Sato, H., Takata, H., Seguchi, Y., Ohno, T., Tokuda, T., Terada, H. : A 50MFLOPS Superpipelined Data-Driven Microprocessor, IEEE ISSCC Digest of Technical Papers, 92~93 (1991)

- (5) Tamura, T., Komori, S., Asai, F., Tsubota, H., Sato, H., Takata, H., Seguchi, Y., Tokuda, T., Terada, H. : A Data-Driven Architecture for Distributed Parallel Processing, Proc. IEEE ICCD, 218~224 (1991)

- (6) Peterson, J. L. (市川惇信, 小林重信訳) :ペトリネット入門, 共立出版 (1984)

- (7) Asai, F., Komori, S., Tamura, T., Sato, H., Takata, H., Seguchi, Y., Tokuda, T., Terada, H. : Self-Timed Clocking Design for a Data-Driven Microprocessor, IEICE Trans. E 74, No.11 (1991)

- (8) Takata, H., Komori, S., Tamura, T., Asai, F., Sato, H., Ohno, T., Tokuda, T., Nishikawa, H., Terada, H. : A 100Mega-Access per Second Matching Memory for a Data-Driven Microprocessor, IEEE J. Solid-State Circuits, 25, No. 1, 95~99 (1990)

- (9) Seguchi, Y., Komori, S., Tamura, T., Asai, F., Tsubota, H., Sato, H., Takata, H., Ohno, T., Tokuda, T., Terada, H. : A Flexible Router Chip for Massively Parallel Data-Driven Computer, Symp. VLSI Circuits Digest of Technical Papers, 27~28 (1991)

# 16M ビット DRAM

有本和民\* 若宮 亘\*

日高秀人\* 野崎雅彦\*\*

平山和俊\*\*

## 1. まえがき