# MITSUBISHI

# 三菱電機技報

MITSUBISHI DENKI GIHO Vol.65 No.2

2

1991

最近のASIC技術特集

## 最近の ASIC 技術特集

### 目 次

#### 特集論文

|                                           |    |

|-------------------------------------------|----|

| ASIC 特集に寄せて                               | 1  |

| 岡 久雄                                      |    |

| システムの動向と ASIC の現状と展望                      | 2  |

| 吉富正夫・松本平八・仁田重之・元吉啓登                       |    |

| 多層配線技術                                    | 9  |

| 中尾修治・大崎明彦・高田佳史・堤 聰明・松浦正純・石井敦司・小谷秀夫        |    |

| 0.8 $\mu$ m CMOS ASIC プロセス                | 14 |

| 畠中正宏・大野多喜夫・山口澄夫・森本博明・松田修一                 |    |

| セルベース設計用モジュール ジェネレータ                      | 18 |

| 篠原尋史・津田和彦・松本憲昌・辻橋良樹・藤森久美子・味岡佳英・塚本美智子      |    |

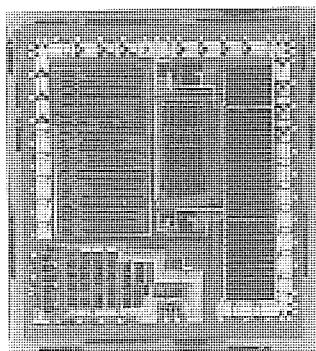

| 0.8 $\mu$ m CMOS ゲートアレー                   | 24 |

| 岡辺雅臣・柿沼守男・国岡美千子・村井正弘・川端啓二                 |    |

| 1.0 $\mu$ m CMOS ゲートアレー M60060 シリーズ       | 29 |

| 鈴木正博・中村博隆・布上裕之・小野眞司・瀧口真美・福水利之             |    |

| 32ビット CPU コアを内蔵した ASSP の開発手法              | 35 |

| 北上尚一・中尾裕一・大木正司・中村充善・鎌倉 寛・是松次郎             |    |

| ASIC 対応パッケージング技術の最新動向                     | 39 |

| 吉田 稔・島本晴夫・上田哲也・中尾 伸                       |    |

| デジタルオーディオの高音質化へのアプローチ                     | 45 |

| 加藤久雄・水野幹滋・森岡幸一                            |    |

| 低消費電力・映像用 CMOS A/D コンバータ LSI              | 50 |

| 細谷史郎・三木隆博・前田 敦・矢澤信春                       |    |

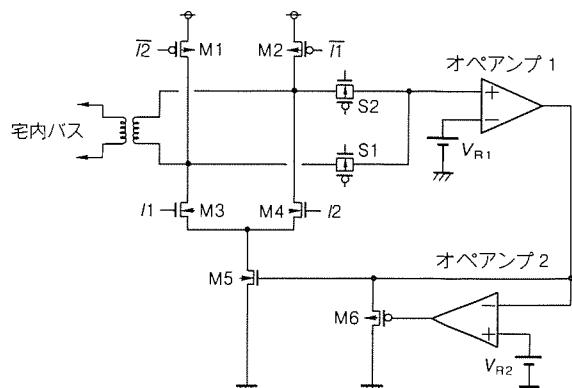

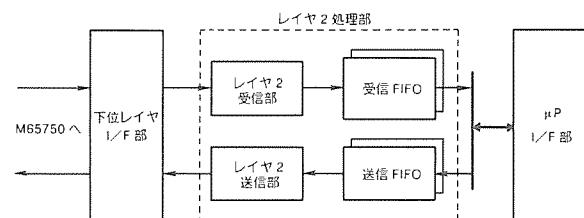

| ISDN 基本インターフェース用 LSI                      | 54 |

| 中林竹雄・近藤晴房・歳永 寛・長谷川浩一・山本誠二                 |    |

| CB-1 設計システムを用いた                           |    |

| 8kbps 単位交換可能な大容量時分割スイッチ LSI               | 58 |

| 覚塙高音・鈴木孝昌・川畑英雄・岸田 悟・長谷川浩一                 |    |

| FAX 用画像処理コントローラ M66332FP                  | 62 |

| 滝 洋一郎・中林祥恵・広川祐之・瀬政孝義・永田良浩                 |    |

| 光ディスク用誤り訂正 LSI                            | 68 |

| 森 信太郎・児玉幸夫・吉田英夫・井上 徹・清瀬泰広                 |    |

| 特許と新案                                     |    |

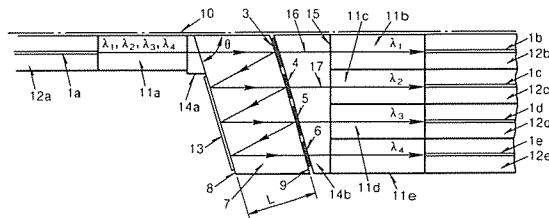

| 光波長分波装置、端末装置                              | 75 |

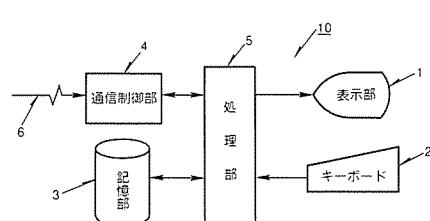

| リード・ソロモン符号の符号化方法                          | 76 |

| スポットライト                                   |    |

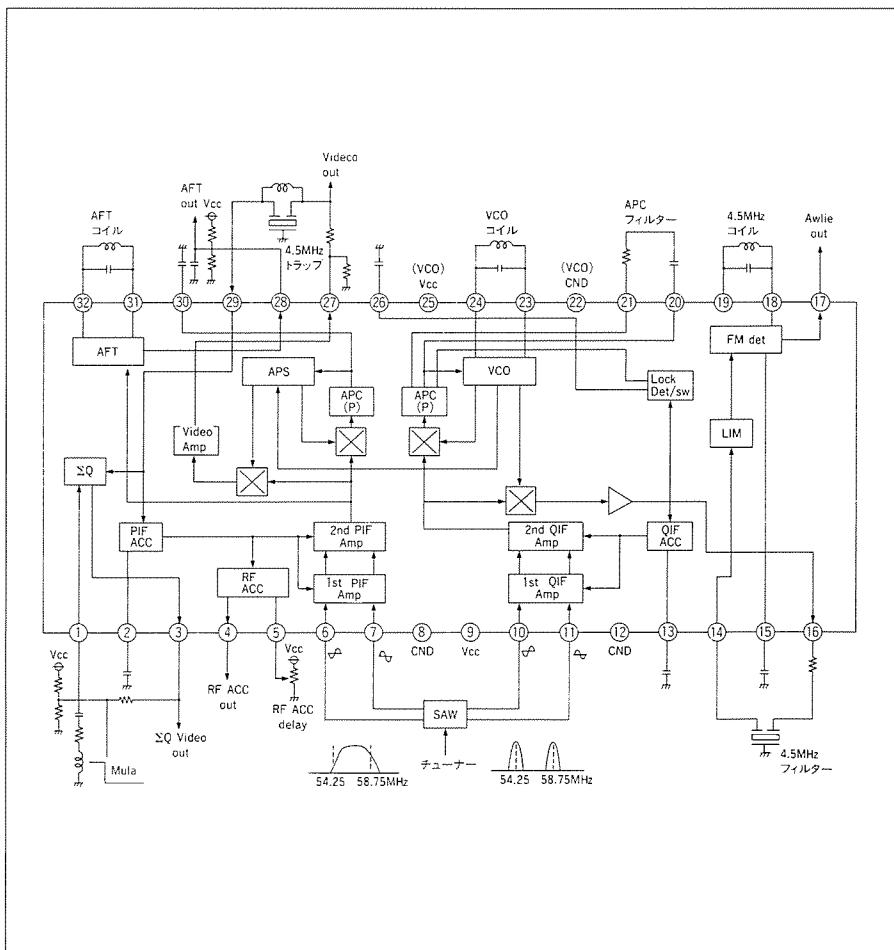

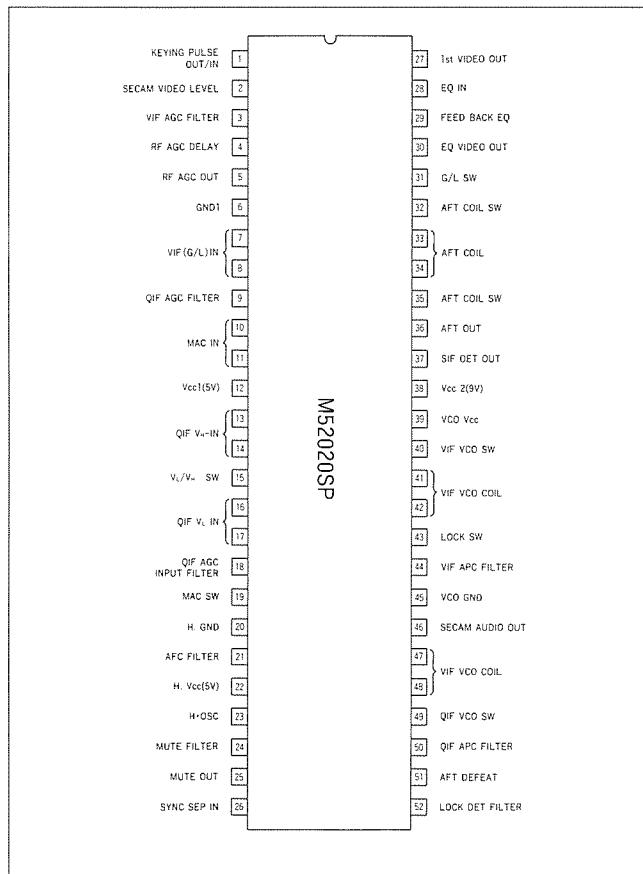

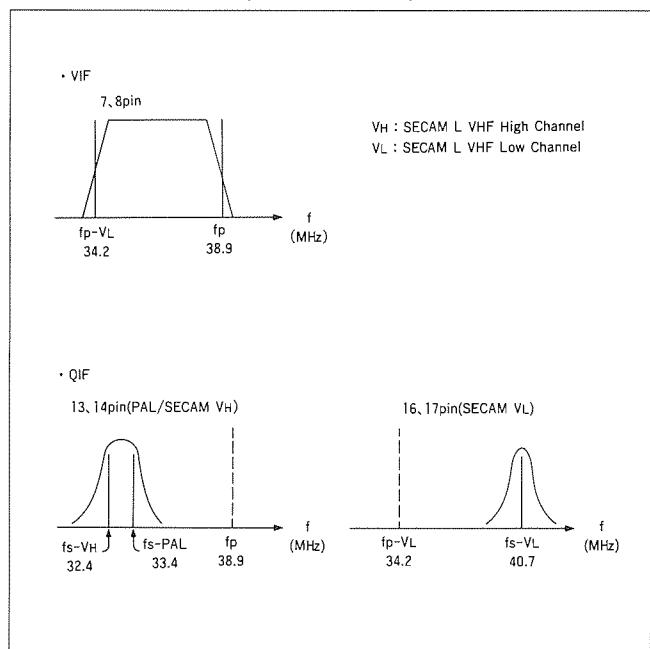

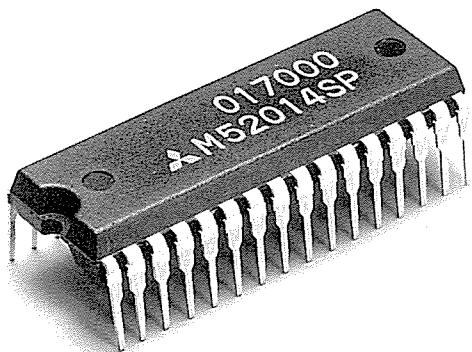

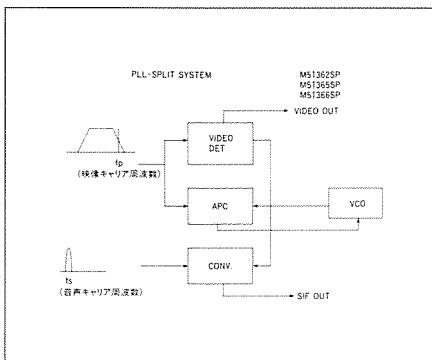

| マルチスタンダード対応 PLL VIF/SIF IC "M52020SP"     | 74 |

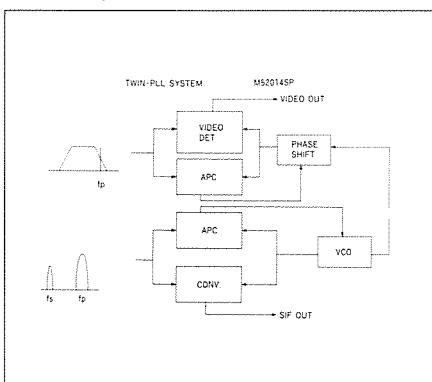

| TWIN-PLL 方式テレビ中間周波信号処理 IC "M52014SP" (表3) |    |

#### 表紙

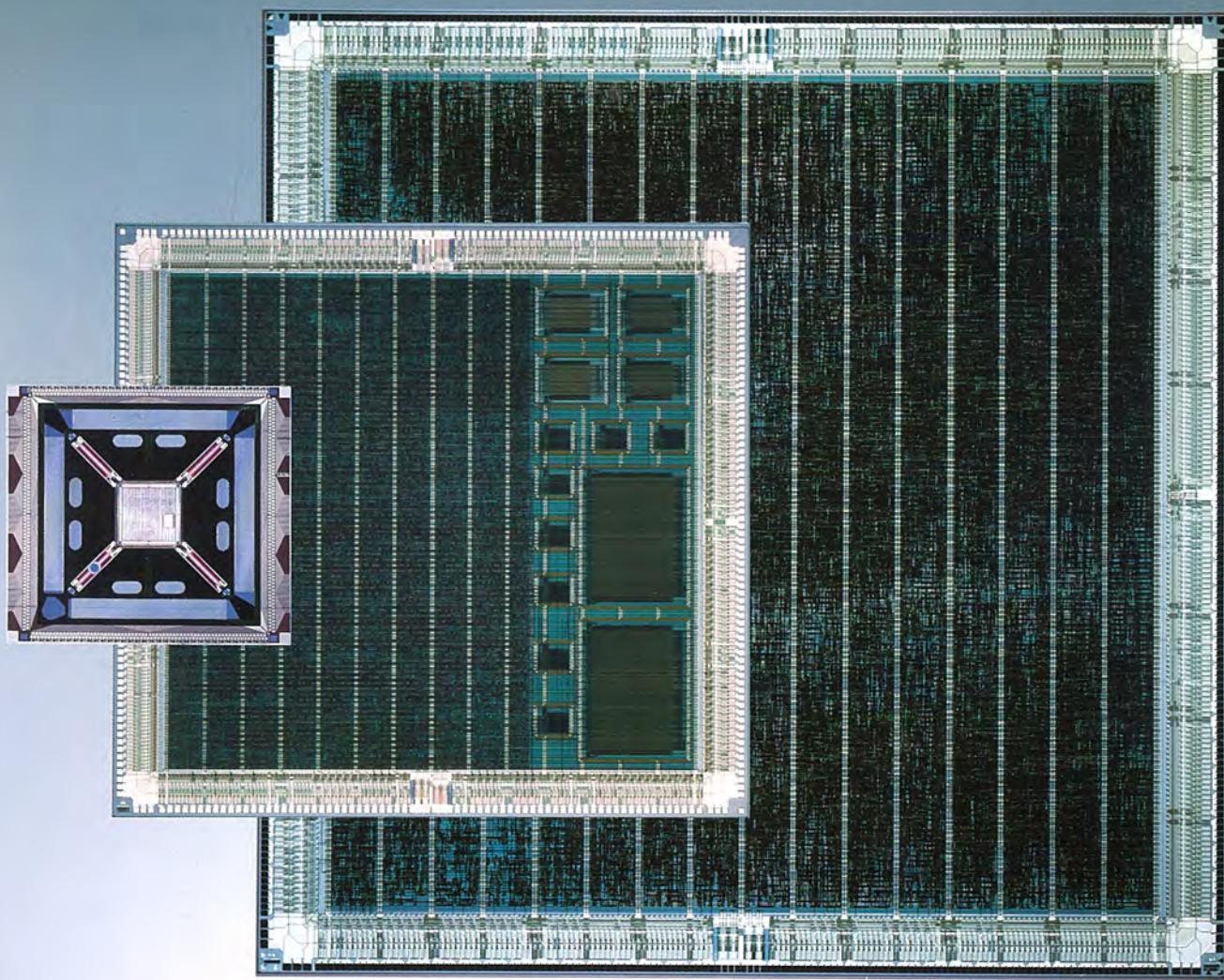

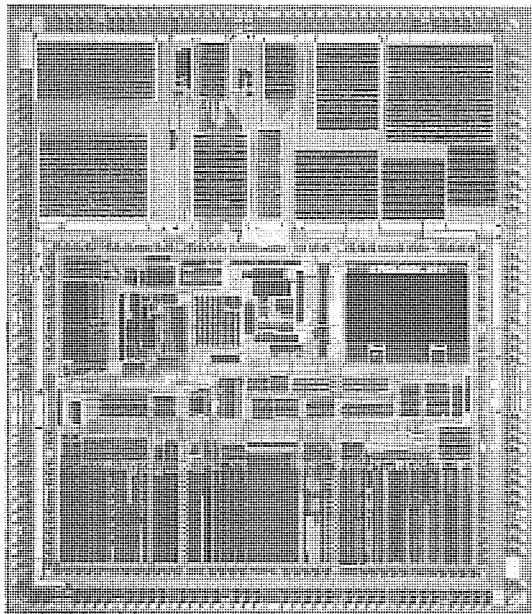

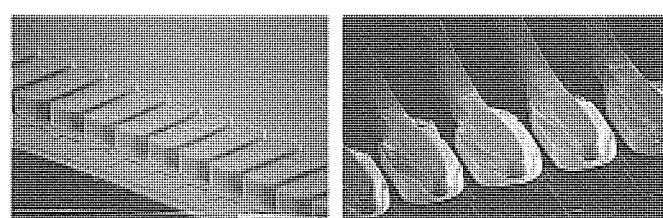

#### 0.8 $\mu$ m CMOS ゲートアレー

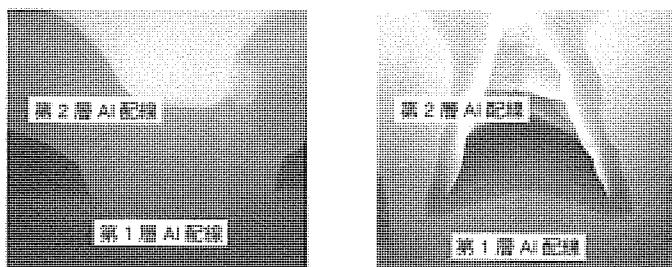

0.8  $\mu$ m CMOS アルミ 3 層配線技術を用いて開発した 400KG (写真: 大) と 250KG (写真: 中) のゲートアレーのチップ写真と 576 ピン TCP (Tape Carrier Package) に実装された 400KG ゲートアレー (写真: 小) の写真。

チップサイズは、250KG が 13.08mm × 12.22mm, 400KG が 14.56mm × 14.46mm である。写真の 250KG には、モジュールジェネレータで生成されたシングルポート RAM と デュアルポート RAM が合わせて 14 ブロック搭載されている。写真の 400KG には、121KG の回路が集積され、1615 のフリップフロップを一括駆動するクロックドライバを採用している。

## アブストラクト

### システムの動向と ASIC の現状と展望

吉富正夫・松本平八・仁田重之・元吉啓登

三菱電機技報 Vol. 65・No. 2・P 2~8

電子システムの中において ASIC が果たしている役割について述べた。ASIC は、電子システムの発展とともに成長してきた。現在あらゆるシステムの中で、キーデバイスとして重要な役割を果たしている。システムにおける様々なニーズと半導体のシーズが、ASIC によって実を結んでいるためである。今後とも ASIC は、その技術革新により重要性をますます高め、システムオンチップを目指してシステムとともに表裏一体となって発展していくと思われる。

### 多層配線技術

中尾修治・大崎明彦・高田佳史・堤 聰明・松浦正純ほか

三菱電機技報 Vol. 65・No. 2・P 9~13

最先端 ASIC に不可欠であるサブミクロン多層アルミ配線技術について報告する。コンタクトにおける Si 析出を防止する電極形成技術、信頼性を向上させるための AI 配線材料技術、配線パターンの微細化に対応する反射防止膜技術について述べる。また、有機シランとオゾンを用いた常圧 CVD による平たん化特性に優れた新しい層間絶縁膜形成法について示す。さらに、接続孔の歩留り、信頼性を改善する CVD タンゲステン技術についても言及する。

### 0.8 $\mu$ mCMOS ASIC プロセス

畠中正宏・大野多喜夫・山口澄夫・森本博明・松田修一

三菱電機技報 Vol. 65・No. 2・P 14~17

0.8  $\mu$ m デザインルールによる CMOS ASIC 対応のデバイス構造、及びプロセス技術について紹介するとともに、ASIC の開発期間短縮に有効な EB 直接描画技術についても述べた。主なプロセス技術としては、N<sup>-</sup> オーバラップ LDD 構造を採用することで、NMOS の高信頼化を実現したこと、配線の 3 層化に対応して、TEOS 系の低温平たん化絶縁膜により、微細な多層配線構造を可能としたことである。

### セルベース設計用モジュール ジェネレータ

篠原尋史・津田和彦・松本憲昌・辻橋良樹・藤森久美子ほか

三菱電機技報 Vol. 65・No. 2・P 18~23

RAM・ROM・乘算器・PLA 4 種類のセルベース設計用モジュール ジェネレータを、1.0  $\mu$ mASIC 用 CMOS プロセスを用いて開発した。このモジュール ジェネレータは、セルの規模パラメータに加えて形状パラメータや機能オプション等の自由度の高い選択肢を提供するとともに、セルベース設計 CAD ツールに対応したデータをすべて自動生成する。生成されるモジュールセルは、回路・レイアウト共に最適設計されており、高集積度・高速性能を示す。

### 0.8 $\mu$ mCMOS ゲートアレー

岡辺雅臣・柿沼守男・国岡美千子・村井正弘・川端啓二

三菱電機技報 Vol. 65・No. 2・P 24~28

最先端の 0.8  $\mu$ mCMOS アルミ 3 層配線技術を用いて開発した 400KG ゲートアレーをはじめとする M6008X シリーズのデバイス技術及び EWS ベースの設計システム(GA-2)について述べる。TAB(Tape Automated Bonding)方式によるパッケージ技術を採用し、最大 512 I/O を搭載する。モジュール ジェネレータ生成 RAM/ROM、スルーレート制御出力バッファ、一括駆動方式による低スキューロック分配技術を新たに開発した。

### 1.0 $\mu$ mCMOS ゲートアレー M60060 シリーズ

鈴木正博・中村博隆・布上裕之・小野眞司・瀧口真美・福水利之

三菱電機技報 Vol. 65・No. 2・P 29~34

1.0  $\mu$ mCMOS ゲートアレー M60060 シリーズの特長及び技術について述べるとともに、CAD サポート体制について紹介する。

同シリーズは、1.0  $\mu$ mCMOS 2 層配線プロセス技術と最新のアセンブリ技術により、高速かつ低消費電力で更に多ピンプラスチック QFP パッケージが利用できる特長を備えている。

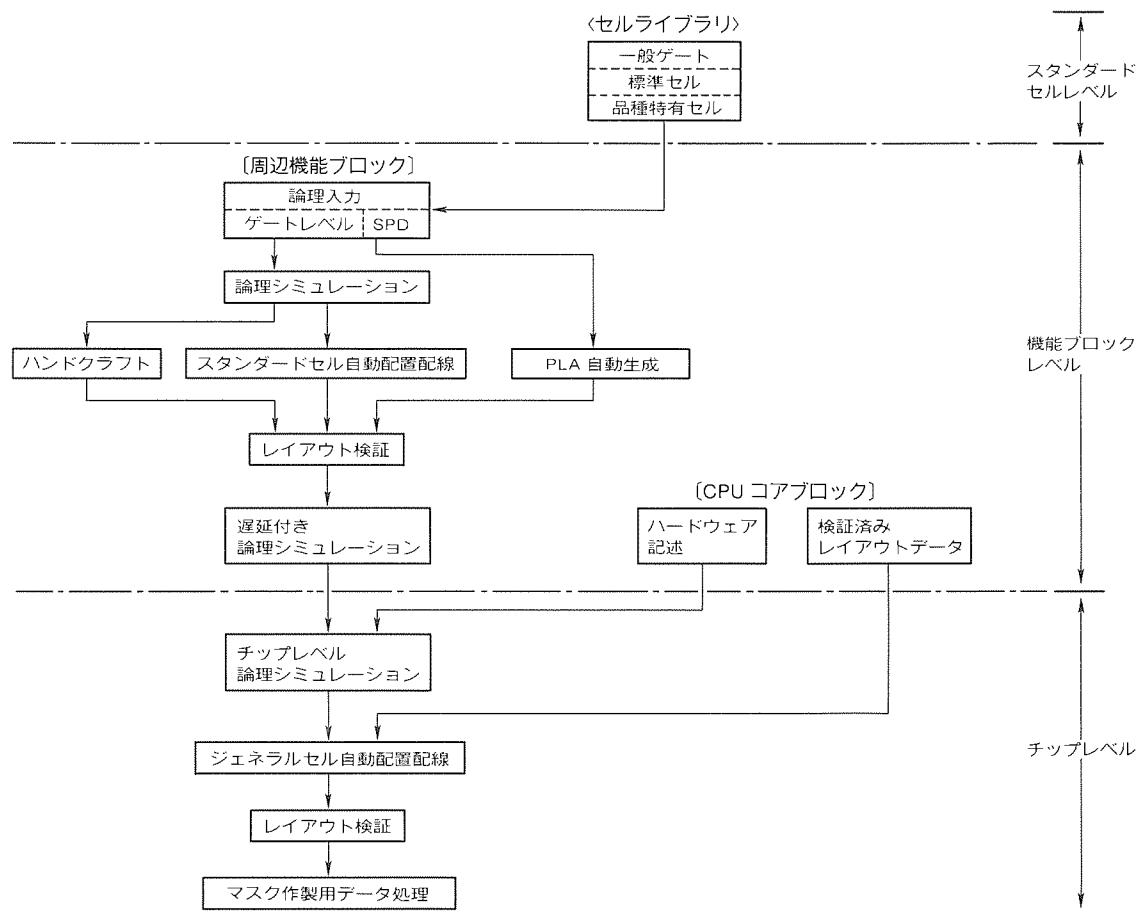

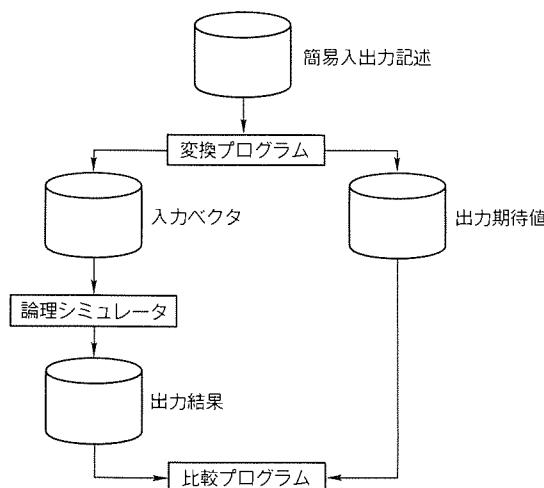

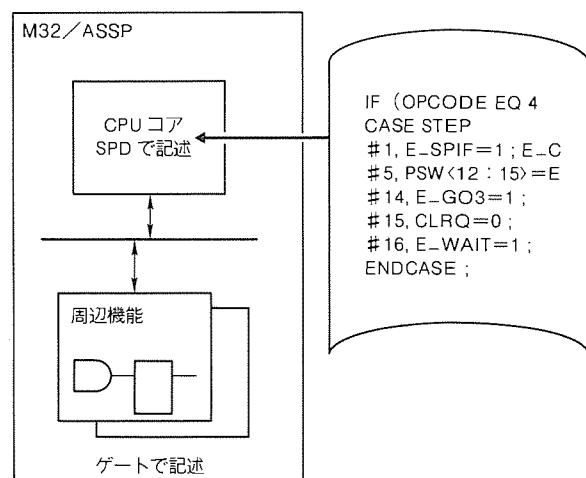

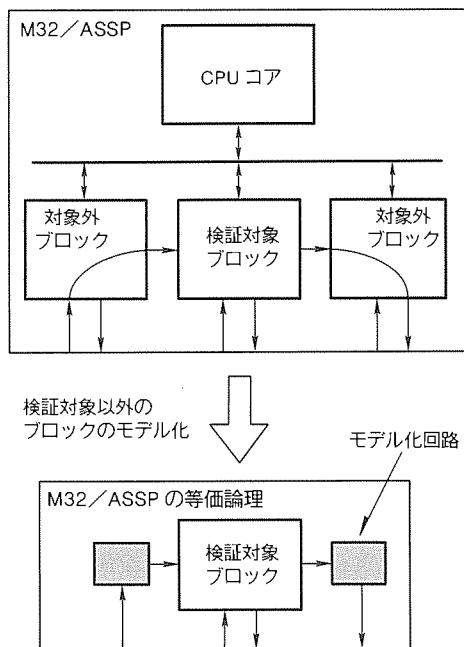

### 32ビット CPU コアを内蔵した ASSP の開発手法

北上尚一・中尾裕一・大木正司・中村充善・鎌倉 寛・是松次郎

三菱電機技報 Vol. 65・No. 2・P 35~38

トロン仕様に準拠した32ビット マイクロプロセッサ M32/100 をコアとして、周辺機能を内蔵した ASSP(Application Specific Standard Products)を開発した。セルベース CAD に基づいた階層設計、専用の入出力信号記述の使用による論理シミュレーション時のマンマシンインターフェース改善、効率的な論理のモデル化等によって開発工数を大幅に削減し、かつ迅速な製品展開を可能にした。

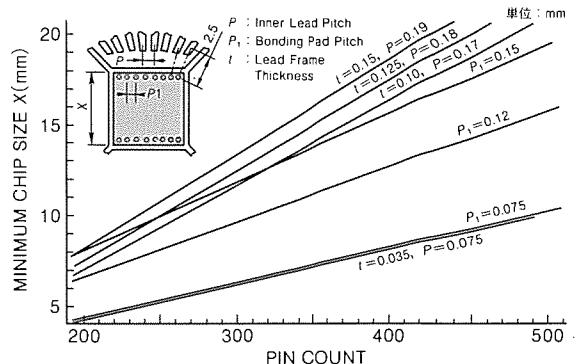

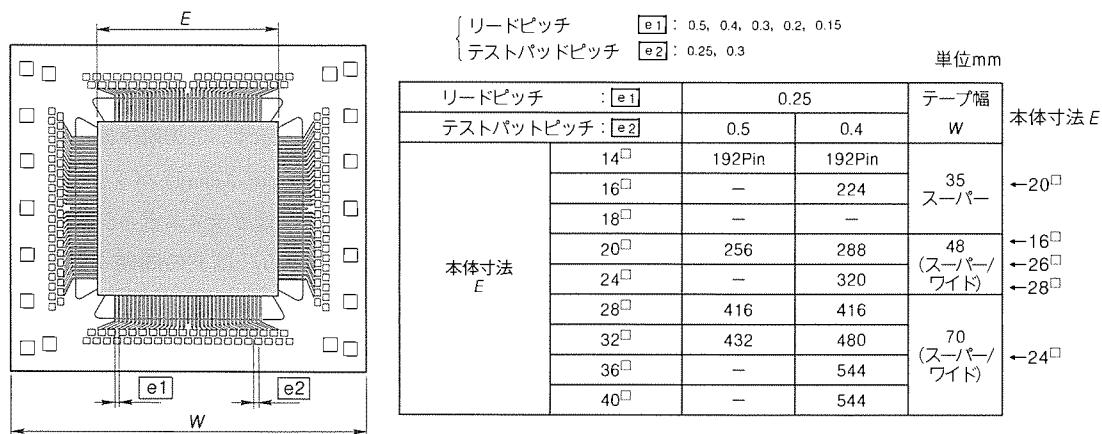

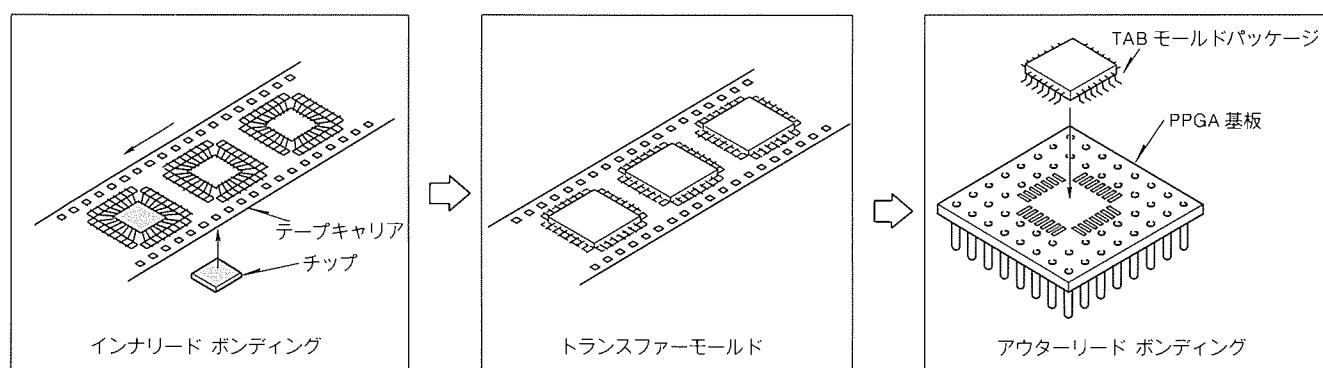

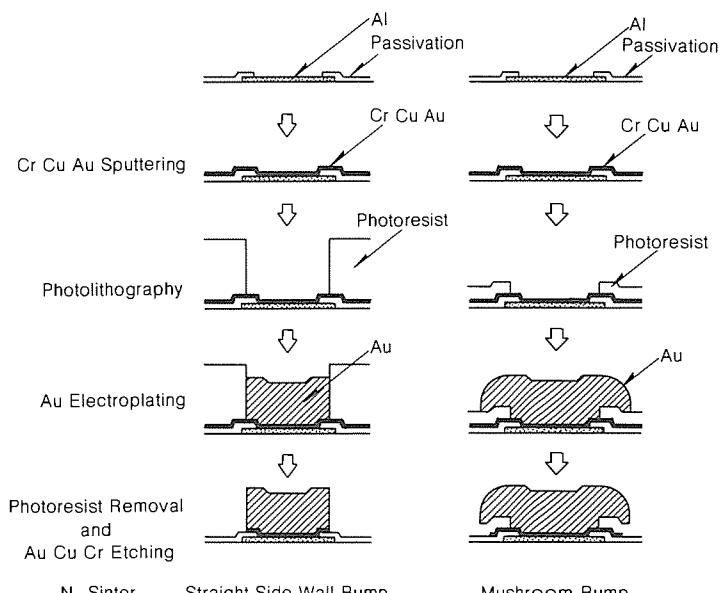

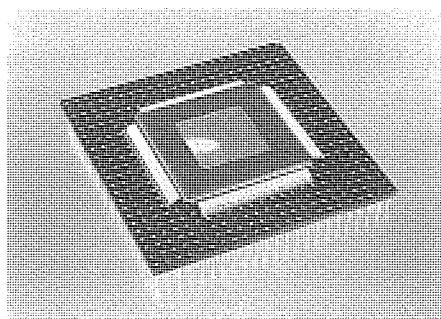

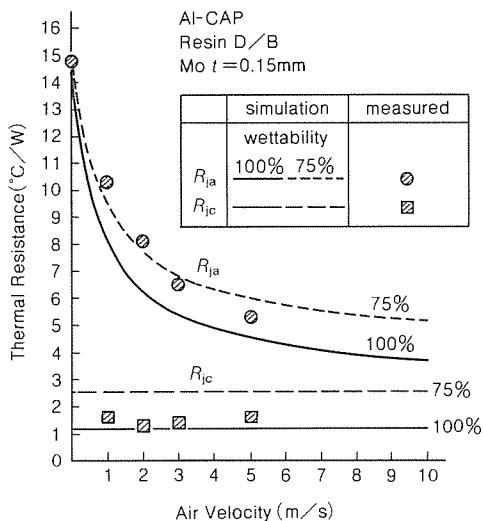

### ASIC 対応パッケージング技術の最新動向

吉田 稔・島本晴夫・上田哲也・中尾 伸

三菱電機技報 Vol. 65・No. 2・P 39~44

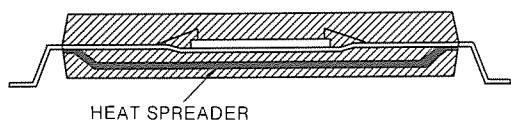

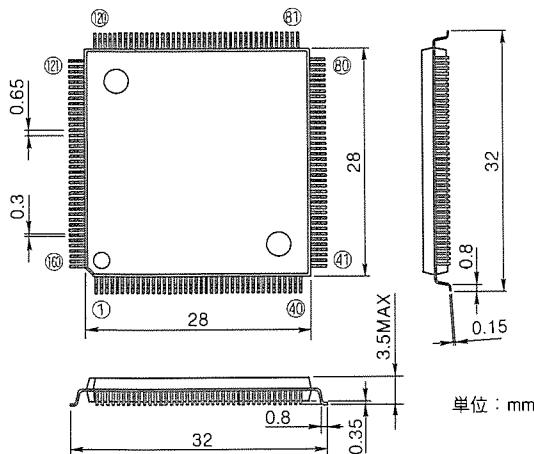

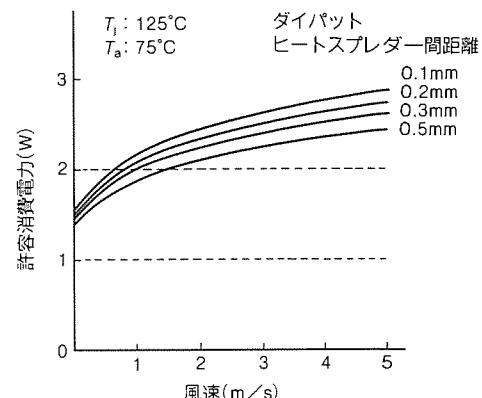

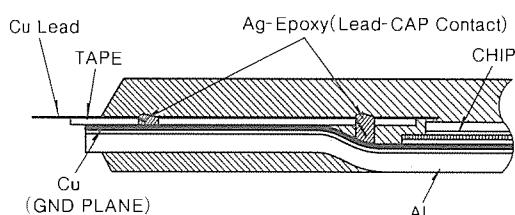

多様化しつつある ASIC(Application Specific Integrated Circuit)対応パッケージの動向について、多ピン化の視点からとらえた。当社は、従来 QFP と同一外形で、約 1/2 の熱抵抗を持つヒートスプレッダー内蔵のプラスチックパワー QFP を開発した。さらにワイヤボンド代替の TAB 技術を用い、低熱抵抗、低リードインダクタンス化を実現した、AI キャップ構造の超多ピンプラスチック TCP について紹介する。

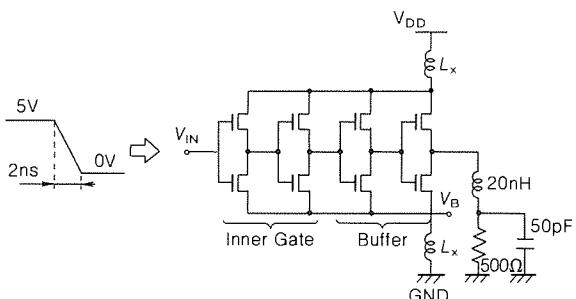

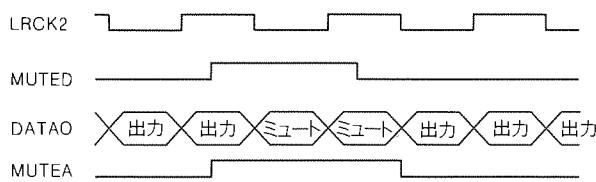

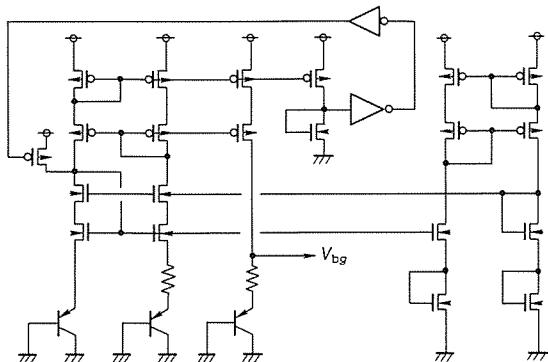

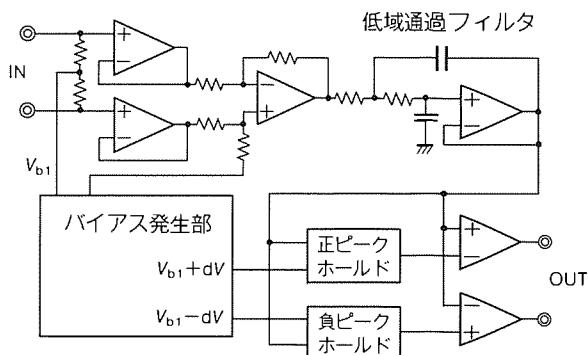

### デジタルオーディオの高音質化へのアプローチ

加藤久雄・水野幹滋・森岡幸一

三菱電機技報 Vol. 65・No. 2・P 45~49

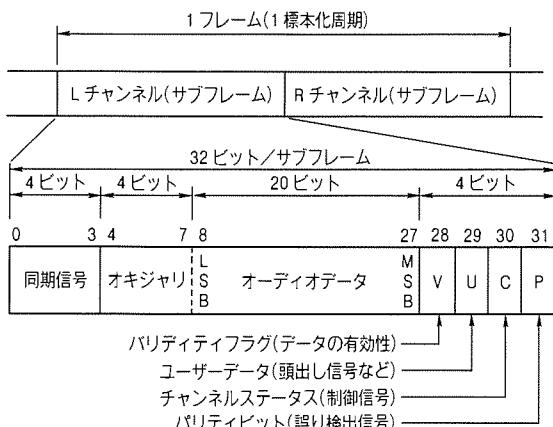

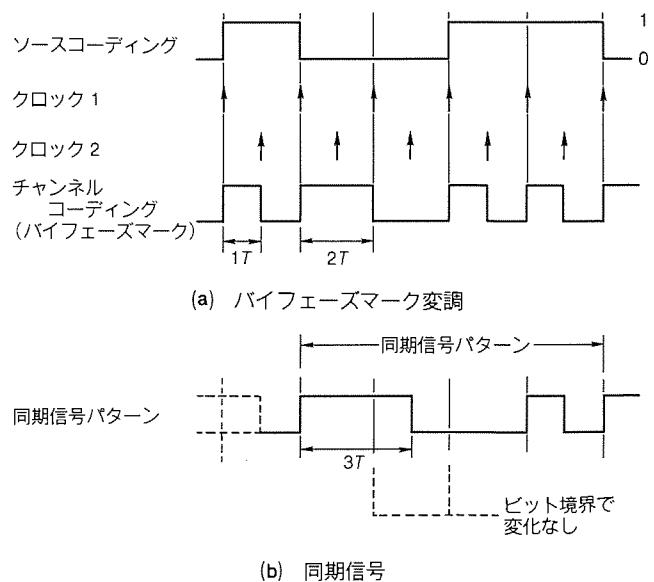

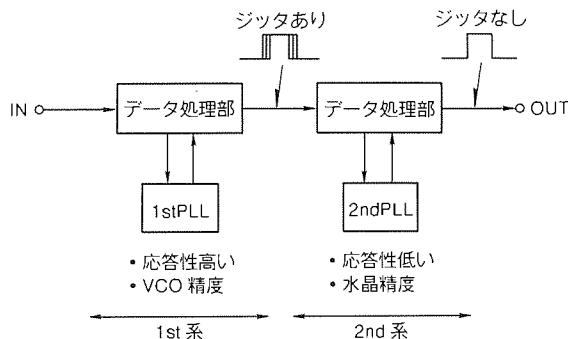

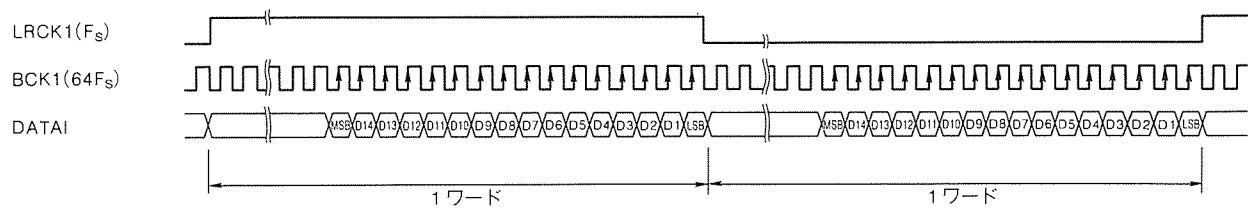

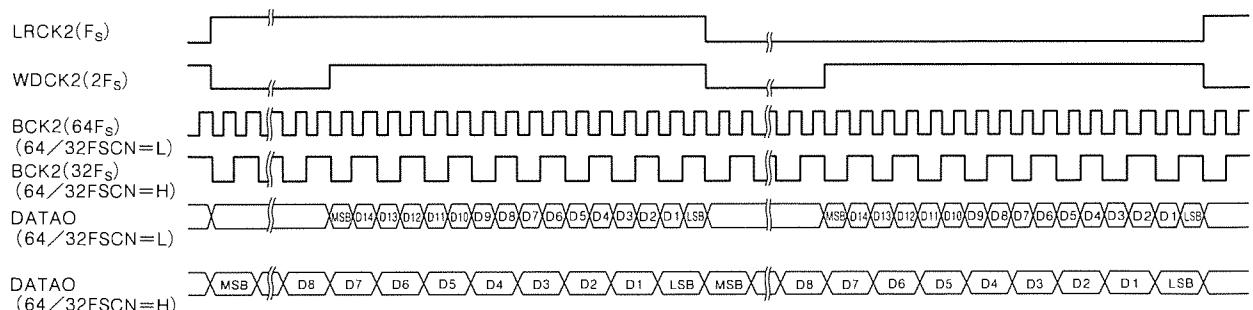

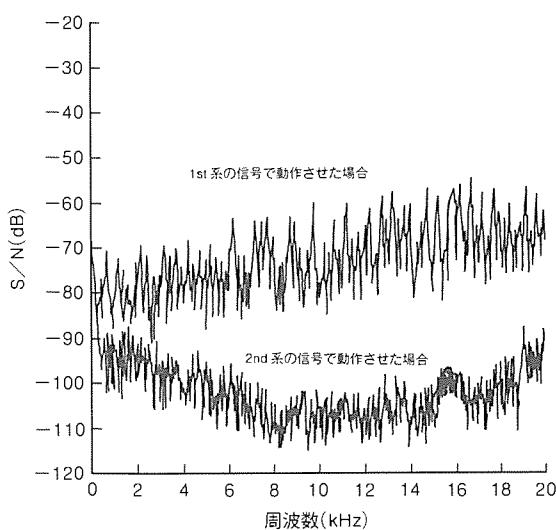

デジタルオーディオでは、符号が変化しない限り理論的に音質は変化しないとされてきた。ところが最近の研究で、デジタル信号中の符号とは関係のないジッタや波形ひずみが、アナログ部に伝達され、音質を損ねていることが明らかになった。デジタルオーディオの高音質化を図るためにには、この問題を早急に解決しなければならない。当社では、ジッタや波形ひずみを吸収し、水晶精度のデジタル信号を送り出すジッタ吸収 IC M65811FP を開発した。

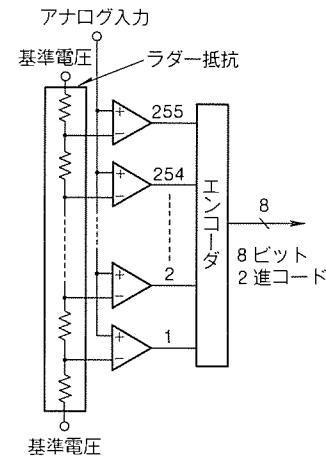

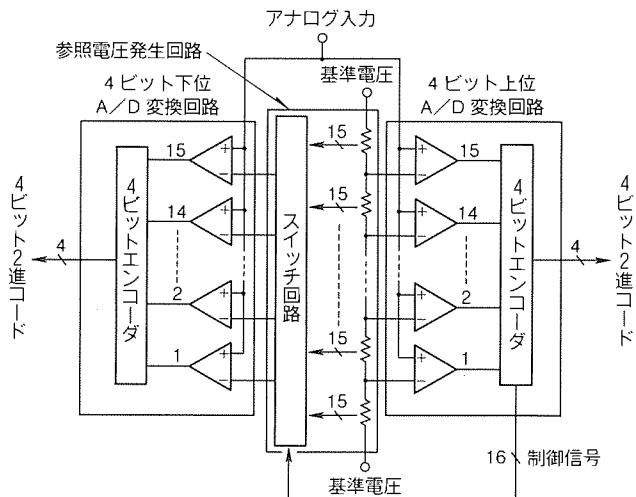

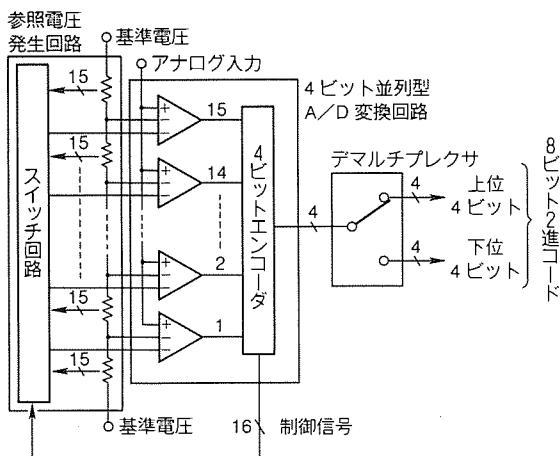

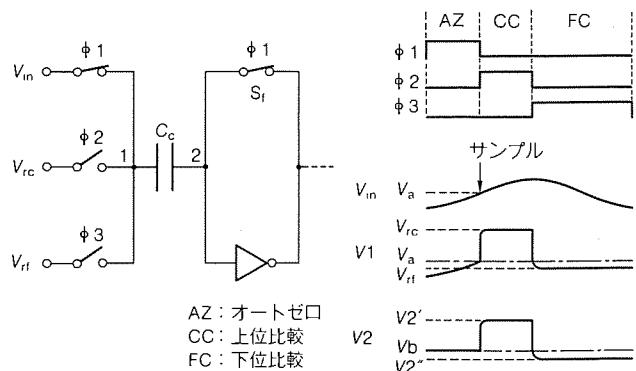

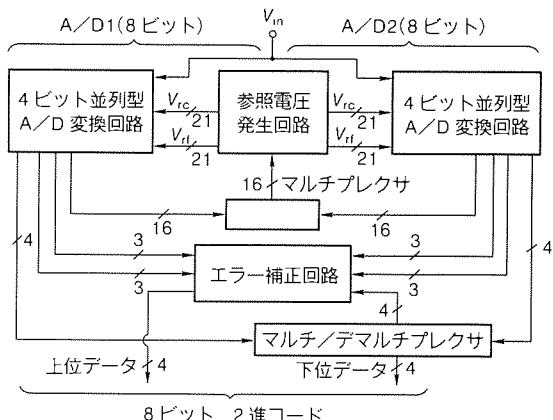

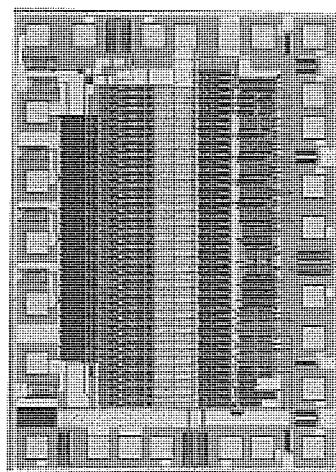

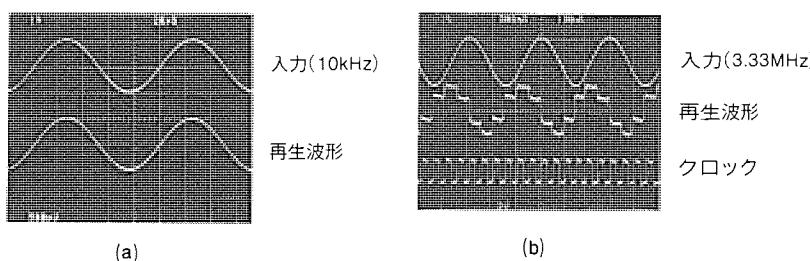

### 低消費電力・映像用 CMOS A/D コンバータ LSI

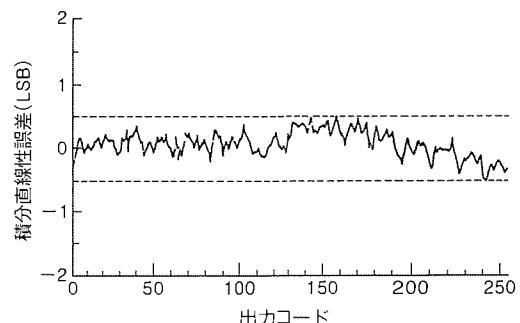

細谷史郎・三木隆博・前田 敦・矢澤信春

三菱電機技報 Vol. 65・No. 2・P 50~53

セルベース設計システムのマクロセルをターゲットとして、8 ビット、20MS/s (Mega Sample/second) 直並列型 CMOS A/D コンバータを開発した。独自のユニファイド アーキテクチャを用いることにより、低消費電力化(80mW)、小面積化(パッドと出力バッファを除くセル領域の面積: 2.2mm<sup>2</sup>)を実現した。これらの特徴は、セルベース設計システムにおけるマクロセルとして有用である。

# Abstracts

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 29~34 (1991)

## The M60060 Series 1.0 $\mu$ m CMOS Gate Arrays

by Masahiro Suzuki, Hirotaka Nakamura, Hiroyuki Nunogami, Shinji Ono, Mami Takiguchi & Toshiyuki Fukumizu

The article reports on the features and technology of the M60060 Series 1.0  $\mu$ m CMOS gate arrays employing double-layer metal coupled with the latest in assembly technology. It also offers high speed and low power dissipation, allowing its use in high-pin-count plastic QFPs.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 2~8 (1991)

## Trends in Systems and the Present and Future of ASICs

by Masao Yoshitomi, Heiichi Matsumoto, Shigeyuki Nita & Yoshinori Motoyoshi

The article describes the role played by ASICs (application-specific integrated circuits) in electronic systems. The development of ASIC technology has paralleled that of electronic systems as a whole, and ASICs now play a vital role as key parts in all types of systems. Various system needs combined with semiconductor-technology "seeds" have achieved these remarkable results. ASICs will become increasingly important in the future. ASIC technology will continue to evolve hand-in-glove with systems technology, eventually leading to true system-on-a-chip integration.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 35~38 (1991)

## A Methodology for the Development of ASSPs Based on a 32-Bit CPU Core

by Naiochi Kitakami, Yuichi Nakao, Masashi Oki, Mitsuyoshi Nakamura, Yutaka Kamakura & Jiro Kuromatsu

The 32-bit microprocessor core of this methodology is based on the TRON specification and offers abundant peripheral-function units. A cell-based CAD system was used to achieve a hierarchical design. A dedicated signal-description language for the peripheral-function units has simplified the man-machine interface for logic simulation, and a highly efficient modeling of logic circuits is used. The methodology greatly reduces the time, including turn-around time, and the number of steps required to develop new devices.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 9~13 (1991)

## Multilevel Interconnection Technology

by Shuji Nakao, Akihiko Osaki, Yoshifumi Takata, Toshiaki Tsutsumi, Masazumi Matsuura, Atsushi Ishii & Hideo Kotani

The article covers submicron multilevel aluminum interconnection technology, which is of vital importance to ASIC fabrication. Pad-fabrication technology that prevents silicon precipitation at metal silicon-contacts and antireflective-film technology for fine metalization patterns are discussed. Also treated is a new chemical vapor deposition (CVD) technique for producing interlayer insulation films. The method uses organic silicon source and ozone to achieve excellent film flatness at atmospheric pressures. A final topic is a CVD tungsten process that improves the yield and reliability of via holes.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 39~44 (1991)

## The Latest Trends in ASIC Packaging Technology

by Minoru Yoshida, Haruo Shimamoto, Tetsuya Ueda & Shin Nakao

Packages for ASICs are evolving toward larger numbers of pins. The Corporation has developed "heat-spreader" plastic quad flat packages for power devices having half the thermal resistance of previous products with the same package outlines. The Corporation has replaced wire bonding with TAB technology to realize low thermal resistance and lead inductance. The article introduces an extremely high-pin-count plastic tape carrier package (TCP) with an Al cap structure.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 14~17 (1991)

## A 0.8 $\mu$ m CMOS ASIC Process

by Masahiro Hatanaka, Takio Ohno, Sumio Yamaguchi, Hiroaki Morimoto & Shuichi Matsuda

The article reports on device structures and process technology suitable for fabrication of CMOS ASICs with 0.8  $\mu$ m design rule, and covers a direct-writing electron-beam method that shortens the ASIC development cycle. A key process technology involves a lightly doped drain structure with gate-N<sup>-</sup> overlapped structure that raises NMOS device reliability and allows the use of three-layer metalizations. Flat-insulation films using tetra ethyle ortho silicate (TEOS) are fabricated at low temperatures to permit the use of fine multilayer wiring configurations.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 45~49 (1991)

## An Approach to High Tone Quality in Digital-Audio Products

by Hisao Kato, Kanji Mizuno & Koichi Morioka

Recent research has demonstrated that digital-audio signals are vulnerable to random fluctuations. These studies have shown that jitter and waveform distortion accompanying otherwise error-free digital signals can enter the analog circuitry of digital music systems causing a degradation of tone quality. The Corporation has developed the M65811FP IC that absorbs jitter and waveform distortion to regenerate crystal-clock-precision digital signals for analog conversion.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 18~23 (1991)

## Module Generators for Cell-Based Designs

by Hirofumi Shinohara, Kazuhiko Tsuda, Noriaki Matsumoto, Yoshiaki Tsujishashi, Kumiko Fujimori, Yoshihiko Ajisaka & Michiko Tsukamoto

The authors have developed cell-based ASIC module generators that design SRAM, ROM, multipliers, and PLA cells for fabrication by a 1.0  $\mu$ m CMOS process. In addition to cell-size parameters, the module generators allow the designer to specify shape parameters, function options, and other design parameters with a high-degree of freedom. The module generator can generate the full set of design data for CAD tools to be integrated into cell-based ASIC design systems. The module cells are optimized for both circuit function and layout facility, leading to high integration and high-speed operation.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 50~53 (1991)

## A Low-Power CMOS A/D Converter for Video Applications

by Shiro Hosotani, Takahiro Miki, Atsushi Maeda & Nobuharu Yazawa

An 8-bit 20-megasample/s CMOS subranging A/D converter has been developed. Low power consumption (80mW) and small chip area(2.2 mm<sup>2</sup> active area) were realized by a newly developed "unified architecture." The A/D converter is also suitable for use in cell-based design systems.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 24~28 (1991)

## A 0.8 $\mu$ m CMOS Gate Array

by Masatomi Okubo, Morio Kakinuma, Michiko Kunioka, Masahiro Murai & Keiji Kawabata

The article reports on device technology and the GA-2 workstation-based design system used for M6008X Series gate arrays. These gate arrays employ a state-of-the-art 0.8  $\mu$ m design-rule CMOS process with three-layer Al metalization to yield up to 400 kilogates per chip. TAB packaging provides these devices with up to 512 I/O pins. New technologies developed for the series include a module generator for RAMs and ROMs, output buffers with slew-rate control, and a ganged-driver configuration for low-skew clock distribution.

## アブストラクト

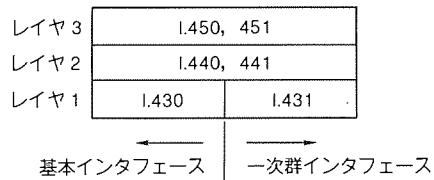

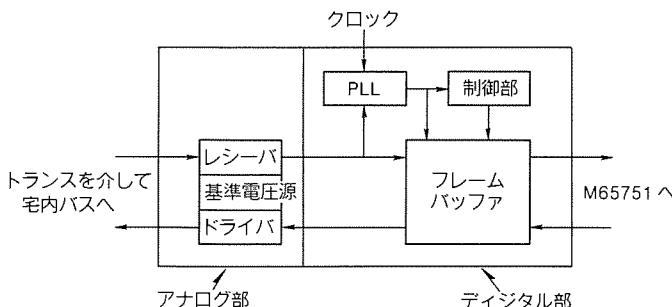

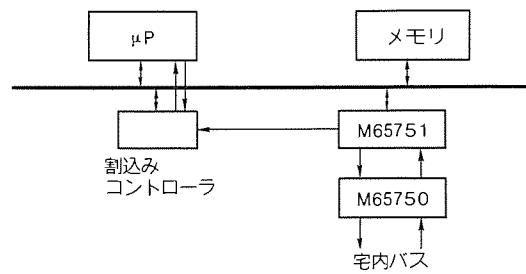

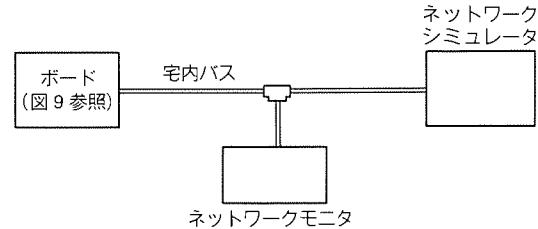

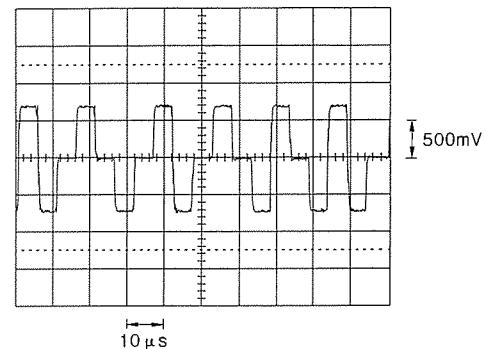

### ISDN 基本インターフェース用 LSI

中林竹雄・近藤晴房・戸永 寛・長谷川浩一・山本誠二

三菱電機技報 Vol. 65・No. 2・P 54~57

ISDN 基本インターフェース用 LSI 2 品種(M65750, M65751)を開発した。M65750 は ISDN ユーザー・網インターフェースのレイヤ 1 の全機能を実現し、M65751 はレイヤ 2 機能のうち HDLC フレーミング機能を実現する。M65750 及び M65751 は、ISDN システムにおいて、網側／端末側両方に適用可能である。M65750 と M65751 との間の接続は専用のインターフェースを用いており、これとマイクロプロセッサを用いてレイヤ 1~3 の機能が実現可能となる。

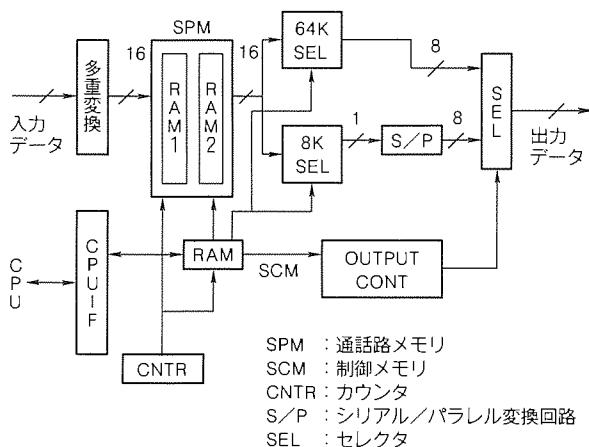

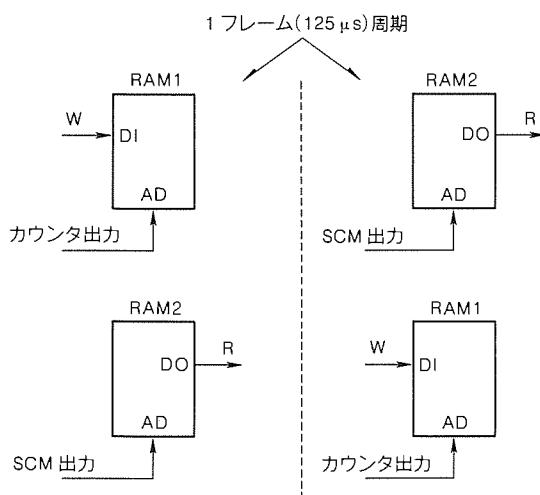

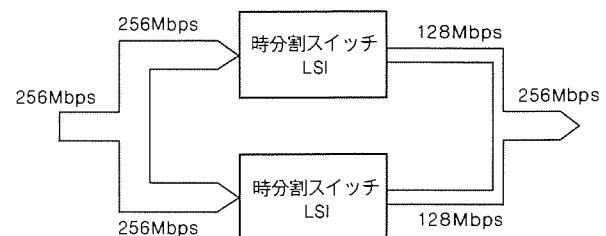

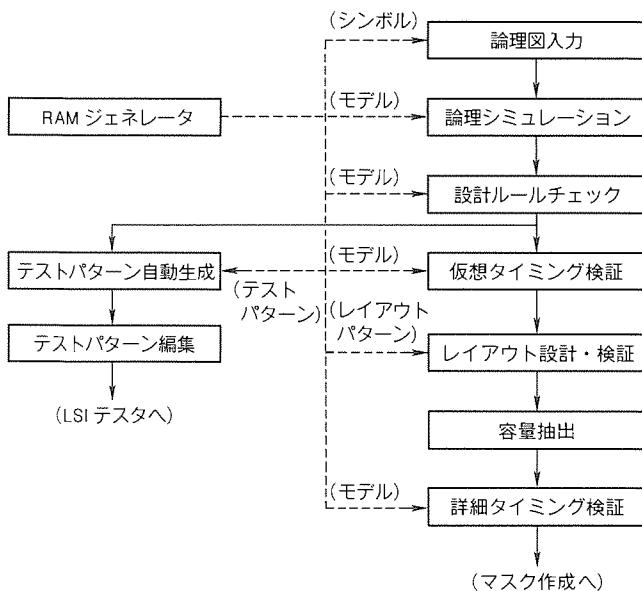

### CB-1 設計システムを用いた 8kbps 単位交換可能な大容量時分割スイッチ LSI

覚塙高音・鈴木孝昌・川畑英雄・岸田 悟・長谷川浩一

三菱電機技報 Vol. 65・No. 2・P 58~61

デジタル ネットワークを構成する PBX, TDM, TS 等の回線交換装置のキーコンポーネントである時分割スイッチ LSI を開発した。この LSI 1 個で最大  $4k \times 2k$  チャネル(64kbps/チャネル)の交換ができる。また、最近の音声圧縮技術の進展による 16kbps や 8kbps 等に圧縮された低速信号を効率良く交換するため、8kbps 単位の交換も可能である。さらに、複数のタイムスロットやビットを用いた高速チャネルの交換のため、TSSI を保証している。本稿では、この LSI について機能、特長及び設計手法を述べる。

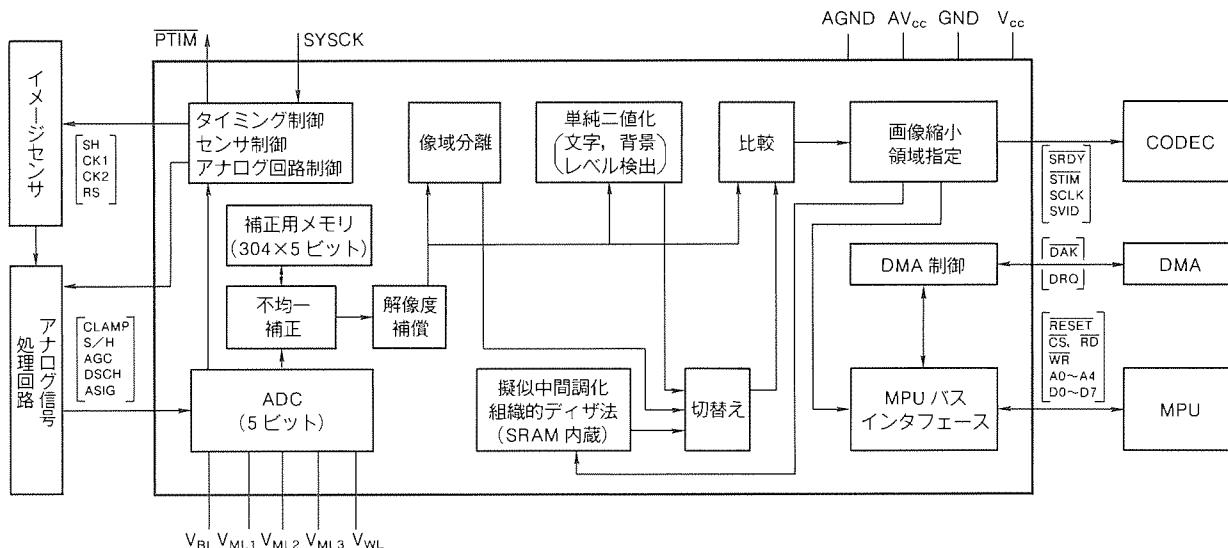

### FAX 用画像処理コントローラ M66332FP

滝 洋一郎・中林祥恵・広川祐之・瀬政孝義・永田良浩

三菱電機技報 Vol. 65・No. 2・P 62~67

G3 ファクシミリの普及機用画像処理コントローラを開発した。基本機能は、イメージセンサで光電変換された画像信号の二値化である。原稿を再現性良く白黒画像に二値化するために、不均一補正、解像度補償、ディザ化、像域分離などの画像処理機能を持たせた。また、A/D コンバータ、補正メモリの内蔵は特徴の一つである。ここでは、FAX 用画像処理の現状とこのコントローラの仕様・構成・画質シミュレーション・画質評価について報告する。

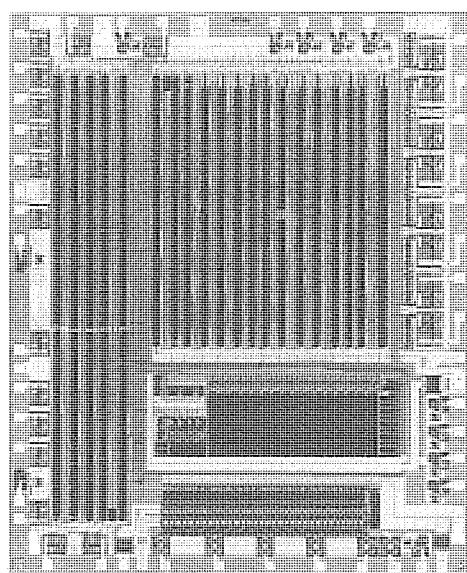

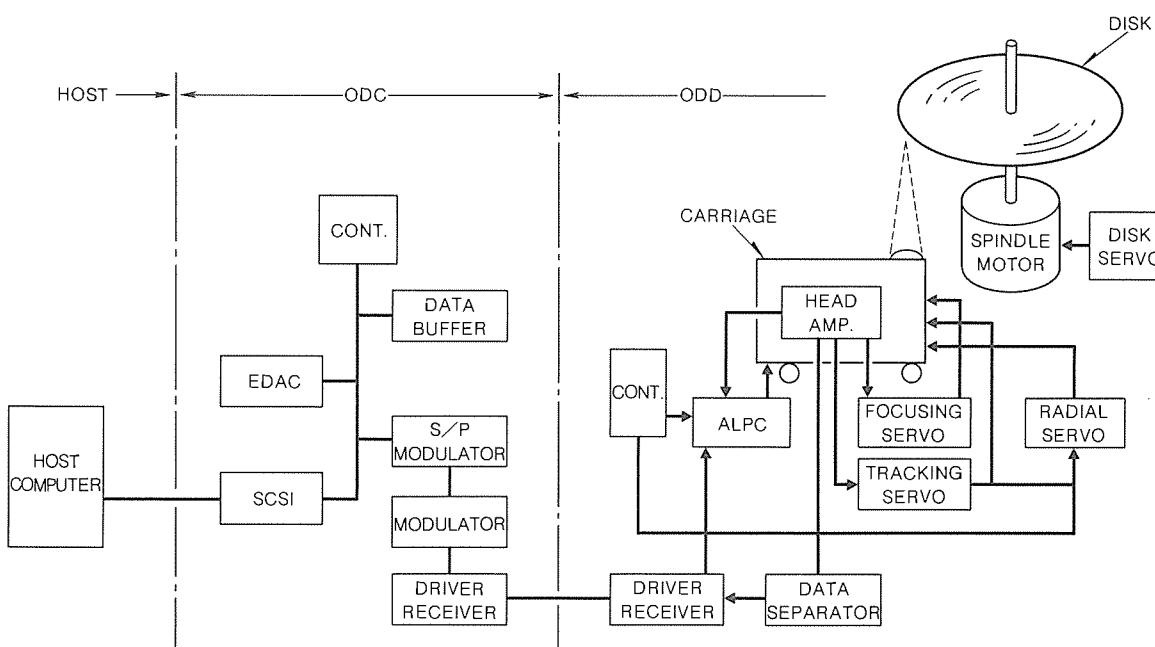

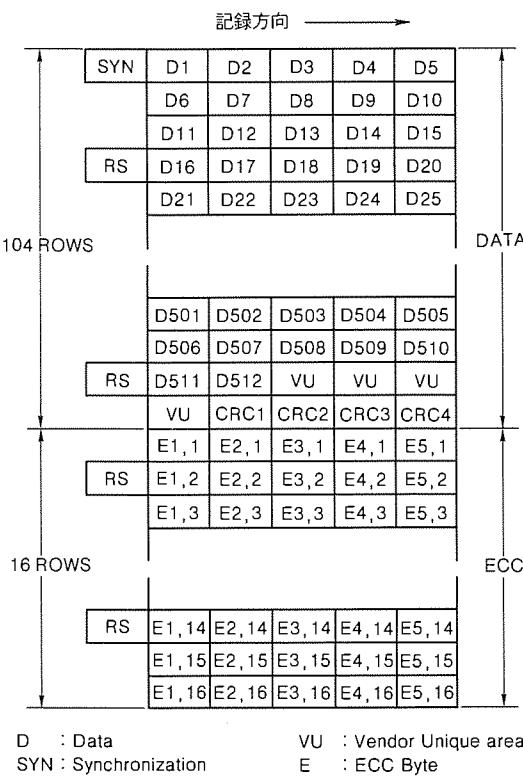

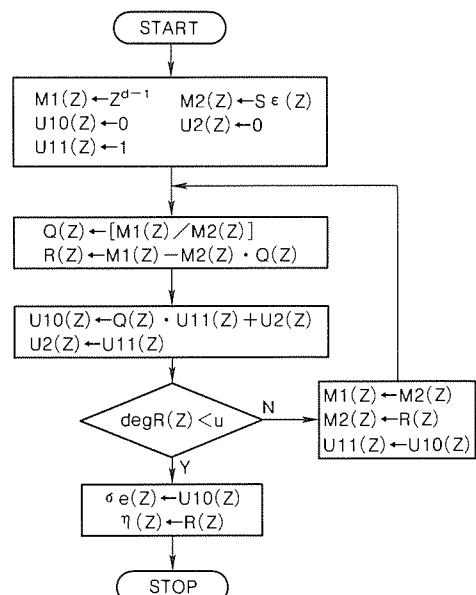

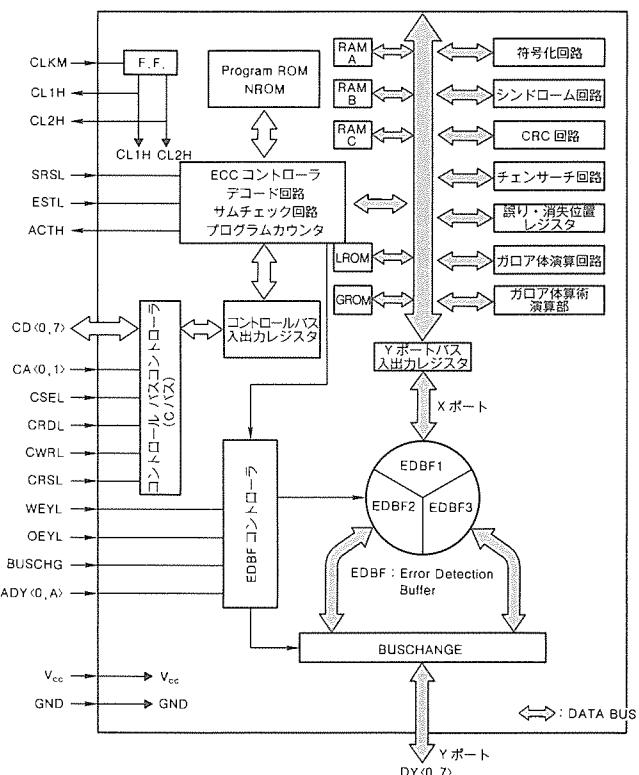

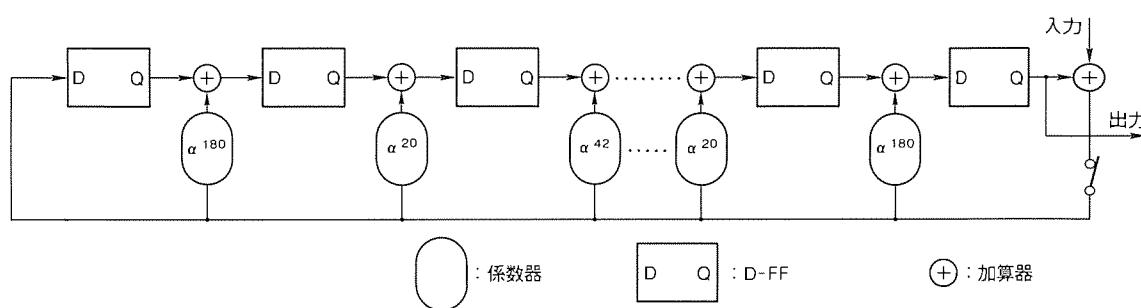

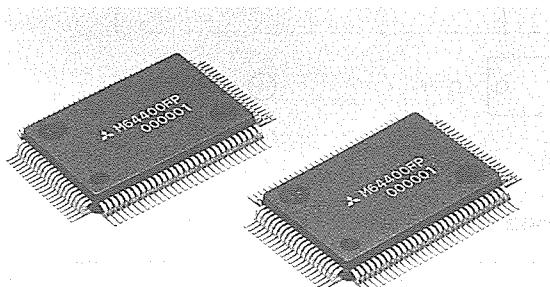

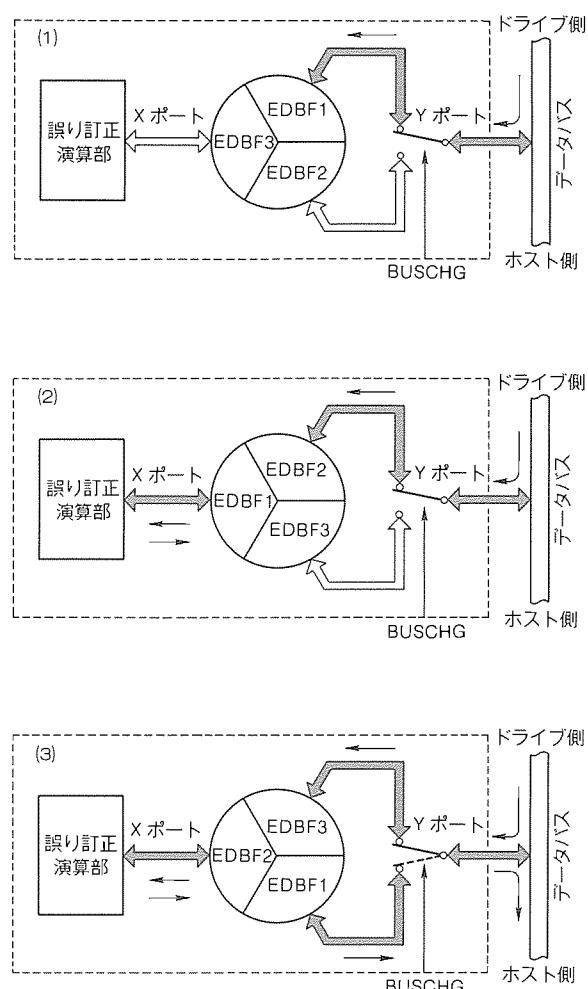

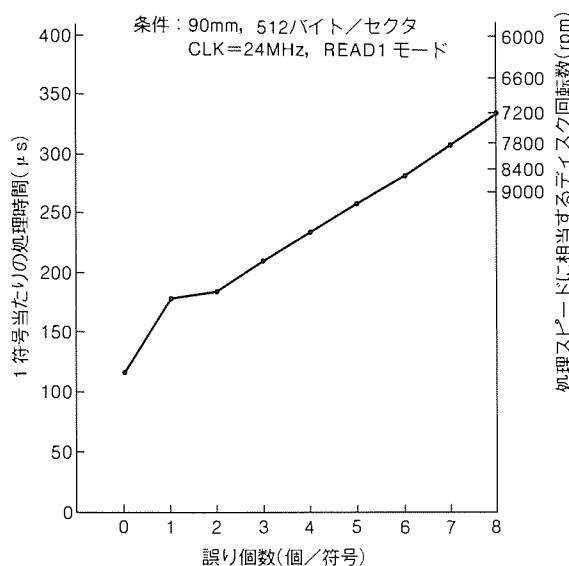

### 光ディスク用誤り訂正 LSI

森 信太郎・児玉幸夫・吉田英夫・井上 徹・清瀬泰広

三菱電機技報 Vol. 65・No. 2・P 68~73

光ディスクは、高密度・大容量で更に可搬性のある記憶媒体として期待されている。しかし、光ディスク媒体のビット誤り率が高いため、強力な誤り訂正をかけないとコンピュータ補助記憶装置として使用することができない。我々は、 $1.0 \mu\text{m}$  CMOS セルベース設計手法を用い、光ディスク用誤り検出・誤り訂正 LSI の開発を行った。この LSI 化により、訂正能力最大時におけるリアルタイム訂正が可能となった。

# Abstracts

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 62~67 (1991)

## The M66332FP Facsimile-Image Data Processor

by Yoichiro Taki, Yoshie Nakabayashi, Masayuki Hirokawa, Takayoshi Semasa & Yoshihiro Nagata

An image-processing controller IC for mass-market facsimile machines has been developed. The IC processes image data read in by an image sensor and generates bi-level image data. The IC uses nonuniform compensation, modulation transfer function compensation, a dither method, split-region processing, and other techniques to optimize the reproduction of black-and-white originals. It also contains an A/D converter and a memory for compensation values. The article discusses current facsimile-image processing technology, and reports on the specifications and configuration of the new IC. It also reports on an image-quality simulation and processed-image evaluation results.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 68~73 (1991)

## An Erasure and Error-Correction LSI for Optical-Disk Systems

by Shintaro Mori, Yukio Kodama, Hideo Yoshida, Toru Inoue & Yoshihiro Kiyose

Optical disks are a promising data-storage medium due to their high recording density, high capacity, and media portability. One drawback of the medium is a high bit-error rate. The use of powerful error-correction codes is therefore a prerequisite to employing optical disks for computer auxiliary storage. The authors have developed an optical-disk error-detection-and-correction LSI using a 1.0  $\mu$ m-design-rule cell-based CMOS LSI design system. The integrated device makes it possible to maintain real-time error detection and correction even under heavy bursts of errors requiring maximum performance.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 54~57 (1991)

## ISDN Basic Interface LSIs

by Takeo Nakabayashi, Harafusa Kondo, Hiroshi Kuranaga, Koichi Hasegawa & Yamamoto Seiji

The Corporation has developed two LSIs that perform ISDN basic interface functions. M65750 implements all the Layer 1 functions at the ISDN user-network interface. M65751 implements the Layer 2 HDLC framing functions. Both devices can be used on either the network or terminal side. Layers 1, 2, and 3 functions can be implemented by configuring a special interface and a microprocessor to link together the two LSIs.

Mitsubishi Denki Giho: Vol. 65, No. 2, pp. 58~61 (1991)

## A High-Capacity Time-Division Switch LSI Capable of Exchanging the 8kbps Channels Used in the CB-1 Design System

by Takane Kakuno, Takamasa Suzuki, Hideo Kawabata, Satoru Kishida & Koichi Hasegawa

The Corporation has developed a time-division switch LSI for use in PBXs, time-division multiplexers, tandem switches, and other digital network components. A single device can switch a maximum of  $4 \times 2$  K channels each carrying 64kbps. The LSI can also efficiently route compressed narrow-bandwidth signals of 1, 6, 16, or  $n \times 8$  kbps. Guaranteed time-slot sequence integrity makes it possible to implement complicated time-slot and bit-based high-speed channel switching. The article reports on the LSI's functions, features, and design methodology.

### ASIC 特集に寄せて

取締役副社長

技術本部長・開発本部長

工学博士 岡 久雄

LSI が産業の米とよばれるようになって既にかなりの年月がたったが、その言葉どおり、LSI はいまや社会のすみずみまで行き渡っている。またその間に、日本の半導体産業は世界トップの地位を占めるようになったが、これは主として、メモリを中心とした高集積化と高生産性に関する“HOW-TO”的技術によってなし遂げられたものである。一方、集積度の向上に伴って、1980年代の半ばから、チップの上にどのような機能を乗せるかという、いわゆる“WHAT”的問題が重要視されるようになってきた。すなわち、ASIC 時代の到来である。

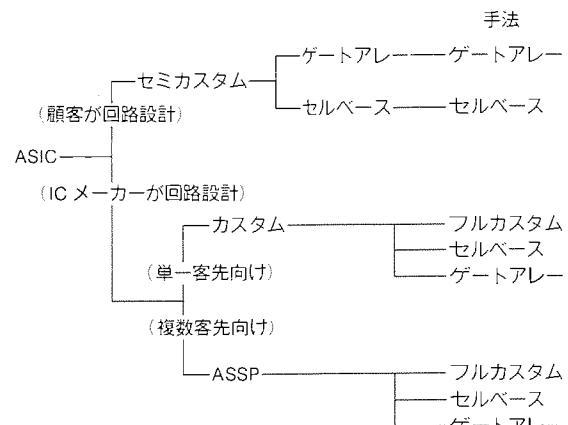

ASIC (Application Specific IC) には、大別して、フルカスタム IC, セミカスタム IC, ASSP (Application Specific Standard Product) の三種類がある。このうちフルカスタム IC は、電卓用 IC などで馴みの深いものであるが、設計に時間と労力がかかり過ぎ、種類の拡大には自ずと限界がある。このような事情により、1980年代の前半から、より短期間に開発ができ、かつユーザーの技術者にも比較的容易に設計が可能なゲートアレー、ついでセルベース LSI によるセミカスタム IC のマーケットが次第に形成され、近年になっていよいよ本格的な立ち上がりをみせている。

セミカスタム IC のうち、ゲートアレーは、自動設計を旨とし、ユーザーの技術者にも設計可能であり、かつ、ターンアラウンドも速い。また、最近では、SOG (Sea of Gate) 方式が普及して面積効率が上がり、マクロセルもある程度取り込めるようになってきたので、マーケットの拡大が一層加速されている。一方、セルベースシステムは、ゲートアレーに較べて設計の自由度は大きい利点があるが、セルライブラリの整備にかなりの時間がかかるため、ゲートアレーよりは高性能が必要なものへの展開が期待される。セミカスタム IC に共通した一つの問題は、ベンダー・

ユーザー間の CAD システムのマッチングである。CAD システムの選択はベンダー・ユーザー間で異なることが多く、更には、一つのベンダーやユーザーの中でも何種類かの CAD システムが使われていることが珍しくない。この問題は、今後解決しなければならない重要な課題である。

ASSP は、文字通り応用に特化した標準品であり、ある程度のフレキシビリティを持たせるために、RAM/ROM を組み込んで、プログラムにより多少の機能選択ができるようにしてあるのが普通である。ASSP は、最先端に近いプロセスを使用し、かつ、半導体を熟知したベンダー(半導体メーカー)側の設計者が設計するので、性能、生産性共に優れたものができる。

ところで、ASIC という言葉が普及して以来、ASIC であれば少量でも低価格で容易に入手できるという錯覚を抱くユーザーが少なくない。しかし、“同じ物をより多く作るほど安くなる”という半導体の原則は依然として生きている。したがって、全体システムをどのように分割し、それぞれの部分をいかなる手法で LSI 化するか、機能/コストをいかに最大化するかは、ユーザーにとって大変重要な判断となる。また性能に関しプロセスはやはり重要なファクタであり、そのための投資は設計に対するそれを遙かに上回る。設計、プロセス、CAD を総合的に有効に活用することがメーカーにとっての重要な判断である。

当社は、ASIC の分野特にセミカスタムの分野においては、従来、どちらかと言えば社内向けに重点を置いて技術の蓄積を進めてきたが、いよいよ本格的な外販の拡大にも乗り出す。本特集号は、当社の ASIC 技術と製品群の一部を紹介したものである。顧客の皆様方の暖かいご支援をお願いしたい。

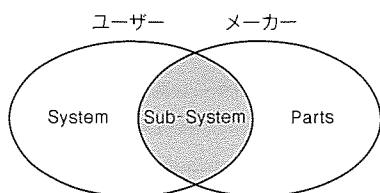

# システムの動向と ASIC の現状と展望

吉富正夫\* 元吉啓登\*

松本平八\*\* 仁田重之\*

## 1. まえがき

1947年世界で初めてトランジスタが実用化されて以来、約45年になる。この間ゲルマニウムからシリコン、トランジスタからLSIへと発展してきた。半導体は、電子機器と一体となって成長してきたが、中でもメモリはコンピュータの進展に大きく寄与し、マイクロコンピュータ（マイコン）はパソコンや家庭機器に広く用いられてきた。さらに、ASIC（Application Specific IC）は電子機器の中に広く用いられており、システムの中のキーデバイスとしての重要性をますます強めている。

本稿では、システムの中におけるASICの役割と今後の展望について述べる。

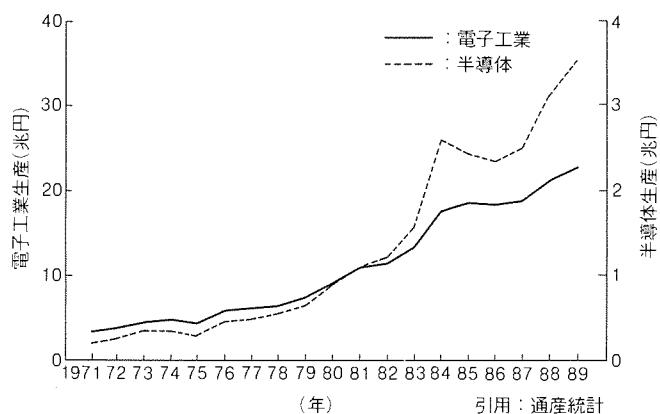

## 2. 電子機器と半導体

半導体は、電子機器の発展とともに成長してきた。図1に日本における電子工業と半導体の生産推移を示す。図からも分かるように、半導体の成長率（17.3%/年）は電子工業の成長率（11.3%/年）よりも高い。特に、1980年代からの半導体の成長は目覚ましく、電子工業の中に占める比率も10%を超え、今後とも増加の傾向にある。

半導体の成長の要因は、下記の2点にあると思われる。

- (1) 半導体が使用される機器が年々広がってきたこと。

- (2) 半導体の投入係数（半導体使用金額／機器生産金額）が増加していること。

特に、1980年からの半導体の急速な伸びは、パソコンのような多量のメモリを使用するシステムの出現や、システム

図1. 日本の電子工業と半導体

のアナログからデジタルへの移行が急であることによるとと思われる。

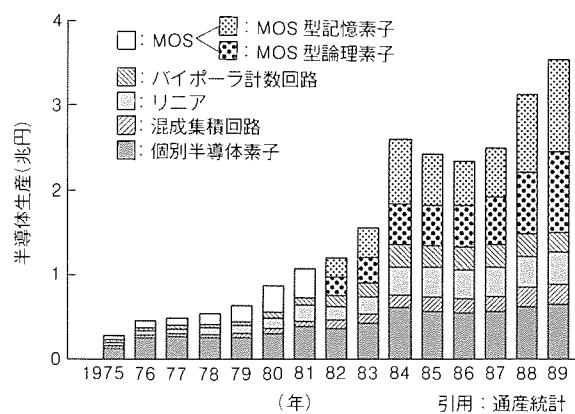

図2に日本における半導体の生産推移を示す。この中で、ASICが含まれるリニア、バイポーラ計数回路及びMOS型論理素子の伸びが大きいが、このことは電子システムの中でASICが重要な役割を果たし、システムとともに成長していることを示している。

## 3. システムにおけるASICの役割

“ASIC”の名がデータクエスト社によって1987年に提唱されてから、広く用いられるようになってきた。しかしながら、その定義はEIAJ（日本電子機械工業会）のそれとも異なっており、世界で統一された定義にはなっていない。そのため、ここでは図3に示す定義を用いて、大きくはセミカスタム（ゲートアレー、セルベース）とカスタム及びASSPに分類することにする。

図4に種々のシステムの中におけるASICの機能の実現の歴史を示す。同図からオーディオ機器、テレビ、カメラ等民生機器は、日本の電子産業の牽引役であったが、その発展の背後にASICがシステムの中心として機能していることが理解できる。1970年代の主としてバイポーラ（リニア）ICのASICから1980年代は、MOS型ASICを用いたデジタルシステムに移行しているのが分かる。

一方、パソコンを中心とする産業用電子機器では、主としてデジタルシステムに対応したMOS型ASICが多く使われている。パソコン、電話、ファクシミリ、自動車等で普及が進み、家庭で用いられるようになり数が増えるに従って、

図2. 半導体の生産推移

ASIC はゲートアレーから用途を特化した ASSP へ移行し、コストダウンを図る動向にある。

いずれの場合も ASIC がシステムの中の重要なキーデバイスとして役割を果たしている。

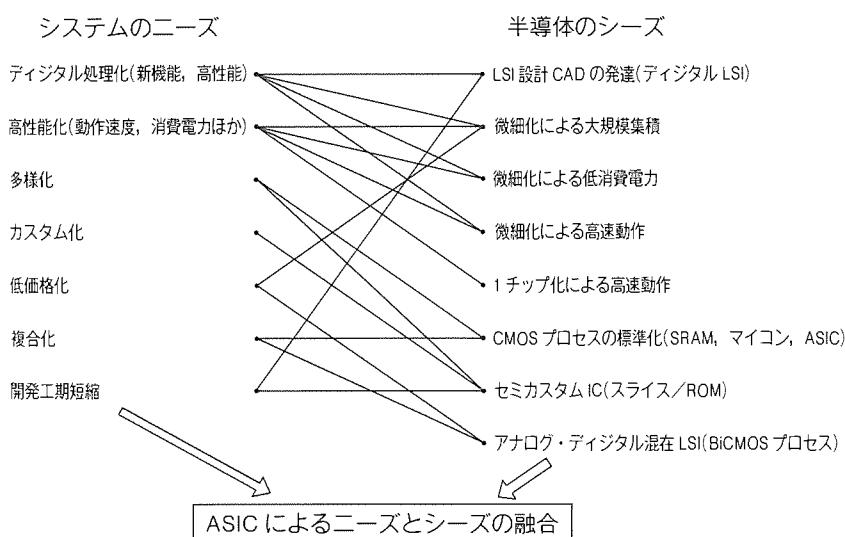

図5にシステムのニーズと半導体のシーズとの関連を示す。多くの項目について、シーズとニーズの融合が行われ、ASIC として実現されている。

各分野でデジタル処理化が行われ、システムの高性能化、新機能の追加が図られているが、これは LSI 設計 CAD の発達により、LSI 設計が容易になってきたこと、微細化による大規模集積・低消費電力・高速化が実現できるようになつたためである。

多様化・カスタム化・複合化のニーズに対しては、CMOS プロセスの標準化により、SRAM、マイコン、ASIC の複合化が容易になり、BiCMOS によるアナログ・デジタル混在 LSI が可能になってきた。

低価格化の要求に対しては、微細化技術を用いた 1 チップ化及びアナログ・デジタル混在 LSI による機能の最適化

により、対応できるようになってきた。

さらに、開発工期短縮については、LSI 設計 CAD の発達による設計期間、セミカスタム IC による試作工期の短縮が図れるようになってきた。

注 ASIC : Application Specific IC

ASSP : Application Specific Standard Product

図3. ASICの定義

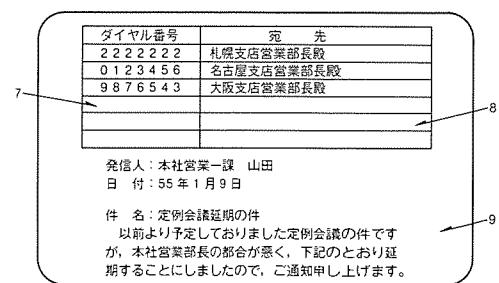

| 機器               | 年 | 1975                                      | 1980                             | 1985                              | 1990                       |                             |                         |                                  |                       |                     |                   |

|------------------|---|-------------------------------------------|----------------------------------|-----------------------------------|----------------------------|-----------------------------|-------------------------|----------------------------------|-----------------------|---------------------|-------------------|

| オーディオ機器          |   | ▼▼<br>カーステレオ/<br>ラジカセ用<br>プリアンプ<br>パワーアンプ | ▼<br>BCL ラジオ<br>周波数<br>カウント      | ▼<br>カセットテッキ<br>キーボード<br>プレーヤー    | ▼<br>DD<br>グラフィック<br>イコライザ | ▼<br>CD 用<br>DSP            | ▼<br>音場制御<br>DSP        | ▼<br>DAT 用<br>DSP                | ▼<br>衛星放送<br>PCM      |                     |                   |

| テレビ              |   | ▼<br>信号系<br>6IC                           | ▼<br>リモコン<br>信号系                 | ▼▼<br>シンセサイザ方式<br>チューナー(VS/FS)    | ▼<br>音声多重<br>4IC           | ▼<br>液晶<br>デコーダ             | ▼<br>文字多重<br>1チップ       | ▼<br>信号系                         | ▼<br>衛星放送<br>PCM      | ▼<br>クリアビジョン<br>DSP | ▼<br>MUSE<br>デコーダ |

| VTR              |   | ▼<br>信号系<br>LSI                           | ▼▼<br>リモコン<br>音声多重<br>電子チューナー    | ▼<br>デジタル<br>サーボ                  | ▼<br>ハイ<br>ファイ             | ▼<br>画質改善<br>(HO)           | ▼<br>デジタル<br>特殊再生       | ▼<br>ピクチャ<br>ピクチャ                | ▼<br>クロマノイズ<br>リダクション | ▼<br>信号系<br>DSP     | ▼<br>デジタル<br>記録   |

| VTR カメラ          |   | ▼<br>VTR<br>カメラ                           | ▼<br>小型カメラ用<br>信号処理 IC           | ▼<br>カメラ<br>一体型用<br>専用 IC         | ▼<br>AF 用<br>専用 IC         | ▼<br>CCD カメラ                | ▼<br>オートホワイト<br>バランスセンサ | ▼<br>カメラ部<br>DSP                 | ▼<br>ビデオ部<br>DSP      |                     |                   |

| カメラ              |   | ▼<br>1眼レフ<br>AE                           | ▼<br>モータ<br>ドライバ                 | ▼<br>コンパクト<br>カメラ AF              | ▼<br>AF 用<br>CCD           | ▼<br>1眼レフ<br>AF             | ▼<br>電子スチル<br>カメラ信号処理   |                                  |                       |                     |                   |

| パソコン             |   | ▼<br>FDC                                  | ▼<br>表示コントローラ<br>(CGA)           | ▼<br>表示コントローラ<br>(EGA)            | ▼<br>表示コントローラ<br>(VGA)     | ▼▼<br>チップセット                | ▼<br>表示コントローラ<br>(XGA)  | ▼<br>マルチメディア<br>対応 DSP           |                       |                     |                   |

| 電話<br>(自動車電話を含む) |   | ▼▼▼<br>ダイアラ<br>トーンリング<br>クロスポイント          | ▼<br>スピーチ<br>ネットワーク              | ▼<br>DTMF<br>レシーバー                | ▼<br>DRAM<br>音声録音          | ▼<br>静止画<br>電話              | ▼<br>コードレス<br>電話        | ▼<br>デジタル電話用<br>CODEC, TDMA, 変復調 |                       |                     |                   |

| ファクシミリ           |   | ▼▼<br>CCD<br>サーマルヘッド<br>ドライバ              | ▼<br>モデム<br>3チップ<br>(ゲート<br>アレー) | ▼<br>帯域圧縮<br>密着<br>イメージ<br>センサ    | ▼<br>画像<br>処理              | ▼<br>帯域圧縮<br>(ASSP)         |                         |                                  | ▼<br>信号処理<br>1チップ     |                     |                   |

| 自動車              |   | ▼<br>エアフロー<br>センサ<br>受信部                  | ▼<br>点火制御                        | ▼<br>エンジン制御<br>バックアップ<br>(ゲートアレー) | ▼<br>サスペンション<br>制御 DSP     | ▼<br>GPS<br>ナビゲーション<br>デコーダ | ▼<br>車載 LAN             | ▼<br>エンジン制御<br>DSP               |                       |                     |                   |

| 交換機              |   | ▼<br>クロスポイント<br>スイッチ                      | ▼▼▼<br>CODEC<br>SLIC             | ▼<br>光送受信用 IC<br>時分割スイッチ          | ▼<br>ISDN<br>チップセット        |                             |                         | ▼<br>ATM 用 LSI                   |                       |                     |                   |

注 ▼: バイポーラ(リニア) ASIC, ▽: MOS ASIC

図4. システムの中における ASIC の機能の実現

これらニーズとシーズは、すべて ASIC によって実現できる。そのため、ASIC は今後ともシステムのキーデバイスであるとともに、高い成長を続けるものと思われる。

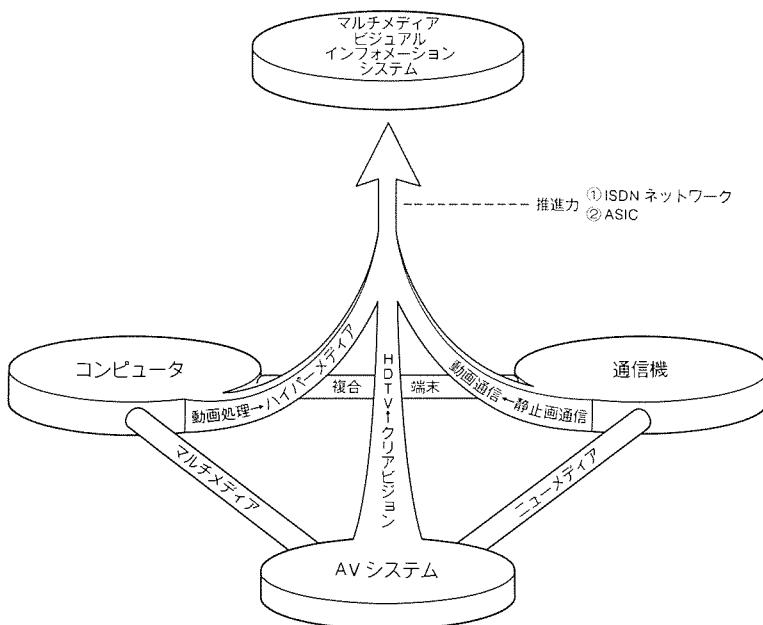

電子機器の中で主要部分を占める機器は、コンピュータ、通信機及び AV 機器であり、これらはお互いに技術革新を行いながら成長を続けている。今後これら機器は領域を広げる動向にあり、さらにシステムの複合化のニーズも相まって、三つが融合したいわゆる“マルチメディア・ビジュアル・インフォメーション システム”へ発展するものと思われる（図 6）。

これら発展の原動力になっているものは、下記の 2 点に集約される。

(1) ISDN ネットワーク網によるデジタル情報量の拡大とデータ・音声・画像伝送方式の標準化

図 5. システムのニーズと半導体のシーズ

図 6. システム進展と融合

(2) ASIC を中心とするデジタル信号処理半導体の技術革新と性能向上。

以下に、上記コンピュータ、通信機及び AV 機器について、システムの動向と ASIC の現状と展望について述べる。

#### 4. 代表システムにおける ASIC の現状と展望

##### 4.1 コンピュータ

1940 年代に発明されたコンピュータは、1950 年代のトランジスタの採用、1960 年代の IC の採用、そして 1970 年代の LSI の採用で飛躍的に価格・性能を改善することで、社会に深く浸透してきた。特に、1970 年代のマイクロプロセッサ (MPU) の発明によって用途が爆発的に拡大し、今日のコンピュータ時代の幕開きとなった。コンピュータは、もともと複雑な計算を高速に実行したいという願望から生まれた

ものであり、“より大量データのより高速処理”を至上命令として開発が進められてきた。

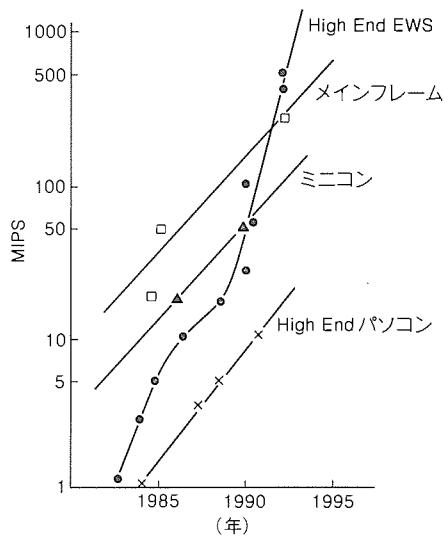

図 7 に、コンピュータの性能動向を示す。メインフレームやミニコンは、10 年間で 100 倍弱の性能向上が達成されている。High End のパソコンや EWS (Engineering Work Station) では、さらに急速な性能向上が実現されており、特に EWS では RISC (Reduced Instruction Set Computer) プロセッサの採用や Multi-CPU の導入で、ほぼビル・ジョイの法則（10 年間で 1,000 倍）に従って急激な性能向上が図られている。EWS と汎用コンピュータ

図 7. コンピュータの性能動向

を単純に MIPS 値で比較するのはあまり意味がないかもしれないが、EWS はミニコンとは 1990 年に、メインフレームとは 1992 年に性能面でクロスすることになり、High End EWS は汎用コンピュータの一部市場をも侵食して大きく伸びていく可能性がある。また、今後大きく成長すると予測されているマルチメディアが、パソコンや EWS の市場を更に大きく拡大すると思われる。マルチメディアのプラットホームとして、パソコンや EWS が使われるためである。この場合、高画質の動画を扱えることがかぎ(鍵)になると考えられ、超高速画像処理プロセッサの開発が進められている。これらコンピュータの高性能化・小型化・低価格化は、半導体の急速な微細化・高集積化によって達成されてきたとはいえる。特に 1970 年代の後半から普及し始めたゲートアレーの貢献が大きい。

表 1 に電算機分野での ASIC の概要をまとめる。汎用大型機(メインフレーム)やスーパコンピュータの CPU や周辺ロジック部はゲートアレーで構成されている。現在は ECL 中心であるが、メインフレームでは消費電力への対策から徐々に BiCMOS の使用が増加していくと考えられる。

スーパコンピュータでは、同じ消費電力の問題と更なる高速化をねらって GaAs の導入が始まっている。汎用中小型機の CPU は、現在、主にセミカスタム品(ゲートアレーやセルベース)で構成されているが、高性能化が著しい汎用 MPU(特に RISC チップ)を使い始める傾向にある。EWS の CPU は、汎用の CISC(Complex Instruction Set Computer)型 MPU が中心であったが、現在 RISC チップに急速に移行している。それぞれの RISC チップ対応で周辺ロジック部のチップセット(ASSP)が精力的に開発されており、EWS の高性能化・小型化・低価格化に寄与している。EWS や汎用中小型機では、現在 1.0  $\mu\text{m}$ CMOS が主に使われており、0.8  $\mu\text{m}$ CMOS の導入が始まったところである。2~3 年後には RISC 対応で 100MHz の動作速度が必要で、BiCMOS が必ず(須)になると思われる。パソコンは、汎用の CISC 型 MPU の世界であり、今後も当分変わりそうにない。また、de-facto 標準機が世界市場の 6 割を占めており、ここをね

図 8. 大規模集積化の現状と今後の展望

らったチップセットが、10 億ドル/年という巨大市場を形成している。技術の高いパソコンメーカーは、差別化のため、CPU 周辺部や表示部でセミカスタムを使い続けるだろう。コスト重視のため、プロセスは CMOS 中心であり、今後も変わらない。

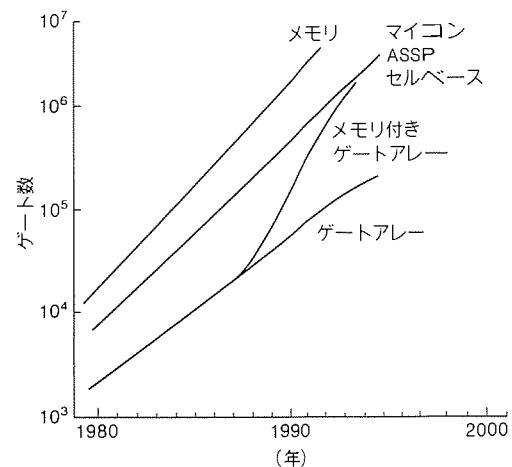

ゲートアレーはセルベースと比較し、開発期間が短かく開発コストも比較的安くできるが、チップサイズ・性能・設計に際してのフレキシビリティの点で劣る。しかし、全面敷き詰め型(SOG: Sea of Gate)のゲートアレーの登場及び CAD の改善で、ゲートアレーは短納期の特徴を生かしつつセルベースのフレキシビリティを取り込みつつある。図 8 に、大規模集積化の現状と今後の展望を示す。ASSP やセルベースは、論理 LSI としては最高の集積度を実現しているが、全面敷き詰め型のゲートアレーはメモリ内蔵の形で徐々にセルベースとの差を縮めている。

このため、当初の予測“セルベースがゲートアレーを駆逐する。”に反し、現在ゲートアレーは ASIC 市場の 60% 以上を占めている。セルベースの将来の本命は、CPU や DSP をコアとしたものであろう。また、2000 年にはトランジスタ数で  $10^8$  の集積度に到達し、この時点で文字通りのシステムオンチップが実現するだろう。

表 1. コンピュータ分野での ASIC

|                | パソコン                                                     | EWS                                                           | 汎用中小型機 | 汎用大型機                               | スーパコンピュータ                            |

|----------------|----------------------------------------------------------|---------------------------------------------------------------|--------|-------------------------------------|--------------------------------------|

| デバイス           | ASSP(チップセットが主) 中心であるが、システムの独自性を出す部分でゲートアレー セルベースが使われている。 | ゲートアレー セルベースが中心。今後は、それぞれの MPU(特に RISC) 対応で ASSP が増加していく。      |        | ゲートアレーが中心。                          |                                      |

| ウェーハプロセス       | CMOS 中心                                                  | CMOS 中心であるが、高速化のため今後 BiCMOS が導入される。                           |        | ECL 中心であるが、低消費電力化のため BiCMOS が導入される。 | ECL 中心であるが、低消費電力・高速化のため GaAs が導入される。 |

| 必要性能(1990 年時点) | • 10~33MHz<br>• 数十 K ゲート                                 | • 現在 33~50MHz が主であるが、RISC 対応で 100MHz が必要となる。<br>• 数十~数百 K ゲート |        | • 250MHz<br>• 1,000K ゲート以上          | • 300MHz<br>• 1,000K ゲート以上           |

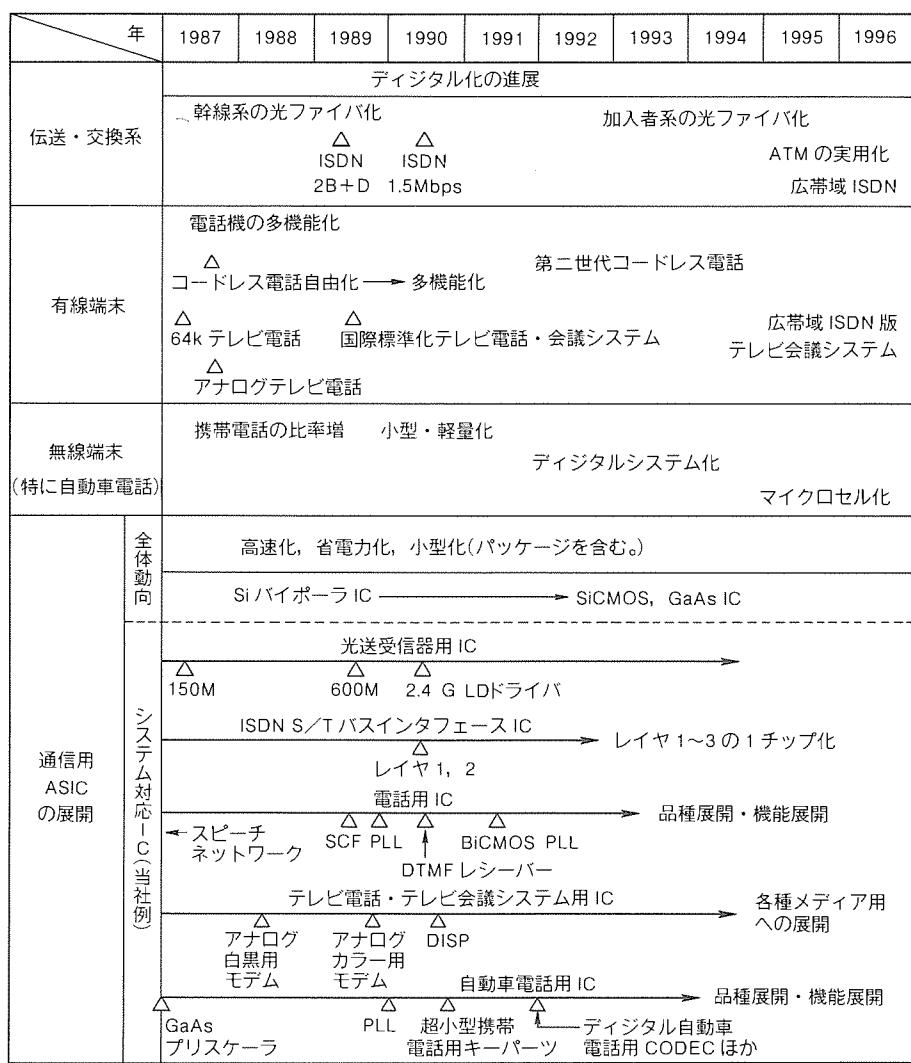

## 4.2 通信機

### 4.2.1 通信市場の動向

情報化社会の進展に伴い、通信機の役割もますます重要になってきている。通信の基盤（インフラストラクチャ）である伝送・交換系では、幹線系の高速・大容量化とデジタル化が進み、光ファイバ伝送とデジタル交換機にとって替わった。幹線系の高速・大容量化も更に進むが、広帯域ISDNでは加入者端まで150Mbps以上の通信網が広がり、各種高度な通信サービスをだれでも受けられることが可能になっていく。

端末においても、従来の電話機は多機能化が進み、移動可能なコードレス電話は国内においても自由化以降目を見張る需要の伸びを示している。また、新しいメディアとしての画像通信では、アナログ系での静止画テレビ電話、デジタル系でのテレビ電話・テレビ会議システムなどが登場している。一方、無線系では衛星通信や各種移動体通信が発展期を迎えている。自動車電話では、車載型から携帯電話に比重が移り始め、メーカーの小型・軽量化競争は激しさを増すばかりである。デジタル化の計画も目の前に迫っており、将来の需要増に対応するため、準マイクロ波帯の使用やマイクロセル化も検討されている。

図9に以上のような市場動向をまとめた。

### 4.2.2 通信用ASICの現状と展望

通信用ASICでは、バイポーラIC主体からMOS ICの使用比率が上がってきていている。また、超高速伝送や高周波化に伴いGaAs ICも使われ始めている。ASICの最近の動向と展望を図9にまとめ、以下主要なものにつき記述する。

交換・伝送系では、幹線の高速・大容量化に並行して各社でゲートアレー、セルベースを中心に先端プロセスによるASICが展開されている。光通信も採用され、光送受信器がシステムの中で重要な位置を占める。この機器用ICは、LD（レーザダイオード）ドライバ、受光増幅IC、タイミング抽出／識別再生用IC、伝送路符号化用ICでセットを構成する。新同期網には620Mbps速度対応まで実用化が進み、2.4Gbps以上の開発が精力的に進められている。速度的にGaAsによるIC構成が多くなる。

広帯域ISDNの実現に向け、ネットワークの構成を統合化するATM（非同期転送モード）交換の具体化が国内

でも進み出した。この用途にも各機能に応じた先端プロセスを使用してASICが開発されよう。

端末系では電話用として、図4にも示すようにダイアラ、トーンリング、スピーチネットワーク、DTMF（Dual Tone Multi Frequency）レシーバーなどのASICが製品化されてきた。コードレス電話の需要急増に対応して、低消費電流のPLL（Phase Locked Loop）も提供されるようになった。このICはI<sup>2</sup>Lプロセスを使用したものであるが、更なる電流低減のため、BiCMOSによる開発に拍車がかかっている。戸外でも使用可能なデジタル方式の第二世代コードレス電話が計画されており、CODEC（Coder and Decoder）、TDMA（Time Division Multiple Access）、変復調等のICが新たにキーパーツとなる。

ISDN端末では、S/Tバス・インターフェースIC、64kbpsCODEC、レートアダプタなどがキーパーツである。インターフェースICは、通常レイヤ1、2、又はレイヤ1～3までをサポートしており、これらの1チップ化が進みつつある。CODECは、現在アナログ型が中心であるが、製造プロセスの発展を考慮すると微細パターンで有利になるデジ

図9. 通信市場の動向と通信用ASICの展開

タル型へ移行していくものと予測される。

有線系の新しいメディアとして、テレビ電話・テレビ会議システムが実現している。アナログ回線を使用する静止画テレビ電話では、モデム IC、ディジタル回線を使用する動画テレビ電話・テレビ会議システムでは画像処理用 IC 等が重要である。後者の IC として、DISP (Digital Image Signal Processor) のような画像圧縮に適した DSP (Digital Signal Processor) が製品化されている。この IC は  $1.0 \mu\text{m}$  CMOS で 538K トランジスタを集積し、命令サイクル 50ns という高速性が実現されている。DSP 方式では、各種のアルゴリズムに基づいた処理への応用が可能であるが、画像通信や画像蓄積メディアは、それぞれの応用に対して世界標準化が進みつつあり、今後は各標準化に準拠したハードウェア構成の IC も展開されよう。

無線端末も市場の伸長が続いている。ASIC にとっても小型化とディジタル化が主要テーマである。既にアナログ携帯電話では超小型の競争となっており、超小型・低消費電力を目指したバイポーラ (アナログ)、MOS 各種 ASIC が開発されつつある。ディジタル自動車電話は、国内でも来年からサービスが開始される。変復調器、波形生成、音声 CODEC 等が新しく鍵となる IC である。例えば、CODEC では DSP をコアに A/D, D/A コンバータ、メモリを 1 チップに集積する動きもあり、この場合 100 万トランジスタ以上で構成される大規模な ASIC となる。小型化や低消費電力化を図るため GaAs IC で開発されるデバイスも出よう。

以上、通信用 ASIC の動向と展望を述べた。この分野に必要とされる ASIC は、伝送・交換系を中心として最先端プロセスを必須とするものから、端末系を中心にコスト重視のものまで幅が広い。しかしながら、ディジタル化の進展とともに、端末系においても高速化や小

型・低消費電力化のため GaAs も含め先端プロセスが使われるようになっており、この場合、同時に低コストを実現する手段を製品開発段階より、よく考察する必要があろう。

#### 4.3 AV 機器 (家庭用 VTR)

1974~75 年に現行のホーム用 VTR が開発され、その後各部品の改善、各技術開発によって今日のように変遷してきた。もちろん半導体もアナログ及びディジタルの小規模の汎用 IC の導入に始まり、さらに専用 IC、マイコンが大いにその進展に貢献したが、逆に VTR の発展が半導体事業を大きく拡大させることにもなった。

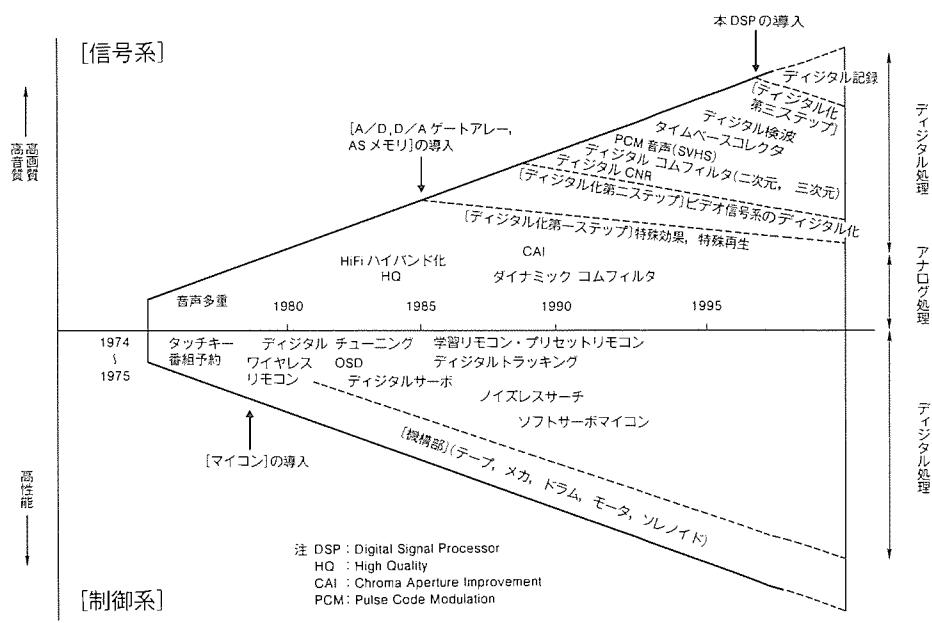

VTR の性能向上は、図 10 に示

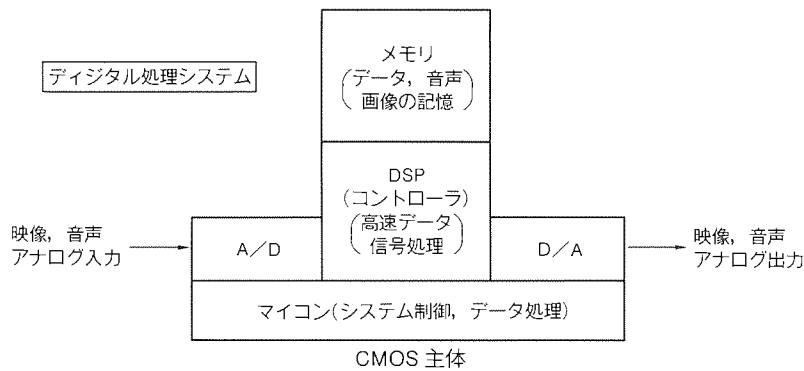

すように当初はアナログ技術を主体にした ASIC (BIP 主体) によって進められたが、1985 年ごろから信号系では DSP (コントローラ) を核として図 11 に示すディジタル処理システム、制御系では本格的なマイコン導入によって推進された。

本稿では、ホーム用 VTR の信号系のディジタル化に伴う ASIC (CMOS 主体) の現状と展望について述べる。

第 1 ステップとして、VTR のディジタル化はディジタル特殊再生機能付き VTR から始まった。これは、従来のメカ制御によるスロー、スチル、スピードサーチ等の特殊再生に加えて、メモリを使用しないとできない PIP (Picture In Picture)、モザイク画、マルチ画、ソラリゼーション、ズームアップ等の特殊効果を実現したものである。システム構成は、図 11 のディジタル処理システムに準するが、A/D, D/A、色信号用のデコーダ、エンコーダ等専用アナログ IC、TV/VTR 用に最適で、シリアル信号で入出力される画像信号をリアルタイムに記録、再生できる 500K ビットのフィールドメモリ (FSAM) とそれを制御する中枢部のメモリコントローラ及びシステム制御、データ処理用の 8 ビットマイコンからなる。標準画質の 6 ビットフル フィーチャシステムと高画質、多機能の 8 ビットのシステムがある。現在このフィーチャは、今後需要が期待できるビデオ・カラープリントに応用されている。

第 2 ステップとして、高画質化を実現するためにビデオ信号系のディジタル化が推進されている。この信号処理のために輝度信号 Y と色信号 C を分離するが、ディジタル Y/C 分離システムとして、画面の水平、垂直方向 (二次元空間) に斜め解像度を向上させた二次元適応型と二次元空間に時間方向を加え、三次元空間で信号処理する三次元動き適応型がある。前者は、入力信号に対して、相関の強い画素間に

図 10. ホーム VTR のディジタル化による機能向上

図11. AV機器のデジタル化への対応

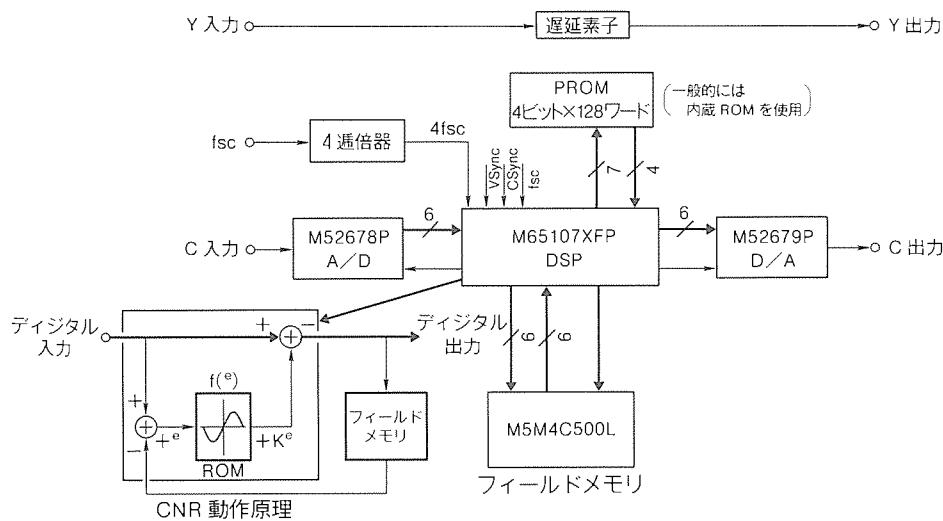

図12. 6ビットデジタルCNRシステムのブロック図

演算によるフィルタリングで Y/C 分離を行っている。後者は、クリアビジョン (EDTV) 受像機に採用されているシステムで、高性能な Y/C 分離が実現できるものの高価であるために、VTRへの導入は一部の高級機にとどまっている。

スーパー VHS では Y 信号の改善はされたが、C 信号は置き去りで、その対策としてデジタル CNR (Chroma Noise Reducer) システムで、ノイズがフィールド間の相関がないことを利用し、デジタル処理によるノイズの減少と動き適応による動画の残像の抑制を図り、改善している。このシステムには、図12に示すように 500K の FSAM 1 個で実現できるコストパフォーマンスの良い 6 ビットシステムと、高価ではあるがより高性能な 8 ビットシステムがある。なお、フレーム処理によって更に高画質にできる。次に、メモリの有効利用を図る親画面用 CNR と垂直補間を行い、高画質の PIP 機能を同時に実現する複合システムもある。

一方、長時間高画質記録のニーズから 3 倍モードの高画質化が推進され、ヘッドの改善、デジタルトラッキングの調整分解能の向上及び再生されるビデオ信号の時間軸を補正するデジタル TBC (Time Base Corrector) システムを採用し、色のちらつきの減少や低ジッタ化を図っている。

カメラ一体型 VTR では、VHS-C, 8mm 共に小型、軽量

化に拍車がかかっているが、CCD の小型化もさることながら、今後の鍵はカメラ部及びビデオ部の信号処理のデジタル化にある。ビデオ信号のデジタル処理は、その必要性、価格余裕度からカメラ一体型 VTR が据置 VTR に比較して早そうである。

高音質化は、スーパー VHS (S-VHS) でテープへのデジタル記録が画像に先駆けて現実のものになろうとしている。これは従来の VHS, S-VHS に互換性を保ちながら、BS 放送の PCM 音声 (B モード) や DAT の標準モードに対応するものである。

第3ステップにおけるデジタル記録 VTR は、画質、録画時間ともアナログ記録より有利と考えられているが、そのコンセプトは高画質、高音質、多機能及び小型化にある。その実現のために、高密度記録と画像データの圧縮技術がキーポイントとなる。しかしながら、相反する問題をかかえており、課題は多い。例えば、記録密度を上げるとビット誤

り率が高くなり、かつ画像圧縮は画質を劣化させるとともに圧縮率を上げるほど回路が大規模化及び消費電力が増大する等がある。これらデジタル処理部の小型、低消費電力化のために、半導体のシーズとしての微細化技術を更に促進させ、大規模集積化、高速動作を達成させる必要がある。この処理部は 1 チップ化を要し、デザインルールは 0.8~0.5  $\mu\text{m}$  が必要となるであろう。

これまで述べてきた各システムのオンチップ化 (ASIC 化) は、デザインルールの縮小化とともに進展するが、図11において、まずは DSP への A/D, D/A のアナログ回路 (CMOS 化) の取り込み、次に中規模メモリ、さらにマイコンとの一体化も 0.5  $\mu\text{m}$  ルールでは現実となるであろう。

## 5. むすび

システムの動向と ASIC のかかわり合いについて、幾つかの局面から述べた。ASIC がシステムの中でキーデバイスとして重要な役割を果たしてきた。今後とも自らの技術革新により、その重要性をますます高め、システムオンチップの時代を目指して、システムとともに表裏一体となって発展していくものと思われる。

# 多層配線技術

中尾修治\* 提 聰明\* 小谷秀夫\*\*

大崎明彦\* 松浦正純\*

高田佳史\* 石井敦司\*

## 1. まえがき

LSI の高集積化は着実に進められ、それをけん(牽)引する微細化技術はハーフ～クォーターミクロのレベルに達しつつある。高集積化と同時にデバイスの高速化、高機能化も進められ、これを実現する手段として多層 Al 配線の適用がほとんどすべてのデバイスで不可欠となっている。なかでも、ASIC (Application Specific IC) では配線の自由度がその機能を規定していると言って過言ではなく、多層配線の果たす役割は非常に大きい。

多層配線技術は、成膜・転写・加工等の基本要素技術の集成であり、これらを有機的に総合化することによって成立している。ユニット技術として見れば、①配線、②層間絶縁膜、③スルーホールの各技術に分けることが可能で、それぞれに必要な特性を満たすとともに相互のマッチングを取ることが重要である。

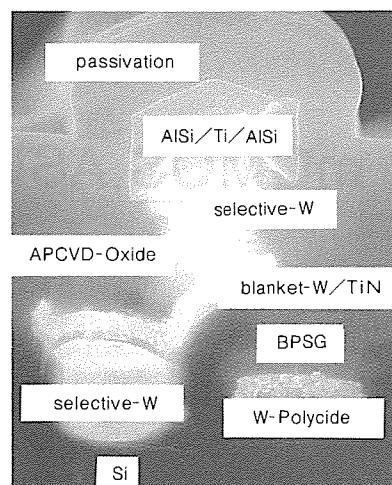

本稿では、ASIC に必ず(須)あるサブミクロン多層配線技術について報告する。以下では、まずデザインルールを概観し、続いて Al 配線、層間絶縁膜、スルーホールの各技術について述べる。

## 2. デザインルール

表1に、1.0～0.6  $\mu\text{m}$  ルールの多層配線のデザインルールを示す。第1層配線のピッチは、1.0, 0.8, 0.6  $\mu\text{m}$  ルールに対し、それぞれ 3.0, 2.4, 1.8  $\mu\text{m}$  であり、公称最小寸法(ルール)の3倍である。また、第2層、第3層配線のピッチは、それぞれ第1層の4/3倍、2倍であり、第1スルーホールの径はほぼルールで示される寸法である。

## 3. Al 配線技術

### 3.1 コンタクト電極(バリアメタル)

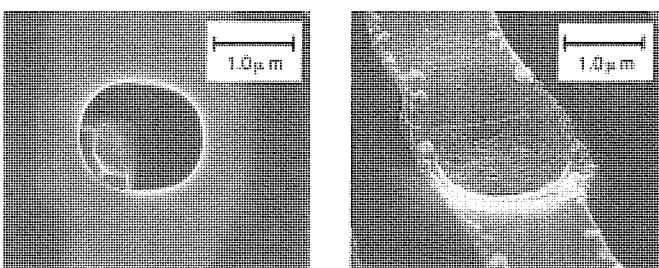

Si を含む Al 合金配線におけるサブミクロン領域のコンタ

クトホールでの深刻な問題の一つに Si 析出がある<sup>(1)</sup>。これは、ホール底部の Si 基板との界面に Al 合金中の Si が固相エピタキシャル機構により、成長することによっている<sup>(2)</sup>。この Si 析出はコンタクト抵抗の上昇を招き、著しい場合にはオープン不良となる。図1(a)は、AlSi 合金のコンタクトホールにおける Si 析出を示す SEM 写真である。ホール底のかなりの部分が析出した Si によって覆われており、導通が困難な状態となっている。

この問題を解決するためには、Al 合金の下に高融点金属やそのシリサイド、窒化物を、Si の移動を阻止するバリアメタルとして形成することが有効である。なかでも、TiN/TiSi<sub>2</sub> の2層構造は安定性に優れ良好なコンタクト特性が得られる<sup>(3)</sup>。図1(b)は、TiN/TiSi<sub>2</sub> 電極を用いたコンタクトホールの SEM 写真である(図1(a)と同じように Al 合金形成、熱処理の後、AlSi を除去している)。図から TiN/TiSi<sub>2</sub> 電極を用いることにより、Si 析出が発生していないことが分かる。

### 3.2 Al 配線

主配線体である Al 合金は、配線の信頼性の確保のために最も重要なものである。配線の信頼性不良の代表的なもの一つに、電流を担う電子によって Al 原子が移動することに起因するエレクトロマイグレーションがある。この不良は、従来はバイポーラデバイスにおいて問題化していたが、配線の微細化に伴い電流密度が増加し、MOS デバイスでも問題となってきた。

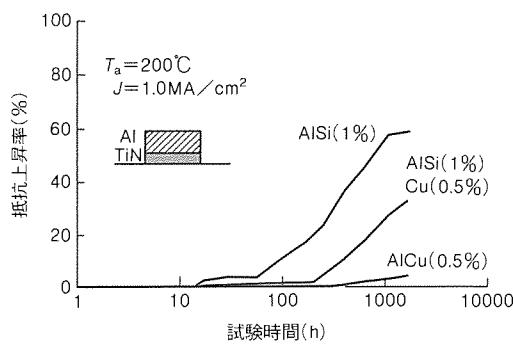

このエレクトロマイグレーションに対する耐量の向上には、Al に Cu<sup>(4)</sup>、Ti<sup>(5)</sup> などの金属を不純物として導入することが有効である。図2に AlSi (1%)、AlSi (1%) Cu (0.5%) 及び AlCu (0.5%) 配線のエレクトロマイグレーション試験の結果を示す。Cu の添加により、抵抗上昇に至る

(a) AlSiのみ

(b) AlSi/TiN/TiSi<sub>2</sub>

図1. コンタクト部の SEM 写真(AlSi 除去後)

時間すなわち寿命が長くなっている、高信頼化が可能であることが分かる。

また、配線の微細化に伴う新たな信頼性不良として、ストレスマイグレーションが問題となっている<sup>(6)</sup>。この不良は、配線に働く応力によると考えられており、電流を流さず高温状態(約200°C)に保存するだけで発生する。このストレスマイグレーションに対しては、配線をカバーする絶縁膜の低応力化が有効であるが、先に述べたエレクトロマイグレーションと同様に、Al合金にCuを添加することでも大幅に改善されることが知られている<sup>(7)</sup>。

### 3.3 反射防止膜(ARC)

Al配線の形成はSiウェーハ上にトランジスタなどの素子や多結晶Si、高融点金属系材料などによる配線が形成された後に行われるため、層間絶縁膜の平たん化が行われているとはいえ、厳しい段差上で微細パターンを転写することが必要となる。これに加え、Al合金は反射率が高くハレーションにより、精密な転写が困難となる。また、スルーホールの転写においても同様の現象により、精密なパターン形成が妨げられている。

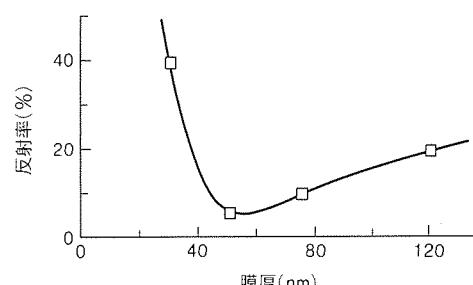

このようなAl合金の高反射に起因する問題の解決法として、Al合金膜上に反射防止膜(ARC)を形成し、反射を低減する方法があげられる。このARC材料としては、高融点金属及びそのシリサイド、窒化物、アモルファスシリコン(a-Si)などがプロセスの整合性より有力な候補と考えられる。表2にAlSiCu膜上に各種の膜を形成したときのg線(436nm)及びi線(365nm)光の反射率を示す。AlSiCuのみの場合に比べ、ARCを形成することにより、反射率が低減されることが分かる。図3に特に反射率の低いTiNに注目し、

表2. Al上に形成した薄膜の反射率

| 材 料<br>(膜厚 nm) | W<br>(50)     | TiN<br>(50) | WSi<br>(50) | a-Si<br>(20) |

|----------------|---------------|-------------|-------------|--------------|

| 反射率(%)         | g線<br>(436nm) | 55          | 5           | 57           |

|                | i線<br>(365nm) | 54          | 5           | 60           |

注 蒸着Alを100%とした。

図2. Cu添加Al合金のエレクトロマイグレーション特性

その膜厚と反射率の関係を示す。反射率は膜厚に依存し約50nmで最小となり、TiNなどの透過性の膜では形成膜厚の制御が重要であることが分かる。

図4に、段差上に形成した本来一定の幅を持つべきAl配線のSEM写真を示す。(a)はARCなし、(b)はARCを用いたものである。ARCによって下地段差の影響の少ない、マスクに忠実なパターンの形成が可能となっている。

### 4. 層間絶縁膜技術

層間絶縁膜は、多層配線において文字どおり上下の配線層を電気的に絶縁するためのものである。このため、絶縁性に優れ、低欠陥密度、低比誘電率であり、配線体との整合性が良いことが必要である。さらに、層間絶縁膜には下層配線や接続孔により、形成された段差を平たん化するという重要な役割が課されている。すなわち、サブミクロンレベルの配線スペースや接続孔部にボイド(空洞)を形成することなしに絶縁膜を埋め込むとともに、その表面を平たんにすることが要求される。現在の層間絶縁膜技術における開発の大部分は、この平たん化法の開発にあると言つうことができる。

表3に種々の平たん化法の方式・特長・問題点などを示す。これらの中でSOG(塗布ガラス)による方法は、装置、プロセスが簡便なため最も広く使われてきたものである。しかし、パターンの微細化に伴い、接続孔部などでのクラックやボイドの発生が問題となっている。

SOGに代わるものとして、有機シランを材料とするCVDによる酸化膜がその優れた平たん化特性により、注目されている<sup>(8)</sup>。なかでも、テトラエトキシシラン(TEOS)とオゾン(O<sub>3</sub>)を用い常圧CVDにより形成した酸化膜(以下“AP-TEOS酸化膜”という)は画期的な埋め込み、平たん化特性を持っている。以下に、このAP-TEOS酸化膜の形成及び層間絶縁膜への適用について述べる<sup>(9)</sup>。

図3. TiNの反射率の膜厚依存性

(a) ARCなし

(b) TiNをARCとして使用

図4. ARCによるAl配線/パターン転写特性の改善

表3. 絶縁膜の形成技術及び平たん化技術

| 方 式     |            | 原 理          | 模 式 図                                       | 特 長                          | 問 題 点                    |

|---------|------------|--------------|---------------------------------------------|------------------------------|--------------------------|

| 形 成 技 術 | 有機シラン系 CVD | プラズマ CVD     | 表面反応が支配的なプロセス                               | 膜質がよい<br>コンフォーマル<br>形状に近い    | 従来法からの改<br>善が少ない         |

|         |            | 減圧 CVD       |                                             | コンフォーマル<br>形状                | 膜質<br>クラック耐性             |

|         |            | 常圧 CVD       |                                             | 狭い隙間を埋め<br>込める<br>フロー形状      | 膜質                       |

|         | 加工整形       | バイアススパッタ     | 膜形成と同時に<br>スパッタエッチ<br>を行い角をとる。              | シンプル（膜形<br>成と同時に平た<br>ん化できる） | 平たん性のパ<br>ターン依存性ダ<br>メージ |

|         |            | バイアス ECR CVD |                                             |                              |                          |

|         | 塗 布        | 無機 SOG       | 液体のため凹部<br>に厚くたまる。                          | 工程が容易<br>処理能力が大き<br>い        | 膜質<br>クラック耐性             |

|         |            | 有機 SOG       |                                             | 無機 SOG より<br>厚く塗布できる         | 酸素プラズマ耐<br>性             |

|         |            | 有機樹脂         |                                             | 工程が容易<br>低誘電率                | 加工性<br>膜質                |

|         | リフロー       | 高温熱処理        | 熱処理によって<br>軟化する。                            | 工程が容易                        | 高温熱処理が必<br>要             |

| 平たん化技術  | エッチ<br>バッ  | (スパッタ)エッチ    | (スパッタ)<br>エッチによって<br>角をとる。                  | 工程が容易                        | 従来法からの改<br>善が少ない         |

|         |            | マスク材         | マスク材（レジ<br>スト）を塗布し,<br>平たんな表面を<br>エッティングする。 | 汎用性                          | 制御性                      |

#### 4.1 AP-TEOS 酸化膜の平たん化特性

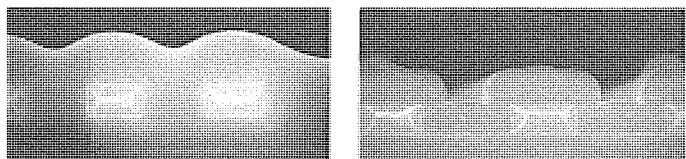

図5(a)に段差上にAP-TEOS酸化膜を形成したサンプルの断面SEM写真を示す。また、(b)は一般的な層間絶縁膜材料である、シラン( $\text{SiH}_4$ )及び亜酸化窒素( $\text{N}_2\text{O}$ )を材料とするプラズマCVD酸化膜のものである。AP-TEOS酸化膜によって配線スペースが埋め込まれるとともに、あたかも高温熱処理により、リフローしたガラスのように滑らかな表面形状が実現されており、プラズマCVD酸化膜に比べて形状特性が飛躍的に優れていることが分かる。

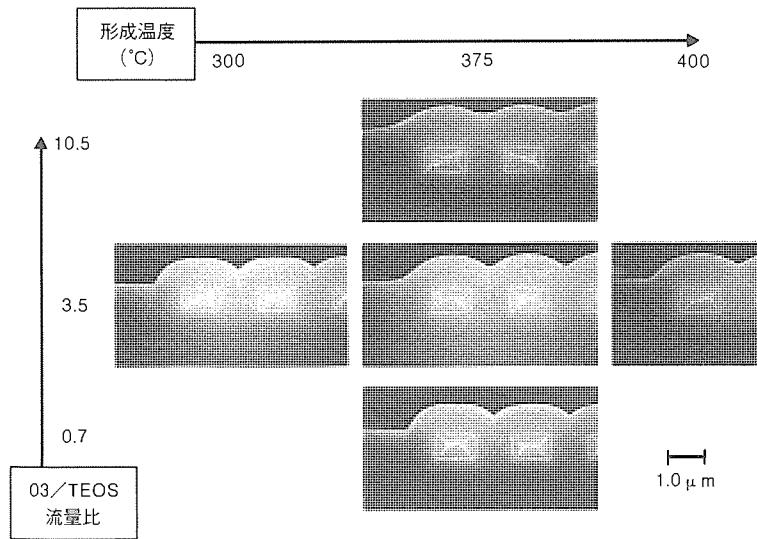

図6は、形成条件による平たん性の変化を示す断面SEM写真であり、変化させたパラメータは形成温度及び $\text{O}_3/\text{TEOS}$ 流量比である。形成温度について見ると、 $300^\circ\text{C}$ 、 $450^\circ\text{C}$ に比べ、 $375^\circ\text{C}$ で形成したものが優れており、形成温度には最適値があることが分かる。 $\text{O}_3/\text{TEOS}$ 流量比に対しては、大きくなるほど表面がより滑らかになる。

#### 4.2 AP-TEOS酸化膜の層間絶縁膜への適用

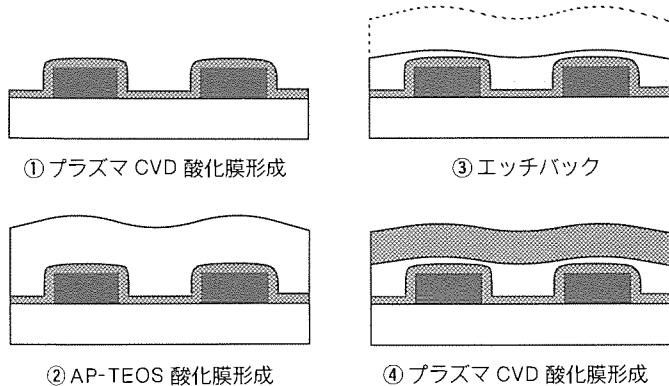

図7に、AP-TEOS酸化膜を用いた層間絶縁膜の形成フローを示す。Al配線形成後、まずプラズマCVD酸化膜を薄く形成する。これは、TEOSを材料とする常圧CVDの形

(a) AP-TEOS 酸化膜 (b) プラズマ CVD 酸化膜

図5. 低温形成酸化膜のカバレッジ

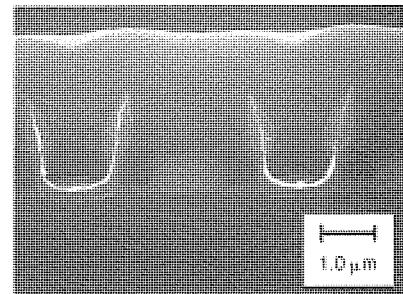

成特性が表面状態に敏感なため<sup>(10)</sup>、均一な表面を作るためである。次に、AP-TEOS酸化膜を厚く形成して下地段差部を埋め込み、平たん化した後、エッチバックによってさらに平たん性を向上する。続いて、絶縁性に優れるプラズマCVD酸化膜を形成し必要な膜厚とする。図8は、このフローで形成した層間絶縁膜の微細コンタクトホール部での形状を示す断面SEM写真である。ボイド、クラックの発生なくコンタクトホールが埋め込まれ、かつ平たん化されていることが分かる。

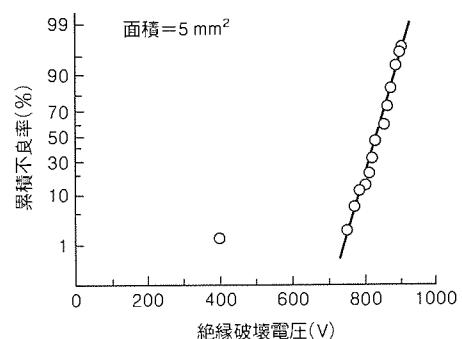

図9に、このプロセスによる層間絶縁膜の絶縁耐圧の分布を示す。横軸は印加電圧、縦軸は累積不良率である。平均耐圧は約800Vを示し、また分布もシャープで欠陥も少なく、

図6. AP-TEOS酸化膜の形成条件による平たん性の変化

図7. 層間絶縁膜の形成フロー

優れた絶縁性を持っていることが分かる。

## 5. スルーホール技術

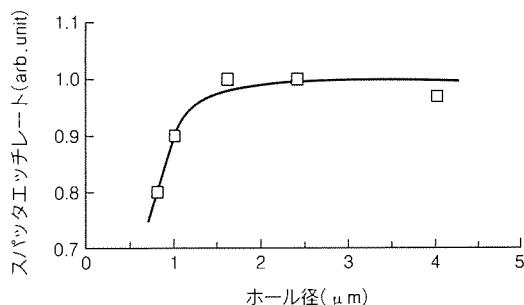

上層と下層のAl配線をつなぐスルーホールも微細化とともに信頼性上の問題を生じる。この問題の多くはホール径の減少と、径が小さくなるのに比べ、層間絶縁膜厚が薄くならないことにより生じるアスペクト比の増大に起因している。例えば、上層のAl配線をスパッタで形成するとホールの側壁での膜厚が小さくなり、エレクトロマイグレーション耐性の劣化を招く。また、ホール底部の下層Al表面をクリーニングするための逆スパッタエッチングにおいても、底部に到達するArイオンの減少によるエッチング速度の低下や、ホール側壁によってスパッタされた絶縁物がホール底部に再付着することによる不良などがある<sup>(11)</sup>。図10にRIEのみにより、ほぼ垂直な側壁を持つように形成したホール底部での、Siのスパッタエッチレートの径依存性を示す。径が、約1.0 μmより小さくなるとエッチレートが減少することが分かる。

このようなアスペクト比の増加に起因する問題に対し、テープエッチングによって実効的にアスペクト比を小さくす

図8. AP-TEOS酸化膜を用いた層間絶縁膜の微細コンタクトホール埋め込み特性

図9. 層間絶縁膜の絶縁耐圧分布

図10. ホール底部でのスパッタエッチレート

る方法をあげることができる。その一例として、ウェットエッチングとRIEの複合によるテープエッチングで形成したスルーホールでの上層Alのカバレッジを示す断面SEM写真を図11(a)に示す。(b)に示したRIEのみによって形成したものに比べ、ホールの側壁に形成されるAlの膜厚が厚くなっていることが分かる。

しかしながら、このテープエッチングを用いると最も接近するホールが重ならないようにするために、配線のピッチを大きく形成したホール入口の径より小さくすることが困難であり、微細化の点からは十分な方法とは言い難い。これを克服する方法として、埋め込み特性のよいCVD法によりホールに金属を埋め込む技術が有望視されている<sup>(12)</sup>。図12に選択CVD法により、タンゲステンを微細ホールにのみ形成したサンプルのSEM写真を示す。ホールがタンゲステンにより、埋め込まれていることが分かる。今後の微細化スルーホールに不可欠な技術であり、実用化が急がれている。

(a) テーパエッチ (b) ストレートエッチ(RIEのみ)

図11. スルーホールでの上層 Al のカバレッジ

## 6. む す び

以上、最先端 ASIC に必須であるサブミクロン多層配線技術について述べた。微細化に伴う問題を克服して、高信頼、高歩留まりを確保することが必要であり、①微細転写・加工技術、②配線材料、構造技術、③平たん化技術、④ホールへの金属埋め込み技術、などを駆使することによってその実現が図られている。

先に述べたように、ASIC のみならずすべての LSI にとって多層配線が不可欠となってきており、多層配線技術は製品の歩留まり・性能・信頼性を支配するキーテクノロジーの位置を占めている。今後さらに、ハーフヘクオーターミクロン多層配線の実用に向け、Cu 配線や有機樹脂による層間絶縁膜などの新技術の開発により、微細化と高信頼化という相反する課題を克服することが求められている。

## 参 考 文 献

- (1) Mori, M. : Resistance Increase in Small-Area Si-Doped Al-n-Si Contacts, IEEE Trans. Electron Devices, ED-30, p.81 (1983)

- (2) Majini, G., Ottaviani, G. : Large-Area Uniform Growth of <100> Si through Al Film by Solid Epitaxy, Appl. Phys. Lett., 31, p.125 (1977)

- (3) Okamoto, T., Shimizu, M., Oosaki, A., Mashiko, Y., Tsukamoto, K., Matsukawa, T., Nagao, S. : Simultaneous Formation of TiN and TiSi<sub>2</sub> by Lamp Annealing in NH<sub>3</sub> ambient and its Application to Diffusion Barriers, J. Appl. Phys., 62, p.4465 (1987)

- (4) Merchant, P., Cass, T. : Comparative Electromigration Test of Al-Cu Alloys, Rel. Phys. Symp., p.259 (1984)

- (5) Fisher, F., Neppl, F. : Sputtered Ti-Doped Al-Si for Enhanced Interconnect Reliability, Rel. Phys. Symp., p.190 (1984)

- (6) Klema, J., Pyle, R., Domangue, E. : Reliability Implications of Nitrogen Contamination During Deposition of Sputtered Aluminum/Silicon Metal Films, Rel. Phys. Symp., p.1 (1984)

- (7) Mayumi, S., Umemoto, T., Shishino, M., Nanatue, H., Ueda, S., Inoue, M. : The Effect of Cu Addition on Stress Induced Open-circuit Failures, IEDM Tech. Dig., p.15 (1987)

- (8) Nishimoto, Y., Tokumasu, N., Fukuyama, T., Maeda, K. : Low Temperature Chemical Vapor Deposition of Dielectric Films Using Ozone and Organosilane, Ext. Abs. 19th SSDM, p.447 (1987)

- (9) Kotani, H., Matsuura, M., Fujii, A., Genjou, H., Nagao, S. : Low-Temperature APCVD Oxide Using TEOS-Ozone Chemistry for Multilevel Interconnection, IEDM Tech. Dig., p.669 (1989)

- (10) Matsuura, M., Kotani, H., Abe, H. : Substrate-Dependent Characteristics of APCVD Oxide Using TEOS and Ozone, Ext. Abs. 22nd SSDM, p.239 (1990)

- (11) Tomioka, H., Tanabe, S., Mizukami, K. : A New Reliability Problems Associated with Ar-Ion Sputter Cleaning of Interconnect Vias, Rel. Phys. Symp., p.53 (1989)

- (12) Kotani, H., Tsutsumi, T., Komori, J., Nagao, S. : A Highly Reliable Selective CVD-W Utilizing SiH<sub>4</sub> Reduction for VLSI Connects, IEDM Tech. Dig., p.217 (1987)

図12. 選択 CVD タングステンによるホールの埋め込み

# 0.8 μmCMOS ASIC プロセス

畠中正宏\* 森本博明\*\*\*

大野多喜夫\* 松田修一\*

山口澄夫\*\*

## 1. まえがき

高度情報化社会の進展に伴って、電子機器の高性能化・システム化が進んでいるが、その中核をなし、原動力となっているのが、超 LSI 技術であることは周知の事実である。現在市販されている最先端の LSI は、4M DRAM で、そのデザインルールは 0.8 μm である。この DRAM に関しては、更に 0.5~0.6 μm ルールの 16M DRAM も鋭意開発中で、今世紀末には 0.1 μm ルールによる 1G ビットの容量を持つ DRAM の出現が予想されている。

一方、機器のシステム化のかなめともいえる ASIC(Application Specific IC) も、このような微細加工技術の進歩を取り入れ、また CAD 技術の発達もあり、大規模で高機能な製品が登場している。ASIC におけるデザインルールは、現在 1.0 μm のものが市販レベルでは最先端で、当社においても大規模なゲートアレー M60050 シリーズ<sup>(1)</sup>や、TRON 仕様の 32 ビットマイクロプロセッサ<sup>(2)</sup>、画像／映像処理用シグナルプロセッサ<sup>(3)</sup>等の 1.0 μm ルールによる製品を開発してきた。

今回開発した 0.8 μm ルールによる CMOS ASIC プロセスは、上述した 1.0 μm プロセスをもとに、更に高性能・高集積化をねらいとしたもので、レイアウト上のデザインルールは原則として 1.0 μm ルールからの縮小を可能とし、微細化

• メモリ内蔵プロセッサ

• A/D コンバータ

• ニューロチップ

に対応して縦方向のスケーリングも行っている。

本稿では、このような 0.8 μm ルールによる CMOS ASIC プロセスの概要と、ASIC の開発期間短縮には最も有効な手法である電子ビーム(EB)によるウェーハ直接描画技術について紹介する。

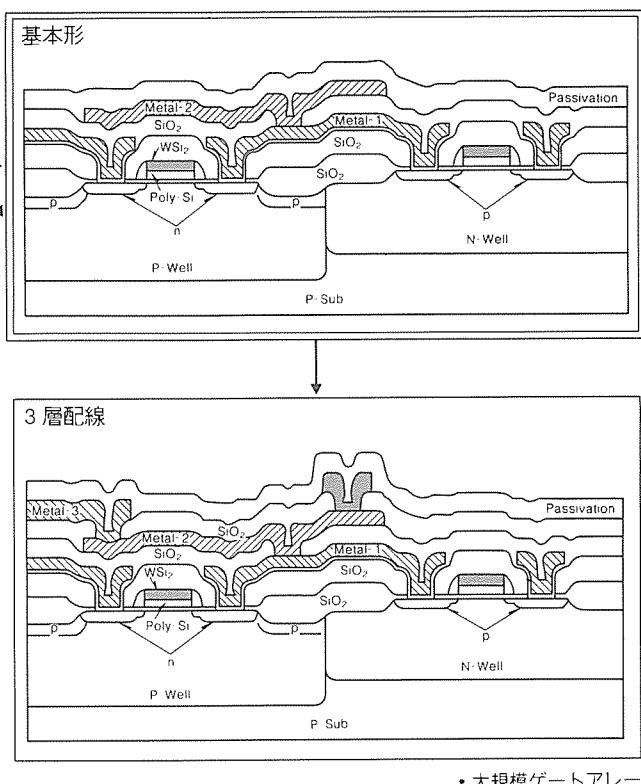

## 2. デバイス構造及び構成

異なる機能を持つ様々な ASIC 群を効率良く開発し、しかも生産コストを最小限に抑えるためには、それらを実現するためのデバイス構造の統一化が欠かせない。このため、0.8 μmASIC では図1に示すように、論理回路を構成するための CMOS デバイス構造を基本形とし、他の機能が必要な場合には、それに応じてモジュール化したデバイスをこの基本デバイスに付加することで、事実上多種類のデバイス構造が実現できる構成となっている。

### 2.1 基本 CMOS 構造

この基本形となる CMOS デバイスは、ASIC 上に構成される種々の論理回路を実現するためのもので、高性能な MOS トランジスタと 2 層構造を持つ信号配線からなっている。シリコン基板は P 型を原則とし、ウェルは P/N ツイ

図1. 0.8 μmCMOS ASIC のデバイス構成

ンウェル構造である。このウェル内に形成される MOS トランジスタは、NMOS, PMOS 共にゲート長が  $0.8 \mu\text{m}$  で、ゲート電極には低抵抗化のために、 $\text{WSi}_2/\text{Poly-Si}$  のポリサイド構造を採用している。また、配線層下の層間絶縁膜は平たん化のため、 $1.0 \mu\text{m}$  プロセスと同様、BPSG (Boron-phospho-Silicate-Glass) 膜を用いている。配線層に用いる材料は、2層共  $\text{AlSiCu}$  膜を用い、エレクトロ マイグレーションによる信頼性劣化を防いだ。

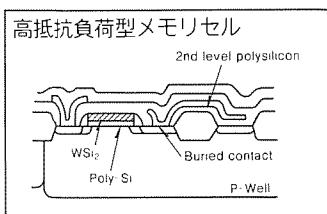

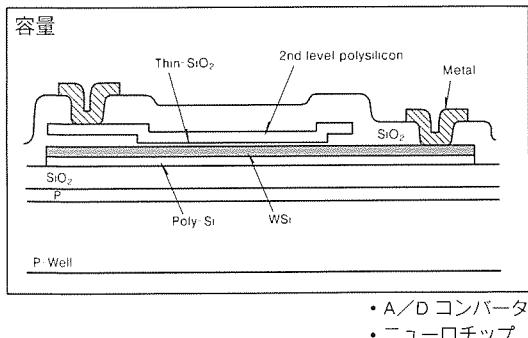

## 2.2 モジュール化デバイス構造

上述した基本 CMOS デバイス構造に付加されるオプションとしてのデバイスには、主として次の 3種類を用意した。すなわち、Poly-Si 層を 1層追加して、ゲート電極である  $\text{WSi}_2/\text{Poly-Si}$  との間に絶縁膜を形成することで、容量素子を形成するもの、あるいは、この 2層目の Poly-Si 層を高抵抗層とした高抵抗負荷型メモリセルを形成するものである。また、配線層としても、もう 1層合計 3層構造まで構成できるようにした。これらのモジュール化されたデバイス構造をオプションとして付加する ASIC としては、容量素子を組み込んだ A/D コンバータやメモリ内蔵のプロセッサが実現できるほか、配線層を 3層としたことで、特にゲートアレーにおけるゲート使用効率向上が達成される。

## 2.3 統一化の留意点

以上述べたデバイス構造の統一化の過程において留意すべきことは、設計パラメータの共通化である。付加するモジュールセル内でのプロセス条件やデバイス構造は、基本形となる CMOS 構造には影響を与えないように配慮しており、論理回路を構成している部分は、すべての  $0.8 \mu\text{m}$  ASIC に対してその性能を同一としている。こうすることで、回路シミュレーションのためのトランジスタ パラメータや各種浮遊容量・寄生抵抗の値は、同じものが使用可能となる。この結果、カスタム、セミカスタムを問わず、各種機能ブロックの共有化も図られると同時に、生産面から見ても製造上のプ

表 1.  $0.8 \mu\text{m}$  プロセスの主なパラメータ

単位:  $\mu\text{m}$

| 項目                               | パラメータ   |

|----------------------------------|---------|

| (MOS トランジスタ)                     |         |

| ゲート長 (NMOS/PMOS)                 | 0.8     |

| ゲート酸化膜厚 (nm)                     | 18      |

| (ウェル)                            |         |

| ウェル深さ (P ウェル/N ウェル)              | 4.0/2.5 |

| (層間絶縁膜)                          |         |

| 1層配線下部                           | 0.7     |

| 1層 - 2層間                         | 0.8     |

| 2層 - 3層間                         | 0.8     |

| (レイアウトルール)                       |         |

| 拡散配線 ( $\text{N}^+/\text{P}^+$ ) | 1.0/1.4 |

| コンタクトホール                         | 0.8×0.8 |

| スルーホール (1層目 - 2層目)               | 0.8×1.0 |

| 第 1 層配線ピッチ                       | 2.4     |

| 第 2 層                            | 3.2     |

| 第 3 層                            | 4.8     |

ロセスパラメータがかなりの部分標準化された。

以上述べた CMOS デバイス構造の主なデバイスパラメータとレイアウト寸法を表 1 に示す。

## 3. プロセス技術

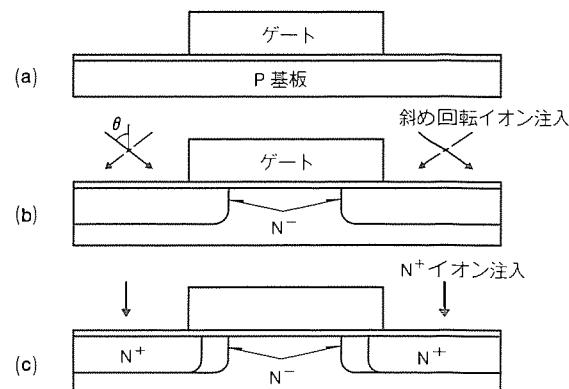

$0.8 \mu\text{m}$  ASIC プロセス技術の中心は、ゲート長  $0.8 \mu\text{m}$  の MOS トランジスタと 3層配線構造まで可能な多層配線技術である。特に電源電圧が  $5\text{V}$  であることに対応して、ホットエレクトロンによる特性劣化を防止するため、 $\text{N}^-$  オーバラップ LDD 構造の NMOS トランジスタ<sup>(4)</sup>を採用した。この構造は、プロセス技術として、斜め回転イオン注入技術<sup>(5)</sup>を使って実現したもので、これによって MOS トランジスタの信頼性を確保している。図 2 には、斜め回転イオン注入を用いた  $\text{N}^-$  オーバラップ LDD 構造のプロセスフローを示す。また、PMOS トランジスタについても、LDD 構造を採用し、一方、チャネル部の不純物分布を最適化することで十分な耐圧を確保しながら高い電流駆動能力を得ている。

ASIC プロセスとして、もう一つ重要な技術が多層配線技術である。 $0.8 \mu\text{m}$  ASIC プロセスでは、3層配線まで可能とするために、特に層間絶縁膜の平たん化に注意を払った。この平たん化のために、従来の  $\text{SiH}_4$  系の低温 CVD 酸化膜に代えて、TEOS 系の CVD 酸化膜を採用した。図 3 には、この TEOS 系の CVD 酸化膜を層間絶縁膜に用いた 3層配線の断面図を示す。

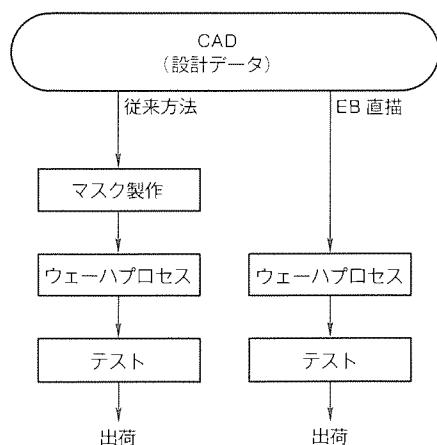

## 4. 電子ビーム直接描画を用いた ASIC 製作

### 4.1 電子ビーム直接描画法の特長

現在、LSI の回路パターン形成には、フォトリソグラフィ技術によってマスクパターンを縮小転写するステッパーが広く用いられている。この方式では、現在  $0.5 \mu\text{m}$  程度のパターンまで形成が可能であり、また 1 時間に 20 枚以上のスループット (ウェーハ処理能力) を持っている。

これに対し、EB 直接描画 (以下、“EB 直描”という) では、ウェーハ上に直接回路パターンを描画する。したがって、マスクが不要であり、マスク製作工程 (通常で数日、最短で

図 2.  $\text{N}^-$  オーバラップ LDD 構造 MOS トランジスタのプロセスフロー

も1~2日)を省略できる。ステッパを用いた工程とEB直描を用いた工程の差を図4に示す。

EB直描を使用することによって、ターンアラウンド(製作開始から終了までの時間)を短縮することができる。しかし、EB直描は回路パターンを順次一つずつ描画していくために、スループットが低い(現在1時間に1枚前後)という短所がある。すなわち、EB直描を用いるとスループットは低いが、生産量が少なければターンアラウンドが短いということになる。したがって、少量多品種品を短納期で製作したり、サンプル品を少量製作して回路のデバッグを行うためには、非常に有効な方法である。

EB直描のもう一つの特長は、微細加工性である。ステッパでは、露光に使用する光の回折の影響のため現在0.5 μm前後に解像度限界があるのに対し、EB直描では0.2 μmまで可能である。図5は、EB直描を用いて形成した0.2 μm幅のパターン写真である。20kVの可変成型ビームを用いて3層レジストの上層パターンを形成している。レジストは、SAL-601ER7、膜厚は0.5 μm、基板はSOG/ボトムレジスト/Si基板である。

#### 4.2 近接効果補正

EB直描に特有な問題として、近接効果<sup>(6)</sup>がある。これは、電子ビームがレジスト中で散乱、あるいは基板からはね返っ

図3. 3層配線構造の断面SEM写真

図4. ステッパを用いた通常のLSI製造工程とEB直描を用いた場合の工程の比較

てくることによって描画した回路パターンが変形する現象である。近接効果のために、設計パターンに対して、例えば孤立したパターンは小さくなり、近接するパターン同士はくっ付き合うように変形する。したがって、微細パターンを形成するためには、この近接効果をパターンデータ上で補正する必要がある。補正の方法及び補正結果の例を以下に述べる。

まず、EB描画条件(加速電圧、レジスト膜厚、レジストの種類・感度など)に対するレジスト中への蓄積エネルギー分布(EID関数<sup>(6)</sup>)を求める。EID関数のパラメータを求めるために、モンテカルロシミュレータELIS<sup>(7)</sup>を使用する。次に、各回路パターンのエッジ部分における蓄積エネルギー量が、十分に大きいパターンの中心部分における蓄積エネルギー量の1/2になるように、回路パターンごとにビーム照射量を決定する。すなわち、EB描画を行うときに、描画する回路パターンごとの蓄積エネルギー量が等しくなるように、EB照射時間を各パターンごとに設定する。

図6(a)は補正前の描画パターンデータ、(b)は補正後のパターンデータの例である。図中の数字は、各パターンのビーム照射量(照射時間)に対応する。補正前は各パターンとも同一ビーム照射量であるが、補正後は孤立した場所では多く、大面積パターンの場所では少なく設定されているのが確認できる。このパターンデータを用いて形成したレジストパターンの写真を図6(c)、(d)に示す。補正前のデータ(a)を用いたものが(c)、補正後のデータ(b)を用いたものが(d)である。補正を行っていない場合、写真左側の孤立した配線の先端部が細くなっているが、補正後は場所によらず所望のパターン寸法が得られている。

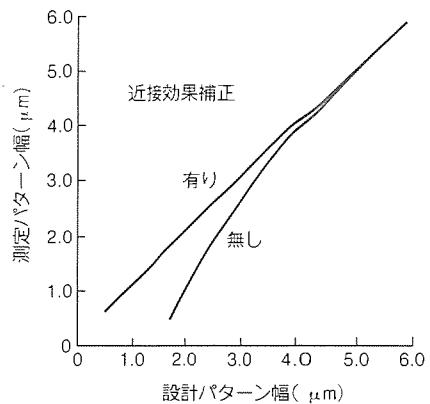

近接効果補正による回路パターン寸法の改善を測定した結果を図7に示す。1 μm厚のポジレジストを6 μC/cm<sup>2</sup>で描画したものである。近接効果補正なしでは、3 μm以下のパターンでリニアリティが悪くなる(設計寸法と仕上り寸法に差が出てくる。)のに対し、近接効果補正を行ったものに対しては、サブミクロン領域まで良好なリニアリティを示している。近接効果補正を行うためには、長い計算時間を必要としていたが、描画パターンデータ、及びデータ処理の階層化などによって計算時間は飛躍的に短縮されている<sup>(8)</sup>。

20kVの可変成型ビームを用いて3層レジストの上層パターンを形成。レジストはSAL-601ER7、膜厚は0.5 μm、基板はSOG/ボトムレジスト/Si

図5. EB直描を用いて形成した0.2 μm幅のパターン

(a) 補正前の描画パターンデータ

(b) 補正後の描画パターンデータ。数字は各パターンのビーム照射量に対応する。

(c) 補正前の描画パターンデータを用いて形成したレジストパターン

(d) 補正後の描画パターンデータを用いて形成したレジストパターン

図 6. 近接効果補正の例

図 7. 近接効果を行った場合と行わなかった場合の回路パターン寸法の実測値比較

図 8. EB 直描を用いて製作した CMOS ゲートアレーのチップ拡大写真

#### 4.3 電子ビーム直接描画による ASIC 製作例

EB 直描によって製作した CMOS ゲートアレーのチップ拡大写真を図 8 に示す。スライスの 4 工程に EB 直描を使用した。A1 1 と A1 2 工程にはネガレジスト、コンタクトとバイヤホール工程にはポジレジストを用いた。DC 特性、回路特性ともステッパによって製作した従来のものと同等である。

以上述べたように、EB 直描技術は少量多品種 ASIC の短納期製作やサンプル品の短期納入に有効である。

#### 5. むすび

以上、 $0.8 \mu\text{m}$  CMOS ASIC プロセスの概要と EB 直描技術について紹介した。ゲート長を、NMOS, PMOS 共  $0.8 \mu\text{m}$  としながら、高い信頼性を確保するとともに、3 層配線構造実現のため、新しい平たん化層間絶縁膜を導入した。また、デバイス構造を統一することで、多様な ASIC に対し、共通のデバイスパラメータが適用可能となっている。今回開発した  $0.8 \mu\text{m}$  プロセスと EB 直描技術により、さらに高集積・高機能な ASIC の効率的な開発の土台になるものと確信している。

#### 参考文献

- 中村博隆、後藤諭利、布上裕之、川端啓二、西谷一治：高速、低消費電力の  $1.0 \mu\text{m}$  CMOS ゲートアレー M600 50 シリーズ、三菱電機技報, 63, No.11, 954~956

- (1989)

- 日向純一、市山寿雄、吉田豊彦、富沢 治、是松次郎：TRON 仕様 32 ビットマイクロプロセッサ M32/100, 三菱電機技報, 63, No.11, 921~924 (1989)

- 寺根秀幸、嶋田敏明、中川伸一、篠原尋史、吉本雅彦、畠中正宏：24 ビット、50 ns 画像／映像処理用シグナルプロセッサ (DISP), 三菱電機技報, 63, No.11, 929~932 (1989)

- Inuishi, M., Mitsui, K., Komori, S., Shimizu, M., Oda, H., Mitsuhashi, J., and Tsukamoto, K. : Optimum Design of GATE /  $N^-$  Overlapped LDD Transistor, Digest of Technical Papers, Symposium on VLSI Technology, 33~34, IEEE Electron Devices Society (1989)

- 御城俊宏、長友正男、高橋武人、大崎三郎：斜め回転イオン注入技術、三菱電機技報, 63, No.11, 980~983 (1989)

- Parikh, M. : J. Vac. Sci. Technol. 15, No. 3 931~933 (1978)

- 藤野 肇、竹内 晋、楠瀬治彦、森泉幸一、青山 哲、渡壁弥一郎：電子情報通信学会、SDM 89-73, 1~6 (1989)

- Moriizumi, K., Takeuchi, S., Fujino, T., Aoyama, S., Yoneda, M., Morimoto, H., and Watake, Y. : Digest of Papers, 3rd Microprocess Conference, 52~53, The Japan Society of Applied Physics (1990)

# セルベース設計用 モジュール ジェネレータ

篠原尋史\* 辻橋良樹\* 塚本美智子\*\*

津田和彦\*\* 藤森久美子\*

松本憲昌\*\*\* 味岡佳英\*\*

## 1. まえがき

セルベース LSI では、あらかじめ準備されたライブラリ中の各種セルを用いてチップを構成する。セルの種類に応じて最適に回路設計・レイアウト設計されたものを使用することができるため、セルベース設計方式は USIC (User Specific Integrated Circuits) の分野において、ゲートアレーでは困難な高性能・高機能な LSI あるいは量産によるコストダウンをねらった LSI に適した設計方式である。また、従来フルカスタム手法で設計されてきたプロセッサ LSI や専用 LSI の分野では、集積度の向上と品種の増大に伴う設計負荷の爆発的増大に対処すべく設計効率改善が急務となっている。そのため、共通のライブラリセルと専用セルを混在する方法で、セルベース設計方式が浸透しつつある。

以上のように、セルベース設計方式は、回路・機能ブロックが高度に集積されたシステム オン チップの時代における LSI の広い範囲をカバーする設計方式である。そのなかでライブラリセルは、セルベース LSI 及びセルベース設計システムを特徴付けるキーエレメントとして重要性が高まっている。とりわけ、RAM に代表される規則的内部構造を持ったモジュールセルは、下記の理由によって最も基本的かつ主要なものである。

- (1) 様々な用途の LSI に汎用的に用いられ、使用頻度が高い。

- (2) LSI の動作速度を律速するクリティカルパスの構成要素となる場合が多い。

- (3) 最適設計により、ゲートアレー や標準セルで組むよりも大幅な性能向上と面積削減が得られる。

- (4) タイプ方式のモジュール生成手法<sup>(1)</sup> (4章(2)参照) を用いてモジュール ジェネレータとすることにより、指示パラメータに応じて最適設計に近いセルを自動的に生成することができる。

このような背景のもとに、RAM・ROM・乘算器・PLA の4種類のモジュールセルを各々生成する4種類のモジュール ジェネレータを開発した。本稿では、これらの概要について述べる。

## 2. 開発のねらい

今回開発したモジュール ジェネレータは、セルベース設計方式の適用範囲の広がりを考慮して、プロセッサ LSI や

専用 LSI を開発する LSI 設計者のみならず、USIC を自ら設計するシステム設計者の両者に使用されることを目的としている。このため、開発に当たって下記の点に留意した。

### (1) 自由度の高い選択肢

LSI 設計におけるタイミングやレイアウトの制約に対して柔軟に対応できるよう、規模パラメータの範囲だけでなく、機能オプションや、形状ファクター (メモリの縦横比) をも選べるようにする。

### (2) 高性能特性

最先端の高性能 LSI にも適用できるよう、汎用性を維持しつつ、速度・消費電力・面積のバランスのとれた高性能特性を追求する。このため、リーフセル (4章(2)参照) は主として人手でレイアウト設計する。

### (3) ライブラリデータの完備

セル内部のレイアウトパターンや詳細な回路を知らないでもモジュールセルを使って LSI を設計できるよう、シミュレーション モデル等のセルベース設計環境で必要なすべてのライブラリデータを自動生成する。

### (4) 標準プロセス技術

広範囲の LSI に適用可能なよう、1.0  $\mu\text{m}$  CMOS ASIC の標準プロセス技術を使用し、配線レイヤは基本の1層ポリシリコン、2層金属とする。

## 3. 設計技術とモジュール ジェネレータ仕様

この章では、4種類のモジュール ジェネレータ各々につき、設計技術及び機能の特徴並びにカスタマイズするための入力パラメータの種類とその範囲について述べる。

### 3.1 RAM ジェネレータ

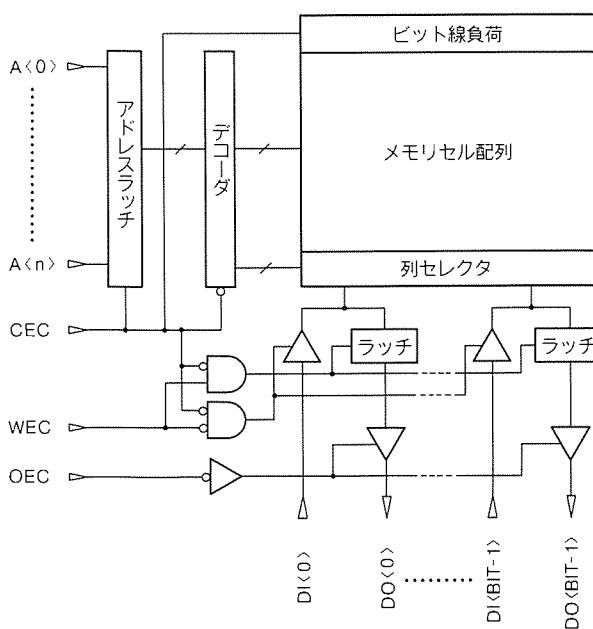

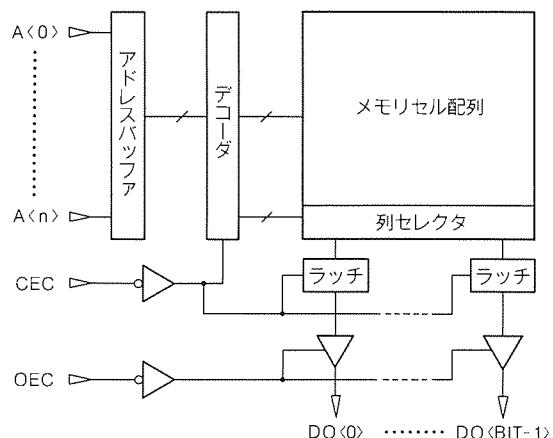

図1にRAMのブロック図を示す。このRAMは同期型のスタティックRAMであり、直流の動作電流をなくして低消費電力化を図った。チップ内蔵RAMの場合、1ワードが数バイトの多ビット構成をとる場合が多いため、読み出し回路では少ない電流でセンス感度を高める工夫が必要である。このため、NMOSクロスカップ型の差動センスアンプを採用し、トランジスタサイズを最適化して高速化を図った。標準の1層ポリシリコン CMOS プロセス技術を用いたため、メモリセルはフル CMOS 6トランジスタ構成で、セル面積は231  $\mu\text{m}^2$  である。

汎用 SRAM と端子の種類は同様であるが、チップ内蔵用として使いやすいよう、次の特徴を持たせている。セルイ

ネーブル(チップイネーブル)信号 CEC=0 のとき、アドレス変化による誤動作を防止するため、アドレスを CEC でラッチしている。また、読み出しデータをプリチャージ時にラッチし、出力のトライステート制御を OEC により、他の制御信号(CEC, WEC)とは独立に制御するようにしている。この結果、例えば、CEC=1 のプリチャージ時にも読み出しデータを出力し、次段によるデータ取り込みのタイミングに余裕を与えることができる。

さらに、オプション指定により、書き込み制御信号 WEC を CEC によってラッチすることもできる。WEL=true を選択すると WEC はアドレスと同様に同期信号 CEC でラッチされ、そのサイクルが書き込みサイクルか読み出しサイクルかが設定される。したがって、アドレスと同時に読み出し／書き込みが決定する場合に有効である。一方、WEL=false を選択すると、汎用 SRAM と同様 WEC=0 の期間に書き込み、WEC=1 の期間に読み出しができるので、リードモディファイライタやライトモディファイリードのような回路動作が可能となる。

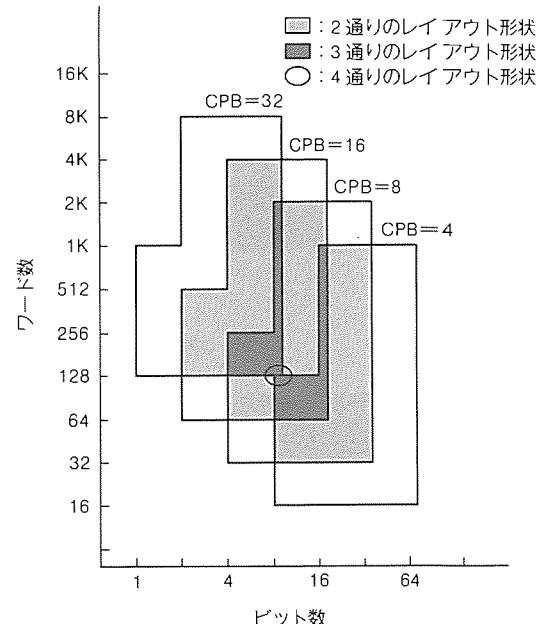

表1にRAMジェネレータの入力パラメータを、他のモジュールジェネレータのものとともにまとめる。ビット数は1~72ビット、ワード数は16ワード~8Kワード、メモリ容量は128ビット~72Kビットまで自動生成できる。ワード数は、2のべき乗以外も選択可能である。また、RAMの形状を指定するためのパラメータCPB(Column Per Bit)を導入した。CPBは1ビット当たりのメモリセル配列の列数を意味し、4, 8, 16, 32の中から選択できる。図2に示したとおり、CPBが大きいときはワード数の大きいRAMをカバーし、小さい場合は多ビット構成のRAMをカバーする。同一のビット数、ワード数で複数のCPBを取り得る場

合、RAM形状はCPBが大きいと横長(列数大)、CPBが小さいと縦長(行数大)になる。図3に16ビット・128ワード構成で、CPBが4, 8, 16のときの各々の生成RAMレイアウトを示す。

ワード幅をサブワードに分割し、サブワードごとに読み出し及び書き込み可否を制御するサブワード機能<sup>(2)</sup>をオプションとして準備している。各サブワードは、サブワードライト制御信号SWC<n>と共に制御信号CEC, WECによって独立に書き込み可否が制御され、サブワード出力制御信号OEC<n>により独立にトライステート出力が制御される。この機能を付加すると、DIバス幅とDOバス幅が異なる場合や、ビット／ワード構成がダイナミックに変化する応用への適用が容易になる。

表1. モジュール ジェネレータ入力パラメータ

| 種類  | パラメータ          | 範囲                        |

|-----|----------------|---------------------------|

| RAM | ビット数 (BIT)     | 1~72                      |

|     | ワード数 (WORD)    | 16~8K<br>(BIT·WORD≤72K)   |

|     | 形状ファクタ (CPB)   | 4, 8, 16, 32              |

|     | WEC ラッチ (WEL)  | true, false               |

| ROM | サブワード (SW)     | true, false               |

|     | ビット数 (BIT)     | 2~64                      |

|     | ワード数 (WORD)    | 64~32K<br>(BIT·WORD≤512K) |

|     | 形状ファクタ (CPB)   | 8, 16, 32                 |

| 乗算器 | アドレスラッチ (ADL)  | true, false               |

|     | 乗数ビット数 (YNUM)  | 8~32                      |

|     | 被乗数ビット数 (XNUM) | 8~32                      |

|     | 入力ラッチ (TI)     | 1, 0                      |

| PLA | 中間ラッチ (TC)     | 1, 0                      |

|     | 出力ラッチ (TO)     | 1, 0                      |

|     | 入力数 (IN)       | 1~40                      |

|     | 出力数 (OUT)      | 1~82                      |

|     | 積項数 (PRO)      | 1~200                     |

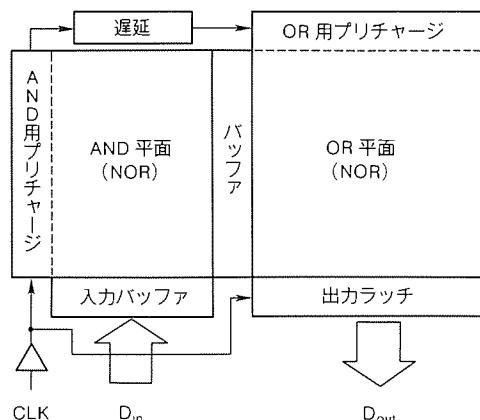

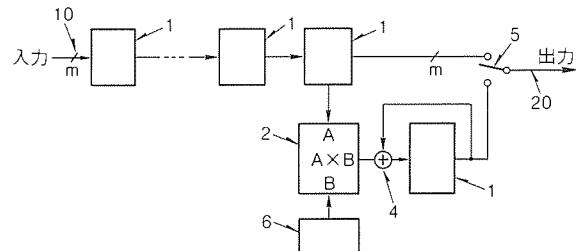

図1. RAM ブロック図

図2. RAM の生成範囲

## 3.2 ROM ジェネレータ

ユーザー指定の ROM コードに応じて、マスク ROM を自動生成する。ROM コードをプログラムするマスク工程として、拡散工程あるいはコンタクト工程のいずれかを選択できる。コンタクトプログラム方式のメモリセルは  $18 \mu\text{m}^2$  と、拡散プログラム方式の  $27 \mu\text{m}^2$  より 1.5 倍大きくなるが、ウェーハプロセスの後工程でプログラムできる利点がある。100K ビットを越える大容量 ROM においても高速性を実現するため、ビット線振幅がわずかでビット線負荷容量依存性の小さい、電流センス型センスアンプを採用した。

表 1 に示したとおり、ビット数は 2~64 ビット、ワード数は 64 ワード~32K ワード、そしてメモリ容量は 512 ビット~512K ビットまで自動生成可能である。ワード数は、2 のべき乗以外も選択可能である。RAM ジェネレータと同様に、生成 ROM の形状をパラメータ CPB (8, 16, 32) の指定によって選択できる。

図 4 に論理ブロック図を示す。制御信号 CEC は、パワーダウンモードの設定を行う。CEC にクロック信号を入力する同期動作と CEC を 0 に保持してアドレスを変化させる非同期動作の両方が可能である。また、RAM と同様に、アドレスを CEC でラッチすることもオプションとして提供している。出力制御信号 OEC は、CEC とは独立にデータ出力のトライステート制御を行う。

## 3.3 乗算器ジェネレータ

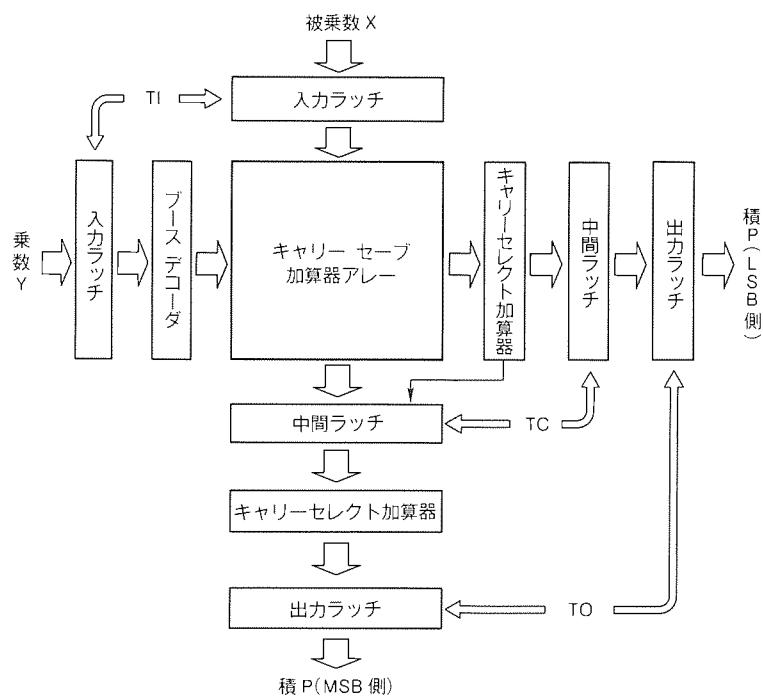

デジタル信号処理 LSI の主要な構成要素である並列乗算器を生成する。2 の補数表現の乗数、被乗数を入力とし、1 サイクルで積を出力することが可能である。

図 3. RAM のレイアウト生成例(16 ビット, 128 ワード)

図 5 に生成される乗算器の論理ブロック図を示す。このジェネレータでは、2 次のブースアルゴリズムを採用して部分積の数を半減させ、生成された部分積の並列加算には、回路構成の規則性が高いキャリーセーブ法を用いた。キャリーセーブアダのアレーを構成する 1 ビットの全加算器は、入力から和出力まで、及び入力からけた(桁)上げ出力までの速度が均等に速くなるよう最適化し、アレー 1 段当たりの速度を向上させた。さらに、アレー部の出力を最終的に足し合わせる桁上げ伝搬加算器にはキャリーセレクトアダ(3)を採用し、上位桁でサブロックのビット幅を順次増やすことにより、クリティカルパスである桁上げ信号連鎖のゲート段数を減らした。以上の手法を用いることにより、高速乗算を実現している。

入力パラメータとしては、乗数ビット幅、被乗数ビット幅共に 8~32 の範囲で、互いに独立に選択可能である。オプ

図 4. ROM ブロック図

図 5. 乗算器ブロック図

ションとして、入力データラッチ、中間データラッチ、出力データラッチの挿入の有無を各々選択できる。

### 3.4 PLA ジェネレータ

図6のブロック図に示すとおり、このPLAは1相クロックによる同期型であり、非同期型において必要なアクティブ時の直流電流を最小のクロック数で防止している。PLAのAND平面・OR平面の構成方法には、NAND・NAND型、NOR・NAND型等幾つかの方法があるが、高速化のため、NMOSトランジスタを並列に用いるNOR・NOR型を採用した。この場合、OR平面用の同期型NORは、積項値であるAND平面出力が確定した後にプリチャージ状態から評価状態に移行する必要がある。このPLAでは、規模に応じて遅延時間が変わる遅延回路を内蔵しており、OR平面用クロックの立ち上がりを外部入力から与えられるAND平面クロックより遅延させている。この結果、必要最小の遅延時間で確実な動作を果たしている。

データ出力段には、クロックと同相で制御されるデータラ

図6. PLA ブロック図

ッチを備えている。これにより、PLAがプリチャージ時ににおいても出力データを保持することができ、これを用いてLSIを設計するうえでのタイミング制約が緩くなる。

PLAを生成する際にユーザーが指定するのはブール式である。表1に示す範囲の規模の組合せ論理回路であれば、任意のものを生成できる。ここで、積項数はPLAの性能・面積を左右する重要なパラメータであるが、入力ブール式では指示されない。このPLAジェネレータでは、入力ブール式をAND・ORの二段論理に展開する際に積項数を最小にする最適化処理を行う。

### 4. 設計データの自動生成

モジュールジェネレータを使用することの利点は、高集積・高性能なモジュールセルを短期間に得られることに加えて、それを回路やレイアウトに関する専門知識なしに利用できることである。

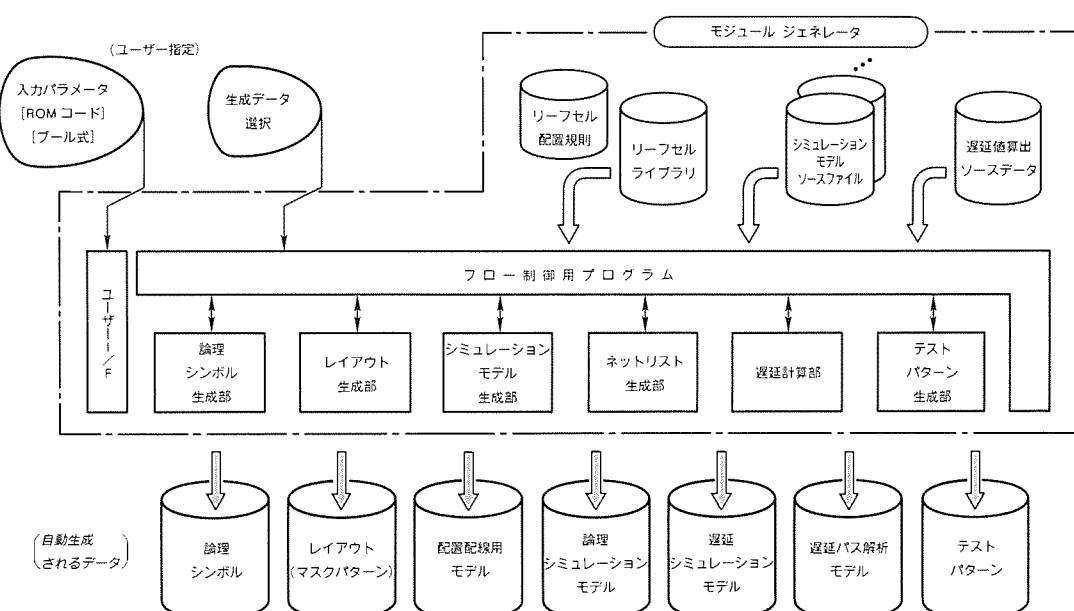

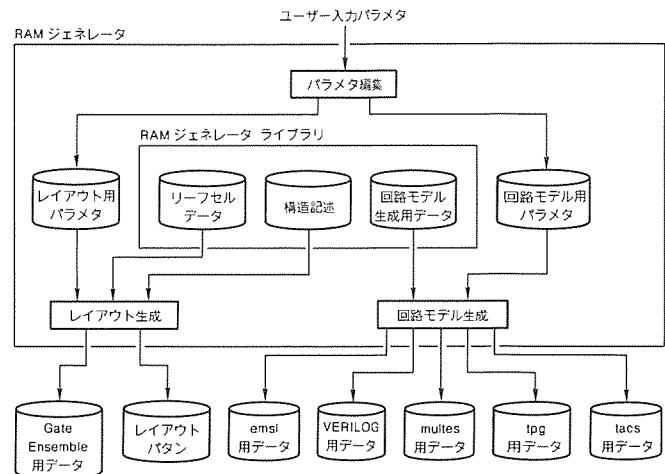

このモジュールジェネレータは、ユーザーであるLSI設計者の要求する設計環境に対応するため、種々のセルベース設計CADツールに対応したすべてのデータを自動生成する。図7にこのモジュールジェネレータの構成概念を示す。

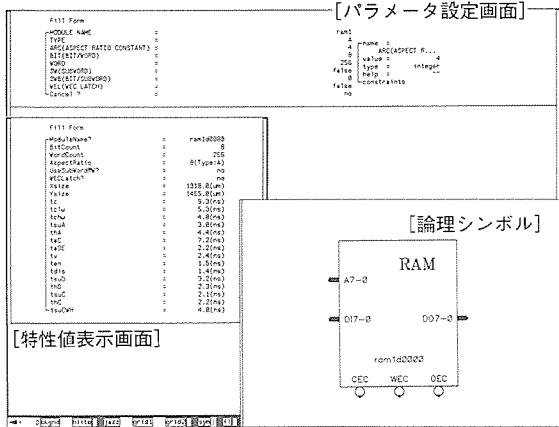

ユーザーは、所望するモジュールの規模・機能仕様(ビット数・ワード数等のパラメータ値、ROMコード、PLAのブール式等)を入力するとともに、使用する設計ツールを選択する。一例として、RAMジェネレータのユーザーインターフェースを図8に示す。ユーザーは、伝票形式のパラメータ設定画面で生成パラメータを設定する。ジェネレータは、パラメータの組合せや許容範囲等の条件に対してパラメータ値をチェックした後、生成されるモジュールの諸特性値(セルサイズ、タイミング特性値等)を計算し表示する。ユー

図7. モジュール ジェネレータ構成

図 8. モジュール ジェネレータのユーザー インタフェース (RAM ジェネレータの例)

ユーザーは、これらの特性値を確認後、生成すべきデータを選択し、処理を続行すれば、後述する各種データが生成される。

以下に各生成データの主な特徴について説明する。

#### (1) 論理シンボル

ユーザーは、この論理シンボルを使用して、モジュールセルを含んだ回路図を論理回路図入力編集ツールを用いて作成する。シミュレーションや自動配置配線等の設計ツールは、すべてこの回路図に対して実行することができるため、設計データの整合性が損なわれる心配はない。

#### (2) レイアウト (マスクパターン)

RAM・ROM・乗算器・PLA は、共に規則的な構造をとっているため、タイル方式のモジュール ジェネレーションにより、手設計とそん (遙) 色のないレイアウトを自動生成することができる。

タイル方式では、既設計のリーフセルと呼ばれる基本セル (例えば、RAM のメモリセル) を隣接配置することによって全体レイアウトを生成する。リーフセルの配置規則は、モジュール ジェネレータ専用の手続き言語<sup>(4)</sup>を使用して、ビット数・ワード数等の規模パラメータや、オプションパラメータを引き数に記述されている。この方式は完全自動の配置配線に比べ、リーフセルとその配置を人手で最適化することにより、高性能なセルが得られるだけでなく、すべての入力パラメータの組合せに対して動作・性能を見通すことができる利点がある。

#### (3) 自動配置配線用モデル

生成レイアウトのセル枠と端子情報から成るモデルである。

#### (4) 論理シミュレーションモデル

専用のモデル記述言語<sup>(5)</sup>で記述されたソースファイルから、入力パラメータに応じた機能記述を生成する<sup>(6)</sup>。

#### (5) 遅延シミュレーションモデル・遅延パス解析モデル

これらのモデルに用いる生成モジュールセル内部の速度性能は、回路シミュレーションと実測を基に規定した遅延値算出式 (5 章参照) から求めている。仮想配線負荷を想定した場合と、配置配線後の実配線負荷の場合の双方に対応可能で

図 9. テストチップ写真

図 10. テスト RAM(15K ビット)の入出力波形

ある。なお、これらも専用のモデル記述言語を用いてソースファイルを記述している。

#### (6) テストパターン

RAM と ROM に対しては、アルゴリズミックにテストパターンを生成し、乗算器と PLA に対しては、論理等価なゲートレベルのネットリストを生成する。ユーザーは、これらの生成データとテストパターン生成/編集プログラムで LSI のテストパターンを生成することができる。

なお、これらの各種設計ツール用データのほかにドキュメントデータとして、生成モジュールセルのサイズ、タイミング特性値、消費電力をリポートする。

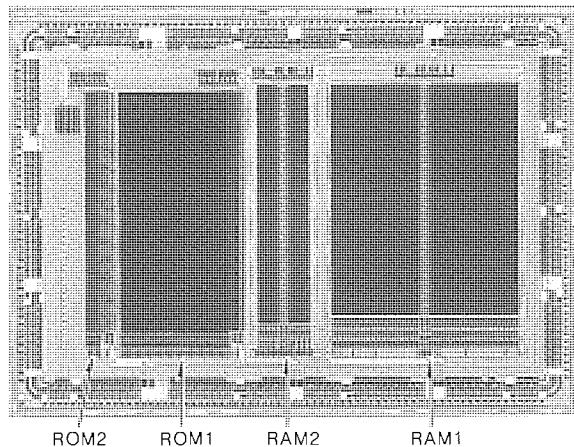

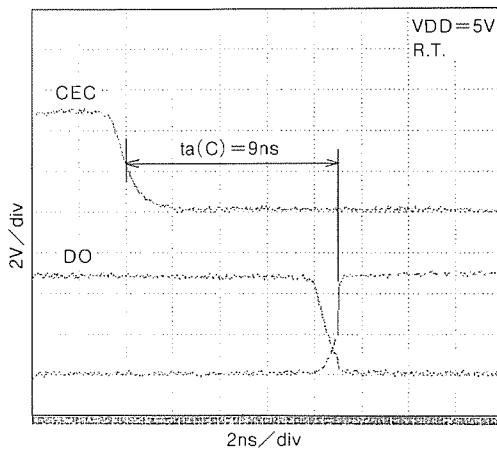

## 5. 電気的特性

このモジュール ジェネレータで生成したモジュールセルの動作を確認し、特性を評価するため、テストチップを作成した。比較的大規模な RAM と ROM を搭載したテストチップの写真を図 9 に示す。同図の RAM1, RAM2, ROM1, ROM2 の規模は、各々 65K ビット、15K ビット、636K ビット、53K ビットである。図 10 はチップ内部にある RAM2 入出力端子を電子ビームテスターを用いて測定した波形図であり、CE アクセス時間 9ns を示している。

表2. 生成モジュールセル特性値

| 種類  | 規模                                | セル面積<br>(mm <sup>2</sup> ) | 遅延時間*<br>(ns)   | 動作電流* (mA)<br>@10 MHz |

|-----|-----------------------------------|----------------------------|-----------------|-----------------------|

| RAM | 72ビット, 1Kワード<br>(CPB=4)           | 25.9                       | $t_a(C) = 16.7$ | 35                    |

|     | 8ビット, 2Kワード<br>(CPB=16)           | 7.6                        | $t_a(C) = 9.8$  | 8                     |

| ROM | 64ビット, 8Kワード<br>(field, CPB=8)    | 12.8                       | $t_a(C) = 16.9$ | 21                    |

|     | 16ビット, 8Kワード<br>(contact, CPB=32) | 5.9                        | $t_a(C) = 13.5$ | 10                    |

| 乗算器 | 32ビット×32ビット                       | 9.2                        | $t_{pd} = 33.7$ | 44                    |

|     | 24ビット×16ビット                       | 4.2                        | $t_{pd} = 21.9$ | 18                    |

| PLA | IN 40, OUT 82<br>PRO 200          | 1.8                        | $t_{pd} = 17.3$ | 22                    |

|     | IN 20, OUT 41<br>PRO 100          | 0.7                        | $t_{pd} = 11.6$ | 7                     |

注 \*標準値

モジュールセルの詳細なタイミング特性評価にはLSIテストを用いて測定する必要があるが、この場合、入出力バッファ遅延が含まれると正確な値が得られない。このテストチップでは、タイミング測定用テスト回路<sup>(7)</sup>を内蔵して測定精度をあげている。

モジュールジェネレータで生成するモジュールセルの各種タイミング特性と電源電流特性の予想は、回路シミュレーションと上記テストチップの実測の両面から行った。回路シミュレーションでは、入力パラメータの変化に対して、網羅的にタイミングデータを収集してパラメータ依存式を導出した。テストチップの実測値にプロセスパラメータ依存性を考慮したうえで、導出式の正当性確認と微修正を行った。

生成モジュールセルの特性値の例を表2にまとめる。セルベースLSIの構成セルとして十分適用可能なセル面積と動作電流で、高速性能を達成している。

## 6. むすび

当社ASIC標準の1.0 μmCMOSプロセスを用いて、RAM・ROM・乗算器・PLAの4種類のモジュールジェネレータを開発した。これらは、全種類既にセルベースLSI<sup>(8)(9)(10)</sup>に適用されており、大規模なRAMの使用例では合計100Kビットを越えるもの<sup>(9)</sup>もある。いずれも最初のシリコンチップ(1st Silicon)で動作しており、LSIの実品種でモジュールジェネレータの有効性を確認することができた。今後は、需要の大きいメモリにおいて、機能・性能に特徴あるものを加えるなど種類を充実させるとともに、より

微細なサブミクロンプロセスへと展開していく予定である。

今回のモジュールジェネレータの開発に当たって、協力・支援いただいた三菱電機エンジニアリング(株)、三菱電機セミコンダクタソフトウェア(株)及び当社の関係各位に深く感謝する。

## 参考文献

- (1) Preas, B., Lorenzetti, M. : Physical Design Automation of VLSI Systems, The Benjamin/Cummings Publishing Company, Inc., 317 ~ 321 (1988)

- (2) 藤森久美子, 篠原尋史, 加藤周一 : サブワードライト機能付きRAMジェネレータ, 1989年電子情報通信学会春季全国大会, C-353

- (3) 辻橋良樹, 篠原尋史, 加藤周一 : キャリー セレクトアダプタを用いた乗算器ジェネレータ, 1989年電子情報通信学会春季全国大会, C-287

- (4) 中尾博臣, 塚本美智子, 栗山 茂, 岡崎 芳 : 規則構造モジュール用ジェネレータ開発システム, 1989年電子情報通信学会春季全国大会, SA-9-4

- (5) 津田和彦, 中尾博臣, 田中 宏, 片井ちひろ, 塚本美智子, 岡崎 芳 : モジュールジェネレータのレイアウト及び回路モデル生成方法, 電子情報通信学会技術研究報告, VLT89-38

- (6) 松本憲昌, 篠原尋史, 加藤周一, 原 雅生 : ROMモジュールジェネレータの論理シミュレーション用機能モデル, 1990年電子情報通信学会春季全国大会, C-630

- (7) 松本 尚, 辻橋良樹, 篠原尋史, 加藤周一 : ライブリセルの高精度速度評価, 1990年電子情報通信学会春季全国大会, C-638

- (8) 中林竹雄, 近藤晴房, 蔵永 寛, 長谷川浩一, 山本誠二 : ISDN基本インターフェース用LSI, 三菱電機技報, 65, No. 2, 186~189 (1991)

- (9) 覚整高音, 鈴木孝昌, 川畠英雄, 岸田 悟, 長谷川浩一 : CB-1設計システムを用いた8kbps単位交換可能な大容量時分割スイッチLSI, 三菱電機技報, 65, No. 2, 190~193 (1991)

- (10) 森 信太郎, 鬼玉幸夫, 吉田英夫, 井上 徹, 清瀬泰広 : 光ディスク用誤り訂正LSI, 三菱電機技報, 65, No. 2, 200~205 (1991)

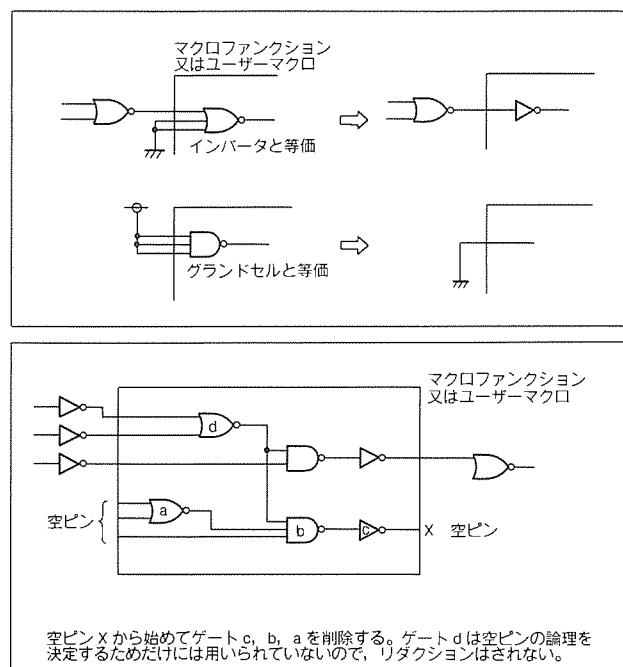

# 0.8 μmCMOS ゲートアレー

岡辺雅臣\* 村井正弘\*\*

柿沼守男\*\* 川端啓二\*\*\*

国岡美千子\*\*

## 1. まえがき

最近のコンピュータを中心とする高度情報化社会の展開において、ASIC (Application Specific IC) はその原動力として急速な進歩を遂げている。システムの高性能化が要求されるにつれて、ASIC の高速化・大規模化・低消費電力化が加速されており、特に CMOS ゲートアレーは集積度、性能、価格などの要求をバランス良く満足し、今後も ASIC の中核をなすデバイスである。

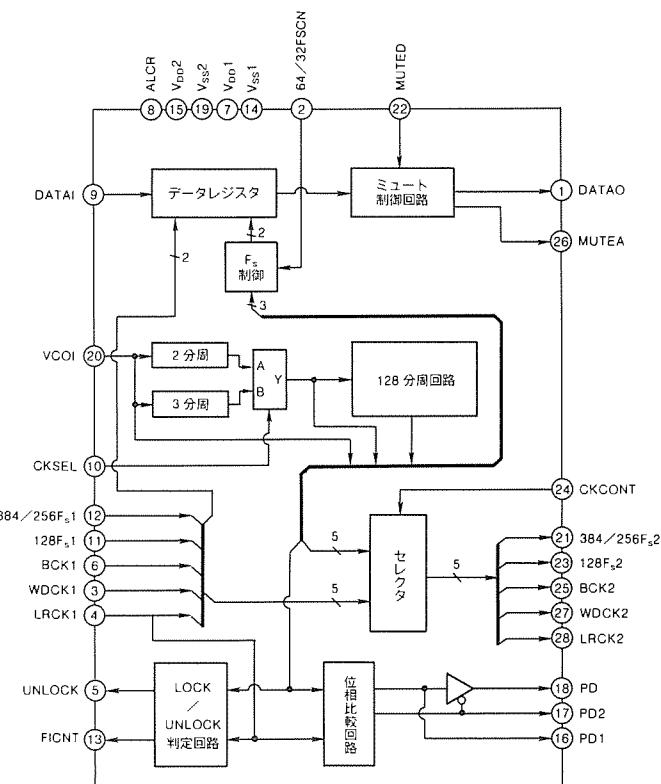

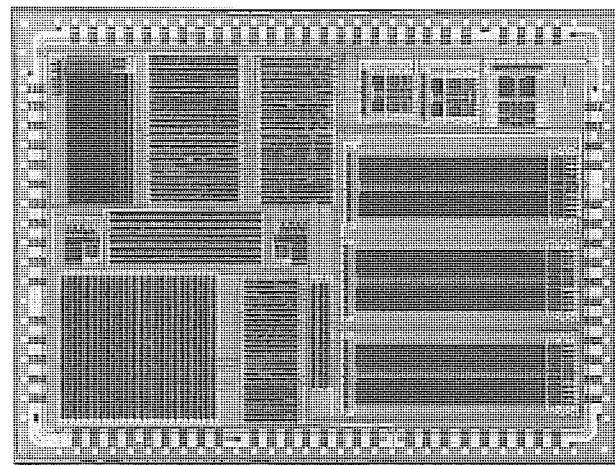

当社では、市場からの更なる高ゲート化、高性能化の要請にこたえるべく、最先端の 0.8 μmCMOS アルミ 3 層配線技術を用いた Sea-of-Gates (SOG) 型 400KG ゲートアレーのデバイス開発と、それに対応する EWS ベースの統合化設計システムの開発を同時に進めてきた。400KG ゲートアレーの開発における課題は、システムの大規模化に伴って要求されるデバイス性能の実現と、設計検証システムの構築である。

本稿では、今回開発した 400KG ゲートアレーを始めとする 0.8 μmCMOS ゲートアレーの設計技術と設計システムについて述べるとともに、M6008X シリーズの特長について紹介する。

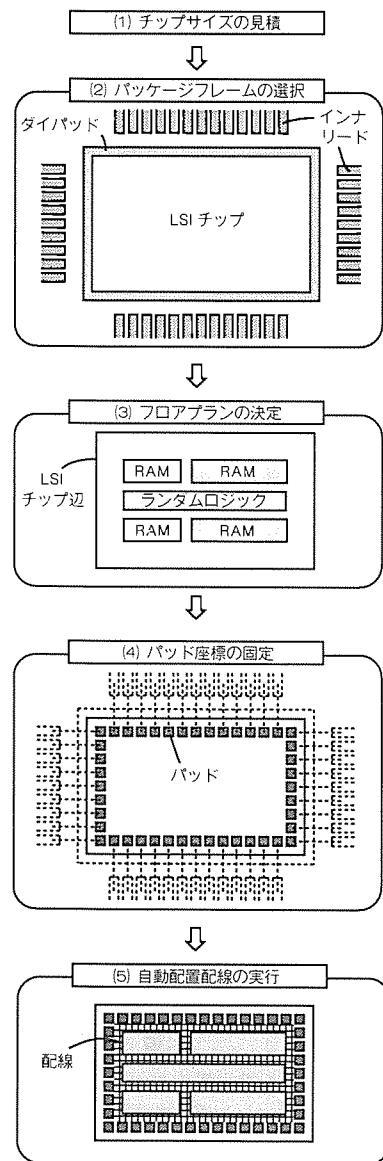

## 2. LSI 設計

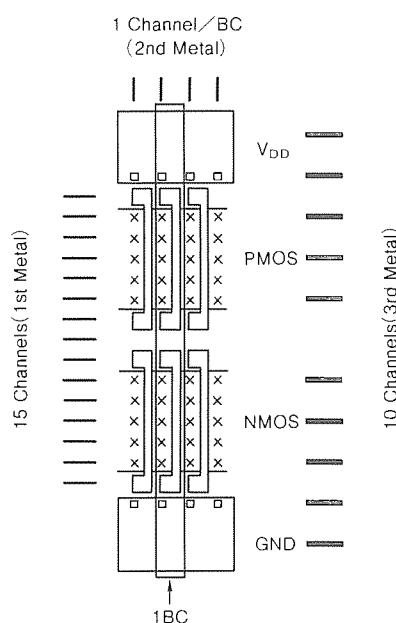

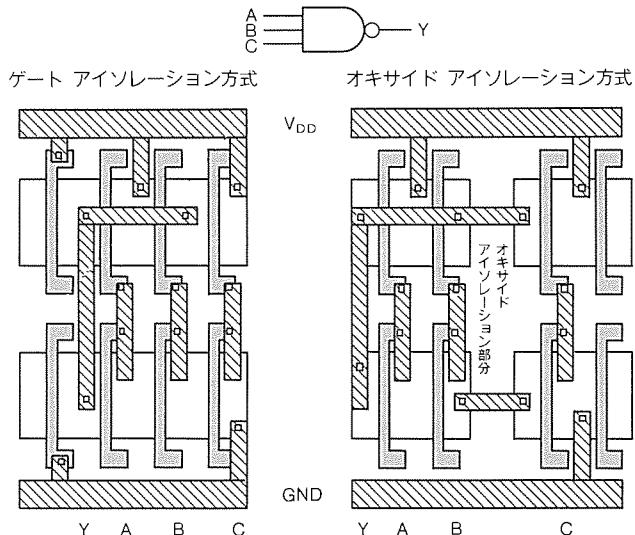

### 2.1 ベーシックセル (BC) 設計

SOG は、ベーシックセル (BC) をアレー状に並べて内部セル領域を構成するので、BC の構成でチップの集積度、速度等の性能が左右される。BC 構造の特徴は、図 1 に示すように当社独自のゲート アイソレーション方式を採用しており、1BC は PMOS、NMOS トランジスタ 1 ペアで構成されている。このゲートアレーでは、敷き詰めゲート数 400KG の実現と 3 層配線による高集積化及び低消費電力化に重点をおき、以下の指針で設計した。

- (1) PMOS、NMOS トランジスタのサイズを同一とし、最も複雑なマクロセルでも BC セル列内で配線を完結できる最小のゲート幅に設定する。

- (2) 1BC 当たりの配線チャネル数は、1AI が水平方向に 15 本、2AI は垂直方向に 1 本、3AI は配線ピッチを 1AI の 2 倍のピッチとし、水平方向に 10 本割り当てる構造とする。

ゲート アイソレーションによる上記(1)、(2)による効果と配線の微細化技術により、マクロセル及び RAM の密度で他社の 1.5 倍以上の高集積化を達成している。

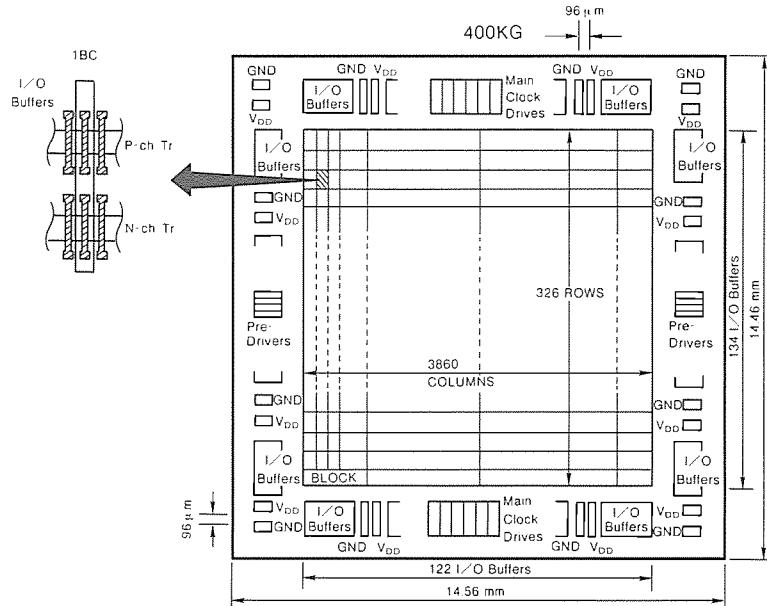

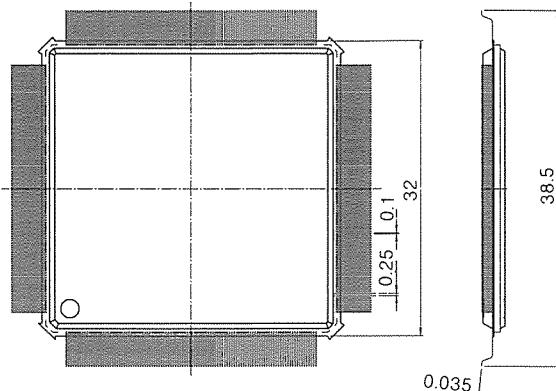

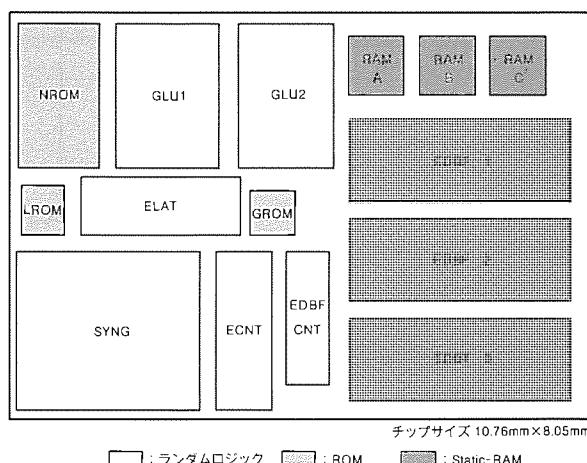

## 2.2 マスタ設計

図 2 に 400KG マスタのフロアプランを示す。チップサイズは 14.56mm × 14.46mm であり、BC 数は 1.25MBC、I/O 数は最大 512 である。I/O バッファ領域は 76.8 μm ピッチで設計し、スルーレート制御回路等の必要な機能はすべて盛り込まれている。1 I/O 領域で  $I_{OL} = 8\text{mA}$  までの出力バッファを構成でき、3 I/O 領域を組み合わせて  $I_{OL} = 24\text{mA}$  まで実現できる。パッドピッチは、TAB による多ピン化と量産性のトレードオフにより、96 μm ピッチとした。クロック分配用のプリドライバセルとクロックドライバセルは、4 相クロック分の回路を周辺領域に I/O 領域とは分離して配置している。クロックドライバ及び出力バッファのスイッチングノイズによるチップの誤動作を防止するため、入力バッファ、出力バッファ、内部ゲート、クロックドライバ用の電源を各々分離して設けた。

## 3. 0.8 μmCMOS ゲートアレー M6008X シリーズの特長

### 3.1 モジュール ジェネレータ生成セル

従来の VTM (Variable Track Master-slice) では、RAM / ROM はマクロファンクションとして提供したが、この SOG では新たに RAM / ROM 用モジュール ジェネレータを開発し、生成されたセルをライブラリとして提供する。

図 1. ベーシックセル(BC)構造

図2. 400KG マスターフロアプラン

RAMを例にとると、シングルポートRAM(1p-RAM)とデュアルポートRAM(2p-RAM)を生成する。ビット／ワード構成は、各々1～72ビット／32～8,192ワードの範囲で可変とし、セルのアスペクト比も一部選択が可能である。1p-RAMは655種、2p-RAMは495種の構成が可能である。メモリ容量は、最大9Kビット／ブロックであり、1チップに14ブロックまで搭載でき最大128Kビットまで集積できる。

### 3.2 スルーレート制御出力バッファ

多ピン化と高速化に伴う同時スイッチングノイズを低減するために、従来型の出力バッファに加えて、3タイプのスルーレート制御バッファを新たに開発した。スライス工程の第1層目のアルミ配線を切り替えることにより、出力のスルーレートを制御する構成としており、ユーザーは実装系のLCR、同時スイッチング数に応じて出力バッファのタイプを選択できる。

### 3.3 低スキュークロック分配方式

回路の大規模化に伴ってF/F等の順序回路数は増加し、クロックの負荷となる順序回路数は1,000個から2,000個にも達する。また、システムの高速化のためにはクロックサイクルの短縮化が必要なため、1ns以下の低スキューのクロック分配技術がゲートアレーにも要求されている。従来のクロックツリー構造では対応が困難なため、駆動力の大きいクロックドライバにより、一括駆動するクロック分配技術を新たに開発した。プリドライバセルとクロックドライバセル及びその出力信号を、内部セル領域に供給するためのリング状の配線を一体化してクロックライブラリとして提供する。クロックライブラリから順序回路への接続はスキューを低減するために、レイアウトツールにより、2層アルミと1層アルミのメッシュ状に自動配線される。4相クロックまで使用でき、総駆動可能ファンアウトは2,000まで許容している。

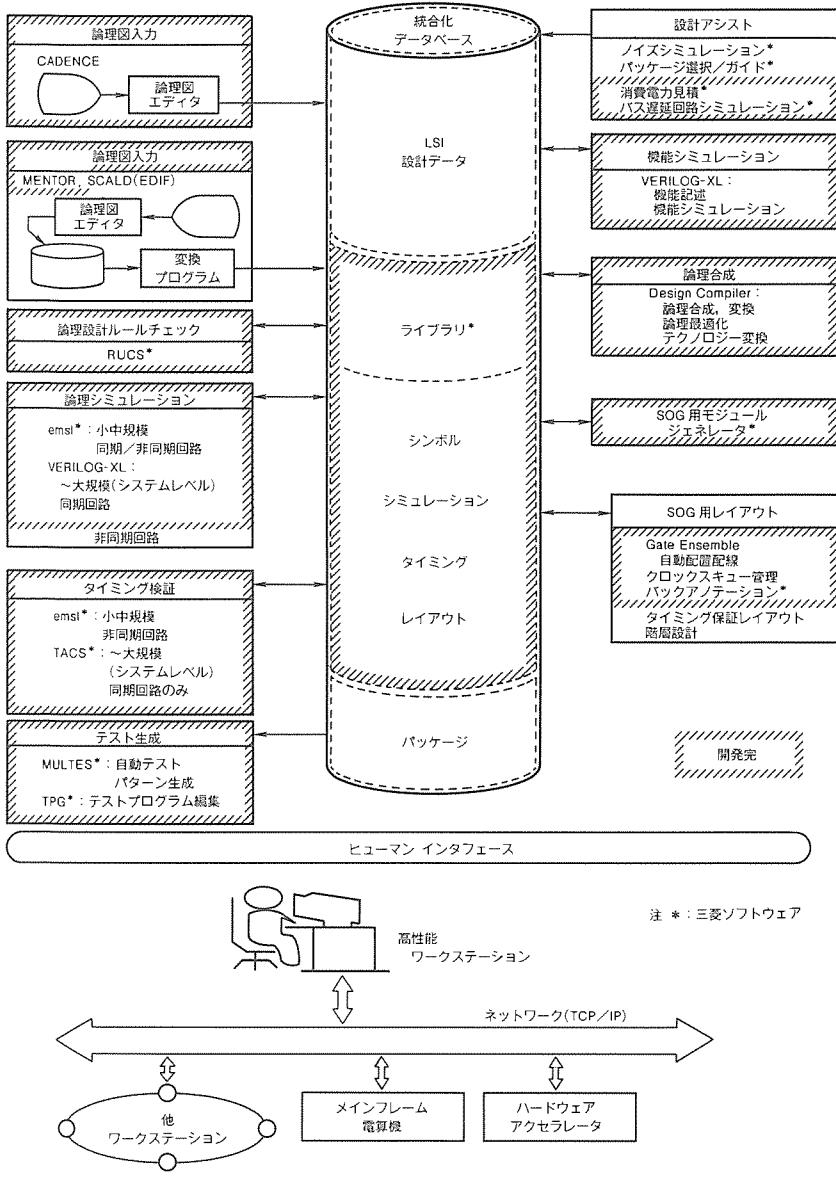

## 4. 設計システム(GA-2)の概要

0.8 μmCMOSゲートアレーを開発するため、現状のセルベース方式LSI設計システム(CB-1)をベースに、0.8 μmCMOSゲートアレー設計システム(GA-2)を開発した。この設計システムの構成を図3に示す。現在、図3の斜線部を品種開発に適用中である。

この設計システムの構築のねらいは、次のとおりである。

- (1) LSIの大規模化に対応して、設計の上流特に機能・論理設計部分の設計効率の向上を図る。このため、論理合成・変換の実用化、方式設計最適化のための機能シミュレータを実用化する。

- (2) 高性能VLSIを実現するため、主として下流設計の質の向上を図る。このため、クロックスキュー管理レイアウト、特定パス遅延解析のための回路シミュレーション、消費電力見積り、スイッチングノイズ対策、パッケージ選択サポート等のツールを開発する。

- (3) 共通の操作で異なる設計手法のLSIを設計できるようするため、CB-1とGA-2のフレームワークを統一し、1台のEWS上で機能・論理設計からレイアウト・テストプログラムまで一貫した操作で設計可能なLSI設計システムを開発し、ゲートアレーとセルベースの論理設計レベルのシステム統合を図る。

以下に主な構成内容を示す。

### 4.1 論理図入力

#### (1) スケマティックエディタ

論理図の入力・編集には、CADENCE社のスケマティックエディタを使用する。

入力した論理図面は、単に各アプリケーションに対する接続情報を提供するためだけに使用するのではなく、ユーザーインターフェースとして使用できる。例えば、対話形式シミュレーションにおける信号値表示、ブレークポイント指示を行ったり、ルールチェックプログラムやタイミングチェックプログラムの実行結果の対話的解析を行うインターフェースにも使用できる。これにより、従来長い階層名を入力したり、解釈したりしていた手間がなくなり、直感的に各ツールとインターフェースできる。

### 4.2 論理設計

設計した論理回路が、正しく動作することを確認するために、論理シミュレータを用いて検証する。このシステムでは、MOSトランジスタレベル、ゲートレベル及び回路の動作を専用の言語で記述する機能レベルの混合シミュレータとしてemslとVERILOG-XLを使用する。シミュレーションパターンの作成には、使用シミュレータによらない共通のシミュレーションパターン記述言語(MTPL)を使用する。また、

図3. 0.8 μm CMOS ゲートアレー設計システム

シミュレーション結果と期待値の比較は、共通のイベントフォーマット (MEF) を介することにより、同一の比較ツールを使用する。

これらの共通化によって論理設計者は、複数のシミュレータを使っていても一つのシミュレーションパターンをメンテナンスするだけでよく、また同一の操作法で作業できる。さらに、テストプログラム編集ツールが MEF をインターフェースとしてするのでシミュレーションパターンをテストのテストパターンにも使用できる。

同期式回路設計のタイミング検証は、信号経路トレース方式のタイミングチェックプログラムを使用する。この方式では、全経路の解析をシミュレーションパターンなしに高速に実行できる。一方、非同期式回路設計の場合には、ゲート遅延を考慮したシミュレータがタイミングエラーを検出する。考慮する遅延には、標準遅延、仮想配線容量に基づく遅延、実配線容量に基づく遅延が可能である。

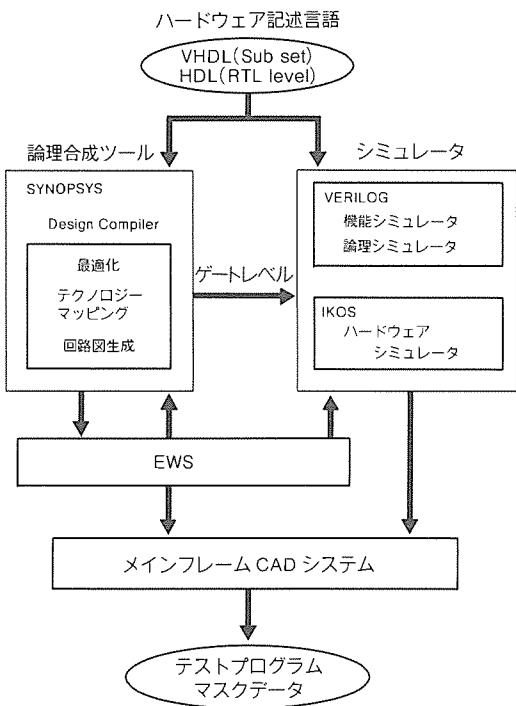

さらに、従来の設計・開発手法を越える技術として、論理合成技術を導入した。具体的には、真理値表、ブール式、組合せ回路の図面(ネットリスト)、及びVERILOG-XL のハードウェア記述言語 (HDL) を入力として、指定した設計制約(面積、遅延、ドライブ能力など)を満足する回路を生成する機能を実現した。論理合成ツールとしては、SYNOPSYS 社の Design Compiler を使用する。

#### 4.3 レイアウト設計

このシステムでは、0.8 μm CMOS ゲートアレーのレイアウト仕様を実現するために、CADENCE 社の Gate Ensemble を使用する。実現する主なレイアウト仕様を次に示す。

##### (1) RAM/ROM の使用

当社製モジュール ジェネレータが生成する RAM/ROM を含んだゲートアレーを、Gate Ensemble はレイアウトする。Gate Ensemble は、チャネルレスのレイアウトが可能であるため、RAM/ROM 内部に配線チャネルを設定する必要がなく高密度な RAM/ROM を使用できる。また、RAM/ROM の配置位置に制約がないため、チップ全体としても高集積なレイアウトが可能である。

##### (2) 信号の 3 層配線

セルの信号端子間を接続する信号配線は、配線チャネル内及びセル上を、1 層、2 層及び 3 層アルミを使用して自動配線する。

3 層アルミ配線は、1 層アルミ配線、2 層アルミ配線、及びマクロセル、RAM/ROM の上を通過できるため高集積なチップを実現する。

##### (3) クロックスキー管理配線

クロックのスキー値を保障するため、クロック信号は品種ごとに Gate Ensemble のコマンドで配線する。コマンドでは、配線の経路・幅・層を指定するので、品種ごとに最適なクロック配線を実現する。なお、配線コマンドはチップの集積度と RAM/ROM の位置を考慮して自動で生成できる。

#### 4.4 テスト CAD

大規模論理回路のテストの困難さ及びテストデータ生成時間の飛躍的増大に対処するため、テスト容易化設計とテストデータ自動生成ツールは、ASIC 開発に必要不可欠になっている。以下にこのゲートアレーのテスト CAD の特長を示す。

##### (1) 内蔵 RAM/ROM

当社製モジュール ジェネレータは、RAM/ROM 単体の

テストデータを生成する。このテスト CAD は、設計者が指定した LSI 外部から RAM/ROM へのアクセス経路に従って、RAM/ROM 単体テストデータを LSI 全体のテストデータへ自動変換できる。

また、あらかじめスキャンレジスタ等のテスト回路を内蔵した RAM/ROM を使用する場合には、RAM/ROM の面積は増加するが、アクセス経路の指定は不要になる。さらに、テスト回路のデータ圧縮機能を活用することにより、テストデータの短縮が可能になる。

## (2) スキャン変換

100KG を超える規模の論理回路では、テストデータ自動生成のためのスキャン設計が必ず(須)である。スキャン設計とは、LSI 内の記憶素子をスキャンレジスタに置換し、それらをシリアルバスで結合する手法である。このテスト CAD では、スキャン設計されていない論理回路をスキャン設計回路に自動変換することが可能である。

## (3) バウンダリスキャン方式のサポート

最近プリント回路基板のテスト容易化手法として、バウンダリスキャン方式が標準化されつつある。バウンダリスキャンとは、LSI の各 I/O 端子にシフトレジスタを割り付け、スキャンテストの原理によって LSI 端子に対する信号値の設定、観測を可能とする設計手法である。この手法により、テストプローブを立てにくい高密度実装基板に対してもインサーキットテストが可能になる。

このシステムは、当面この手法の実現に不可欠なバウンダリスキャンレジスタをセルとして、またそれらを制御するコントローラをマクロファンクションとして提供する。今後、バウンダリスキャン設計ルールチェック、バウンダリスキャン自動変換等のツールを提供する予定である。

## 4.5 モジュール ジェネレータ

このゲートアレーでは、数百 K ゲート規模の回路を 1 チップ上に実現できる。このような規模の回路にとって、大容量の RAM/ROM は必要不可欠である。このシステムのモジュール ジュネレータにより、設計者は簡単なパラメータ(例えば、RAM の場合ビット長、ワード長等)を指定するだけで RAM/ROM を自動で生成可能である。

ジュネレータは、単にレイアウトデータや論理回路入力用シンボルだけではなく、図 4 に示すように種々のツールが必要とするデータ(例えば、タイミング検証用データ、単体テストデータ等)も自動生成する。

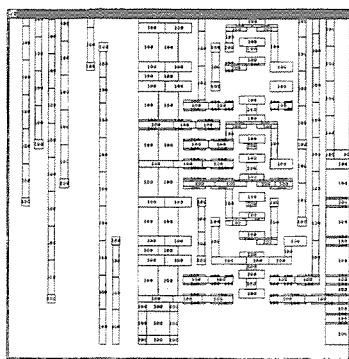

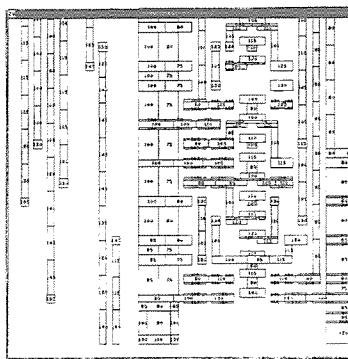

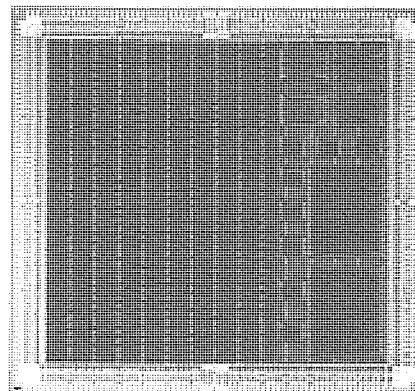

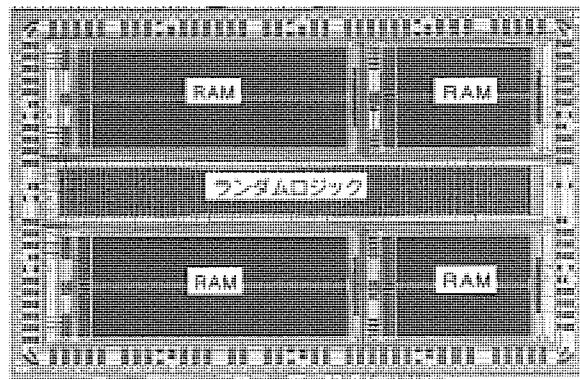

## 5. LSI 試作結果

100KG を超える大規模回路を GA-2 を用いて設計し、3 層アルミ配線  $0.8 \mu\text{m}$  CMOS プロセス技術によって試作した。図 5 は、250KG のチップ写真であり、チップサイズは  $13.08\text{mm} \times 12.22\text{mm}$  である。この LSI は 64 点の高速フーリエ変換を行う機能を持ち、1 相エッジトリガによる同期式

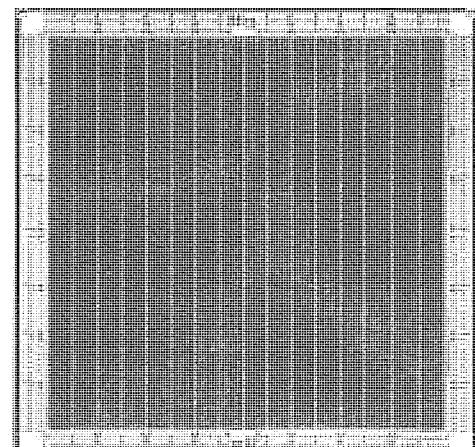

設計で実現され、1812 の F/F をクロック ドライバによって一括駆動している。回路規模は、42KG のロジックとモジュール生成された 9 ビット  $\times$  32 ワードの 1p-RAM を 8 ブロック、16 ビット  $\times$  64 ワードの 2p-RAM を 4 ブロック、16 ビット  $\times$  512 ワードの 2p-RAM を 2 ブロック搭載している。内蔵の 1p-RAM を EB テスタによって評価した結果、アクセスタイム 6ns が得られた。図 6 に 400KG のチップ写真を示す。チップサイズは  $14.56\text{mm} \times 14.46\text{mm}$  である。

図 4. RAM ジェネレータシステムの概要

図 5. 250KG チップ写真

図 6. 400KG チップ写真

表1. M6008Xシリーズの仕様

| 品種名             | M60084                                 | M60085                                                                                                            | M60086 | M60087      | M60089      |

|-----------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|

| 総敷き詰めゲート数(Kゲート) | 80                                     | 120                                                                                                               | 170    | 250         | 400         |

| チップサイズ(mm)      | —                                      | —                                                                                                                 | —      | 13.08×12.22 | 14.56×14.46 |

| 最大I/O数          | —                                      | —                                                                                                                 | —      | 384         | 512         |

| RAM容量(ビット)      | シングルポート<br>デュアルポート                     | 256~9K                                                                                                            |        |             |             |

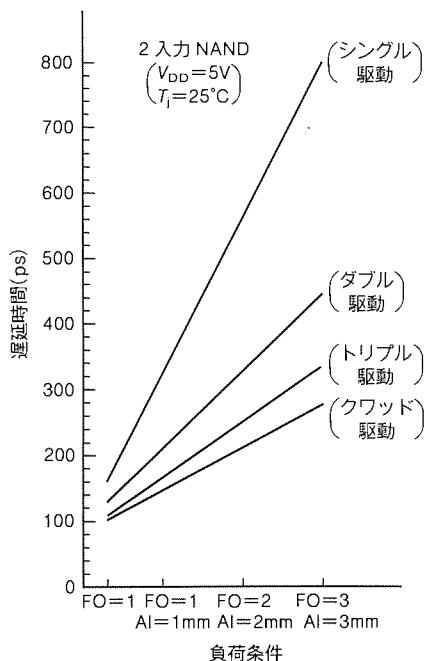

| 遅延時間            | 内部ゲート                                  | 135 ps (2 NAND トリプル駆動 $FO = 2$ )<br>255 ps (2 NAND トリプル駆動 $FO = 2$ , 配線長 = 2 mm)                                  |        |             |             |

|                 | パッファ                                   | TTL入力バッファ 0.62 ns ( $FO = 2$ , 配線長 = 2 mm)<br>出力バッファ ( $I_{OL} = 8 \text{ mA}$ ) 2.0 ns ( $C_L = 50 \text{ pF}$ ) |        |             |             |

| 出力電流(mA)        | $I_{OL} = 1, 2, 4, 8, 16, 24$          |                                                                                                                   |        |             |             |

| テクノロジー          | 0.8 $\mu\text{m}$ CMOS 2層/3層 アルミ配線プロセス |                                                                                                                   |        |             |             |

注 ——: 開発中

図7. 2入力NAND遅延時間負荷依存性

121KGを集積し、1相エッジトリガによる同期式設計で実現され1615の4b-F/Fをクロックドライバにより、一括駆動している。

基本ゲートの速度については、図7にプロセスモニタ用TEGに収納した2入力NANDリングオシレータの遅延時間負荷依存性の測定結果を示す。最適な設計ができるよう4種

類の駆動力から選択でき、標準的な負荷条件の $FO = 2$ 、配線長=2mmに対し255ps(トリプル駆動)、215ps(クワッド駆動)と高速性能が得られクリティカルパスの高速化に有効である。

## 6. 製品概要

表1にM6008Xシリーズのレパートリ及び製品仕様を示す。総敷き詰めゲート数世界最大級の400KGを実現しており、以下250KG、170KG、120KG、80KGまで展開する。各マスター及びセルライブラリは2層/3層アルミ配線プロセス共通の構造とし、集積度とコスト、製造期間のトレードオフにより2層プロセス、3層プロセスのいずれかを選択できる。

パッケージは、高集積化に伴う多ピン化の要求に対応するため、TAB方式によるTCP(Tape Carrier Package)を採用し、最大512 I/Oを実現している。

## 7. むすび

本稿では、高速・高集積化のための0.8  $\mu\text{m}$  3層アルミ配線プロセス技術と多ピン化のためのTAB技術を採用したM6008Xシリーズのデバイス技術とEWSベースの設計システム(GA-2)の概要を述べた。また、100KGを超える大規模回路の試作例を紹介した。今後幅広い分野への応用に対応するため、大規模RAM等のライブラリ拡充による高機能化を図っていく予定である。

# 1.0 $\mu$ mCMOS ゲートアレー M60060 シリーズ

鈴木正博\* 小野眞司\*

中村博隆\* 瀧口真美\*

布上裕之\* 福水利之\*

## 1. まえがき

プロセス技術や CAD の目覚ましい進歩により、ASIC はますます高速かつ高集積になると同時に多機能化の道を歩んでいる。ASIC のうちでも CMOS ゲートアレーは、高ゲート化・高性能化のテンポが早く、高性能化が進むにつれて従来問題とならなかった LSI の発するノイズや発熱等、システム設計時点から考慮しておくべき重要な問題が表面化してきた。

当社では、高速化、低消費電力化、さらにより一層の多ビンパッケージ化を実現するとともに、出力端子の同時スイッチングノイズ対策を講じた 1.0  $\mu$ mCMOS ゲートアレー M60060 シリーズを開発した。本稿では、M60060 シリーズの特長及び技術について述べるとともに、CAD サポート体制について紹介する。

## 2. 1.0 $\mu$ mCMOS ゲートアレー M60060 シリーズの特長

M60060 シリーズの主な特長を以下に示す(図1)。

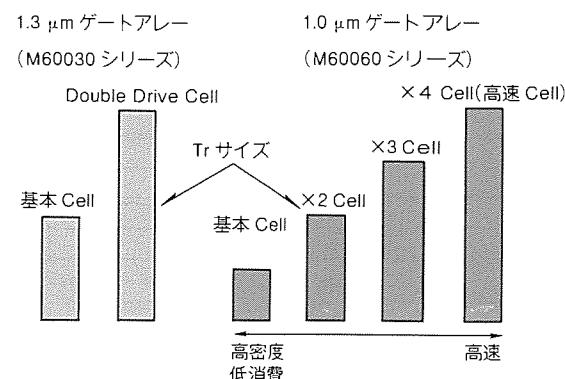

### 2.1 高速性能と低消費電力の最適化の実現<sup>(1)</sup>

高速性能を追求する余りトランジスタのサイズを大きくすると、消費電力が増大しゲート密度が低下する。逆にトランジスタのサイズを小さくすれば高密度で低消費電力になるが、速度が遅くなる。これは、LSI 全体にいえる傾向で、ゲートアレーもその例外ではない。従来のゲートアレーは、高速性能とゲート密度のバランスを考慮してトランジスタのサイズを決定していた。

このシリーズに従来の考え方を当てはめると、トランジスタサイズは  $W=20\sim25 \mu\text{m}$  となる。しかし、例えば同じマクロセル内で隣のトランジスタをドライブする場合、このサ

図1. 1.0  $\mu$ mCMOS ゲートアレー M60066 チップ写真

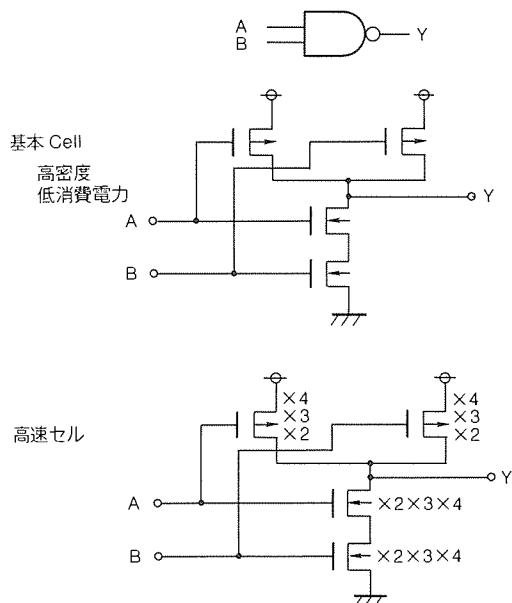

イズでは大き過ぎ、図2に示す考え方を導入した。すなわち、基本となるトランジスタの大きさを従来の考え方によるサイズの約1/2にし、その上で基本トランジスタサイズの2倍、3倍、4倍のトランジスタサイズを持ったマクロセルを開発した。図3に2入力 NAND ゲートのマクロセルの例を示す。低消費電力セル・高速セル・高駆動能力セルと各種セルを開発したので、回路の中で特に高速性能が要求される部分には、高速セルを選択し、それ以外は低消費電力セルを選択することにより、高速性と低消費電力の最適化がきめ細かく図れるようになっている。表1に2入力 NAND ゲートにおける各種セルタイプのゲート速度、消費電力値を示す。

### 2.2 高密度マクロセルの開発

当社の CMOS ゲートアレーは、独自のゲート アイソレーション方式を基本セル構造に採用し、高密度セル化を図ってきた。M60060 シリーズにおいても、この方式を導入するとともに、マクロセル内の配線本数を極限まで減少させ、より一層の高密度化を図っている。図4にゲート アイソレーション方式と酸化膜分離方式における 3 入力 NAND ゲートのセル構造を示す。ゲート アイソレーション方式では、酸化膜分離方式に比べて、集積度で約 20 %、スピードで約 10 % の性能向上が得られる。また、一世代前の 1.3  $\mu$ mCMOS ゲートアレーから採用したゲート全面敷き詰め構造を採用し、チャネル方式ゲートアレーの約 2 倍のメモリを効率的に内蔵することができた。

### 2.3 ノイズ低減回路付き出力バッファの開発

プロセス技術の微細化によって LSI の高速化が進むなかで、従来は影響が少なかった出力端子の同時スイッチングノ

1. 基本マクロセルを縮小 → 高密度、低消費電力を実現

2. 高速マクロセルを用意 → 高速性の実現

3. 4種類のマクロセルを選択 → 高密度、低消費と高速の最適化設計

図2. 高密度・低消費電流と高速との最適化設計

ノイズに対する問題が表面化してきた。

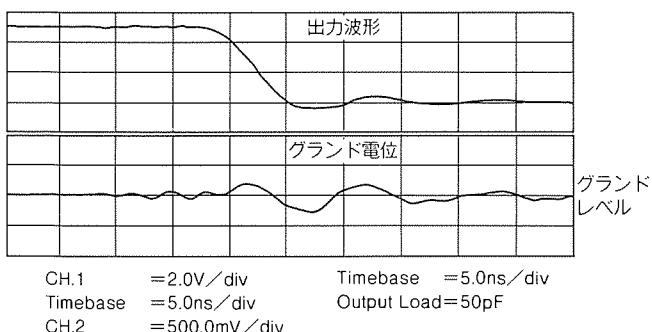

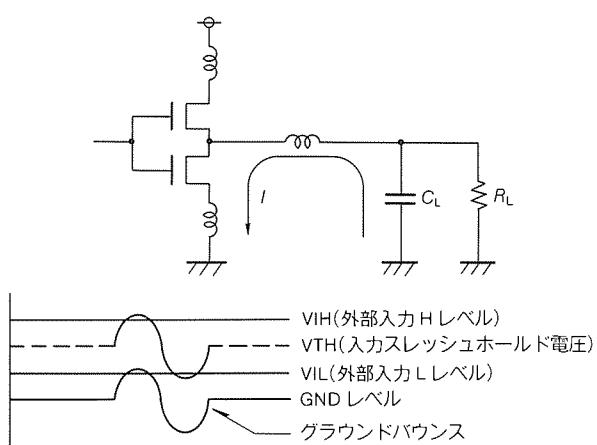

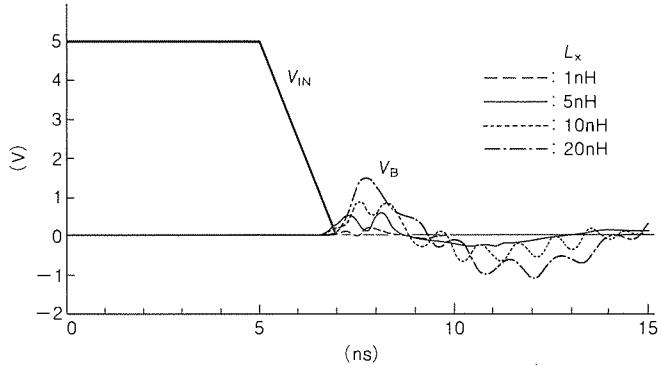

出力端子がスイッチングすることにより、負荷容量を充放電するため、負荷とLSI素子間に過渡電流が流れる。そして、この過渡電流に対する電流変化率( $di/dt$ )は、LSIの高速化に伴って大きくなる。そのため、特に複数の出力端子が同時にH→Lに変化した場合、この電流変化率( $di/dt$ )によってLSIと基板間のインダクタンスに電圧が誘起され、LSIの接地電位が上がる。これがグラウンドバウンスであり、同時スイッチングノイズとも呼ばれる。このグラウンドバウンスは、図5に示すように入力レベルマージンの低下を引き起こし、最悪の場合システムの動作に悪影響を与える<sup>(2)</sup>。

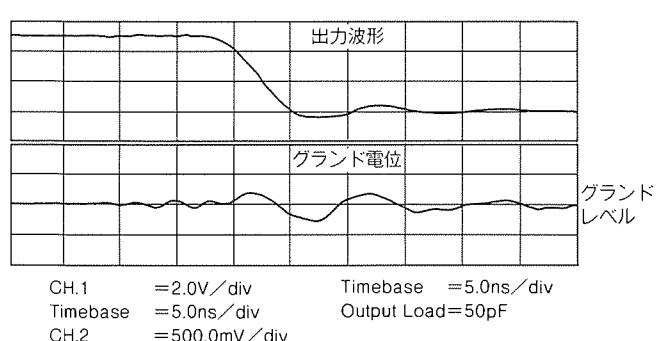

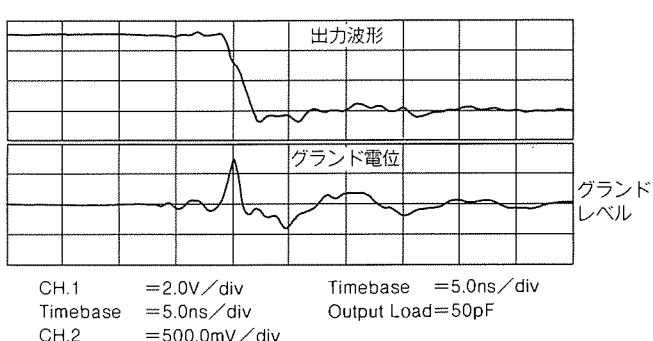

M60060シリーズでは、この同時スイッチングノイズを抑えるために、出力バッファ及び多方向バッファにノイズ低減回路付きバッファを用意した。図6にノイズ低減回路付き出力バッファとノイズ低減回路なし出力バッファのスイッチング応答波形例を示す。ノイズ低減回路付き出力バッファの方が、グラウンドバウンスが約1/4に低減されていることが分かる。

図3. 2入力NANDゲートにおけるマクロセル構成例

表1. 2入力NANDゲートにおけるゲート速度と消費電力

| セルタイプ             | 低消費電力 |     |     |     |

|-------------------|-------|-----|-----|-----|

|                   | 4     | 3   | 2   | 1   |

| ゲート速度(ps)         | 370   | 400 | 450 | 630 |

| 消費電力(μW/MHz/Gate) | 12    | 9   | 7   | 5   |

注 FO(Fan Outの略)=2, AI=2mm

図4. 3入力NANDゲートにおけるセル構造

図5. 出力端子のスイッチングによるグラウンドバウンス

(a) ノイズ低減回路付き出力バッファ

(b) ノイズ低減回路なし出力バッファ

図6. 出力バッファのスイッチング応答波形例

## 2.4 多ピンパッケージ対応マスタの開発

ゲートアレーの応用範囲は、データプロセッシング市場を始め、通信・工業用と拡大してきている。ゲート数についても、数千ゲートから数万ゲートが主流となっているが、機器の小型化を図るためにできるだけパッケージ数を減らす必要があり、100ピンから208ピンの多ピンプラスチックQFPパッケージが主に採用されている。このため、ゲート数にかかわらず多ピンパッケージの使用可能なゲートアレーの重要性が増してきている。

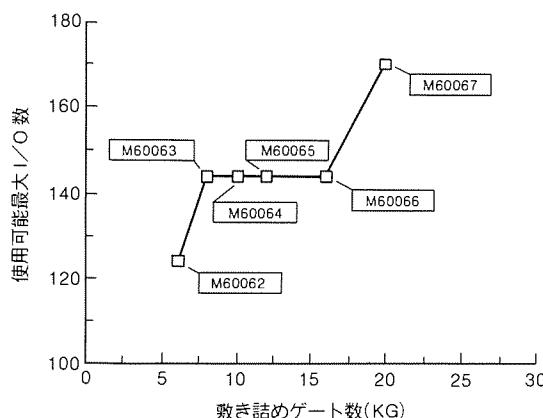

このニーズにこたえるため、敷き詰めゲート数6~20KGで、かつ120~208ピンのプラスチックQFPパッケージが使用できるゲートアレーとして、M60060シリーズを開発した。多ピンパッケージ対応マスタを開発するに当たっては、従来のアセンブリ技術では対応できないため、微細ワイヤボンディング技術の導入を行った。この技術によってパッドピッチを120μmまで縮小するとともに、微細リードフレーム加工技術を導入することにより、敷き詰めゲート数8KGで160ピンQFPパッケージが使用可能となった。図7に、M60060シリーズのゲート数と使用可能最大I/O数の関係を示す。

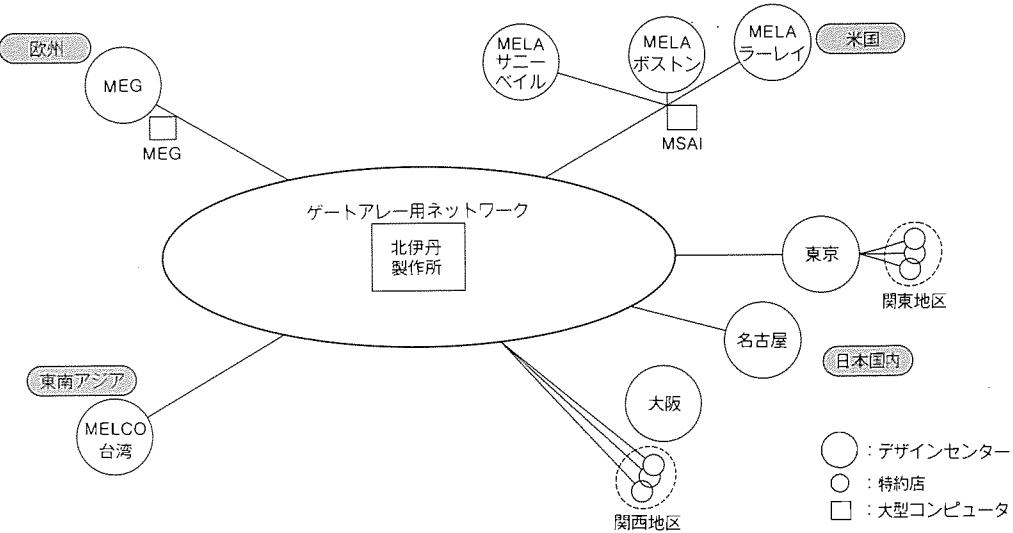

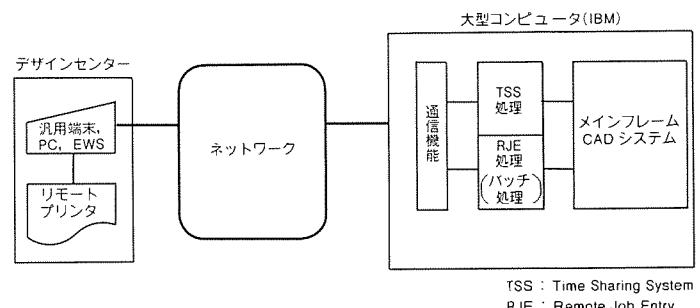

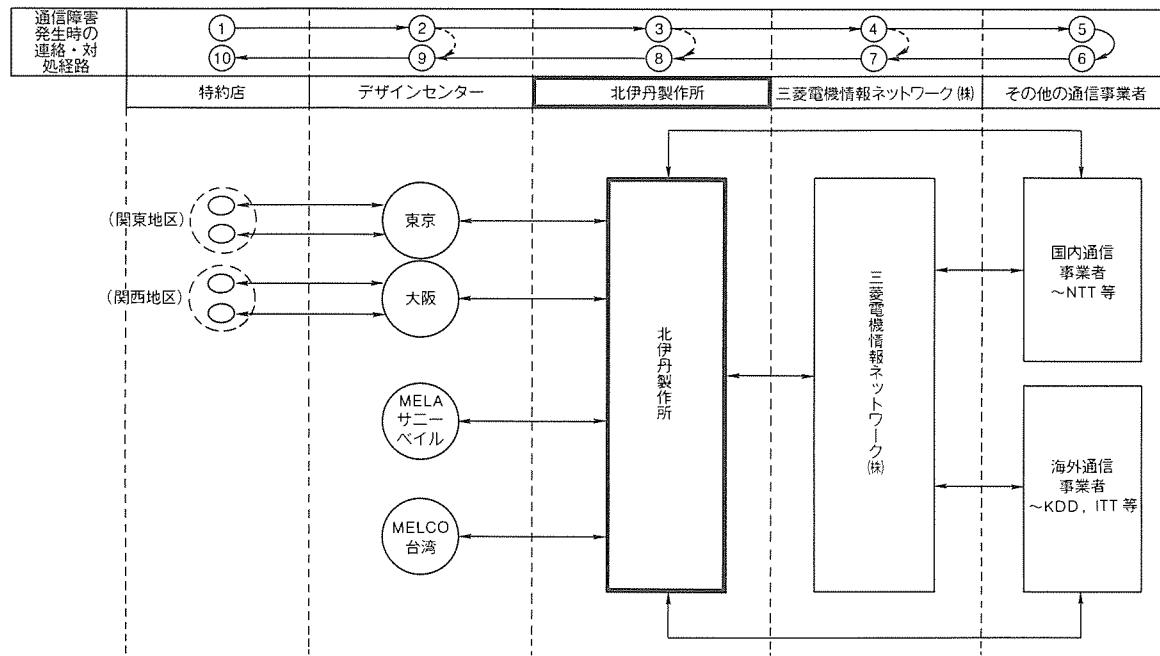

### 3. ゲートアレー CAD システムの概要

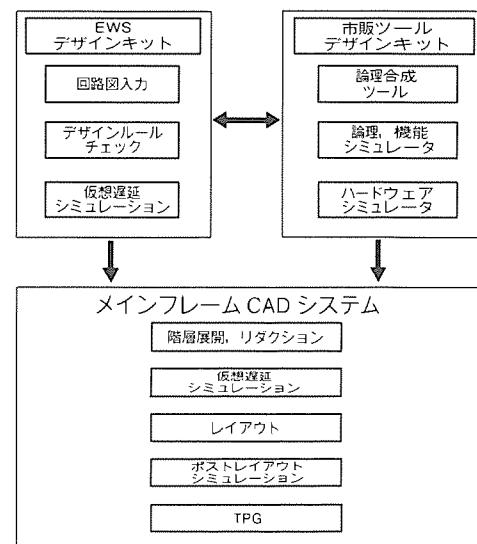

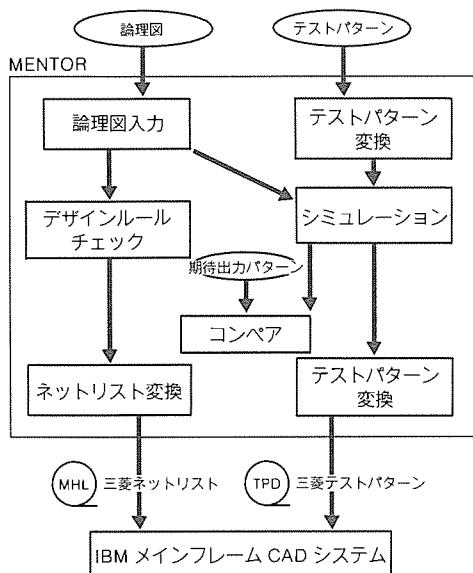

ゲートアレー設計に使用されるCADシステムは、図8に示すように、①EWS(Engineering Work Station)デザインキット、②市販ツールデザインキット、③メインフレームCADシステムで構成されている。

EWSデザインキットは、論理図入力、論理シミュレーションを主として行う総合的な論理設計システムである。EWSの普及に伴い、ユーザーの場所で使用されることが増え、精度の高い論理検証が要求されるため、EWSデザインキットの重要性がますます高くなっている。

市販ツールデザインキットは、ハードウェアシミュレータ、論理合成、レイアウトツール等の個別的な設計ツールである。EWSにはない機能、専門的に優れた性能を持ち、EWSと併用して使われるケースが増えている。

図7. M60060シリーズ使用可能最大I/O数

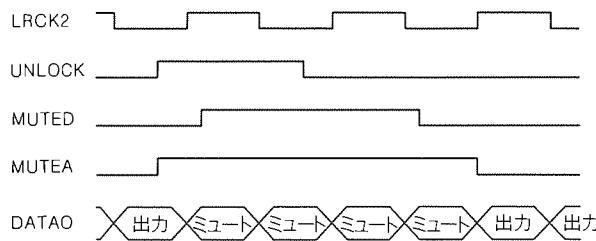

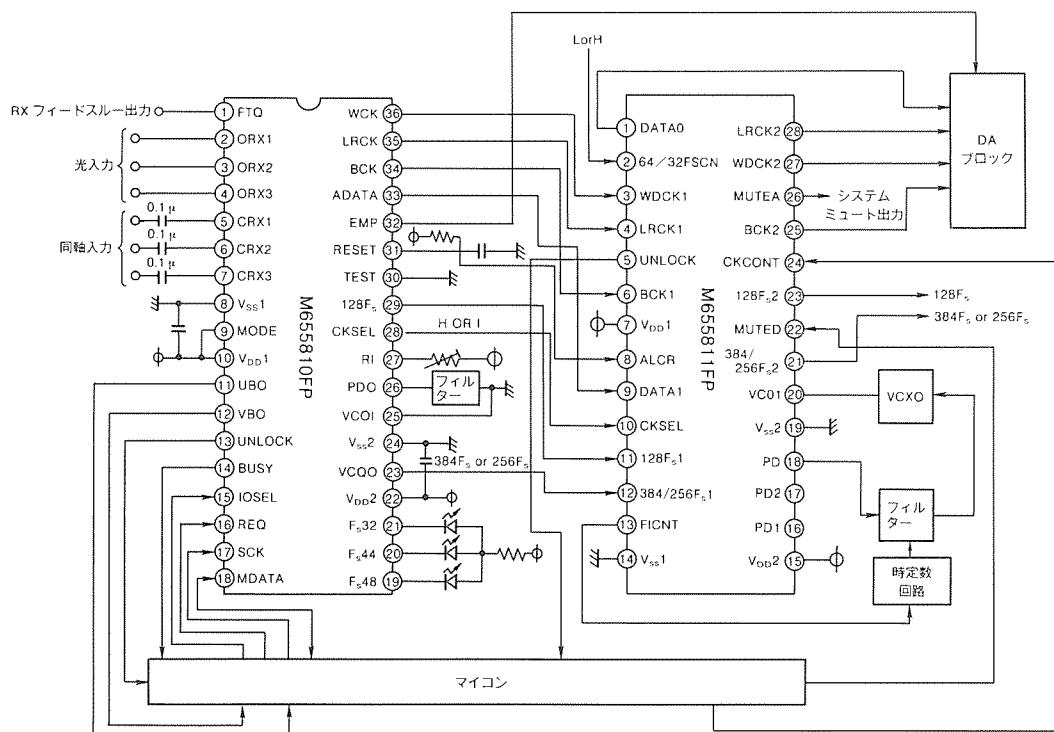

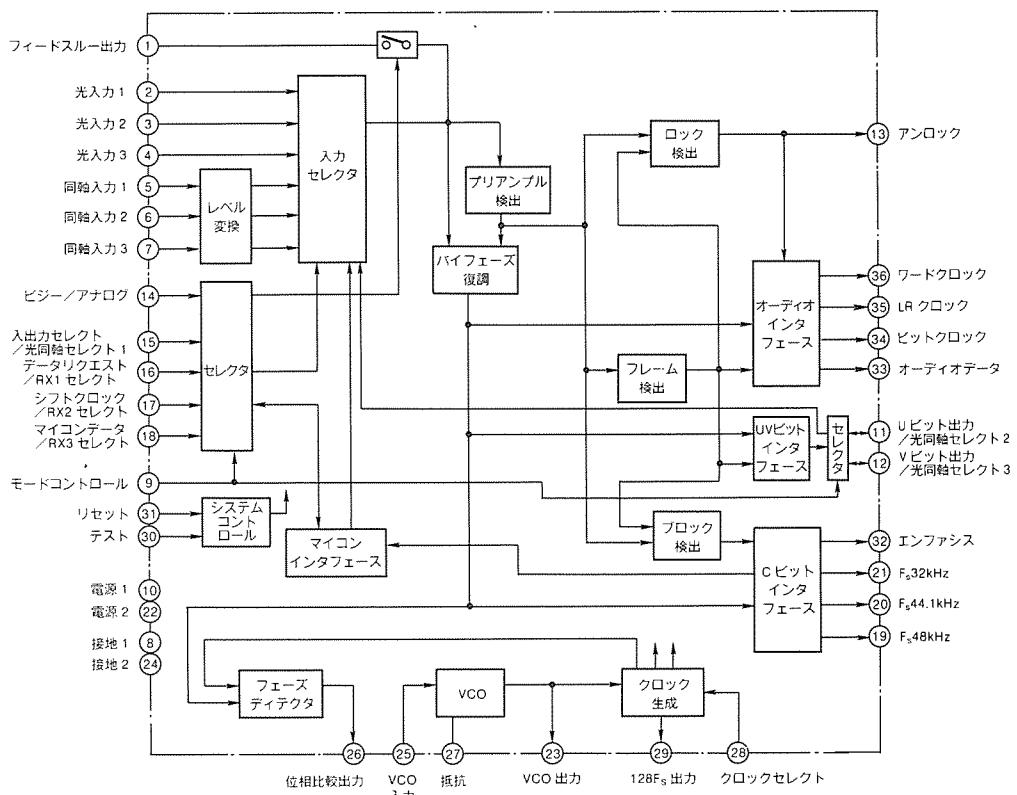

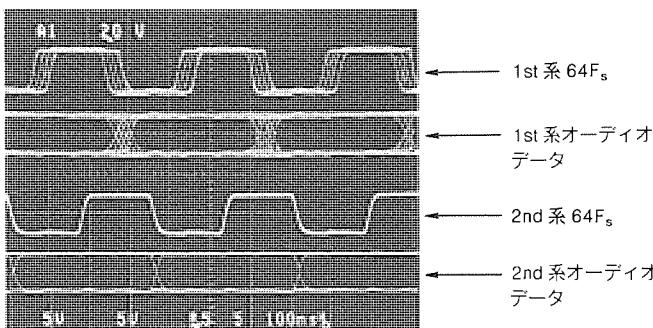

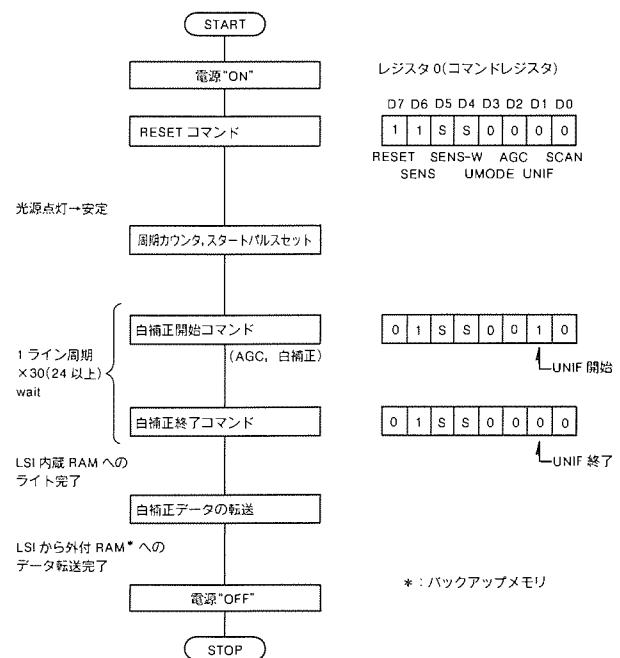

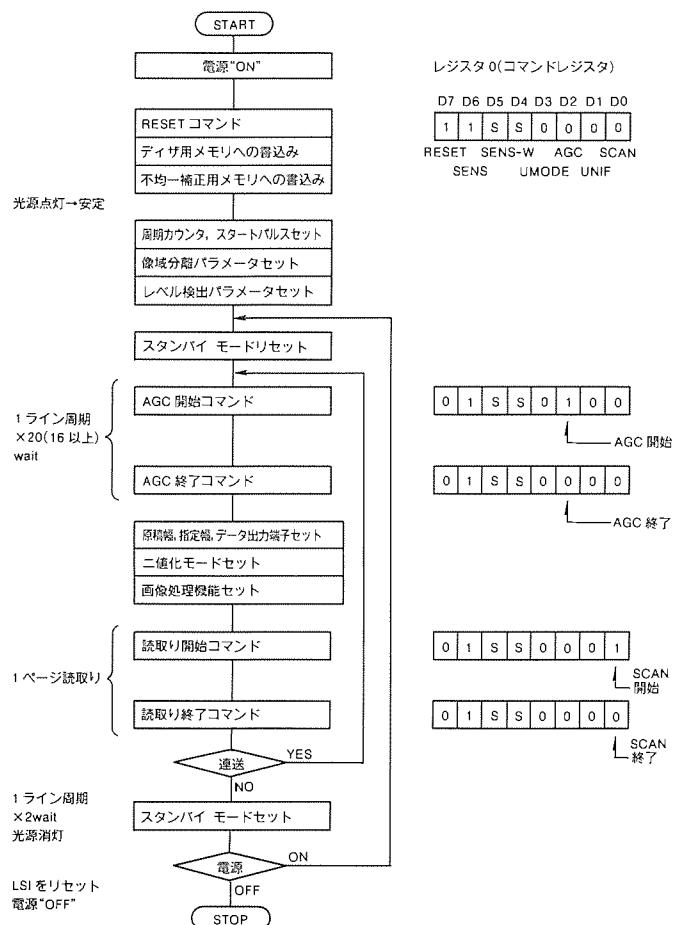

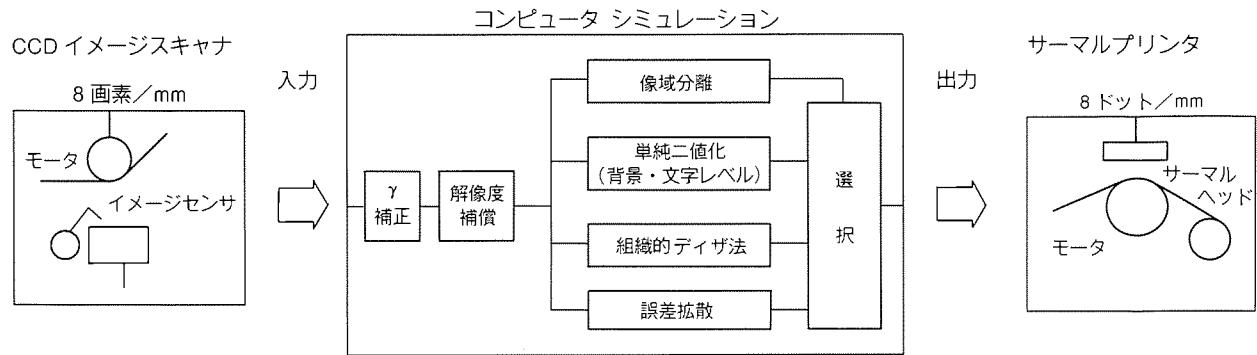

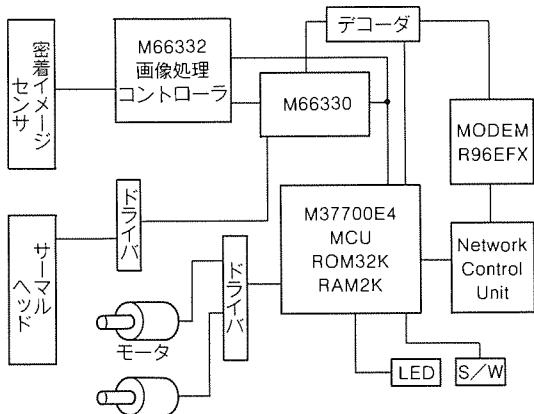

EWSデザインキットと市販ツールデザインキットは、ユーザーが所有している汎用的なCADツールに対して三菱ゲートアレー ライブドリとインターフェース ソフトウェアを提供する形式であり、ユーザーが自ら構築する設計システムに適応したサービスを提供するものである。