# MITSUBISHI

# 三菱電機技報

MITSUBISHI DENKI GIHO Vol.63 No.11

11

1989

三菱半導体事業30周年記念特集号

## 三菱半導体事業30周年記念特集号

### 目 次

|                                     |    |                                                                        |      |

|-------------------------------------|----|------------------------------------------------------------------------|------|

| 巻頭言                                 | 1  | 光通信用1.5μm帯MQW-DFBレーザ                                                   | 93   |

| 志岐守哉                                |    | 柿本昇一・吉田直人・榎原 靖・水口一男・須崎 渉                                               |      |

| カラーグラビア                             | 2  | 超低雑音GaAsSAMFETの開発とMMICへの応用                                             | 97   |

| 三菱半導体事業30周年に寄せて                     | 12 | 細木健治・綾木なぎさ・加藤隆幸・谷野憲之・高野博三                                              |      |

| 坂村 健                                |    | インバータ用パワーICモジュール                                                       | 100  |

| 佐藤真一・若宮 亘・重富 晃                      |    | 中嶋利廣・ゴーラブ マジムダール・福永匡則・飯尾幸司・梶田武良・宮嶋辰夫                                   |      |

| <b>特集論文</b>                         |    | 三次元形状シミュレータ                                                            | 105  |

| 三菱電機半導体技術30年の歩み                     | 14 | 藤永正人・小谷教彦                                                              |      |

| 小宮啓義                                |    | 超微細加工プロセス技術                                                            | 109  |

| 最先端DRAMプロセス技術                       | 17 | 西岡久作・小川佐知子・藤原伸夫・河合 晃・魚谷重雄・永田一志                                         |      |

| 佐藤真一・若宮 亘・重富 晃                      |    | 斜め回転イオン注入技術                                                            | 112  |

| 4Mビット ダイナミックRAM                     | 23 | 御城俊宏・高橋武人・大崎三郎・長友正男                                                    |      |

| 宮本博司・長友正男・山田通裕・長山安治・水津克巳            |    | アイススクラバ洗浄                                                              | 116  |

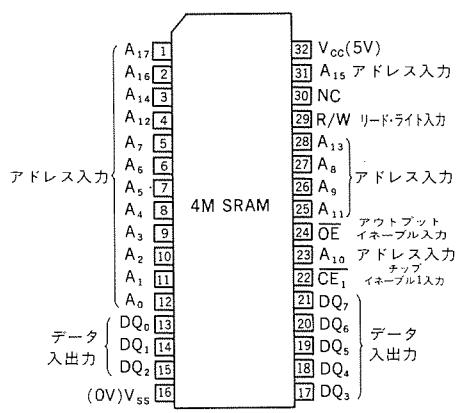

| 高速1MビットCMOSスタティックRAM                | 27 | 大森寿朗・福本隼明・加藤忠雄・川口利明・多田益太                                               |      |

| 菅野雅直・和田知久・杠 幸二郎・向井孝夫・河野芳雄           |    | 半導体のFA技術                                                               | 120  |

| 5V単一電源で動作する高速1MビットEEPROM            | 31 | 石橋一昭・大谷雅樹・吉田博之・加藤雄一                                                    |      |

| 寺田 康・有馬秀明・小林和男・味香夏夫                 |    | <b>特許と新案</b>                                                           |      |

| 1MビットデュアルポートRAM                     | 35 | 半導体メモリ装置、MOS型半導体不揮発性メモリ装置の製造方法                                         | 125  |

| 小川俊行・井上一成・浜野尚徳                      |    | 半導体レーザ                                                                 | 126  |

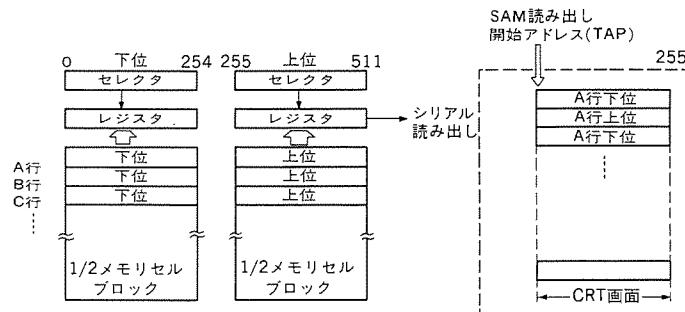

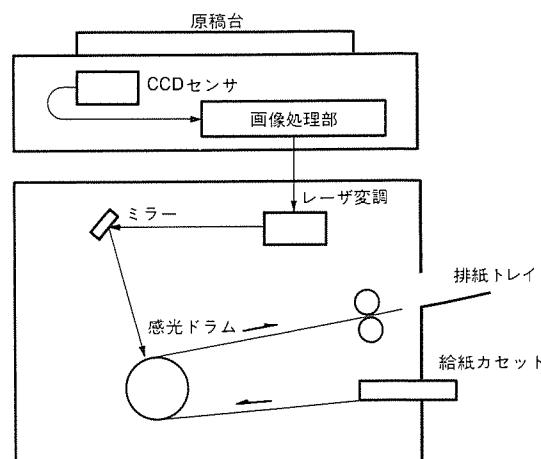

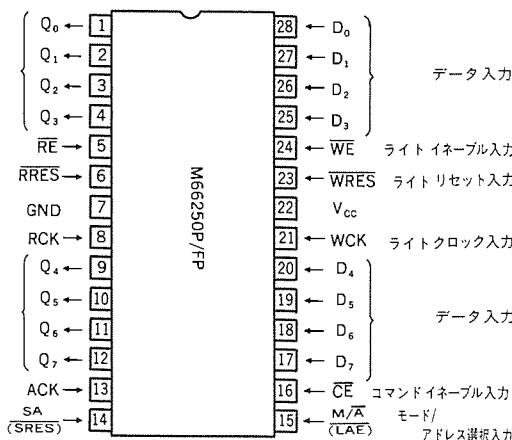

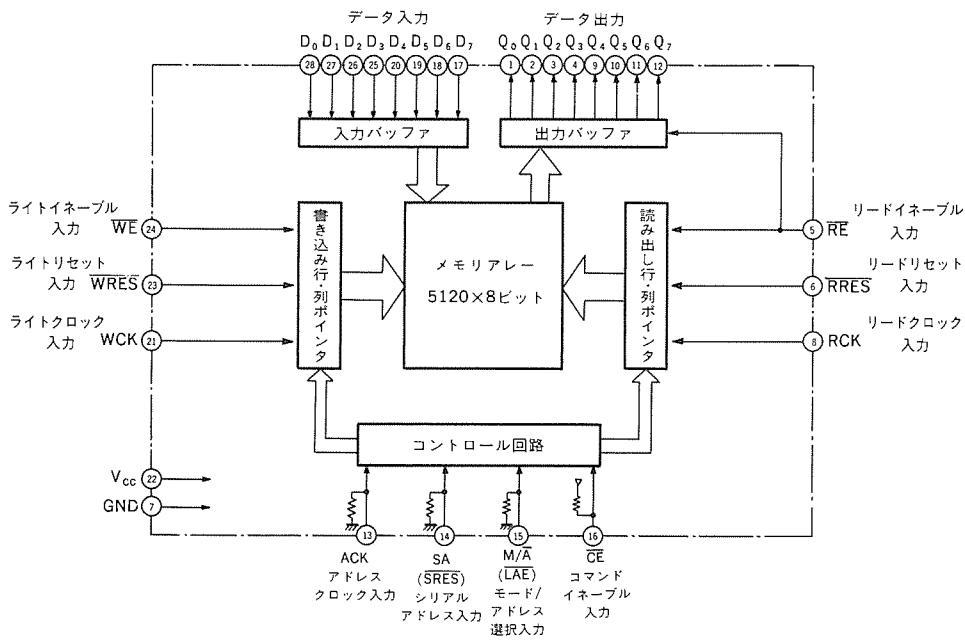

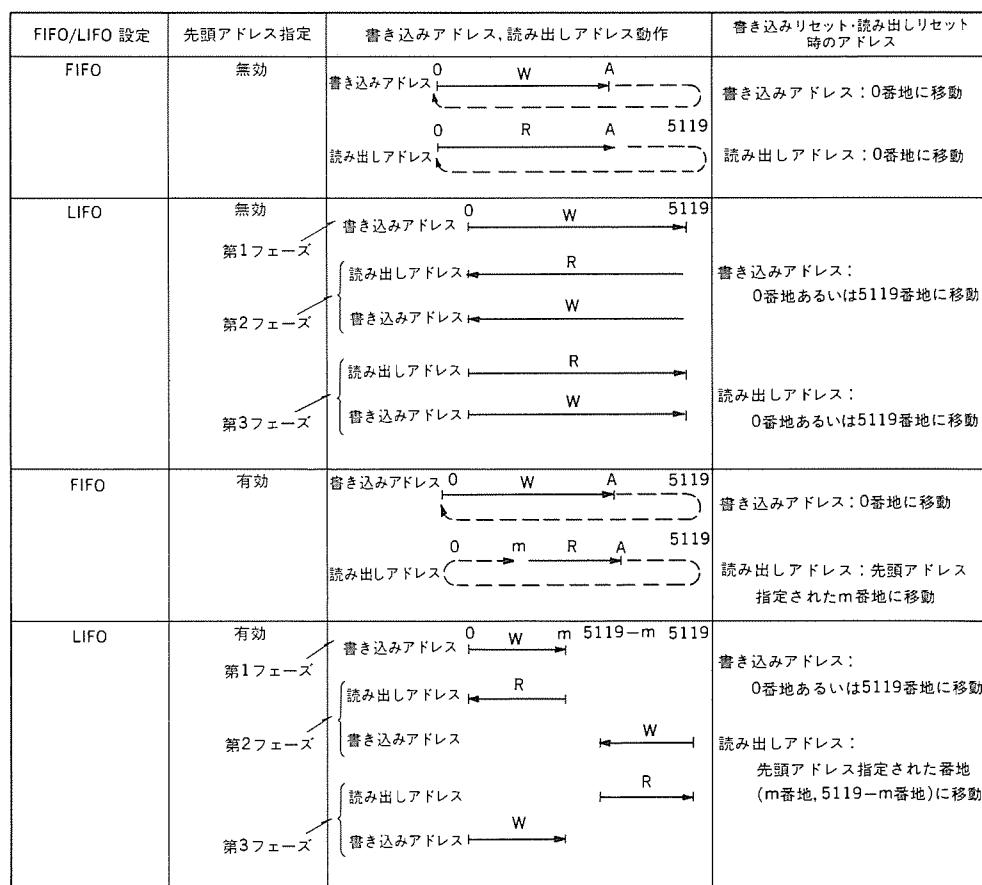

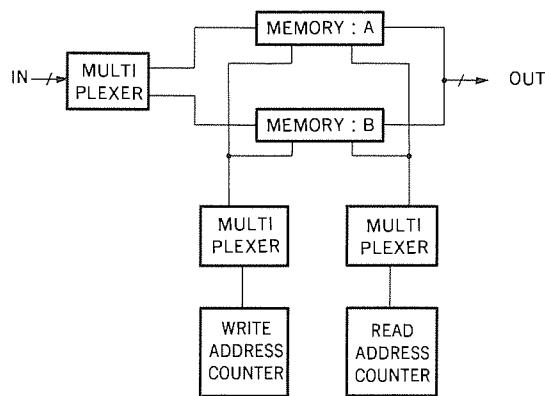

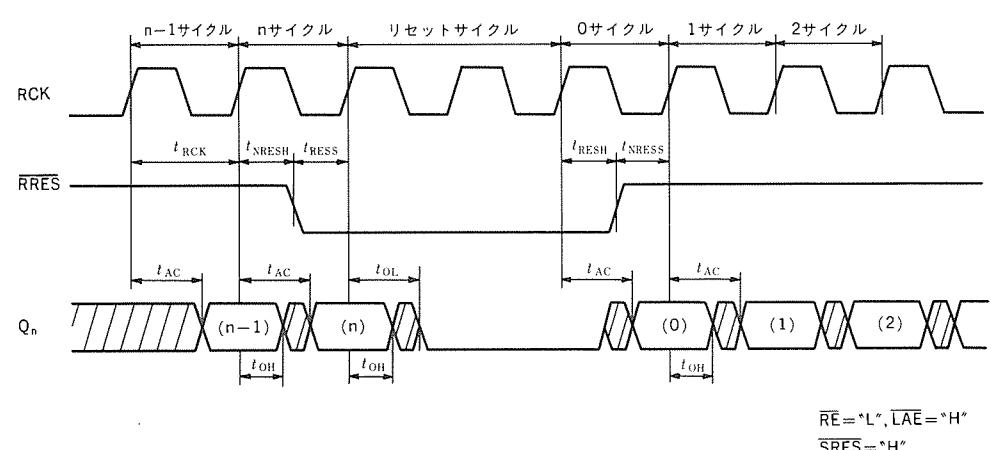

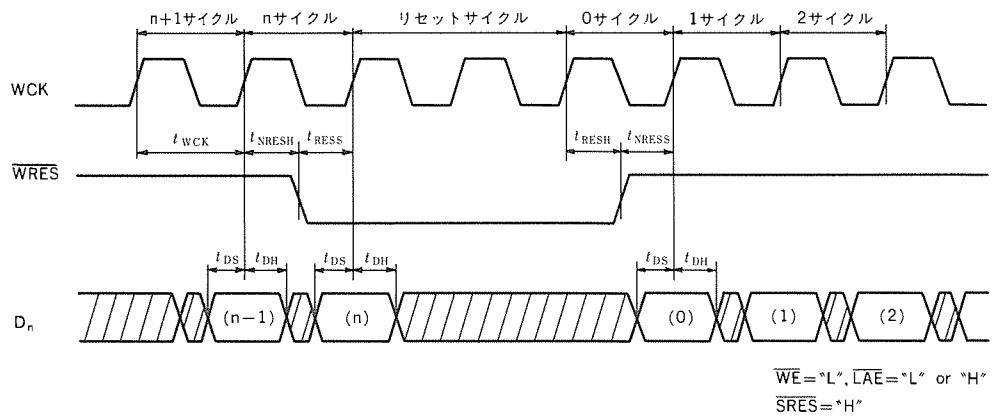

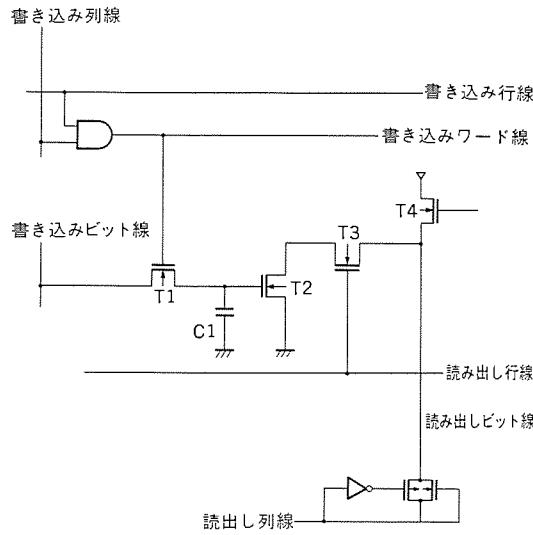

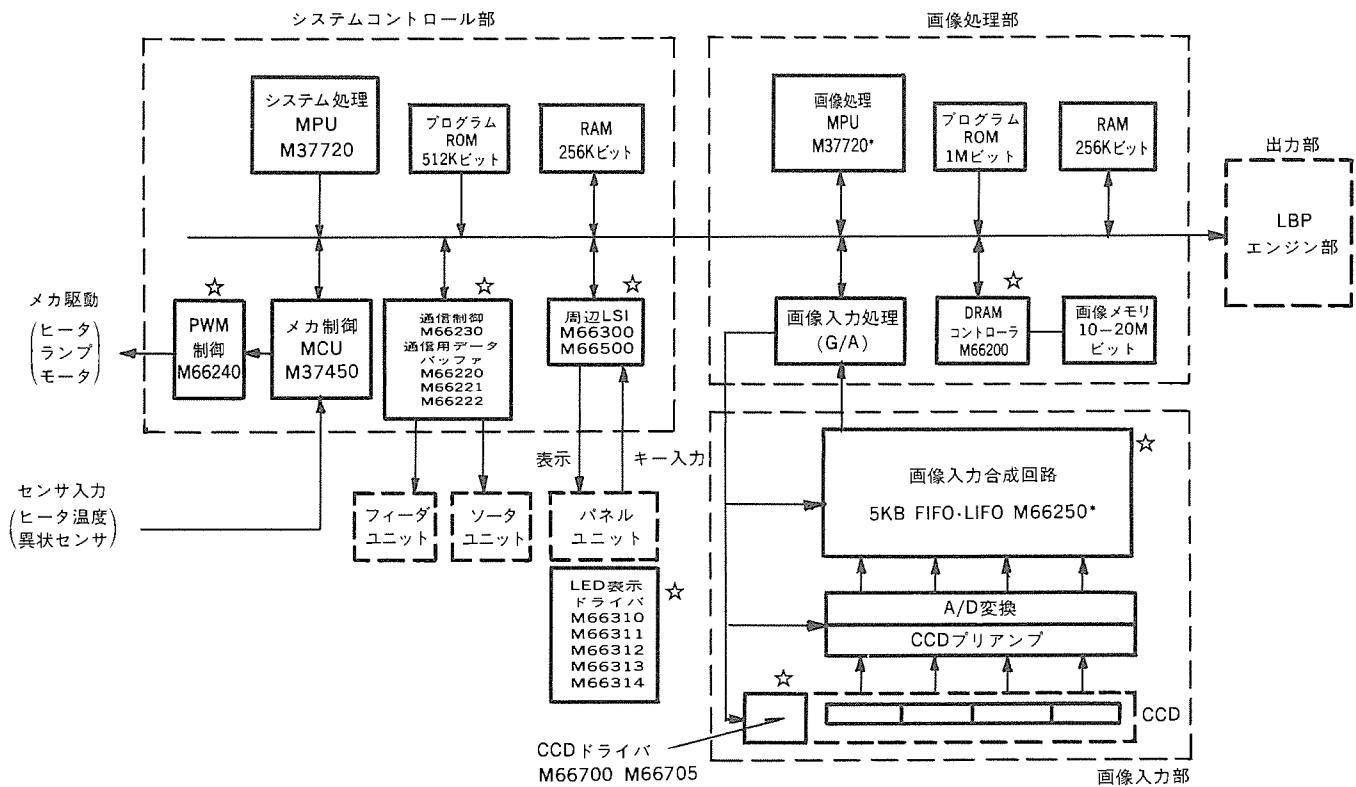

| ディジタルPPC用5KバイトFIFO/LIFOメモリIC        | 39 | <b>製品紹介</b>                                                            |      |

| 前田安範・沖高毅則・池田敏男・宮田和明・服部正人・鎌倉 寛       |    | 三菱32ビットマイクロプロセッサ                                                       | 124  |

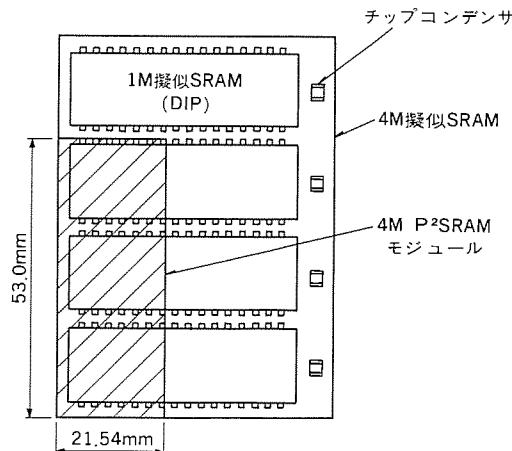

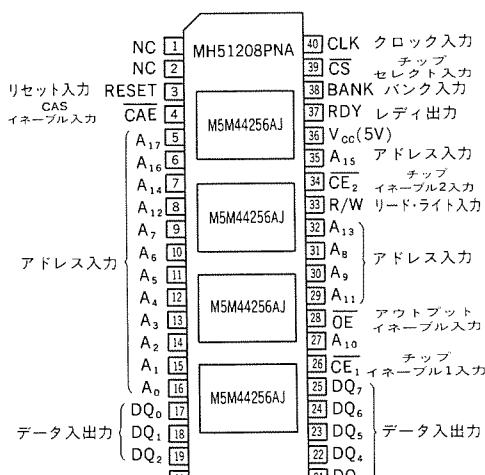

| 4MビットP <sup>2</sup> SRAMモジュールの開発と応用 | 45 | 三菱大容量メモリカード                                                            | (表3) |

| 田原次夫・小杉龍一・谷口正治・辻 哲郎・戸田 均            |    | <b>表紙</b>                                                              |      |

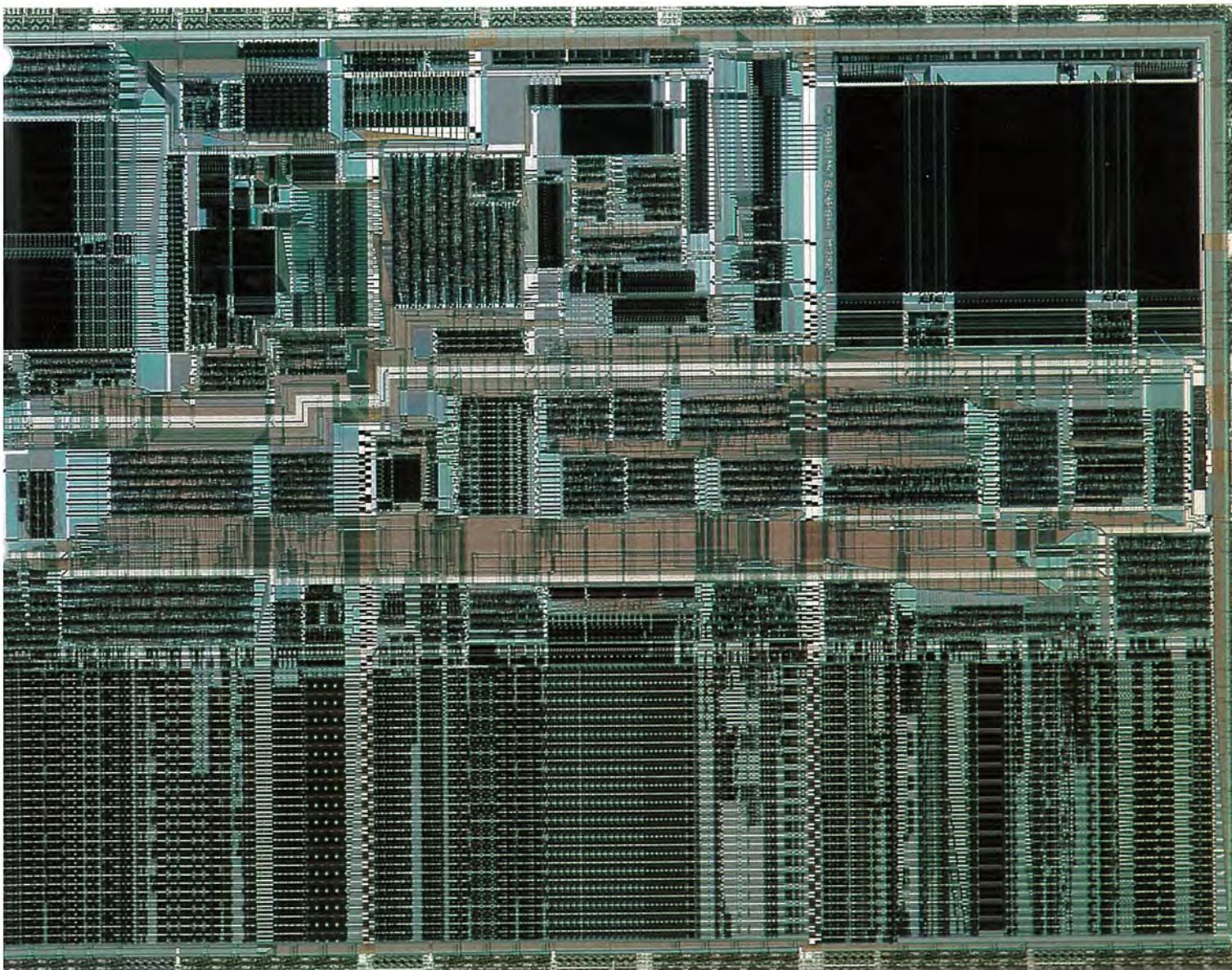

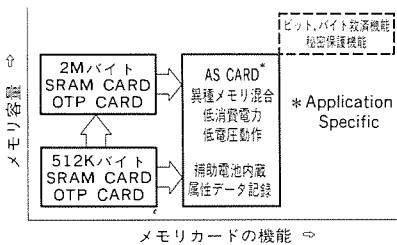

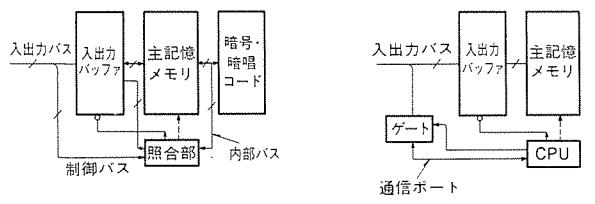

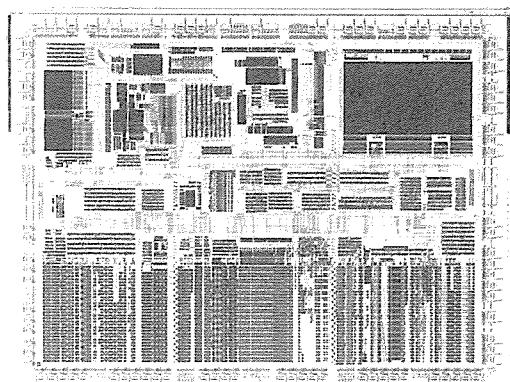

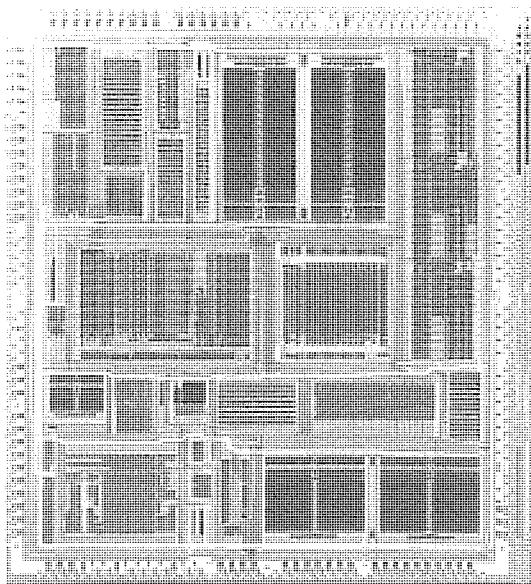

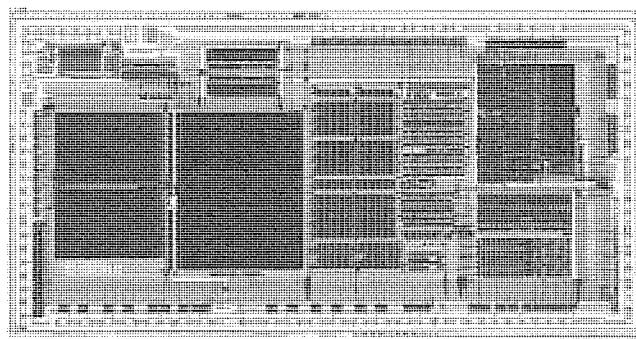

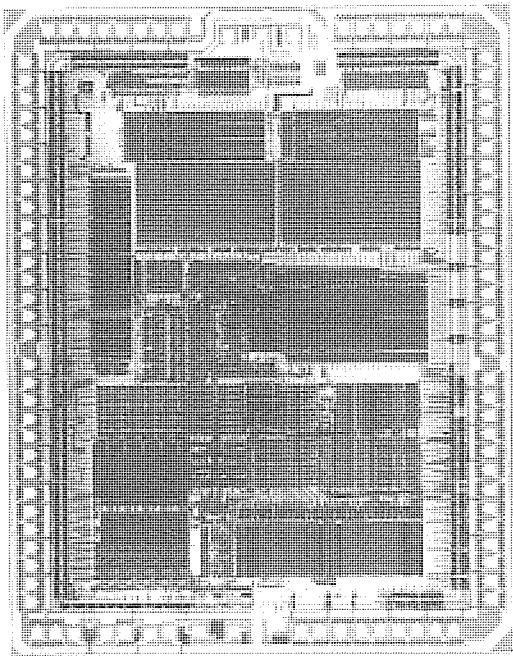

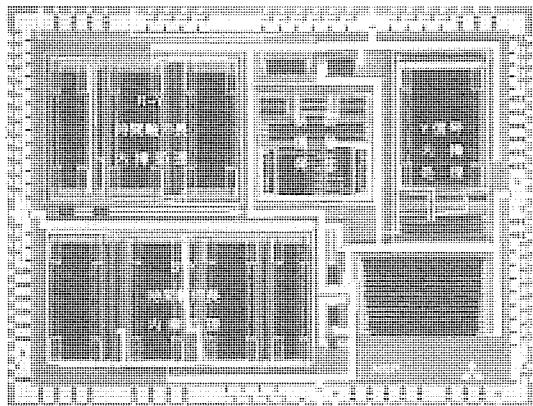

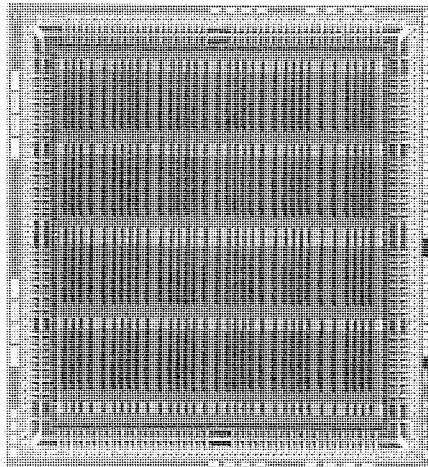

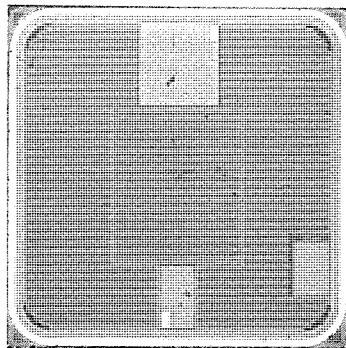

| 三菱大容量メモリカード                         | 49 | G <sub>MIC 80</sub> チップ                                                |      |

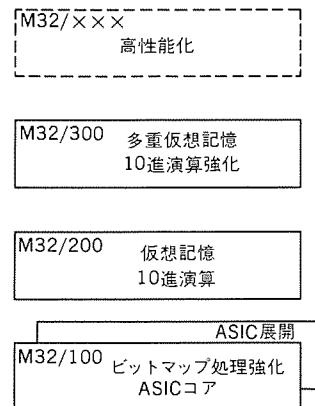

| 木村正俊・井内隆敏・前田 甫                      |    | TRON仕様に基づく32ビットマイクロプロセッサM32/100のチップ写真。                                 |      |

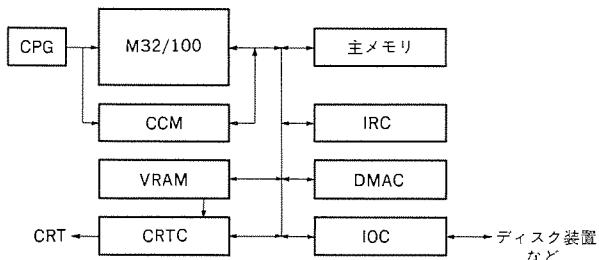

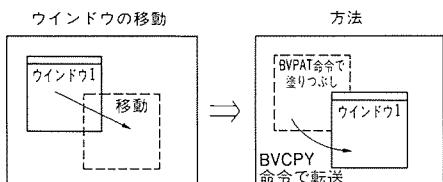

| TRON仕様32ビットマイクロプロセッサM32/100         | 53 | このチップは11.47mm×8.89mmのサイズで、1μmルール2層メタルCMOSプロセス技術を用い、約33万トランジスタが集積されている。 |      |

| 日向純一・吉田豊彦・是松次郎・市山寿雄・富沢 治            |    | (本文53ページ参照)                                                            |      |

| M32用μITRON仕様OS:MR3200と開発環境          | 57 |                                                                        |      |

| 平野浩爾・坪田秀夫・清水 徹・齊藤和則・桶口敬三            |    |                                                                        |      |

| 24ビット、50ns画像／映像処理用                  |    |                                                                        |      |

| シグナルプロセッサ(DISPL)                    | 61 |                                                                        |      |

| 寺根幸季・中川伸一・吉本雅彦・鶴田敏明・篠原尋史・畠中正弘       |    |                                                                        |      |

| 自動車用16ビットワンチップマイコン                  | 66 |                                                                        |      |

| 城田省三・村松菊男・田山俊明・宮田和明・安達忠吉・川崎忠義・井上 功  |    |                                                                        |      |

| DMAコントローラ内蔵                         |    |                                                                        |      |

| 高性能16ビットワンチップマイコン                   | 71 |                                                                        |      |

| 山崎貴志・新村健太郎・清水 康・中村充善・松永毅彦・山内直樹      |    |                                                                        |      |

| MUSE/NTSCコンバータ用LSI                  | 77 |                                                                        |      |

| 岡田圭介・中村雅彦・村上謙二・水谷芳樹・矢澤信春            |    |                                                                        |      |

| 静止画テレビ電話用モデムLSI                     | 82 |                                                                        |      |

| 杉野博之・金子幸司・仁田重之・鈴木 武                 |    |                                                                        |      |

| 高速、低消費電力の1.0μmCMOSゲートアレー            |    |                                                                        |      |

| M60050シリーズ                          | 86 |                                                                        |      |

| 中村博隆・布上裕之・西谷一治・後藤諭利・川端啓二            |    |                                                                        |      |

| 超低雑音HEMT                            | 89 |                                                                        |      |

| 林 一夫・園田琢二                           |    |                                                                        |      |

## アブストラクト

|                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

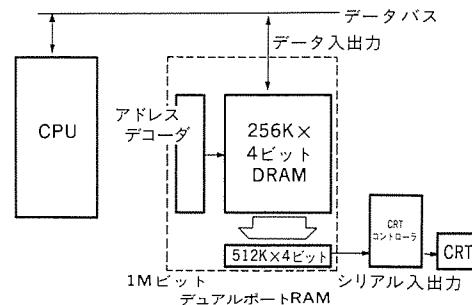

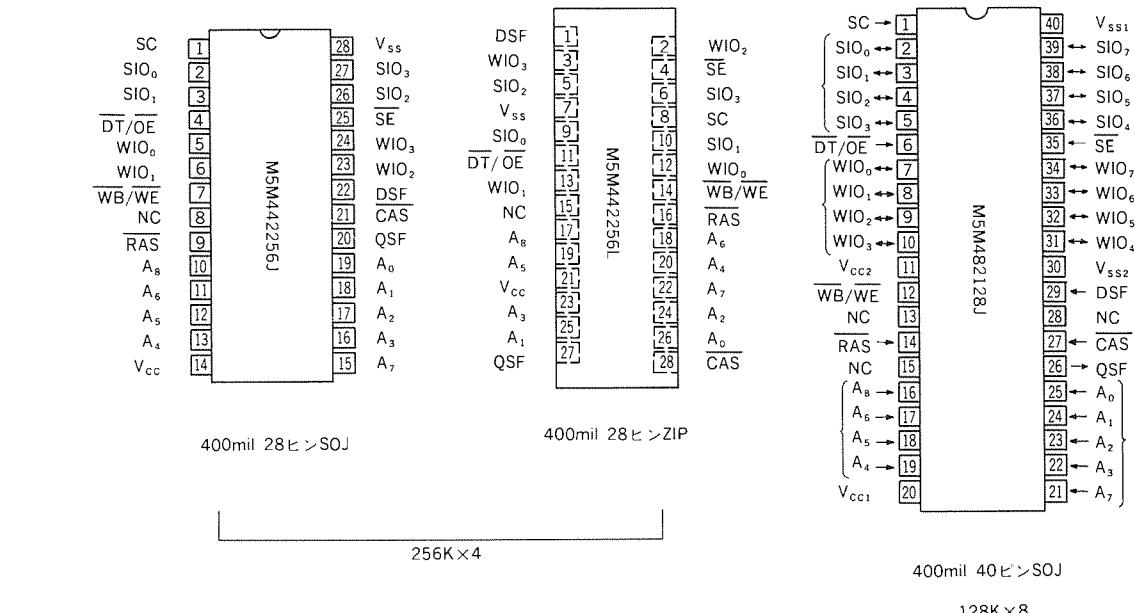

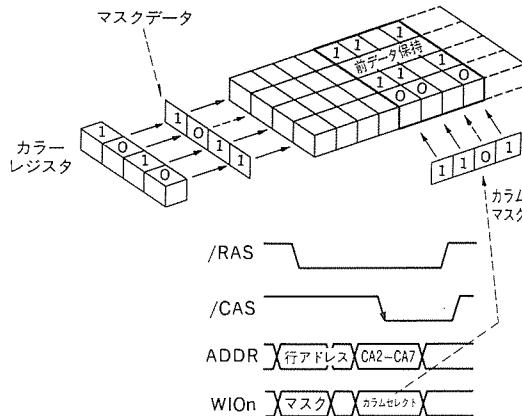

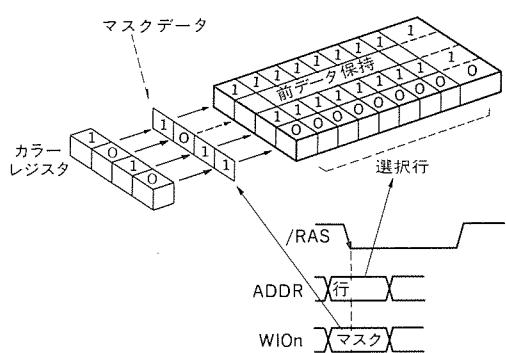

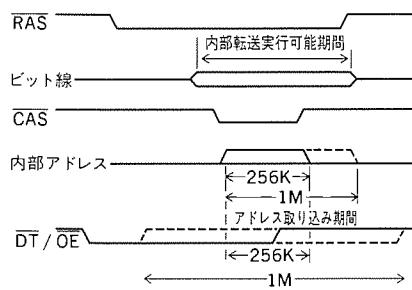

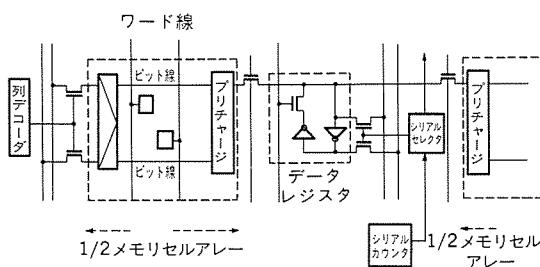

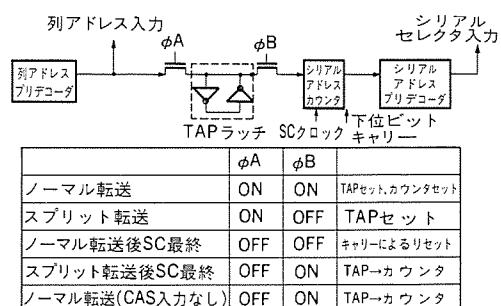

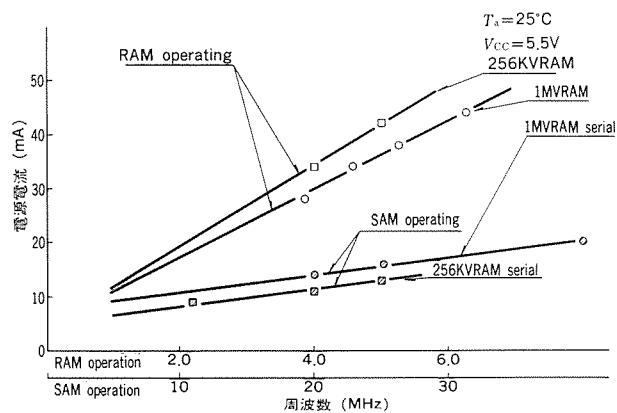

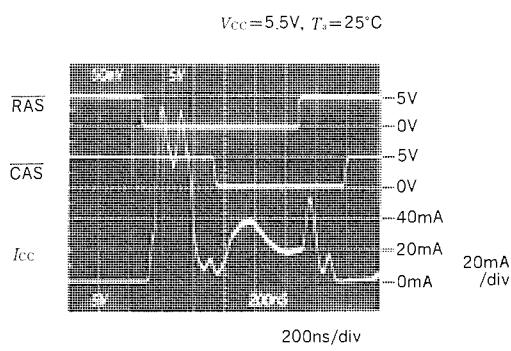

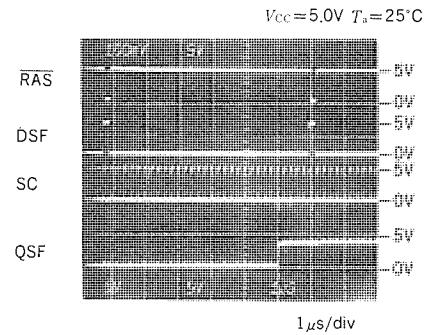

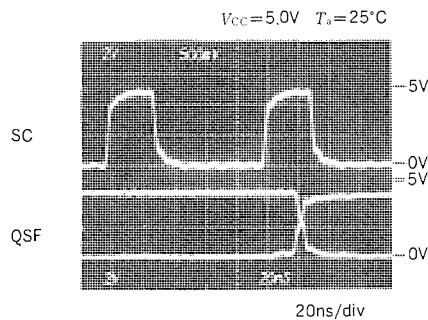

| <p><b>三菱電機半導体技術30年の歩み</b><br/>小宮啓義<br/>三菱電機技報 Vol.63・No.11・P14~16</p> <p>三菱電機の半導体事業は、1960年の半導体工場設立以来、幾多のう(紹)余曲折を経て今日の隆盛を見るに至った。その間の技術の流れと今後の方向を、IC/LSIやパワーモジュールなどのシリコンデバイス、光素子とマイクロ波素子を柱とする化合物半導体製品、ウェーハプロセス技術を中心とした製造技術に関して概観し、さらに本特集号に収録した論文の位置付けを紹介する。</p>                                                            | <p><b>IMビットデュアルポートRAM</b><br/>小川俊行・井上一成・浜野尚徳<br/>三菱電機技報 Vol.63・No.11・P35~38</p> <p>IMビットデュアルポートRAMを開発した。この製品は、従来の256KビットデュアルポートRAMの基本機能に加えて、フラッシュライト、ロックライト、スプリットSAMなどの拡張機能を搭載する。また、データレジスタ回路部を工夫し、低消費電力化と転送タイミングの緩和を実現した。ワード構成は、256Kワード×4ビットと128Kワード×8ビットの2品種を同時に開発し、それぞれ28ピンSOJ、ZIPと40ピンSOJパッケージに封入した。</p>                                                                   |

| <p><b>最先端DRAMプロセス技術</b><br/>佐藤真一・若宮 亘・重富 晃<br/>三菱電機技報 Vol.63・No.11・P17~22</p> <p>0.5μmルールULSIを代表する16M DRAM及び次世代64M DRAMに向けたプロセス技術を開発している。メモリセルには当社独自の完全平担なスタックトキャバシタ構造を採用し、シンプルな構造と安定したプロセスによって大きな蓄積容量が得られた。マスク作成時の電子ブーム描画は、可変形型装置を使用し、特殊な階層構造をもつデータ処理システムを構築することで高スループット化を達成した。これら最先端プロセス技術の現状を紹介する。</p>                | <p><b>ディジタルPPC用5KバイトFIFO/LIFOメモリIC</b><br/>前田安範・沖高毅則・池田俊男・宮田和明・服部正人・鎌倉 寛<br/>三菱電機技報 Vol.63・No.11・P39~44</p> <p>ディジタルPPC(Plain Paper Copier)の画像処理に最適な機能を持つ5KバイトFIFO(First In First Out)/LIFO(Last In First Out)メモリIC M66250P/FPを開発した。画像処理に適した5120ワード×8ビットのメモリ容量、書き込みと読み出しが非同期にできるFIFO/LIFO機能、任意のアドレスからデータを読み出せる先頭アドレス指定機能を内蔵し、さらに高速アクセスを実現した。ここでは、これらの機能概要、電気的特性などについて報告する。</p> |

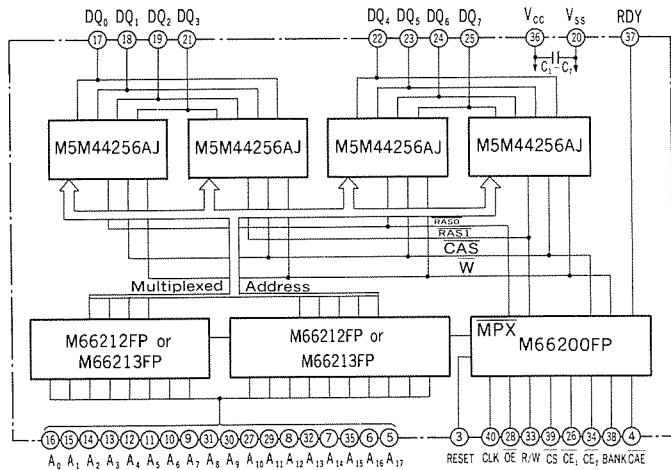

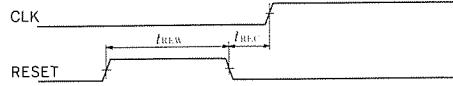

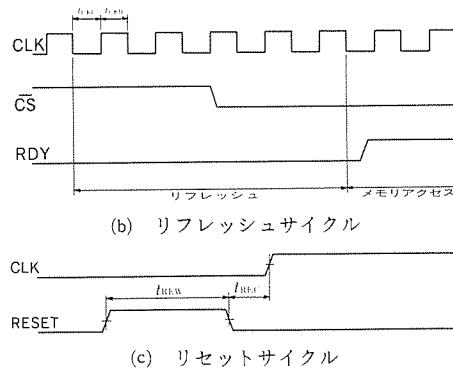

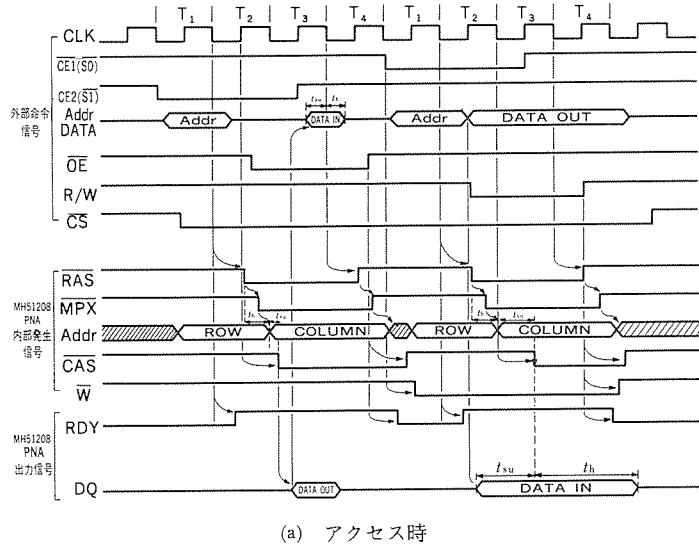

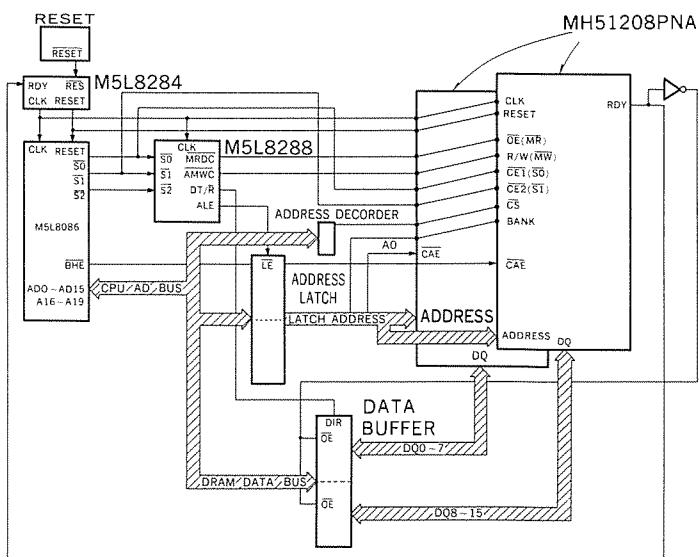

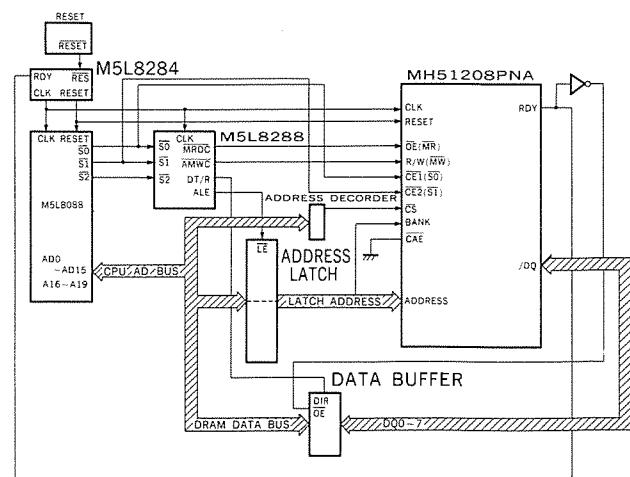

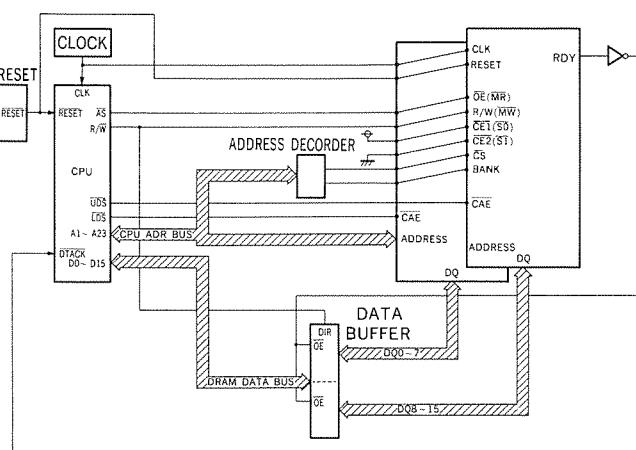

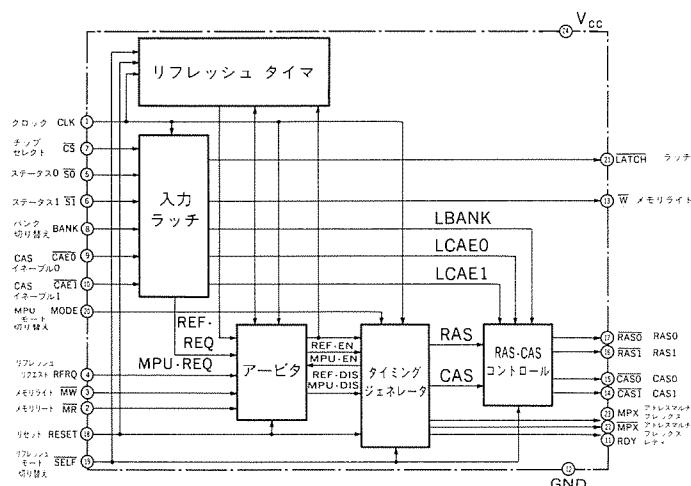

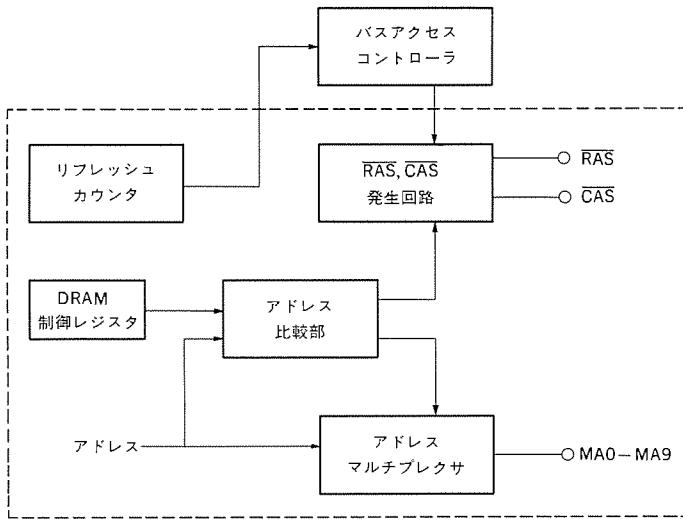

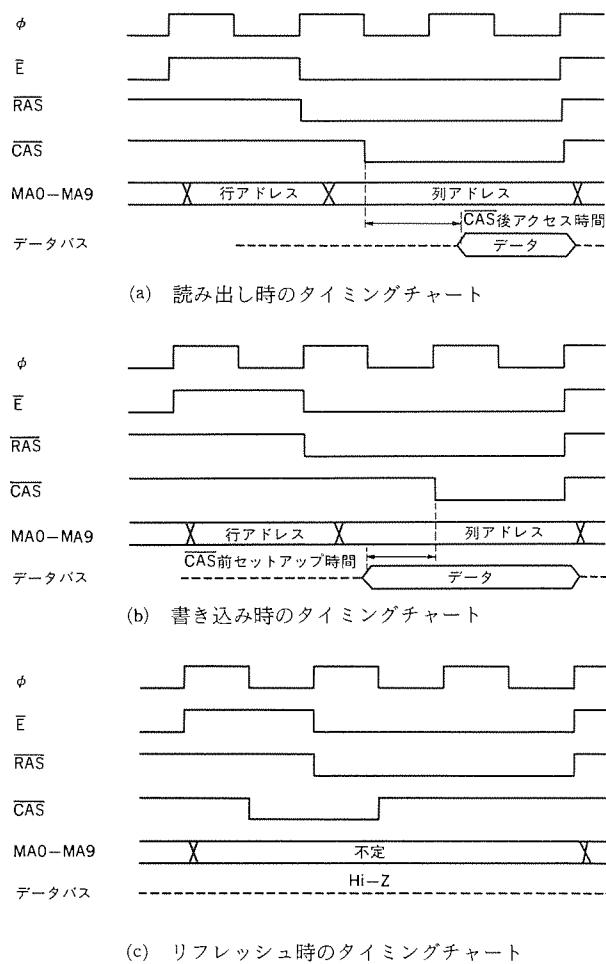

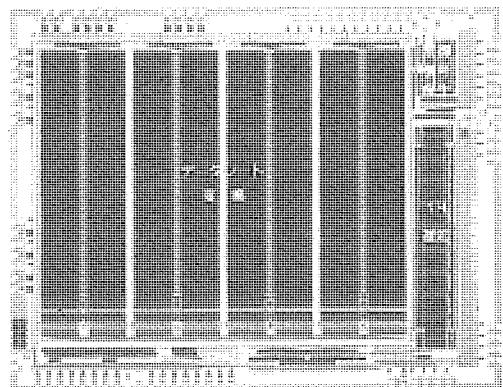

| <p><b>4MビットダイナミックRAM</b><br/>宮本博司・長友正男・山田通裕・長山安治・水津克巳<br/>三菱電機技報 Vol.63・No.11・P23~26</p> <p>0.8μmツインウェルCMOSプロセス技術とスタックトキャバシタメモリセルを採用して4M DRAMを開発した。8ビット並列テストモードによりテスト時間が短縮できる。4M×1構成と1M×4構成をAIマスクで選択する。高速ページ、ニブル、スタティックコラムモード及びライトバーピット機能をワイヤボンディングで選択する。チップサイズは6.84mm×14.95mmで、350ミルSOJ及び400ミルZIPに収納する。</p>             | <p><b>4MビットP<sup>2</sup>SRAMモジュールの開発と応用</b><br/>田原次夫・小杉龍一・谷口正治・辻 哲郎・戸田 均<br/>三菱電機技報 Vol.63・No.11・P45~48</p> <p>汎用8及び16ビットマイクロプロセッサに接続容易な4Mビット擬似SRAMモジュールを開発した。このためにDRAMコントローラをASSPとしてワンチップ化し、標準1M DRAM 4個と高密度実装した。このモジュールは、小形、リフレッシュ回路内蔵、耐ノイズ性の特長があり、電源は5V単一・TTLレベル入力・各種信号のタイミング自動処理など使い易い設計で、現時点で4M SRAMを用いたシステム設計が可能である。</p>                                                 |

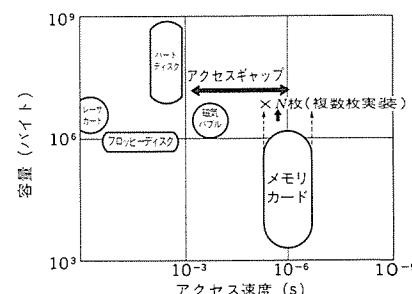

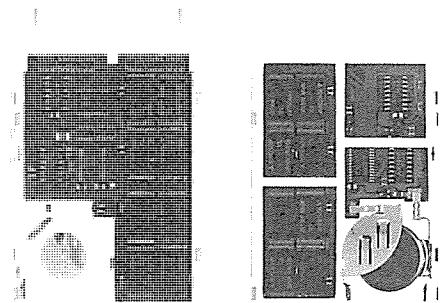

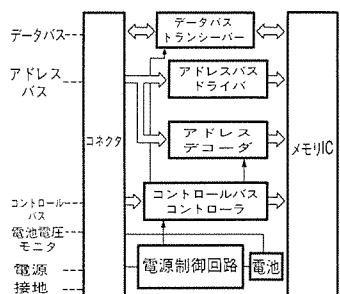

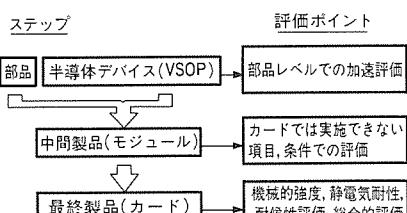

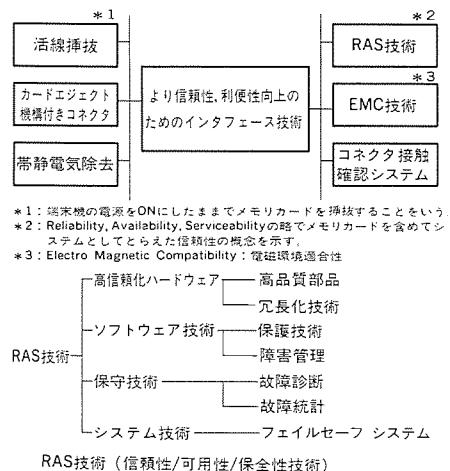

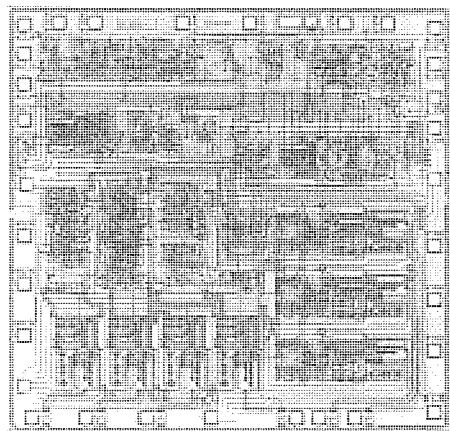

| <p><b>高速1MビットCMOSスタティックRAM</b><br/>菅野雅直・和田知久・杠 幸二郎・向井孝夫・河野芳雄<br/>三菱電機技報 Vol.63・No.11・P27~30</p> <p>最大アクセスタイム35nsの高速1MビットCMOSスタティックRAMを開発した。設計面では、変形分割ワード線選択方式を用いてワード線での遅延時間を抑えていること、1M語×1ビット構成にテスト時間短縮のためのビット構成可変機能を備えていることが特長である。プロセス面では、多層配線技術などを駆使して、0.7μm設計ルールの3層ボリシリコン2層アルミ構造のデバイスを実現している。</p>                      | <p><b>三菱大容量メモリカード</b><br/>木村正俊・井内隆敏・前田 甫<br/>三菱電機技報 Vol.63・No.11・P49~52</p> <p>最先端の超小型・薄形パッケージ技術と高密度実装技術を結集し、大容量のメモリカードを開発、量産化した。メモリカードは、従来の低速外部記憶装置に比較して、アクセススピード・低消費電力・可搬性に優れる。電子機器の小型・薄形化・パーソナル指向と利用面でのソフト、アプリケーションソフトの充実等により、既に多岐にわたる機器に利用され、本格的実用期を迎えたといえる。</p>                                                                                                           |

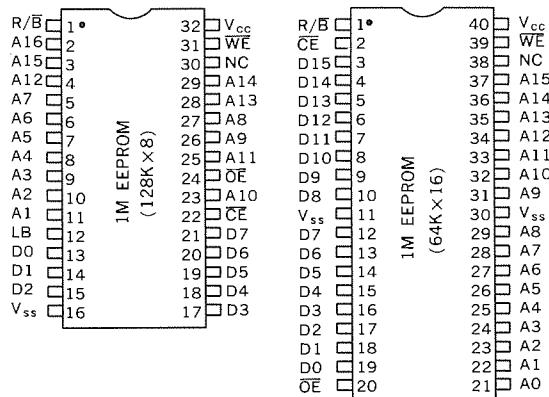

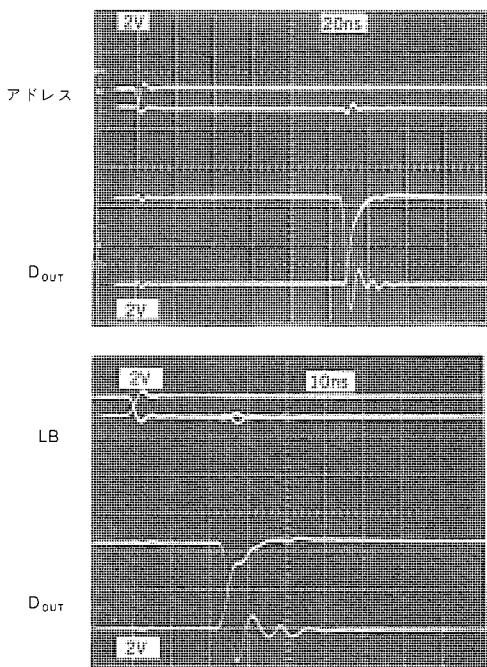

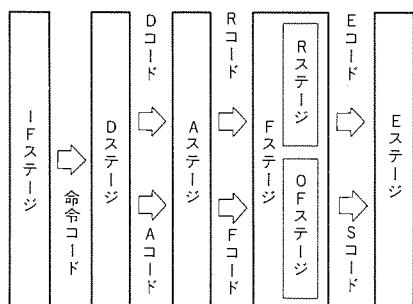

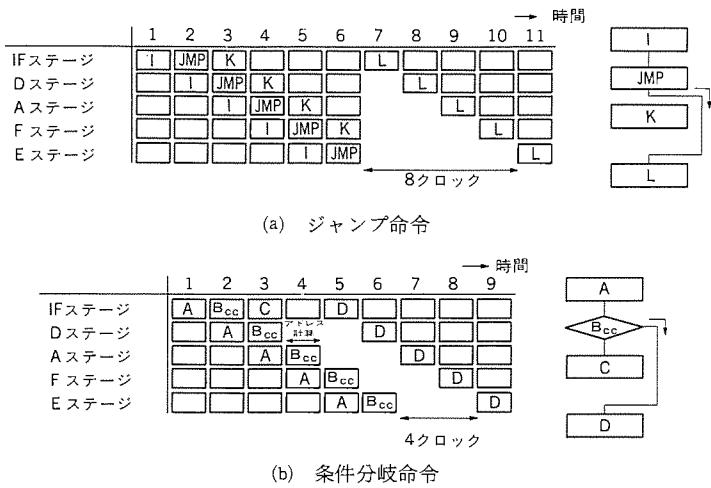

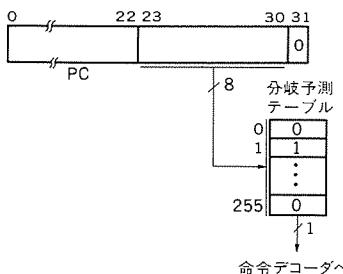

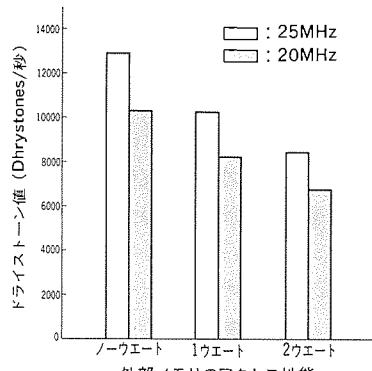

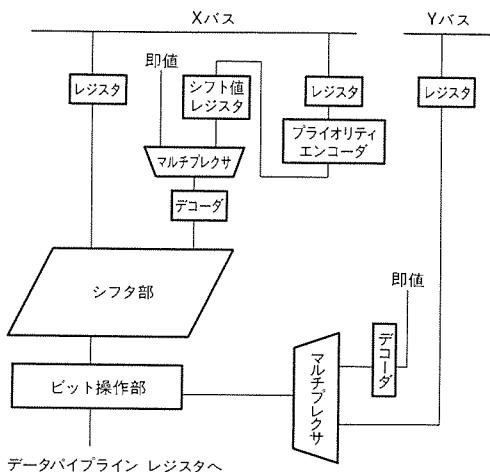

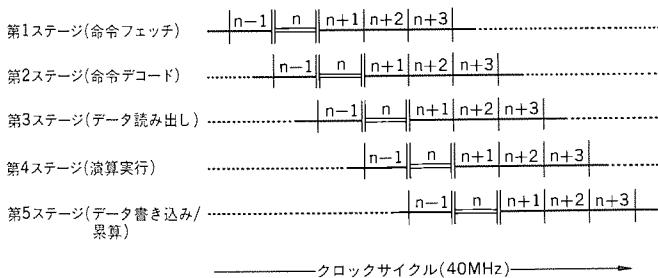

| <p><b>5V単一電源で動作する高速1MビットEEPROM</b><br/>寺田 康・有馬秀明・小林和男・味香夏男<br/>三菱電機技報 Vol.63・No.11・P31~34</p> <p>1μmツインウェルCMOS 3層ボリシリコン2層アルミプロセスを用いて5V単一電源で動作する1MビットEEPROMを試作した。チップサイズは11.83mm×7.73mm、セルサイズは3.8μm×8.0μmである。3層ボリシリコン型メモリセルと、非選択のメモリアレイでリファレンスレベルを生成する差動型センスアンプの開発により、120nsの高速アクセスを実現した。また、ECC回路を内蔵することにより高い信頼性を持っている。</p> | <p><b>TRON仕様32ビットマイクロプロセッサM32/100</b><br/>日向純一・吉田豊彦・是松次郎・市山寿雄・富沢 治<br/>三菱電機技報 Vol.63・No.11・P53~56</p> <p>機器組み込みコントローラや小型ワークステーションへの応用に適するTRON仕様32ビットマイクロプロセッサM32/100を開発した。1μmCMOS技術を用いて約33万トランジスタをコンパクトなチップサイズに集積し、ASIC展開のCPUコアとして利用可能である。5段のパイプライン、先行シャンパン処理機構を採用して高性能を実現した。また、リアルタイムOSを効率的に実行する高機能命令を持っている。</p>                                                              |

# Abstracts

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 35 ~ 38 (1989)

## A 1M-Bit Dual-Port RAM

by Toshiyuki Ogawa, Kazunari Inoue & Hisanori Hamano

In addition to the functions of its 56K-bit predecessor, this new product offers flash write, block write, and split serial access memory functions. The data-register circuitry has been improved to realize lower power consumption and relaxed inversion timing. Two products are available with word configurations of 256K words × 4 bits and 128K words × 8 bits. Both are supplied in 23-pin SOJ, 23-pin ZIP, and 40-pin SOJ packages.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 14 ~ 16 (1989)

## Mitsubishi Electric Semiconductor Technologies: The Last Thirty Years and the Current Status

by Hiroyoshi Komiya

Since the founding of its first semiconductor plant in 1960, Mitsubishi Electric has achieved many successes in this field. The article surveys technical trends and future directions of the Corporation's products including silicon devices such as ICs, LSIs, and power modules, and GaAs devices such as optoelectronic and microwave devices. The article also provides an orientation for the other articles of this special issue.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 39 ~ 44 (1989)

## A 5KB FIFO/LIFO Memory IC for Digital PPCs

by Yasunori Maeda, Takenori Okitaka, Toshio Ikeda, Kazuaki Miyata, Masato Hattori & Yutaka Kamakura

The M66250P/FP FIFO/LIFO (first-in-first-out and last-in-first-out) memory IC is optimized for image processing by plain-paper copiers. The 5,120 word × 8 bit memory architecture implements FIFO and LIFO functions for asynchronous write and read, an address head specifier that allows readout from an arbitrary address, and high-speed access. The article introduces these functions and reports on the electrical characteristics of the product.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 17 ~ 22 (1989)

## Advanced DRAM Process Technologies

by Shin'ichi Sato, Wataru Wakamiya & Akira Shigetomi

Mitsubishi Electric is developing process technology for ULSI devices such as 16M- and 64M-bit DRAMs employing a 0.5μm channel width. The memory cells will employ proprietary Mitsubishi technology—completely flat stacked-capacitor structures. This simple structure provides a high charge capacity and the DRAMs may be mass-produced with uniform results. The electron-beam writing during mask production employs a variable-shape system and a data-processing system with a special layered structure for high throughput. The article introduces these leading-edge technologies.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 45 ~ 48 (1989)

## A 4M-Bit Pseudo-Pseudo SRAM Module

by Tsugio Tabaru, Ryuichi Kosugi, Masaharu Taniguchi, Tetsuro Tsuji & Hitoshi Toda

This module is easily linked to general-purpose 8- and 16-bit microprocessors. The DRAM controller is implemented as a single-chip application-specific standard product and is housed with four 1M-bit DRAMs to form a single high-density compact module. Designed for easy use, the module features a built-in refresh circuit, high noise resistance, a single 5V power supply, TTL-level inputs, and automatic signal-timing control. The module may be used in 4M-bit SRAM system applications.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 23 ~ 26 (1989)

## A 4M-Bit Dynamic RAM

by Hiroshi Miyamoto, Masao Nagatomo, Michihiro Yamada, Yasuji Nagayama & Katsumi Suizu

The article reports on the development of a 4M-bit DRAM employing a 0.8μm twin-well CMOS process and a stacked-capacitor memory cell. A test mode with 8-bit parallel access is implemented to reduce testing time. The A1 mask selects either a 4M × 1 or 1M × 4-bit architecture. Fast-page mode, nibble mode, static-column mode, and write-per-bit functions are selected at wire bonding. The chip size is 6.84 × 14.95mm<sup>2</sup>. The chip is housed in either a 350mil SOJ or 400mil ZIP.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 49 ~ 52 (1989)

## MELCARDS: High-Density Transportable Memory-Card Subsystems

by Masatoshi Kimura, Takatoshi Iuchi & Hajime Maeda

MELCARDS employ the latest technologies for thin ultracompact packaging and high-density mounting. The high access speed, low power consumption, and portability of these cards make them a vast improvement over conventional auxiliary storage devices employing magnetic media. The cards help make electronic equipment smaller, thinner, and easier to carry. They function with a broad range of applicable software and are entering widespread use.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 27 ~ 30 (1989)

## A Fast 1M-Bit CMOS Static RAM

by Masanao Eino, Tomohisa Wada, Kojiro Yuzuriha, Takao Mukai & Yoshio Kono

This SRAM offers a maximum access time of 35ns. It features a modified divided-word-line structure that reduces delay time, and a variable-bit organization that reduces the test time below the requirement for a 1M × 1-bit structure. Multilayer process technology is used to realize the three-layer polysilicon two-layer aluminum CMOS device with a 0.7μm channel width.

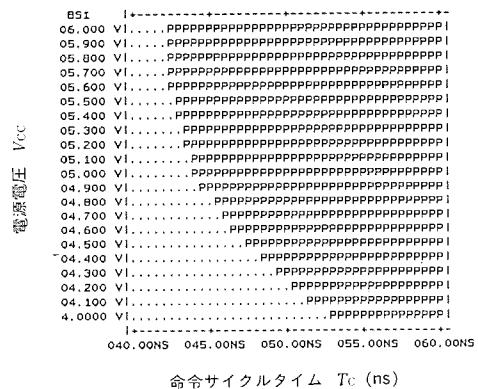

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 53 ~ 56 (1989)

## The MEL32/100: 32-Bit Microprocessors Based on the TRON Architecture

by Jun'ichi Hinata, Toyohiko Yoshida, Jiro Korematsu, Toshio Ichiyama & Osamu Tomisawa

Designed for applications in embedded-equipment controllers and compact workstations, these microprocessors integrate approximately 330,000 transistors on a compact chip in a 1μm CMOS process and are designed to be utilized as a CPU core for ASIC development. They realize high performance through use of a five-level pipeline. The microprocessors also feature a sophisticated instruction set designed to support real-time operating systems.

Mitsubishi Denki Gihō: Vol. 63, No. 10, pp. 31 ~ 34 (1989)

## A 120ns 1M-Bit Full-Featured EEPROM

by Yasushi Terada, Hideaki Arima, Kazuo Kobayashi & Natsuo Ajika

A three-layer polysilicon two-layer aluminum CMOS twin-well process with a 1μm channel width was used to trial produce a 1M-bit EEPROM that operates from a single 5V power supply. The chip size is 11.83 × 7.73mm and the cell size 3.8 × 8.0μm. The three-layer polysilicon memory cell and a newly developed differential sense amplifier that generates a reference level at nonselected memory arrays realize a high-speed access of 120ns. An error checking and correction circuit has been integrated for improved reliability.

## アブストラクト

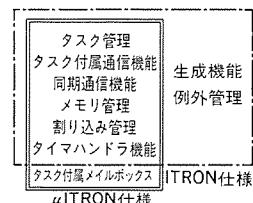

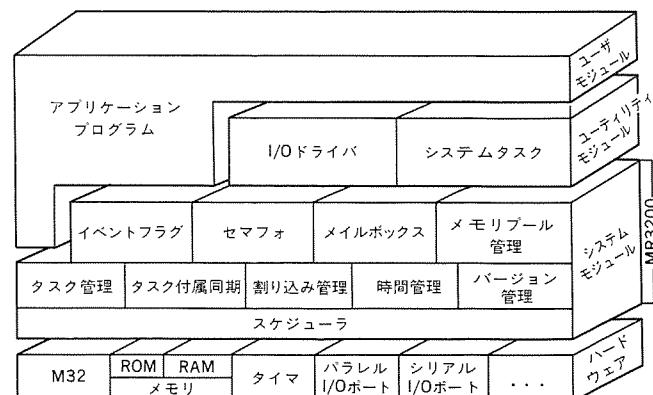

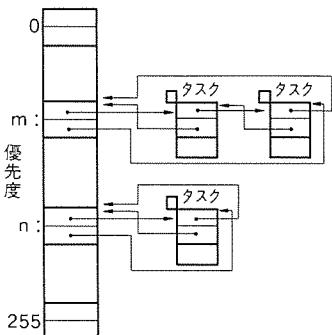

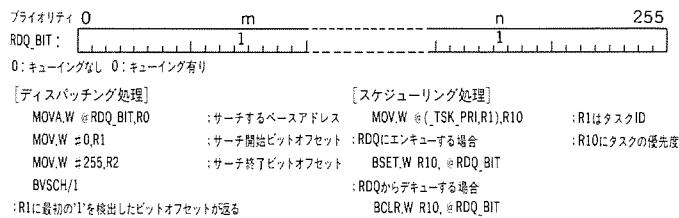

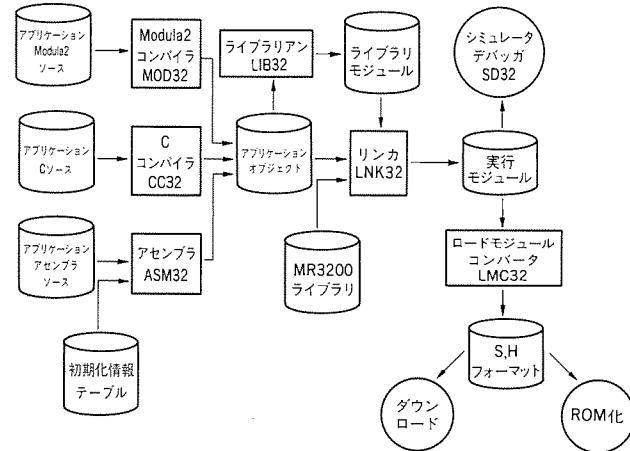

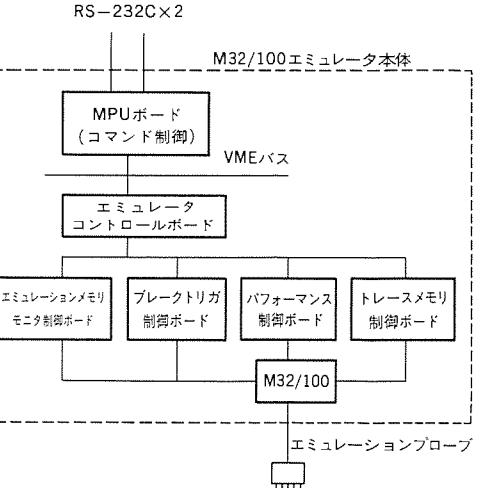

### M32用μITRON仕様OS：MR3200と開発環境

平野浩爾・坪田秀夫・清水 徹・斎藤和則・樋口敬三

三菱電機技報 Vol.63・No.11・P57～60

TRON仕様32ビットマイクロプロセッサM32シリーズ用リアルタイムOSとして、機器組み込み型制御をターゲットとするμITRON仕様に準拠した“MR3200”を開発した。

さらに、リアルタイムOS上のアプリケーションの開発において、“M32／100”を搭載したシステムをリアルタイムの環境の下でデバッグ可能なハードウェアエミュレータも同時に開発した。

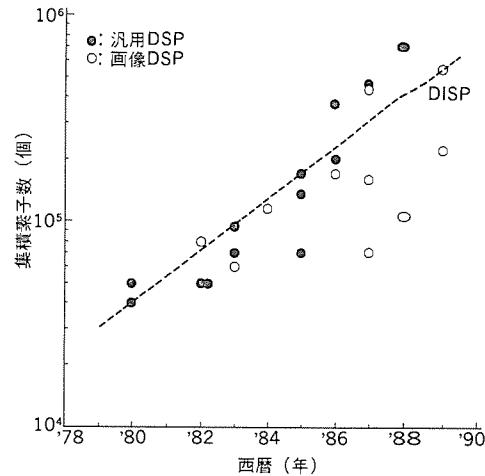

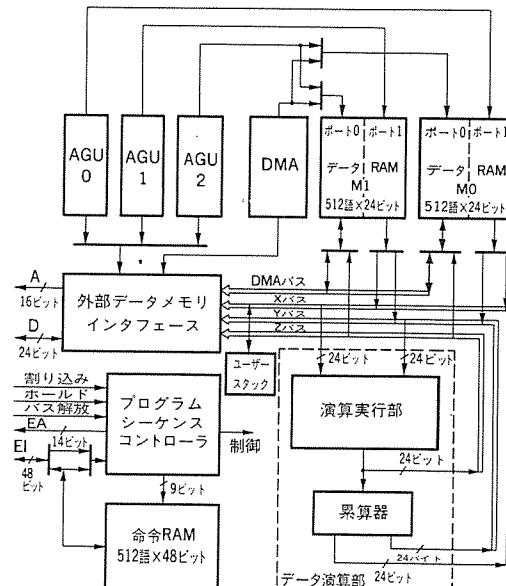

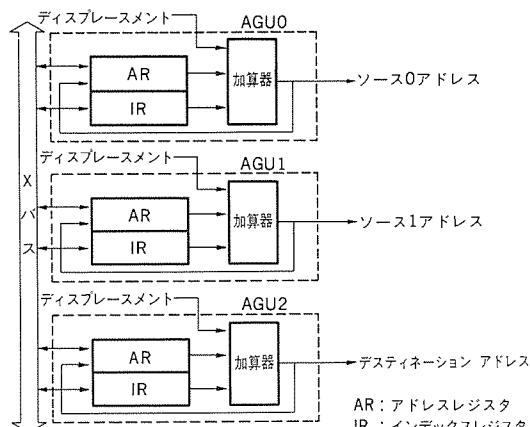

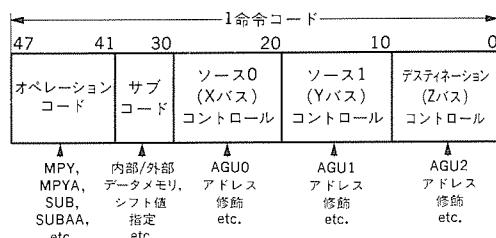

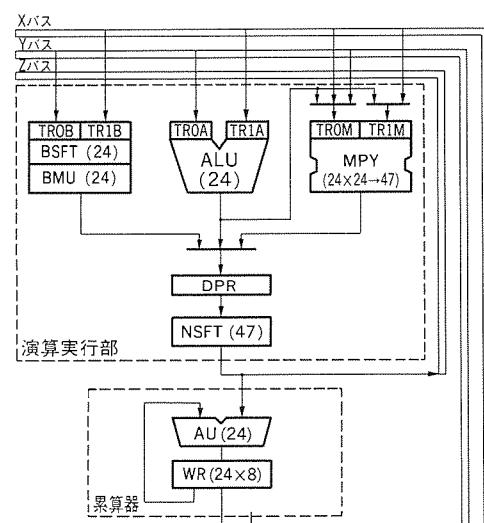

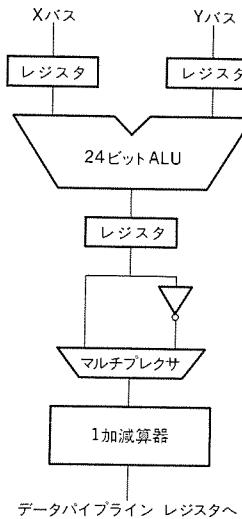

### 24ビット、50ns画像／映像処理用シグナルプロセッサ (DISP)

寺根秀幸・中川伸一・吉本雅彦・嶋田敏明・篠原尋史・畠中正弘

三菱電機技報 Vol.63・No.11・P61～65

1 μm 2層AlCMOSプロセス技術を用いて538kTrを集積した24ビット固定小数点方式、最大命令サイクル時間50nsの画像／映像信号処理プロセッサDISPを開発した。信号処理機能の並列度を強化し、画像処理向きのデータ演算・制御部を内蔵することにより実時間処理性能を向上させた。また、大容量命令RAM、データRAM、各種制御機能をワンチップに集積した。DISPは、高精度、高速な画像／映像信号処理分野において幅広く利用できる。

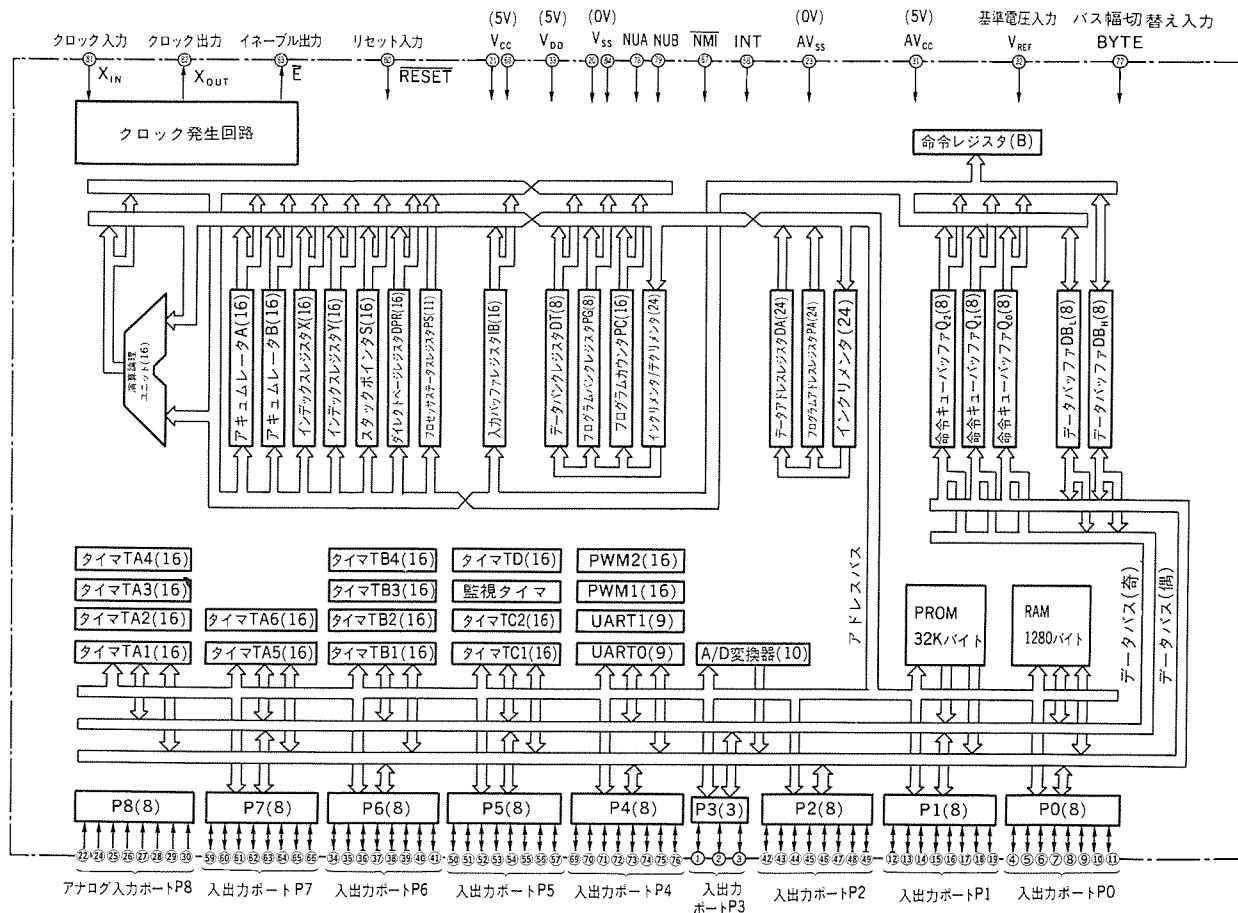

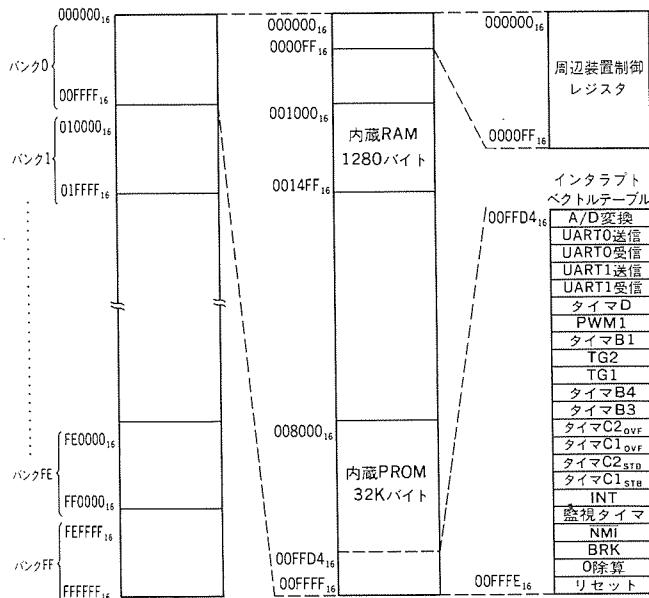

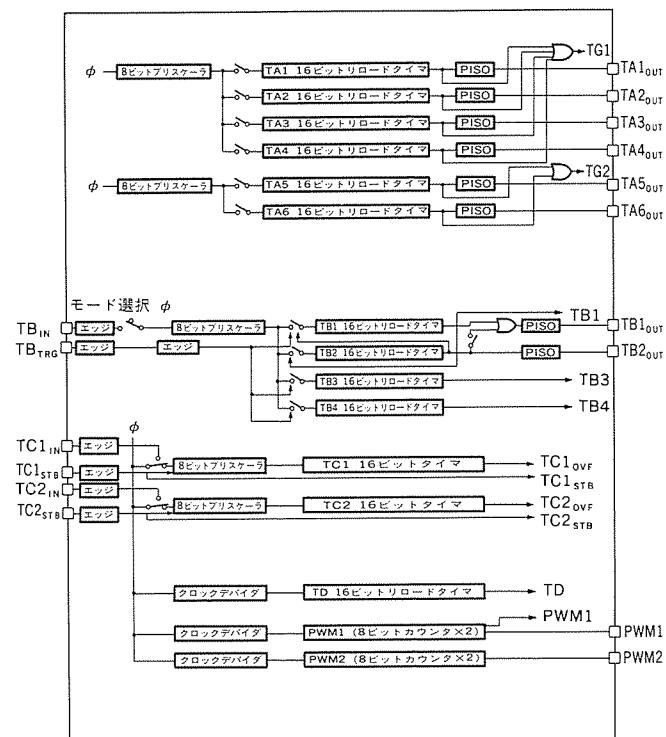

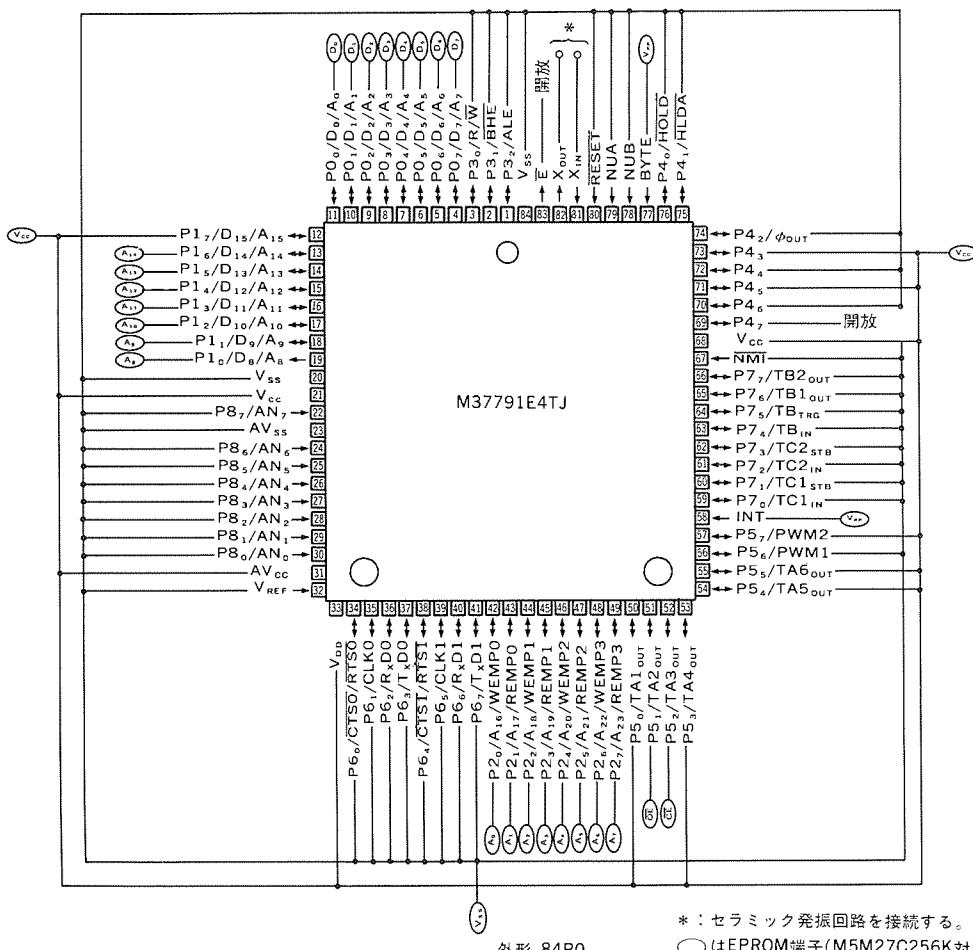

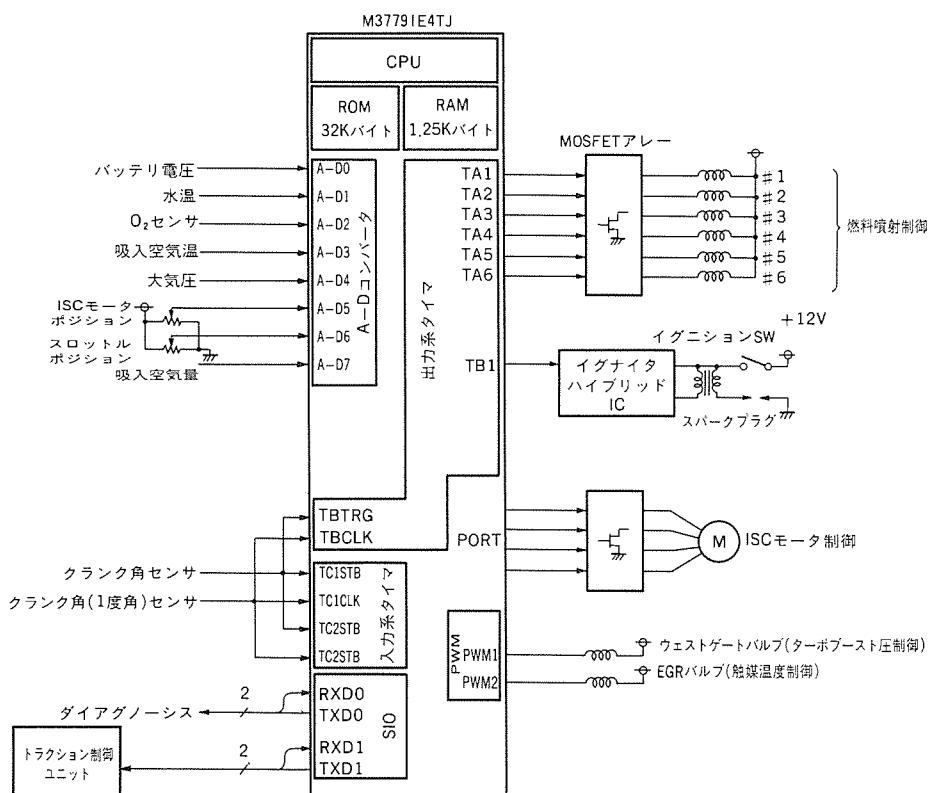

### 自動車用16ビットワンチップマイコン

城田省三・村松菊男・田山俊明・宮田和明・安達忠吉ほか

三菱電機技報 Vol.63・No.11・P66～70

オリジナル16ビットマイコンシリーズ《MELPS7700》のファミリーとして自動車エンジン制御用マイコンM37790STJを既に開発・量産化しているが、これに続く第二弾として大容量メモリ内蔵型のワンチップマイコンM37791E4 TJを開発した。最先端の高信頼度プロセスを採用し、32KバイトワンタイムPROM、1.25KバイトRAM、16ビットタイマ、10ビットA/D変換器、UARTなどをワンチップに内蔵している。

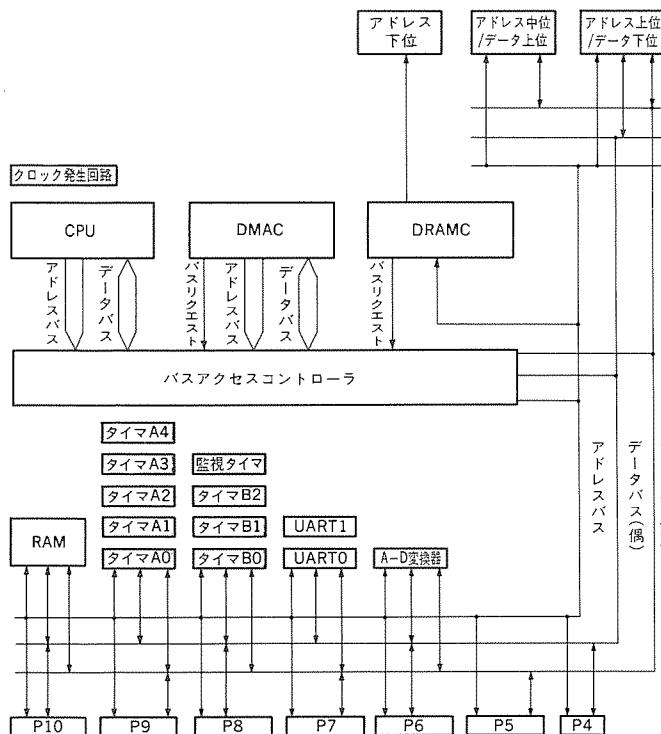

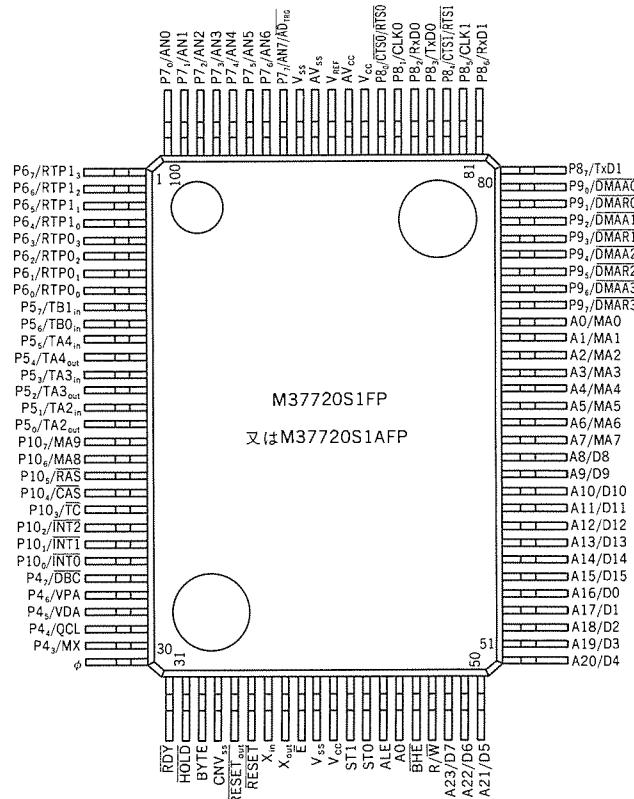

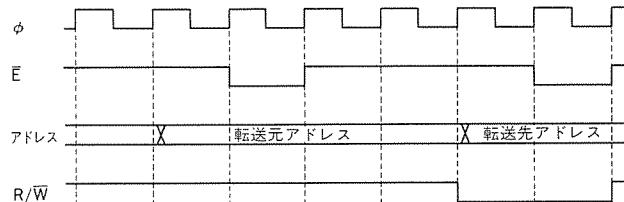

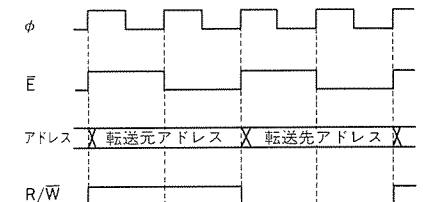

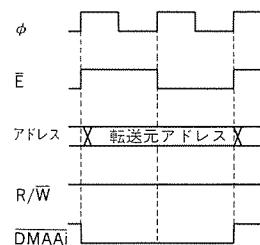

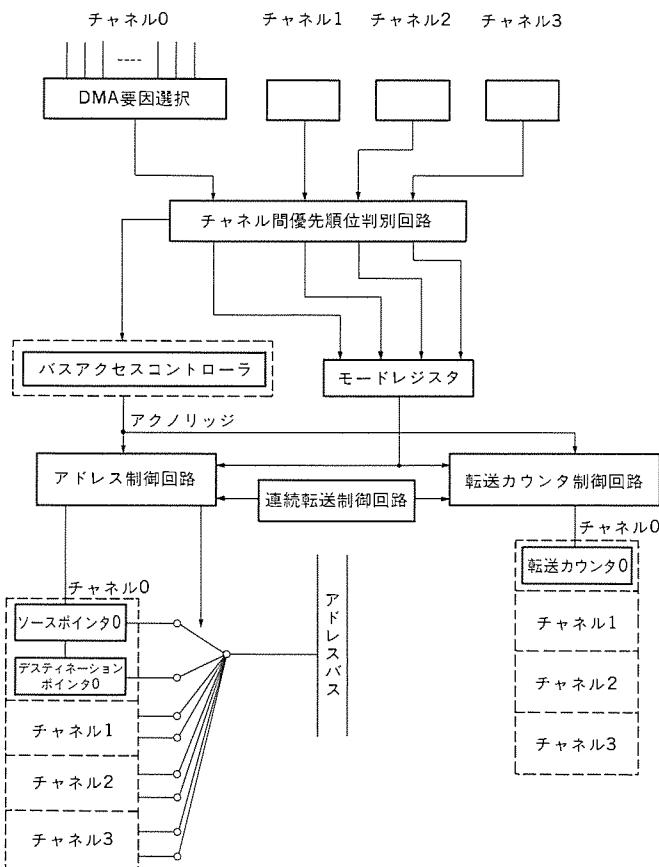

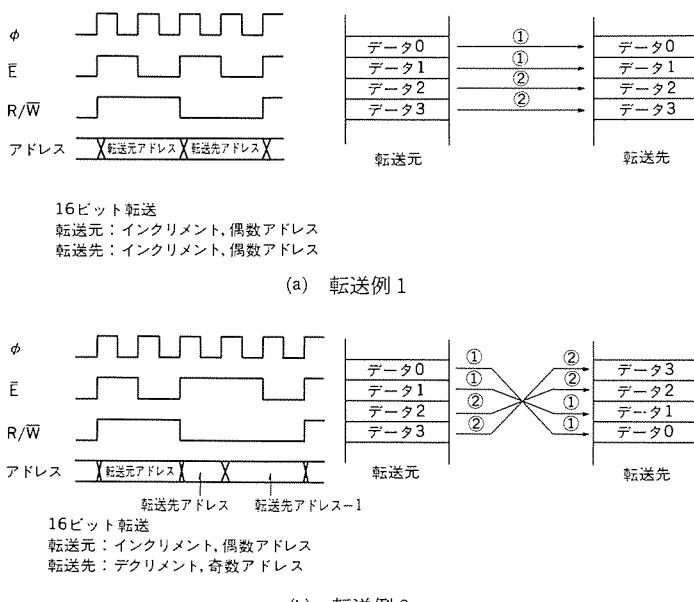

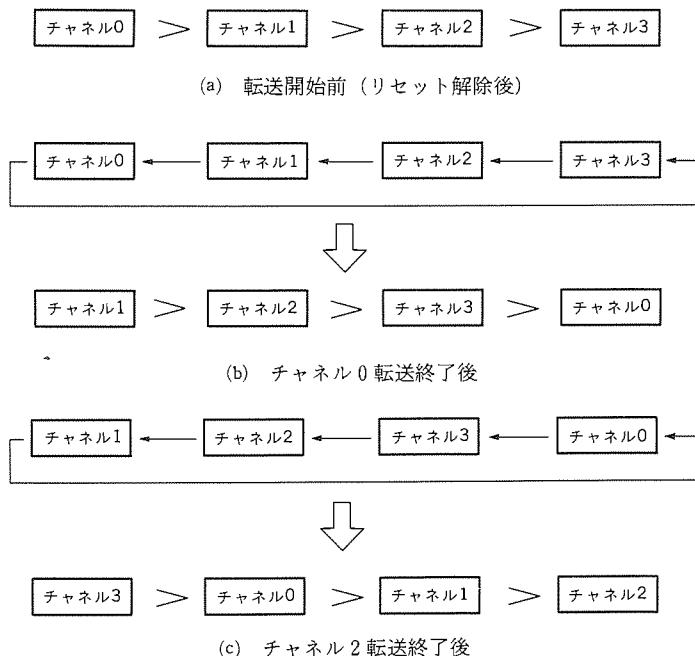

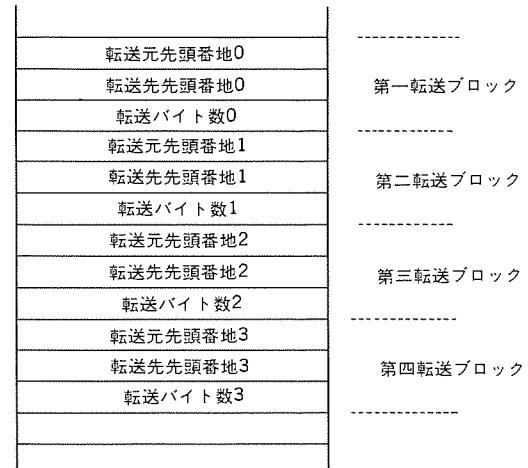

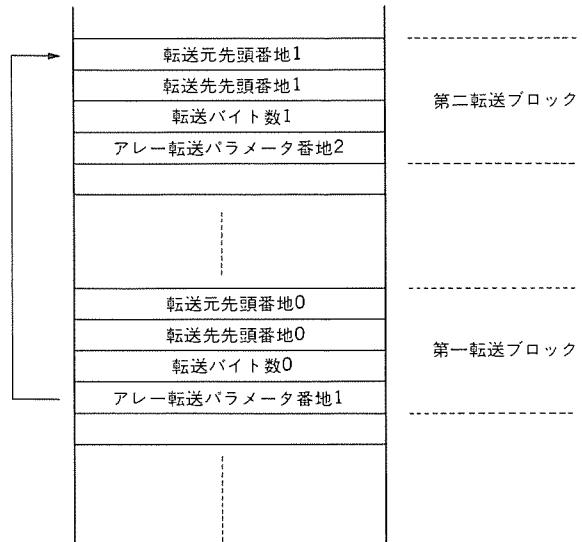

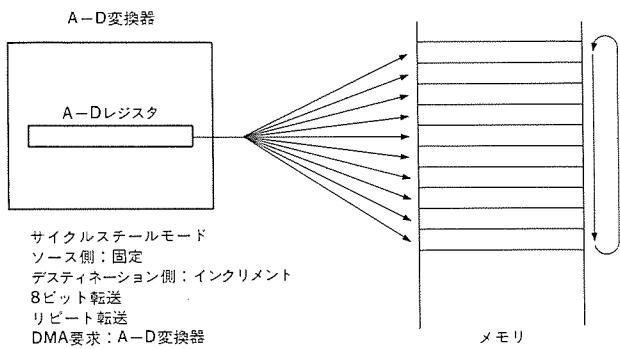

### DMAコントローラ内蔵高性能16ビットワンチップマイコン

山崎貴志・新村健太郎・清水 康・中村充善・松永毅彦・山内直樹

三菱電機技報 Vol.63・No.11・P71～76

OA・産業用機器制御に適した高速・高性能16ビットワンチップマイコン《MELPS7700》のファミリーの一員として、高速に大量のデータを転送するDMAコントローラや大容量のDRAMを直接制御できるDRAMコントローラなどの新しい機能を内蔵したM37720S1 FP/S1 AFP(高速版)を開発した。

本稿では、本製品について紹介するとともに、これらの新機能の概要、特徴などについて述べる。

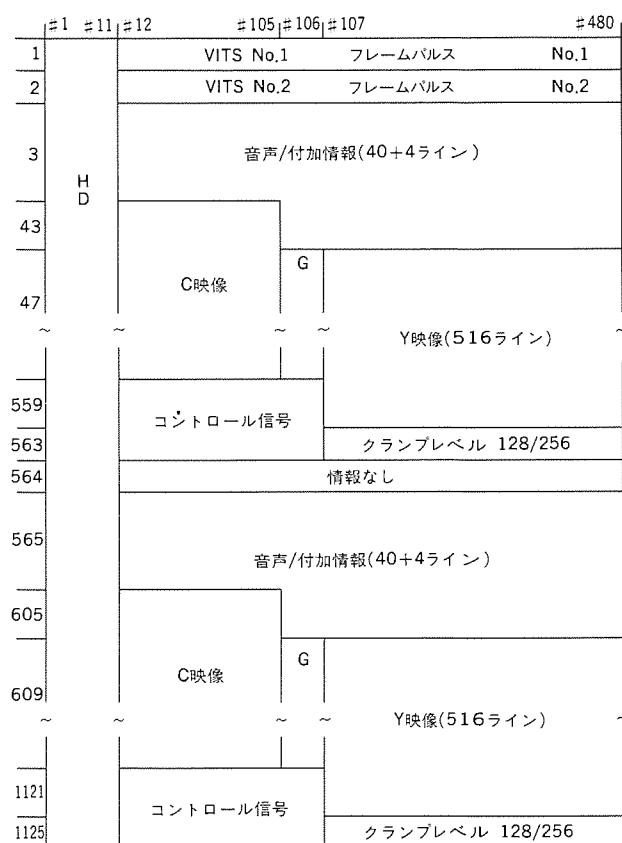

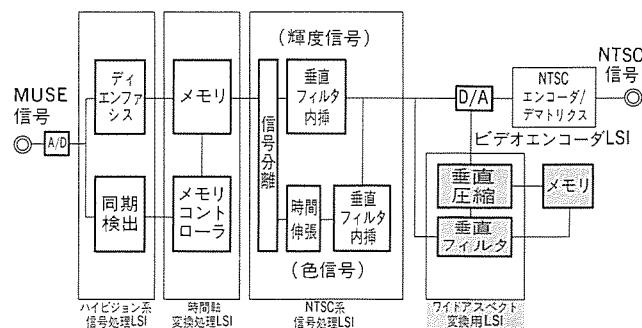

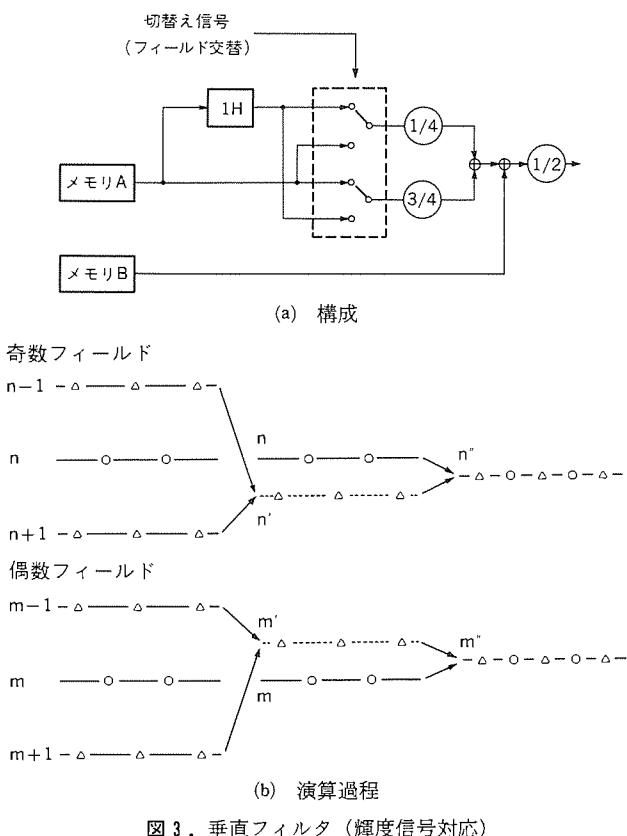

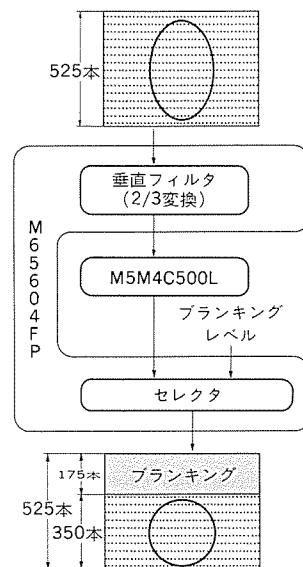

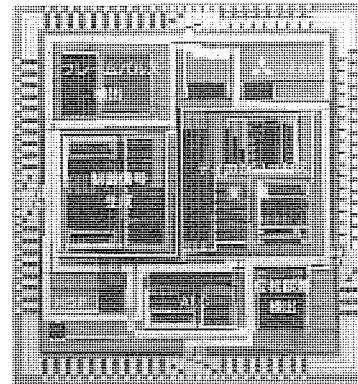

### MUSE／NTSCコンバータ用LSI

岡田圭介・中村雅彦・村上謙二・水谷芳樹・矢澤信春

三菱電機技報 Vol.63・No.11・P77～81

MUSE方式によるハイビジョン衛星放送は、方式が異なるため現行のNTSC方式受像機で受信することはできない。NTSC方式受像機で受信するには、MUSE信号をNTSC信号に変換することが必要である。この方式変換に必要な映像信号処理部のLSI化と方式変換器(MUSE／NTSCコンバータ)の開発を行った。

本稿では、開発した方式変換器のシステムとLSIの機能と構成について述べる。

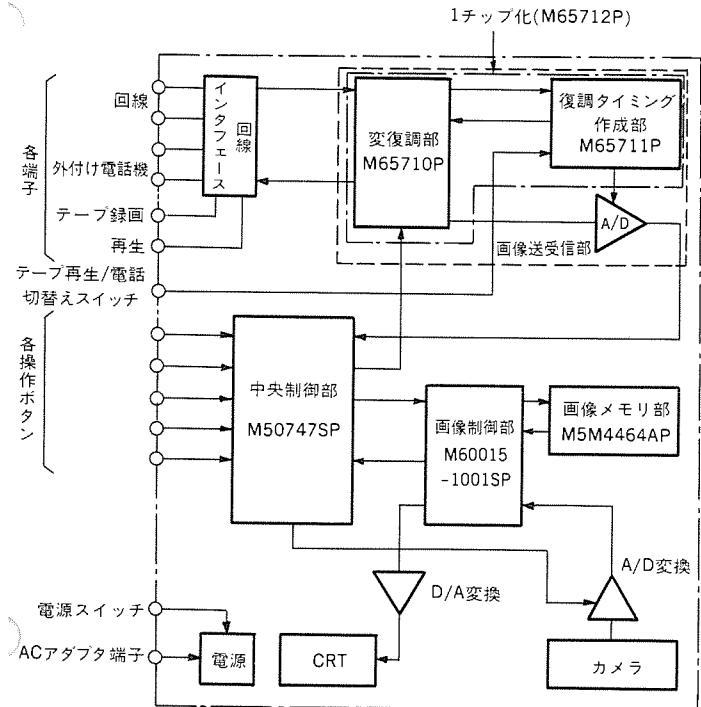

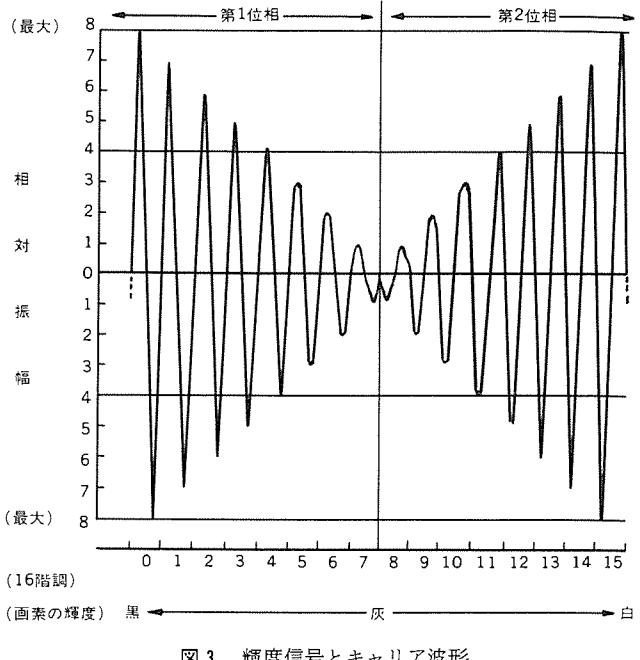

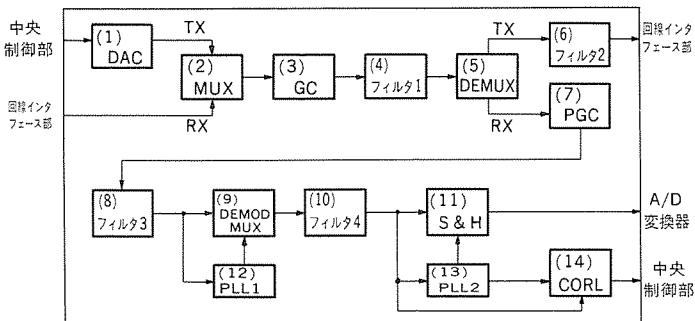

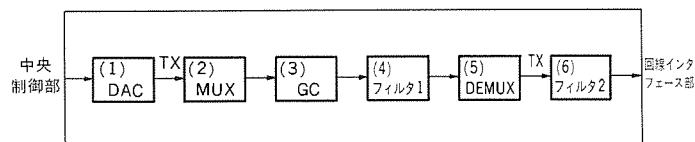

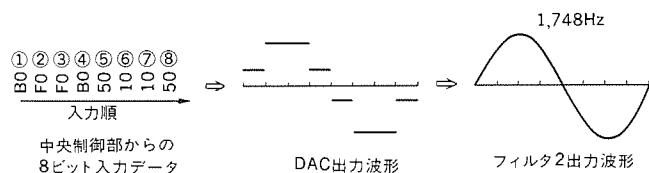

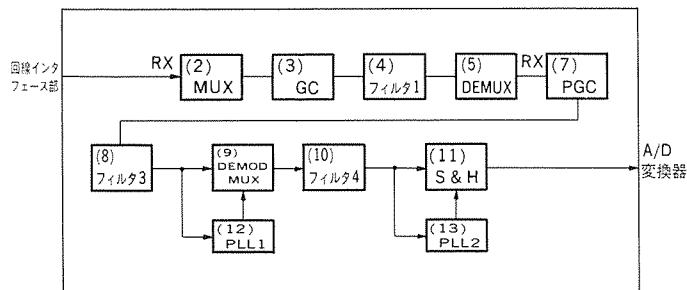

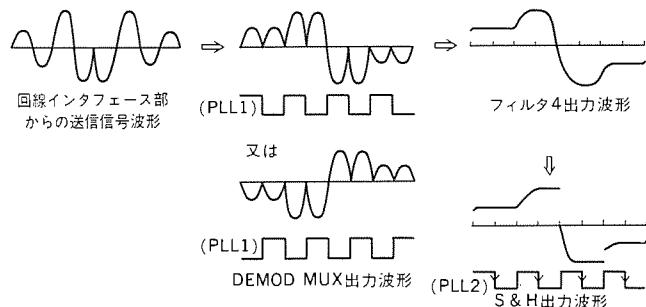

### 静止画テレビ電話用モデムLSI

杉野博之・金子幸司・仁田重之・鈴木 武

三菱電機技報 Vol.63・No.11・P82～85

公衆アナログ電話回線を利用して白黒静止画テレビ電話が、1988年6月に国内標準化されて以来注目を浴びている。今後、より一層の需要拡大を促進するために、多機能化に加えて製品価格の低減化が強く要求されている。

本論文では、次期普及版の画像送受部用に開発した1チップモデムLSIを中心に、静止画テレビ電話のシステムについて説明する。

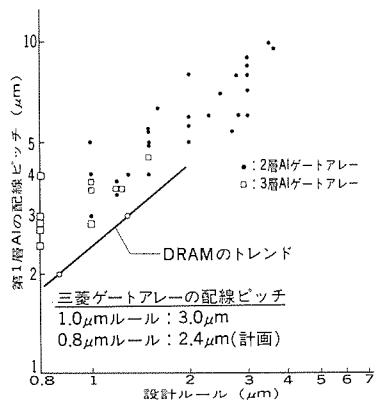

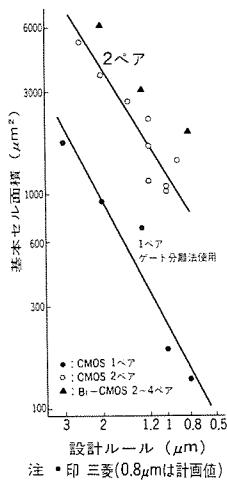

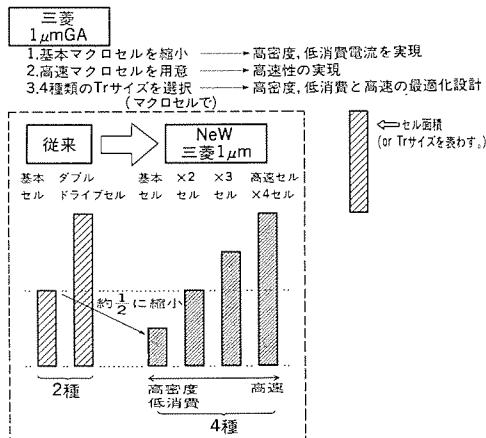

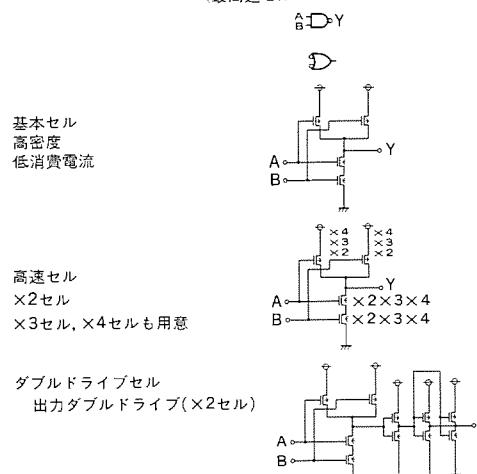

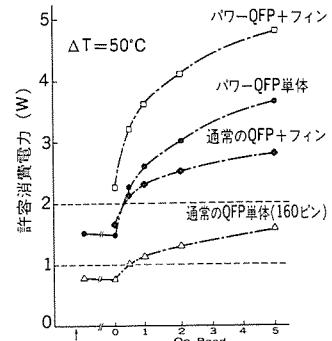

### 高速、低消費電力の1.0μmCMOSゲートアレーM60050シリーズ

中村博隆・布上裕之・西谷一治・後藤諭利・川端啓二

三菱電機技報 Vol.63・No.11・P86～88

三菱1.0μmゲートアレーM60050シリーズは、高速かつ低消費電力を特長としたゲートアレーである。1.0μmプロセス本来の高速性能を生かした上で、低消費電力を追求した。さらに、熱抵抗の小さいプラスチックパッケージを新規開発し、広い用途に対応できるようにしている。多機能のバッファは細かく出力電流や、スルーレートを設定でき、ノイズの問題に容易に対処できる。最先端技術を採用し、しかも使いやすさを追求した製品である。

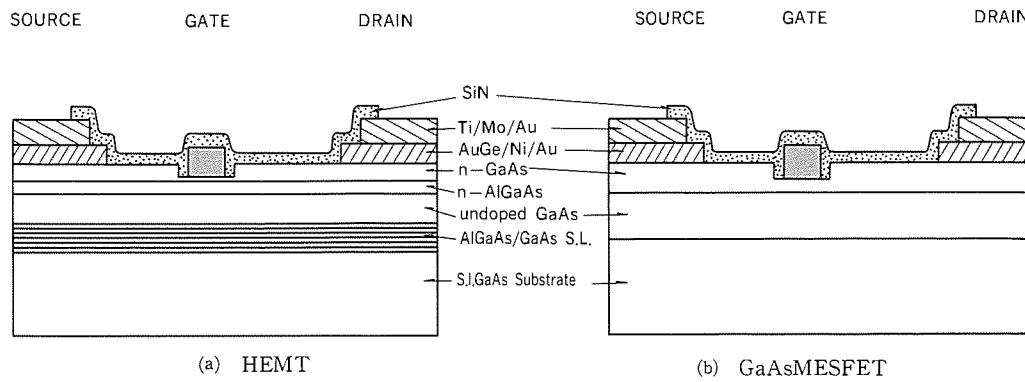

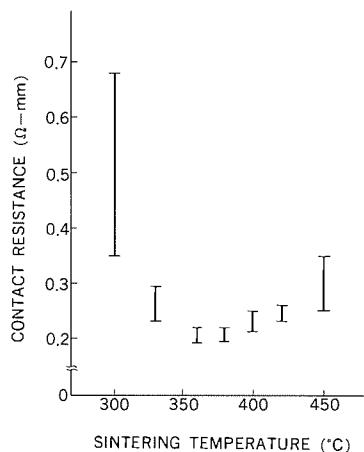

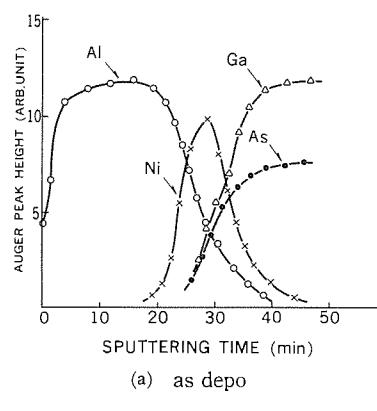

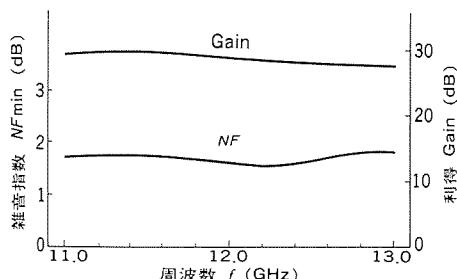

### 超低雑音HEMT

林 一夫・園田琢二

三菱電機技報 Vol.63・No.11・P89～92

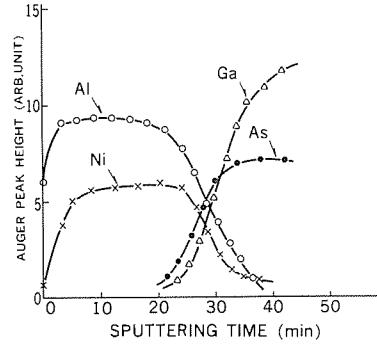

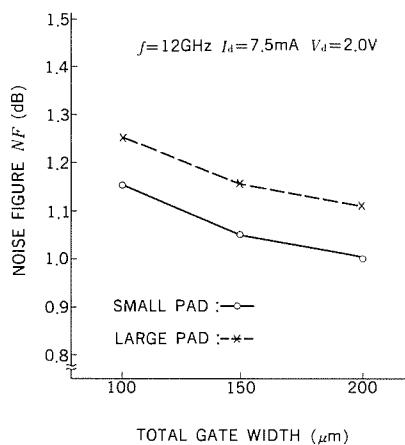

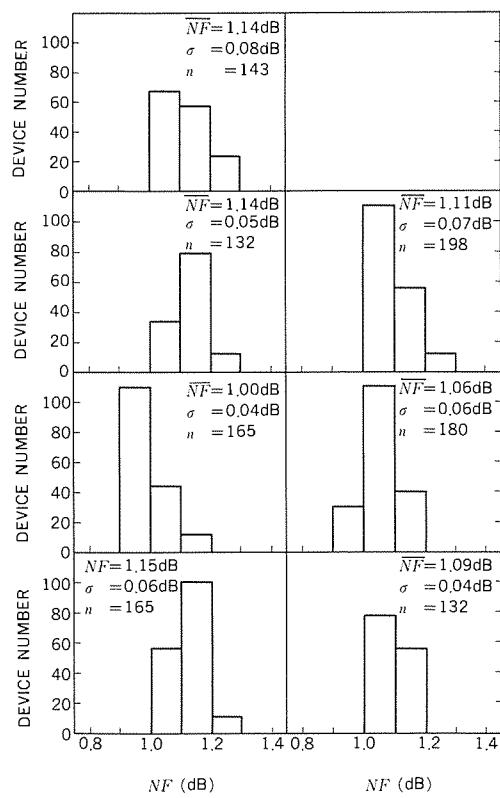

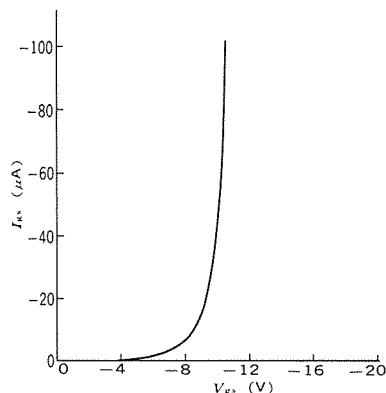

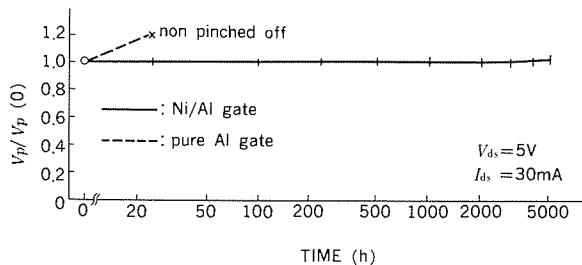

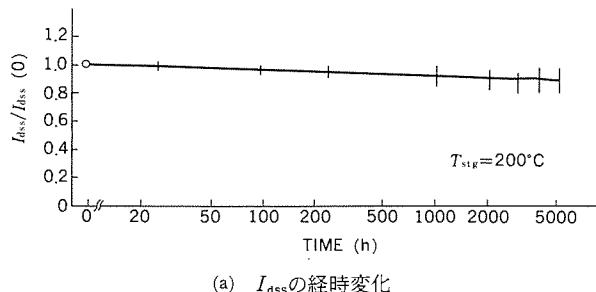

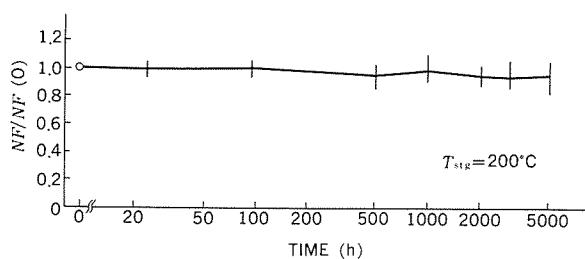

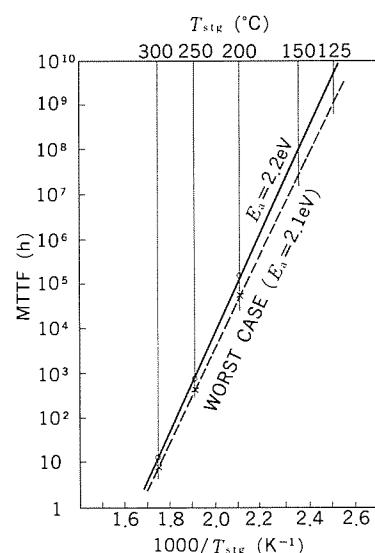

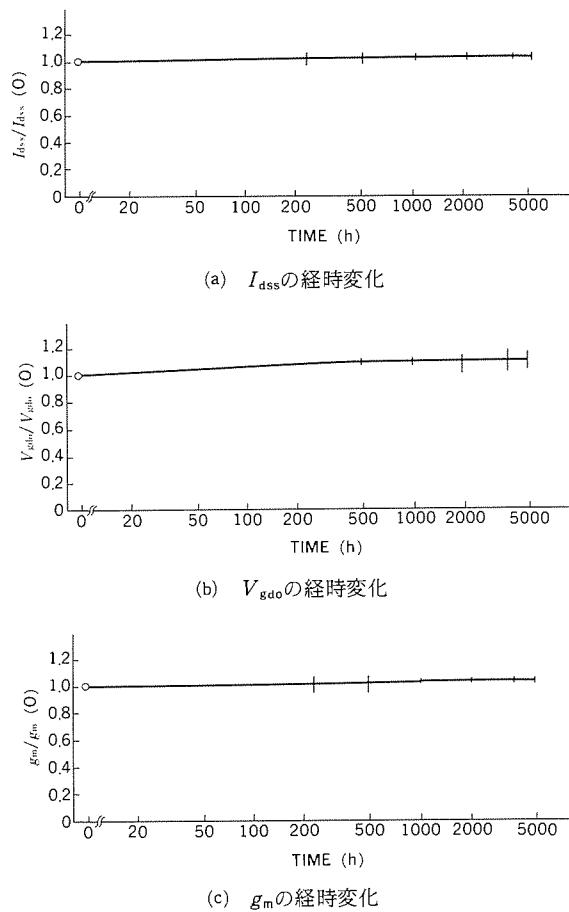

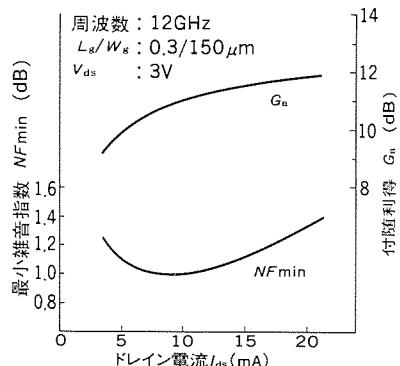

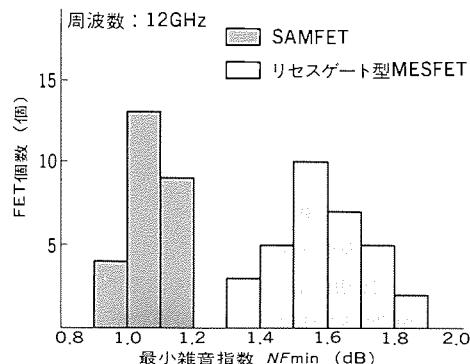

衛星放送をはじめとするマイクロ波通信システムのキーデバイスである超低雑音HEMTを開発・製品化した。当社独自の低温オーミックセンター技術、Ni/AI合金化ゲート、並びに全自動分子線エピタキシー装置の開発により、周波数12GHzで雑音指数 $NF \leq 1.0\text{dB}$ という従来のGaAs-FETでは達成し得ない優れた性能と、平均故障時間が $10^9$ 時間以上の高い信頼性を持つ超低雑音・高信頼度HEMTの量産化を実現した。

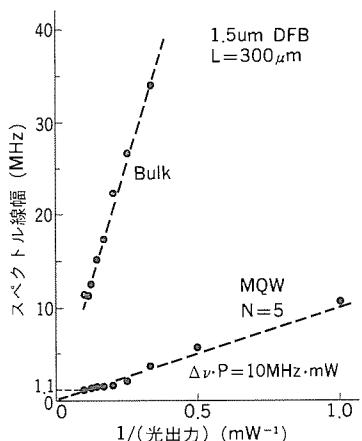

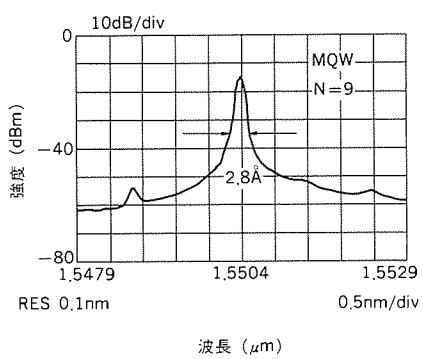

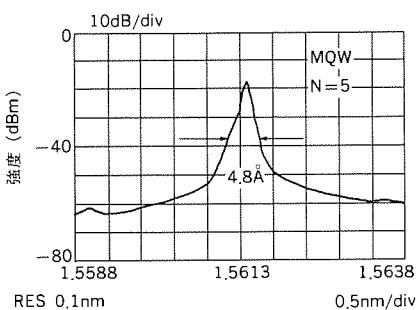

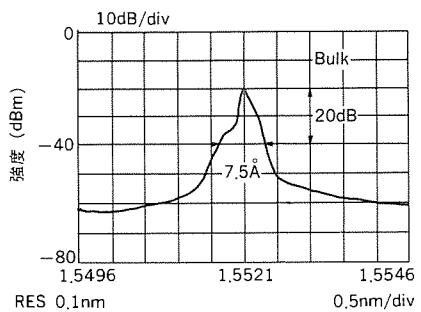

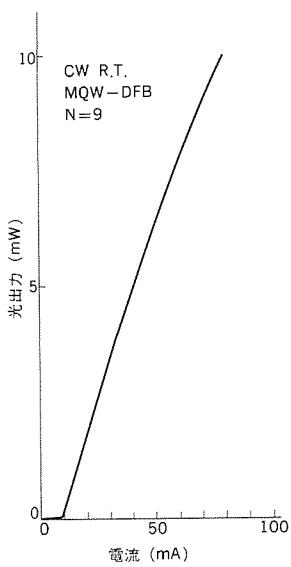

### 光通信用1.5μm帯MQW-DFBレーザ

柿本昇一・吉田直人・榊原 靖・水口一男・須崎 渉

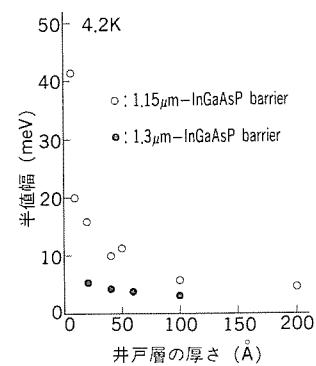

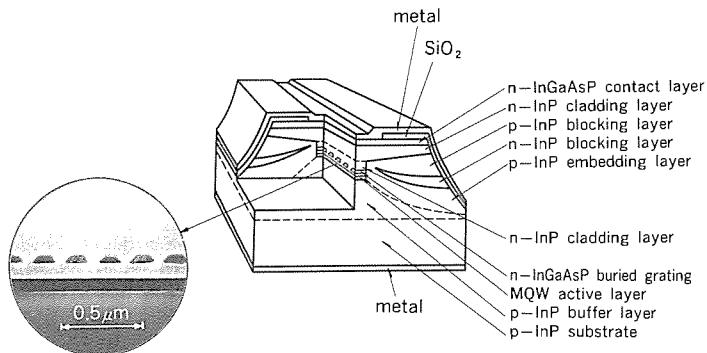

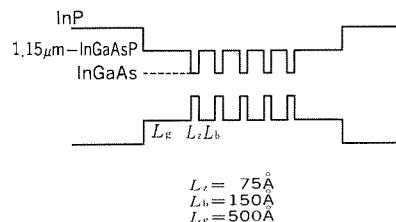

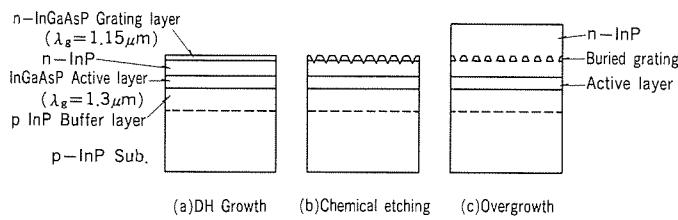

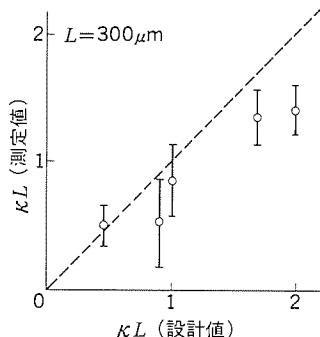

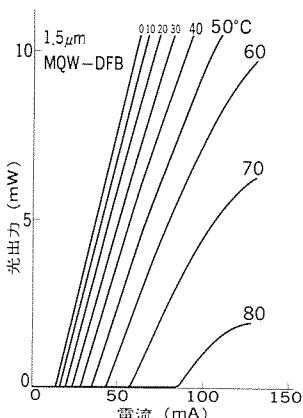

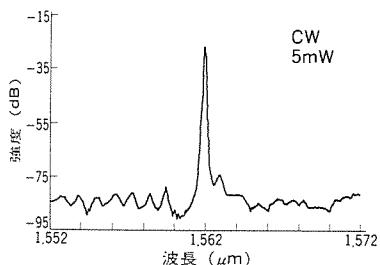

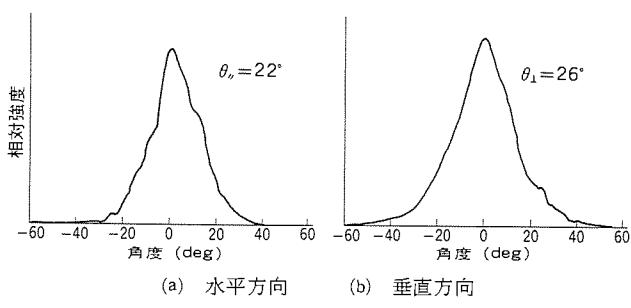

三菱電機技報 Vol.63・No.11・P93～96

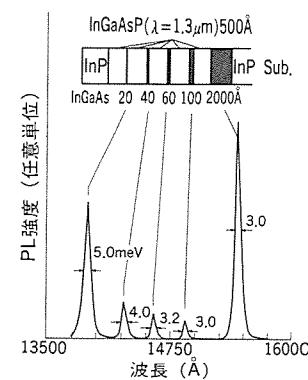

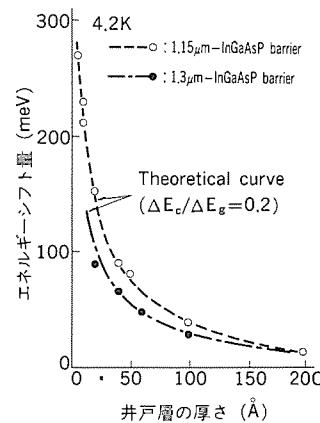

当社がこれまでに開発してきたInGaAsP-DFB-PPIBHレーザに、新たにBG型のレーザ共振器構造とMQW構造を採用することにより、10mA以下の低しきい値電流、45dB以上の高いサイドモード抑圧比、1.1MHzという狭スペクトル線幅及び2 Gbps変調時のチャーピング量として2.8 Åといい小さな値を得ることができた。このMQW-DFBレーザは、大容量・長距離光通信やコヒーレント光通信用の光源に適している。

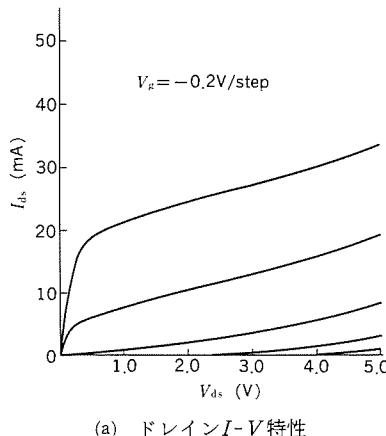

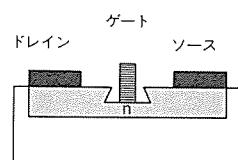

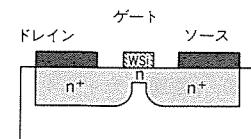

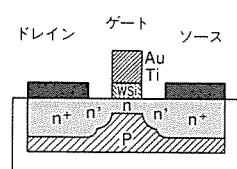

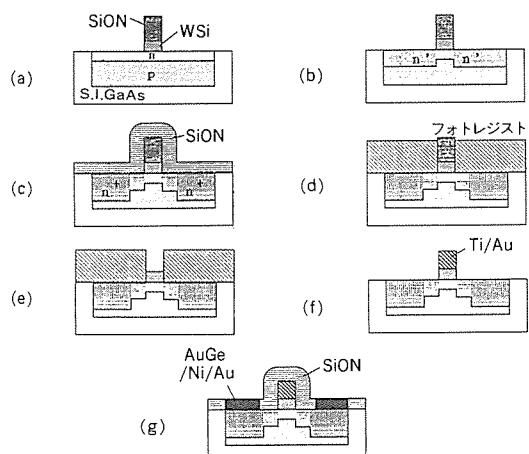

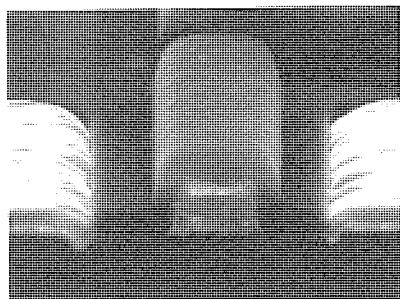

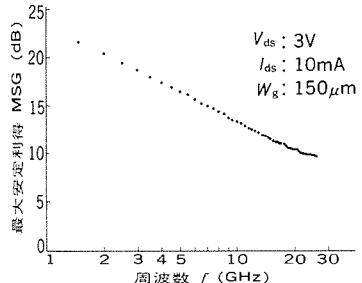

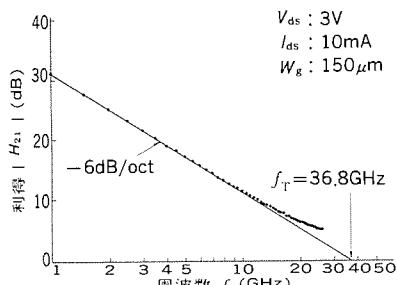

### 超低雑音GaAsSAMFETの開発とMMICへの応用

細木健治・綾木なぎさ・加藤隆幸・谷野憲之・高野博三

三菱電機技報 Vol.63・No.11・P97～99

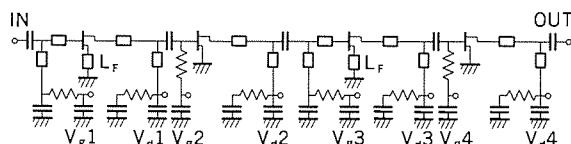

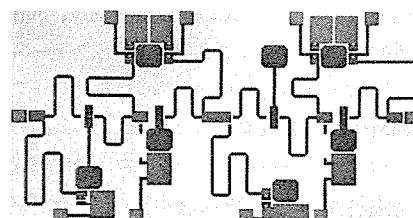

均一性・再現性に優れた多層ゲート電極を持つ当社独自の自己整合型GaAsFET—SAMFET (Self-Aligned Multi-layer gate FET) を開発し、12GHzにおける最小雑音指数が $1.0\text{dB}$ という従来のリセスゲート型MESFETでは得られない優れた性能を実現した。このトランジスタを4段低雑音MMIC増幅器に適用し、11.7～12.7GHzにおいて雑音指数 $1.76\text{dB}$ 以下、利得 $28\text{dB}$ 以上の世界最高性能を得た。

# Abstracts

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 82 ~ 85 (1989)

## A Modern LSI for Still-Frame Video Telephones

by Hiroyuki Sugino, Koji Kaneko, Shigeyuki Nita & Takeshi Suzuki

In June 1988, the Japanese government established domestic standards for telephones with still-frame monochrome video transmission capabilities that use conventional analog telephone lines. Sales of this equipment are expected to accelerate as additional functions become available and prices drop. The article introduces a newly developed monolithic system LSI and a new still-frame video telephone that uses it.

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 57 ~ 60 (1989)

## The MR3200 Operating System (Based on MICRO-ITRON Specifications for the M32 Series 32-Bit Microprocessors) and Its Development-Support Environment

by Koji Hirano, Hideo Tsubota, Toru Shimizu, Kazunori Saito & Keizo Higuchi

This operating system is based on the MICRO-ITRON specifications developed to support embedded-controller applications. A hardware emulator has also been developed to enable debugging of applications software in the operating system's real-time environment.

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 86 ~ 88 (1989)

## The M60050 Series High-Speed, Low-Power-Consumption, 1.0 $\mu$ m CMOS Gate Arrays

by Hirotaka Nakamura, Hiroyuki Nunogami, Kazuharu Nishitani, Tsugutoshi Goto & Keiji Kawabata

The high speed of these gate arrays is associated with the 1.0 $\mu$ m CMOS process; the reduced power consumption is also a new development. The devices also feature a newly developed plastic package with low thermal resistance, opening the door to a wide range of applications. The multifunction buffer allows fine control over output current and slew rate for an easy solution to noise problems. The product employs advanced technologies and is also easy to use.

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 61 ~ 65 (1989)

## A 24-Bit 50ns Digital-Image and Video-Signal Processor (DISP)

by Hideyuki Terane, Shin'ichi Nakagawa, Masahiko Yoshimoto, Toshiaki Shimada, Hirofumi Shinohara & Masahiro Hatanaka

This DISP, developed using 1.0 $\mu$ m double-metal CMOS technology, integrates 538,000 transistors. It features an enhanced parallel architecture and a video-oriented data-processing function to improve its real-time processing capability. Moreover, the processor integrates an instruction RAM, two dual-port data RAMs, and various control units so that external components are minimized. The DSIP is suitable for a wide range of high-precision, high-speed digital-image and video-signal processing.

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 89 ~ 92 (1989)

## A Super-Low-Noise HEMT

by Kazuo Hayashi & Takuji Sonoda

The Corporation has developed a mass-production version of a super-low-noise high-electron-mobility transistor (HEMT) for DBS systems and other microwave communications systems. The device is fabricated using proprietary technology for low-temperature ohmic sintering, NiAl alloy gates, and fully automated electron-beam epitaxy to achieve a noise figure of  $\leq 1.0\text{dB}$  at 12GHz, a value impossible to attain by existing GaAsFET technology. The device also features high performance and a high-reliability design with a mean-time-to-failure of over  $10^9$  hours.

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 66 ~ 70 (1989)

## 16-Bit One-Chip Microcomputers for Automotive Use

by Shozo Shirota, Kikuo Muramatsu, Toshiaki Tayama, Kazuaki Miyata & Tadayoshi Adachi

The M37791E4TJ Series monolithic microcomputers feature an enhanced on-chip memory capacity as a successor to the M37790STJ 16-bit microcomputers for engine-control applications. Both devices belong to the MELPS7700 family of control microcomputers. The new microcontrollers feature a 32KB one-time PROM, 1.25KB RAM, 16-bit timer, 10-bit A/D converter, and UART implemented on a single chip by an advanced high-reliability process.

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 93 ~ 96 (1989)

## A 1.5 $\mu$ m MQW-DFB Laser Diode for Optical Communications

by Shoichi Kakimoto, Naohito Yoshida, Yasushi Sakakibara, Kazuo Mizuguchi & Wataru Susaki

The Corporation has developed an InGaAsP distributed feedback laser diode with a P-substrate partially inverted buried heterostructure, buried grating, and multi-quantum-well structure. This construction yields a low threshold current of 10mA, a high side-mode suppression of over 45dB, a narrow spectral linewidth of 1.1MHz, and a small chopping level of 2.8 under 2Gbps modulation. The device is suitable as a light source for high-volume, long-haul communications and coherent communications systems.

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 71 ~ 76 (1989)

## A High-Performance 16-Bit Single-Chip Microcomputer with a Built-in DMA Controller

by Takashi Yamasaki, Kentaro Shimmura, Yasushi Shimizu, Mitsuyoshi Nakamura, Takehiko Matsunaga & Naoki Yamauchi

This high-speed microcomputer has an on-chip DMA controller for rapid transfer of large volumes of data and a controller capable of directly controlling high-capacity DRAM. It is available in standard (M37720S1FP) and high-speed (M37720S1AFP) versions and is a member of the MELPS7700 microcomputer family. The device is intended for control of office and industrial equipment. The article introduces the device and its new functions and features.

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 97 ~ 99 (1989)

## A Super-Low-Noise GaAs SAMFET and Its Application in MMICs

by Kenji Hosogi, Nagisa Ayaki, Takayuki Kato, Noriyuki Tanino & Hirozo Takano

Developed with a proprietary multilayer self-aligned gate structure, this SAMFET (self-aligned multilayered-gate FET) has a minimum noise figure of 1.0dB at 12GHz, a substantial improvement over the previous technology for recessed-gate MESFETs. The device is currently the world's highest-performance solid-state microwave detector with a noise index of 1.76dB and gain over 28dB across the 11.7~12.7GHz band. It is suited for applications in four-stage low-noise MMIC amplifiers.

Mitsubishi Denki Giho: Vol. 63, No. 11, pp. 77 ~ 81 (1989)

## Application-Specific LSIs for Use in MUSE and MTSC Converters

by Keisuke Okada, Masahiko Nakamura, Kenji Murakami, Yoshiaki Mizutani & Nobuharu Yazawa

To handle signals from the multiple sub-Nyquist sampling encoding system (MUSE) used in satellite broadcasting of high-definition TV signals a converter is required. The Corporation has developed an image-signal processing LSI and system converter that implement this function. The article describes the conversion process and its ASIC implementation.

## アブストラクト

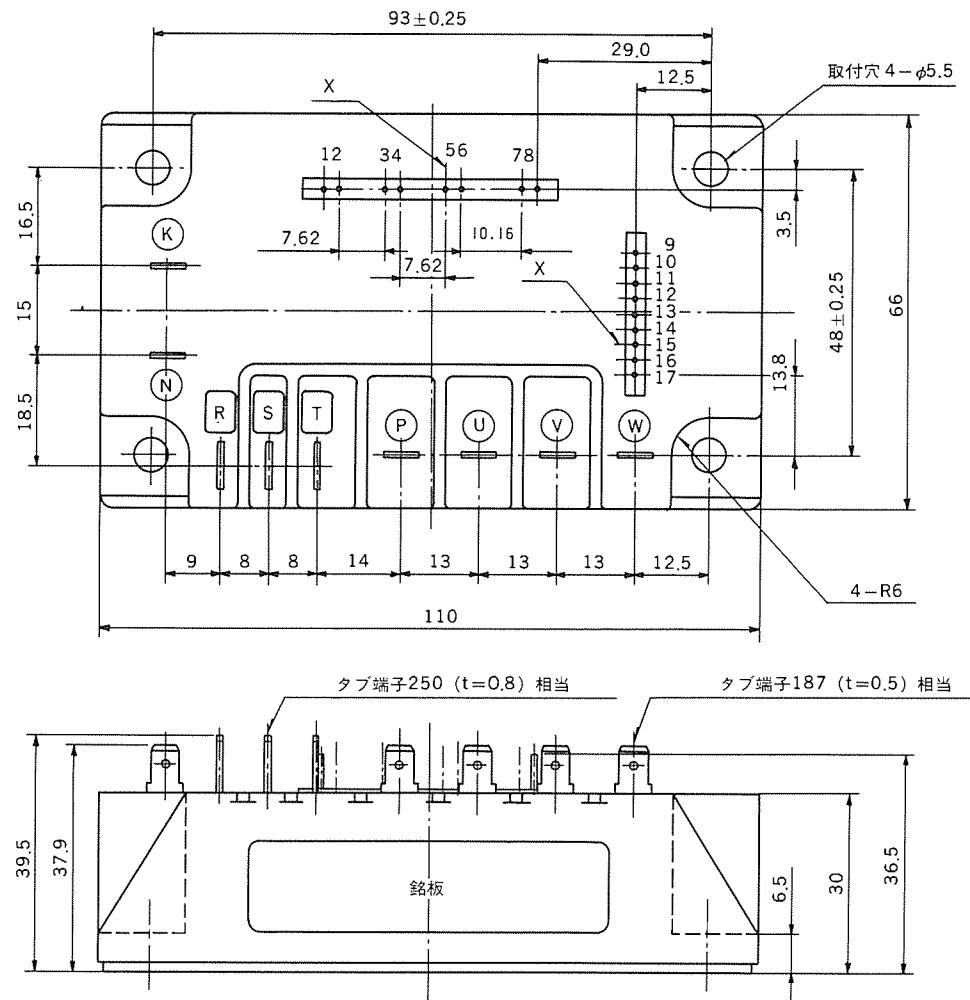

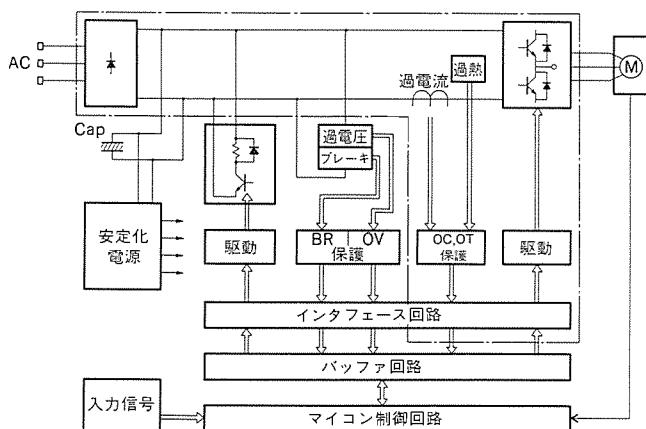

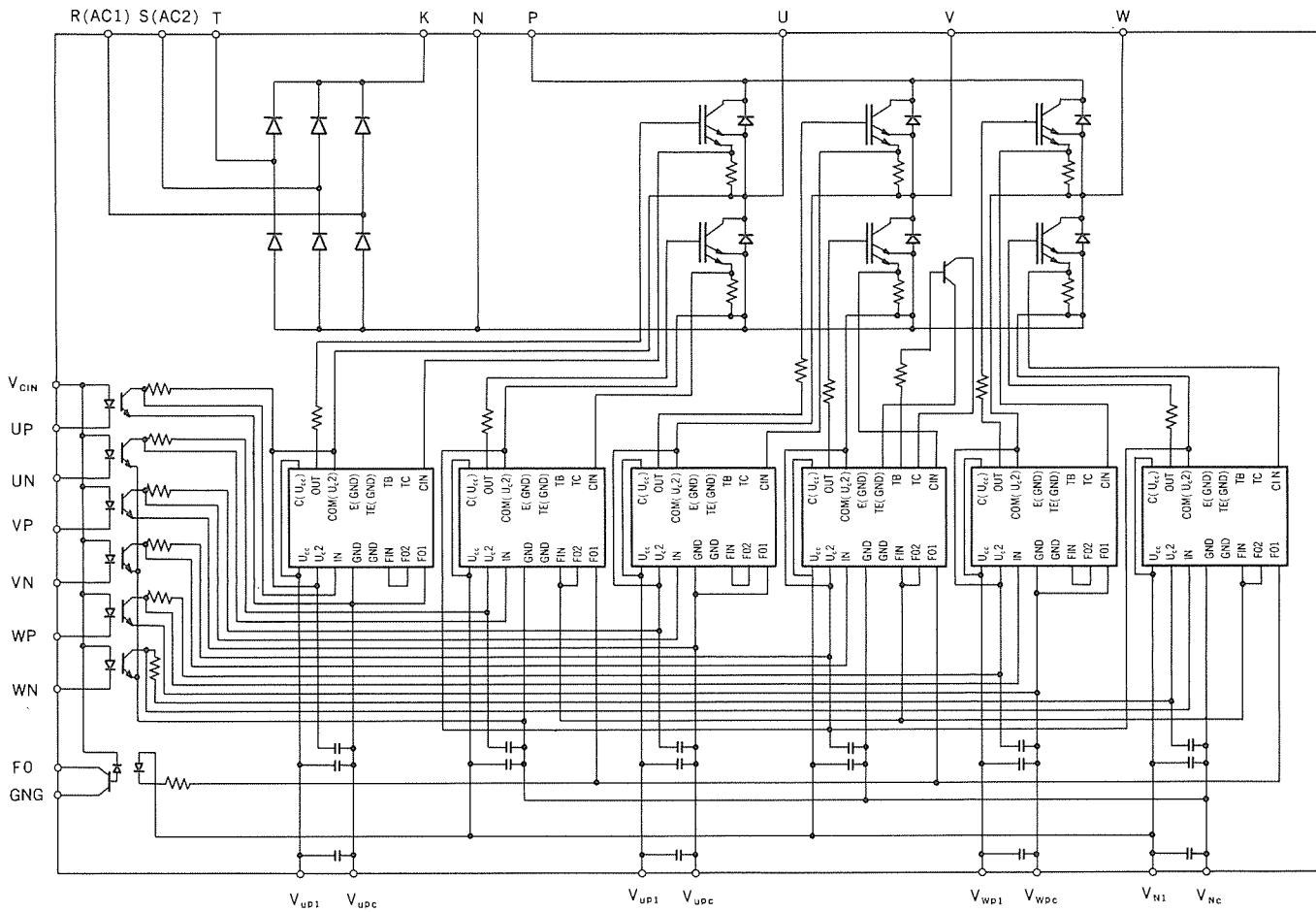

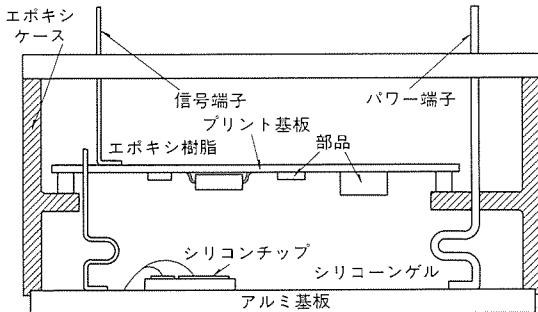

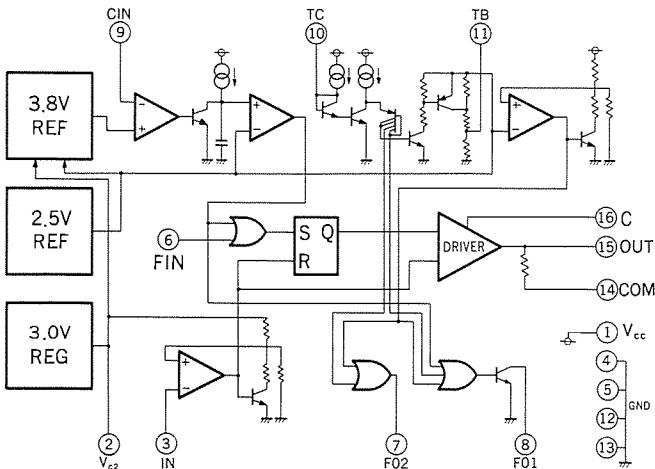

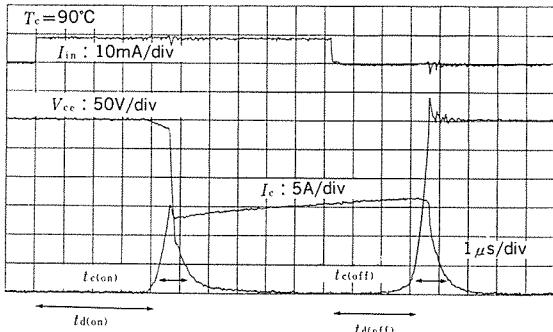

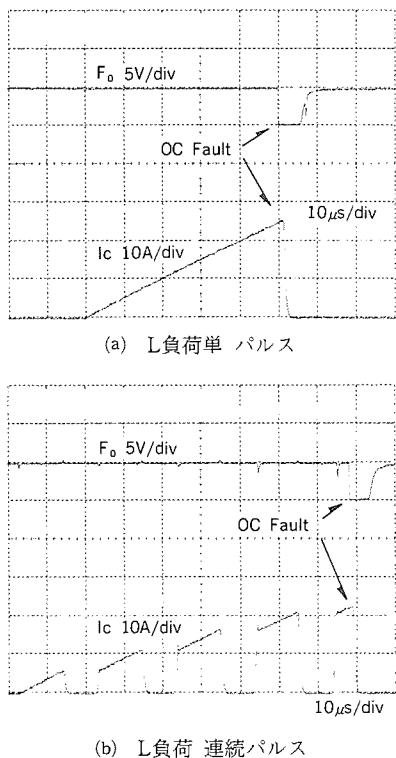

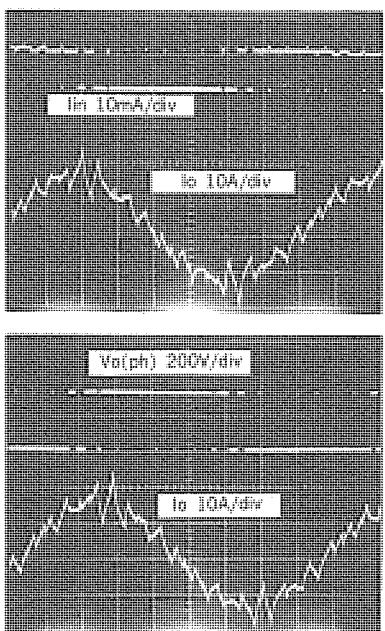

### インバータ用パワーICモジュール

中嶋利廣・ゴーラブ・マジュムダール・福永匡則・飯尾幸司・

梶田武良・宮嶋辰夫

三菱電機技報 Vol.63・No.11・P100～104

電流センス内蔵のIGBTと周辺回路を、一つのパッケージに集積した500V、10～20AのパワーICモジュールの開発・量産化に成功した。このパワーICモジュールは、コンバータ・インバータ・駆動回路・保護回路等の機能を集積化し、多機能で自己診断機能を持ち、マイコンからの入力信号を印加するだけでインバータとして動作する。このパワーICモジュールにより、システムの小型化、高性能化、高信頼度が実現できる。

### 三次元形状シミュレータ

藤永正人・小谷教彦

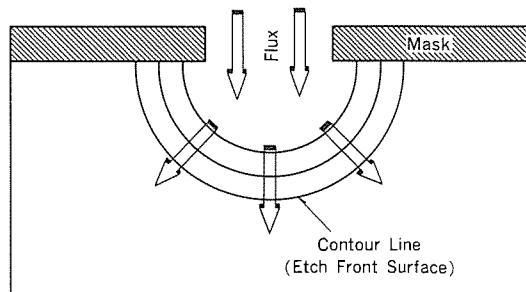

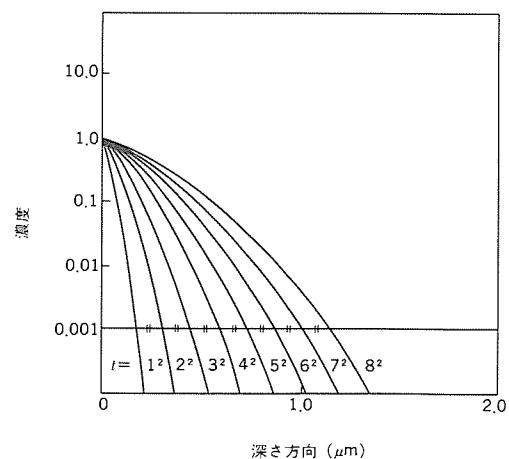

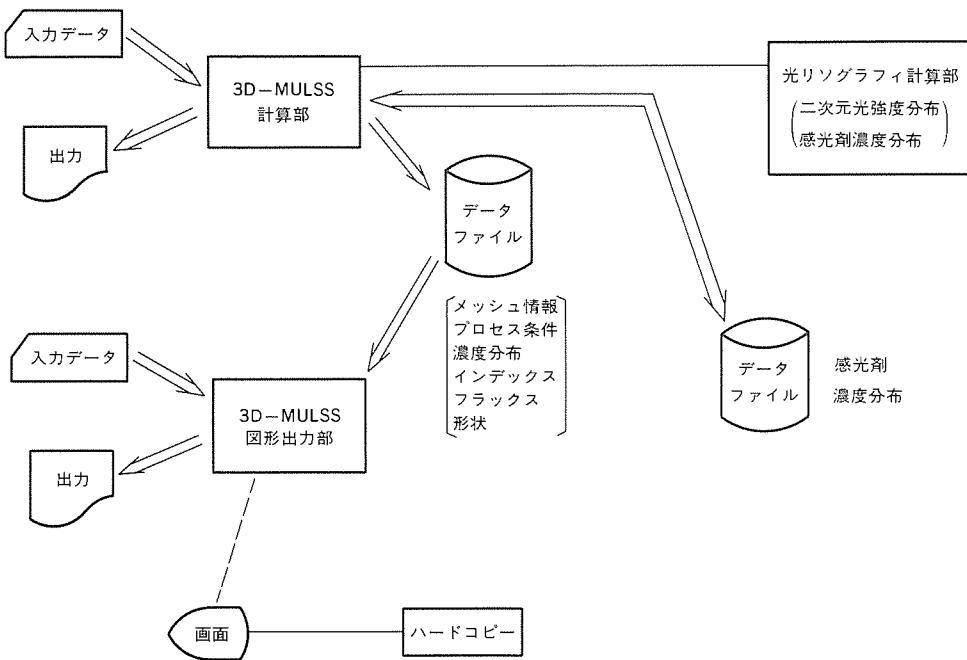

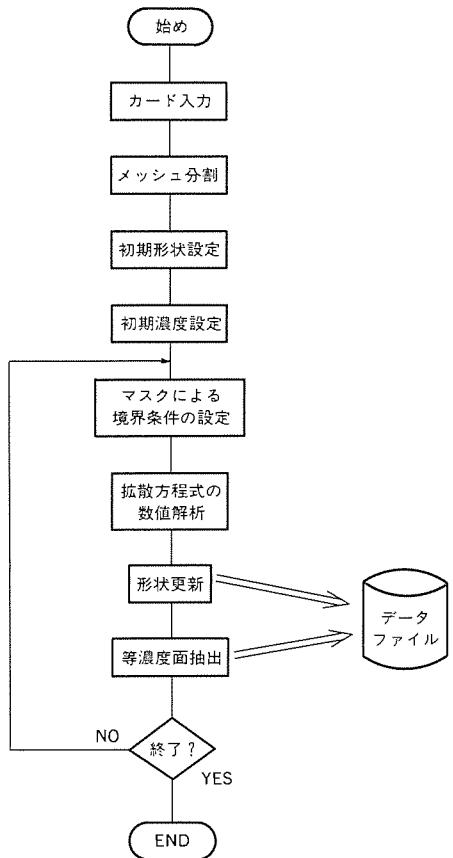

三菱電機技報 Vol.63・No.11・P105～108

ULSIに使われる素子が微細化されるにつれ、素子の角の部分の形状が素子特性に影響し、素子構造も複雑になってきた。このため、LSI素子形状を立体的に予測できる三次元形状シミュレータが要求されている。今回、拡散現象をヒントに全く新しいエッチングモデルを考案し、高速・高精度な三次元形状シミュレータを開発した。これを用いて、光リソグラフィのレジスト形状やWet/Dryエッチング形状をシミュレーションしたので、ここに報告する。

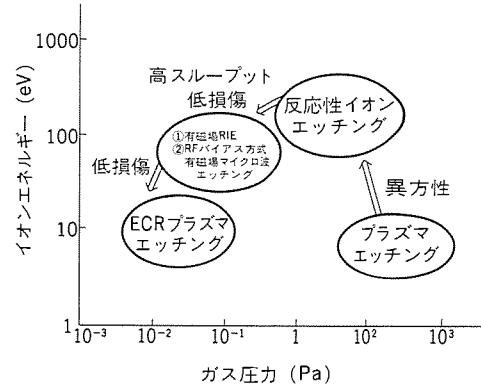

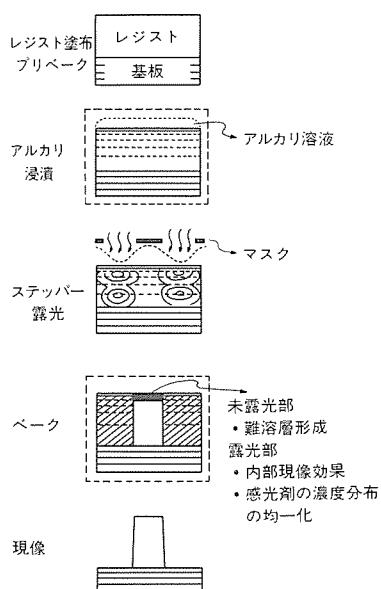

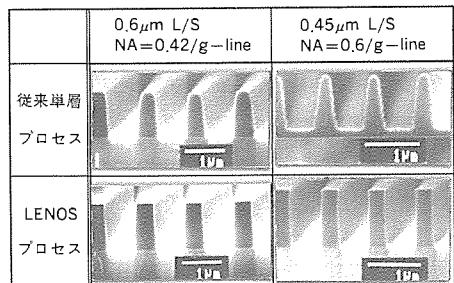

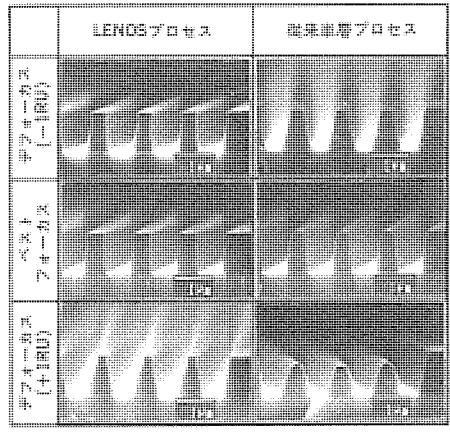

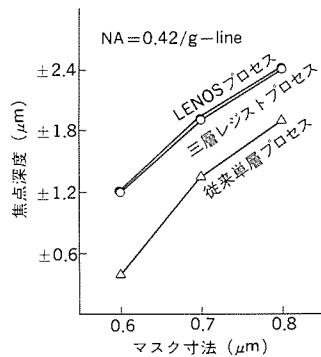

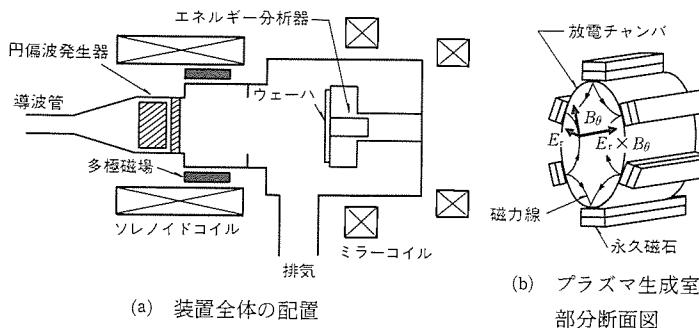

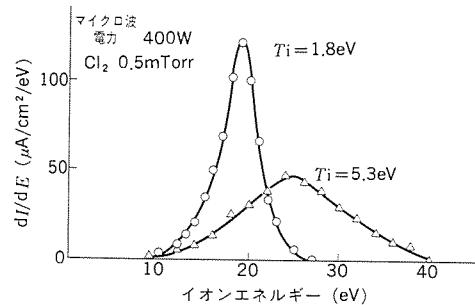

### 超微細加工プロセス技術

西岡久作・小川佐知子・藤原伸夫・河合 晃・魚谷重雄・永田一志

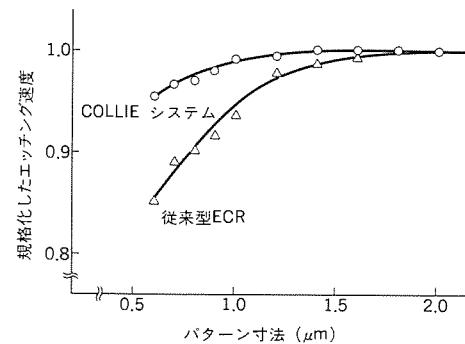

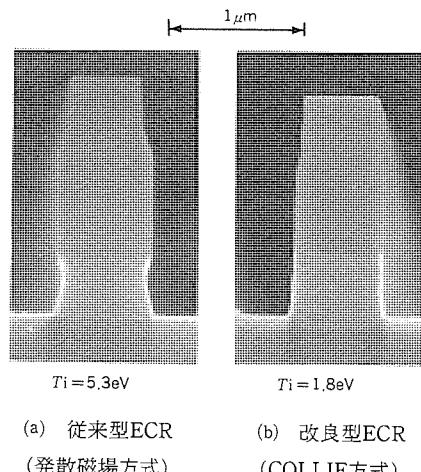

三菱電機技報 Vol.63・No.11・P109～111

超LSIの実現を可能とするハーフミクロン対応超微細加工プロセス技術を開発した。一つは、LENOS (Latitude Enhanced Novel Single Layer Lithography) 法であり、プリベーク後アルカリ処理することと露光後加熱処理することにより、単層レジストプロセスでありながら三層レジスト並みの性能が得られた。もう一つは、COLLIE (Cold and Low-energy Ion Etching) 法であり、多極カスペ複合磁場方式ECRプラズマエッチング技術である。

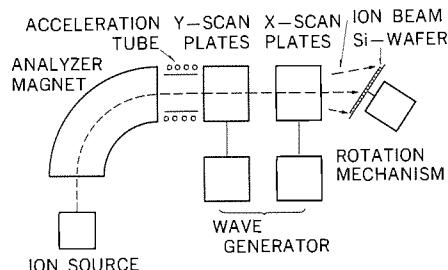

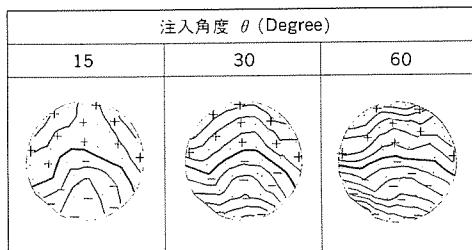

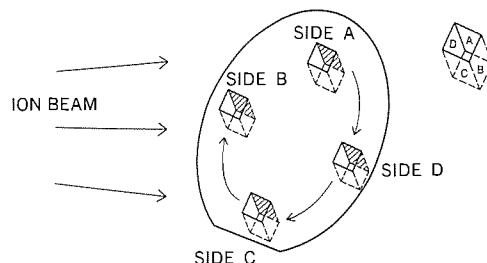

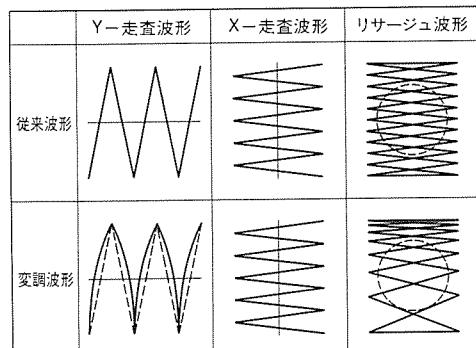

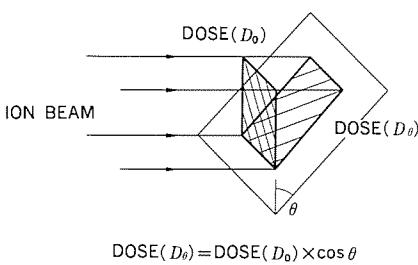

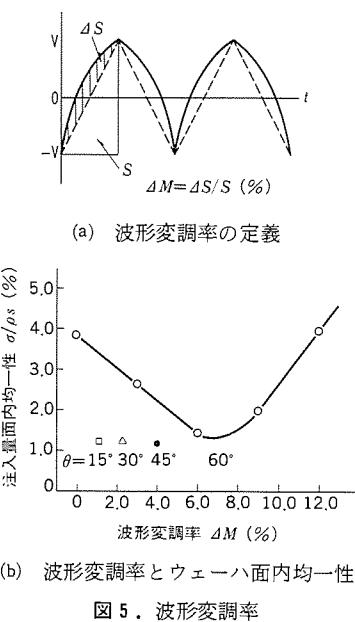

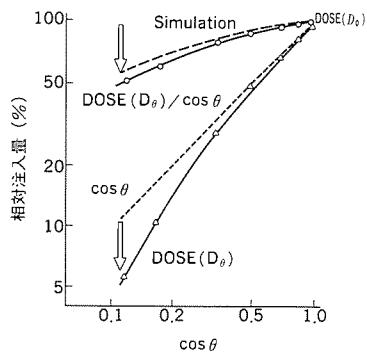

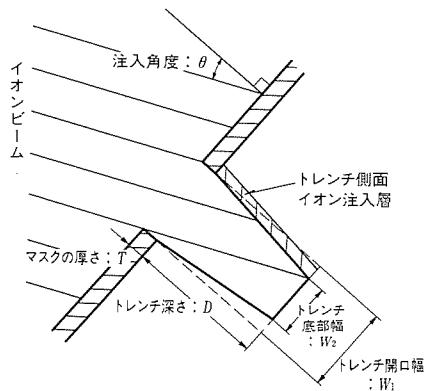

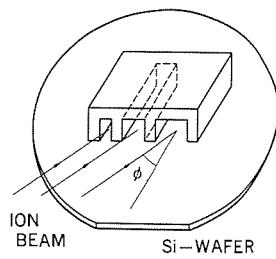

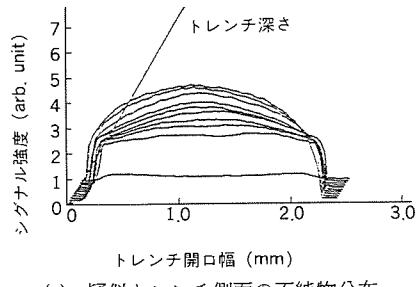

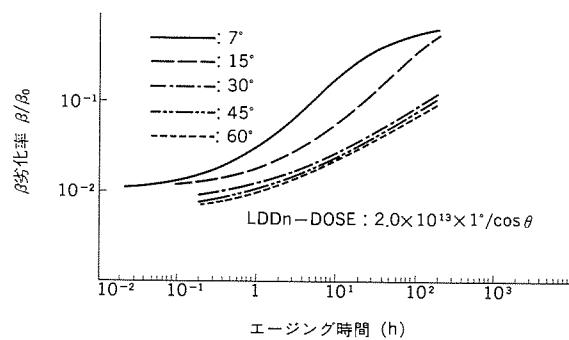

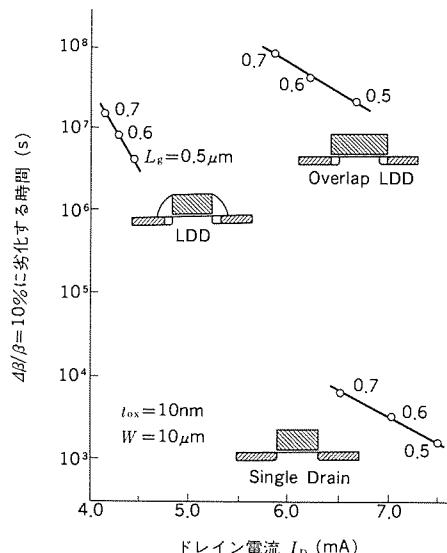

### 斜め回転イオン注入技術

御城俊宏・高橋武人・大崎三郎・長友正男

三菱電機技報 Vol.63・No.11・P112～115

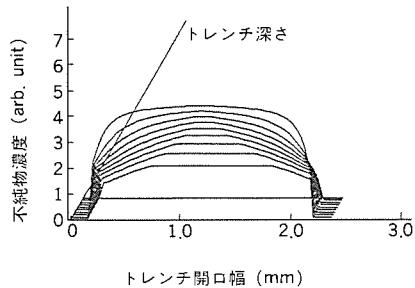

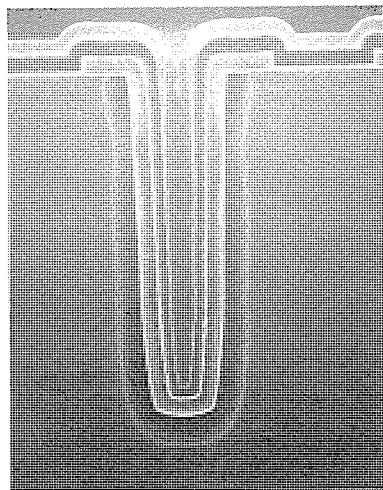

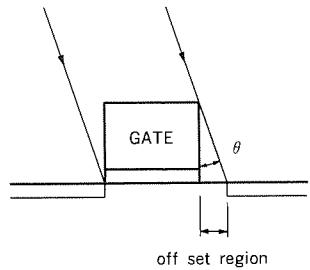

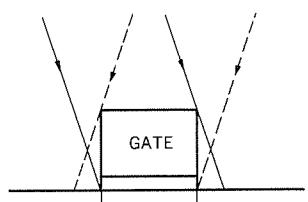

デバイスの微細化と三次元化に対応する斜め回転イオン注入技術を開発した。本技術の基本的特性である注入量の面内均一性、補正について検討し、デバイスへの適用を図った。その結果、トレンチ側面に均一な拡散層の形成ができ、LDD構造MOSトランジスタの非対称電気特性の解消と信頼性の向上を達成した。さらに、斜め回転イオン注入技術は、ハーフミクロン デバイスに適用できる良好な特性と信頼性を持つ新構造トランジスタを実現可能にした。

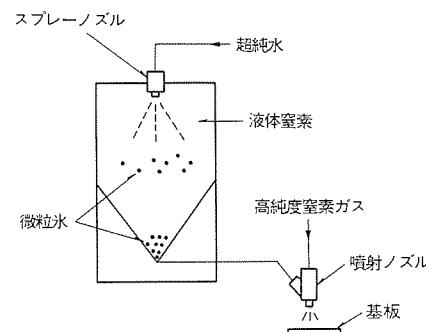

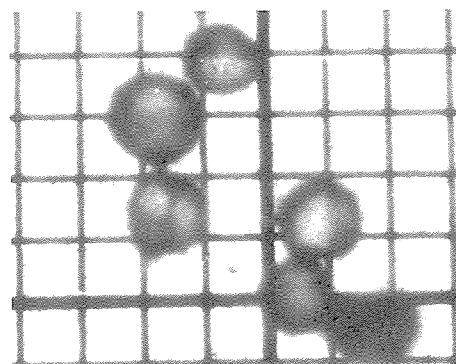

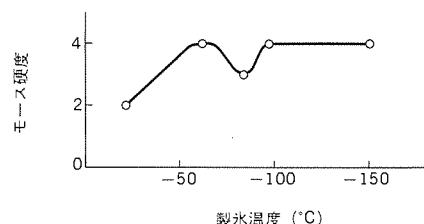

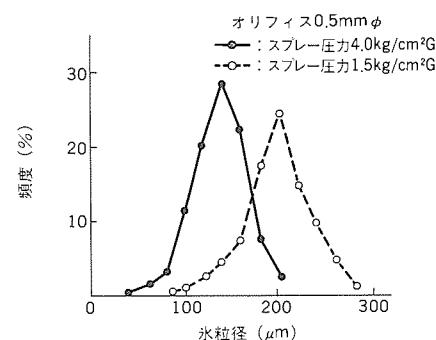

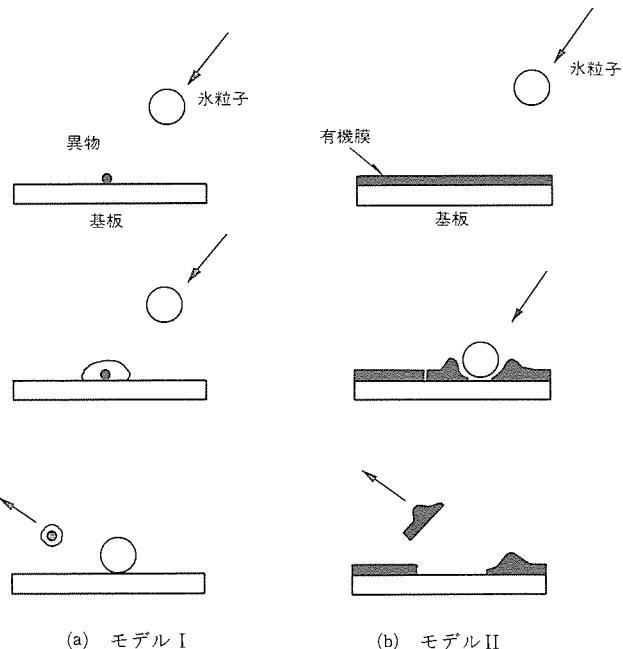

### アイススクラバ洗浄

大森寿朗・福本隼明・加藤忠雄・川口利明・多田益太

三菱電機技報 Vol.63・No.11・P116～119

超LSIの新洗浄法として、極めてクリーンでかつ微小な氷粒子を用いた洗浄装置を開発した。超純水から製造した粒径0.1～300μmの氷粒子を基板表面に噴射することにより汚染物を除去する。特に、サブミクロンレベルの微粒子やCVD膜の異常成長異物など基板表面に強固に付着した汚染物の除去に有効である。本洗浄法は、氷粒子の噴射条件及び硬度を調節することにより、ダメージを制御することが出来る。また、有機物の除去も可能である。

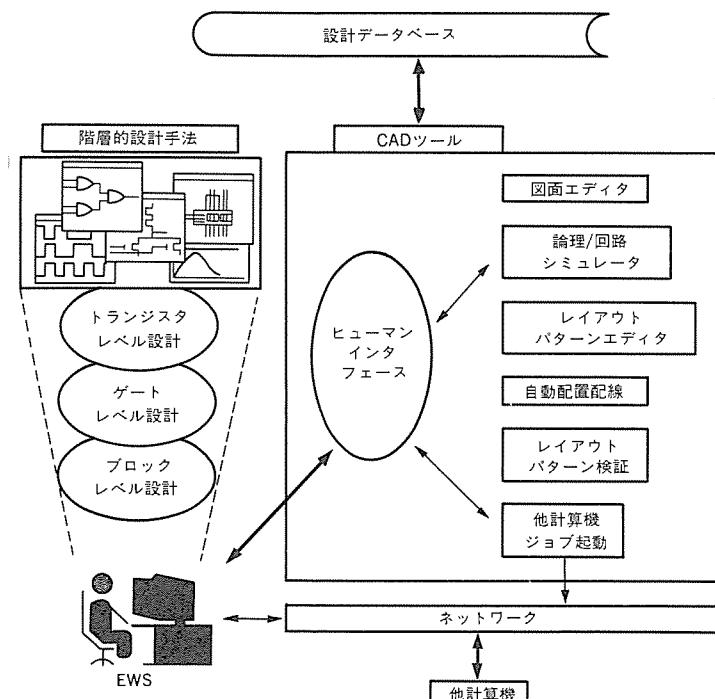

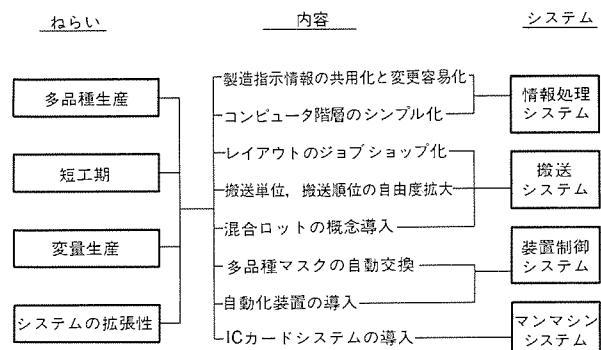

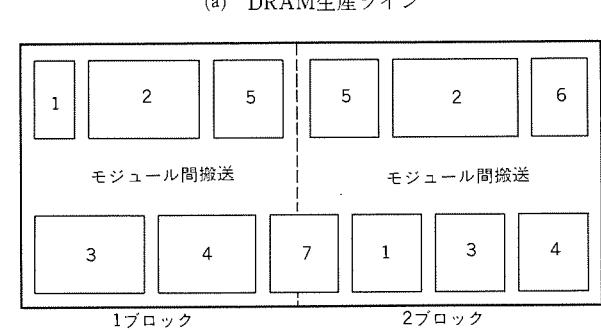

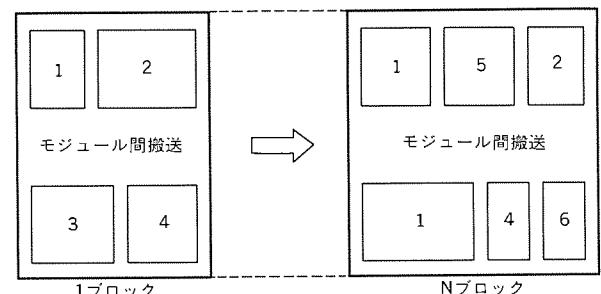

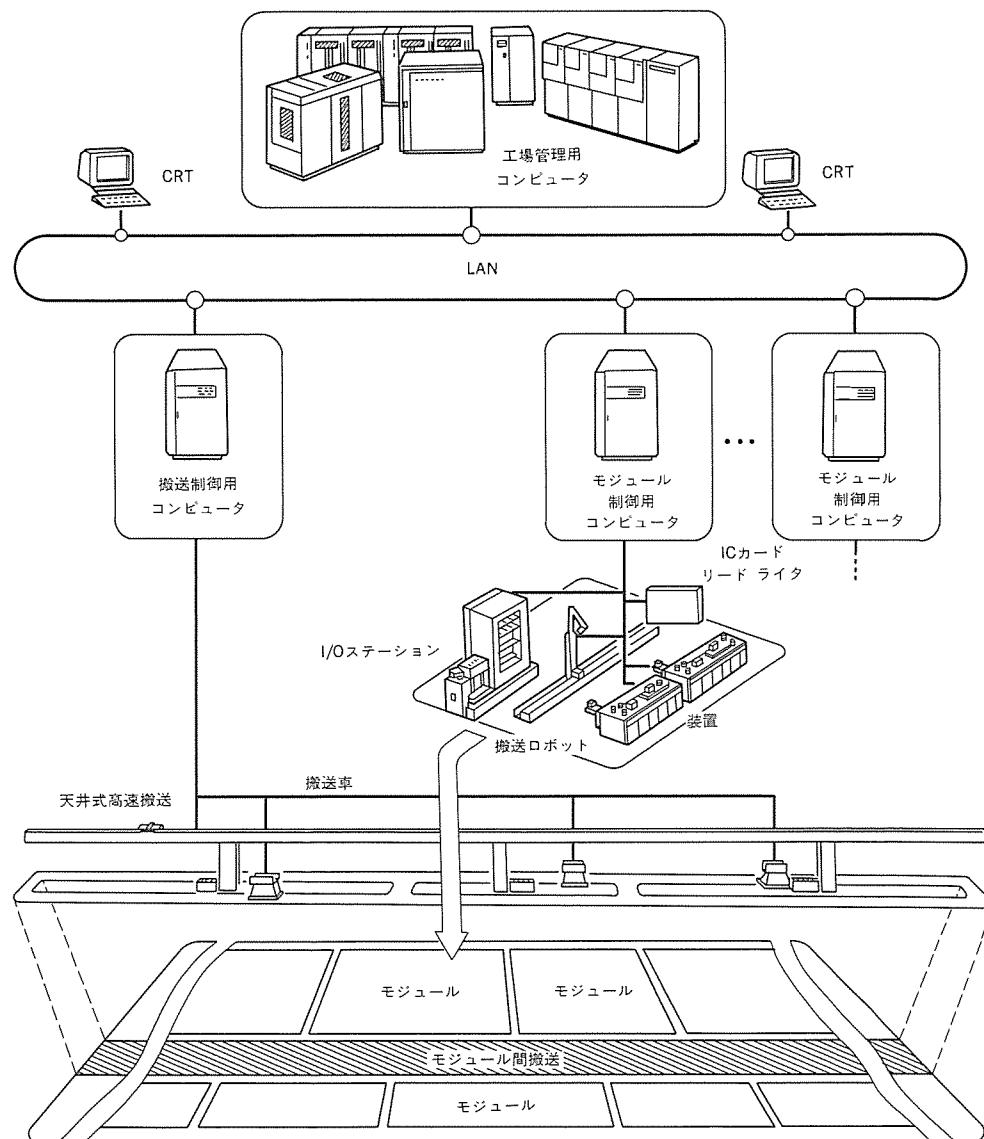

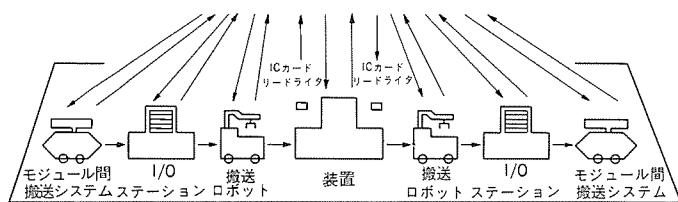

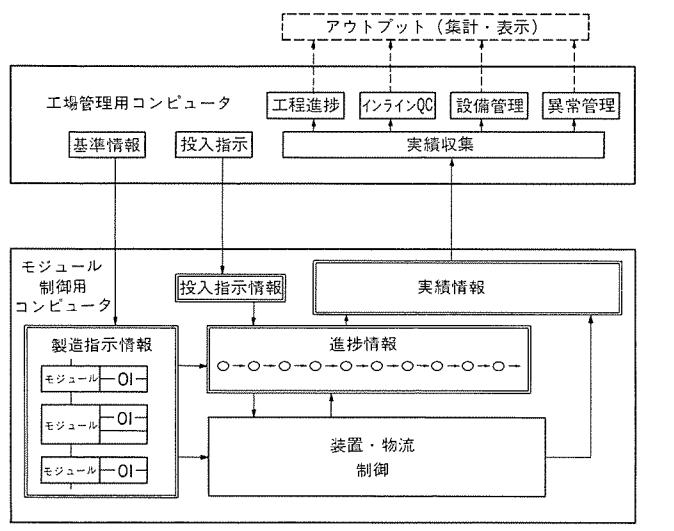

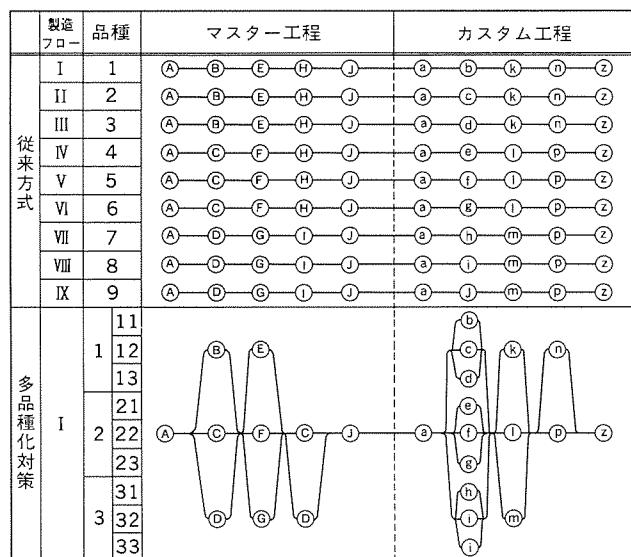

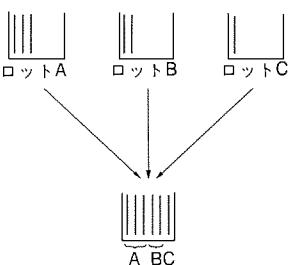

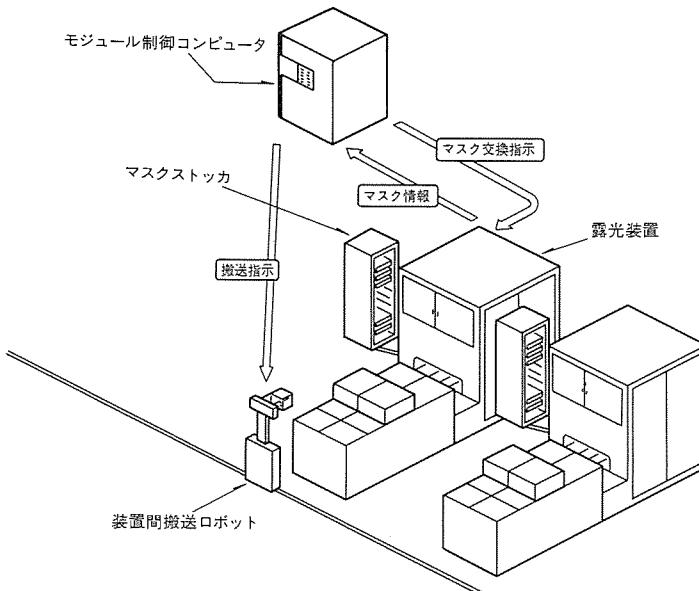

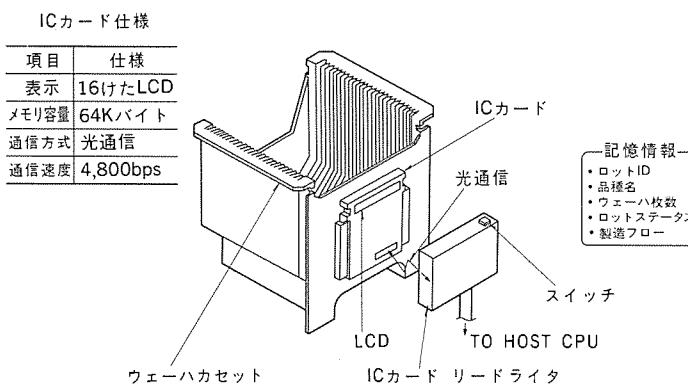

### 半導体のFA技術

石橋一昭・大谷雅樹・吉田博之・加藤雄一

三菱電機技報 Vol.63・No.11・P120～123

生産工場における自動化は、個別装置の自動化の段階から装置間の物流を含めた工場全体の自動化、いわゆるFA(ファクトリーオートメーション)化の段階へと、進展しつつある。当社半導体工場においても、ASIC(特定用途向けIC)を対象とした、短工期かつ多品種変量型生産ラインのFA化に積極的に取り組んできた。

本稿では、高知工場で実現したASICウェーハプロセスラインのFAシステム概要について述べる。

# Abstracts

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 112~115 (1989)

## Oblique-Rotating Ion-Implantation Technology

by Toshihiro Miki, Taketo Takahashi, Saburo Osaki & Masao Nagatomo

This technology is intended for fabricating fine, three-dimensional device features. The authors investigated oblique-rotating ion-implantation technology, and applied their findings to create uniformly diffused layers in trench walls. The process eliminates the asymmetrical electrical characteristics of lightly doped drain MOS transistors, and raises device reliability. Uniform characteristics and high reliability make the technology a promising candidate for production of half-micron-scale devices employing new transistor structures.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 100~104 (1989)

## A Power IC Module for Inverter Systems

by Toshihiro Nakajima, Gourab Majumdar, Masanori Fukunaga, Koji Iio, Takeyoshi Kajita & Tatsuo Miyajima

This module is rated at 500V and 10~20A and includes an insulated-gate bipolar transistor with a current-sense amplifier and peripheral circuits. It has converter, inverter, driver, protection, and self-diagnostic functions. The module functions as an inverter with a single control input from a microprocessor. It facilitates equipment size reductions and boosts equipment performance and reliability.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 116~119 (1989)

## An IC Substrate-Scrubbing System Using a Fine Jet of Ultrapure Ice Particles

by Toshiaki Omori, Takaaki Fukumoto, Tadao Kato, Toshiaki Kawaguchi & Masuo Tada

The authors have developed a VLSI cleaning system that employs ultrafine particles of ice made from deionized water as a cleaning agent. The system employs a jet of particles ranging in size from 0.1~30 $\mu$ m that effectively removes contamination from substrate surfaces, including submicron particles and strongly adhering spurious CVD deposits. The ice-particle velocity and particle hardness are controlled to limit damage to the substrate surface. Organic products are also removed.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 105~108 (1989)

## A Three-Dimensional Topography Simulator

by Masato Fujinaga & Norihiko Kotani

Accurate 3D topography simulators are required to analyze the effects of edge topography on VLSI performance. The authors propose a new etching model based on a modified diffusion equation, and have implemented this model in a simulator. The paper reports on the concept of this model and its applications in photolithography and wet and dry etching processes.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 120~123 (1989)

## Factory Automation for LSI Manufacturing

by Kazuaki Ishibashi, Masaki Otani, Hiroyuki Yoshida & Yuichi Kato

The Corporation has introduced factory automation (FA) technology in its ASIC production lines where varied-size batches of many different devices must be completed on tight schedules. The article describes an ASIC wafer-production line incorporating this factory automation technology at our Kochi Factory. FA technology unites the separate systems that comprise production processes and generally include workpiece transport.

Mitsubishi Denki Gihō: Vol. 63, No. 11, pp. 109~111 (1989)

## Ultrafine Patterning and Etching Technology

by Kyusaku Nishioka, Sachiko Ogawa, Nobuo Fujiwara, Akira Kawai & Shigeo Uoya

The Corporation has developed process technology for half-micron VLSIs. The latitude-enhanced novel single-layer lithography process (LENOS) consists of an alkaline treatment after prebaking and heating after exposure that enables a single-layer resist process to equal the performance of a three-layer process. The cold and low-energy ion-etching process (COLLIE) is an ECR plasma-etching system employing a multicusp hybrid magnetic field.

## 卷頭言

取締役 社長

志岐 守哉

人は30歳を而立という。事業も30歳は而立て働き盛りのときである。而立は自立にも自律にも通ずるもので、親兄弟、恩師、お客さまに恩を返していかなければならない年頃である。

当社は、1959年8月1日、半導体の量産工場として北伊丹工場（現、北伊丹製作所）を創設し、半導体事業に本格的進出をした。以来、30年間、世界の半導体産業の発展と歩みを共にし、今日の隆盛を迎えることができた。

もちろん、これまでの道程は、必ずしも平坦ばかりではなかった。しかし、先人の血の滲むような努力と、三菱電機の総力を結集して、さまざまな苦難を克服してきたからこそ、現在にまで成長できたのであって、心から感謝の意を表さずにはいられない。

半導体事業を振り返ってみると、黎明期には、アメリカから基本技術を学び、1960年代になって日本政府の産業振興策により事業の礎を固めることができた。日本経済の高度成長期には、大電力シリコン整流素子、サイリスタ等が、電鉄、鉄鋼、化学等の基幹産業分野で精力的に使用され、近代化に大きく貢献した。

1970年代に入ると、半導体は一段と技術革新の速度を増し、メモリ、マイクロプロセッサの新製品を続々と世に送り出し、さらには先駆的化合物半導体製品も発表し、これが多様な社会的ニーズに対応し得る能力向上に貢献したのである。即ち、応用範囲も民生機器分野のみならず、コンピュータをはじめとし、宇宙、通信、情報処理、オフィスオートメーション、自動車等々、産業機器分野へと需要が拡大され、産業構造の変換に伴い、基幹産業へと変貌してきたのだ。

この間、三菱電機は自社技術開発の芽を育て、先端技術に対処する巨額の設備投資を計画的に行い、世界最新鋭工場や最先端研究所群を建設し、かつ優秀な人材を投入することで事業体质の強化を図ってきた。まさに「仕事が人を育て 人が仕事を拓く」で着実に力をつけてきた。

しかし、今日、欧米諸国との通商摩擦、知的財産権、NIESの台頭、生産基地のグローバル化等々の問題が山積しており、厳しい環境下に置かれている一方、我が国半導体産業は世界の指導的立場に置かれているため、国際協調の推進をはじめとし、各国から寄せられる期待に応えていかなければならない使命も担っている。

海外と国内、というとらえ方のみならず、海外と海外、国内と国内、あるいは社内外というように多面的なとらえかたをする中で、さまざまな問題を解決していく姿勢が求められているのである。つまり、四方八方お客さまなのだから、顧客優先の精神を貫き、技術力はもちろんのこと、あらゆる情報を取り込んだサービスを提供していく必要に迫られている。

社会は、テクノロジープッシュ型を望んでいる。半導体、デバイスは、さらに、今後、新しい先端技術を磨き、大いなる可能性を追究しながら、国際的にも、国内的にも、現在置かれている立場を十二分に認識し、責任ある事業を推進していかなければならないと考えている。それは而立の責務である。

# 三菱半導体事業30周年に寄せて

三菱半導体事業30周年記念特集号発刊にあたり、心からお慶び申し上げます。

今から30年ほど前、可能性は高くとも、海のものとも山のものともわからなかつた半導体にかなり早くから着手され、事業として持ち上げられたご努力はさぞ大変だったろうと思われます。

ところで現在の半導体界と30年前の半導体界の違いはどのようなところにあるのかというようなところを30周年の区切りに考えてみるのも一考かと思われ、現代半導体界の特徴を30年前の考えと対比させて考えてみたいと思います。

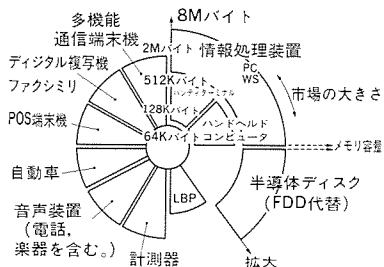

その一つにまず言えることは30年前の半導体界といわれるものは、きわめて科学色が強く、科学上の問題の解決に全力が注がれたのに対して、現代の半導体界の動きというのはもちろん科学技術的な考察も重要であります。それに加えて、マーケティング的な考察いわゆる事業面への考察がかなり重要視されているように思われてなりません。

たとえば、最近マイクロプロセッサ関係で話題となっているRISC(Reduced Instruction Set Computer)の動きなどは科学技術の成果というよりはマーケティング力や宣伝広報、マスコミ操作面での勝利というようにとれることもあります。RISCは発明者、事業者のパフォーマンスがきわめてうまく、その結果、持っている可能性以上に評価されているという見方もできます。しかし、私はこのようなことが全て悪いといっているわけではありません。現在の半導体が抱えている問題はきわめて多岐、複雑であり、RISCの問題一つをとっても半導体事業が単なる科学技術の研究開発だけでは成立しないということをきわめて象徴的に物語っているのであります。

二番目に私がいいたいことは、現在の半導体はアプリケーションの広範囲な広がりにより、半導体単体で物事を考えるのがきわめて苦しくなっているという点です。よくコンピュータのハードウェア、ソフトウェアの問題で、残る問題はソフトウェアだけというようにソフトウェアの問題がきわめて強く強調されることがあります。もちろんソフトウェア的思考ということは重要ではありますが、ソフトウェア思考というのはハードウェアがあってこそ行えるわけであります。決してソフトウェアだけが一人歩きするものではないということです。そこで、私はハードウェアもソフトウェアも重要であるということを再確認したいと思います。そしてこれをトータルアーキテクチャの時代というようになります。ですから、ソフトウェアが重要というあまり、ハードウェアを極端にシンプルにし、ソフトウェアだけでものごとを考えていくということもまた危険であります。

システムというのはハードウェアとソフトウェアのバランスが非常にうまくとれた時にはじめて成功したといえるわけであり、今後のシステム的思考からして半導体にもシステム的思考いわゆるトータルにものごとを考え、ハードウェアとソフトウェアのバランスをうまく決めていくということが重要になります。

その結果として、三番目にいえることは、これから半導体はその開発期間がより長期化するということです。プロセス技術の改良、集積度の増大、複雑化、ソフトウェア開発等々やらねばならぬことは多く、短期間で開発するのはきわめて困難になっています。そして最後に、半導体が人類並びに世界に与える影響が30年前に比べ格段に大きくなっていることを指摘したいと思います。このような時代においては半導体の開発にあたって、開発者が半導体の社会的影響の大きさを強く認識して開発にあたるべきであり、科学的、技術的な面だけにしか興味がないという姿勢はきわめて危険であります。半導体開発者に対し今ほど高い社会的モラルが要求されている時代はありません。

ところで私は1984年からトロンプロジェクトという90年代から21世紀にかけてひろく使われるであ

東京大学 理学部情報科学科 助教授

## 坂 村 健

ろう未来コンピュータシステムのための研究開発プロジェクトを推進しております。まさにこのプロジェクトでは将来の社会においてマイクロプロセッサをはじめとした半導体が非常に多く使われるようになり、その量は現在の1,000倍、1万倍、10万倍という規模でくる、このような都市を私は電腦都市というように象徴的に呼んでおりますが、そのような社会の基礎作りをする研究を中心としております。

このプロジェクトで最終的に目指しているのはマイクロコンピュータや半導体であふれた電腦都市であり、このようなシステムを超機能分散システム(HFDS:Highly Functional Distributed System)と呼んでおります。多くの機能システムがネットワークでつながれ相互に協調動作をする従来にはなかったタイプのシステムであります。そのために何をやり何をやってはいけないのかという哲学、理念を決め、それを技術開発項目にブレークダウンし、そして開発に着手するというきわめて用意周到、時間はかかりますがきわめて正当的な努力を日夜続けているわけです。

私どものプロジェクトではまず未来のコンピュータがどのようなものに使えるのかという応用分析を行い、その結果から基本的なコンピュータシステムの要素であるオペレーティングシステム並びにマイクロプロセッサへの要求を引きだし、それを実際に作りあげるというようなことを進めております。そして、このマイクロプロセッサに相当する部分でもトロン仕様チップというきわめて未来思考の強力なマイクロプロセッサの研究開発を行っております。三菱電機株式会社におかれましても私のトロンプロジェクトに全面的に賛同、参画をしてくださいり、特に半導体事業部におかれましてはトロン仕様チップGMICRO/100の研究開発製造を通して、プロジェクトに貢献していただいております。

このGMICRO/100はまさに未来のコンピュータシステムについての私の考えをダイレクトに表わした半導体であり、ソフトウェアとハードウェアのバランスのとれたトータルアーキテクチャのコアとして考えられています。ソフトウェアの生産性をあげるためにハードウェアだけを分離して考えるのではなく、オペレーティングシステムやコンパイラとハードウェアをトータルなシステムとして考え、最適化しているというようにユニークなフィーチャがあります。

ところで現在の国際的な関係における日本の位置付けを考えるにおいて今ほど日本の世界への貢献が望まれている時もありません。トロンプロジェクトでは国際協力ということを全面に打ち出し、日本のリスクにおいて将来の技術展開に重要な技術をいち早く先取り的に研究開発し、その成果を世界中にオープンするというオープンアーキテクチャ・ポリシィに基づき運営しておりますが、三菱電機株式会社におかれましてもその趣旨をご理解いただき、多大の協力をいただいております。

現在日本が世界に対して与える影響はきわめて大きくなってきております。そのような影響力の増大とともにいくつかの誤解も起っているようですが、世界に与えるスケールの大きさから考えていましたかたないことかもしれません。しかしながら、我々は努力を続ける必要があります。分かった目標に対して短期に勝負するというパターンではなく、目的は非常に明確であるが、その目的達成にあたってきわめて大きな困難が予想されるような長期レンジの努力が必要なものに対しても、自らのリスクで積極的に解決にあたっていく必要があります。三菱電機株式会社におかれましても90年代、21世紀の世界に向かい、このような現在の国際情勢並びに複雑度を増す半導体界において、世界に対しての貢献、ひいては人類の未来のためへの努力を今後とも続けられることを願い、簡単ですが、私のお祝いの言葉とさせていただきます。

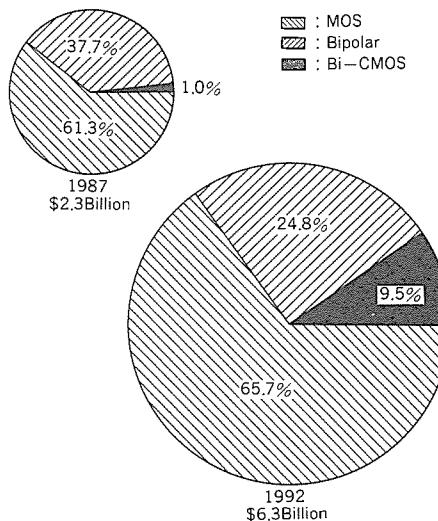

# 三菱電機半導体技術30年の歩み

小宮啓義\*

## 1. まえがき

1945年にショックレイ等により点接触型トランジスタが発明されてからはや40年以上が過ぎ、半導体は今やあらゆる分野に浸透して、産業の火と呼ばれるまでに発展した。

三菱電機の半導体は、1950年代前半に研究所においてゲルマニウムの材料研究を開始したことから端を発する。その後ゲルマニウムトランジスタ／ダイオード、シリコン電力用ダイオード等が試作・製造され、更にシリコンサイリスタ、シリコントランジスタへと発展していった。そしてこれらを量産するために1960年に半導体工場として北伊丹工場が完成し、半導体事業の本格的口火を切った。一方、1961年にシリコンチップ上にトランジスタ、抵抗、コンデンサ等を一体化した“モレクトロン”を完成した。この技術は、現在のプレーナ技術によるモノリシックICと異なってはいるが、一個のチップ上に異なる素子を集積し一つの回路を構成した点では本邦初のICということができる。ICはこの後バイポーラリニア、TTLと進み、1970年前後からはAIゲートP-MOSによる電卓用ICの生産が始まっている。

III-V族化合物半導体では1963年に国内で初めて液体窒素温度でのGaAsレーザの発振に成功、1970年代にはAlGaAs/GaAsダブルヘテロ接合による室温連続発振を実現して世界に大きなインパクトを与えた。一方マイクロ波素子は、1966年のガンドライオードの開発に始まって、1970年にかけてGaAsインパットダイオード、GaAsFETへと展開している。

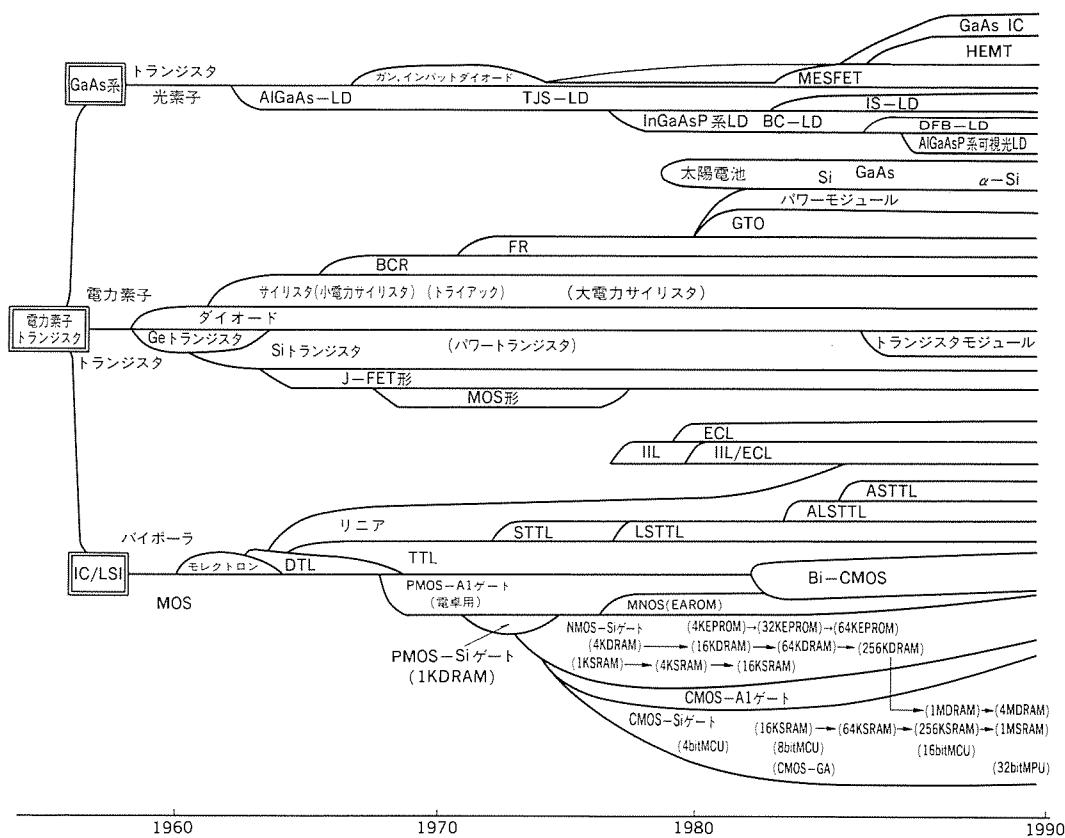

以上のように始まった三菱電機の半導体は、その後幾多のう(紆余曲折を経ながら)発展し、現在のような多くの品種を擁するに至った。その様子を図1に示す。また、このような品種の発展は、その基礎となる多種類の製造技術、設計技術及び周辺技術の進歩に支えられている。本稿は、半導体事業30周年記念特集号を組むに当たり、各品種及び技術の変遷を概観したものである。

## 2. シリコンデバイス

### 2.1 メモリ

メモリは1972年のシリコンゲートP-MOSによる1KビットDRAMの開発に始まる。その後DRAMはN-MOSによる4Kビットから16Kビットへと進み、64Kビットにおいて大きくシェアを伸ばした。更に256KビットからCMOSによる1Mビットへと順調にシェアを拡大し1Mビットの量産化に成功し1Mビットでは世界第二位の地位を占めるに至った。現在は4Mビットの量産化に成功し16Mビットに開発の主体が移り更には64Mビットを目指した研究・開発が進んでいる。この辺の状況の一端を論文“最先端DRAMプロセス技術”及び“4MビットダイナミックRAM”でかいま見ることができる。

また、256KビットDRAMの時代からASIC化の動きが進み、その最初である256KビットデュアルポートRAMは1986年度のR&D

100賞を受賞している。論文“1MビットデュアルポートRAM”に述べた製品はその次世代であり、また、“ディジタルPPC用5KバイトFIFO/LIFOメモリIC”もASICメモリの一つである。

一方、SRAMは1970年代前半にN-MOSによる1Kビットを製品化したのが起点であり、64Kビットの時代にCMOSとなり、現在1Mビットの中速版及び高速版まで製品化が進んでいる。論文“高速1MビットCMOSスタティックRAM”はSRAMの最先端製品を紹介したものである。また、SRAMそのものではないが、4個の1MビットDRAMとワンチップ化したコントローラを高密度実装した4Mビット疑似SRAMが、論文“4MビットP<sup>2</sup>SRAMモジュールの開発と応用”に述べられている。

EPROMについては、1975年の2Kビットの開発に始まり、256KビットからCMOS版が加わり、現在2Mビットまで製品化されている。また、1980年代前半に64Kビットを製品化したEEPROMは現在1Mビットまで到達しているが、これを紹介したのが論文“5V単一電源で動作する高速1M EEPROM”である。さらに、今後は、フラッシュEEPROMの開発にも注力する計画である。

メモリは今後とも、高集積化と高速化が進むであろう。また、ASSP(Application Specified Standard Product)としてのASICメモリの種類も増加すると考えられ、これらがメモリの今後の指向である。

### 2.2 マイコン

当社のマイコンは、当初インテル系8ビットMPUで出発したが、1978年に最初のオリジナル4ビットMCU M58840を完成させてから次第に中心をオリジナルMCUに置くようになった。1982年に開発したオリジナル8ビットMCU M50740では、微細化されたCMOSプロセスを採用し、これをコアに専用MCU MELPS740シリーズを発展させ、CMOS4ビットMCUシリーズと合わせて、民生、OA分野を中心に大きく成長し、この製品分野においてトップグループの座を得るに至っている。

さらに、現在は、斬新なアーキテクチャと1.3μmCMOSプロセスを用いた高機能の16ビットMCU MELPS7700シリーズの展開を推進中である。このシリーズは、高速化、内蔵メモリの大容量化、種々の周辺機能の搭載等により広く産業分野へ対応でき、OA、自動車、FA等の分野を中心に展開してきている。今回収録した“自動車用16ビットワンチップマイコン”“DMAコントローラ内蔵・高性能16ビットワンチップマイコン”の2編の論文は、それらを紹介したものである。

一方、TRON仕様に基づく汎用32ビットMPUに関しては、複数同業者との開発協業の中で、3種類のMPUと周辺LSI群を開発中である。当社で開発したM32/100は、最先端CMOSプロセス技術と多段パイプライン制御等の高度な計算機技術を駆使した7MIPSの性能を有する製品であり、これからは産業用分野に最適である。高度な開発環境やリアルタイムOSも開発した。“TRON仕様32ビットマイクロプロセッサM32/100”“M32用μITRON仕様OS：MR3200と開

図1. 当社の半導体デバイス及び製造技術の変遷

発環境”の2編の論文は、これらの一端を紹介したものである。

今後マイコンは、MPU、MCU共に、微細化技術の進展による高速化と高集積化をベースにして、一層の高性能・高機能化製品群を実現し、かかる後、MPUについては、複数のオンチップ・マルチプロセッサによる並列処理や64ビットアーキテクチャへと進展していくであろう。今後の展開でもう一つ重要なのは、多様化への対応である。16ビットMCU MELPS7700シリーズはもともとこれを意図して作られたものであるが、TRON仕様32ビットMPUにおいてもM32ファミリーを標準アーキテクチャとし、各種応用分野に特化した周辺機能のオンチップ化等、さまざまな展開が期待できる。

### 2.3 ASIC

当社のゲートアレーは、当初社内向けとして開発に着手し、1977年に144ゲートECLゲートアレーと920ゲートN-MOSゲートアレー及びその設計用CADシステムを開発したのに始まる。MOSゲートアレーは後にCMOS構造に切り替え、1982年に当社独自のゲートアイソレーション方式で、2.6kゲートを開発、その後外販を開始するとともに高集積化、ROM/RAM内蔵、ゲート敷きつめ方式などの開発を経て現在、0.8μmCMOS技術による400kゲートCMOSゲートアレーの開発を進めている。論文“高速、低消費電力の1.0μmCMOSゲートアレーM60050シリーズ”は、顧客要求にこたえるべく低消費電力化を最重視した15Kゲート／25Kゲート／35KゲートのCMOSゲートアレーシリーズを紹介している。

また、セルベース方式については、1.3μm及び1.0μmCMOSセルベース方式用統合CADシステムの開発を完了し、鋭意セルライブラリの充実に努めるとともに、各種ロジックLSIの設計に活用して開発期間の短縮と設計の質の向上を実現している。次に述べるASSPのうちの二品種もこのセルベースシステムを用いて設計したもので

ある。

ASSPは専用標準LSIとも呼ばれ、特定用途向けの複数ユーザーを対象とした製品として位置付けられる。この種LSIの価値の指標は性能(機能)/コストであるが、ASSPではこれをセミカスタムLSIより高くすることができます。これは、ASSPがメーカー主導の設計であることから、最先端プロセスの使用と同時に最先端CADツールによる自動化設計とベテラン設計者による人手設計とを組み合わせた最適化設計が可能のことによる。また、複数ユーザーの使用に供することによる量産効果も、コストダウンに寄与する。

本特集号では、ASSPの画像及び映像処理分野での開発事例の中から、画像処理に対してアーキテクチャの最適化を図った“24ビット、50ns画像／映像処理用シグナルプロセッサ(DISPP)”，LSIパーティショニングによる性能の最適化を図った“MUSE／NTSCコンバータ用LSI”及びアナログ／ディジタル混在による高集積化を図った“静止画テレビ電話機用モジュールLSI”的3件の論文を掲載した。

### 2.4 カード

ICを搭載したカードにはマイコンカードとメモリカードの二種類があるが、当社は両カードとも半導体の先端応用製品として位置付け1984年から積極的な開発を進めてきた。このうち各種メモリICを複数個搭載するメモリカードは1985年の発表を皮切りに、1987年には世界最大容量カードとして512KバイトSRAMカードを、続いて1988年には、これまた世界最大容量の2MバイトOTPカードを完成させている。

これら当社大容量メモリカードは、①最先端メモリICの搭載、②カード専用の周辺ICの開発と導入、③カード用に開発した超薄形プラスチックモールドパッケージの全面採用、の三点を統合した最先端半導体応用製品であり、論文“三菱大容量メモリカード”はその一端を紹介したものである。

### 2.5 パワーモジュール

パワーデバイスは、高耐圧化、大容量化、高速化の歴史をたどってきたが、一方で複数のパワーデバイスあるいはパワーデバイスとコントロールチップを一体化してアセンブルするモジュール化の動きも盛んである。当社では、1978年のダイオード及びサイリスタモジュールを開発・製品化して以来、各種のパワーデバイスを組み合わせた新製品を開発し、電力変換装置の小型・軽量化に著しく貢献してきた。これらのパワーデバイスは、高耐圧・大容量及び高周波

化とともに、現在、高集積化、高機能化の方向に進んでおり、これに対応して、当社は、1989年にパワーICモジュールを発表した。論文“インバータ用パワーICモジュール”は、これを紹介したものである。

### 3. 化合物半導体製品

#### 3.1 光 素 子

半導体レーザについては、初期の研究・開発の後、1982年以降事業化に注力し、世界に先駆けて $0.78\mu\text{m}$ CD用レーザの量産化に成功、CD生産の急激な立ち上りに貢献してきた。最近では、論文“光通信用 $1.5\mu\text{m}$ 帯MQW-DFBレーザ”で紹介している量子井戸活性層と埋め込み型の新しい回折共振器を持つ素子の開発に見られるような低しきい値、高出力、狭スペクトルなどの特徴を持つ高性能光通信用 $1.3/1.55\mu\text{m}$ レーザをはじめ、光ディスク用高出力レーザ、可視光レーザ、加入者系通信用の直線性の優れた低雑音レーザ等の開発に注力するとともに、将来のコヒーレント通信用波長チューナブルレーザ、OEIC等の開発も進めている。

#### 3.2 マイクロ波素子

マイクロ波素子の開発方向は、いまでもなく低雑音化、高速化、低消費電力化、高出力化である。III-V族半導体を用いたマイクロ波素子のうち、個別素子の中心は、従来、MESFETであったが、1980年代に入って、より低雑音、高速が期待できるHEMTを実用化し、今日に至っている。論文“超低雑音HEMT”はその最先端デバイスの紹介である。

一方、マイクロ波素子においても集積化(MMIC)は必ず(須)の流れであり、当社においては1980年代後半から実用化を始めている。その中で、低雑音化を中心にして紹介したのが、論文“超低雑音GaAs SAMFETの開発とMMICへの応用”である。このほか、Source Island Via-hole FETを用いた高出力増幅器、デジタルICでは1989年度のR&D100賞を受賞したプリスケーラ等がある。

### 4. 製 造 技 術

#### 4.1 シミュレーション技術

シミュレーション技術は、CAD技術の一環であるが、当社でも、論理シミュレーションからプロセスシミュレーションに至る一連の各種シミュレータを開発、実用化し、LSIの設計・開発の大幅な期間短縮及び効率化を実現している。これらのシミュレータのうち、トランジスタの構造と外部電圧を与えて、その電気特性を計算するデバイスシミュレータとプロセス条件を設定して加工後の形状や不純物分布を求めるプロセスシミュレータが、近年のデバイス構造の微細化と複雑化に伴って急速に重要度を増している。

デバイスシミュレーションやプロセスシミュレーションにおいて重要なのは、物理的、化学的現像をいかにモデル化するかということであり、その良し悪しによって、実用的な計算時間内に必要な精度のシミュレーションができるかどうかが決まると言つてもよい。論文“三次元形状シミュレータ”は、そのようなモデル化の一例として、従来のストリングモデルとは全く異なった、拡散現像をヒントにした新しいエッティングモデルを考案採用した形状シミュレータについて述べたものである。このモデルにより、三次元化が困難であった形状シミュレーションを一挙に三次元化することが可能となつた。

#### 4.2 ウェーハプロセス技術

ウェーハプロセス技術の中の最も基本的なものの一つは写真製版技術である。初期には、コンタクト又はプロキシミティ露光が用いられたが、1970年代後半から反射投影露光技術を導入し、64K DRAMの量産に用いた。さらに1980年代前半の256K DRAMの量産からはg線ウェーハステッパーを用い、その後レンズの改良が行われ、現在 $0.8\mu\text{m}$ パターンを用いた4M DRAMの量産に至っている。更に今後のパターン微細化のためにi線ステッパー及びエキシマステッパーを導入しつつあり、その先の技術としてX線露光や電子線直接描画の研究を行つていている。

一方、微細加工技術のもう一つの要素であるエッティング技術については、1971年のプラズマアッキング技術のIC製造プロセスへの導入成功に始まり、 $\text{Si}_3\text{N}_4$ 膜及びポリSi膜のプラズマエッティング技術の導入と、世界の先陣をきつてエッティングのドライ化を進めてきた。その後、平行平板型プラズマエッティング、RIE、と進み、さらに、磁場強化型RIE、ECRプラズマエッティング等と高精度エッティングのための工夫がなされている。論文“超微細加工プロセス技術”は、これららの技術の研究・開発の一端を紹介したものである。

当社のイオン注入技術は、1970年前後に研究・開発を開始し、1975年前後から量産に導入、N-MOS及びCMOSの本格的量産を可能にした。その後、不純物濃度及び深さの制御性の良さにより広い範囲で使用してきている。最近では、高集積化に伴つてイオン注入の方向性が問題になってきており、トレンチ技術に関してこの方向性の問題を解決し、また、トランジスタの微細化のために方向性を利用すべく開発したのが、論文“斜め回転イオン注入技術”である。

半導体ウェーハの洗浄は、有機溶剤や酸等の薬液と純水を用いて行われるが、表面に付着した微粒子やCVD異常成長粒子等の除去には、通常ブラシスクラバが用いられている。しかし、パターンが小さくなり、問題となる異物の粒径が小さくなつくると、ブラシスクラバはその有効性が問題になるとともに損傷の原因にもなる。これを解決する目的で開発したのが、論文“アイスクラバ洗浄”で紹介した氷の微粒子を吹き付けて洗浄するユニークな技術であり、今後、半導体ウェーハの洗浄だけでなく、多方面への応用が期待されている。

#### 4.3 FA技術

半導体の製造工程は、1960年代後半から、急速に個々の製造装置についての自動化が進み、また、これに並行して、各種の生産管理情報を電算機で処理する生産管理情報システムの構築も進んできた。

これらを背景として、当社ではLSI工場全体の一貫自動化技術の開発を進め1984年に西条工場のLSI全自動化一貫生産ラインを完成了。このラインは世界最初のFA化LSI工場として高く評価され、その高生産性及び製品の高品質とあいまつて多くの重要顧客からお褒めの言葉を頂くとともに、1987年度には大河内賞を授与された。

この経験をベースに、以後に建設された当社の製造ラインは、すべてFA化を基本としており、西条工場第二棟、高知工場第一、第二ラインと進むに従つて、FA化技術も高効率化、Flexible化の方向で急速に進歩を続けている。論文“半導体のFA技術”は、これらの状況を紹介したものである。

### 5. む す び

本稿は、今回の特集号に採録した論文に関連した品種及び技術についてその概要を述べたため、すべての品種を網羅していないが、三菱電機の半導体技術の流れを理解する上で参考となれば幸である。

# 最先端DRAMプロセス技術

佐藤真一\*

若宮 亘\*\*

重富 晃\*\*

## 1. まえがき

0.5μmルールULSIを代表する16M DRAMは、いよいよ本格的な製品開発の段階を迎え、キャパシタ、素子分離、配線などメモリセルを中心としたプロセス技術開発が鋭意展開中である。さらには、クオータミクロンプロセス要素技術への取組も活発に行われており、64M DRAMをにらんだメモリセル構造も提案され始めている。一方、素子の高集積化に伴いフォトマスク作成技術も一段と高性能化が進んでおり、特に電子ビーム描画用データの増大に対応した短時間で精度の良いレティカル作成技術は、ULSI技術のかなめ(要)となってきている。

本稿では、16M及び64M DRAMに向けて開発中のメモリセル構造及びそのプロセス技術と最新のマスク作成技術についてその一端を紹介する。

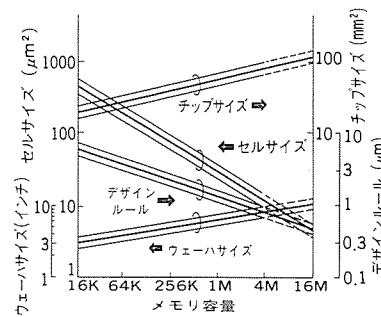

## 2. DRAMプロセス技術の動向

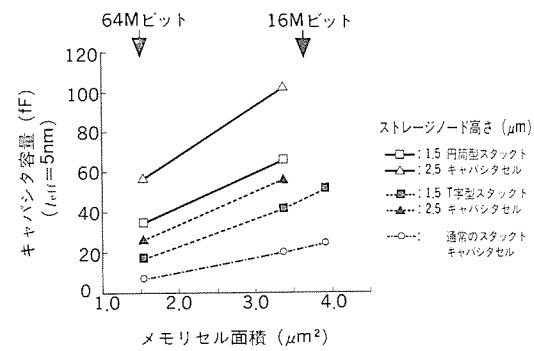

図1にDRAMの微細化トレンドを示す。DRAMの中心を占めるメモリセル1ビットの基本構成は、16K以降シンプルな1素子型セル（1トランジスタ+1キャパシタセルとも呼ばれる）を踏襲しており、比例縮小則に従った微細化へのたゆまぬ努力の結果、ほぼ一定の比率(30~40%)で縮小されてきた。その結果、今日みられるDRAMの高密度・高集積化を達成している。この微細化トレンドは、種々の技術動向から当分続くと予想され、16Mのメモリセル面積は約4μm<sup>2</sup>、64Mでは実に1.5μm<sup>2</sup>という微小な値が想定される。その結果、ソフトエラーやホットエレクトロン効果あるいはエレクトロマイグレーションといった信頼性上の課題に加えて物理的限界そのものにかかる問題の出現が予想され、デバイス構造やプロセス技術、材料面での新規なアイデアとそれに基づくアプローチが強く求められる。特にメモリセルの核を成すキャパシタは、α線の影響や電源等からの雑音に対して回路動作を保証するために、30フェムトファラッド(fF)以上の十分な蓄積容量の確保が必要であり、4M DRAM以降その三次元構造化が不可欠になるなどDRAM開発の要となっている。

現在、三次元キャパシタは、スタック型及びトレンチ型の2派に分かれて各社実用化が進んでいるが、微小なセル面積に大きな蓄積容量を確保するためにはスタックはより高く、トレンチはより深くといったキャパシタ電極の側面利用効果を一段と突き詰める必要がある。各社16M DRAMでは、4Mで実用化されたスタックトキャパシタ構造<sup>(1)</sup>を踏襲しており、蓄積容量を増大させるため種々の改良を加えてきた。以下、新規なスタックトキャパシタ構造をめぐる16M及び64M DRAMプロセス技術の現状を紹介する。

## 3. 16M及び64M DRAMプロセス技術

### 3.1 16M DRAMメモリセル技術

約4μm<sup>2</sup>という微小なセル面積の中にスタックトキャパシタセル

を実現するに当たり、更に次のような改良点を加えた<sup>(2)</sup>。

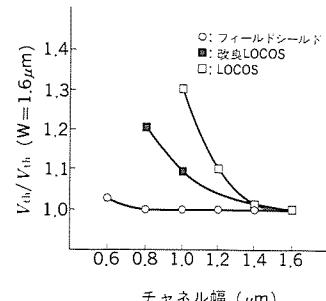

- (1) 分離方法として従来のLOCOS系分離に代わり、フィールドシールド分離を採用して分離領域を縮小するとともに狭チャネル効果を抑えた。

- (2) アスペクト比の高いコンタクトホールに対して、安定した電気的接続をとるため、選択CVDタンクステンによる穴埋め技術を導入した。

- (3) キャパシタ構造として各社独自のT字型スタックトキャパシタを採用し、微小セル面積においても十分なキャパシタ容量を確保するとともに、断差部での電極パターンの加工という従来の問題点を解消することを可能とした。以下これらの3点について順次詳述する。

#### 3.1.1 素子分離技術

素子分離領域の縮小化という問題を解消するためにトレンチ分離を始め幾つかの提案がなされてきたが、プロセスの複雑さ、信頼性上の問題からLOCOS法にとって代わるまでには至らず、プロセスの改良によってバーズピークの伸びを抑えた改良LOCOS法がDRAMの素子分離としてこれまで使用してきた。しかしながら、チャネル幅がサブミクロンレベルの16M DRAMでは、バーズピークもさることながら狭チャネルに対する対策がより重要となり、チャネルカットのために高濃度の不純物層を直下にかかるLOCOS法では狭チャネル効果の問題が顕在化していく。

今回16M DRAMに適用したフィールドシールド分離は、基本的にトランジスタ分離の一環で、LOCOS法のような高濃度層を必要とせず、図2に示すようにチャネル幅0.6μmまで狭チャネル効果を抑

図1. DRAMの微細化トレンド

図2. 狹チャネル効果

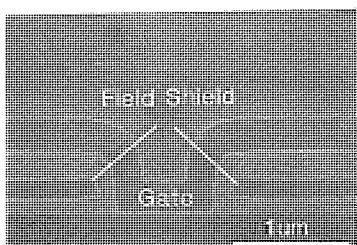

図3. フィールドシールド分離トランジスタの断面

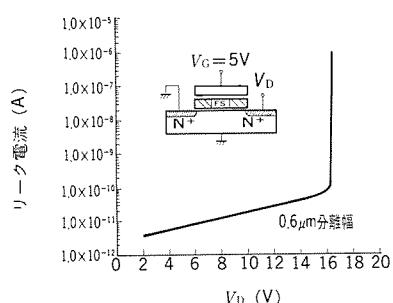

図4. フィールドシールド寄生トランジスタのリーク電流

図5. n<sup>+</sup>-p接合のリーク電流

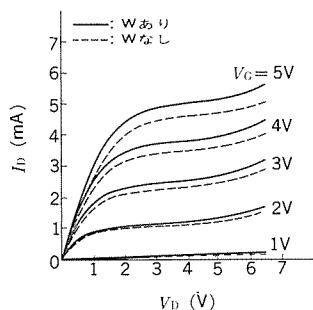

図6. タングステン ソース／ドレイントランジスタのI-V特性

制することができる。構造的には図3に示すように、ゲート酸化膜とゲート電極及びこれらを被覆している絶縁層から成り、通常のサイドウォール付きトランジスタと同じ形状を持ち、プロセス的にも従来技術がそのまま利用できる。また、LOCOS法のように厚い酸化膜のストレスに起因した結晶欠陥の発生がないため、リフレッシュ特性の向上等が期待できる。フィールドシールド分離のゲート電極を保護するサイドウォールの直下にはn<sup>+</sup>層がなく、オフセットゲート構造になっており、フィールドシールド寄生トランジスタのV<sub>th</sub>を高める効果がある。また、図4に示すように寄生トランジスタのソース／ドレイン間リーク電流もドレイン電圧16Vまで低く抑えられており、分離領域を0.6μmまで縮小することができた。

### 3.1.2 高アスペクト比コンタクトホール形成技術

スタックトキャパシタは、素子分離領域及びワード線の段差を利用

してキャパシタ面積を増大させようとするものであるから、特にキャパシタ領域形成後のデバイス表面の凹凸は必然的に激しくなる。このような凹凸の上にピット線あるいはアルミ配線を精度良く形成するためには、これらの配線の下を極力平坦にしておく必要がある。そうすると、今度は特に凹部に形成すべきコンタクトの層間絶縁膜が厚くなり、アスペクト比（層間絶縁膜厚／コンタクト径）が大きくなってしまう、上部配線材料が被覆できずコンタクトがとれないという問題が生じる。

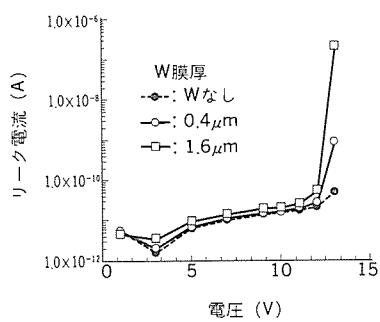

この問題を解決するための有効な方法の一つとして、コンタクトホールを導電材料で埋め込んでしまう穴埋め技術がある。この方法によればアスペクト比の大きなコンタクトでも確実に電気的接続がとれ、かつコンタクト上部が平坦にできるという特徴がある。コンタクトを埋める導電材料は幾つかあるが、16M DRAMでは選択CVDタングステン膜による穴埋め技術を導入した。この構造をとることにより、同時にトランジスタのソース／ドレイン領域にもタングステン膜が張り付けられることになり、トランジスタ特性の向上も期待できる。

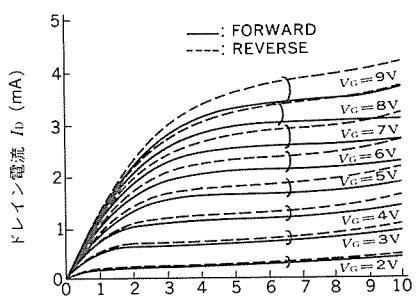

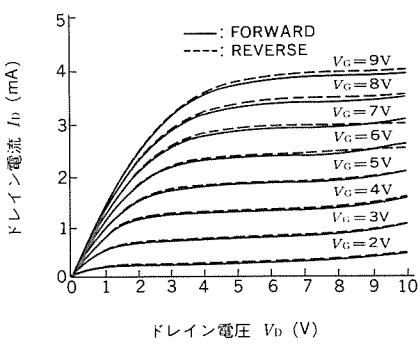

選択CVDタングステンの形成方法としては、当社独自のWF<sub>6</sub>のSiH<sub>4</sub>による還元法を用い、タングステン膜下の接合リーク電流を低減させた。図5はn<sup>+</sup>-p接合上に0.4μmと1.6μm厚のタングステンを形成した時の接合リーク電流を示したもので、いずれの膜厚でもリファレンスとして示した従来のアルミコンタクトと同程度の低い値を示している。この選択CVDタングステン膜を、直接ソース／ドレイン領域に成長させたLDDトランジスタのI-V特性を図6に示す。このトランジスタはnMOSトランジスタで、ゲート長は0.5μm、チャネル幅は10μm、またタングステン膜とゲート電極とは0.15μmのサイドウォールで分離されている。この場合のタングステン膜厚は0.15μmである。図には比較のためタングステン膜のない同一サイズのLDDトランジスタのI-V特性も示してある。図から明らかのように、ソース／ドレイン領域に直接タングステン膜を張り付けることによって電流駆動能力が上がる。

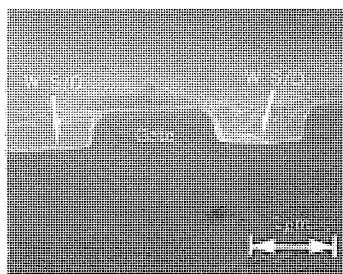

上記の例はタングステン膜が比較的薄い場合であるが、図7にはトランジスタのソース／ドレイン領域により厚くタングステン膜を成長させた場合の断面SEM写真を示す。この時のタングステン膜厚は、約0.4μmである。写真から分かるように、タングステン膜を厚く成長させた場合でも横方向への浸食(Encroachment)や虫食い(Wormhole)などの現象は見られず、かつ平坦な構造が得られている。

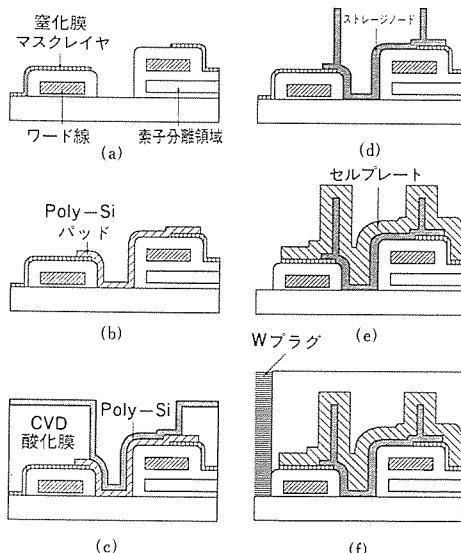

### 3.1.3 キャパシタ構造

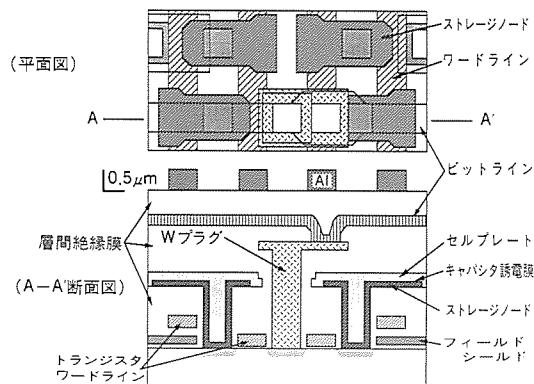

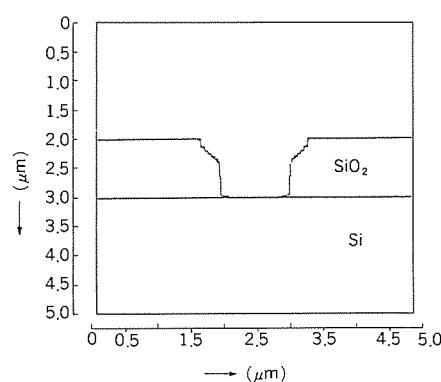

下地の段差を利用してキャパシタ面積を拡大させているスタックトキャパシタでは、その段差ゆえに電極パターンの形成に負担がかかる。特に下部電極のストレージノードは、その側壁部分もキャパシタとして利用できるため膜厚を厚くする傾向にあり、加工上最大の難関の一つである。そのため16M DRAMでは図8に示すように、ストレージノードの下に比較的厚い層間絶縁膜を堆積して更にその表面を平坦にし、開口部を形成してトレーニチ状のストレージノード(T字型スタックトキャパシタ)とした。このように、平坦な層間絶縁膜を形成することにより、ストレージノードの加工を含めそれ以後の各パターン形成が非常に容易となつた。

また、層間絶縁膜の膜厚を厚くすることによって容易にキャパシタ面積を増大させることができ、例えば誘電膜として酸化膜換算で6 nmの窒化膜／酸化膜の複合膜を使った場合、35fFの容量を確保す

図7. タンクステン ソース／ドレイン トランジスタの断面

図8. T字型スタックトキャパシタセルの概念図

図9. 円筒型スタックトキャパシタセルの概念図

図10. 円筒型スタックトキャパシタセルの製造フロー概略

することができる。このような構造をとった場合、メモリセル内ではビット線コンタクトのアスペクト比が非常に大きくなるが、それに対しては前述の選択CVDタンクステンで埋め込むことにより、ビット線との電気的接続を容易にとることができる。

以上のように、フィールドシールド分離によって分離領域を縮小

することができ、T字型スタックトキャパシタと選択CVDタンクステンによるコンタクト穴埋め技術を組み合わせることにより、微小なメモリセルでも十分なキャパシタ容量を確保することが可能となつた。

### 3.2 64M DRAMメモリセル技術

#### 3.2.1 メモリセル構造と特徴

上記のT字型スタックトキャパシタセルを更に微小なメモリセルに適用する場合、一般的にトレンチ型のキャパシタ構造が持つ本質的な問題、すなわちトレンチ開口部の縮小に伴う側壁面積の減少という問題に直面する。本来のトレンチセルの場合には、トレンチ深さを深くしてキャパシタ面積の減少を防ぐこともできるが、T字型キャパシタセルの場合ストレージノードを無制限に上方に伸ばすことはできない。

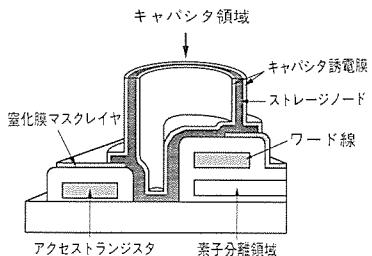

この問題を解決するために、T字型スタックトキャパシタの発展型として、図9に示すようなキャパシタ構造を開発した<sup>(3)</sup>。構造的には、T字型スタックトキャパシタの外側の層間絶縁膜が除去された形になっており、円筒型ストレージノードの内壁部、外壁部、及び底面部のすべてがキャパシタ領域として利用できる。したがって、ストレージノードの高さが同じならば、T字型スタックトキャパシタセルの2倍以上のキャパシタ面積が得られる。また、ストレージノードの表面がすべて露出しているため、ストレージノードへの不純物導入が、例えばトレンチ型キャパシタセルの場合に比べて非常に容易である。

#### 3.2.2 プロセス技術

この円筒型キャパシタセルを実現するためのプロセスについて、図10の製造フローに基づいて概説する。

- (1) 素子分離領域及びアクセストランジスタ／ワード線形成後（これらの側壁は自己整合的にサイドウォールで保護されている），シリコン窒化膜を堆積し、通常のリソグラフィ法でストレージノードのコンタクト部分の窒化膜を除去する。この窒化膜は、後で層間絶縁膜の酸化膜をウェット法で除去するときの下層レイヤ（素子分離領域、ワード線）に対するマスクとなる。

- (2) 今開口したストレージノードのコンタクト部分を被覆し、窒化膜マスクレイヤに一部オーバラップするように多結晶シリコンのパッドレイヤを形成する。続いてイオン注入法で、Asをパッドレイヤに導入する。この多結晶シリコンのパッドレイヤは、後で形成するストレージノードの一部（底面部）となる。

- (3) 次に全面に厚い層間絶縁膜（酸化膜）を堆積し、その表面を平坦化する。この時点で層間絶縁膜を完全に平坦にしておくことが、この製造フローの一つのポイントである。平坦化するためには幾つかの方法があるが、従来のBPSG、リフロー法でも容易に平坦な構造が得られる。この層間絶縁膜の膜厚によってもキャパシタ容量を調整（拡大）することができる。

- (4) ストレージノードを形成する部分にコンタクトホールを開口し、続いて多結晶シリコンを堆積する。次に、RIE等の異方性エッティングによって多結晶シリコンの全面エッティングを行う。その結果、平坦な層間絶縁膜上の多結晶シリコン及びコンタクトホール底部の平坦部の多結晶シリコンが除去され、コンタクトホール側壁部の多結晶シリコンは残る。コンタクトホールの底部には以前に形成した多結晶シリコンのパッドレイヤが残っており、側壁部の多結晶シリコンと合わせてストレージノードを形成する。

- (5) 層間絶縁膜の酸化膜をウェットエッティングによって除去するこ

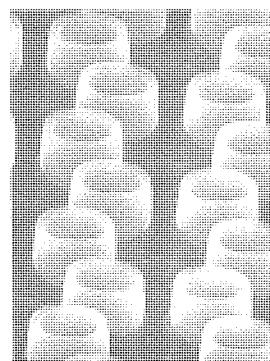

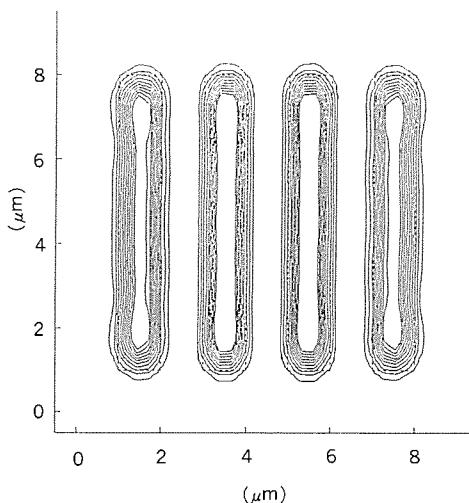

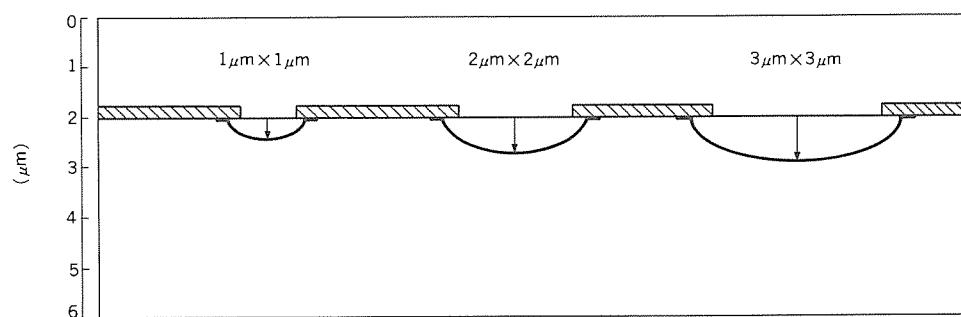

とにより円筒型のストレージノードが形成される。酸化膜をウエットエッチングの間、素子分離領域、ワード線は以前に形成した窒化膜マスクレイヤ及び多結晶シリコンのパッドレイヤによって保護されている。図11はこの段階でのメモリセル部のSEM写真である。この場合の円筒型ストレージノードは、外径 $1.5\mu\text{m}$ 、高さ約 $1.5\mu\text{m}$ である。

(6) ストレージノードにイオン注入法によりAsを導入する。続くキャパシタ誘電膜（窒化膜／酸化膜の複合膜）及びセルプレートの形成は、従来のスタックトキャパシタセルの場合と同様である。高アスペクト比のビット線コントラクトに対しては、T字型スタックトキャパシタセルの場合と同様、選択CVD法によってタンクステンプラグを形成する。

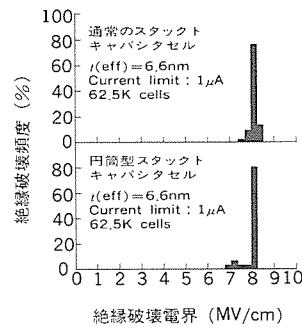

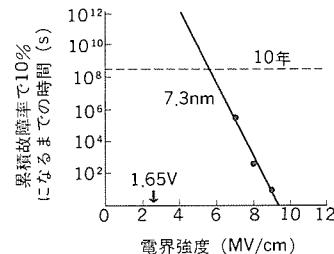

以上のように、円筒型キャパシタの製造フローは基本的にT字型スタックトキャパシタの場合と変わらず、窒化膜マスクレイヤを形成する工程が一回増えるだけである。この製造フローでは、キャパシタ誘電膜がその上部に形成されるストレージノードの一部が直接RIEの照射を受けるが、図12及び図13に示すように円筒型キャパシタ上の誘電膜の特性は、初期耐圧の点でも従来のスタックトキャパシタの場合と有意差なく、TDDBから予測される寿命も実使用上十分である。また、ストレージノードパターンが全面エッチングによって形成できるため、加工に対する負荷が大幅に軽減される。

### 3.2.3 今後の展望

図14は種々のメモリセル面積に対して、T字型スタックトキャパシタ及び円筒型スタックトキャパシタ容量を、ストレージノードの高さをパラメータとして見積もったものである。約 $4\mu\text{m}^2$ のメモリセルは16M DRAM、 $1.5\mu\text{m}^2$ は64M DRAMで予想されるメモリセル面積である。図から分かるようにT字型スタックトキャパシタセルの場合、 $1.5\mu\text{m}^2$ というメモリセルの中で十分な容量を得ようとすると $3\mu\text{m}$ 近いストレージノード高さが必要となる。それに対して、円筒型スタックトキャパシタセルでは、その半分以下のストレージノード高さで十分な容量を得ることができる。もちろん、64M DRAMでは、メモリセル構造以外にもブレークスルーしなければならない技術課題は数多くあり、またキャパシタ構造にしても誘電膜の開発次第によつては別の展開も考えられるが、この円筒型スタックトキャパシタセルは、従来技術の延長での一つの可能性を示すものである。

## 4. 16M DRAMマスク技術

LSI製造技術の中心的役割を担っているのは、光転写技術である。4M DRAMの量産が、G線5:1ウェーハステップを使用して始まった。また、16M DRAMの開発も、G線あるいはI線5:1ウェーハステップを使用して活発に行われている。さらに、クオータミクロンリソグラフィをねらったエキシマレーザ技術の開発も盛んである。64M DRAM以降の、いわゆるULSIの製造にどのようなリソグラフィ技術が適用されるのかは、いまだに不透明なところであるが、いずれの技術を使おうとも、フォトマスクが必要なことは言うまでもない。したがって、高品質フォトマスクを短期間で製造することが、デバイスの開発、製造に非常に大きな意味を持ってくる。

本章では、16M DRAM用マスク作成に必須な、可変形電子ビーム描画装置とそのデータ作成方法について述べる。

### 4.1 フォトマスク描画時間

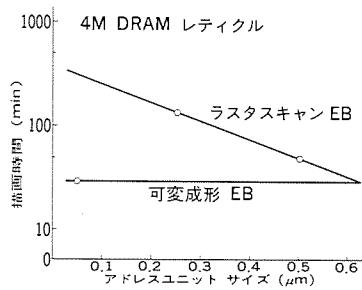

従来、フォトマスクの描画には、ラスタスキャン型電子ビーム描

図11. 円筒型スタックトキャパシタセル

図12. 絶縁破壊電界強度分布

図13. 円筒型スタックトキャパシタセルの誘電膜寿命

図14. メモリセル面積と容量の関係

画装置が使用してきた。16M DRAMの5倍レティクル(LSIパターンを5倍に拡大したフォトマスク)上の最小パターン寸法は、高々 $2.5\mu\text{m}$ 程度であり、これぐらいのパターンは、ラスタスキャン型装置を使っても簡単に形成可能である。しかしながら、このタイプの装置では、16M DRAM用レティクルの描画時間が膨大になり実用的でなくなるという問題が発生する。

一般に、ラスタスキャン型装置でレティクルを描画する場合、アドレスユニットとして $0.5\mu\text{m}$ が用いられる。ところが16M DRAMのように、パターン寸法を非常に厳しく管理しなければならないレティクルを描画するには、 $0.25\mu\text{m}$ アドレスユニットを用いる必要

図15. アドレスユニットに対する4 M DRAM用レティクルの描画時間

図16. 可変成形とラスタスキャン型電子ビーム描画装置による16M DRAM用レティクルの描画時間

図17. データ作成システムの構成

がある。この場合、一枚のレティクルの描画時間は、アドレスユニットの2乗に反比例するため、計算上4倍に膨れ上がる。図15に、アドレスユニットに対するレティクルの描画時間を示す。一例として、4 M DRAMの1レイヤを実験に用いた。ラスタスキャン型装置を用いた場合、描画時間は、0.5μmアドレスユニットの場合50分であったのが、0.25μmアドレスユニットの場合は、140分に增加了。16M DRAMの場合は、更に図形数が増加することを考えると、ラスタスキャン型装置を使ってレティクルを描画することは、スループットの点で大きな問題になることは明らかである。このスループットの問題を解決するために、可変成形電子ビーム描画装置JBX-6 A III<sup>(4)</sup>を用いた。このタイプの装置は、アドレスユニットにかかわらず、描画時間が一定であるという特徴を持っている。実際、図15に示すようにアドレスユニットが0.05μmと非常に小さいにもかかわらず、4 M DRAM用レティクルの描画時間はわずか30分であった。

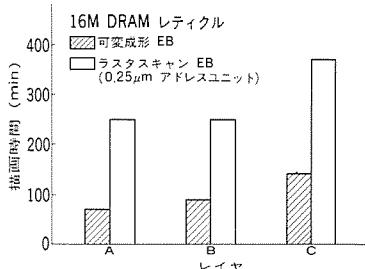

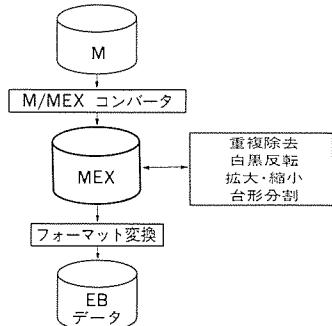

次に、実際に16M DRAM用レティクルを描画した。図16は、JBX-6 A IIIとラスタスキャン型装置を用いた場合の16M DRAMの典型的な3レイヤのレティクルの描画時間を示している。1レイヤ当たりの平均の描画時間は、ラスタスキャン型装置の場合は290分で、可変成形型装置の場合は100分であった。このように可変成形型装置を用いることにより、描画時間を約1/3に短縮することが可能になっ

た。

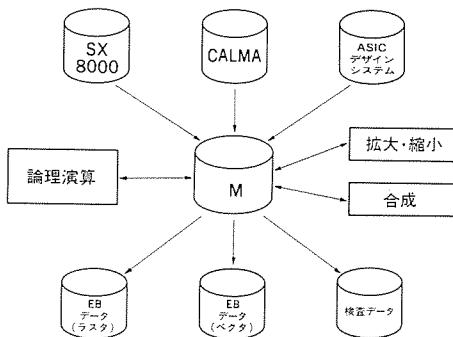

#### 4.2 描画用データ作成

可変成形電子ビーム描画装置は、ラスタスキャン型装置と比べて高速描画が可能であるが、一つだけデメリットがある。それは、描画用データを作成する際に、ラスタスキャン型装置では必要としない図形間の重複除去処理や白黒反転処理といった複雑なデータ処理を必要とするため、データ作成のスループットが非常に低いという点である。この問題を解決するために、新しく可変成形電子ビーム描画装置用のデータ作成システムを開発した。

図17に、当所におけるデータ作成システムの構成を示す<sup>(5)</sup>。このシステムは図に示すように、Mフォーマットと呼ばれる共通の中間ファイルを中心として構成されている。まず各々のCADデータは、Mフォーマットに変換され、次いでこのMフォーマットに対して、論理演算やサイジング、データマージングといった様々な処理が施される。その後、Mフォーマットは希望の電子ビーム描画用データや欠陥検査用データに変換される。このデータ作成システムは、次のようなメリットを持っている。新しく別のタイプのCAD装置や電子ビーム描画装置、欠陥検査装置が導入されても、それらのデータフォーマットとMフォーマットとの間の変換ソフトウェアを開発するだけで、それらの装置用のデータ作成が可能となる。

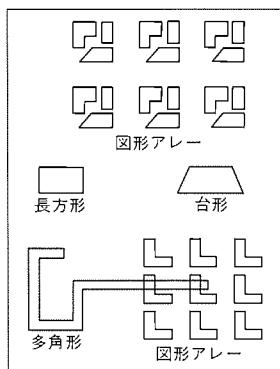

このMフォーマットの構造を、図18に示す。Mフォーマットは、基本図形と図形のアレイ配置からできている。上述したように、可変成形型装置の電子ビーム描画用データを作成するには、重複除去処理や白黒反転処理を施さなければならない。これらの処理には、図形間の相対位置関係を考慮する必要がある。よって、Mフォーマットにこれらの処理を施す場合には、図形のアレイ配置はまず展開され、その後すべての展開された図形に対して処理が施される。この場合、変換時間は非常に長くなり、また、変換後のデータ量も膨大なものとなる。この問題を解決するために、一層の階層構造をもつたMEXフォーマットと呼ばれる中間ファイルを導入した。このフォーマットの構造を図19に示す。この図でユニットとは、一般にCADで用いられるセルに相当し、図形の集合体を意味するが、セルとは違いそれ自身の大きさを持っている。このユニットが、エリアユニット リファレンスと呼ばれる特殊な参照法によって配置されている。すなわち、あるユニットは、他の図形が全く存在しない領域（エリア）に隙間なく配置されている。このユニットが配置されている領域内の図形に対する上述の処理は、一つのユニット内の図形に対してのみ行えばよい。よって、この方法を使えば、DRAMのように、同一のユニットが大量に配置されているデータに対しては非常に有効で、データ作成時間並びに処理後のデータ容量を大幅に減少させることができる。

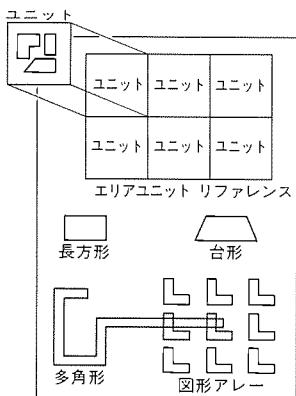

図20に、この新しく開発されたデータ作成システムにおけるデータのフローを示す。Mフォーマットは、まずM-to-MEXコンバータによって、MEXフォーマットに変換される。このMEXフォーマットに対して、階層構造を利用することにより重複除去や白黒反転の処理が行われる。最後に、MEXフォーマットは、可変成形電子ビーム描画用フォーマットに変換される。

#### 4.3 データ作成時間及びデータ量

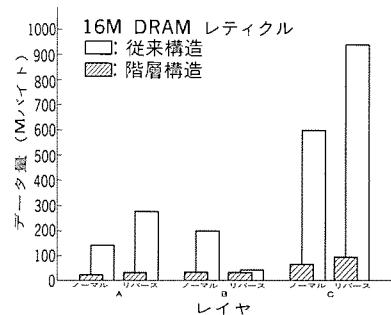

図21に、CADデータから最終的な可変成形電子ビーム描画用データまでの変換時間を示す。6 MIPSのスーパミニコンピュータを使用した。描画時間を調べた時に使用したものと同じ16M DRAMの典型的な3レイヤのデータを作成した。各々のレイヤで、左側はノ

図18. Mフォーマットの構造

図19. MEXフォーマットの構造

図20. 可変成形電子ビーム描画用データの変換フロー

一マルトーン、すなわち重複除去処理のみに対するデータ作成時間と示し、右側はリバーストーン、すなわち重複除去処理と白黒反転処理に対するデータ作成時間を示す。ハッチングを施した棒グラフは、階層構造すなわちMEXフォーマットを利用した場合のデータ作成時間を示し、ハッチングを施していない棒グラフは、従来の階層構造を持たないMフォーマットを利用した場合のデータ作成時間を示す。MEXフォーマットの階層構造を利用することにより、データ作成時間は大幅に短縮されたことが分かる。データ作成時間は、1レイヤ当たり65.7分で、従来法の10%程度であった。

図22に、最終的に作られた可変成形電子ビーム描画用データのデータ量を示す。データ量は、データ作成時間と同様にMEXフォーマットを利用することにより大幅に減少している。1レイヤ当たりのデータ量は、39.4メガバイトで、レイヤBのリバーストーンを除いては従来法の10%程度であった。レイヤBは、重複除去処理と白黒反転処理を施すと、大量の图形が結合して一つの非常に大きな图形を形成するため、従来法でもデータ量が少ないという非常に特殊なケースであった。

図21. 可変成形電子ビーム描画用データの変換時間

図22. 可変成形電子ビーム描画用データのデータ量

以上の結果より、新しく開発したデータ作成システムは、16M DRAMの電子ビーム描画用データ作成に非常に効果的であることが分かる。

以上述べてきたことをまとめると、可変成形電子ビーム描画装置JBX-6 A IIIを用いて、高スループットで、16M DRAM用5倍レティクルを作成することが可能になった。描画用データは、特殊な階層構造を利用したデータ作成用システムを構築して作成した。データ作成時間とデータ量は、1レイヤ当たりそれぞれ66分及び39メガバイトであった。レティクルの描画時間は、1レイヤ当たり100分であった。このレティクル作成技術は、64M DRAMに代表される、いわゆるULSI用フォトマスクの作成にも適用されるであろう。

## 5. むすび

以上、当社16M及び64M DRAMに向けたメモリセル構造及びマスク技術の成果を軸に、最先端DRAMプロセス技術の現状を紹介した。比例縮小則を指導原理に素子の微細化によって実現してきたLSIの高集積化は、極限に向けたプロセス技術の一層の努力と異分野との融合など新しいコンセプトに基づいた展開とによって、今後も止まることなく拡大し、高性能・低価格化への市場要求を満たしつつ21世紀高度情報化社会に貢献していくであろう。

## 参考文献

- (1) 宮本ほか：三菱電機技報, 63, No.11, p.23 (1989)

- (2) W. Wakamiya, et al. : International Electron Device Meeting Tech. Dig., p.246 (1988)

- (3) W. Wakamiya, et al. : Symposium on VLSI Technology Dig., p.69 (1989)

- (4) M. H. Shearer, et al. : Improvements in the JBX-6AIII series of shaped beam lithography tools, Proc. SPIE, 923, p.290 (1988)

- (5) T. Kato, et al. : Technologies for electron beam direct writing, Microelectronic Engineering 1, p.69 (1983)

# 4 Mビット ダイナミックRAM

宮本博司\* 長山安治\*\*\*

長友正男\*\* 水津克巳\*\*\*

山田通裕\*\*

## 1. まえがき

ダイナミックRAM(DRAM)は大容量化と高性能化を同時に達成することにより、大型コンピュータから通信機器、OA機器まで幅広く使用されている。DRAMの開発の流れの中で、高速化・低消費電力化の要請にこたえて1MビットでCMOSタイプのDRAMが本格的に登場し、CMOSの特長を生かして、高速動作モードなどの機能の拡張を行った。当社では市場からの更なる大容量化・高性能化の要請にこたえるべく4M DRAMの開発を進めてきた。4M DRAMの開発における課題の一つはメモリセルの三次元化である。当社は、ISSCC87(1987 IEEE International Solid-State Circuits Conference)において、FASIC(Folded bit-line Adaptive Side-wall Isolated Capacitor)セルと名付けた三次元セルを採用した4M DRAMを発表した<sup>(1)</sup>。しかし、今回量産的見地からJEDEC(Joint Electron Device Engineering Council)で標準化された350ミル幅のSOJ(Small Outline Package with J-lead)に適合した4M DRAMをスタックト(Stacked, 積み上げ)型セルを採用して開発した。

本稿では、今回開発した4M DRAMの特長及び技術について述べるとともに、その電気的特性を紹介する。

## 2. 4M DRAMの設計

### 2.1 4M DRAMの特長

4M DRAMは1M DRAMまでのDRAMの開発の延長線上にあるとはいえる<sup>(2)(3)(4)(5)(6)(7)</sup>、1M DRAMと比較しても種々の新しい技術を採用した。4M DRAMと1M DRAMの主な相違点は、表1に示すように、DRAMの心臓部とも言うべきメモリセルをプレーナ型からスタックト型に変更した点、テストモードをスーパーV<sub>cc</sub>印加方式からJEDECで標準化されたタイミングでセット及びリセットを行う方式に変更した点、パッケージの幅が300ミルから350ミルに変更になった点が挙げられる。これら、プロセス技術、回路技術、テスト技術、アセンブリ技術、更には、信頼性技術を駆使して開発した4M DRAMの特長は次のとおりである。

- (1) 高速アクセス時間( $t_{RAC}=80\text{ns}$ )：16MHzの高速32ビットマイクロプロセッサにキャッシュメモリなしで対応できる。

- (2) 低消費電力：動作時の電源電流が $I_c=190\text{ns}$ で約60mA(実力値)である。

- (3)  $\times 1$ 構成品と $\times 4$ 構成品をAlマスクで切り替えていたため生産性に優れている。

- (4) 高速アクセス機能：高速ページ( $\times 1, \times 4$ )、ニブル( $\times 1$ )、スタティックコラム( $\times 1, \times 4$ )モードの高速アクセス機能と、ライトペーブット機能( $\times 4$ )を備え、これらの機能をすべてアセンブリ工程のワイヤボンディングで切り替えていたため、顧客の品種要望に柔軟に対応できる。

- (5) スタックトキャパシタセル及び0.8μmCMOSプロセス技術の

採用により十分なメモリセル容量を確保し、高い信頼性を実現している。

(6) テストの容易性：JEDECで標準化された8ビット同時にテストできるテストモードを備えることにより、テスト時間を短縮できる。

(7) パッケージ展開：350ミル幅のSOJと400ミル高のZIP(Zig-zag In-line Package)に収納可能であるとともに、各パッケージに最適なパッド配置をアセンブリ工程のワイヤリングで切り替えていたため、顧客の品種要望に迅速に対応できる。

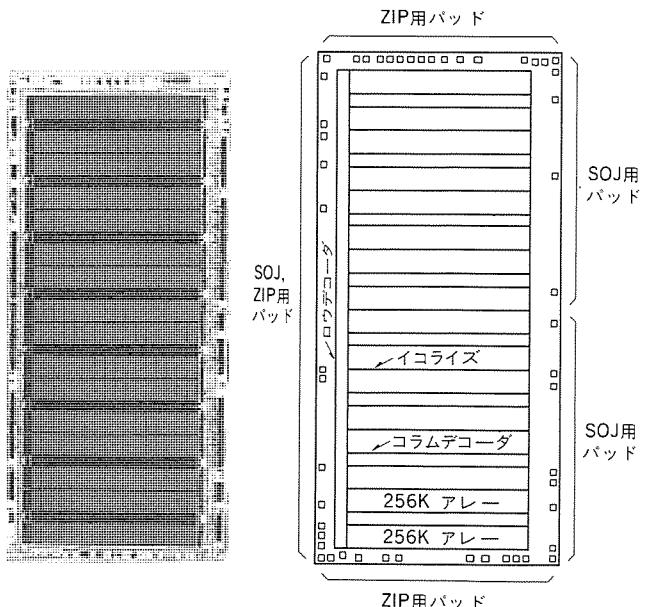

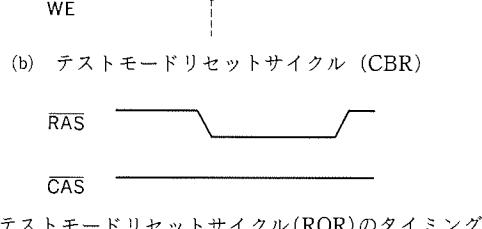

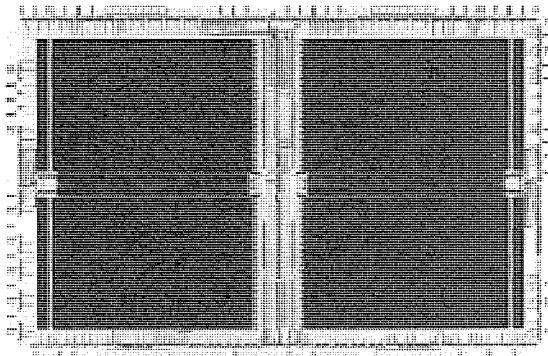

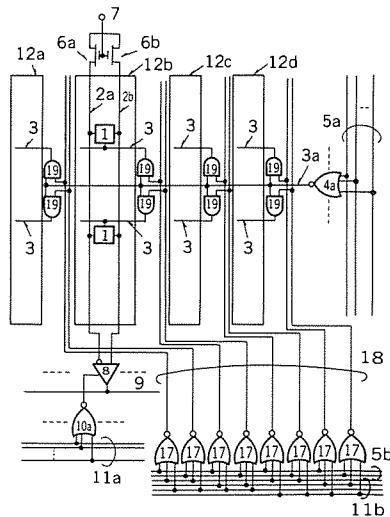

### 2.2 チップ構成

4M DRAMのチップ写真を図1に、ブロック図を図2に示す。構成は4M×1と1M×4をAlマスクにより切り替えていた。チップサイズは6.84mm×14.95mm(=102.3mm<sup>2</sup>)、メモリセルサイズは2.4μm×5.2μm(=12.5μm<sup>2</sup>)である。図に示すように、メモリセルアレーは8個の512Kビットのブロックに分割されており、各512Kビットのブロックは、センスアンプ及びコラムデコーダによって更に2個の256Kビットのサブブロックに分割されている。256Kビットのサブブロックは256ロウ×1024コラムから成っており、1本の

表1. 1M DRAMと4M DRAMの相違点

|           | 1M DRAM                            | 4M DRAM                        |

|-----------|------------------------------------|--------------------------------|

| メモリ キャパシタ | プレーナ型                              | スタックト型                         |

| テストモード    | 4ビット並列<br>スーパーV <sub>cc</sub> 印加方式 | 8ビット並列<br>タイミング方式<br>(JEDEC標準) |

| SOJ パッケージ | 300ミル幅                             | 350ミル幅                         |

図1. 4M DRAMのチップ

図2. 4M DRAMのブロック図

図3. 4 M DRAMのパッケージ

図4. アドレスバッファ

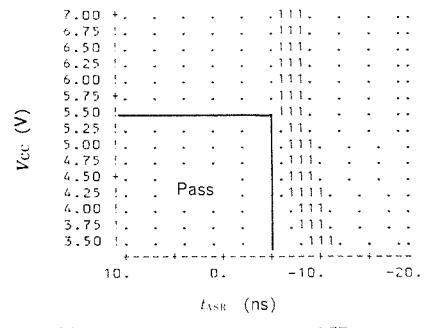

(a) ロウアドレスホールド時間t<sub>ASR</sub>(b) ロウアドレスセットアップ時間t<sub>RAH</sub>

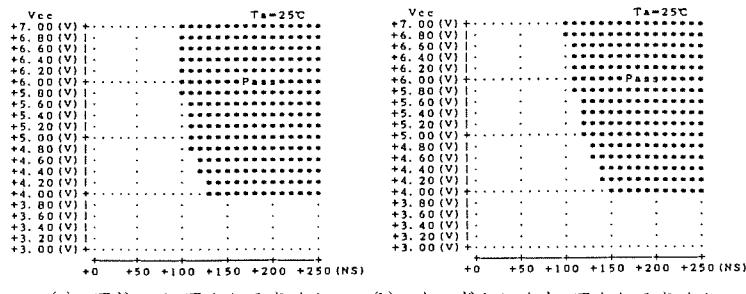

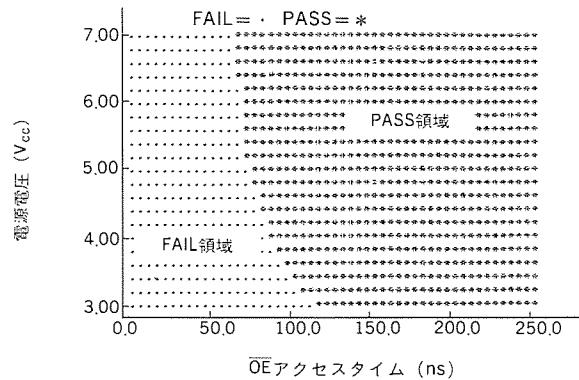

図5. シュムープロット

ビット線に128個のメモリセルが接続されている。ロウデコーダはコラムデータと直交する形でメモリセルアレーの端に設けられている。ビット線はタンクスチタンによるポリサイド（ポリシリコンとタンクスチタンシリサイドの二重層）構造であり、ワード線はポリシリコンにより形成されている。各RASサイクルにおいて8個の512Kブロックのうち2個のみを動作させることにより、電源電流を低減させて

いる。冗長回路としては、1 M DRAMで実績のあるレーザプログラム方式を採用した。8 ロウ及び8 コラム分のスペアメモリセルを設けて、歩留りの向上を図っている。

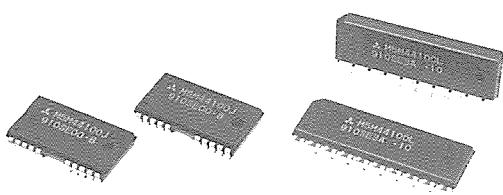

ボンディングパッドはメモリセルアレーを囲むようにチップの4辺に沿って配置されている。ボンディングパッドのうち一方の長辺に沿う位置に配置されたものは、SOJ及びZIPのどちらのパッケージに収納する場合にも使用される。これに対し、チップのもう一方の長辺に沿って配置されたパッドはSOJに収納する場合にのみ使用し、短辺に沿う位置に配置されたパッドはZIPに収納する場合にのみ使用することにより、各パッケージに対してパッド配置を最適にしている。パッケージによって切り替えるパッドについては、同一信号の2個のパッドを設け、これらのうち一方のパッドからの信号のみを内部回路へ伝達する。パッケージに対応したパッドの切替えは、1個の選択パッドへのワイヤボンディングによって行う。図3にSOJ及びZIPのパッケージ写真を示す。

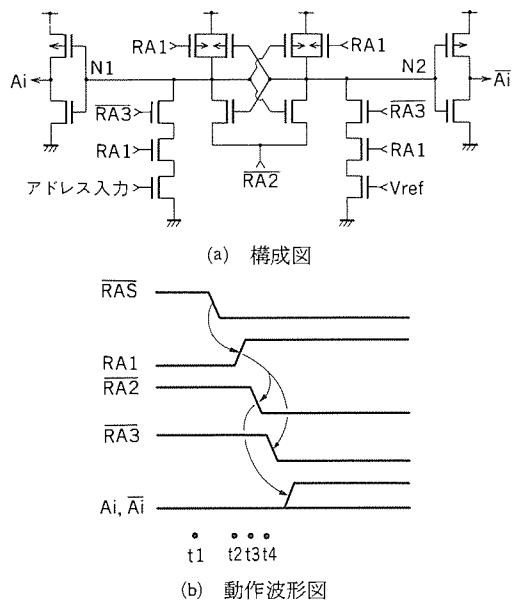

### 2.3 アドレスバッファ

アクセス時間の高速化はDRAMを開発する際の主要な目標の一つである。RASアクセス時間の高速化を妨げる原因の一つに、ロウアドレスホールド時間t<sub>RAH</sub>がある。すなわち、メモリに外部からロウアドレスを印加する際、RASを“L”レベルにした後t<sub>RAH</sub>の期間はロウアドレスを保持する必要がある。実際にどのくらいの時間ロウアドレスを保持する必要があるかは、ロウアドレスバッファの構成に依存している。t<sub>RAH</sub>の実力値が短いことは、アドレスバッファの回路が早く動作することを意味し、その結果RASアクセス時間が短縮される。

図4(a), (b)は各々、4 M DRAMに採用したアドレスバッファの構成図と動作波形図である。バッファ回路は1個のCMOSラッチ回路と二つの入力回路で構成されており、各入力回路は直列接続された3個のnチャネルトランジスタから成る。バッファの動作は次のとおりである。

t<sub>1</sub>：プリチャージ状態であり、信号RA1は“L”レベル、信号RA3は“H”レベルになっている。

t<sub>2</sub>：RAS信号が“L”になることにより信号RA1が“H”レベルになり、外部アドレス信号がバッファ内に伝達される。

t<sub>3</sub>：信号RA2が“L”レベルになりCMOSラッチ回路が活性化されて、外部アドレス信号のレベルを判定する。

t<sub>4</sub>：信号RA3が“L”レベルになり、外部アドレス信号の受付を止める。

一連の動作のなかで、入力回路が外部アドレス信号を受け付け始める信号RA1の立ち上がりエッジと、外部アドレス信号の受付を止める信号RA3の立ち下がりエッジとによって、入力回路はワンショット動作を行う。この実効的なワンショットパルスは二つの別々の信号によって形成されるため、単独の信号で形成した場合に比べて、パルス幅が狭い場合でも十分に高いレベルのワンショットパルスを得ることができる。したがって、外部アドレスが入力回路からラッチ回路に高速に伝達され、ロウアドレスホールド時間を短くできる。

上記アドレスバッファを備えた4 M DRAMのロウアドレスセットアップ時間t<sub>ASR</sub>とロウアドレスホールド時間t<sub>RAH</sub>の室温におけるシュムープロットを図5(a)及び(b)に示す。t<sub>ASR</sub>はV<sub>CC</sub>=5.5Vで-5 nsであり、t<sub>RAH</sub>はV<sub>CC</sub>=4.5Vで6 nsである。|t<sub>ASR</sub>|とt<sub>RAH</sub>の差はわずか1 nsであり、アドレスバッファが高速に動作していることが分かる。

図6. 4 M DRAMのデータ入出力系の構成

図7. テストモードセットサイクル

る。

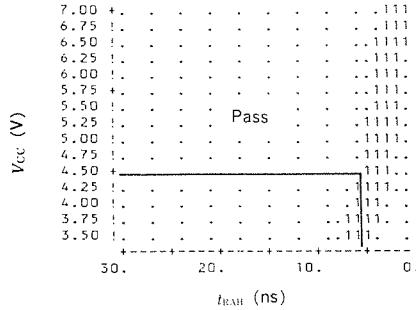

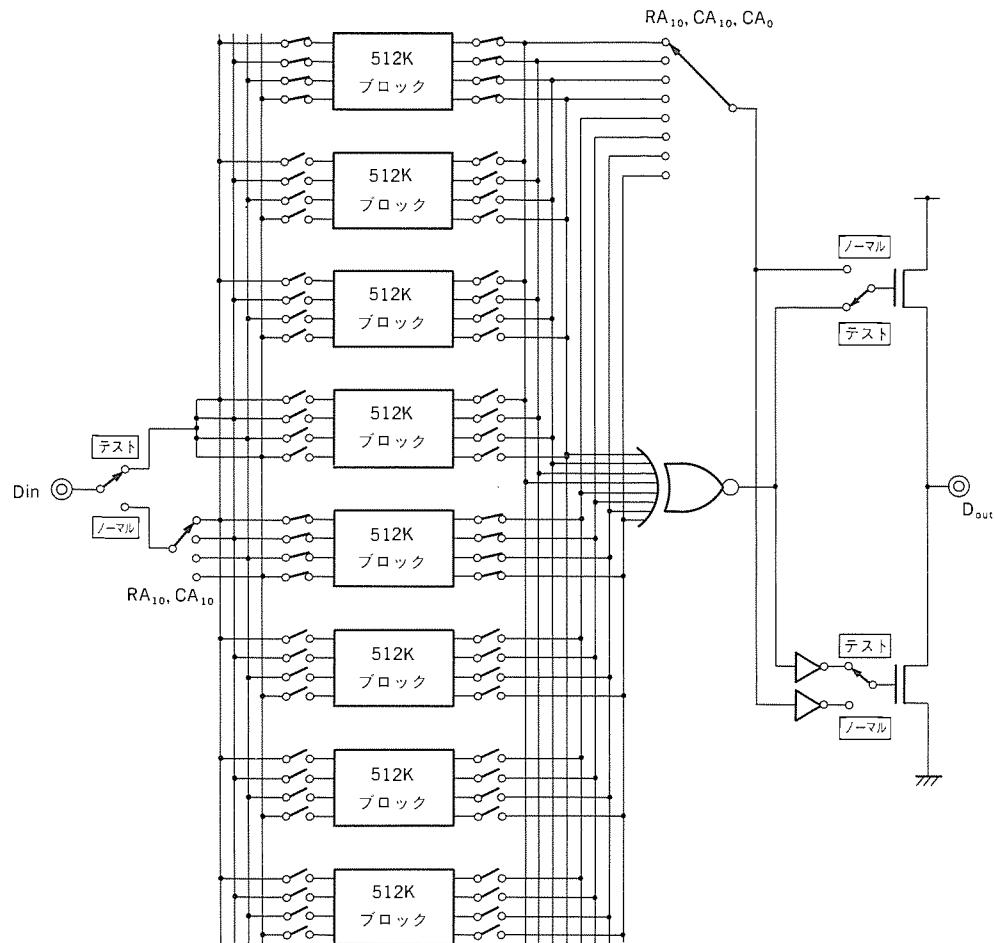

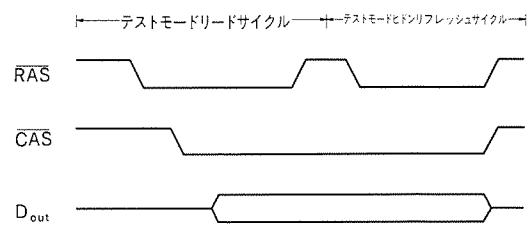

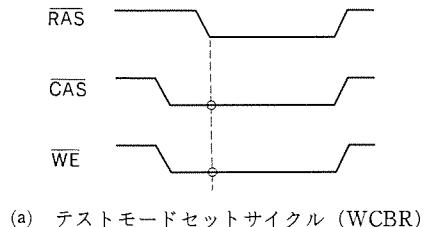

#### 2.4 テストモード

DRAMのテスト時間はビット数の増大に伴い指数関数的に増加する。テスト時間を短縮してテストコストを低減するためには、複数ビット同時にテストできるテストモードの採用が有効である。4 M DRAMでは8ビット同時にテストでき、タイミングでセット及

びリセットを行うテストモードを採用了。×1ビット構成品のノーマルモード及びテストモードにおけるデータ入出力系の構成を図6に示す。テストモード期間中は三つのアドレス、すなわち、ロウアドレスの最上位ビットRA<sub>10</sub>とコラムアドレスの最上位ビットCA<sub>10</sub>、更に、コラムアドレスの最下位ビットCA<sub>0</sub>が不要になる。テストモードライトサイクルには、同一データが8ビット同時に書き込まれる。テストモードリードサイクルには8ビットのデータが同時に読み出され、読み出しデータのEXNOR (Exclusive NOR) データがD<sub>out</sub>端子に出力される。8ビットの読み出しデータがすべて同じ ("H"又は "L") のときD<sub>out</sub>に "1" が出力され、1ビットでもデータが異なるときはD<sub>out</sub>に "0" が出力される。

テストモードのセット及びリセットのタイミングは、図7に示すように信号のタイミングの組合せによって行う。ノーマルモードからテストモードへの切替えは図7(a)に示すWE&CASビフォアRAS (WCBR) サイクルで行う。一方、テストモードからノーマルモードへの切替えには図7(b)及び(c)に示すように、テストモード中にCASビフォアRAS (CBR) サイクル又はRASオンリーリフレッシュ

図9. メモリセルの断面図

図10. RASアクセス時間( $t_{RAC}$ )の電源電圧( $V_{cc}$ )依存性(周囲温度25°C)

(ROR)サイクルを行う。テストモード中にリフレッシュを行う場合にはWCBRサイクルを再度行うほか、図8に示すようにヒドリフリッシュも可能である。テストモードの使用によって4M DRAMを512K DRAMのようにテストすることができ、テスト時間はN系パターンで1/8に短縮できる。

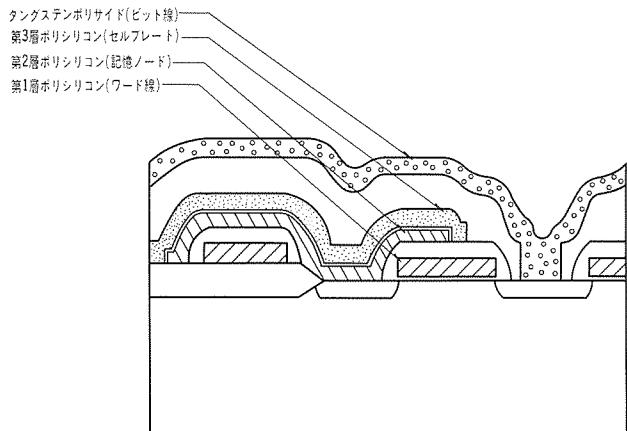

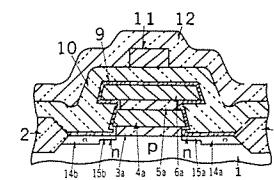

### 3. プロセス技術とメモリセル構造

4M DRAMではメモリセル面積が小さくなり、1M DRAMで採用したプレーナ型キャパシタでは十分なメモリセル容量が確保できないため、三次元構造のメモリセルが必要となる。種々の三次元構造のメモリセルについて検討した結果としてスタックト型メモリセルを採用した。メモリセルの断面図を図9に示す。2層目と3層目のポリシリコンの間の100Å(酸化膜換算)の絶縁膜によってメモリセルキャパシタを形成している。スタックト型メモリセルの特長は、メモリセル容量部分の接合面積が小さいため、ポーズリフレッシュ特性が良好であり、アルファ線ソフトエラーに対しても強いことである。リフレッシュ特性、ソフトエラー率ともに1M DRAMと同等以上の性能を持っている。

プロセスは、0.8μmツインウェルCMOSプロセスを採用した。配

表2. 4M DRAMの性能一覧

|           |                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------|

| 構成        | 4M語×1ビット、1M語×4ビット<br>(Alマスク切替え)                                                                  |

| チップサイズ    | 6.84×14.95mm <sup>2</sup>                                                                        |

| セルサイズ     | 2.4×5.2μm <sup>2</sup>                                                                           |

| プロセス技術    | 0.8μm ツインウェルCMOS<br>3層ポリシリコン、1層ポリサイド、1層Al                                                        |

| メモリキャパシタ  | スタックト型                                                                                           |

| RASアクセス時間 | 58ns                                                                                             |

| 動作時平均電源電流 | 60mA<br>(サイクル時間=190ns)                                                                           |

| 待機時電源電流   | 0.2mA<br>(CMOS入力レベル)                                                                             |

| 動作モード     | $V_{cc}=5V$<br>高速ページ、スタティックコラム<br>(×1, ボンディング切替え)<br>高速ページ、スタティックコラム、ライトバーピット<br>(×4, ボンディング切替え) |

| テストモード    | 8ビット並列タイミング方式<br>(JEDEC標準)                                                                       |

| 冗長回路      | 8コウ 8コラム (レーザプログラム)                                                                              |

| パッケージ     | 350ミルSOJ<br>400ミルZIP                                                                             |

線層は3層ポリシリコン、1層ポリサイド、1層Alである。

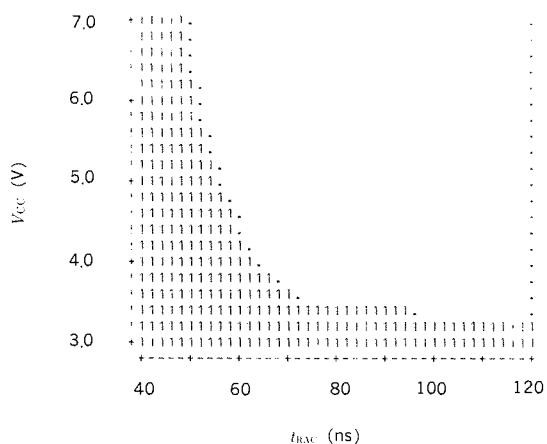

### 4. 電気的特性

図10は周囲温度25°CにおけるRASアクセス時間( $t_{RAC}$ )の電源電圧( $V_{cc}$ )依存性を示すシュムープロット図で、負荷条件は100pFを付加した等価的な2TTL負荷である。 $V_{cc}=5V$ において $t_{RAC}=58ns$ の高速動作を達成している。また、 $V_{cc}=5V$ 、サイクル時間190nsにおける動作平均電源電流は60mA、待機時の電源電流はCMOS入力レベルで0.2mAである。表2に4M DRAMの性能一覧を示す。

### 5. むすび

0.8μmツインウェルCMOSプロセスを駆使して4M DRAMを開発した。メモリセルにスタックトキャパシタを採用してソフトエラーに対して強いメモリセルを実現した。8ビット並列テストモードを備えることによりテスト時間の短縮を可能にした。4M×1構成と1M×4構成をAl工程のマスクで切り替えるとともに、×1構成品では高速ページ、ニブル及びスタティックコラムモードをボンディングで切り替え、×4構成品では高速ページ、スタティックコラムモード及びライトバーピット機能をボンディングで切り替えてるので生産性に優れている。×1構成品、×4構成品ともに350ミル幅SOJ及び400ミル高ZIPに収納する。今回開発した4M DRAMは、1M DRAMの次世代のメモリとして市場の要求に十分にこたえ得ると確信している。

### 参考文献

- (1) K. Mashiko, et al.: A 90ns 4M DRAM in a 300mil DIP, ISSCC Dig. Tech. Papers, p.12 (1987-2)

- (2) 谷口ほか: 三菱電機技報, 55, No.5, p.368 (昭56)

- (3) 山田ほか: 三菱電機技報, 58, No.8, p.535 (昭59)

- (4) 熊野谷ほか: 三菱電機技報, 59, No.9, p.676 (昭60)

- (5) 藤島ほか: 三菱電機技報, 60, No.3, p.205 (昭61)

- (6) 山田ほか: 三菱電機技報, 61, No.7, p.581 (昭62)

- (7) 山田ほか: 三菱電機技報, 62, No.8, p.653 (昭63)

# 高速 1 MビットCMOSスタティックRAM

菅野雅直\* 向井孝夫\*\*

和田知久\*\* 河野芳雄\*\*

杠 幸二郎\*\*

## 1. まえがき

電子機器・コンピュータによる高度情報化社会において、超LSIはその原動力として急速な進歩を遂げている。そのうえ、システムが高性能化されるにつれ、超LSIは高速化・大容量化・低消費電力化が要求されている。

MOSスタティックRAM (SRAM) は、動作タイミングが簡単で使いやすく、さらに高速なアクセス時間が得られるといった利点があり、OA機器・ICカード・LSIテストなど広範囲の製品に利用されている。また、最近、高速かつ大容量のSRAMは、コンピュータの性能を上げるためにスーパーコンピュータ・超大型コンピュータのメインメモリへと新しいニーズが広がりつつある。

以上のような市場動向の中で、当社では高抵抗負荷型メモリセルを用いた最大アクセスタイム35nsの高速 1 Mビット CMOS SRAM<sup>(1)</sup>を開発した。本稿では、このRAMの開発方針、設計、製造プロセス技術及び電気的特性について紹介する。

## 2. 開発の基本方針

RAMの大容量化は、プロセスの微細技術によって達成が可能である。しかしながら、RAMの大容量化に伴い、

- (1) RAMをテストする時間が長くなる。

- (2) 寄生容量・抵抗が増大してアクセス時間が大きくなる。

- (3) RAM自体のスイッチングノイズにより、動作マージンの低下をもたらす。

- といった問題が生じる。高速・大容量SRAM実現のために、以上の問題点を十分に考慮し、回路・パターンレイアウト・プロセス技術の面での開発方針を以下のように設定した。

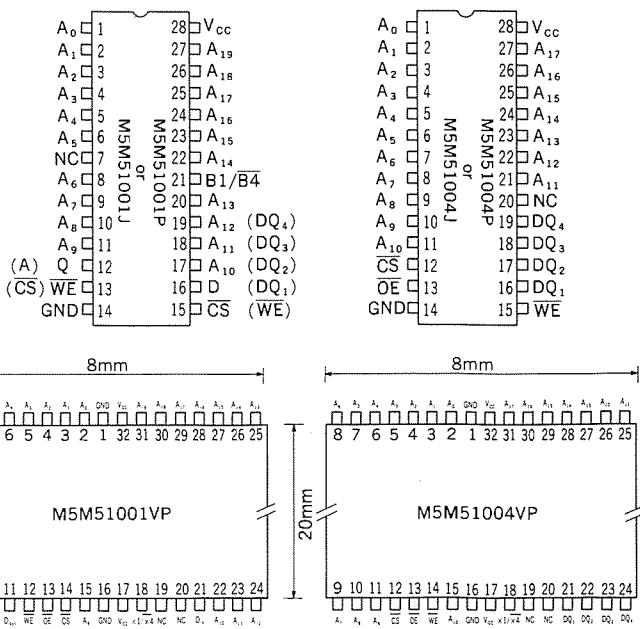

### (1) ビット構成

#### (a) 1 M語×1ビット構成 (M5M51001)

外部から電気的信号を与えることで、内部回路が256K語×4ビット構成に切り替わるテスト時間短縮モード付き。

#### (b) 256K語×4ビット構成 (M5M51004)

(a), (b)をアルミ配線マスクの差し替えのみで作り分ける(アルミマスクスライス)。

### (2) パッケージ対応

●28ピン 400ミル幅 プラスチックDIP

●28ピン 400ミル幅 プラスチックSOJ

●32ピン 8mm×20mm プラスチックTSOP

上記3種類をアルミマスクスライスで作り分ける。ピン配置を図1に示す。

### (3) 高速アクセス時間

最大アクセス時間を35ns/45nsとし、1 Mビットで初の35ns品を実現する。

### (4) 低消費電力

内部同期回路、及び変形分割ワード線選択方式を用いることによ

り、過渡電流を極力抑えて、最小サイクルでの最大平均電流、及びピーク電流を軽減する。また、待機時には、内部回路の貫通電流経路を遮断することにより、高速品でありながら待機時消費電流を小さく抑える。

### (5) プロセス

最先端のフォトリソグラフィ技術・イオン注入技術・多層配線技術などのプロセスを駆使して、0.7μm設計ルールの3層ポリシリコン2層アルミ構造のデバイスを実現する。

## 3. 設計技術

### 3.1 チップ構成

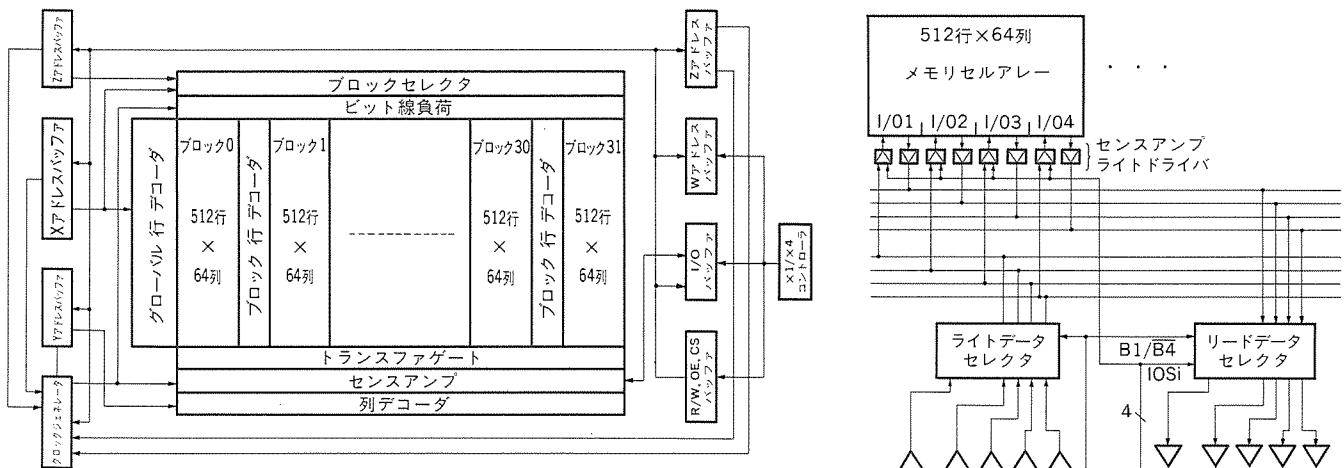

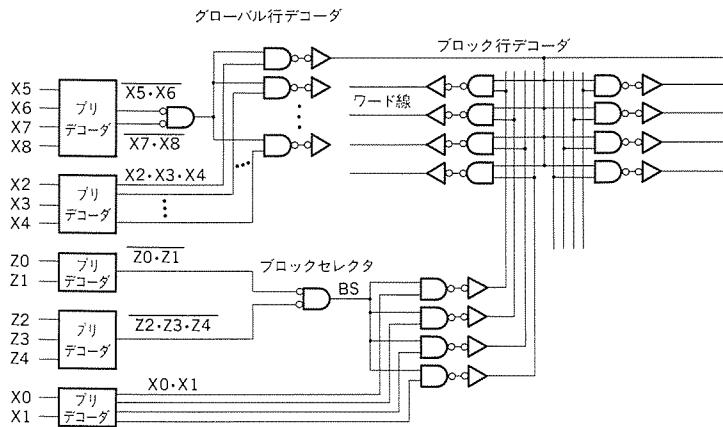

M5M51001/4のブロック構成を図2に示す。これは、×1構成・×4構成の両方に共通である。M5M51001 (1M語×1ビット) では×1/×4コントローラにより、ビット構成が1M語×1ビットから256K語×4ビットに切替えが可能である。

任意のメモリセルを選択するために、アドレス入力は四つのグループ(X, Y, Z, W)に分かれており、X, Y, Zはそれぞれ行選択・列選択・ブロック選択に使用し、WはM5M51001に追加されるアドレス入力信号である。

メモリセルアレーは、全体で512行×2048列から構成され、これをワード線方向に32のブロックに分割して、1ブロックは、512行×64列と1本の予備列から成っている。したがって、1本のワード線長は65列分と短く、かつその材料として低抵抗のタンゲステンポリサイドを用いているので、ワード線での遅延が0.5nsに抑えられ高速化に寄与している。各ブロックは、さらに512行×16列から成る四つのサブブロックに分割されており、それぞれにセンスアンプを配置

図1. ピン配置

図2. ブロック構成

図3. ワード線選択回路

して256K語×4ビットに対応させている。

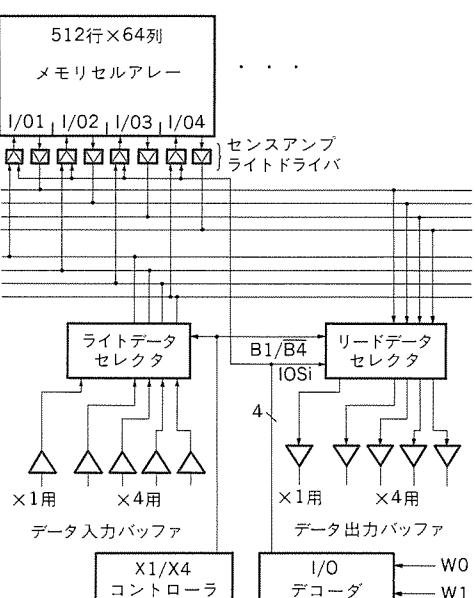

### 3.2 変形分割ワード線選択方式

高速1MビットSRAMでは、当社独自のワード線選択方式を用いている。図3にワード線選択回路を示す。これは、1本の行を1本の行選択線で選択する従来の方式を改良し、複数の行の組を選択する行グループ選択を用いた分割ワード線構成である。

X0～X8及びZ0～Z4は、それぞれ行選択・ブロック選択のアドレス入力信号である。Xアドレスの上位X2～X8は、グローバル行デコーダでプリデコードされ、行グループ選択線を活性化する。ここで行グループは4行から成っており、グループ内の1本の行は、ブロック行デコーダ内でXアドレスの下位X0・X1のプリデコード信号によって選択される。したがって、選択される列の数は、1／(ブロック数)であるため、カラム電流は1／32となり大幅に低減できる。また、行グループ選択線を第2層アルミで形成することにより、高速化も同時に達成している。

### 3.3 ビット構成可変機能

通常RAMのテスト方法は、DC的なパラメータテストとAC的な動作機能テストから成っている。比較的テスト時間の短いNパターン(Nはメモリ容量)と呼ばれるテストパターンを用いると、ACテスト時間はメモリ容量に比例して増大する。

したがって、1MビットSRAMでは、単純に256KSRAMの4倍近いテスト時間を必要とするため、今回テスト時間を低減する目的でビット構成可変機能を1M語×1ビット(M5M51001)に適用した。M5M51001は、1M語×1ビットと256K語×4ビット構成が可能

図4. ビット構成可変方式ブロック図

表1. プロセスパラメータ

| 項目                    | 高速256K SRAM<br>M5M51257/5258 | 高速1M SRAM<br>M5M51001/51004 |

|-----------------------|------------------------------|-----------------------------|

| プロセス方式                | 2層ボリSi1層 AI<br>MoSixボリサイド    | 3層ボリSi2層 AI<br>WSixボリサイド    |

| ゲート電極                 | MoSixボリサイド                   | WSixボリサイド                   |

| トランジスタ構造              | LDD構造                        | 修正LDD構造                     |

| 素子分離法                 | LOCOS                        | 修正LOCOS                     |

| ゲート長 (NMOS) (μm)      | 1.1                          | 0.8                         |

| ゲート長 (PMOS) (μm)      | 1.6                          | 1.0                         |

| ゲート酸化膜厚 (nm)          | 22                           | 18                          |

| n+拡散層 (線幅/間隔) (μm)    | 1.3/1.2                      | 0.9/0.8                     |

| ポリシリコン (線幅/間隔) (μm)   | 1.0/1.0                      | 1.0/0.7                     |

| 第一アルミニ配線 (線幅/間隔) (μm) | 1.8/1.6                      | 1.4/1.0                     |

| 第二アルミニ配線 (線幅/間隔) (μm) | —                            | 2.6/1.4                     |

| コンタクト (μm)            | 1.2×1.3                      | 0.8×0.8                     |

| スルーホール                | —                            | 1.0×1.0                     |

で、その切替えは×1／×4コントローラによって制御されている。図4にビット構成可変方式のブロック図を示す。一つのメモリセルブロックは、4本のリードデータバスに接続されている。1M語×1ビット構成の場合、4本のデータバス信号のうち、リードデータバス切替回路によって1本選択され、その信号が出力バッファに転送される。また、256K語×4ビット構成の場合は、4本のデータバス信号がそのまま四つの出力バッファに転送される。このため、テスト時のアクセス経路と通常のアクセス経路が同じで、1M語×1ビット構成時のアクセス時間を保ったままテスト時間が低減される。

### 3.4 動作マージンの拡大

高速RAMにおいては、駆動能力の大きなトランジスタ、特に出力トランジスタが動作するときに発生する電源線・接地線のノイズが動作マージンの低下をもたらす。

このRAMにおいては、上記のノイズ対策として出力トランジスタをNch-Nchトランジスタで構成し、出力の小振幅化を図っている。また、内部回路でノイズを吸収するような遅延回路を設けたり、あるいは電源線・接地線の配線などの工夫によって、内部回路の電位安定化がなされることにより、動作マージンの拡大が可能となっている。

#### 4. 製造プロセス

このRAMの製造プロセスは、N基板ツインウェルCMOS、3層ポリシリコン（ポリサイドを含む。）、2層アルミプロセスから成り、中速1MSRAMのプロセス<sup>(2)</sup>にアルミ多層配線技術を付加したフローとなっている。

大容量高速SRAMにおいては、パッケージサイズからの制約によるメモリセルの縮小化と、高速性を追求するためにトランジスタの高性能化や寄生容量の低減及び配線の低抵抗化を図らなければならない。

##### 4.1 メモリセル形成技術

表1に、1.0μm設計ルールの高速256KビットSRAM<sup>(3)</sup>との主要なプロセスパラメータの比較を示す。メモリセルの形成法、レイアウトはほぼ中速1MビットSRAMを踏襲している。すなわち、第1ポリシリコン（WSixポリサイド）はゲート電極及びワード線に、第2ポリシリコンは電源線とクロスカップル線に、第3ポリシリコンは高抵抗に、第1アルミはビット線に、N<sup>+</sup>拡散層はトランジスタのソース・ドレイン、接地線及びクロスカップル線に用いている。第2アルミは、セルアレー中ではブロック行デコーダに用いているため、ビット線と垂直方向に4セルごとに1本配置されている。図5はブロック行デコーダ及びメモリセル近傍における第2アルミ配線形成後の顕微鏡写真を示す。

0.7μm設計ルールのメモリセルを量産レベルで安定して形成するためには、新規なプロセス技術が必要である。フォトリソグラフィ技術においては、高感度レジスト、高NAステッパーの採用により全層シングルレジスト化を達成した。さらに、反射強度が強いアルミ工程においては、反射を抑制して下地の影響によるハレーションを防いでいる。また、メモリセルの素子分離には修正LOCOS法を採用し、バーズピークを片側0.15μm以下に抑制している。

高速SRAMでは、待機時消費電流の規格値は緩くなっているのが一般的であるが、バッテリバックアップも可能とするため、高抵抗には専用の薄膜ポリシリコンを採用することにより、中速1MビットSRAMと同レベルの低い待機時消費電流を達成している。

##### 4.2 高速化技術

アクセス時間と最も密接な関係にあるのは、トランジスタ性能である。高速SRAM用トランジスタに求められている特性は、単に電流増幅率が高いのみならず、ホットキャリア効果を防止するために、LDD構造の採用によりドレイン近傍の電界を緩和することが一般的に行われている。しかしながら、通常のLDD構造ではN<sup>-</sup>層の不純物濃度が低いためにソース抵抗が高く、電流増幅率が低下するという問題がある。このため、修正LDD構造を採用することにより、電流増幅率を犠牲とすることなく信頼性の高いトランジスタ形成が可能となっている。

高速化手法としてトランジスタの高性能化以外に、アルミ多層配線技術が挙げられる。アルミは、抵抗が低いため配線材料としては最も使い易い材料であるが、融点が低く高温プロセスが使えない、エレクトロマイグレーション、ヒロック、スライドが発生しやすい等かかえている問題点も多い。高速大容量SRAMでは流れる電流が大きく、かつ自らのICが発生するノイズにより誤動作の危険がある。このため、周辺回路においては、できるだけアルミ配線幅を広くすることが望ましい。しかしながら、パッケージ幅の制約条件によりチップサイズの拡大が困難なため、1層アルミプロセス方式で

はアルミ配線幅は制限されることが多い。2層アルミ方式では、電源線に幅広い第2アルミ配線を採用することにより、ノイズ対策が容易となっている。メモリセルアレー中では、第2アルミ配線は行グループ選択線に用いられているために、配線ピッチは23.5μmと非常に緩くなっている。当社では、完全CMOS型メモリセルの16KSRAM<sup>(4)</sup>においてアルミ多層配線を採用し、第2アルミ配線をビット線に用いていた。高抵抗負荷型メモリセルにおいては、ビット線を第2アルミ配線にすることにより接地線を低抵抗な第1アルミ配線にすることが可能となり、メモリセルの安定化動作が期待される。しかしながら、第2アルミ配線のピッチが約3μmと厳しくなるために、アルミの層間膜を十分に平たん化する技術が必要となり、また歩留りの点で懸念されるためビット線としては用いていない。

前述のように、アルミ多層配線技術の信頼性保証は重要なテーマである。エレクトロマイグレーション対策として、第1及び第2アルミ配線材料にはAlSiCuを採用している。また、スルーホール内のアルミのカバレッジを改善するために、スルーホールをテーパーエッチしている。また、コンタクト内に形成されるシリコン析出の防止及び接合部への銅汚染を防ぐために、TiNのバリアメタルを採用している。

ブロック行デコーダに第2アルミ配線を採用することにより、高速にワード線を立ち上げることが可能となり、またビット線容量を低減できるため高速動作が可能となっている。

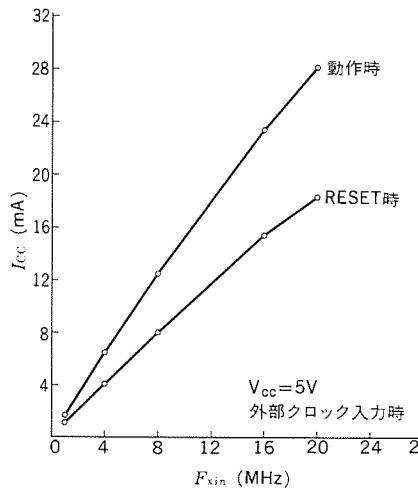

#### 5. 電気特性

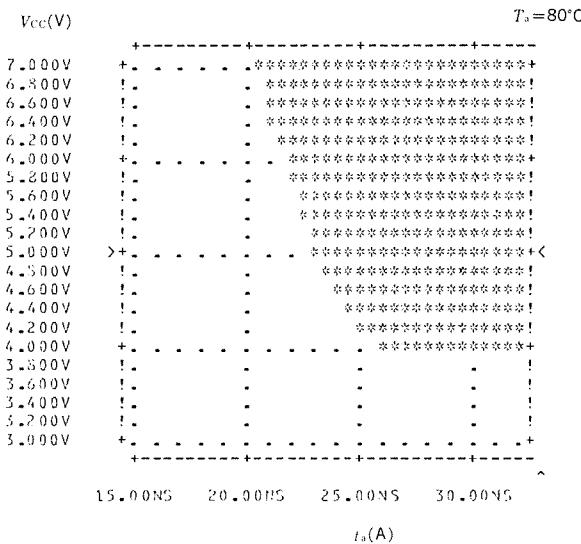

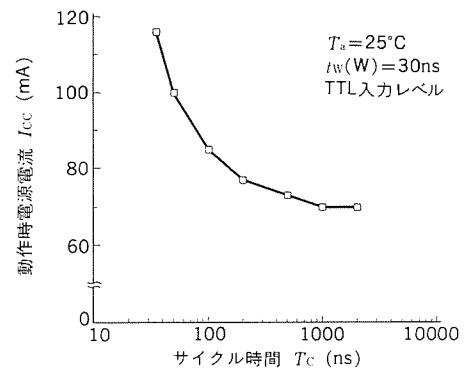

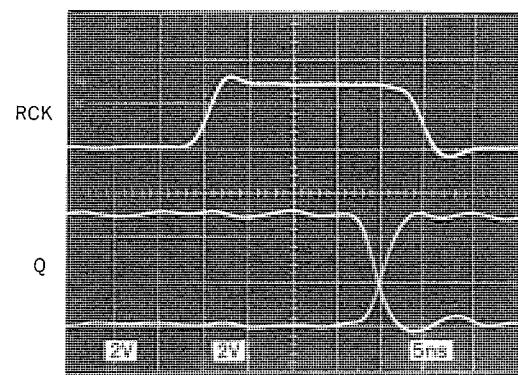

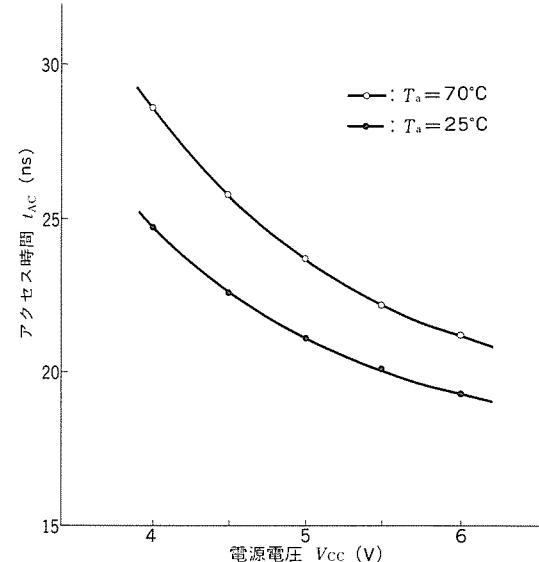

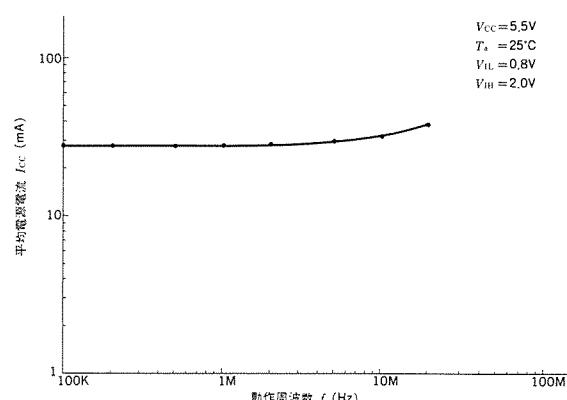

高速1MビットSRAMのチップ写真を図6に示す。チップサイズは6.10mm×15.84mmで、28ピン400ミル幅のプラスチックSOJ、DIP及び8mm×20mmのTSOPに収納可能である。図7は、電源電圧V<sub>cc</sub>=5.0V、室温時での出力波形写真で、アドレスアクセス時間t<sub>a</sub>(A)=14nsを示している。高温時のアクセス時間特性を図8に示し、T<sub>a</sub>=80°C、V<sub>cc</sub>=4.5Vの最悪条件でT<sub>a</sub>(A)=24nsと高速性を保っていることが分かる。動作時における電源電流I<sub>cc1</sub>のサイクル時間依存性を図9に示す。最小サイクル時間35nsのとき、I<sub>cc1</sub>は116mAとなって

図5. 第2アルミ配線形成後のブロック行デコーダ及びメモリセル近傍の写真

図6. チップ写真

図 7. 出力波形写真

図 8. アクセス時間特性のシムプロット

いる。待機時には周辺回路での直流電流をすべて遮断するので、待機時消費電流 $I_{cc2}$ はメモリセルの高抵抗ポリシリコン負荷に流れる電流のみで決まる。したがって、 $T_a=70^\circ\text{C}$ での待機時最大 $100\mu\text{A}$ 以下と小さい。高速 1 M ピット SRAM の性能一覧を表 2 にまとめる。

## 6. むすび

このRAMの特長をまとめると次のとおりである。

- (1) 0.7μm設計ルールの3層ポリシリコン2層アルミ構造を、最先端のプロセス技術を駆使し、高抵抗負荷型NMOSメモリセルを用いた最大アクセス時間35nsの高速 1 M ピット CMOS SRAM を実現している。

- (2) 複数の行の組を選択する行グループ選択を用いた変形分割ワード線方式を導入することにより、チップサイズを増大させることなしにワード線での遅延時間を0.5nsに抑え、かつピット線容量を15%

図 9. 電源電流特性

表 2. 高速 1 M ピット SRAM の性能一覧

|                    |                                              |

|--------------------|----------------------------------------------|

| 構成                 | IM語×1ピット (M5M51001)<br>256K語×4ピット (M5M51004) |

| プロセス               | 3層ポリシリコン 2層アルミ<br>ツインウェルCMOS<br>高抵抗負荷型NMOS   |

| メモリセル              | 5.875×8.5 (49.9μm <sup>2</sup> )             |

| メモリセルサイズ (μm)      | 6.10×15.84 (96.6mm <sup>2</sup> )            |

| チップサイズ (mm)        | 5V単一<br>TTL                                  |

| 使用電源               | 35/45 (最大)                                   |

| 入出力レベル             | 35/45 (最大)                                   |

| アドレスアクセス時間 (ns)    | 35/45 (最小)                                   |

| チップセレクト アクセス時間(ns) | 35/45 (最大)                                   |

| サイクル時間(ns)         | 120 (最大)                                     |

| 電源電流動作時 (mA)       | 10 (最大)                                      |

| 待機時 (mA)           |                                              |

程度低減している。

(3) ピット構成可変機能を 1 M 語 × 1 ピット構成に適用したことにより、通常のアクセス経路でテスト時間を  $N$  パターン ( $N$  はメモリ容量) で  $1/4$  に短縮している。

今後も高速 1 M ピット SRAM で培った技術を土台にして、高速化・大容量化を進める予定である。

## 参考文献

- (1) Y. Kohno : IEEE Journal of Solid-State Circuits, 23, No. 5, p.1060 (1988)

- (2) 広瀬ほか : 三菱電機技報, 62, No. 6, p.81 (1988)

- (3) 一瀬ほか : 三菱電機技報, 61, No. 4, p.73 (1987)

- (4) 有田ほか : 三菱電機技報, 57, No. 2, p.58 (1983)

# 5 V単一電源で動作する高速 1 Mビット EEPROM

寺田 康\* 味香夏夫\*

有馬秀明\*\*

小林和男\*\*

## 1. まえがき

EEPROM(Electrically Erasable and Programmable Read Only Memory)は、電気的に書換え可能な不揮発性メモリであり 5 V 単一電源で動作するという優れた特徴を持つため幅広い応用が期待されているが、これまで集積度がDRAMやSRAMに比べて低く、高集積化が望まれていた。今回、 $1 \mu\text{m}$  CMOSプロセスを用いて 1 Mビット EEPROMを試作したので、その技術内容について報告する。

## 2. 開発のねらい

1 Mビット EEPROMの開発に当たって目標としたのは、

- (1) チップサイズの縮小による低コスト化。

- (2) 高速アクセス時間

- (3) ECC (Error Checking and Correcting) 回路内蔵による高信頼性の確保。

であった。ECCを内蔵した場合チップサイズを決定する要因は、メモリセルのサイズ及びエラー訂正に要する検査ビット数となる。

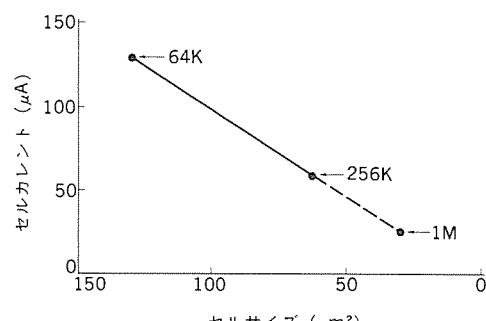

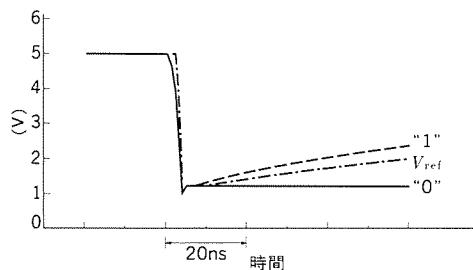

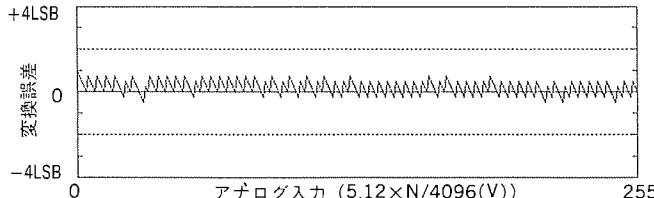

フローティングゲート型メモリセルでは、薄い酸化膜(トンネル酸化膜と呼ばれる)中の電子のトンネル現象を利用して消去・書き込みを行うが、データ保持特性を保証するためには酸化膜厚をあまり薄くできない。すなわちスケーリングができない。また、容量結合を利用してフローティングゲートの電位を変化させトンネル酸化膜に高電界を印加するために、メモリトランジスタの各ノード間の容量結合比を64K, 256Kと同程度に保たなければならない。このような制限の下でセルサイズの縮小を行わなければならない。さらに、セルサイズを縮小するとメモリセルを流れる電流(セルカレント)が減少する。図1にテストデバイスで測定したセルカレントとセルサイズの関係を示す。高速アクセスのためには高感度のセンスアンプの開発が必ず(須)となる。

このため、

- (1) 3層ポリシリコン型メモリセル

- (2) 非選択メモリアレーを利用した新しい差動型センス手法

- (3) 2バイト(16ビット)で5ビットのパリティビットを生成するECC回路

の開発を行った。以下、これらについて説明する。

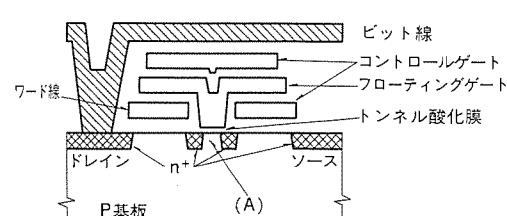

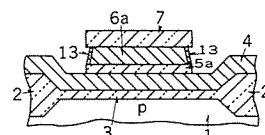

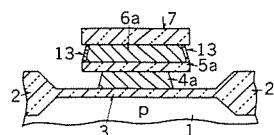

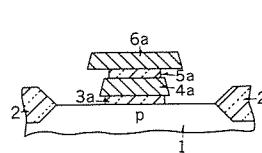

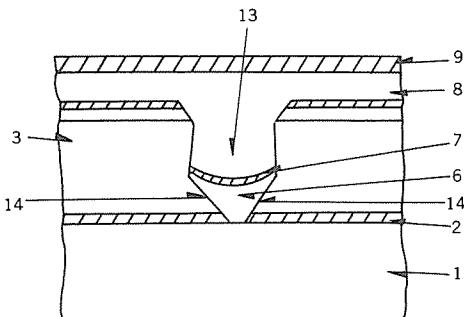

## 3. SSTRメモリセル<sup>(1)</sup>

図2に、SSTR(Stacked floating gate with Self-aligned Tunnel Region)と名付けられたメモリセルの断面図を示す。セルサイズは $3.8 \mu\text{m} \times 8.0 \mu\text{m}$ である。第1層目のポリシリコンで選択トランジスタ(ワード線に接続されている)と下層のコントロールゲートが形成されている。第2層目でフローティングゲートが、第3層目で上層のコントロールゲートが形成されている。下層と上層のコントロールゲートは電気的に接続されている。トンネル酸化膜の膜厚は90Åであり、64K EEPROM(トンネル酸化膜厚100Å)からほとん

ど変化していない。

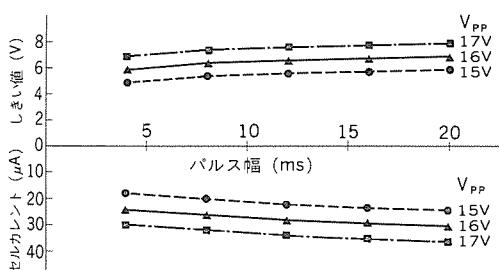

消去はコントロールゲートに高圧パルスを印加しドレインを接地することにより行われる。トンネル酸化膜に高電界が印加され電子がフローティングゲートに注入されることによりメモリトランジスタ(図2中の(A)の部分)のしきい値が高くなる。書き込みは、ドレン並びに選択トランジスタに高圧パルスを印加し、コントロールゲートを接地することにより行われる。フローティングゲートに注入された電子が引き抜かれメモリトランジスタのしきい値が低くなる。読み出しはコントロールゲートに読み出し電圧(2~3V)を印加したときにメモリトランジスタがオンするかどうか、すなわち選択されたメモリセルを介して電流が流れるか否かを検出することにより行われる。メモリセルの書き込み・消去特性を図3に示す。セルカレントはドレン電位1V、コントロールゲート電位2Vの条件下測定されている。16V、4msの高圧パルスにより十分な深さに書き込み・消去が行われていることが分かる。これは、従来1層であったコントロールゲートを2層のポリシリコンでフローティングゲートをサンドイッチするよう形成したのでセルサイズが小さいにもかかわらず高い容量結合比が得られ、16Vという低い電圧でもトンネル酸化膜に大きな電界を印加することができるところによる。また、高圧パルスの立ち上がり時定数は400μsに設定されている。これはトンネル酸化膜に過大な電界が印加されるのを防ぐためである。

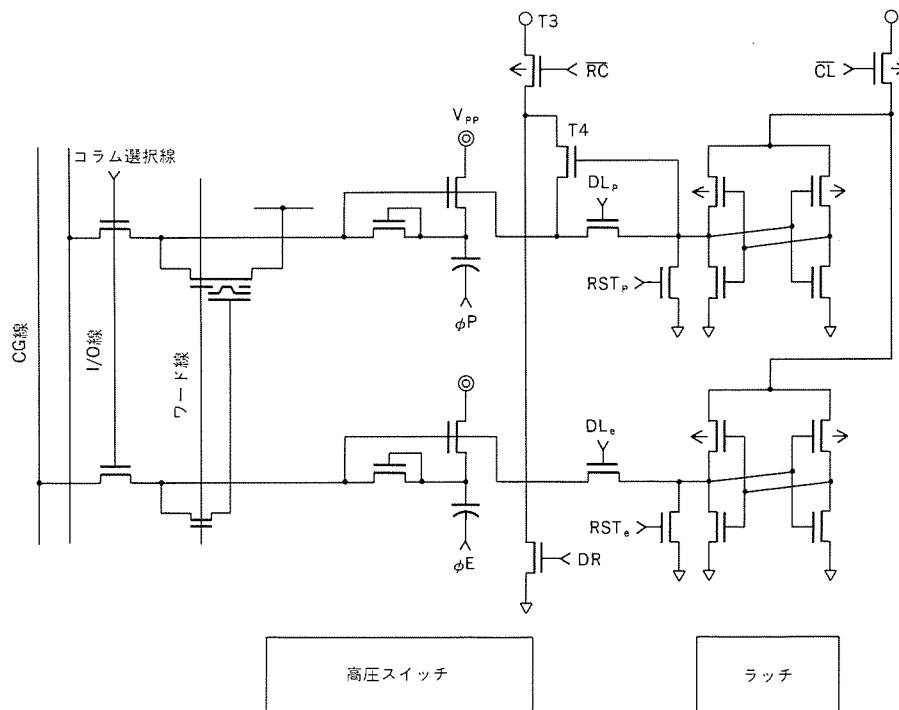

## 4. 回路技術

今回、1 Mビット EEPROMの開発に当たって工夫を行った回路のうちセンスアンプ及びEEPROM特有の回路であるコラムラッチについて説明する<sup>(2)~(4)</sup>。コラムラッチはビット線ごとに設けられたラッチのことであり実効的な書き込み時間の短縮のための回路であ

図1. セルカレントとセルサイズの関係

図2. SSTRメモリセルの断面図

る。

#### 4.1 ダミーセルを要しない差動型センスアンプ

EPROMやEEPROMではメモリセルに電流が流れるか否かを検出して書き込まれたデータが“1”であるか“0”であるかを判定する電流センス型センスアンプが用いられている。セルカレントがセルサイズとともに減少するのでセンスアンプの高感度化が必要となるが、これはアクセス時間の遅延を引き起こす。高速化のためにはダミーセルを用いて差動増幅をすることが有効でありEPROMでは一般に用いられているが、EEPROMではダミーセルを用いることは困難である。これは、EEPROMでは紫外線を照射することによりチップ全体の一括消去を行うためメモリセルの特性とダミーセルの特性を同じにすることが可能であるが、EEPROMではバイト単位で書き換えるためメモリセルの特性にばらつきが生じることと、書き込み・消去された状態はいずれもフローティングゲートが電気的に中性な状態ではないことによる。

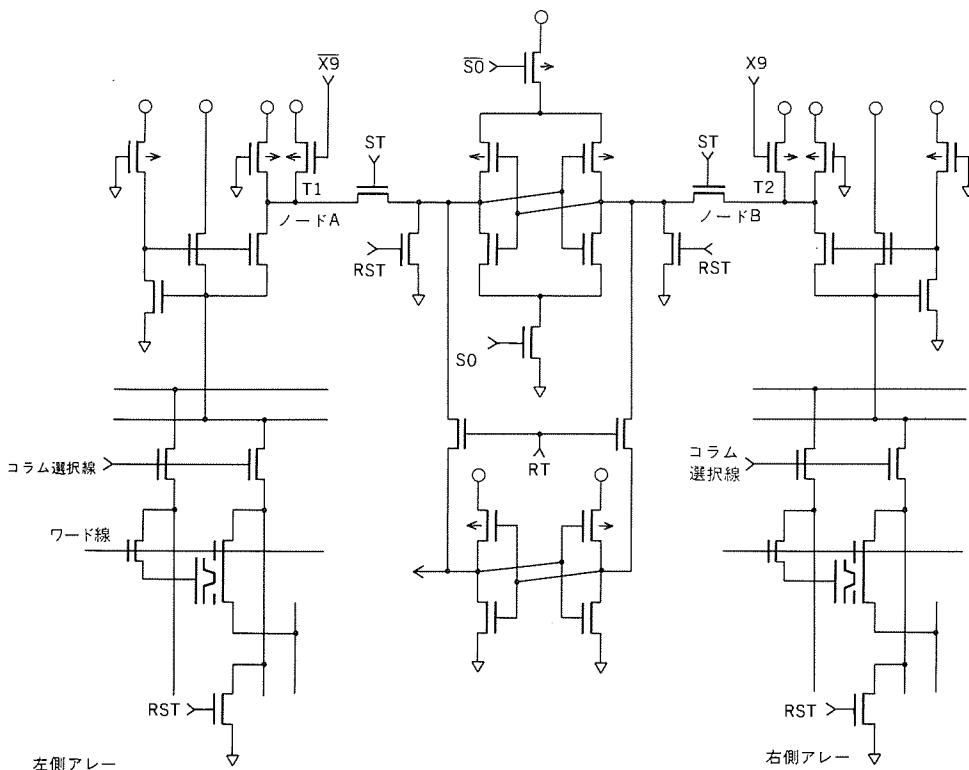

そこで、ダミーセルを要しない差動型センスアンプの開発を行った。図4にセンスアンプの回路図を示す。センスアンプは電流センス回路・差動増幅器・ラッチから構成されている。メモリアレーを2分割し、各々に電流センス回路を設け、非選択側のメモリアレーを利用してリファレンスレベルを設定し、差動型センスを行おうとするものである。各電流センス回路の出力・ノードA・ノードBが差

動増幅器に入力されている。